US 20170301619A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2017/0301619 A1

## Alur et al.

# Oct. 19, 2017 (43) **Pub. Date:**

### (54) INTEGRATED CIRCUIT SURFACE LAYER WITH ADHESION-FUNCTIONAL GROUP

- (71) Applicant: Intel Corporation, Santa Clara, CA (US)

- (72) Inventors: Siddharth K. Alur, Chandler, AZ (US); Sri Chaitra J. Chavali, Chandler, AZ (US); Robert A. May, Chandler, AZ (US); Whitney M. Bryks, Chandler, AZ (US)

- (21) Appl. No.: 15/641,117

- (22) Filed: Jul. 3, 2017

#### **Related U.S. Application Data**

(62) Division of application No. 14/972,936, filed on Dec. 17, 2015, now Pat. No. 9,728,500.

#### **Publication Classification**

(51) Int. Cl.

| H01L 23/528  | (2006.01) |

|--------------|-----------|

| H01L 21/768  | (2006.01) |

| H01L 21/3205 | (2006.01) |

| H01L 21/3105 | (2006.01) |

| H01L 21/02   | (2006.01) |

| H01L 21/768<br>H01L 21/02 | (2006.01)<br>(2006.01) |

|---------------------------|------------------------|

| H01L 21/02                | (2006.01)              |

|                           |                        |

(52) U.S. Cl. CPC ..... H01L 23/528 (2013.01); H01L 21/76841 (2013.01); H01L 21/76834 (2013.01); H01L 21/02118 (2013.01); H01L 21/31058 (2013.01); H01L 21/02282 (2013.01); H01L **21/32051** (2013.01)

#### (57)ABSTRACT

Embodiments of the present disclosure describe an integrated circuit and associated fabrication techniques and configurations, which may include forming on at least one of a metal layer or a polymer layer of an integrated circuit die a surface layer that includes an adhesion-functional group, and applying to the surface layer a next layer to adhere to the surface layer with the adhesion-functional group. In embodiments wherein the at least one of the metal layer or the polymer layer is a polymer layer, forming the surface layer may include copolymerizing on the polymer layer a polar monomer that includes the adhesion-functional group. In embodiments wherein the at least one of the metal layer or the polymer layer is a metal layer, forming the surface layer may include forming on the metal layer a self-assembled monolayer that includes amine group terminations. Other embodiments may be described and/or claimed.

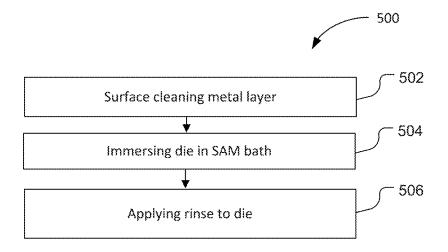

FIG. 5

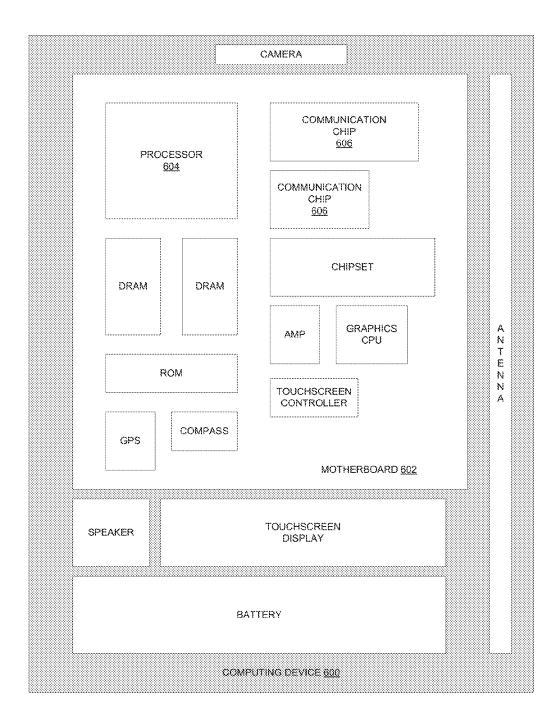

FIG. 6

### INTEGRATED CIRCUIT SURFACE LAYER WITH ADHESION-FUNCTIONAL GROUP

### CROSS REFERENCE TO RELATED APPLICATION

**[0001]** This application is a divisional application of U.S. patent application Ser. No. 14/972,936, entitled "INTE-GRATED CIRCUIT SURFACE LAYER WITH ADHE-SION-FUNCTIONAL GROUP", filed Dec. 17, 2015, and claims priority to the Ser. No. 14/972,936 application. The Specification of Ser. No. 14/972,936 is hereby fully incorporated by reference.

#### TECHNICAL FIELD

**[0002]** Embodiments of the present disclosure generally relate to the field of integrated circuits, and more particularly, to adhesion-receptive surfaces for integrated circuit die layers and associated techniques and configurations.

#### BACKGROUND

**[0003]** Currently, integrated circuit dies include successive layers, such as polymer/polymer, polymer/metal or polymer/silica, between which there may be low adhesion. Techniques to improve adhesion between polymer/polymer and polymer/silica layers may include plasma or ultra-violet (UV) treatment of the surfaces to enhance the surface area or surface energy. Techniques to improve adhesion between polymer and an underlying metal layer may include etching of the metal, but etching may degrade electrical performance or patterning.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0004]** Embodiments will be readily understood by the following detailed description in conjunction with the accompanying drawings. To facilitate this description, like reference numerals designate like structural elements. Embodiments are illustrated by way of example, and not by way of limitation, in the figures of the accompanying drawings.

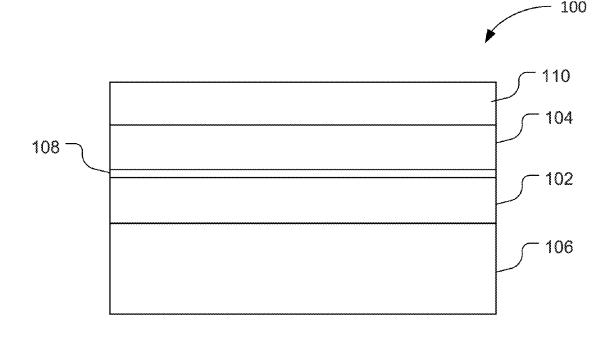

**[0005]** FIG. **1** schematically illustrates a cross-section view of an example integrated circuit (IC) die, in accordance with some embodiments.

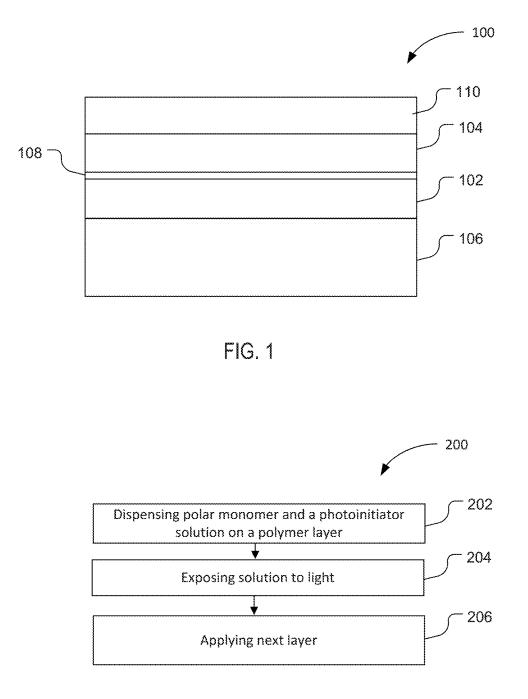

**[0006]** FIG. **2** schematically illustrates a flow diagram for a method of fabricating an IC, in accordance with some embodiments.

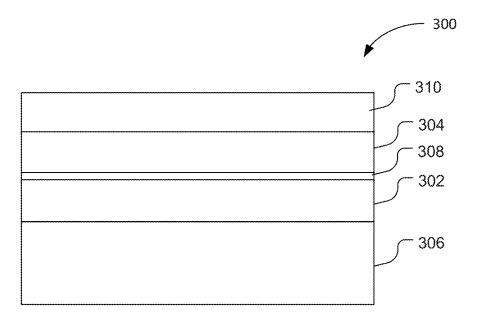

**[0007]** FIG. **3** schematically illustrates a cross-section view of another example IC die, in accordance with some embodiments.

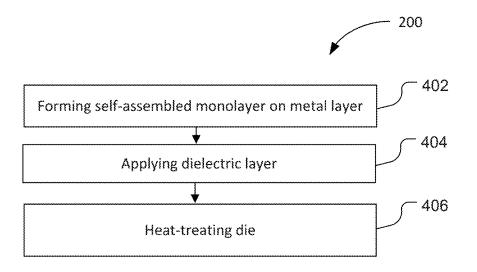

**[0008]** FIG. **4** schematically illustrates a flow diagram for another method of fabricating an IC, in accordance with some embodiments.

**[0009]** FIG. **5** schematically illustrates a flow diagram for a method of forming a self-assembled monolayer (SAM) on a metal layer of a die, in accordance with some embodiments.

**[0010]** FIG. **6** schematically illustrates a computing device incorporating some aspects of embodiments described herein, in accordance with some embodiments.

#### DETAILED DESCRIPTION

**[0011]** Embodiments of the present disclosure describe an integrated circuit and associated fabrication techniques and

configurations, which may include forming on at least one of a metal layer or a polymer layer of an integrated circuit die a surface layer that includes an adhesion-functional group, and applying to the surface layer a next layer to adhere to the surface layer with the adhesion-functional group. In embodiments wherein the at least one of the metal layer or the polymer layer is a polymer layer, forming the surface layer may include copolymerizing on the polymer layer a polar monomer that includes the adhesion-functional group. In embodiments wherein the at least one of the metal layer or the polymer layer is a metal layer, forming the surface layer may include forming on the metal layer a self-assembled monolayer that includes amine group terminations.

**[0012]** In the following detailed description, reference is made to the accompanying drawings which form a part hereof, wherein like numerals designate like parts throughout, and in which is shown by way of illustration embodiments in which the subject matter of the present disclosure may be practiced. It is to be understood that other embodiments may be utilized and structural or logical changes may be made without departing from the scope of the present disclosure. Therefore, the following detailed description is not to be taken in a limiting sense, and the scope of embodiments is defined by the appended claims and their equivalents.

**[0013]** For the purposes of the present disclosure, the phrase "A and/or B" means (A), (B), or (A and B). For the purposes of the present disclosure, the phrase "A, B, and/or C" means (A), (B), (C), (A and B), (A and C), (B and C), or (A, B and C).

**[0014]** The description may use the phrases "in an embodiment," or "in embodiments," which may each refer to one or more of the same or different embodiments. Furthermore, the terms "comprising," "including," "having," and the like, as used with respect to embodiments of the present disclosure, are synonymous.

**[0015]** The term "coupled with," along with its derivatives, may be used herein. "Coupled" may mean one or more of the following. "Coupled" may mean that two or more elements are in direct physical or electrical contact. However, "coupled" may also mean that two or more elements indirectly contact each other, but yet still cooperate or interact with each other, and may mean that one or more other elements are coupled or connected between the elements that are said to be coupled with each other.

**[0016]** In various embodiments, the phrase "a first layer formed on a second layer" may mean that the first layer is formed over the second layer, and at least a part of the first layer may be in direct contact (e.g., direct physical and/or electrical contact) or indirect contact (e.g., having one or more other layers between the first layer and the second layer) with at least a part of the second layer.

**[0017]** In various embodiments, the phrase "a first feature formed, deposited, or otherwise disposed on a second feature," may mean that the first feature is formed, deposited, or disposed over the second feature, and at least a part of the first feature may be in direct contact (e.g., direct physical and/or electrical contact) or indirect contact (e.g., having one or more other features between the first feature and the second feature) with at least a part of the second feature.

**[0018]** FIG. **1** schematically illustrates a cross-section view of an example integrated circuit (IC) die **100** with layers **102** and **104**, in accordance with some embodiments. The die **100** may represent a discrete product made on a

substrate of semiconductor material (e.g., silicon) using semiconductor fabrication techniques such as thin film deposition, lithography, etching, and the like used in connection with forming IC devices. In embodiments, the die **100** may be, include, or be a part of a radio frequency (RF) die, a processor, memory, system-on-chip (SoC), or ASIC, for example.

[0019] Layers 102 and 104 may be two of two or more layers that are included in die 100. In embodiments, layer 102 may be of or include a polymer and may be referred to as polymer layer 102. Polymer layer 102 may be formed upon one or more die layers 106 (only one shown), which may include a semiconductor substrate. Layer 104 may be applied to die 100 after polymer layer 102 and may be formed of or include metal, silica or polymer. An adhesionreceptive surface 108 may be formed between layers 102 and 104 to enhance adhesion between them. The adhesionreceptive surface 108 enhance adhesion between layers 102 and 104 without adversely affecting mechanical and/or electrical properties of the bulk of polymer layer 102.

**[0020]** In embodiments, a layer **110** may optionally be applied to die **100** after layer **104**. Layer **104** and/or **110** may be incorporated onto die **100** or may be an embedding or encapsulating material that embeds or encapsulates die **100** in or as part of an IC package or package assembly (not shown).

**[0021]** FIG. 2 schematically illustrates a flow diagram for a method 200 of fabricating an IC, in accordance with some embodiments. The method 200 may comport with the configuration of die 100 in FIG. 1, for example.

[0022] At 202, the method 200 may include dispensing on a polymer layer of a die a solution that includes a polar monomer and a photoinitiator. In embodiments, the polymer layer may be polymer layer 102, and the polar monomer may include an adhesion-functional group that functionalizes adhesion between the polymer layer and the next layer. In embodiments, the functional group may include an amine group if the next layer includes or is of silica, a cyano group if the next layer includes or is of a metal such as copper (Cu), or a hydroxyl group if the next layer includes or is of a polymer. Dispensing the solution on the polymer layer may include applying the solution in liquid form, such as by dipping the die and the polymer layer into the solution. In other embodiments, the polar monomer may include more than one adhesion-functional group to functionalize adhesion between the polymer layer and the next layer. In embodiments, the more than one functional groups may include an amine group and a cyano group if the next layer includes or is of a metal such as copper, or may include an amine group and a hydroxyl group if the next layer includes or is of silica.

**[0023]** At **204**, the method **200** may include exposing the solution on the polymer layer to light to form on the polymer layer an adhesion-receptive polymer surface, which may also be referred to as a surface layer that includes an adhesion-functional group. In embodiments, the light may be ultra-violet light that may graft copolymerize the polar monomer on the polymer layer to form the adhesion-receptive polymer surface. The adhesion-receptive surface **108** of FIG. **1**.

**[0024]** At **206**, the method **200** may include applying a next layer to the adhesion-receptive polymer surface to affix the next layer to the polymer layer. In embodiments, the next

layer applied to the adhesion-receptive polymer surface may be formed of or include materials that may include metal, silica, or polymer. The next layer may correspond to layer 104 of FIG. 1. In embodiments, the next layer may be of or include silica if the functional group of the polar monomer at 202 includes an amine group, the next layer may be of or include a metal such as copper (Cu) if the functional group of the polar monomer at 202 includes a cyano group, or the next layer may be of or include a polymer if the functional group of the polar monomer at 202 includes or a hydroxyl group. In other embodiments, the next layer may be of or include a metal such as copper if the polar monomer includes more than one adhesion-functional group, such as an amine group and a cyano group, and the next layer may be of or include silica if the polar monomer includes more than one adhesion-functional group, such as an amine group and a hydroxyl group.

[0025] The method 200 may provide to polymer layer 102 the adhesion-receptive surface layer 108 without affecting properties of the bulk of polymer layer 102. In embodiments, polymer layer 102 may be free from adhesionfunctional groups by which adhesion-receptive surface layer 108 may functionalize adhesion between polymer layer 102 and the next layer 104. Adhesion-functional groups included in the bulk of polymer layer 102 may adversely affect mechanical and/or electrical properties of polymer layer 102, including any or all of high modulus, low CTE, low dielectric loss, etc., which may adversely affect reliability of an IC. Polymer layer 102 may be free from adhesionfunctional groups such that adhesion-functional groups are completely or sufficiently absent from the bulk of polymer layer 102 that its mechanical and/or electrical properties are substantially unchanged. In embodiments, adhesion-receptive surface layer 108 may include an adhesion-functional group, and polymer layer 102 may be free from the adhesion-functional group.

[0026] In embodiments, the adhesion-receptive polymer surface provided by method 200 may be very thin (40-50 nm) and uniform. The uniformity may smooth out issues that may be observed after some wet or dry process treatments. The adhesion-receptive polymer surface provided by method 200 may also enable polymer surfaces with higher surface energy and wettability. In embodiments, polar functional groups (e.g., carboxylic acid, amides, alcohols, etc.) may be employed to improve surface energy and/or wettability without resorting to plasma or UV treatment. If used for a solder resist layer, for example, method 200 may resolve or decrease solder resist surface transparency issues. [0027] Die embedding in a polymer material may be employed in some IC packages and package assemblies, including system-in-package technologies that may include more than one IC die. Delamination between an embedded IC die and an encapsulating dielectric may be a serious reliability issue. Method 200 may improve wettability for subsequent polymers included in mold, underfill, or encapsulant materials. A polymer or dielectric may be functionalized through graft polymerization with adhesion-functional groups, which may include amines or silanols, to bind embedding surfaces with greater reliability.

**[0028]** FIG. **3** schematically illustrates a cross-section view of another example IC die **300** with layers **302** and **304**, in accordance with some embodiments. The die **300** may represent a discrete product made on a substrate of semiconductor material (e.g., silicon) using semiconductor fabrication techniques such as thin film deposition, lithography, etching, and the like used in connection with forming IC devices. In embodiments, the die **300** may be, include, or be a part of a radio frequency (RF) die, a processor, memory, system-on-chip (SoC), or ASIC, for example.

[0029] Layers 302 and 304 may be two of two or more layers that are included in die 300. In embodiments, layer 302 may be of or include a metal (e.g., copper) and may be referred to as metal layer 302. Metal layer 302 may be formed upon one or more die layers 306 (only one shown), which may include a semiconductor substrate. Layer 304 may be applied to die 300 after metal layer 302 and may be formed of or include polymer. An adhesion-receptive surface 308 may be formed between layers 302 and 304 to enhance adhesion between them. In embodiments, a layer 310 may optionally be applied to die 300 after layer 304. Layer 304 and/or 310 may be incorporated onto die 300 or may be an embedding or encapsulating material that embeds or encapsulates die 300 in or as part of an IC package or package assembly (not shown).

[0030] FIG. 4 schematically illustrates a flow diagram for a method 400 of fabricating an IC, in accordance with some embodiments. The method 400 may comport with the configuration of die 300 in FIG. 3, for example.

**[0031]** At **402**, the method **400** may include forming on a metal layer (e.g., copper) of a die a self-assembled monolayer (SAM) that includes amine group terminations. The SAM may be referred to as a surface layer that includes an adhesion-functional group. In embodiments, the metal layer may be metal layer **302**, and forming the SAM may include applying to the metal layer an ethanolic solution that includes an alkane thiol with a terminal amine group, as described in greater detail below. The amine group may be referred to as an adhesion-functional group that functionalizes adhesion between the metal layer and the next layer.

**[0032]** At **404**, the method **400** may include applying a dielectric layer on the surface layer. In embodiments, the dielectric layer may include an epoxy resin.

**[0033]** At **406**, the method **400** may include heat-treating the die to affix the dielectric layer to the metal layer. In embodiments, heat-treating may arise by contact and elevated temperature of a rubber press or a steel press, or by a final IC polymer cure, which may provide a more prolonged heat-treatment period.

[0034] SAMs are instances of molecular interactions that lead to supramolecular order. In embodiments, alkanes having a head group with an affinity for a surface may assemble in a close-packed network (e.g., in order to maximize van der Waals interactions). To promote adhesion with a dielectric layer, a terminal amine group may provide a chemical moiety to bond to the layer with enhanced adhesion. In embodiments, a dielectric layer may include an epoxy resin, which may include a high density of epoxide groups. Amine groups may be reactive with epoxides, and amine-based molecules may function as hardening agents for epoxy resins. Thus, after applying a dielectric layer at 404 and heat-treating at 406, covalent bonding between the SAM and the dielectric layer may be established. In embodiments, method 400 may enhance adhesion between copper and a polymer or dielectric layer with chemical interactions or bonds, rather than mechanical interactions. Chemical interactions are individually small or weak. However, when provided at sufficient density, as may be provided the SAM, chemical interaction may provide substantial adhesion.

**[0035]** FIG. **5** schematically illustrates a flow diagram for a method **500** of forming a self-assembled monolayer (SAM) on a metal layer (e.g., copper) of a die, in accordance with some embodiments.

**[0036]** At **502**, method **500** may include surface cleaning the metal layer. In embodiments, the surface cleaning may include an acid rinse in an aqueous solution of sulfuric acid to remove oxides from the surface of the metal layer.

**[0037]** At **504**, method **500** may include immersing the die in a SAM bath. In embodiments, the SAM bath may include may include an alkane thiol, such as 11-amino-1-undecanethiol, with a terminal amine group.

**[0038]** At **506**, method **500** may include applying a rinse bath to the die. In embodiments, applying the rinse bath to the die may include immersing the die in an ethanol bath to remove un-bonded thiol.

**[0039]** Methods **400** and **500** may be performed on a metal layer, such as patterned copper, as an alternative to "CZ" chemistry. Methods **400** and **500** may be improvements over copper-roughening chemistry, which may uses many baths to facilitate oxidative etching.

**[0040]** Various operations are described as multiple discrete operations in turn, in a manner that is most helpful in understanding the claimed subject matter. However, the order of description should not be construed as to imply that these operations are necessarily order-dependent. For example, actions of the method **400** may be performed in another suitable order than depicted.

[0041] Embodiments of the present disclosure may be implemented into a system using any suitable hardware and/or software. FIG. 6 schematically illustrates a computing device 600 that may include an IC as described herein, in accordance with some embodiments. The computing device 600 may house a board such as motherboard 602. The motherboard 602 may include a number of components, including but not limited to a processor 604 and at least one communication chip 606. The processor 604 may be physically and electrically coupled to the motherboard 602. In some implementations, the at least one communication chip 606 may also be physically and electrically coupled to the motherboard 602. In further implementations, the communication chip 606 may be part of the processor 604. In some embodiments, the processor 604 and/or chip 606 may comprise an IC, such as IC 100 or 300 described in reference to FIGS. 1 and 3.

[0042] Depending on its applications, computing device 600 may include other components that may or may not be physically and electrically coupled to the motherboard 602. These other components may include, but are not limited to, volatile memory (e.g., DRAM), non-volatile memory (e.g., ROM), flash memory, a graphics processor, a digital signal processor, a crypto processor, a chipset, an antenna, a display, a touchscreen display, a touchscreen controller, a battery, an audio codec, a video codec, a power amplifier, a global positioning system (GPS) device, a compass, a Geiger counter, an accelerometer, a gyroscope, a speaker, a camera, and a mass storage device (such as hard disk drive, compact disk (CD), digital versatile disk (DVD), and so forth). The processor 604 of the computing device 600 may be packaged in a stacked IC package assembly with a memory, as described herein, and/or other components may be packaged together in a stacked IC package assembly with a memory, as described herein.

[0043] The communication chip 606 may enable wireless communications for the transfer of data to and from the computing device 600. The term "wireless" and its derivatives may be used to describe circuits, devices, systems, methods, techniques, communications channels, etc., that may communicate data through the use of modulated electromagnetic radiation through a non-solid medium. The term does not imply that the associated devices do not contain any wires, although in some embodiments they might not. The communication chip 606 may implement any of a number of wireless standards or protocols, including but not limited to Institute for Electrical and Electronic Engineers (IEEE) standards including Wi-Fi (IEEE 502.11 family), IEEE 502.16 standards (e.g., IEEE 502.16-2005 Amendment), Long-Term Evolution (LTE) project along with any amendments, updates, and/or revisions (e.g., advanced LTE project, ultra mobile broadband (UMB) project (also referred to as "3GPP2"), etc.). IEEE 502.16 compatible BWA networks are generally referred to as WiMAX networks, an acronym that stands for Worldwide Interoperability for Microwave Access, which is a certification mark for products that pass conformity and interoperability tests for the IEEE 502.16 standards. The communication chip 606 may operate in accordance with a Global System for Mobile Communication (GSM), General Packet Radio Service (GPRS), Universal Mobile Telecommunications System (UMTS), High Speed Packet Access (HSPA), Evolved HSPA (E-HSPA), or LTE network. The communication chip 606 may operate in accordance with Enhanced Data for GSM Evolution (EDGE), GSM EDGE Radio Access Network (GERAN), Universal Terrestrial Radio Access Network (UTRAN), or Evolved UTRAN (E-UTRAN). The communication chip 606 may operate in accordance with Code Division Multiple Access (CDMA), Time Division Multiple Access (TDMA), Digital Enhanced Cordless Telecommunications (DECT), Evolution-Data Optimized (EV-DO), derivatives thereof, as well as any other wireless protocols that are designated as 3G, 4G, 5G, and beyond. The communication chip 606 may operate in accordance with other wireless protocols in other embodiments.

**[0044]** The computing device **600** may include a plurality of communication chips **606**. For instance, a first communication chip **606** may be dedicated to shorter range wireless communications such as Wi-Fi and Bluetooth and a second communication chip **606** may be dedicated to longer range wireless communications such as GPS, EDGE, GPRS, CDMA, WiMAX, LTE, Ev-DO, and others.

**[0045]** In various implementations, the computing device **600** may be a laptop, a netbook, a notebook, an ultrabook, a smartphone, a tablet, a personal digital assistant (PDA), an ultra mobile PC, a mobile phone, a desktop computer, a server, a printer, a scanner, a monitor, a set-top box, an entertainment control unit, a digital camera, a portable music player, or a digital video recorder. In an embodiment, the computing device **600** may be a mobile computing device. In further implementations, the computing device **600** may be any other electronic device that processes data.

#### Examples

**[0046]** Some non-limiting examples are provided below. **[0047]** Example 1 may include a method of fabricating an integrated circuit (IC), the method comprising: forming on at least one of a metal layer or a polymer layer of a die a surface layer that includes an adhesion-functional group; and applying to the surface layer a next layer to adhere to the surface layer with the adhesion-functional group.

**[0048]** Example 2 may include the method of example 1, wherein the at least one of the metal layer or the polymer layer is a polymer layer and forming the surface layer includes copolymerizing on the polymer layer a polar monomer that includes the adhesion-functional group.

**[0049]** Example 3 may include the method of example 2, wherein forming the surface layer further comprises: dispensing on the polymer layer a solution that includes a photoinitiator and the polar monomer with the adhesion-functional group; and exposing the solution to light to form the surface layer on the polymer layer.

**[0050]** Example 4 may include the method of example 3 wherein exposing the solution to light copolymerizes the polar monomer on the polymer layer.

**[0051]** Example 5 may include the method of any of examples 2-4 wherein the adhesion-functional group includes an amine group.

**[0052]** Example 6 may include the method of example 5 wherein the next layer includes silica.

**[0053]** Example 7 may include the method of any of examples 2-4 wherein the adhesion-functional group includes a cyano group.

**[0054]** Example 8 may include the method of example 7 wherein the next layer includes a metal.

**[0055]** Example 9 may include the method of any of examples 2-4 wherein the adhesion-functional group includes a hydroxyl group.

**[0056]** Example 10 may include the method of any examples 2-4 wherein the next layer includes a second polymer layer.

**[0057]** Example 11 may include the method of example 2 wherein the polar monomer further includes a second adhesion-functional group.

**[0058]** Example 12 may include the method of example 1, wherein the at least one of the metal layer or the polymer layer is a metal layer and forming the surface layer includes forming on the metal layer a self-assembled monolayer that includes amine group terminations.

**[0059]** Example 13 may include the method of example 12, wherein applying the next layer further comprises: forming the next layer as a dielectric layer; and heat-treating the die to affix the dielectric layer to the metal layer.

**[0060]** Example 14 may include the method of any of examples 12-13 wherein forming the self-assembled monolayer includes applying to the metal layer an ethanolic solution that includes an alkane thiol with a terminal amine group.

**[0061]** Example 15 may include the method of example 14 wherein applying the solution to the metal layer includes immersing the die in the solution.

**[0062]** Example 16 may include an integrated circuit (IC), comprising: a polymer layer of a first monomer on a die; a polymer surface layer with a polar monomer that is copolymerized on the polymer layer, wherein the polar monomer includes a functional group and the polymer layer is free from the functional group.

**[0063]** Example 17 may include the IC of example 16 further comprising a subsequent layer applied to the polymer surface layer with adhesion functional by the functional group.

**[0064]** Example 18 may include the IC of example 16 wherein the functional group includes an amine group.

**[0065]** Example 19 may include the IC of example 16 wherein the functional group includes a cyano group.

**[0066]** Example 20 may include the IC of example 19 wherein the next layer includes a metal.

**[0067]** Example 21 may include the IC of example 16 wherein the functional group includes a hydroxyl group.

**[0068]** Example 22 may include the IC of example 18 in which the next layer includes silica.

**[0069]** Example 23 may include the IC of example 21 in which the next layer includes a solder resist.

**[0070]** Example 24 may include the IC of example 16 in which the next layer includes a second polymer layer.

**[0071]** Example 25 may include the IC of example 24 in which the second polymer layer embeds the die in an IC package assembly.

**[0072]** Example 26 may include the IC of example 24 in which the second polymer layer includes an underfill material.

**[0073]** Example 27 may include an integrated circuit (IC), comprising: a die with multiple layers that include a metal layer; a surface layer on the metal layer, wherein the surface layer includes amine group terminations; and a heat-treated dielectric layer on the surface layer.

**[0074]** Example 28 may include the IC of example 27 wherein the surface layer includes a self-assembled mono-layer.

**[0075]** Example 29 may include the IC of example 28 wherein the self-assembled monolayer is thiol-based.

**[0076]** Example 30 may include a method of fabricating an integrated circuit (IC), the method comprising: providing a die with a polymer layer; dispensing on the polymer layer a solution that includes a polar monomer and a photoinitiator; exposing the solution to light to form on the polymer layer an adhesion-receptive polymer surface; and applying a next layer to the adhesion-receptive polymer surface.

**[0077]** Example 31 may include the method of example 30 in which exposing the solution to light copolymerizes the polar monomer on the polymer layer to form the adhesion-receptive polymer surface.

**[0078]** Example 32 may include the method of example 30 in which the polar monomer includes an amine group.

**[0079]** Example 33 may include the method of example 32 in which the next layer includes silica.

**[0080]** Example 34 may include the method of example 30 in which the polar monomer includes a cyano group.

**[0081]** Example 35 may include the method of example 34 in which the next layer includes a metal.

**[0082]** Example 36 may include the method of example 30 in which the polar monomer includes a hydroxyl group.

**[0083]** Example 37 may include the method of example 36 in which the next layer includes a solder resist.

**[0084]** Example 38 may include the method of example 30 in which the next layer includes a second polymer layer.

**[0085]** Example 39 may include the method of example 30 in which the light includes ultra-violet light.

**[0086]** Example 40 may include a method of fabricating an integrated circuit (IC), the method comprising: providing a die with a first metal layer; forming on the metal layer a self-assembled monolayer that includes amine group terminations; forming a dielectric layer on the self-assembled monolayer; and heat-treating the die.

**[0087]** Example 41 may include the method of example 40 in which forming the self-assembled monolayer includes

applying to the first metal layer a solution that includes an alkane thiol with a terminal amine group.

**[0088]** Example 42 may include the method of example 41 in which the solution is ethanolic.

**[0089]** Example 43 may include the method of any of examples 41-42 in which applying the solution to the first metal layer includes immersing the die in the solution.

**[0090]** Example 44 may include the method of example 40 in which forming a dielectric layer on the self-assembled monolayer includes applying a dielectric epoxy resin.

**[0091]** Example 45 may include a method of fabricating an integrated circuit (IC), the method comprising: providing a die with a first metal layer; applying to the first metal layer an ethanolic solution that includes an alkane thiol with a terminal amine group to form a surface layer with amine group terminations; applying a dielectric layer on the surface layer; and heat-treating the die.

**[0092]** Example 46 may include the method of example 45 in which applying the ethanolic solution to the first metal layer includes immersing the die in the ethanolic solution. **[0093]** Example 47 may include the method of example 45 in which applying the dielectric layer on the surface layer includes applying a dielectric epoxy resin.

**[0094]** The above description of illustrated implementations, including what is described in the Abstract, is not intended to be exhaustive or to limit the embodiments of the present disclosure to the precise forms disclosed. While specific implementations and examples are described herein for illustrative purposes, various equivalent modifications are possible within the scope of the present disclosure, as those skilled in the relevant art will recognize.

**[0095]** These modifications may be made to embodiments of the present disclosure in light of the above detailed description. The terms used in the following claims should not be construed to limit various embodiments of the present disclosure to the specific implementations disclosed in the specification and the claims. Rather, the scope is to be determined entirely by the following claims, which are to be construed in accordance with established doctrines of claim interpretation.

What is claimed is:

1. An integrated circuit (IC), comprising:

a die;

a polymer layer formed on a die; and

a surface layer comprising a polar monomer that is copolymerized on the polymer layer in response to exposure of a solution disposed on the polymer layer to light, wherein the solution includes a photoinitiator and a polar monomer with an adhesion-functional group, wherein the polymer layer is free from the adhesionfunctional group.

**2**. The IC of claim **1** further comprising a next layer applied to the polymer surface layer with adhesion functional by the adhesion-functional group.

**3**. The IC of claim **2** wherein the adhesion-functional group includes an amine group.

4. The IC of claim 3, wherein the next layer includes silica.

5. The IC of claim 2, wherein the adhesion-functional group includes a cyano group.

6. The IC of claim 5, wherein the next layer includes a metal.

**7**. The IC of claim **1**, wherein the adhesion-functional group includes a hydroxyl group.

9. The IC of claim 1, wherein the polar monomer further includes another adhesion-functional group.

10. An integrated circuit (IC), comprising:

- a die with multiple layers that include a metal layer; a surface layer disposed on the metal layer, wherein the surface layer comprises an adhesion-functional group and amine group terminations; and

- a next layer disposed on the surface layer, wherein the next layer is adhered to the surface layer with the adhesion-functional group.

11. The IC of claim 10, wherein the surface layer includes a self-assembled monolayer.

12. The IC of claim 11, wherein the self-assembled monolayer is thiol-based.

13. The IC of claim 10, wherein the next layer comprises a heat-treated dielectric layer.

\* \* \* \* \*