【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第2区分

【発行日】平成17年8月18日(2005.8.18)

【公開番号】特開2003-234481(P2003-234481A)

【公開日】平成15年8月22日(2003.8.22)

【出願番号】特願2002-30638(P2002-30638)

【国際特許分類第7版】

H 01 L 29/80

【F I】

H 01 L 29/80

V

【手続補正書】

【提出日】平成17年2月4日(2005.2.4)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【書類名】明細書

【発明の名称】半導体装置

【特許請求の範囲】

【請求項1】 一導電型のシリコン基板の表面に、該基板と同一導電型のエピタキシャル成長層を有し、前記シリコン基板と同一導電型のソース領域及び逆導電型のゲート領域が前記エピタキシャル成長層に設けられ、前記シリコン基板の裏面には前記シリコン基板と同一導電型のドレイン領域が設けられた半導体装置において、前記エピタキシャル成長層の不純物密度を $1 \times 10^{14} \text{ cm}^{-3}$ 未満とし、ゲートゼロバイアス時の空乏層幅 $W_0$ を大きくし、低バイアス領域から高バイアス領域まで高領域で均一な阻止能力あるいは均一な電圧増幅率を再現できることを特徴とする半導体装置。

【請求項2】 前記請求項1記載の半導体装置において、ソース領域からドレイン領域境界までが1層のエピタキシャル成長層で構成されて、不純物密度を一定にすることと、均一な阻止能力あるいは均一な電圧増幅率を再現できることを特徴とする半導体装置。

【請求項3】 前記請求項1記載の半導体装置において、チャンネル幅 $W_{CH}$ をゲートゼロバイアス時に広がる空乏層幅 $W_0$ より短くすることで( $W_{CH} < W_0$ の設計)、ゲート低バイアス領域から高バイアス領域まで広領域で均一な阻止能力あるいは均一な電圧増幅率を再現できることを特徴とする半導体装置。

【請求項4】 請求項1ないし3のいずれかに記載の半導体装置を静電誘導型トランジスタとすることを特徴とする半導体装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、静電誘導型トランジスタ(以下、S I Tと称する)に関し、特にオーディオ用の表面ゲート型S I Tの半導体装置に関する。

【0002】

【従来の技術】

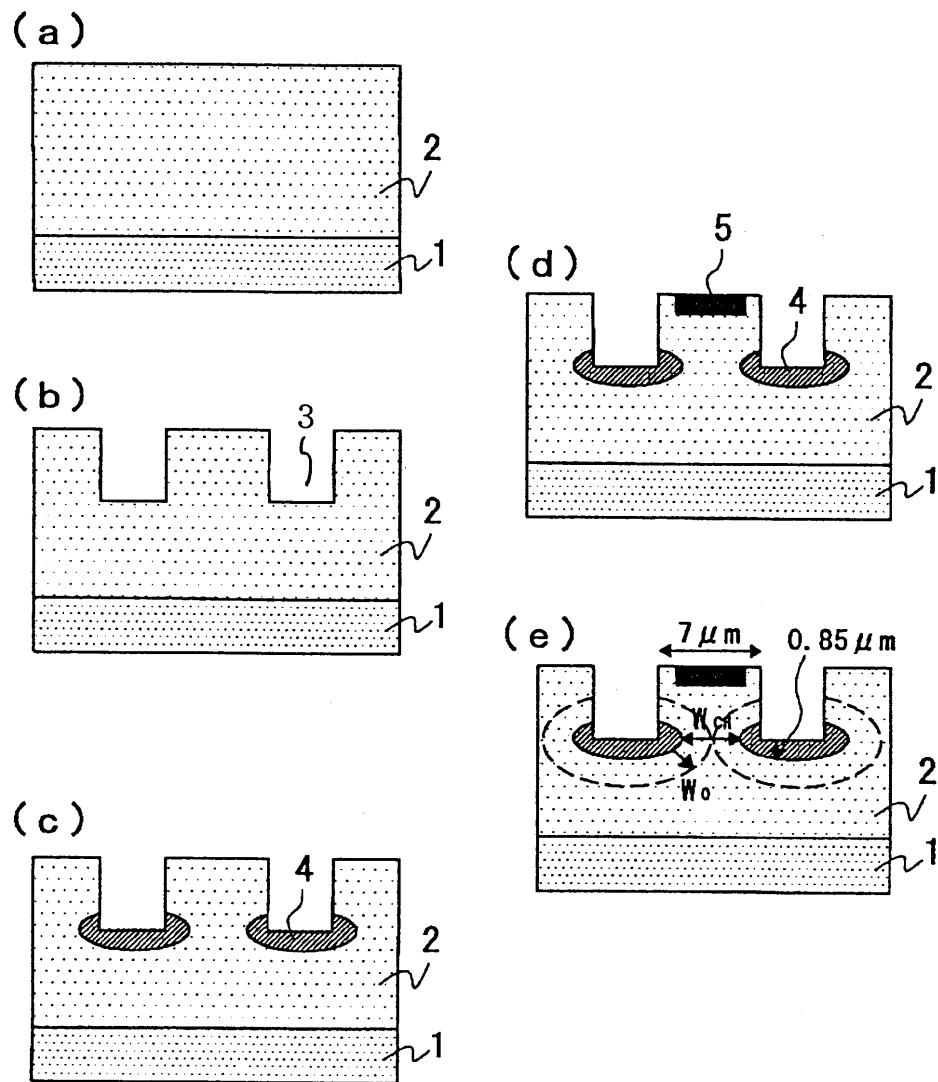

図3は、従来の表面ゲート型S I Tの製造方法を示す図である。以下、図3によって従来のS I Tの製造工程を説明する。

【0003】

図3(a)に示すエピタキシャル層は、成長工程では、ドレイン層である不純物密度が $1 \times 10^{18} \text{ cm}^{-3}$ のN<sup>+</sup>型シリコン基板1の上に不純物密度が $1 \times 10^{14} \text{ cm}^{-3}$

のシリコンのN<sup>-</sup>エピタキシャル層2が約50μm設けられている。図3(b)に示すシリコンピット3は、シリコンのN<sup>-</sup>エピタキシャル層2をドライエッチングし設けられている。図3(c)に示すゲートは、シリコンピット3の溝の底に該基板と逆導電型のゲートP<sup>+</sup>層4で設けられている。

## 【0004】

図3(d)に示すソースは、シリコン表面のN<sup>-</sup>エピタキシャル層2の上に該基板と同一導電型のN<sup>+</sup>ソース層5が設けられている。これが、従来の表面ゲート型SITの概略構造である。図3(e)では、従来の内部構造を解説する。ここで、N<sup>-</sup>エピタキシャル層2とP<sup>+</sup>ゲート層4は逆導電型なので、PN接合が形成される。PN接合の逆バイアス時に広がる空乏層幅をW<sub>D</sub>とし、以下で与えられる。

## 【0005】

$$W_D = 2 \times (V_{GS} + \dots) / (q \times N_D)$$

## 【0006】

ここで、空乏層幅W<sub>D</sub>は、P<sup>+</sup>ゲート層4とN<sup>-</sup>エピタキシャル層2の不純物密度で与えられる。ここで、外部印加電圧V<sub>GS</sub>を0Vとしてゲートゼロバイアス時の空乏層の幅をW<sub>0</sub>とした。

## 【0007】

空乏層幅W<sub>0</sub>は、不純物密度が低い方のN<sup>-</sup>エピタキシャル層2の方へ広がる。例えば、ここでアプセクタ不純物密度 $1 \times 10^{19} \text{ cm}^{-3}$ として、ドナー不純物密度 $1 \times 10^{14} \text{ cm}^{-3}$ とした場合には、ゼロバイアス時の空乏層幅W<sub>0</sub>はおよそ2.06μmとなる。シリコンピットに設けたゲートの溝から隣のゲートの溝まで7μmとし、ゲートの拡散深さを0.85μmとすれば、チャンネル幅W<sub>CH</sub>は5.3μmとなり、ゲートからゼロバイアス時の空乏層幅W<sub>0</sub>が隣のゲートまで届かないものであった。つまり、W<sub>CH</sub> > W<sub>0</sub>の領域であった。

## 【0008】

## 【発明が解決しようとする課題】

上記した従来の半導体では、低逆バイアス領域から均等な阻止能力を発揮するのは難しく、また、均等な阻止能力を発揮するためにはある程度の逆バイアスが必要であった。また、言い換えると、低バイアス領域から均一な電圧増幅率を得るのは難しかった。また、低バイアス領域では高バイアス領域に比べ阻止能力が低いので、または、電圧増幅率が小さいので、低バイアス領域から使用する際は、変動を補正するために余分な回路が必要とされた。

## 【0009】

そこで、本発明の目的は、低逆バイアス領域から充分な阻止能力を発揮し、または低逆バイアス領域から均等な電圧増幅率を再現し、高範囲の領域で均等な電圧増幅率を再現しリニアリティの良い優れた半導体装置を提供することにある。

## 【0010】

## 【課題を解決するための手段】

そこで、本発明は、一導電型のシリコン基板の表面に、該基板と同一導電型のエピタキシャル層を設け、該エピタキシャル層に該基板と同一導電型のソース領域及び逆導電型のゲート領域を設け、前記基板の裏面には前記基板と同一導電型のドレイン領域を設けた静電誘導型トランジスタにおいて、前記エピタキシャル成長層の不純物密度を低くすること、また1層のエピタキシャル成長層のみで形成すること、またチャンネル幅W<sub>CH</sub>をゼロバイアス時の空乏層幅W<sub>0</sub>よりも短くする構造とすることで、低バイアス領域から高バイアス領域まで広領域での均一な電圧増幅率を再現できることを特徴とする半導体装置である。

## 【0011】

即ち、本発明は、一導電型のシリコン基板の表面にエピタキシャル成長層が形成され、前記シリコン基板と同一導電型のソース領域及び逆導電型のゲート領域が形成され、前記シリコン基板の裏面には前記シリコン基板と同一導電型のドレイン領域が形成される半導

体装置において、前記エピタキシャル成長層の不純物密度を  $10^{14} \text{ cm}^{-3}$  未満とし、ゼロバイアス時の空乏層幅  $W_0$  を大きくし、低バイアス領域から高バイアス領域まで高領域で均一な阻止能力あるいは均一な電圧増幅率を再現できる半導体装置である。

【0012】

また、本発明は、前記半導体装置において、ソース領域からドレイン領域が1層のエピタキシャル成長層であって不純物密度が一定であり、均一な阻止能力あるいは均一な電圧増幅率を再現できる半導体装置である。

【0013】

また、本発明は、前記半導体装置において、チャンネル幅  $W_{CH}$  をゲートゼロバイアス時に広がる空乏層幅  $W_0$  より短くすることで ( $W_{CH} < W_0$  の設計)、低バイアス領域から高バイアス領域まで広領域で均一な阻止能力あるいは均一な電圧増幅率を再現することを特徴とする半導体装置である。

【0014】

また、本発明は、前記半導体装置の構造を特徴とした静電誘導型トランジスタである。

【0015】

【発明の実施の形態】

本発明の実施の形態による半導体装置の製造方法について、以下に説明する。

【0016】

本発明の特徴は、エピタキシャル成長層の不純物密度を低くすること、またエピタキシャル層を1層のエピで行うこと、またチャンネル幅  $W_{CH}$  をゲートゼロバイアス領域の空乏層幅  $W_0$  よりも短く設計することで、低バイアス領域から高バイアス領域まで広領域での均一な電圧増幅率を再現できた。

【0017】

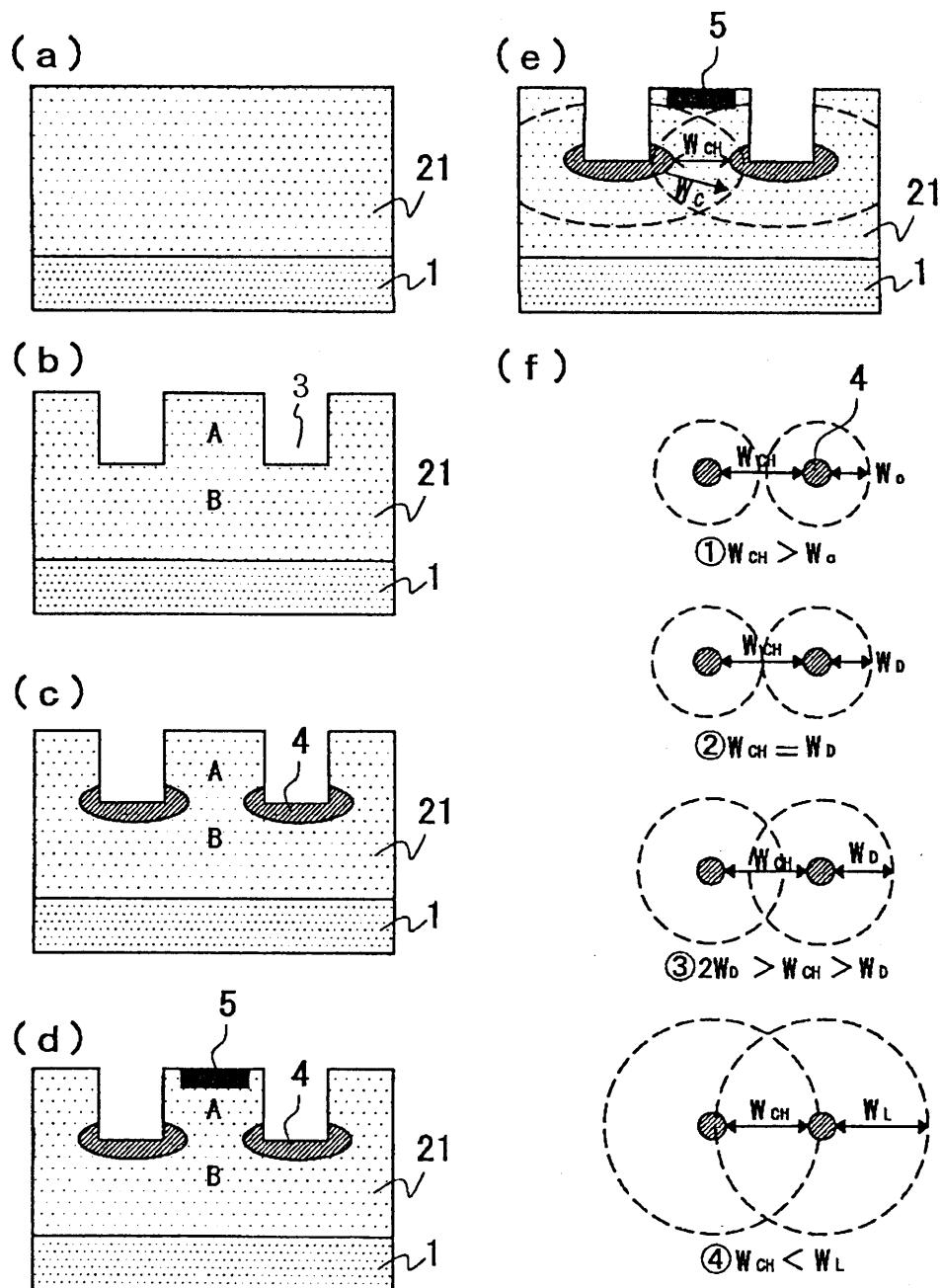

図1は、本発明の実施の形態による表面ゲート型SITの説明図である。以下、図1によって本発明のSITを説明する。

【0018】

図1(a)に示すエピタキシャル成長層は、ドレイン層である不純物密度が  $1 \times 10^8 \text{ cm}^{-3}$  のN<sup>+</sup>型シリコン基板1の上に不純物密度が  $1.2 \times 10^{13} \text{ cm}^{-3}$  といった低濃度のシリコンのN<sup>-</sup>エピタキシャル層21を約  $50 \mu\text{m}$  を設けた。

【0019】

図1(b)に示すシリコンピットは、シリコンのN<sup>-</sup>エピタキシャル層21をドライエッティングによりエッティングし、シリコンピット3を設けた。ここで、表面側のエピタキシャル層21をA領域とし、基板内部側のN<sup>-</sup>エピタキシャル層21をB領域とする。

【0020】

図1(c)に示すゲートは、シリコンピット3の溝の底に該基板と逆導電型のP<sup>+</sup>ゲート層4で設けた。

【0021】

図1(d)に示すソースは、シリコン表面のN<sup>-</sup>エピタキシャル層2の上に該基板と同一導電型のN<sup>+</sup>ソース層で設けた。

【0022】

図1(e)では、本発明のSITの内部構造を説明する。ここで、従来のSITと同様に、N<sup>-</sup>エピタキシャル層21とP<sup>+</sup>ゲート層4は、逆導電型なので、バイアスを加えなくても空乏層はある程度形成される。ここで、前述と同様に、ゲートゼロバイアス時の空乏層幅  $W_0$  を求めてみると、アクセプタ不純物密度  $1 \times 10^{19} \text{ cm}^{-3}$  とし、ドナー不純物密度  $1.2 \times 10^{13} \text{ cm}^{-3}$  とすると  $W_0$  はおよそ  $5.72 \mu\text{m}$  となる。ゲートの溝から隣のゲートの溝まで  $7 \mu\text{m}$  とし、ゲートの拡散深さを  $0.85 \mu\text{m}$  とすれば、チャンネル幅  $W_{CH}$  は  $5.3 \mu\text{m}$  となり、本発明のSITは、ゲートからゼロバイアス時の空乏層幅  $W_0$  は、すでに隣のゲートに接触している。これで、本発明の表面型SITが完成する。

【0023】

ここで、補足として説明すると、チャンネル幅は4種類のタイプの構造に分類される。図1(f)では、補足の説明として、チャンネル近傍の図を4種類に分けて説明する。例として、ゲートから逆バイアスを加え空乏層を広げていった場合のモデルである。

#### 【0024】

(1)  $W_{CH} > W_0$

ゼロバイアスではお互いの空乏層は接触していない領域

(2)  $W_{CH} = 2W_D$

逆ゼロバイアスを加え、お互いの空乏層が接触する領域(ジャストピンチオフ)

(3)  $2W_D > W_{CH} > W_D$

さらに逆バイアスを加え、お互いの空乏層が重なり合う領域

(4)  $W_{CH} < W_D$

さらに逆バイアスを加え、空乏層が隣のゲートに接触している領域

#### 【0025】

上記のように分類されるが、その構造によりゼロバイアスの時点での空乏層がどの領域にあるかで、低バイアス領域から高バイアス領域まで、電圧増幅率が均等であるかが決定される。例えば、(1)の  $W_{CH} > W_0$ とした構造の場合は、ゲートに逆バイアスを加えていくと、空乏層が広がり、やがて(2)  $W_{CH} = 2W_D$ の領域に達する。さらに、逆バイアスを加えると、(3)  $2W_D > W_{CH} > W_D$ の領域に到達する。また、さらに、逆バイアスを加えると、(4)  $W_{CH} < W_D$ 領域に到達する。以後は、空乏層に変化はなくボテンシャルバリアの高さは大きくなっていく。

#### 【0026】

ここで、(4)  $W_{CH} < W_D$ の領域に到達するまでは、数ボルトのゲート逆バイアスを必要とし、この数ボルトの低逆バイアス領域までは空乏層が変化していき、阻止状態が均一ではなく、可変電圧増幅率を発生させている。この構造を用いると、低バイアス領域では、 $V_{DS} - I_D$ 特性の阻止間隔が $V_{GS}$ に対して均一ではない領域で、この領域は阻止能力が加速度的に増加している状態である。

#### 【0027】

しかし、図1(e)のように、ゼロバイアス状態で  $W_{CH} < W_0$  の条件を満たした空乏層である場合には、ここから逆バイアスを加えていっても構造の変化はなく、低バイアス領域から充分な阻止能力を発揮し、また広範囲において均等な電圧増幅率を再現できる。よって、 $V_{DS} - I_D$ 特性でみると、阻止間隔が $V_{GS}$ に対して均一になり、リニアリティの良い $V_{DS} - I_D$ 特性が得られる。

#### 【0028】

またここで、ゼロバイアスの空乏層幅  $W_0$  は、エピタキシャル成長層21の不純物密度が小さい方が(ドナー密度  $N_D$  を小さくすることで)、 $W_0$ を大きくできるので、エピタキシャル成長層21の濃度を小さくした方が上記SITを設計しやすい。また、高逆バイアス領域になっても、1層のエピタキシャル成長層で形成しているので、ソース側のAの領域とドレイン側のBの領域は同じ不純物密度なので(ドナー密度  $N_D$  は変化しない)、空乏層の広がりが安定するため均一な電圧増幅率を再現できる。

#### 【0029】

図2(b)では、例として  $W_{CH} > W_0$  の条件の  $V_{DS} - I_D$  特性を示す。この条件では、例えば、低バイアスの( $V_{GS} = 0 \sim -8V$ )の領域では高バイアス領域に比べ阻止間隔が狭くなっている。そして、高バイアス領域( $V_{GS} = -8V$ )以上になると間隔が大きくなり均一になってくる。

#### 【0030】

図2(a)では、例として、 $W_{CH} < W_0$  の条件の  $V_{DS} - I_D$  特性を示す。この条件では、例えば、低バイアスの( $V_{GS} = -1V$ )の領域からすでに間隔が大きくなり、均一になっている。つまり、低バイアス領域から高バイアス領域にかけて広領域で  $V_{DS} - I_D$  特性が  $V_{GS}$  に対して間隔が均一で、等間隔の電圧増幅率を再現している。

#### 【0031】

**【発明の効果】**

本発明によれば、一導電型のシリコン基板の表面に、該基板と同一導電型のソース領域及び逆導電型のゲート領域が設けられ、前記基板の裏面には前記基板と同一導電型のドレイン領域が設けられている静電誘導型トランジスタにおいて、エピタキシャル成長層の不純物密度を低くすることで、ゼロバイアス時の空乏層幅 $W_0$ を大きくし、また、1層のエピタキシャル成長のみで行うことで、不純物密度を均一にすることで、また、チャンネル幅 $W_{CH}$ をゼロバイアス時に広がる空乏層幅 $W_0$ より短く( $W_{CH} < W_0$ )することで、低バイアス領域から高バイアス領域まで広領域で均一な電圧増幅率を再現できるSITを提供することができる。

**【0032】**

またこれにより、オーディオ用のアンプを設計する際に、低バイアス領域から高バイアス領域まで広領域で阻止間隔が均等なので、リニアリティが良く歪みの少ない良好なアンプを提供できる。また、従来より電圧増幅率がバイアス領域で変化する場合は、回路設計により補正していたが、こういった余分な回路は省くことが出来、単純な回路でアンプが提供できる。

**【図面の簡単な説明】**

**【図1】** 本発明の実施の形態による表面ゲート型SITの説明図。図1(a)は、エピタキシャル成長工程の説明図、図1(b)は、シリコンピット形成工程の説明図、図1(c)は、ゲートの説明図、図1(d)は、ソースの説明図、図1(e)は、本発明のSITの内部構造の説明図、図1(f)は、本発明のSITのチャンネル近傍の空乏層の説明図。

**【図2】** 表面ゲート型SITの電圧対電流特性の説明図。図2(a)は、本発明の実施の形態による表面ゲート型SITの電圧対電流特性を示す図、図2(b)は、従来の表面ゲート型SITの電圧対電流特性を示す図。

**【図3】** 従来の表面ゲート型SITの製造方法を示す図。図3(a)は、エピタキシャル成長層の説明図、図3(b)は、シリコンピットの説明図、図3(c)は、ゲートの説明図、図3(d)は、ソースの説明図、図3(e)は、従来のSITの内部構造の説明図。

**【符号の説明】**

- 1 ドレイン層

- 2, 2 1 N<sup>-</sup> エピタキシャル成長層

- 3 シリコンピット

- 4 P<sup>+</sup> ゲート層

- 5 N<sup>+</sup> ソース層

**【手続補正2】**

**【補正対象書類名】**図面

**【補正対象項目名】**図1

**【補正方法】**変更

**【補正の内容】**

【図1】

【手続補正3】

【補正対象書類名】図面

【補正対象項目名】図3

【補正方法】変更

【補正の内容】

【図3】