(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4886160号

(P4886160)

(45) 発行日 平成24年2月29日(2012.2.29)

(24) 登録日 平成23年12月16日(2011.12.16)

(51) Int.Cl.

F 1

H01L 27/28 (2006.01)

H01L 27/10 449

H01L 51/05 (2006.01)

G11C 13/00 100

G11C 13/00 (2006.01)

請求項の数 31 (全 11 頁)

(21) 出願番号 特願2002-588554 (P2002-588554)

(86) (22) 出願日 平成14年5月7日 (2002.5.7)

(65) 公表番号 特表2004-527130 (P2004-527130A)

(43) 公表日 平成16年9月2日 (2004.9.2)

(86) 國際出願番号 PCT/US2002/014236

(87) 國際公開番号 WO2002/091384

(87) 國際公開日 平成14年11月14日 (2002.11.14)

審査請求日 平成17年5月6日 (2005.5.6)

(31) 優先権主張番号 60/289,054

(32) 優先日 平成13年5月7日 (2001.5.7)

(33) 優先権主張国 米国(US)

(73) 特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVICES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンディベール、ビイ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・ブレイス、メイル・ストップ

・68 (番地なし)

(74) 代理人 100108833

弁理士 早川 裕司

(74) 代理人 100132207

弁理士 太田 昌孝

最終頁に続く

(54) 【発明の名称】セルフアセンブリによるポリマーフィルムを用いた記憶装置およびその製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

アドレス指定可能なトランジスタのアレイと、

前記トランジスタアレイを覆う絶縁体層と、

前記絶縁体層を介して前記トランジスタアレイに対して設けられる複数のコンタクトであって、前記トランジスタから前記絶縁体層の表面に伸びる導電プラグと、前記導電プラグ上のバリア層と、前記バリア層上に形成された接着層とを含むコンタクトと、

少なくとも一部の前記コンタクト上のメモリ素子であって、前記接着層上にのみ形成され、前記絶縁体層上には形成されないメモリ素子と、

前記メモリ素子のそれぞれに接続する共通電極とを備え、

10

前記メモリ素子はポリマーであり、前記メモリ素子はセルフアセンブリの方法で形成され、前記セルフアセンブリの方法は液体モノマーとモノマーガスが導入された密閉チャンバ内に前記記憶装置を設置する処理を含む、記憶装置。

## 【請求項2】

前記コンタクトは前記トランジスタに接続する第1導電材料を含み、前記絶縁体層を貫通して伸びる、請求項1記載の記憶装置。

## 【請求項3】

前記メモリ素子は印加される電界に応答して抵抗値を変化させる材料を含む、請求項2記載の記憶装置。

## 【請求項4】

20

前記材料は、少なくとも 3 つの異なる抵抗値のうちの 1 つに設定され、それを維持することが可能である請求項 3 記載の記憶装置。

**【請求項 5】**

前記材料は、前記接着層にのみ接着し、前記絶縁体層には接着しない性質を持つ請求項 4 記載の記憶装置。

**【請求項 6】**

前記材料はポリ共役ポリマーである請求項 4 記載の記憶装置。

**【請求項 7】**

前記ポリ共役ポリマーは、少なくとも、ポリパラフェニレン、ポリフェニルビニレン、ポリアニリン、ポリチオフェンまたはポリピロールのなかの 1 つである請求項 6 記載の記憶装置。 10

**【請求項 8】**

前記材料は高分子フタロシアニンである請求項 4 記載の記憶装置。

**【請求項 9】**

前記材料は高分子ポルフィリンである請求項 4 記載の記憶装置。

**【請求項 10】**

前記導電プラグはアルミニウムを含む請求項 1 記載の記憶装置。

**【請求項 11】**

前記バリア層はタンクスティンを含む請求項 10 記載の記憶装置。 20

**【請求項 12】**

前記接着層は銅または銅合金を含む請求項 11 記載の記憶装置。

**【請求項 13】**

前記材料はポリ共役ポリマーである請求項 12 記載の記憶装置。

**【請求項 14】**

前記材料は高分子フタロシアニンである請求項 12 記載の記憶装置。

**【請求項 15】**

前記材料は高分子ポルフィリンである請求項 12 記載の記憶装置。

**【請求項 16】**

前記材料はポリ共役ポリマー、高分子フタロシアニン、高分子ポルフィリンのうちの少なくとも 1 つである請求項 12 記載の記憶装置。 30

**【請求項 17】**

前記共通電極はアルミニウムを含む請求項 16 記載の記憶装置。

**【請求項 18】**

記憶装置を製造する方法であって、

トランジスタのアレイを形成する処理と、

前記トランジスタを絶縁体層で覆う処理と、

前記絶縁体層を介して前記トランジスタに対する導電性コンタクトを形成する処理であって、底部がトランジスタに接触する導電性プラグを形成する処理と、前記導電性プラグの上にバリア層を形成する処理と、前記バリア層上に接着層を形成する処理とを含む処理と。 40

液体モノマーとモノマーガスが導入された密閉チャンバ内に前記記憶装置を設置し、もって複数の選択可能な抵抗値を持つポリマーメモリ素子をセルファセンブリの方法で前記接着層上にのみ形成する処理と、

前記メモリ素子のそれぞれに接続する共通電極を前記ポリマーメモリ素子上に形成する処理とを含む、方法。

**【請求項 19】**

前記メモリ素子を形成する処理は、前記接着層にのみ接着して、前記絶縁体層には接着しない第 1 材料をデポジションする処理を含む、請求項 18 記載の方法。

**【請求項 20】**

前記第 1 材料はポリ共役ポリマーである請求項 19 記載の方法。 50

**【請求項 2 1】**

前記ポリ共役ポリマーは、ポリパラフェニレン、ポリフェニルビニレン、ポリアニリン、ポリチオフェンまたはポリピロールのうちの 1 つである請求項 2 0 記載の方法。

**【請求項 2 2】**

前記第 1 材料は高分子フタロシアニンである請求項 1 9 記載の方法。

**【請求項 2 3】**

前記第 1 材料は高分子ポルフィリンである請求項 1 9 記載の方法。

**【請求項 2 4】**

前記液体モノマーおよびモノマーガスはメチルフェニルアセチレンであり、メチルフェニルアセチレンのポリ共役ポリマーが前記メモリ素子として形成される請求項 1 8 記載の方法。 10

**【請求項 2 5】**

前記液体モノマーおよびモノマーガスはテトラシアノベンゼンであり、フタロシアニン銅が前記メモリ素子として形成される請求項 2 4 記載の方法。

**【請求項 2 6】**

メモリセルを形成する方法であって、

第 1 電極を形成する処理と、

前記第 1 電極の上にセルファーセンブリの方法でメモリ素子を形成する処理と、

前記メモリ素子の上に第 2 電極を形成する処理とを含み、

前記第 1 電極を形成する処理は、導電プラグを形成する処理と、前記導電プラグの上にバリア層を形成する処理と、前記バリア層の上に接着層を形成する処理とを含み、 20

前記メモリ素子は、前記第 1 電極にのみ接着するポリマーを含み、前記ポリマーは電界を印加することによって選択可能な複数の抵抗値を持ち、

前記メモリ素子を形成する処理は、液体モノマーとモノマーガスが導入された密閉チャンバ内に前記記憶装置を設置する処理を含む、ところの方法。

**【請求項 2 7】**

前記ポリマーはポリ共役ポリマーである請求項 2 6 記載の方法。

**【請求項 2 8】**

前記ポリ共役ポリマーは、ポリパラフェニレン、ポリフェニルビニレン、ポリアニリン、ポリチオフェンまたはポリピロールのうちの 1 つである請求項 2 7 記載の方法。 30

**【請求項 2 9】**

前記ポリマーは高分子フタロシアニンである請求項 2 6 記載の方法。

**【請求項 3 0】**

前記フタロシアニンはフタロシアニン銅である請求項 2 9 記載の方法。

**【請求項 3 1】**

前記ポリマーは高分子ポルフィリンである請求項 2 6 記載の方法。

**【発明の詳細な説明】****【関連出願】****【0 0 0 1】**

本出願は、同時に係属する米国特許仮出願 6 0 / 2 8 9 , 0 5 4 に開示された主題に関する発明の主題を含むものである。 40

**【技術分野】****【0 0 0 2】**

本発明は、一般的に電気式記憶装置（メモリデバイス）の分野に関し、さらに詳しくはポリマーメモリの構造および製造方法に関する。

**【背景技術】****【0 0 0 3】**

今日のコンピュータ処理システムは、バイナリデータに基づいて動作している。バイナリデータでは、論理 1 が高電圧レベル（おおよそ Vcc, 一般的に 3.3 または 5 ボルト）で表され、論理 0 が低電圧レベル（おおよそ Vss, 一般的に 0 ボルトまたは接地電位）で表さ 50

れる。在來のランダムアクセスメモリセル（例えばDRAM）では、セルキャパシタを高電圧レベルにチャージすることで論理1を記憶し、セルキャパシタを低電圧レベルに放電させることで論理0を記憶させる。DRAMの読み出しでは、あるセルキャパシタの電圧がVccとVssの間の基準電圧に対して差動検出（センス）され、その結果に応じて、完全なVcまたはVssのレベルにラッチングすることで復元される。メモリセルからのデータは周囲の回路に出力され、そして最終的には様々な入力／出力（I/O）線をVccまたはVssに駆動することでDRAM装置の外部に出力される。

#### 【0004】

増えつづけるメモリ容量への要求に対応するため、記憶容量を増やすためにDRAMチップあたりに記憶できるビット数を増やすことが要求されている。DRAMのチップあたりのビット数を増やすには、DRAMセルの密度（すなわち、与えられたチップ領域あたりのセル数）を高くする方法、またはDRAMセルのキャパシティ（すなわち、各セルに記憶されるビット数）を増やす方法がある。DRAMセルの密度を高くするには、高い密度のアレイに、より小さなセルを詰め込むための高度な回路設計および製造技術を開発する必要がある。それには多くの時間がかかり、高価な写真製版（フォトリソグラフィック）プロセス機器をも必要とする。さらに、DRAMセルが小さくなり、アレイがより高密度化するに従い、装置の物理的な特性、たとえばキャパシタあたりの電荷（チャージ）量が制限要因となりうる。

#### 【0005】

セルに複数のビットを記憶させることで、揮発性のメモリ（例えばDRAM）、または不揮発性のメモリ（例えばフラッシュメモリ）のメモリ容量を増やすことができる。1つのアプローチでは、従来の2つの電圧レベルより多い数の電圧レベルをセルの記憶メカニズムに保持することができ、それぞれの電圧レベルが異なったデータ値を表している。例えば、所与のあるセルに、許可された4つの電圧レベルのうちの1つとしてデータを記憶することができる。このとき、0Vの電圧は、2ビットの論理ワード“00”を表すのに用いられ、およそ1Vの電圧は論理“01”を表し、およそ2Vの電圧は論理“10”を表し、およそ3Vの電圧は論理“11”を表すのに用いることができる。このようにして、NSBおよびLSBを单一のセルに記憶させることができる。所望の設計に応じて、正確な電圧および電圧レベル数が用いられる。

#### 【0006】

多値メモリの実現には多くの問題がある。例えば、ムロタニ他の論文（1997 IEEE International Solid State Circuit Conference, Digest of Technical Papers, pp. 74-75, 1997）は4レベルの記憶装置を提案しており、最上位のビット（MSB）および最下位のビット（LSB）がキャパシタ電圧の関数として单一のセルに記憶可能である。MSBは、記憶された電圧を、Vccのおおよそ半分である基準電圧に対して比較する（センスする）ことによって検出される。MSBをセンスした後、LSBがおおよそVccの3分の1だけオフセットされたVccの半分の値に対してセンスされる。オフセットの符号（+，-）はMSB（1, 0）に依存する。

#### 【0007】

不都合な点としては、このようなシステムにおいて、適当なセンス信号を得るために記憶キャパシタの容量が大きくななければならないことである。これは、記憶素子によって占領されるチップ領域、またはキャパシタを構成する高誘電率材料の使用、もしくは両方の組み合わせに影響を与える。

#### 【0008】

従って、チップ領域を効率的に使用しつつ多値記憶を実現するための回路が求められている。

#### 【発明の開示】

#### 【0009】

上記のおよびその他の要求は本発明の一実施形態によって解決される。当該一実施形態は、第1電極を形成する処理と、この第1電極上にメモリ素子をセルファーセンブリ（self

10

20

30

40

50

assembly, 自己組織化または自己整合配置)で形成する処理とを含むメモリセルを形成する方法を提供する。このメモリ素子は、第1電極にのみ接着し、複数の抵抗値を持つポリマー(重合体)を含む。このポリマーの抵抗値は、ポリマーを電界中におくことで選択可能である。第2電極が、第1メモリ素子の上に形成される。

#### 【0010】

上述の要求は本発明の他の実施形態によっても解決される。他の実施形態は、アドレス指定可能なトランジスタのアレイと、このトランジスタのアレイを覆う絶縁体層とを含む記憶装置を提供する。トランジスタのアレイに対する複数のコンタクトが絶縁体層を貫通して設けられ、これらのコンタクトの少なくとも一部は露出している。メモリ素子は少なくともコンタクトのいくつかの上に形成される。メモリ素子は、コンタクト上にのみ形成され、絶縁体層上には形成されない。メモリ素子のそれぞれに接触する共通の電極が設けられる。10

#### 【0011】

さらに、本発明のその他の実施形態として、トランジスタのアレイを形成する処理と、これらのトランジスタを絶縁体層で覆う処理とを含む、記憶装置を製造する方法が提供される。絶縁体層を貫通してトランジスタに対する導電コンタクトが形成される。複数の選択可能な抵抗値を持つメモリ素子が導電コンタクトの上にセルフアセンブリの方法で形成される。メモリ素子のそれぞれに接触する共通の電極がメモリ素子上に設けられる。

#### 【0012】

上記のおよびその他の特徴、実施形態および本発明の利点は、添付の図面とともに、後述の本発明の詳細な説明を参考することにより明らかになるであろう。20

#### 図面の簡単な説明

#### 【0013】

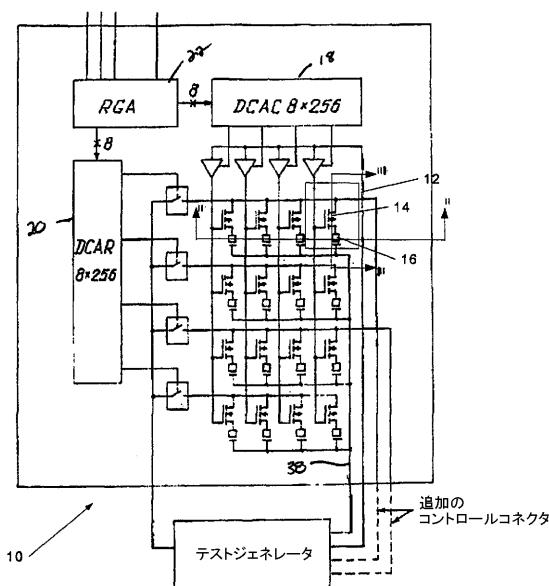

図1は、本発明の一実施形態であるメモリチップを示す概略図である。

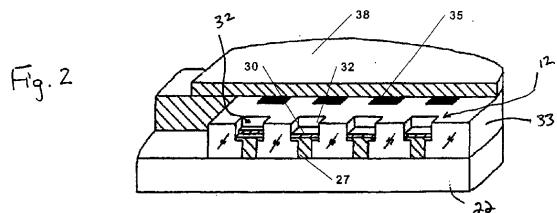

図2は、製造プロセスの一段階における、本発明の一実施形態であるメモリチップの一部の断面を示す斜視図である。

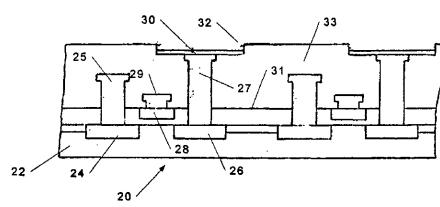

図3は、本発明の一実施形態である製造プロセスの一段階における、図2のメモリアレイの側面図である。

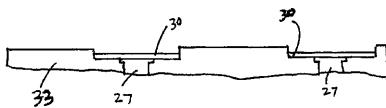

図4は、本発明の一実施形態における、導電プラグ上へのバリア層のデポジション後の図3の構造を示す図である。30

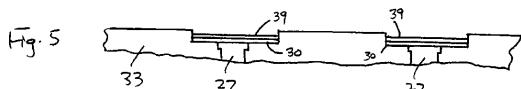

図5は、本発明の一実施形態における、バリア層上への接着層のデポジション後の図4の構造を示す図である。

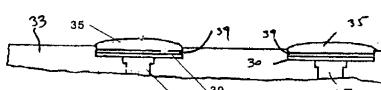

図6は、本発明の一実施形態における、導電コンタクト上へ、セルフアセンブリの方法で形成されるポリマーメモリ素子のデポジション後の図5の構造を示す図である。

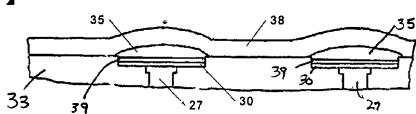

図7は、本発明の一実施形態における、メモリ素子上への共通電極の形成後の図6の構造を示す図である。

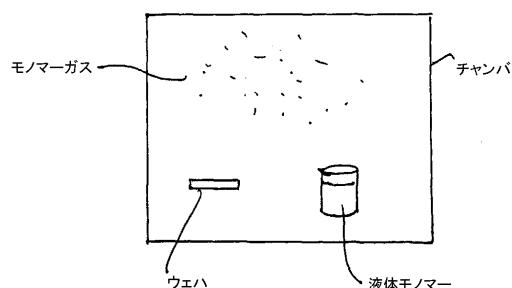

図8は、本発明の一実施形態における、セルフアセンブリのプロセスを示す図である。

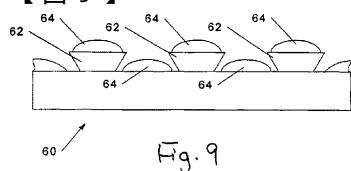

図9は、本発明の一実施形態における、セルフアセンブリの方法で形成された導電路の配線を示す断面図である。40

#### 【発明を実施するための最良の形態】

#### 【0014】

#### 発明の詳細な説明

本発明は、チップの密度を高くすることができ、容易に製造が可能な多値メモリセルを提供するという課題を含む、メモリセルおよび記憶装置(メモリデバイス)の形成に関する課題に対処し、それを解決するものである。本発明は、アドレス指定可能なトランジスタアレイ(配列)と、トランジスタアレイを覆う絶縁体層と、絶縁体層を介するトランジスタアレイへの複数のコンタクトとを含む記憶装置によって、これを達成する。メモリ素子は、コンタクト上にセルフアセンブリプロセス(自己組織化または自己整合配置技術)によって形成される。本発明の一実施形態において、これらのメモリ素子は、印加される50

電界に応答して抵抗値を変化させる材料を含む。これらのメモリ素子においては、複数の抵抗値を選択および設定可能である。この複数の抵抗値は、各メモリセルの複数ビット値に対応する。メモリ素子として用いられる代表的な材料として、ポリ共役ポリマー（Poly conjugated polymers、ポリコンジュゲートポリマー）、フタロシアニン（Phthalocyanine）、ポルフィリン（Porphyrins）があげられる。記憶装置のセルファセンブリの方法は、多値メモリセルを持つ小型の記憶装置を作成するための効率的かつ優れた方法を提供する。

#### 【0015】

従来のDRAMメモリチップでは、"0"または"1"を表す電荷は、半導体ウェハに作成された記憶キャパシタに蓄積される。記憶キャパシタへの電荷の注入は、FETによって制御される。FETのソースは記憶キャパシタの一方の端子に接続され、ドレインは選択的に電源、例えばVssに接続される。記憶キャパシタのもう一方の端子は共通の接地（グラウンド）に接続することができる。このようなデバイスおよびその動作については本技術分野において周知である。記憶キャパシタ、FETおよび相互接続は高コストの写真製版プロセスによって形成される。

#### 【0016】

本発明の記憶装置10は、複数のDRAMセル12を含み、各DRAMセル12はトランジスタ14およびメモリ素子16を有する。図示された実施形態においては、全部で16個のDRAMセル12がある。しかしながら、当業者にとっては、このような配置は説明のための単なる例示であることがあきらかであろう。メモリアレイにもっと多くのDRAMセルを有する記憶装置も実現可能である。個々のメモリセルをアドレス指定するために、メモリチップには列デコーダ18と行デコーダ20とが設けられる。

#### 【0017】

RGAブロック22は、DMAデータ転送の際に、例えばレジスタアドレス信号（RGA）を受信するように動作する。これによって、データの行き先を決定し、メモリセル12におけるデータの位置を指定するダイナミックRAMのアドレスを生成する。

#### 【0018】

各メモリセル16の一方の端子は共通電極38に接続され、他の端子は個々のメモリセル12のトランジスタ14に接続されている。

#### 【0019】

図1に示された記憶装置の回路は単なる例示に過ぎず、本発明の範囲内において他の回路配置を採用することも可能である。そのような応用例においては、典型的には記憶キャパシタから形成されるメモリ素子は、本発明の複数ビット抵抗値メモリ素子によって置換えられる。

#### 【0020】

図2は、III-III切断線に沿った、メモリチップの一部の断面を示す斜視図である。この図には、メモリ素子16は示されていない。実施例たるFETはP型のシリコン基板22の上に形成され、トランジスタアレイは基板22の上および中に形成されている。図面の簡略化のために、トランジスタは図1の基板22には描かれていない。コントクト27（または導電プラグ）のみが示されている。これらの導電プラグ27は絶縁体層33に伸びて、凹部32で終わる。実際には、導電プラグ27は、例えばアルミニウムや銅などの、適切な導電性材料を含むものとすることができます。しかしながら、以下に説明する実施形態においては、導電プラグ27はアルミニウムを含むものと仮定する。バリア層30が導電プラグ27の上部に形成される。これについては後で詳述する。バリア層30は、導電プラグ27と、バリア層30の上部に後から形成される接着層との間の相互作用を防止する材料を含む。

#### 【0021】

共通電極38は、メモリセル12を覆う。しかしながら、図1においては、下部構造を隠してしまわないようにこの電極がセル12を覆うようには描かれていない。

#### 【0022】

10

20

30

40

50

図3には、トランジスタおよびトランジスタのアレイの形成を含む、基板22の断面図が示されている。トランジスタとして、ソースおよびドレイン領域24、26およびゲート電極28が示されている。コンタクト25、29、27がトランジスタの様々な構成要素に伸びている様子が描かれている。酸化シリコンのようなゲート絶縁層が参照符号31で示されている。図3に示されるように、例えば、導電プラグ27は、ドレイン26から伸びて絶縁体層33の凹部32の開口部で止まる。ここまで段階においては、従来のトランジスタ製造技術を用いることができる。

#### 【0023】

図4を参照して、上述したようにバリア層30は導電プラグ27の上に形成される。バリア層30は、導電プラグ27の材料と、バリア層30の上部に後からデポジションされる接着層または高分子材料との間の相互作用を防止する材料を含む。導電プラグ27がアルミニウムを含む本発明の実施形態においては、バリア層30は例えばタンクスチレンを含むことができる。本発明の範囲内において、バリア層として用いることが好適な他の材料を採用することも可能である。もっとも、バリア層30は導電性である必要がある。

#### 【0024】

例えばおおよそ100オングストロームの厚さまで、蒸発法によってバリア層30をデポジションした後、本発明の特定の実施形態においてはバリア層30の上に薄い接着層39が形成される。この様子が図5に示されている。接着層39の材料選択は、接着層39の上にデポジションされる分子フィルムが接着層39にのみ接着し、絶縁体層33には接着しないようになるよう行われる。例えば、導電プラグ27がアルミニウムを含み、バリア層30がタンクスチレンを含むと仮定すると、本実施形態においては、銅を含む接着層39が、ポリメチルフェニルアセチレン(Polymethylphenylacetylene)、またはフタロシアニン銅(Copperphthalocyanine)などの様々な異なった分子フィルムに対する接着層として機能させるためには好適である。従って、この薄い接着層39の選択は、採用される分子フィルムに依存する。単量体(Molecular)または重合体(Polymer)のフィルムを接着層39にのみ接着させ、絶縁体層33には接着させないようにする、セルフアセンブリの方法が採用される。この方法により、メモリ素子はトランジスタアレイに接続されているコンタクトの上の位置に正確に形成される。

#### 【0025】

以下で更に詳しく説明するように、本発明においてセルフアセンブリの方法でデポジションされる特定の分子フィルムは、電界または電流に応答して、制御可能に調節できる抵抗値を示すという特性を持つ。ひとたび特定の抵抗値状態に設定されると、メモリ素子はその抵抗値が消去されない限り、その状態をある期間保持する。

#### 【0026】

接着層39上の分子フィルムをセルフアセンブリの方法で形成するために、本発明の実施形態では、メモリアレイまたは記憶装置は比較的大きな空間またはチャンバ(箱、部屋)に設置され、小さな容量の液体モノマー(単量体)が設けられる。大きな空間にはモノマーガスも導入される。メモリセルまたは記憶装置がこのチャンバの中に一定時間、例えば3時間設置され、所望の温度範囲、例えばおおよそ室温に保たれる。これらの数値は単なる例示であって、使用される材料に応じてその他の数値を用いることも可能である。

#### 【0027】

様々な材料が単量体または重合体のフィルムとして使用可能である。本発明の特定の実施形態において、この材料は共役ポリマーである。本発明の他の実施形態では、この材料はフタロシアニンである。さらに、本発明のその他の実施形態では、この材料はポルフィリンである。これらの材料については、本出願の発明者の一人による論文、"Structural Instability of One-dimensional Systems as a Physical Principal Underlying the Functioning of Molecular Electronic Devices", Journal of Structural Chemistry, Vol. 40, No.4, 1999 (Ju. H. Krieger)に説明されている。この文献は、本出願に参照として含まれるものとする。

#### 【0028】

10

20

30

40

50

接着層にポリマーをデポジションするために、本発明はセルファセンブリの方法を提供する。この方法は、図8に示されるように、記憶装置またはメモリセルが、ガスモノマーが導入された大きなチャンバに設置される。比較的小な容量の液体モノマー52もチャンバ50に設置される。本発明の一実施形態においては、モノマーはメチルフェニルアセチレンである。気体と個体との界面において生じる重合プロセスにより、共役ポリマーの重合フィルムが生成される。この方法により、モノマーからポリマーフィルムを平坦でない複雑な表面、この場合はトランジスタアレイのコンタクト、に形成することができる。

## 【0029】

メチルフェニルアセチレンのモノマーの実施形態においては、メチルフェニルアセチレンの共役重合フィルムが生成される。メモリセルまたは記憶装置が、チャンバ50内に、室温で、およそ3時間保持された場合、フィルムの厚みは典型的にはおよそ1000オングストロームである。図6にそのフィルム35が示される。

10

## 【0030】

本発明の他の実施形態においては、形成される高分子フィルム35はフタロシアニン銅である。これらの実施形態においては、用いられるモノマーガスはテトラシアノベンゼン(Tetracyanobenzene)である。

## 【0031】

これらの高分子フィルムおよびモノマーは単なる例示であり、当業者は本発明の範囲内において、上述のフィルムを生成するために他のモノマーや他の高分子フィルムを採用可能であることは理解できるだろう。本発明において使用可能なポリ共役ポリマーの例としては、ポリパラフェニレン(Polyparaphenylene)、ポリフェニルビニレン(Polyphenylvinylene)、ポリアニリン(Polyaniline)、ポリチオフェン(Polythiophene)またはポリピロール(Polypyrrrole)などがある。

20

## 【0032】

図7に示されているように、セルファセンブリの方法で、トランジスタアレイの導電コンタクト上へのポリマーのデポジションを行った後、共通の電極が各コンタクト35の上に形成される。共通電極38は、アルミニウム、タンゲステン、金、銅などの適切な導電材料から形成することができる。共通電極38は、例えば、蒸発法によって形成可能である。

## 【0033】

30

製造された、本発明のメモリセルは、電界または電流の印加に応答して異なる抵抗値を記憶可能であるという特徴を持つ。例えば、書き込み電流の適切な印加によって、メモリセルは選択された異なる抵抗値を保持する。例えば、300オームの抵抗値は“00”的に対応し、およそ400オームは“01”的に対応し、およそ650オームは“11”的に対応する。これらの異なった抵抗値レベルはメモリセルに異なった書き込み電流を与えることによって実現される。

## 【0034】

記憶装置を形成するための使用方法とは別に、本発明のセルファセンブリの方法は、消去可能であるプログラム可能な抵抗値を持つ、接続パッドおよび接続経路を形成するためにも使用することができる。例えば、図9に示されるように、シリコン基板60をエッチングして、上部が張り出した(オーバーハングした)リブ62を形成することができる。この張り出しあは、従来技術、例えば異方性の化学エッティングまたはイオンビームのミリング(Milling)によって形成可能である。表面上に例示されたような分子の複合材料の層64をデポジションすることで、写真製版プロセスなしに複数の電気的に分離された接続線を形成することができる。外部の電界を接続線に印加するか、または接続線に電流を流すことによって接続線の抵抗値を「オフ」状態と「オン」状態の間で反転可能に切替えることができるので、これらの接続線はチップ上の異なったデバイスを選択的に相互接続するための新規な方法を提供する。

40

## 【0035】

上述したように本発明によれば、セルファセンブリの方法で容易に製造することができ

50

る記憶装置を提供し、従来のトランジスタアレイ上に複数ビットメモリセルを形成することができる。これによって、記憶装置のビット記憶密度を効率的に増加させる。セルファセンブリの方法によって、トランジスタアレイの各コンタクトにメモリセルのポリマーを正確に配置することが可能になる。

【0036】

以上のとおり、本発明を詳しく説明し、図示したが、上記の実施形態は説明のための單なる例示に過ぎず、本発明の範囲を限定しようとするものではないことは明らかなことが理解される。本発明の範囲は、添付の特許請求の範囲によってのみ判断されるべきものである。

【図面の簡単な説明】

10

【0037】

【図1】本発明の一実施形態であるメモリチップを示す概略図。

【図2】製造プロセスの一段階における、本発明の一実施形態であるメモリチップの一部の断面を示す斜視図。

【図3】本発明の一実施形態である製造プロセスの一段階における、図2のメモリアレイの側面図。

【図4】本発明の一実施形態における、導電プラグ上へのバリア層のデポジション後の図3の構造を示す図。

【図5】本発明の一実施形態における、バリア層上への接着層のデポジション後の図4の構造を示す図。

20

【図6】本発明の一実施形態における、導電コンタクト上へ、セルファセンブリの方法で形成されるポリマーメモリ素子のデポジション後の図5の構造を示す図。

【図7】本発明の一実施形態における、メモリ素子上への共通電極の形成後の図6の構造を示す図。

【図8】本発明の一実施形態における、セルファセンブリのプロセスを示す図。

【図9】本発明の一実施形態における、セルファセンブリの方法で形成された導電路の配線を示す断面図。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(74)代理人 100162156

弁理士 村雨 圭介

(74)代理人 100111615

弁理士 佐野 良太

(72)発明者 ジュリ エイチ・クリージャー

アメリカ合衆国マサチューセッツ州 02446、ブルックライン、ビーコン・ストリート 14

54

(72)発明者 ニコライ エフ・ユダノフ

アメリカ合衆国マサチューセッツ州 02446、ブルックライン、アパートメント 501、ビ

ーコン・ストリート 1450

審査官 井原 純

(56)参考文献 特表平11-505071(JP,A)

特開平01-098257(JP,A)

特表平11-504749(JP,A)

特開平06-028841(JP,A)

特開平04-333568(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/28

G11C 13/00

H01L 51/05