(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4655495号

(P4655495)

(45) 発行日 平成23年3月23日(2011.3.23)

(24) 登録日 平成23年1月7日(2011.1.7)

|                         |                    |

|-------------------------|--------------------|

| (51) Int.Cl.            | F 1                |

| HO 1 L 21/28 (2006.01)  | HO 1 L 21/28 301 A |

| HO 1 L 21/285 (2006.01) | HO 1 L 21/285 C    |

| HO 1 L 21/205 (2006.01) | HO 1 L 21/205      |

| HO 1 L 29/78 (2006.01)  | HO 1 L 29/78 301 G |

| HO 1 L 29/49 (2006.01)  | HO 1 L 29/58 G     |

請求項の数 4 (全 14 頁) 最終頁に続く

|           |                               |           |                                                 |

|-----------|-------------------------------|-----------|-------------------------------------------------|

| (21) 出願番号 | 特願2004-106048 (P2004-106048)  | (73) 特許権者 | 000219967<br>東京エレクトロン株式会社<br>東京都港区赤坂五丁目3番1号     |

| (22) 出願日  | 平成16年3月31日 (2004.3.31)        | (74) 代理人  | 100091513<br>弁理士 井上 俊夫                          |

| (65) 公開番号 | 特開2005-294457 (P2005-294457A) | (72) 発明者  | 高橋 豊<br>東京都港区赤坂五丁目3番6号 TBS放送センター 東京エレクトロン株式会社内  |

| (43) 公開日  | 平成17年10月20日 (2005.10.20)      | (72) 発明者  | 高木 聰<br>東京都港区赤坂五丁目3番6号 TBS放送センター 東京エレクトロン株式会社内  |

| 審査請求日     | 平成18年12月15日 (2006.12.15)      | (72) 発明者  | 富田 正彦<br>東京都港区赤坂五丁目3番6号 TBS放送センター 東京エレクトロン株式会社内 |

最終頁に続く

(54) 【発明の名称】成膜方法

## (57) 【特許請求の範囲】

## 【請求項 1】

被処理体を 560 以上の温度に加熱して、シリコンを含む成膜ガスを用い、被処理体の上にアモルファスシリコン膜を形成する成膜工程と、

次いで、この成膜工程時の温度よりも高く且つ680 以下の温度に前記被処理体を加熱することにより、前記アモルファスシリコン膜をポリ化して 第1のポリシリコン膜 を形成するポリ化工程と、

続いて、前記被処理体を、シリコンがポリ化する温度以上の温度に加熱して、シリコンを含む成膜ガスを用い、前記第1のポリシリコン膜の上にさらに第2のポリシリコン膜を形成する工程と、

かかる後、前記第1のポリシリコン膜及び前記第2のポリシリコン膜に導電性不純物元素を注入する工程と、を含むことを特徴とする成膜方法。

## 【請求項 2】

前記ポリ化工程は、不活性ガス雰囲気又は水素雰囲気で行うことを特徴とする請求項1記載の成膜方法。

## 【請求項 3】

前記被処理体はゲート絶縁膜が形成されたものであり、前記成膜工程、ポリ化工程及び前記第2のポリシリコン膜を形成する工程を行うことにより、このゲート絶縁膜の上にポリシリコン膜を成膜することを特徴とする請求項1記載の成膜方法。

## 【請求項 4】

前記導電性不純物元素を注入する工程は、ゲート電極を形成する工程であることを特徴とする請求項3に記載の成膜方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、例えばゲート絶縁膜上にゲート電極としてポリシリコン膜を形成する際に好適な成膜方法及び成膜装置に関する。

【背景技術】

【0002】

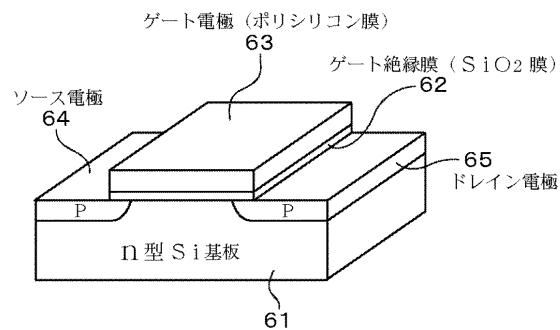

MOSFETトランジスタでは、ソース領域とドレイン領域との間のゲート絶縁膜上にゲート電極が形成され、このゲート電極により、ソースードレイン領域間に流れる電流が制御される。前記ゲート電極としてはポリシリコン膜(多結晶シリコン膜)が広く用いられており、従来から化学気相成長法(CVD)を用いて、モノシリコン(SiH4)ガス等をポリ化(多結晶化)する温度雰囲気下で熱分解することにより、ゲート絶縁膜上に微結晶粒子(グレイン)の集まりとなるポリシリコン膜を成膜していた。そして成膜時の温度、圧力、ガス種、流量を調節することにより、前記微結晶粒子のグレインサイズの調整を行っていた。

【0003】

ここでこのゲート電極は、ソースードレイン領域と同一の導電型にドーピングされており、pチャネルMOSFETトランジスタの場合には、n型シリコン基板上にp型のソースードレイン領域と、p型のゲート電極とが形成され、このためにポリシリコン膜にp型不純物であるボロン(B)が添加されている。

【0004】

このボロンの添加はイオン注入法により行われ、注入種であるボロンなどをイオン化し、これを電界加速した後、磁界を用いた質量分析器で注入種と荷電種を選択し、さらに電界加速して打ち込むことにより行われている。この際、注入エネルギーによってボロンのポリシリコン膜の厚さ方向の打ち込み深さが制御される。

【0005】

ところで近年のデバイスの薄膜化に伴い、ゲート電極であるポリシリコン膜も0.1μm程度の厚さに薄くなっている。このため従来の手法で成膜されたポリシリコン膜では、ボロンの添加を行うと、ボロンがポリシリコン膜を突き抜け、ポリシリコン膜の下層側のゲート絶縁膜や、ソースードレイン領域に到達し、電気的特性の悪化を招いていた。一方ボロン添加の際のイオン注入エネルギーを小さくすると、膜表面で跳ね返ってしまい、結果としてポリシリコン膜へのボロン添加ができなくなってしまうので、前記注入エネルギーをある程度以下にはできないという事情がある。

【0006】

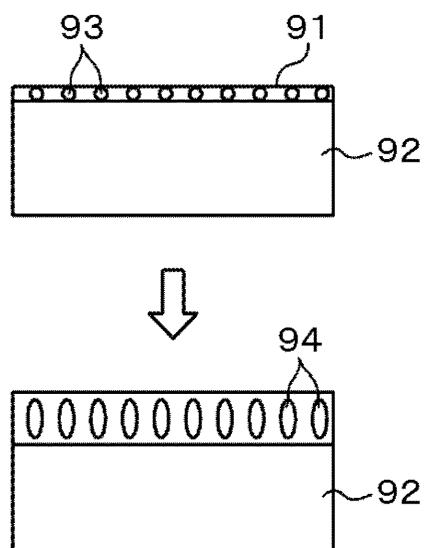

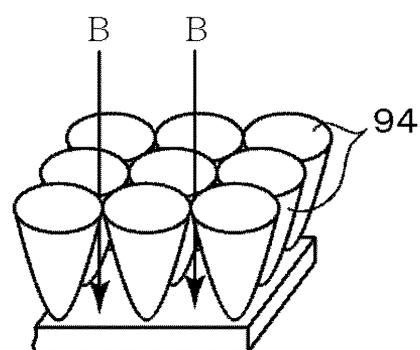

このようにポリシリコン膜にてボロンの突き抜け現象が発生する理由としては、例えばポリシリコン膜の成膜時、シランガス等をポリ化する温度例えば620で熱分解すると、図9に示すように、ポリシリコン膜91はゲート絶縁膜92側から結晶成長していくので、成膜初期時に、錐状に結晶が成長する核93が発生しやすく、これによりゲート絶縁膜92側に錐状結晶94が生成しやすい傾向がある。このように錐状結晶であると、図10に示すように、結晶がポリシリコン膜の厚さ方向に伸びているので、ボロンを添加すると、水平方向の結晶粒界が少なく、ボロンが主に結晶同士の間を通過して突き抜けてしまうためと考えられる。またポリシリコン膜の形成の際、錐状結晶上部に球状結晶が生成されたとしてもほとんどボロン突き抜け耐性を上げることはできないと推察される。ここでボロンの突き抜け防止の技術として、特許文献1の技術が提案されている。

【0007】

【特許文献1】特開2001-68662号公報

【発明の開示】

【発明が解決しようとする課題】

10

20

30

40

50

## 【0008】

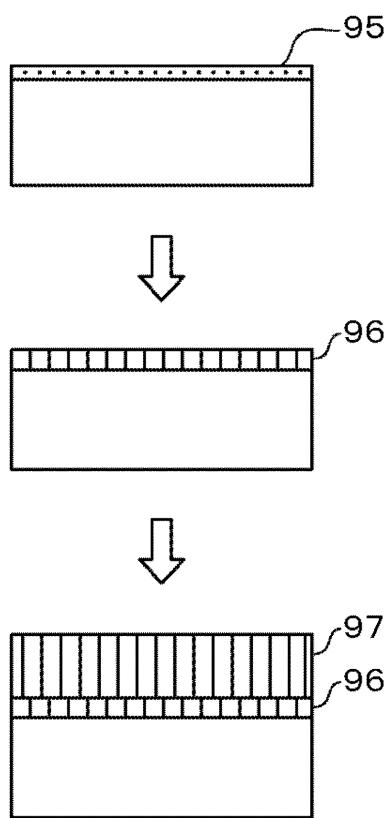

この特許文献1の技術は、図11に示すように、薄いアモルファス半導体層95を成膜する第1の工程と、このアモルファス半導体層95を熱処理して、多結晶半導体層96に変換する第2の工程と、この多結晶半導体層96上に第2の多結晶半導体層97を堆積する第3の工程との3段階からなり、第1の工程で薄いアモルファス半導体層95を成膜し、第2の工程でこのアモルファス半導体層95をポリ化し、第3の工程でさらに多結晶半導体層96を成長させるものである。

## 【0009】

ところで本発明者らは、成膜工程時の温度とアモルファスシリコン膜の結晶構造との間には相関関係があり、後述するように成膜工程時の温度が560以上600以下の場合には、アモルファスシリコン膜が多数の核が散在した状態で形成できることを見出している。

10

## 【0010】

ここで特許文献1の前記第1の工程では、段落0023に記載されているように530で薄いアモルファスシリコン膜を成膜しているので、アモルファス半導体層95は核が散在しない状態で形成されると推察される。このためこの技術では、薄いアモルファス半導体層95の表面が荒れた状態になっていて、第2の工程ではこの荒れた表面から核が成長してそのまま柱状に伸びていき、ポリ化が行われると考えられる。従ってこの特許文献1においても、多結晶半導体層96、97では柱状結晶が形成されると推察される。

20

## 【0011】

またこの文献1では、例えばグレインサイズが25nm以下の多結晶半導体層97を形成することを目的としており、グレインサイズの測定を行っているが、グレイン観察は膜の上から見ているので、ここでいうグレインサイズは微結晶粒子の上面サイズをいい、このことからも結晶は柱状であると考えられる。従ってこの文献で形成された多結晶半導体層96、97においても、ボロンの添加工程では、ボロンの突き抜けが発生すると考えられる。

## 【0012】

本発明は、このような事情の下になされたものであり、その目的は、被処理体にポリシリコン膜を形成するに際し、後の工程で導電性不純物元素を添加するときの、当該導電性不純物元素のポリシリコン膜の厚さ方向への突き抜けを防止することができる成膜方法を提供することにある。

30

## 【課題を解決するための手段】

## 【0013】

本発明の成膜方法は、被処理体を560以上の温度に加熱して、シリコンを含む成膜ガスを用い、被処理体の上にアモルファスシリコン膜を形成する成膜工程と、

次いで、この成膜工程時の温度よりも高く且つ680以下の温度に前記被処理体を加熱することにより、前記アモルファスシリコン膜をポリ化して第1のポリシリコン膜を形成するポリ化工程と、

続いて、前記被処理体を、シリコンがポリ化する温度以上の温度に加熱して、シリコンを含む成膜ガスを用い、前記第1のポリシリコン膜の上にさらに第2のポリシリコン膜を形成する工程と、

40

しかる後、前記第1のポリシリコン膜及び前記第2のポリシリコン膜に導電性不純物元素を注入する工程と、を含むことを特徴とする。ここで前記ポリ化工程は、不活性ガス雰囲気又は水素雰囲気で行うようにしてもよい。

## 【0016】

ここで前記被処理体は、ゲート絶縁膜が形成されたものであり、前記成膜工程、ポリ化工程及び前記第2のポリシリコン膜を形成する工程を行うことにより、このゲート絶縁膜の上にポリシリコン膜が成膜され、前記導電性不純物元素を注入する工程は、ゲート電極を形成する工程である。

## 【発明の効果】

50

## 【0017】

本発明によれば、被処理体にポリシリコン膜を形成するに際し、被処理体を560以上アモルファス層が得られる温度以下の温度に加熱してアモルファスシリコン膜を形成し、次いで前記被処理体を成膜時の温度よりも高く且つ680以下の温度に加熱することにより、前記アモルファスシリコン膜をポリ化してポリシリコン膜を形成しているので、ポリシリコン膜は球状結晶の集合体または、球状結晶と錐状結晶の混合体により形成される。このようなポリシリコン膜は微結晶粒子の粒界が種々の方向を向いて形成されるので、後の工程で当該ポリシリコン膜へ導電性不純物元素を添加したときに、この不純物元素が前記粒界でトラップされ、当該不純物元素のポリシリコン膜の厚さ方向への突き抜けを防止することができる。

10

## 【発明を実施するための最良の形態】

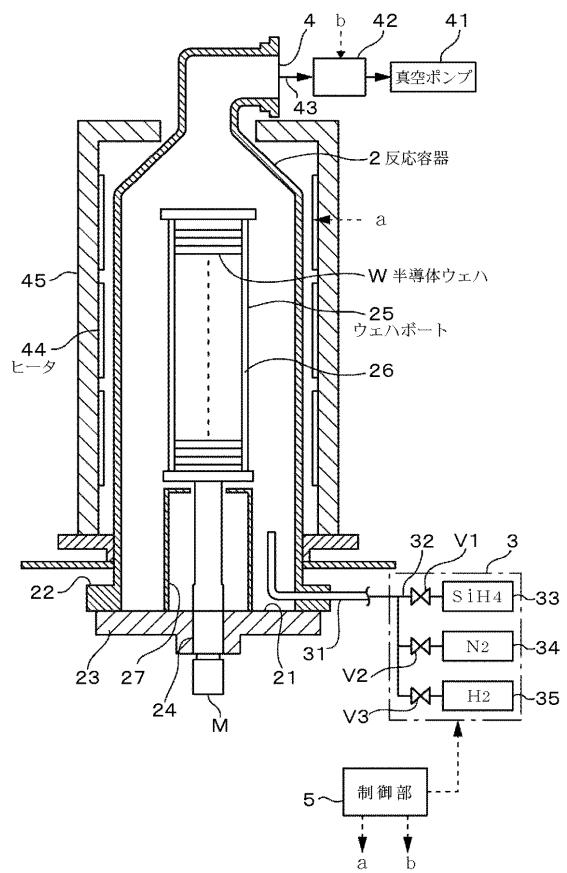

## 【0018】

先ず本発明に係る成膜装置の実施の形態について説明する。図1は、成膜装置であるバッチ式の減圧CVD装置であり、図1中2は、例えば石英により縦型の円筒状に形成された反応容器である。この反応容器2の下端は、炉口として開口され、その開口部21の周縁部にはフランジ22が一体に形成されている。前記反応容器2の下方には、フランジ22の下面に当接して開口部21を気密に閉塞する、例えば石英製の蓋体23が図示しないポートエレベータにより上下方向に開閉可能に設けられている。蓋体23の中央部には、回転軸24が貫通して設けられ、その上端部には、被処理体保持具であるウエハポート25が搭載されている。

20

## 【0019】

このウエハポート25は、3本以上例えば4本の支柱26を備えており、複数枚例えば125枚の被処理体である半導体ウエハ(以下「ウエハ」という)Wを棚状に保持できるように、前記支柱26に溝(スロット)が形成されている。但し、125枚のウエハWの保持領域の内、上下両端部については複数枚のダミーウエハが保持され、その間の領域に製品ウエハが保持されることになる。前記回転軸24の下部には、当該回転軸24を回転させる駆動部をなすモータMが設けられており、従ってウエハポート25はモータMにより回転することになる。また蓋体23の上には前記回転軸24を囲むように保温ユニット27が設けられている。

30

## 【0020】

前記反応容器2の下部のフランジ22には、反応容器1内のウエハWにガスを供給するためのL字型のインジェクタ31が挿入して設けられている。インジェクタ31の基端側には、ガス供給路であるガス供給管32が接続されており、ガス供給管32の他端側は、夫々バルブV1,V2,V3を介して成膜ガス供給源33、不活性ガス例えば窒素(N2)ガスの供給源34、水素(H2)ガスの供給源35に接続され、前記ガス供給管32、インジェクタ31を介して反応容器2の中に成膜に必要なガスを供給できるようになっている。ここでガス供給管32、成膜ガス供給源33、不活性ガスの供給源34、水素ガスの供給源35、バルブV1,V2,V3によりガス供給部3が構成されている。

40

## 【0021】

前記成膜ガスとしては、シリコン(Si)と水素とを含むガス、例えばモノシリラン(SiH4)ガス、ジシリラン(Si2H6)ガス、ジクロロシリラン(SiH2Cl2)ガス、テトラクロロシリラン(SiCl4)ガス、ヘキサクロロシリラン(SiH2Cl6)ガス、ヘキサエチルアミノジシリランガス、ヘキサメチルジシラザンガス、ジシリルアミンガス、トリシリルアミンガス、ビスター・シヤルブチルアミノシリランガスなどを用いることができる。

## 【0022】

また反応容器2の上方には、反応容器内を排気するための排気口4が形成されている。この排気口4には、反応容器内を所望の真空中に減圧排気可能な真空排気手段をなす真空ポンプ41及び圧力調整部42を備えた排気管43が接続されている。反応容器2の周囲には、反応容器2内を加熱するための加熱手段であるヒータ44を備えた加熱炉45が設

50

けられている。前記ヒータ44としては、コンタミネーションがなく昇降温特性が優れたカーボンワイヤー等を用いることが好ましい。

【0023】

さらにこの減圧CVD装置は、コンピュータからなる制御部5を備えている。この制御部5は、処理プログラムを起動し、図示しないメモリ内のプロセスレシピの記載事項を読み出して、そのレシピに基づいて処理条件を制御する機能を有し、ヒータ44、圧力調整部42及びガス供給部3を夫々制御するための制御信号を出力する。

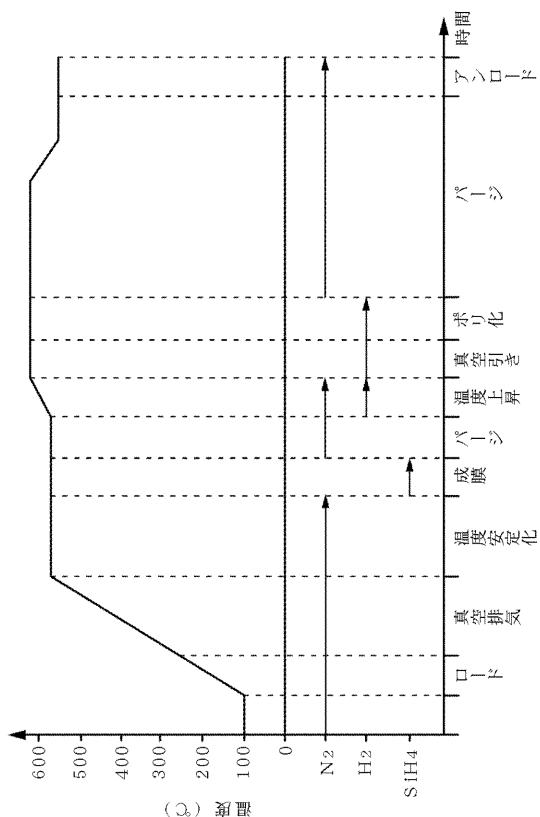

【0024】

次に上述の減圧CVD装置を用いて実施する成膜方法の一例について図2を用いて説明する。先ず被処理体である半導体ウエハW、例えば図3に示すように、n型シリコン基板61上にゲート絶縁膜をなすシリコン酸化膜(SiO<sub>2</sub>)62が形成されたウエハWを所定枚数ウエハポート25に保持させて、例えば温度が100程度に維持された反応容器2内に、図示しないポートエレベータを上昇させることにより搬入(ロード)する。

10

【0025】

ウエハポート25が搬入されて反応容器2の下端開口部21が蓋体23により塞がれた後、反応容器2内の温度を例えば200/分の昇温速度で、550以上でアモルファス層が得られる温度を越えない温度例えば580まで昇温させると共に、反応容器2内を排気口4を通じて真空ポンプ41により所定の真空度に真空排気する。ここで前記アモルファス層が得られる温度とは、それよりも高くするとポリシリコン膜になってしまう温度であり例えば600以下の温度である。

20

【0026】

そして反応容器2内の温度を例えば580に安定させた後、成膜ガス供給源33から例えばモノシランガスを所定の流量例えば180~4000sccmで反応容器2内に供給し、更に圧力調整部42により反応容器2内を例えば13.3~40Pa(0.1~0.3Torr)の減圧雰囲気に調整して成膜工程を10分程度行う。

【0027】

反応容器2内では、モノシランガスが熱分解して、シリコンと水素とを含むアモルファスシリコン膜がウエハWのゲート絶縁膜62の表面に成膜される。ここでこの成膜工程は、後述するように550以上の温度で実施することが必要であり、特に560以上の温度で行うことが好ましい。なお、この工程における上限温度はアモルファス層が得られる温度であり、マージンを考慮すると現実的には600であると考えられる。

30

【0028】

次いで成膜ガスの供給を停止し、窒素ガスの供給を開始して、反応容器2内の残存ガスを排気するために窒素ガスによるバージを行う。続いて窒素ガスを供給した状態で水素ガスの供給を開始して、反応容器2内の温度をアモルファスシリコン膜がポリ化する温度以上の温度例えば620まで、例えば50/分の昇温速度で昇温させ、次いで窒素ガスの供給を停止する一方水素ガスは供給して、圧力調整部42により反応容器2内の圧力を例えば2660~26600Pa(20~200Torr)の減圧雰囲気に調整する。

【0029】

次いで水素ガスを供給した状態で、所定時間例えば10分程度、アモルファスシリコン膜が形成されたウエハWに対して熱処理(アニール)を行い、これによりポリ化工程を実例する。これにより成膜工程にて形成されたアモルファスシリコン膜がポリ化して、ポリシリコン膜が形成される。

40

【0030】

これら一連の工程を行っている間、ウエハポート25はモータMにより回転している。こうしてゲート絶縁膜62上に所定の厚さ例えば150nmでポリシリコン膜を形成した後、反応容器2内への水素ガスの供給を停止し、窒素ガスの供給を開始してバージを行い、反応容器2内の圧力を大気圧に戻すと共に、反応容器2内の温度を例えば300~600の設定された温度まで下降させ、ウエハポート25を反応容器2から搬出(アンロード)する。

50

## 【0031】

そして搬出されたウエハWは、その後、ポリシリコン膜にボロンなどの導電型不純物元素が例えればイオン注入により添加された後、フォトリソグラフィとエッチングによりゲート電極63が形成され、さらにシリコン基板61に導電性不純物元素が打ち込まれて不純物拡散層が形成される。しかる後、これら不純物拡散層の上にソース電極64及びドレイン電極65を形成し、半導体装置であるMOSFETトランジスタが製造される。

## 【0032】

このような手法で形成されたポリシリコン膜は、膜が細粒化され、微結晶粒子が球状であるので、後の工程にて不純物元素例えればボロンを添加する際、粒子間の境界でボロンがトラップされ、ボロンの突き抜けを抑えることができる。このためゲート電極63が膜厚が例えれば0.1μm程度に薄膜化しても、不純物元素の突き抜けを抑えて、確実に不純物元素を添加できる。これにより例えれば不純物元素がポリシリコン膜63を突き抜けて下層側のゲート絶縁膜62やソース電極64、ドレイン電極65に添加されてしまい、電気的特性が悪化する状態の発生を抑えることができる。

10

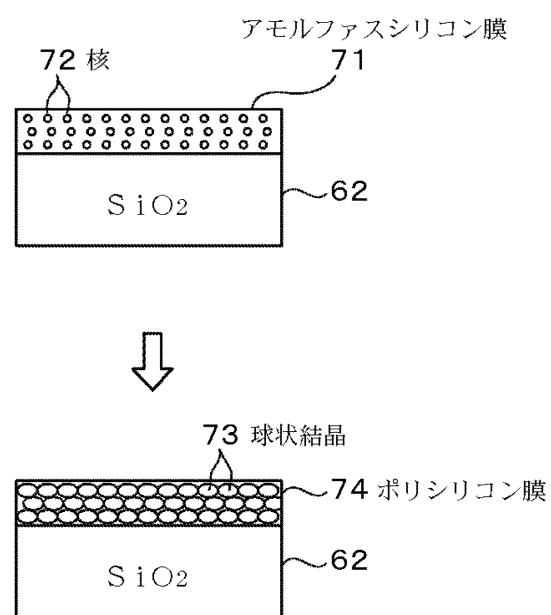

## 【0033】

このように球状の微結晶粒子より構成されたポリシリコン膜を形成できるのは次のような理由による。即ち580の温度で成膜工程を行っているので、例えれば図4に示すように、アモルファスシリコン膜71が、多数の核72が散在した状態で生成される。そしてこの工程により、アモルファスシリコン膜71中に結晶となる核72を散在させ、その後成膜工程よりも高いアモルファスシリコン膜71のポリ化が行われる温度でポリ化工程を行うと、成膜工程にて形成された核72が加熱処理により当該核72を中心に再結晶化して成長し、これにより微結晶粒子が球状結晶73に成長し、細粒化が可能になると推察される。なお球状結晶とは、真球に近い形状のみを意味するものではなく、既述の錘状結晶と比較するための用語であって、アモルファスシリコン膜中の核がある程度三次元的に同程度成長したものであれば、球形から崩れた形状のものも含まれる。

20

## 【0034】

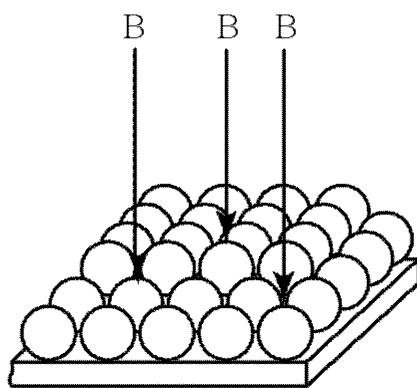

このように微結晶粒子が球状結晶であると、粒界が種々の方向でランダムに多数形成され、この粒界はダンギリングボンドが多いので、例えば後の工程でボロン等の導電性不純物元素の活性粒子をポリシリコン膜73に添加した場合、前記無結合状態の界面がボロン等の移動、拡散に対して障壁となるので、ボロン等が前記粒界にトラップされ、図5に示すように、ポリシリコン膜の厚さ方向へのボロン等の突き抜けが抑えられると推察される。

30

## 【0035】

このため本発明では、球状結晶を含むポリシリコン膜を形成するためには、先ず第1段階でアモルファスシリコン膜を成膜し、次いで第2段階でアモルファスシリコン膜のポリ化を行うことが必要であり、このため後述する実施例からも明らかなように、第1段階では550以上であってアモルファスシリコン膜が形成できる温度以下の温度、好ましくは560以上600以下の温度で成膜工程を行い、次いで第2段階ではアモルファスシリコン膜のポリ化を行う温度以上の温度例えれば620以上で加熱処理を行っている。

40

## 【0036】

ここで後述の実施例より明らかなように、アモルファスシリコン膜の結晶状態と成膜工程の温度との間には相関関係があり、本発明者らはアモルファスシリコン膜の成膜工程の温度は550以上の温度で行うことが必要であると考えている。この際後述の実施例により明らかなように、アモルファスシリコン膜を多数の核が散在する状態で形成するためには、560以上600以下の温度で成膜工程を行うことが好ましいが、成膜温度が550である場合にも、球状結晶と錘状結晶とが混在する状態でポリシリコン膜が形成されるので、従来のように錘状結晶のポリシリコン膜よりも粒界が多く存在し、前記ボロン等のポリシリコン膜の厚さ方向への突き抜けが抑えられる。

## 【0037】

なお成膜温度が550である場合には、成膜温度が560の場合よりもアモルファ

50

スシリコン膜中に核が散在する程度は小さくなるものの、前記核は散在しており、ポリ化工程では前記核やアモルファスシリコン膜表面を起点として結晶が成長するので、これにより球状結晶と錐状結晶とが混在する状態でポリシリコン膜が形成されると推察される。これに対し、背景技術の欄にて説明した引用文献1の技術では、第1の工程を530で行っているので、アモルファス半導体層は核が散在しない状態で形成されると推察される。

【実施例】

【0038】

(実験例1)

上述の装置を用いて、上述の条件、つまり成膜温度580、アニール温度620、成膜温度からアニール温度に温度上昇させるときの反応容器内の雰囲気を水素雰囲気、アニール時の反応容器内の雰囲気を水素雰囲気として、シリコン酸化膜よりなるゲート絶縁膜62の上面に厚さ50nmのポリシリコン膜を形成し、そのポリシリコン膜に対してTEM(透過型電子顕微鏡)により、ポリシリコン膜の厚さ方向の断面を観察した。

10

【0039】

また比較例として、上述の装置を用いて、従来の条件、つまり成膜温度620にて、ゲート絶縁膜62をなすシリコン酸化膜の上面に厚さ50nmのポリシリコン膜を形成したものについても、同様にTEM(透過型電子顕微鏡)により、ポリシリコン膜の厚さ方向の断面を観察した。

【0040】

20

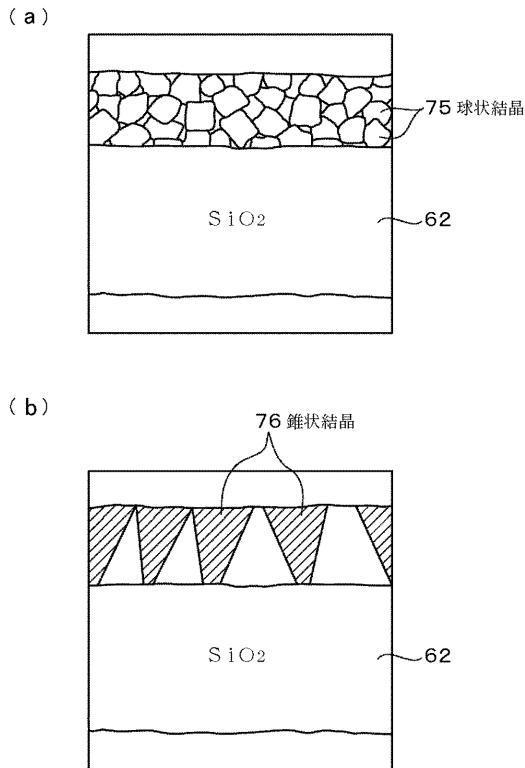

これらの結果を、TEMの撮影写真をトレースして、本発明方法により形成したポリシリコン膜については図6(a)に、従来の手法により形成したポリシリコン膜については図6(b)に夫々示す。この結果、本発明方法により形成したポリシリコン膜は、同じような大きさの球状の微結晶粒子(球状結晶75)の集合体として構成されており、膜の厚さ方向にも多数の微結晶粒子が存在することが認められた。一方従来の手法により形成したポリシリコン膜は、図6(b)中斜線で示すように、膜の厚さ方向に伸び、下側(シリコン酸化膜側)よりも上側が大きい、錐状の結晶76であることが認められた。

【0041】

これにより本発明方法により形成したポリシリコン膜は、球状結晶が接触する界面である結晶粒界が多数存在し、後の工程においてポリシリコン膜の表面側から導電性不純物元素が添加されたとき、ポリシリコン膜の下面に到達する前に、膜の厚さ方向に多数存在する結晶粒界にトラップされ、こうしてポリシリコン膜に均一に拡散されて、不純物元素のポリシリコン膜の突き抜けが防止されると推察される。一方従来の手法により形成したポリシリコン膜は、結晶が膜の厚さ方向に伸びていて、膜の下方側が極端に狭まっているので、膜の下方側は結晶が存在する領域が極めて少ない状態である。このため後の工程においてポリシリコン膜の表面側から不純物元素がポリシリコン膜に注入できるエネルギーで添加されると、結晶粒界が少ないかまたは無いので、不純物イオンがトラップされずにポリシリコン膜を突き抜けてしまうと考えられる。

30

【0042】

(実験例2)

40

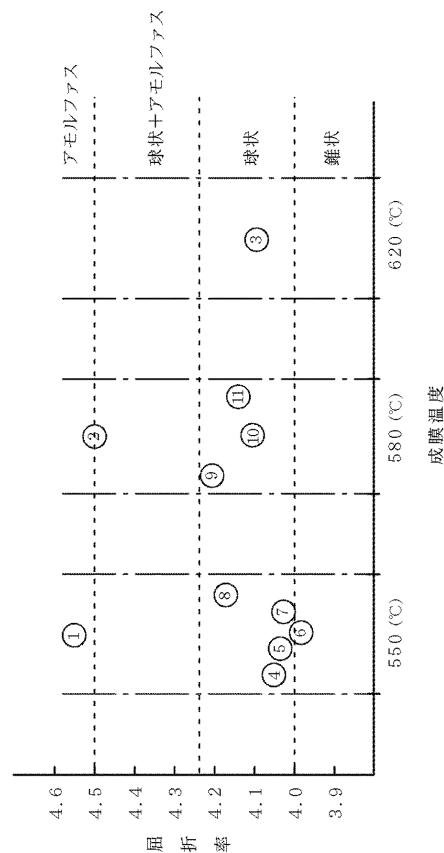

上述の装置を用いて、処理条件を(1)~(11)(図7、図8では丸付きで表示している)まで変えてポリシリコン膜を形成し、そのポリシリコン膜に対してX線回折による結晶構造解析及び屈折率の測定を行った。ここで(1)~(3)は比較例であって成膜処理の後にポリ化のための熱処理を行わない例、(4)~(11)は本発明の実施例であって、550以上アモルファス層が得られる温度以下の温度でアモルファスシリコン膜の成膜処理を行い、次いでアモルファスシリコン膜のポリ化処理を行う例である。

【0043】

各処理条件の成膜温度、アニール温度、成膜温度からアニール温度に温度上昇させるときの雰囲気、膜厚、屈折率、X線回折の解析結果としてグレインサイズを図7に夫々示す。ここでX線回折装置を用いて、比較例(3)、実施例(6)、(7)(成膜温度が550),

50

実施例(9)、(10)、(11)（成膜温度が580℃）について、Si(111)面とSi(220)面、Si(311)面についてグレインサイズを測定することにより行い、屈折率はCaliber 300を用いて測定した。また図7中比較例(1)や実施例(9)、(11)のグレインサイズは、2個のデータが記載されているが、左側がウエハWの中央部、右側が周縁部のデータを示している。なお実施例(9)のSi(111)面のデータは、周縁部のグレインサイズが8.1nmということである。

#### 【0044】

さらにX線回折及び屈折率の測定結果を図7、図8に夫々示す。これによりX線回折の結果、比較例(3)はSi(111)面とSi(220)面が存在し、実施例(6)、(7)はSi(111)面とSi(220)面が存在するものの、比較例(3)とは大きさが異なり、実施例(9)～(11)はSi(111)面とSi(311)面が存在することが認められ、比較例(3)と、実施例(6)、(7)と、実施例(9)、(10)、(11)とは、得られるポリシリコン膜の結晶構造が異なることが認められる。

#### 【0045】

つまり比較例(3)の場合には、Si(111)面の大きさが3.1～3.9nmであるのに対して、Si(220)面の大きさが18.8～24.5nmとかなり大きいので、このデータからも膜厚の厚さ方向に伸びる錐状結晶が形成されていることが理解される。また実施例(6)、(7)の場合には、Si(111)面の大きさとSi(220)面の大きさとが、夫々14.1μm、13.6μmと同じ程度か、またはSi(111)面の大きさ(11.2μm)よりもSi(220)面の大きさ(3.4μm)が小さいので、膜厚の厚さ方向に伸びる錐状結晶と球状結晶とが混在した状態であることが理解される。またSi(220)面が存在するといつても、その大きさは比較例(3)よりもかなり小さいので、膜の厚さ方向にも多数の錐状結晶や球状結晶が存在すると推察され、比較例(3)の結晶構造よりも膜の厚さ方向に粒界が多くなると考えられる。

#### 【0046】

さらに実施例(9)、(10)、(11)では、Si(111)面とSi(311)面の大きさがほぼ同じ程度であり、この大きさが5μm～9.8μm程度と小さいことからこのデータからも同じ程度の大きさの球状結晶が多数ランダムに積まれていることが理解される。従ってこのようなポリシリコン膜では、球状結晶の粒界が種々の方向でランダムに多数形成されるので、導電性不純物元素のような活性粒子が添加された場合、この不純物元素をトラップしやすい構造である。

#### 【0047】

さらにまた屈折率のデータを図8に示すが、屈折率と結晶構造とは相関関係があり、屈折率が4.5以上の場合にはアモルファス層、屈折率が4.24以上4.5未満の場合は球状結晶とアモルファス層との混在、屈折率が4.0以上4.24未満の場合は球状結晶、屈折率が4.0未満の場合は錐状結晶である。

#### 【0048】

ここで屈折率は測定機器によってデータに誤差が生じ、精度は悪いものの、成膜温度が550℃である実施例(4)～(7)は錐状結晶側に近い球状結晶の領域、成膜温度が580℃である実施例(8)～(11)は球状結晶の領域（あるいは球状結晶と非晶質の混在に近い領域）に位置しており、成膜温度によって得られるポリシリコン膜の結晶構造が異なるという概ねの傾向は把握できる。さらにこの屈折率の結果により、比較例(1)、(2)は非晶質の領域に位置しているので、成膜工程を終了した状態ではアモルファス状であったシリコン膜が高温でアニールを行うことにより、結晶化されてポリ膜に変化することが理解される。

#### 【0049】

このようにアモルファスシリコン膜の結晶状態と成膜工程の温度との間には相関関係があり、球状結晶を含むポリシリコン膜を形成するためには、550℃以上の温度で成膜工程を行い、アモルファス層を形成する必要があることが認められる。また上述の実施例2により、ポリシリコン膜を球状結晶の集合体により形成する場合には、560℃以上600℃以下の温度で成膜工程を行うことが好ましいと考えられ、この場合には成膜工程にて

10

20

30

40

50

アモルファスシリコン膜が多数の核が散在する状態で形成され、次いでポリ化工程にて前記核が再結晶化して成長することにより、ポリシリコン膜が球状結晶の集合体により形成されると推察される。

【0050】

また成膜温度が550である場合には、球状結晶と錐状結晶とが混在する状態でポリシリコン膜が形成されるが、この場合では成膜温度が560である場合よりも核が散在する程度は小さいものの、アモルファスシリコン中に核が散在し、ポリ化工程では前記核やアモルファスシリコン膜表面およびSiO<sub>2</sub>界面を起点として結晶が成長するので、これにより球状結晶と錐状結晶とが混在する状態でポリシリコン膜が形成されると推察される。

10

【0051】

以上のように実施例2の結果から、成膜工程時に620で成膜した場合には、成膜時にポリ化してしまうため、細粒化は起こらず、成膜工程時に球状結晶を成膜できる温度条件、この例では550において成膜された膜をアニールすることにより得られたポリシリコン膜は、錐状結晶と球状結晶とを含むものであること、また成膜工程時に球状結晶と非晶質層とを成膜できる温度条件、この例では580において成膜された膜をアニールすることにより得られたポリシリコン膜は、より結晶粒径が小さく細粒化されたものであることが認められ、これにより成膜工程時の温度は550以上であってアモルファス層が得られる温度以下の温度、好ましくは560以上600以下の温度であることが必要であり、アニール工程時の温度はアモルファスシリコン膜のポリ化が行われる温度例えば610以上の温度であることが必要である。

20

【0052】

以上において本発明では、成膜工程とポリ化工程を行い、例えば50nm程度の厚さの第1のポリシリコン膜を形成した後、この第1のポリシリコン膜の上面に例えばポリ化できる温度例えば620以上の温度で、シリコンを含む成膜ガスを用いて例えば100nm程度の厚さの第2のポリシリコン膜を成膜するようにしてもよい。

【0053】

この場合には、後の工程にて不純物元素が添加される場合、第1のポリシリコン膜により不純物元素がトラップされて不純物元素の突き抜けが防止され、一方第2のポリシリコン膜は、ポリ化できる温度で成膜されているので、結晶の成長速度が大きく、所定の厚さのポリシリコン膜を形成する場合に、第1のポリシリコン膜よりも短い時間で成膜することができる。従ってゲート電極としては例えば100nm程度の膜厚が必要となるが、第1のポリシリコン膜により不純物元素の突き抜けを防止し、第2のポリシリコン膜により膜厚を確保することにより、第1のポリシリコン膜にてゲート電極の膜厚を確保する場合に比べて、トータルの成膜時間を短縮することができる。

30

【0054】

さらに本発明では、温度上昇工程は水素雰囲気で行ってもよいし、ポリ化工程は窒素雰囲気で行ってもよい。また本発明により形成されたポリシリコン膜に後の工程にて添加される導電性不純物として、伝導型がp型となる不純物としてはボロンの他にインジウム(In)やアルミニウム(Al)等、伝導型がn型となる不純物としてはリン(P)やヒ素(As)等を夫々用いることができる。

40

【図面の簡単な説明】

【0055】

【図1】本発明に係る成膜装置の一例を示す縦断面図である。

【図2】前記成膜装置にて実施される本発明の成膜方法の工程を説明するための特性図である。

【図3】本発明のポリシリコン膜が用いられるMOSFETトランジスタの構造を示す斜視図である。

【図4】本発明方法にてポリシリコン膜を形成するときの結晶の成長状態を説明するための断面図である。

50

【図5】本発明方法にて形成されたポリシリコン膜の結晶構造と、ボロンの添加の様子を示す斜視図である。

【図6】本発明方法にて形成されたポリシリコン膜と、従来の手法により形成されたポリシリコン膜をTEMにより観察したときのポリシリコン膜の断面を示す図である。

【図7】本発明方法にて形成されたポリシリコン膜と、従来の手法により形成されたポリシリコン膜とに対して、X線回折による結晶構造解析と、屈折率の測定結果を示す特性図である。

【図8】本発明方法にて形成されたポリシリコン膜と、従来の手法により形成されたポリシリコン膜の屈折率の測定結果を示す特性図である。

【図9】従来方法にてポリシリコン膜を形成するときの結晶の成長状態を説明するための断面図である。

【図10】従来方法にて形成されたポリシリコン膜の結晶構造と、ボロンの添加の様子を示す斜視図である。

【図11】特許文献1の方法にてポリシリコン膜を形成するときの結晶の成長状態を説明するための断面図である。

【符号の説明】

【0056】

|     |          |    |

|-----|----------|----|

| W   | 半導体ウエハ   |    |

| 2   | 反応容器     |    |

| 2 5 | ウエハポート   | 20 |

| 3   | ガス供給部    |    |

| 3 2 | ガス供給管    |    |

| 3 3 | 成膜ガス供給源  |    |

| 3 4 | 不活性ガス供給源 |    |

| 3 5 | 水素ガス供給源  |    |

| 4 1 | 真空ポンプ    |    |

| 4 4 | ヒータ      |    |

| 4 5 | 加熱炉      |    |

| 5   | 制御部      |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

|             | 成膜温度<br>(℃) | 温度上昇特<br>性 | アニール温度<br>(℃) | 膜厚<br>(nm) | 屈折率  | グレインサイズ<br>(nm)               |

|-------------|-------------|------------|---------------|------------|------|-------------------------------|

| 比<br>較<br>例 | ① 550       |            |               | 50.44      | 4.54 | Si(111) Si(220) Si(311)       |

|             | ② 580       |            |               | 50.39      | 4.50 |                               |

|             | ③ 620       |            |               | 50.21      | 4.09 | 3.9/3.1 24.5/ <sub>18.8</sub> |

| 実<br>施<br>例 | ④ 550       | N2         | N2            | 51.51      | 4.04 |                               |

|             | ⑤ 550       | H2         | H2            | 51.16      | 4.03 |                               |

|             | ⑥ 550       | N2         | N2            | 52.08      | 3.99 | 14.1 13.6                     |

|             | ⑦ 550       | H2         | H2            | 51.87      | 4.01 | 11.2 3.4                      |

|             | ⑧ 580       | N2         | N2            | 54.63      | 4.17 |                               |

|             | ⑨ 580       | H2         | H2            | 50.91      | 4.22 | /8.1 5.0/9.8                  |

|             | ⑩ 580       | N2         | N2            | 52.73      | 4.10 | 8.4                           |

|             | ⑪ 580       | H2         | H2            | 51.34      | 4.14 | 8.1/6.1 9.3/9.8               |

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/423 (2006.01) C 23 C 16/24

C 23 C 16/24 (2006.01) C 23 C 16/56

C 23 C 16/56 (2006.01)

審査官 辻 弘輔

(56)参考文献 特公昭64-007488 (JP, B1)

特開2000-357666 (JP, A)

特開平05-136048 (JP, A)

特開2001-210820 (JP, A)

特開平04-127519 (JP, A)

特開2001-068662 (JP, A)

特開2002-134420 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/28

H 01 L 21/285

H 01 L 21/205

H 01 L 21/336

H 01 L 29/423

H 01 L 29/49

H 01 L 29/78

C 23 C 16/24

C 23 C 16/56