(19) RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(à utiliser que pour les

commandes de reproduction)

2 622 354

(21) N° d'enregistrement national : 88 13845

(51) Int Cl<sup>4</sup> : H 01 L 29/48, 29/80.

(12)

## DEMANDE DE BREVET D'INVENTION

A

(22) Date de dépôt : 21 octobre 1988.

(71) Demandeur(s) : MITSUBISHI DENKI KABUSHIKI KAISHA. — JP.

(30) Priorité : JP, 22 octobre 1987, n° 62-268435.

(43) Date de la mise à disposition du public de la demande : BOPI « Brevets » n° 17 du 28 avril 1989.

(72) Inventeur(s) : Minoru Noda, Mitsubishi Denki Kabushiki Kaisha, LSI.

(60) Références à d'autres documents nationaux appartenus :

(73) Titulaire(s) :

(54) Transistor à effet de champ ayant une grille du type à barrière de Schottky.

(74) Mandataire(s) : Cabinet Plasseraud.

(57) Un dispositif à semiconducteur comprend un substrat semiconducteur 1, 2, une couche de grille 3b en un matériau réfractaire, formée sur le substrat semiconducteur, et une couche de métal à faible résistance 5 formée sur la couche de grille. Le procédé de fabrication permet de former la couche de métal à faible résistance 5 de façon auto-alignée sur la couche de matériau réfractaire 3b, ce qui procure une excellente maîtrise dimensionnelle dans le cas d'une grille de longueur inférieure au micron. L'invention permet ainsi de réduire la résistance de grille et d'obtenir un dispositif à semiconducteur présentant une bonne reproductibilité des caractéristiques en haute fréquence.

A1

FR 2 622 354

La présente invention concerne un dispositif à semiconducteur, et plus particulièrement un procédé de fabrication d'un transistor à effet de champ ayant une grille du type à barrière de Schottky.

Dans un transistor à effet de champ ayant une grille du type à barrière de Schottky (qu'on appellera ci-après "MESFET") utilisant une grille réfractaire, on forme une couche à faible résistance sur la grille réfractaire afin de réduire la résistance de grille, dans le but d'améliorer les propriétés du MESFET en haute fréquence.

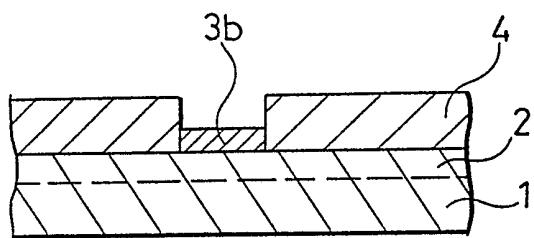

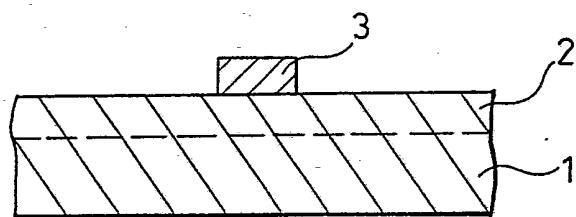

On décrira un procédé de fabrication de l'art antérieur pour ce type de structure de transistor à effet de champ, en se référant aux figures 3(a) à 3 (d).

Tout d'abord, comme le montre la figure 3(a), on forme une couche active 2 sur un substrat semiconducteur, par exemple un substrat en GaAs semi-isolant 1, et on dépose ensuite un matériau réfractaire sur le substrat en GaAs semi-isolant 1, de façon à produire une grille réfractaire 3. Ensuite, comme le montre la figure 3(b), on dépose une résine photosensible 4 sur la totalité de la surface du substrat, et on forme un motif de résine photosensible sur la grille réfractaire 3, par photolithographie. On dépose ensuite un métal à faible résistance 5' sur la totalité de la surface du substrat, comme représenté sur la figure 3(c), et on le décolle sélectivement avec le motif de résine ph-

tosensible 4, pour produire ainsi une couche de métal à faible résistance 5 sur la grille réfractaire 3 (figure 3(d)).

Cependant, dans ce procédé de fabrication de l'art antérieur, du fait qu'il faut aligner le motif de résine 5 photosensible 4 pour déposer un métal à faible résistance 5' après la fabrication de la grille réfractaire 3, il s'est avéré très difficile de fabriquer avec une grande maîtrise le motif de la couche de métal à faible résistance, 5, sur la grille réfractaire 3 ayant une longueur inférieure au 10 micron.

L'invention a pour but de procurer un procédé pour fabriquer un dispositif à semiconducteur, permettant de former avec une grande maîtrise une couche de métal à faible résistance sur une couche d'un matériau réfractaire d'une 15 longueur inférieure au micron.

Un autre but de l'invention est de procurer un dispositif à semiconducteur fabriqué par ce procédé.

Selon un aspect de l'invention, on fabrique un dispositif à semiconducteur en formant sur un substrat semiconducteur un motif d'électrode de grille ayant une structure à 20 deux couches qui comprend une couche de matériau réfractaire supérieure et une couche de matériau réfractaire inférieure, ayant chacune des propriétés d'attaque différentes, en déposant une couche de résine photosensible sur la totalité de 25 la surface du substrat, en attaquant la couche de résine photosensible pour mettre à nu la partie supérieure de la couche de matériau réfractaire supérieure, en enlevant la couche de matériau réfractaire supérieure, en déposant un métal à faible résistance sur toute la surface du substrat, et 30 en formant une couche de métal à faible résistance, de façon auto-alignée, sur la couche de matériau réfractaire inférieure. On améliore ainsi la maîtrise des caractéristiques géométriques de la couche de métal à faible résistance qui est formée sur une couche de matériau réfractaire d'une 35 longueur inférieure au micron.

Selon un autre aspect de l'invention, on fabrique un dispositif à semiconducteur en formant sur un substrat semiconducteur un motif d'électrode de grille ayant une structure à deux couches qui comprend une couche de matériau réfractaire supérieure et une couche de matériau réfractaire inférieure, ayant chacune des propriétés d'attaque différentes, en déposant une couche de résine photosensible sur toute la surface du substrat, en attaquant la couche de résine photosensible pour mettre à nu la partie supérieure de la couche de matériau réfractaire supérieure, en enlevant la couche de matériau réfractaire supérieure, en durcissant la surface de la couche de résine photosensible, en sur-développant la couche de résine photosensible et en déposant un métal à faible résistance sur toute la surface du substrat, et en enlevant le métal à faible résistance en même temps que la couche de résine photosensible, par un procédé de décollement, pour produire ainsi sur la couche de matériau réfractaire inférieure une couche de métal à faible résistance ayant une largeur supérieure à celle de la couche de matériau réfractaire inférieure. La résistance de grille est donc considérablement réduite.

L'invention sera mieux comprise à la lecture de la description qui va suivre de modes de réalisation, donnés à titre d'exemples non limitatifs. La suite de la description se réfère aux dessins annexés sur lesquels :

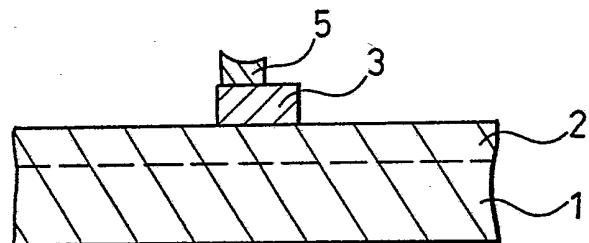

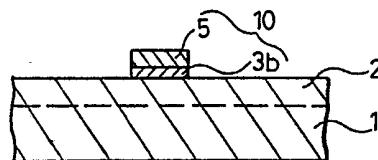

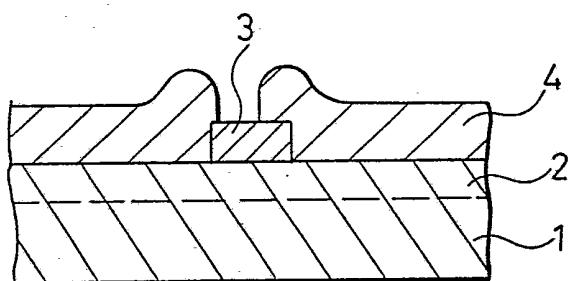

Les figures 1(a) à 1(f) sont des représentations en coupe d'un MESFET qui sont destinées à expliquer un procédé de fabrication d'un dispositif à semiconducteur conforme à un mode de réalisation de l'invention;

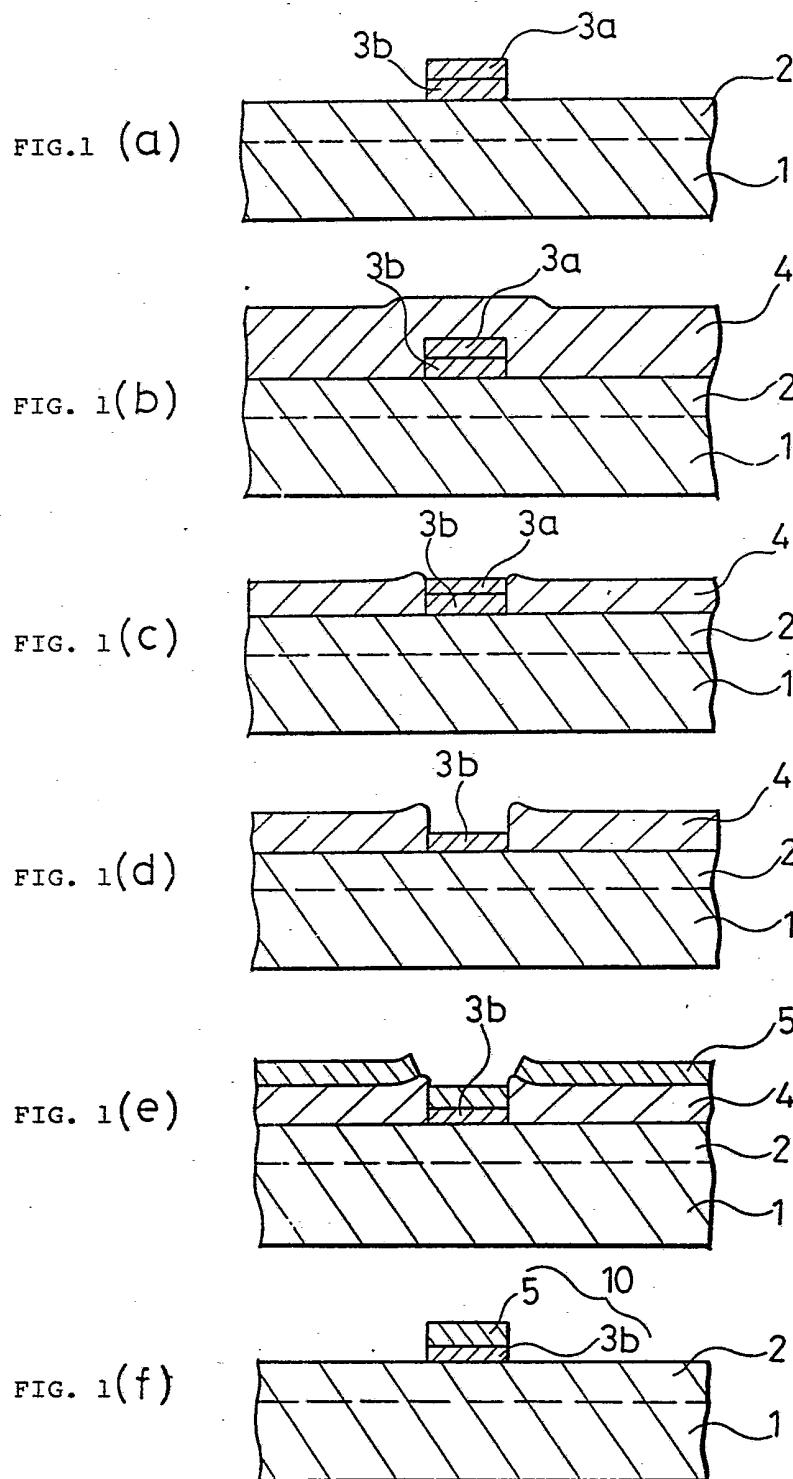

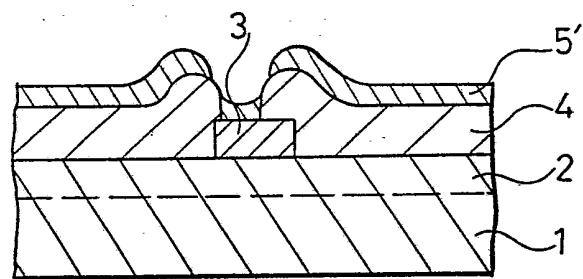

30 Les figures 2(a) à 2(e) sont des représentations en coupe d'un MESFET qui sont destinées à expliquer un procédé de fabrication d'un dispositif à semiconducteur conforme à un autre mode de réalisation de l'invention; et

35 Les figures 3(a) à 3(d) sont des représentations en coupe d'un MESFET qui sont destinées à expliquer un procédé

de fabrication d'un dispositif à semiconducteur conforme à l'art antérieur.

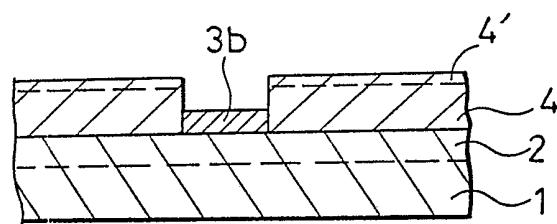

Les figures 1(a) à 1(f) sont des coupes d'un MESFET qui sont destinées à expliquer un processus de fabrication 5 d'un dispositif à semiconducteur conforme à un mode de réalisation de l'invention. Sur la figure 1, la référence 1 désigne un substrat en GaAs semi-isolant, la référence 2 désigne une couche active, et les références 3a et 3b désignent respectivement des couches de matériau réfractaire 10 supérieure et inférieure, qui consistent en un siliciure de métal réfractaire. La référence 4 désigne une couche de résine photosensible, la référence 5 désigne une couche de métal à faible résistance et la référence 10 désigne une électrode de grille.

15 Tout d'abord, comme le montre la figure 1(a), on forme une couche active 2 par implantation ionique de Si, dans des conditions correspondant à une énergie d'injection de plusieurs dizaines de keV et une dose de  $10^{12}$  à  $10^{13}$   $\text{cm}^{-2}$ , dans une région de surface du substrat en GaAs semi-20 isolant 1, ou par un procédé de croissance épitaxiale sur une surface du substrat en GaAs semi-isolant 1. On dépose ensuite une couche de matériau réfractaire inférieure 3b, consistant par exemple en siliciure de tungstène (WSi), avec une épaisseur de plusieurs centaines de nanomètres, ou moins, 25 sur la totalité de la surface du substrat en GaAs 1, par un procédé de pulvérisation cathodique ou un procédé de croissance épitaxiale. On dépose ensuite une couche de matériau réfractaire supérieure 3a, consistant par exemple en siliciure de titane-tungstène (TiWSi), avec une épaisseur d'une 30 centaine à plusieurs centaines de nanomètres, sur la totalité de la surface du substrat en GaAs 1, par un procédé de pulvérisation cathodique ou un procédé de croissance épitaxiale. Ensuite, on attaque et on traite verticalement les couches de matériau réfractaire supérieure et inférieure 3a 35 et 3b, en procédant par attaque ionique réactive ou par at-

taque par résonance cyclotron d'électrons, dans des conditions dans lesquelles ces couches sont attaquées approximativement à la même vitesse, pour produire ainsi un motif d'électrode de grille.

5       Ensuite, comme le montre la figure 1(b), on dépose par centrifugation une couche de résine photosensible à faible viscosité, sur la totalité de la surface du substrat en GaAs 1, de façon à recouvrir les couches de matériau réfractaire supérieure et inférieure 3a et 3b.

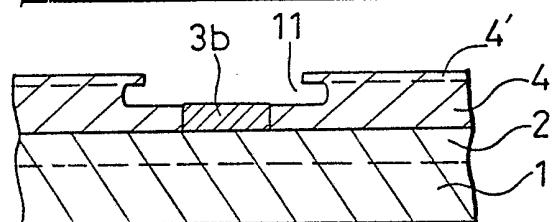

10      Ensuite, comme le montre la figure 1(c), on attaque la couche de résine photosensible 4 en utilisant des ions réactifs d'un mélange de gaz comprenant  $CF_4$  et  $O_2$ , pour mettre ainsi à nu la partie supérieure de la couche de matériau réfractaire supérieure 3a.

15      Ensuite, comme le montre la figure 1(d), on attaque sélectivement la couche de matériau réfractaire supérieure 3a qui a été mise à nu, avec une vitesse d'attaque plus élevée pour cette couche que pour la couche de matériau réfractaire inférieure 3b, en procédant par attaque ionique réactive ou par attaque par voie humide, de façon à laisser la couche de matériau réfractaire inférieure 3b.

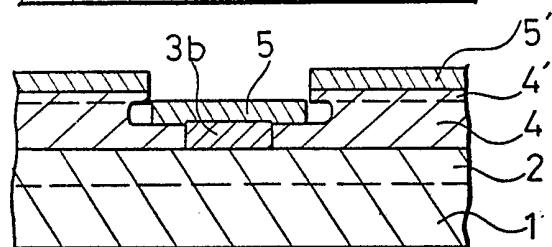

20      Ensuite, comme le montre la figure 1(e), on dépose en phase vapeur un métal à faible résistance 5', consistant par exemple en Ti/Au, de façon à lui donner une épaisseur inférieure à la différence entre l'épaisseur de la couche de résine photosensible 4 et celle de la couche de matériau réfractaire inférieure 3b.

25      Enfin, comme le montre la figure 1(f), on décolle la couche de métal à faible résistance 5' en compagnie de la couche de résine photosensible 4, ce qui produit une électrode de grille 10 ayant une structure à deux couches, dans laquelle une couche de métal à faible résistance 5 est formée de façon auto-alignée sur la couche de matériau réfractaire 3b.

30      35      Dans ce premier mode de réalisation, représenté sur

les figures 1(a) - 1(f), du fait que la couche de métal à faible résistance 5 est formée de façon auto-alignée sur la couche de matériau réfractaire inférieure 3b, on peut produire avec une excellente maîtrise un motif de grille de 5 taille inférieure ou micron, comprenant une couche de matériau réfractaire en tant que première couche (couche inférieure), et une couche de métal à faible résistance en tant que seconde couche (couche supérieure). En outre, du fait que la couche de métal à faible résistance 5 est formée sur 10 la couche de matériau réfractaire inférieure 3b, la résistance de grille est diminuée, et le facteur de bruit minimal qui était de 3 dB dans le dispositif de l'art antérieur, peut être réduit à 1 dB, tandis que le gain qui était de 5 dB dans le dispositif de l'art antérieur peut être augmenté 15 jusqu'à 12 à 13 dB, ce qui donne un MESFET ayant des caractéristiques en haute fréquence stables sur l'ensemble de tranches ou de lots de fabrication.

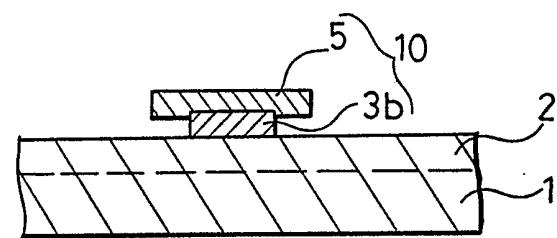

Les figures 2(a) à 2(e) sont des représentations en coupe d'un MESFET qui sont destinées à expliquer un processus de fabrication d'un dispositif à semiconducteur conforme à un autre mode de réalisation de l'invention. Sur les figures 2(a) à 2(e), les éléments identiques à ceux représentés sur les figures 1(a) - 1(f) sont désignés par les mêmes références numériques. La référence 4' désigne une partie 20 dure 25 cie de la couche de résine photosensible, et la référence 11 désigne une partie sur-développée de la couche de résine photosensible. Contrairement au premier mode de réalisation dans lequel une couche de métal à faible résistance, 5, est formée sur une couche de matériau réfractaire inférieure 3b, dans ce second mode de réalisation la couche de métal à faible résistance 5 est formée avec une largeur supérieure à celle de la couche de matériau réfractaire inférieure 3b.

Dans la fabrication de ce second mode de réalisation, on accomplit des opérations de fabrication identiques 30 à celles représentées sur les figures 1(a) à 1(d), jusqu'à

l'étape de la figure 2(a). Comme le montre la figure 2(b), on durcit la surface de la couche de résine photosensible 4 par une opération de recuit, ou par irradiation par des rayons ultraviolets, pour produire ainsi une partie de résine photosensible durcie, 4'.

Ensuite, comme le montre la figure 2(c), on sur-développe la couche de résine photosensible 4 à la partie supérieure de la couche de matériau réfractaire 3b, en employant une longue durée de développement, ce qui produit une partie de résine photosensible sur-développée, 11.

Ensuite, comme le montre la figure 2(d), on dépose en phase vapeur un métal à faible résistance 5', consistant par exemple en Ti/Au, de façon à avoir une épaisseur de couche inférieure à la différence entre l'épaisseur de la couche de résine photosensible 4 et celle de la couche de matériau réfractaire inférieure 3b.

Enfin, comme le montre la figure 2(e), on décolle le métal à faible résistance 5' en compagnie de la couche de résine photosensible 4, ce qui donne une électrode de grille ayant une structure double, qui comprend une couche de matériau réfractaire inférieure 3b et une couche de métal à faible résistance 5 formée sur la couche réfractaire, avec une configuration dans laquelle la couche de métal à faible résistance 5 a une largeur supérieure à celle de la couche de matériau réfractaire inférieure 3b.

Dans ce second mode de réalisation, outre le fait qu'on obtient les effets du premier mode de réalisation, on peut réduire encore davantage la résistance de grille, du fait que la couche de métal à faible résistance 5 est formée avec une largeur supérieure à celle de la grille, ce qui donne un dispositif à semiconducteur ayant d'excellentes caractéristiques en haute fréquence.

Bien qu'on ait décrit un procédé de fabrication de grille de MESFET dans les premier et second modes de réalisation considérés ci-dessus, on peut également appliquer

l'invention à un procédé de fabrication de grille de MISFET (MOSFET), en obtenant les mêmes effets que ci-dessus.

Bien que dans les premier et second modes de réalisation considérés ci-dessus, on utilise TiWSi pour la couche 5 de matériau réfractaire supérieure 3a et on utilise WSi pour la couche de matériau réfractaire inférieure 3b, on peut utiliser d'autres matériaux pour les couches supérieure et inférieure, à condition qu'ils diffèrent l'un de l'autre. On peut par exemple utiliser WNx ou W pour la couche supérieure.

10 Conformément à l'invention, et comme il ressort de façon évidente de la description précédente, on forme sur un substrat semiconducteur un motif d'électrode de grille à structure à deux couches, comprenant des couches de matériau réfractaire supérieure et inférieure, ayant chacune des propriétés d'attaque différentes, on dépose une couche de résine photosensible sur la totalité de la surface du substrat, on attaque cette couche de résine photosensible pour mettre à nu la partie supérieure de la couche de matériau réfractaire supérieure, on enlève la couche de matériau réfractaire supérieure, on dépose un métal à faible résistance sur la totalité de la surface du substrat, et on décolle sélectivement le métal à faible résistance en compagnie de la couche de résine photosensible, pour produire ainsi, de façon auto-alignée, une couche de métal à faible résistance sur la couche 25 de matériau réfractaire inférieure.

20 Selon un autre aspect de l'invention, on forme sur un substrat semiconducteur un motif d'électrode de grille ayant une structure à deux couches qui comprend des couches de matériau réfractaire supérieure et inférieure, ayant chacune des propriétés d'attaque différentes, on dépose une couche de résine photosensible sur la totalité de la surface du substrat, on attaque la couche de résine photosensible pour mettre à nu la partie supérieure de la couche de matériau réfractaire supérieure, on enlève la couche de matériau 30 réfractaire supérieure, on durcit la surface de la couche de

résine photosensible, on sur-développe la couche de résine photosensible et on dépose un métal à faible résistance sur la totalité de la surface du substrat, et on décolle sélectivement le métal à faible résistance, en compagnie de la 5 couche de résine photosensible, pour produire ainsi une couche de métal à faible résistance sur la couche de matériau réfractaire inférieure, cette couche de métal à faible résistance ayant une largeur supérieure à celle de la couche de matériau réfractaire inférieure. Il en résulte qu'on peut 10 obtenir avec une grande maîtrise un motif de grille de longueur inférieure au micron, on peut réduire la résistance de grille, et on peut fabriquer un dispositif à semiconducteur ayant des caractéristiques en haute fréquence qui sont stables.

15 Il va de soi que de nombreuses modifications peuvent être apportées au dispositif et au procédé décrits et représentés, sans sortir du cadre de l'invention.

REVENDICATIONS

1. Dispositif à semiconducteur caractérisé en ce qu'il comprend : un substrat semiconducteur (1, 2); une couche de grille (3b) consistant en un matériau réfractaire, 5 formée sur la surface du substrat semiconducteur (1, 2); et une couche de métal à faible résistance (5), formée sur la couche de grille (3b).

2. Dispositif à semiconducteur selon la revendication 1, caractérisé en ce que la couche de métal à faible 10 résistance (5) est formée avec une longueur égale à celle de la couche de grille (3b).

3. Dispositif à semiconducteur selon la revendication 1, caractérisé en ce que la couche de métal à faible résistance (5) est formée avec une longueur supérieure à 15 celle de la couche de grille (3b).

4. Dispositif à semiconducteur selon la revendication 1, caractérisé en ce que la couche de métal à faible résistance (5) consiste en une couche de Ti/Au.

5. Dispositif à semiconducteur selon la revendication 1, caractérisé en ce que le substrat semiconducteur 20 (1, 2) est un substrat en GaAs semi-isolant.

6. Dispositif à semiconducteur selon la revendication 1, caractérisé en ce que la couche de matériau réfractaire (3b) consiste en un siliciure de métal réfractaire.

25 7. Dispositif à semiconducteur selon la revendication 6, caractérisé en ce que la couche de matériau réfractaire (3b) consiste en siliciure de tungstène.

8. Dispositif à semiconducteur selon la revendication 1, caractérisé en ce que le substrat semiconducteur 30 (1) comporte une couche active (2) à sa surface.

9. Procédé de fabrication d'un dispositif à semiconducteur, caractérisé en ce qu'il comprend : une première opération pour produire un motif d'électrode de grille ayant une structure à deux couches (3a, 3b) sur un substrat semi-conducteur (1, 2), ce motif d'électrode de grille comprenant 35

une première couche de matériau réfractaire, ou couche inférieure (3b), et une seconde couche de matériau réfractaire, ou couche supérieure (3a), ayant respectivement des propriétés d'attaque différentes; une seconde opération consistant 5 à déposer une couche de résine photosensible (4) sur la totalité de la surface du substrat (1, 2), et à attaquer cette couche pour mettre à nu la partie supérieure de la seconde couche de matériau réfractaire supérieure (3a); et une troisième opération pour enlever la seconde couche de matériau 10 réfractaire supérieure (3a) et pour déposer un métal à faible résistance (5') sur la totalité de la surface du substrat (1, 2) et enlever le métal à faible résistance (5') en compagnie de la couche de résine photosensible (4), par un procédé de décollement, de façon à produire une électrode de 15 grille (10) qui comprend la première couche de matériau réfractaire inférieure (3b) et une couche de métal à faible résistance (5) qui est formée de façon auto-alignée sur la première couche de matériau réfractaire inférieure.

10. Procédé de fabrication d'un dispositif à semi-conducteur selon la revendication 9, caractérisé en ce que la première opération pour produire le motif d'électrode de grille (3a, 3b) ayant la structure à deux couches, comprend les étapes suivantes : on forme la première couche de matériau réfractaire inférieure (3b) et la seconde couche de 20 matériau réfractaire supérieure (3a) sur le substrat semi-conducteur (1, 2), par un procédé de pulvérisation cathodique ou un procédé de croissance épitaxiale; et on attaque approximativement à la même vitesse les première et seconde couches de matériau réfractaire inférieure et supérieure 25 30 (3b, 3a).

11. Procédé de fabrication d'un dispositif à semi-conducteur selon la revendication 9, caractérisé en ce que la première couche de matériau réfractaire inférieure (3b) consiste en siliciure de tungstène, et la seconde couche de 35 matériau réfractaire supérieure (3a) consiste en siliciure

de tungstène-titane.

12. Procédé de fabrication d'un dispositif à semi-conducteur selon la revendication 10, caractérisé en ce que la première couche de matériau réfractaire inférieure (3b) 5 consiste en siliciure de tungstène, et la seconde couche de matériau réfractaire supérieure (3a) consiste en siliciure de tungstène-titane.

13. Procédé de fabrication d'un dispositif à semi-conducteur selon la revendication 9, caractérisé en ce qu'on 10 effectue l'attaque de la couche de résine photosensible (4) dans la seconde opération, par attaque ionique réactive en utilisant un mélange gazeux de  $CF_4$  et  $O_2$ .

14. Procédé de fabrication d'un dispositif à semi-conducteur, caractérisé en ce qu'il comprend les opérations 15 suivantes : une première opération pour produire un motif d'électrode de grille (3a, 3b) ayant une structure à deux couches sur un substrat semi-conducteur (1, 2), ce motif d'électrode de grille comprenant une première couche de matériau réfractaire, ou couche inférieure (3b), et une seconde couche de matériau réfractaire, ou couche supérieure (3a), ayant chacune des propriétés d'attaque différentes; une seconde opération pour déposer une couche de résine photosensible (4) sur la totalité de la surface du substrat (1, 2), et pour attaquer cette dernière de façon à mettre à 25 nu la partie supérieure de la seconde couche de matériau réfractaire supérieure (3a); une troisième opération pour enlever la seconde couche de matériau réfractaire supérieure (3a); une quatrième opération pour durcir la surface (4') de la résine photosensible (4), et pour effectuer un sur-développement de la résine photosensible; et une cinquième opération pour déposer un métal à faible résistance (5') sur la totalité de la surface du substrat (1, 2), et pour enlever le métal à faible résistance (5') en compagnie de la 30 couche de résine photosensible (4), par un procédé de décollement, pour produire ainsi une électrode de grille qui com-

prend la première couche de matériau réfractaire inférieure (3b) et une couche de métal à faible résistance (5) qui est formée sur cette dernière, avec une configuration dans laquelle la couche de métal à faible résistance (5) a une largeur supérieure à celle de la première couche de matériau réfractaire inférieure (3b).

15. Procédé de fabrication d'un dispositif à semi-conducteur selon la revendication 14, caractérisé en ce que la première opération pour produire le motif d'électrode de grille (3a, 3b) à structure à deux couches, comprend les opérations suivantes : on forme sur le substrat semiconducteur (1, 2) une première couche de matériau réfractaire, ou couche inférieure (3b), et une seconde couche de matériau réfractaire, ou couche supérieure (3a), par un procédé de pulvérisation cathodique ou un procédé de croissance épitaxiale; et on attaque approximativement avec la même vitesse d'attaque les première et seconde couches de matériau réfractaire inférieure et supérieure (3b, 3a).

16. Procédé de fabrication d'un dispositif à semi-conducteur selon la revendication 14, caractérisé en ce que la première couche de matériau réfractaire inférieure (3b) consiste en siliciure de tungstène, et la seconde couche de matériau réfractaire supérieure (3a) consiste en siliciure de tungstène-titane.

25 17. Procédé de fabrication d'un dispositif à semi-conducteur selon la revendication 15, caractérisé en ce que la première couche de matériau réfractaire inférieure (3b) consiste en siliciure de tungstène, et la seconde couche de matériau réfractaire supérieure (3a) consiste en siliciure de tungstène-titane.

18. Procédé de fabrication d'un dispositif à semi-conducteur selon la revendication 14, caractérisé en ce que l'attaque de la couche de résine photosensible (4) dans la seconde opération est effectuée par attaque ionique réactive 35 en utilisant un mélange gazeux de  $CF_4$  et  $O_2$ .

19. Procédé de fabrication d'un dispositif à semi-conducteur selon la revendication 14, caractérisé en ce que le durcissement de la résine photosensible (4) dans la quatrième opération est effectué par recuit.

5 20. Procédé de fabrication d'un dispositif à semi-conducteur selon la revendication 14, caractérisé en ce que le durcissement de la résine photosensible (4) dans la quatrième opération est effectué par irradiation avec des rayons ultraviolets.

FIG. 2 (a)

FIG. 2 (b)

FIG. 2 (c)

FIG. 2 (d)

FIG. 2 (e)

(ART ANTERIEUR)

FIG. 3 (a)

FIG. 3 (b)

FIG. 3 (c)

FIG. 3 (d)