(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-333107

(P2005-333107A)

(43) 公開日 平成17年12月2日(2005.12.2)

(51) Int.Cl.<sup>7</sup>

H01L 21/336

H01L 21/8234

H01L 21/8238

H01L 27/08

H01L 27/088

F 1

H01L 29/78

H01L 27/08

H01L 27/08

H01L 27/08

H01L 29/78

テーマコード(参考)

5FO48

5F110

審査請求 未請求 請求項の数 30 O L (全 51 頁) 最終頁に続く

(21) 出願番号 特願2005-37949 (P2005-37949)

(22) 出願日 平成17年2月15日 (2005.2.15)

(31) 優先権主張番号 特願2004-125489 (P2004-125489)

(32) 優先日 平成16年4月21日 (2004.4.21)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目2番3号

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100098316

弁理士 野田 久登

(74) 代理人 100109162

弁理士 酒井 将行

最終頁に続く

(54) 【発明の名称】半導体装置、画像表示装置および半導体装置の製造方法

## (57) 【要約】

【課題】 ソース・ドレイン耐圧およびACストレス耐性的の向上が図られ、所望の電流特性の得られる半導体装置と、その製造方法を提供する。

【解決手段】 ガラス基板1上にシリコン窒化膜2およびシリコン酸化膜3が形成されている。そのシリコン酸化膜3上に、ソース領域45、ドレイン領域46、所定のチャネル長を有するチャネル領域40、ソース領域よりもそれぞれ低い不純物濃度を有するGOLD領域41とLDD領域43、ドレイン領域よりもそれぞれ低い不純物濃度を有するGOLD領域42とLDD領域44、ゲート絶縁膜5およびゲート電極6aを含む薄膜トランジスタTが形成されている。ゲート電極6aはチャネル領域40とGOLD領域41, 42と対向するようにオーバラップしている。

【選択図】 図1

## 【特許請求の範囲】

## 【請求項 1】

半導体層、絶縁膜および電極を有して所定の基板上に形成された半導体素子を含む半導体装置であって、

前記半導体素子は、

前記半導体層に形成された第1不純物領域と、

前記第1不純物領域と距離を隔てて前記半導体層に形成された第2不純物領域と、

前記第1不純物領域と前記第2不純物領域との間に位置する前記半導体層の部分に前記第1不純物領域および前記第2不純物領域とそれぞれ距離を隔てて形成され、所定のチャネル長を有するチャネルとなるチャネル領域と、

前記第1不純物領域と前記チャネル領域との間に位置する前記半導体層の部分に前記チャネル領域と接するように形成された第3不純物領域と、

前記第2不純物領域と前記チャネル領域との間に位置する前記半導体層の部分に前記チャネル領域に接するように形成された第4不純物領域と、

前記第1不純物領域と前記第3不純物領域との間に位置する前記半導体層の部分に形成された第5不純物領域と、

前記第2不純物領域と前記第4不純物領域との間に位置する前記半導体層の部分に形成された第6不純物領域と

を有する第1素子を備え、

前記第1素子では、

前記電極は互いに対向する一方側部および他方側部を有し、

前記第3不純物領域と前記第5不純物領域との接合部および前記一方側部は略同一平面上に位置するとともに、前記第4不純物領域と前記第6不純物領域との接合部および前記他方側部は同一平面上に位置し、

前記電極は、前記チャネル領域、前記第3不純物領域および前記第4不純物領域のそれぞれの全体と対向してオーバラップするように形成され、

前記絶縁膜は前記半導体層と前記電極とにそれぞれ接するように前記半導体層と前記電極との間に形成され、

前記第3不純物領域～前記第6不純物領域のそれぞれの不純物濃度は、前記第1不純物領域および前記第2不純物領域のそれぞれの不純物濃度よりも低く、前記チャネル領域の不純物濃度よりも高く設定され、

前記第3不純物領域および前記第4不純物領域の不純物濃度と前記第5不純物領域および前記第6不純物領域の不純物濃度とは異なるように設定された、半導体装置。

## 【請求項 2】

前記第3不純物領域および前記第4不純物領域の不純物濃度は、前記第5不純物領域および前記第6不純物領域の不純物濃度より低く設定された、請求項1記載の半導体装置。

## 【請求項 3】

前記第3不純物領域および前記第4不純物領域の不純物濃度は、前記第5不純物領域および前記第6不純物領域の不純物濃度より高く設定された、請求項1記載の半導体装置。

## 【請求項 4】

前記第1素子はn型およびp型の少なくともいずれかの薄膜トランジスタである、請求項1～3のいずれかに記載の半導体装置。

## 【請求項 5】

前記第3不純物領域および前記第4不純物領域の不純物濃度は、 $1 \times 10^{17}$  atom/cm<sup>3</sup>以上 $1 \times 10^{19}$  atom/cm<sup>3</sup>以下である、請求項1～4のいずれかに記載の半導体装置。

## 【請求項 6】

前記第5不純物領域および前記第6不純物領域の不純物濃度は、 $5 \times 10^{19}$  atom/cm<sup>3</sup>以下である、請求項1～4のいずれかに記載の半導体装置。

## 【請求項 7】

10

20

30

40

50

前記第3不純物領域および前記第4不純物領域のチャネル長方向の長さは、0.5μm以上2μm以下である、請求項1～6のいずれかに記載の半導体装置。

【請求項8】

前記第5不純物領域および前記第6不純物領域のチャネル長方向の長さは、0.5μm以上1.5μm以下である、請求項1～6のいずれかに記載の半導体装置。

【請求項9】

前記第5不純物領域のチャネル長方向の長さと前記第6不純物領域のチャネル長方向の長さとの差は0.3μm以下である、請求項1～6のいずれかに記載の半導体装置。

【請求項10】

前記第1素子は、前記電極、前記第1不純物領域～前記第6不純物領域を複数備え、

複数の前記電極のそれぞれはチャネル長方向に間隔を隔てて配設された、請求項1～9のいずれかに記載の半導体装置。

【請求項11】

前記半導体素子は複数形成され、

前記半導体素子は、

前記半導体層に形成された第7不純物領域と、

前記第7不純物領域と距離を隔てて前記半導体層に形成された第8不純物領域と、

前記第7不純物領域と前記第8不純物領域との間に位置する前記半導体層の部分に前記第7不純物領域および前記第8不純物領域とそれ距離を隔てて形成され、所定のチャネル長を有するチャネルとなるチャネル領域と、

前記第7不純物領域と前記チャネル領域との間に位置する前記半導体層の部分に前記チャネル領域と接するように形成された第9不純物領域と、

前記第8不純物領域と前記チャネル領域との間に位置する前記半導体層の部分に前記チャネル領域に接するように形成された第10不純物領域と

を有する第2素子を備え、

前記第2素子では、

前記電極は互いに対向する一方側部および他方側部を有し、

前記チャネル領域と前記第9不純物領域との接合部および前記一方側部は略同一平面上に位置するとともに、前記チャネル領域と前記第10不純物領域との接合部および前記他方側部は同一平面上に位置し、

前記電極は、前記チャネル領域の全体と対向してオーバラップするように形成され、

前記絶縁膜は前記半導体層と前記電極とにそれぞれ接するように前記半導体層と前記電極との間に形成され、

前記第9不純物領域および前記第10不純物領域のそれぞれの不純物濃度は、前記第7不純物領域および前記第8不純物領域のそれぞれの不純物濃度よりも低く、前記チャネル領域の不純物濃度よりも高く設定された、請求項1～10のいずれかに記載の半導体装置。

。

【請求項12】

前記第2素子はn型およびp型の少なくともいずれかの薄膜トランジスタである、請求項11記載の半導体装置。

【請求項13】

前記第2素子は複数の前記電極を有する、請求項11または12記載の半導体装置。

【請求項14】

所定の前記基板はガラス基板および石英基板のいずれかである、請求項1～13のいずれかに記載の半導体装置。

【請求項15】

前記半導体層は多結晶シリコンである、請求項1～14のいずれかに記載の半導体装置。

。

【請求項16】

前記ゲート電極は単層である、請求項1～15のいずれかに記載の半導体装置。

## 【請求項 17】

画像を表示するための画像表示回路部を備えた画像表示装置であって、

前記画像表示回路部は、半導体装置、絶縁膜および電極を有して所定の基板上に形成された半導体素子を有し、

前記半導体素子は、

前記半導体層に形成された第1不純物領域、

前記第1不純物領域と距離を隔てて前記半導体層に形成された第2不純物領域、

前記第1不純物領域と前記第2不純物領域との間に位置する前記半導体層の部分に前記第1不純物領域および前記第2不純物領域とそれぞれ距離を隔てて形成され、所定のチャネル長を有するチャネルとなるチャネル領域、

前記第1不純物領域と前記チャネル領域との間に位置する前記半導体層の部分に前記チャネル領域と接するように形成された第3不純物領域、

前記第2不純物領域と前記チャネル領域との間に位置する前記半導体層の部分に前記チャネル領域に接するように形成された第4不純物領域、

前記第1不純物領域と前記第3不純物領域との間に位置する前記半導体層の部分に形成された第5不純物領域および

前記第2不純物領域と前記第4不純物領域との間に位置する前記半導体層の部分に形成された第6不純物領域

を有する第1素子と、

前記半導体層に形成された第7不純物領域、

前記第7不純物領域と距離を隔てて前記半導体層に形成された第8不純物領域、

前記第7不純物領域と前記第8不純物領域との間に位置する前記半導体層の部分に前記第7不純物領域および前記第8不純物領域とそれぞれ距離を隔てて形成され、所定のチャネル長を有するチャネルとなるチャネル領域、

前記第7不純物領域と前記チャネル領域との間に位置する前記半導体層の部分に前記チャネル領域と接するように形成された第9不純物領域および

前記第8不純物領域と前記チャネル領域との間に位置する前記半導体層の部分に前記チャネル領域に接するように形成された第10不純物領域

を有する第2素子と

を備え、

前記第1素子では、

前記電極は互いに対向する一方側部および他方側部を有し、

前記第3不純物領域と前記第5不純物領域との接合部および前記一方側部は略同一平面上に位置するとともに、前記第4不純物領域と前記第6不純物領域との接合部および前記他方側部は同一平面上に位置し、

前記電極は、前記チャネル領域、前記第3不純物領域および前記第4不純物領域のそれぞれの全体と対向してオーバラップするように形成され、

前記絶縁膜は前記半導体層と前記電極とにそれぞれ接するように前記半導体層と前記電極との間に形成され、

前記第3不純物領域～前記第6不純物領域のそれぞれの不純物濃度は、前記第1不純物領域および前記第2不純物領域のそれぞれの不純物濃度よりも低く、前記チャネル領域の不純物濃度よりも高く設定され、

前記第3不純物領域および前記第4不純物領域の不純物濃度と前記第5不純物領域および前記第6不純物領域の不純物濃度とは異なるように設定され、

前記第2素子では、

前記電極は互いに対向する一方側部および他方側部を有し、

前記チャネル領域と前記第9不純物領域との接合部および前記一方側部は略同一平面上に位置するとともに、前記チャネル領域と前記第10不純物領域との接合部および前記他方側部は同一平面上に位置し、

前記電極は、前記チャネル領域の全体と対向してオーバラップするように形成され、

10

20

30

40

50

前記絶縁膜は前記半導体層と前記電極とにそれぞれ接するように前記半導体層と前記電極との間に形成され、

前記第9不純物領域および前記第10不純物領域のそれぞれの不純物濃度は、前記第7不純物領域および前記第8不純物領域のそれぞれの不純物濃度よりも低く、前記チャネル領域の不純物濃度よりも高く設定された、画像表示回路部を備えた画像表示装置。

【請求項18】

前記第1素子および前記第2素子は、p型およびn型の少なくともいずれかの薄膜トランジスタである、請求項17記載の画像表示回路部を備えた画像表示装置。

【請求項19】

前記画像表示回路部は、

複数の画素から構成され画像を表示するための画素部と、

前記画素部を動作させるための駆動回路部と

を含み、

前記画素部および前記駆動回路部のいずれかに前記第1素子が適用された、請求項17または18に記載の画像表示回路部を備えた画像表示装置。

【請求項20】

前記画素部の複数の前記画素のそれぞれに前記第1素子が適用され、

前記第1素子は複数の前記電極を有する、請求項19記載の画像表示回路部を備えた画像表示装置。

【請求項21】

前記駆動回路部は、

前記画素部と接続され、前記画素部の前記画素のそれぞれに画像信号の電圧を昇圧して送るための昇圧回路部を有する走査線駆動回路部と、

前記画素部と接続され、前記画素部の前記画素のそれぞれに走査信号を送るためのスイッチング回路部を有するデータ線駆動回路部と

を含み、

前記スイッチング回路部および前記昇圧回路部の少なくともいずれかに前記第1素子が適用された、請求項19記載の画像表示回路部を備えた画像表示装置。

【請求項22】

前記駆動回路部は前記第2素子が適用された所定の回路部を含む、請求項21記載の画像表示回路部を備えた画像表示装置。

【請求項23】

前記画素部に前記第2素子が適用された、請求項19記載の画像表示回路部を備えた画像表示装置。

【請求項24】

前記第2素子は複数の前記電極を有する、請求項23記載の画像表示回路部を備えた画像表示装置。

【請求項25】

所定の前記基板はガラス基板および石英基板のいずれかである、請求項17～24のいずれかに記載の画像表示回路部を備えた画像表示装置。

【請求項26】

前記半導体層は多結晶シリコンである、請求項17～25のいずれかに記載の画像表示回路部を備えた画像表示装置。

【請求項27】

前記ゲート電極は単層である、請求項17～26のいずれかに記載の画像表示回路部を備えた画像表示装置。

【請求項28】

主表面を有する基板上に第1電極を形成する工程と、

前記基板上に所定の第1半導体層を形成する工程と、

前記第1電極を形成する工程と前記第1半導体層を形成する工程との間に前記基板上に

10

20

30

40

50

絶縁膜を形成する工程と、

前記第1半導体層を横切るように第1の部分を含む第1のマスク材を前記第1半導体層上に形成する工程と、

前記第1のマスク材をマスクとして前記第1半導体層に所定導電型の不純物イオンを導入することにより、前記第1のマスク材の直下に位置する前記第1半導体層の部分をチャネル領域とし、前記第1のマスク材を挟んで一方と他方との側に位置する前記第1半導体層の部分に前記チャネル領域に接するように所定の不純物濃度を有する1対の第1不純物領域を形成する第1注入工程と、

前記チャネル領域の全体および1対の前記第1不純物領域のそれぞれの部分を覆う第1の部分を含む第2のマスク材を前記第1半導体層上に形成する工程と、

前記第2のマスク材をマスクとして、前記第1半導体層に所定導電型の不純物イオンを導入することにより、前記チャネル領域を挟んで一方の側と他方の側に位置する前記第1半導体層の部分に前記チャネル領域とはそれぞれ所定の距離を隔てて前記第1不純物領域の不純物濃度よりも高い不純物濃度を有する1対の第2不純物領域を形成する第2注入工程と、

前記チャネル領域の全体および1対の前記第1不純物領域のそれぞれ部分を覆う第1の部分を含む第3のマスク材を前記第1半導体層上に形成する工程と、

前記第3のマスク材をマスクとして、前記第1半導体層に所定導電型の不純物イオンを導入することにより、前記チャネル領域を挟んで一方の側と他方の側に位置する前記第1半導体層の部分に前記チャネル領域とはそれぞれ前記所定の距離よりも短い距離を隔てて前記第2不純物領域の不純物濃度よりも低い不純物濃度を有する1対の第3不純物領域を形成する第3注入工程と、

を備え、

前記第1電極を形成する工程および前記第1不純物領域を形成する工程では、前記チャネル領域および1対の前記第1不純物領域のそれぞれの全体と前記第1電極とがオーバラップして対向するように形成される、半導体装置の製造方法。

#### 【請求項29】

前記基板上に第2電極および第3電極を形成する工程と、

前記基板上に第2半導体層および第3半導体層を形成する工程と、

前記第3半導体層を横切る部分を含むように第4のマスク材を形成する工程と、

前記第4のマスク材をマスクとして前記第3半導体層に所定導電型の不純物イオンを導入することにより、前記第4のマスク材の前記部分の直下に位置する前記第1半導体層の部分をチャネル領域とし、前記第4のマスク材を挟んで一方と他方との側に位置する前記第3半導体層の部分に前記チャネル領域に接するように所定の不純物濃度を有する1対の第6不純物領域を形成する第4注入工程と

をさらに備え、

前記第1のマスク部材を形成する工程では、前記第2半導体層の全体を覆う第2の部分および前記第3半導体層の全体を覆う第3の部分を形成する工程を含み、

前記第2のマスク材を形成する工程では、前記第2半導体層を横切る第2の部分を形成する工程を含み、

前記第2注入工程では、前記第2の部分の直下に位置する前記第2半導体層の部分をチャネル領域とし、前記第2の部分を挟んで一方と他方との側に位置する前記第2半導体層の部分に間隔を隔てて所定の不純物濃度を有する1対の第4不純物領域を形成する工程を含み、

前記第3のマスク部材を形成する工程では、前記第2半導体層の1対の前記第4不純物領域によって挟まれた前記第2半導体層の部分を覆う第2の部分を形成する工程を含み、

前記第3注入工程では、前記第2の部分の直下に位置する前記第2半導体層の部分をチャネル領域とし、前記第2の部分を挟んで一方と他方との側に位置する前記第2半導体層の部分に前記第4不純物領域よりも不純物濃度の低い1対の第5不純物領域を形成する工程を含む、請求項28記載の半導体装置の製造方法。

10

20

30

40

50

## 【請求項 30】

前記第1半導体層を形成する工程と前記第2半導体層および前記第3半導体層を形成する工程とは同時に行なわれ、

前記第1半導体層、前記第2半導体層および前記第3半導体層を形成した後に、前記第1半導体層、前記第2半導体層および前記第3半導体層を覆うように前記絶縁膜を形成する工程が行なわれ、

前記第1のマスク材を形成する工程は、前記第1の部分、前記第2の部分および前記第3の部分として前記絶縁膜上にそれぞれ所定のレジストパターンを形成する工程を含み、

前記第1注入工程の後に、前記絶縁膜上に導電層を形成する工程が行なわれ、

前記導電層を形成する工程の後に、前記第1電極、前記第2電極および前記第3電極をそれぞれ形成する工程が行なわれ、

前記第1電極を形成する工程は、

前記導電層上に前記第1電極をパターニングするための第1のレジストパターンを形成する工程と、

前記第1のレジストパターンをマスクとして前記導電層にエッチングを施すとともに、露出する前記導電層の側部を側方からエッチングを施して前記第1のレジストパターンの寸法よりも短い寸法の前記第1電極を形成する工程と

を含み、

前記第2電極を形成する工程は、

前記導電層上に前記第2電極をパターニングするための第2のレジストパターンを形成する工程と、

前記第2のレジストパターンをマスクとして前記導電層にエッチングを施すとともに、露出する前記導電層の側部を側方からエッチングを施して前記第2のレジストパターンの寸法よりも短い寸法の前記第2電極を形成する工程と

を含み、

前記第3電極を形成する工程は、

前記導電層上に前記第3電極をパターニングするための第3のレジストパターンを形成する工程と、

前記第3のレジストパターンをマスクとしてエッチングを施すことで前記第3電極を形成する工程と

を含み、

前記第2のマスク材を形成する工程では、前記第1の部分として前記第1のレジストパターンを形成し、前記第2の部分として前記第2のレジストパターンを形成する工程を含み、

前記第3のマスク材を形成する工程では、前記第1の部分として前記第1電極を形成し、前記第2の部分として前記第2電極を形成する工程を含み、

前記第4のマスク材を形成する工程では、前記部分として前記第3電極を形成する工程を含む、請求項29記載の半導体装置の製造方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は半導体装置、画像表示装置および半導体装置の製造方法に関し、特に、液晶表示デバイスや有機EL(Electro Luminescence)表示デバイスなどの表示デバイスに適用される半導体装置と、画像表示回路部を備えた画像表示装置と、そのような半導体装置の製造方法に関するものである。

## 【背景技術】

## 【0002】

表示デバイスには薄膜トランジスタが使用されている。そのような薄膜トランジスタの一例として、特許文献1に記載されたGOLD(Gate Overlapped Lightly Doped Drain)構造の薄膜トランジスタについて説明する。GOLD構造のn型薄膜トランジスタは、

10

20

30

40

50

ソース領域、ドレイン領域、チャネル領域、G O L D 領域、ゲート絶縁膜およびゲート電極等を有してガラス基板上に形成される。

#### 【 0 0 0 3 】

G O L D 領域は、チャネル領域とドレイン領域との間の領域において、特に、ゲート電極の直下に位置する領域に形成されて、ゲート電極と平面的にオーバラップしている。そのG O L D 領域はチャネル領域における不純物濃度よりも高く、ドレイン領域における不純物濃度よりも低い不純物濃度に設定されている。

#### 【 0 0 0 4 】

次に、そのG O L D 構造のたとえばn型薄膜トランジスタの動作について説明する。ゲートに所定の正電圧を印加するとチャネル領域にチャネルが形成されて、ソース領域とドレイン領域との間の抵抗が小さくなり、ソース領域とドレイン領域との間に電流を流すことができる状態となる。

#### 【 0 0 0 5 】

一方、ゲートに負電圧を印加するとチャネル領域にチャネルは形成されないため、ソース領域とドレイン領域との間の抵抗が大きくなってしまい、ソース領域とドレイン領域との間に実質的な電流を流すことはできなくなり、微小なリーク電流が流れるだけの状態となる。

#### 【 0 0 0 6 】

このリーク電流は、チャネルに形成されたホールと、ソース領域およびドレイン領域において多数存在する電子とが接合部において再結合することによるものである。接合部の電界が高くなると再結合の確率が高くなるため、リーク電流は増加することになる。

#### 【 0 0 0 7 】

表示デバイスでは、画面を書き換えるまでの1フレームの時間中、液晶に印加された電圧を保持する必要がある。このとき、その電圧保持のために使用される画素トランジスタにおいてリーク電流が多い場合には、液晶に印加された電圧が時間とともに下降して表示特性を劣化させることになる。そのため、画素トランジスタにはリーク電流が極めて低いことが要求される。

#### 【 0 0 0 8 】

次に、表示デバイスに使用される薄膜トランジスタの他の例として、特許文献2に記載されたL D D (Lightly Doped Drain)構造の薄膜トランジスタについて説明する。L D D構造のn型薄膜トランジスタは、ソース領域、ドレイン領域、チャネル領域、L D D領域、ゲート絶縁膜およびゲート電極等を有してガラス基板上に形成される。

#### 【 0 0 0 9 】

L D D領域はチャネル領域とドレイン領域との間の領域に形成されている。また、L D D領域は、チャネル領域の不純物濃度よりも高くドレイン領域の不純物濃度よりも低い不純物濃度に設定されている。

#### 【 0 0 1 0 】

L D D構造の薄膜トランジスタでは、ゲート電圧として負電圧が印加されるとチャネル領域には蓄積層が形成されることになるが、L D D領域によってソース・ドレイン近傍の電界が緩和されて、リーク電流を抑制することができる。

#### 【特許文献1】特開2002-76351号公報

#### 【特許文献2】特開2001-345448号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【 0 0 1 1 】

しかしながら、従来の薄膜トランジスタでは次のような問題点があった。上述したように、画素トランジスタとして使用される薄膜トランジスタにはリーク電流が極めて低いことが要求される。薄膜トランジスタの一例のG O L D構造の薄膜トランジスタでは、ゲート電圧として負電圧が印加されるとG O L D領域に蓄積層が形成され、G O L D領域よりも高い不純物濃度を有するソース領域・ドレイン領域近傍に高い電界が生じてしまう。そのため、リーク電流を抑制することができず、薄膜トランジスタにおけるO F F電流の特

性に影響を与えていた。

#### 【0012】

また、ゲートに比べてドレインにより高い電圧を印加することによって、ドレイン側の接合部分に比較的大きな電界が生じる。この電界により加速された電子がインパクトイオン化現象を引き起こして、電子と正孔の対が生成される。この現象が繰り返されて電子と正孔の対が増大しドレイン電流が増加して、アバランシェ破壊に至ることになる。このときのドレイン電圧がソース・ドレイン耐圧となる。

#### 【0013】

上述したGOLD構造の薄膜トランジスタではドレイン領域近傍の電界はチャネル領域とGOLD領域との接合部において緩和されるため、インパクトイオン化現象をある程度抑制することができる。しかしながら、実用レベルでのGOLD領域の長さ(GOLD長)では、十分なソース・ドレイン耐圧が得られていないという問題があった。

#### 【0014】

また、ゲートに正負のAC(Alternating Current)パルスを印加すると、薄膜トランジスタの特性劣化が観察される。このようなACストレスに対する信頼性は多結晶を用いた薄膜トランジスタに特有の現象である。この現象は次のように説明される。ゲートに負電圧を印加すると、ゲートとソース・ドレイン間の接合部に大きな電界が生じ、また、多結晶の粒界などに捕獲されていたキャリアが徐々に放出される。放出されたキャリアは接合部における強い電界によって加速されてインパクトイオン化現象を引き起こす。

#### 【0015】

インパクトイオン化によって生成した電子・正孔対は極めて高いエネルギーを有するため、ゲート酸化膜・半導体間のエネルギー障壁を超えて酸化膜中に入ることがある。このような高いエネルギーを持つ電子・正孔対はホットキャリアと呼ばれ、酸化膜中に入って固定電荷を形成したり、界面などに欠陥を生成して移動度を劣化させ、トランジスタの特性を劣化させることになる。

#### 【0016】

従来のGOLD構造の薄膜トランジスタではドレイン領域近傍の電界はチャネル領域とGOLD領域の接合部で緩和されるため、ホットキャリアの発生をある程度抑制することはできた。しかし、実用レベルでのGOLD長では、ACストレスに対する信頼性は低く十分なホットキャリア耐性を得ることができないという問題があった。

#### 【0017】

一方、他の例の薄膜トランジスタにおいても、同様の問題があった。すなわち、ドレイン領域近傍の電界はチャネル領域とLDD領域との接合部において緩和されるので、インパクトイオン化現象をある程度抑制することができる。しかしながら、実用レベルでのLDD領域の長さ(LDD長)では十分なソース・ドレイン耐圧やACストレスに対する信頼性が得られていないという問題があった。

#### 【0018】

また、ゲート電圧として正電圧を印加してチャネル領域にチャネルを形成すると、チャネル抵抗に対してLDD領域の抵抗が直列に接続されることになる。LDD領域の不純物濃度はソース領域およびドレイン領域と比べると低いため、LDD領域の抵抗値は高くなってしまい、ON電流が低くなるという問題があった。

#### 【0019】

このように、従来の薄膜トランジスタでは、十分なソース・ドレイン耐圧、ACストレス耐性が得られておらず、また、所望のOFF電流特性またはON電流特性(電流特性)が得られていないという問題があった。

#### 【0020】

本発明は上記問題点を解決するためになされたものであり、一つの目的はソース・ドレイン耐圧およびACストレス耐性の向上が図られ、所望の電流特性の得られる半導体装置を提供することであり、他の目的はそのような半導体装置を含む画像表示回路部を備えた画像表示装置を提供することであり、さらに他の目的はそのような半導体装置の製造方法

10

20

30

40

50

を提供することである。

【課題を解決するための手段】

【0021】

本発明に係る半導体装置は、半導体層、絶縁膜および電極を有して所定の基板上に形成された半導体素子を含む半導体装置であって、半導体素子は、第1不純物領域と第2不純物領域とチャネル領域と第3不純物領域と第4不純物領域と第5不純物領域と第6不純物領域とを有する第1素子を備えている。第1不純物領域は半導体層に形成されている。第2不純物領域は、第1不純物領域と距離を隔てて半導体層に形成されている。チャネル領域は、第1不純物領域と第2不純物領域との間に位置する半導体層の部分に第1不純物領域および第2不純物領域とそれぞれ距離を隔てて形成され、所定のチャネル長を有している。第3不純物領域は、第1不純物領域とチャネル領域との間に位置する半導体層の部分にチャネル領域と接するように形成されている。第4不純物領域は、第2不純物領域とチャネル領域との間に位置する半導体層の部分にチャネル領域に接するように形成されている。第5不純物領域は、第1不純物領域と第3不純物領域との間に位置する半導体層の部分に形成されている。第6不純物領域は、第2不純物領域と第4不純物領域との間に位置する半導体層の部分に形成されている。その第1素子では、電極は互いに対向する一方側部および他方側部を有している。第3不純物領域と第5不純物領域との接合部および一方側部は略同一平面上に位置するとともに、第4不純物領域と第6不純物領域との接合部および他方側部は同一平面上に位置する。電極は、チャネル領域、第3不純物領域および第4不純物領域のそれぞれの全体と対向してオーバラップするように形成されている。絶縁膜は半導体層と電極とにそれぞれ接するように半導体層と電極との間に形成されている。第3不純物領域～第6不純物領域のそれぞれの不純物濃度は、第1不純物領域および第2不純物領域のそれぞれの不純物濃度よりも低く、チャネル領域の不純物濃度よりも高く設定されている。第3不純物領域および第4不純物領域の不純物濃度と第5不純物領域および第6不純物領域の不純物濃度とは異なるように設定されている。

10

20

30

40

50

【0022】

この構造によれば、チャネル領域の不純物濃度よりも高く、第1不純物領域（ソース）および第2不純物領域（ドレイン）よりも低い不純物濃度を有する第3不純物領域および第4不純物領域（GOLD領域）が、チャネル領域と第1不純物領域との間に位置する領域と、チャネル領域と第2不純物領域との間に位置する領域において電極と対向するように形成され、さらに、第1不純物領域および第2不純物領域の不純物濃度よりも低く、チャネル領域よりも高い不純物濃度を有する第5不純物領域および第6不純物領域（LDD構造）が、第1不純物領域と第3不純物領域との間に位置する領域と、第2不純物領域と第4不純物領域との間に位置する領域とに形成されていることで、従来のLDD構造の素子に比べて、より高いソース・ドレイン耐圧とACストレス耐性を得ることができるとともに、低いOFF電流特性が得られることがわかった。

【0023】

本発明に係る画像表示回路部を備えた画像表示装置は、画像を表示するための画像表示回路部を備えた画像表示装置である。画像表示回路部は、半導体装置、絶縁膜および電極を有して所定の基板上に形成された半導体素子を有している。その半導体素子は、第1不純物領域、第2不純物領域、チャネル領域、第3不純物領域、第4不純物領域、第5不純物領域および第6不純物領域を有する第1素子と、第7不純物領域、第8不純物領域、第9不純物領域および第10不純物領域を有する第2素子とを備えている。その第1素子では、第1不純物領域は半導体層に形成されている。第2不純物領域は、第1不純物領域と距離を隔てて半導体層に形成されている。チャネル領域は、第1不純物領域と第2不純物領域との間に位置する半導体層の部分に第1不純物領域および第2不純物領域とそれぞれ距離を隔てて形成され、所定のチャネル長を有している。第3不純物領域は、第1不純物領域とチャネル領域との間に位置する半導体層の部分にチャネル領域と接するように形成されている。第4不純物領域は、第2不純物領域とチャネル領域との間に位置する半導体層の部分に形成されている。第5不純物領域は、第1不純物領域とチャネル領域に接するように形成されている。

領域と第3不純物領域との間に位置する半導体層の部分に形成されている。第6不純物領域は、第2不純物領域と第4不純物領域との間に位置する半導体層の部分に形成されている。そして、電極は互いに対向する一方側部および他方側部を有している。第3不純物領域と第5不純物領域との接合部および一方側部は略同一平面上に位置するとともに、第4不純物領域と第6不純物領域との接合部および他方側部は同一平面上に位置する。電極は、チャネル領域、第3不純物領域および第4不純物領域のそれぞれの全体と対向してオーバラップするように形成されている。絶縁膜は半導体層と電極とにそれぞれ接するように半導体層と電極との間に形成されている。第3不純物領域～第6不純物領域のそれぞれの不純物濃度は、第1不純物領域および第2不純物領域のそれぞれの不純物濃度よりも低く、チャネル領域の不純物濃度よりも高く設定されている。第3不純物領域および第4不純物領域の不純物濃度と第5不純物領域および第6不純物領域の不純物濃度とは異なるように設定されている。第2素子では、第7不純物領域は半導体層に形成されている。第8不純物領域は、第7不純物領域と距離を隔てて半導体層に形成されている。チャネル領域は、第7不純物領域と第8不純物領域との間に位置する半導体層の部分に第7不純物領域および第8不純物領域とそれぞれ距離を隔てて形成され、所定のチャネル長を有している。第9不純物領域は、第7不純物領域とチャネル領域との間に位置する半導体層の部分にチャネル領域と接するように形成されている。第10不純物領域は、第8不純物領域とチャネル領域との間に位置する半導体層の部分にチャネル領域に接するように形成されている。そして、電極は互いに対向する一方側部および他方側部を有している。チャネル領域と第9不純物領域との接合部および一方側部は略同一平面上に位置するとともに、チャネル領域と第10不純物領域との接合部および他方側部は同一平面上に位置する。電極は、チャネル領域の全体と対向してオーバラップするように形成されている。絶縁膜は半導体層と電極とにそれぞれ接するように半導体層と電極との間に形成されている。第9不純物領域および第10不純物領域のそれぞれの不純物濃度は、第7不純物領域および第8不純物領域のそれぞれの不純物濃度よりも低く、チャネル領域の不純物濃度よりも高く設定されている。

#### 【0024】

この構造によれば、第1素子によってより高いソース・ドレイン耐圧とACストレス耐性を得ることができるとともに、低いOFF電流特性を得ることができ、加えて、第1素子よりも占有面積の小さい第2素子を適用することによって、第1素子だけを適用する場合と比べて画像表示回路部の占有面積の増大を抑制することができる。

#### 【0025】

本発明に係る半導体装置の製造方法は、以下の工程を備えている。主表面を有する基板上に第1電極を形成する。基板上に所定の第1半導体層を形成する。第1電極を形成する工程と第1半導体層を形成する工程との間に基板上に絶縁膜を形成する。第1半導体層を横切るように第1の部分を含む第1のマスク材を第1半導体層上に形成する。第1のマスク材をマスクとして第1半導体層に所定導電型の不純物イオンを導入することにより、第1のマスク材の直下に位置する第1半導体層の部分をチャネル領域とし、第1のマスク材を挟んで一方と他方との側に位置する第1半導体層の部分にチャネル領域に接するように所定の不純物濃度を有する1対の第1不純物領域を形成する(第1注入工程)。チャネル領域の全体および1対の第1不純物領域のそれぞれの部分を覆う第1の部分を含む第2のマスク材を第1半導体層上に形成する。第2のマスク材をマスクとして、第1半導体層に所定導電型の不純物イオンを導入することにより、チャネル領域を挟んで一方の側と他方の側に位置する第1半導体層の部分にチャネル領域とはそれぞれ所定の距離を隔てて第1不純物領域の不純物濃度よりも高い不純物濃度を有する1対の第2不純物領域を形成する(第2注入工程)。チャネル領域の全体および1対の第1不純物領域のそれぞれ部分を覆う第1の部分を含む第3のマスク材を第1半導体層上に形成する。第3のマスク材をマスクとして、第1半導体層に所定導電型の不純物イオンを導入することにより、チャネル領域を挟んで一方の側と他方の側に位置する第1半導体層の部分にチャネル領域とはそれぞれ所定の距離よりも短い距離を隔てて第2不純物領域の不純物濃度よりも低い不純物濃度

10

20

30

40

50

を有する 1 対の第 3 不純物領域を形成する（第 3 注入工程）。第 1 電極を形成する工程および第 1 不純物領域を形成する工程では、チャネル領域および 1 対の第 1 不純物領域のそれぞれの全体と第 1 電極とがオーバラップして対向するように形成される。

【 0 0 2 6 】

この製造方法によれば、G O L D 領域となる 1 対の第 1 不純物領域は、第 1 のマスク材をマスクとして第 1 注入工程によって形成されるため、マスク材を 1 枚追加するだけで、G O L D 領域を備えた半導体装置を容易に形成することができる。しかも、第 1 のマスク材の寸法を調整することによって、第 1 不純物領域のチャネル長方向の長さの変更等に容易に対応することができる。

【 発明を実施するための最良の形態 】

10

【 0 0 2 7 】

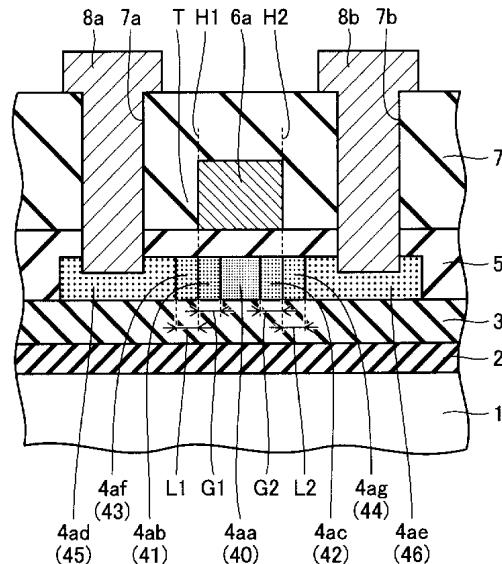

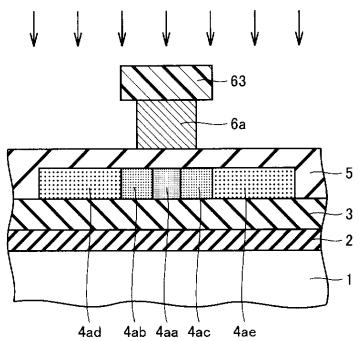

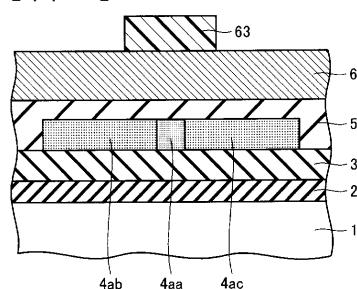

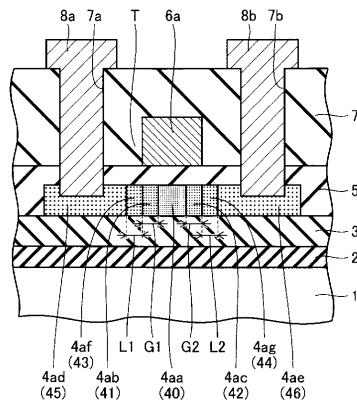

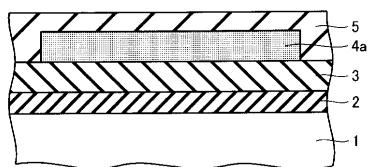

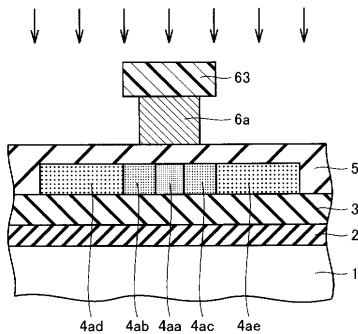

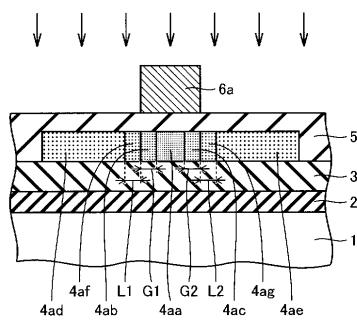

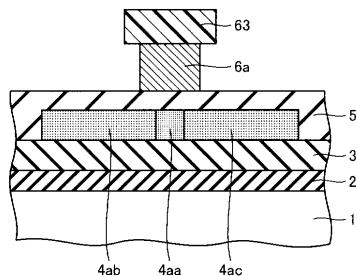

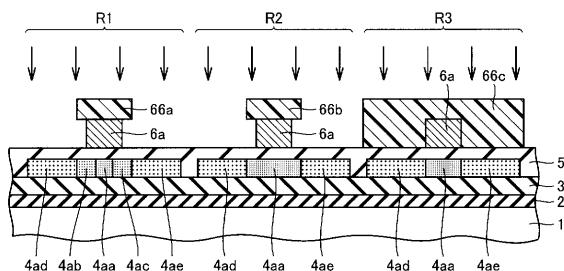

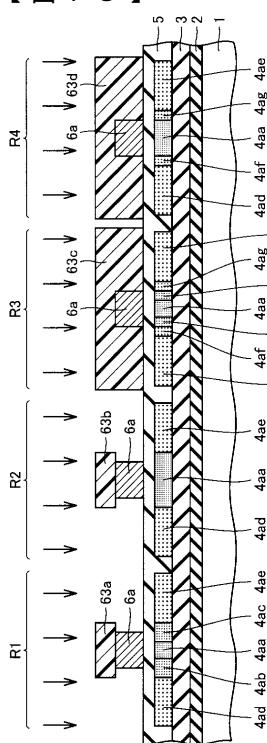

実施の形態 1

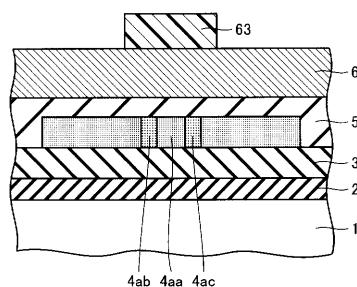

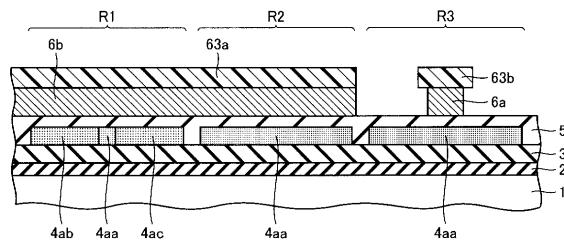

本発明の実施の形態 1 に係る半導体装置について説明する。図 1 に示すように、ガラス基板 1 上にシリコン窒化膜 2 が形成され、そのシリコン窒化膜 2 上にシリコン酸化膜 3 が形成されている。そのシリコン酸化膜 3 上にアイランド状の多結晶シリコン膜が形成されている。その多結晶シリコン膜では、所定の不純物濃度を有するソース領域 4 5 と、そのソース領域 4 5 と距離を隔てられた所定の不純物濃度を有するドレイン領域 4 6 が形成されている。

【 0 0 2 8 】

ソース領域 4 5 とドレイン領域 4 6 との間に位置する領域には、ソース領域 4 5 およびドレイン領域 4 6 とそれぞれ距離を隔てられて、所定のチャネル長を有するチャネル領域 4 0 が形成されている。

20

【 0 0 2 9 】

ソース領域 4 5 とチャネル領域 4 0 との間に位置する領域には、ソース領域 4 5 の側に L D D 領域 4 3 が形成され、チャネル領域 4 0 の側に G O L D 領域 4 1 が形成されている。また、ドレイン領域 4 6 とチャネル領域 4 0 との間に位置する領域には、ドレイン領域 4 6 の側に L D D 領域 4 4 が形成され、チャネル領域 4 0 の側に G O L D 領域 4 2 が形成されている。

【 0 0 3 0 】

L D D 領域 4 3 , 4 4 および G O L D 領域 4 1 , 4 2 のそれぞれの不純物濃度はチャネル領域 4 0 の不純物濃度よりも高く、ソース領域 4 5 およびドレイン領域 4 6 の不純物濃度よりも低く設定されている。そして、さらに、L D D 領域 4 3 , 4 4 の不純物濃度は G O L D 領域 4 1 , 4 2 の不純物濃度よりも高く設定されている。

30

【 0 0 3 1 】

そのアイランド状の多結晶シリコン膜を覆うように、シリコン酸化膜からなるゲート絶縁膜 5 が形成されている。そのゲート絶縁膜 5 上にゲート電極 6 a が形成されている。ゲート電極 6 a を覆うように、たとえばシリコン酸化膜からなる層間絶縁膜 7 が形成されている。

【 0 0 3 2 】

その層間絶縁膜 7 にソース領域 4 5 の表面を露出するコンタクトホール 7 a と、ドレイン領域 4 6 の表面を露出するコンタクトホール 7 b がそれぞれ形成されている。そのコンタクトホール 7 a , 7 b を充填するように、層間絶縁膜 7 上にソース電極 8 a とドレイン電極 8 b とが形成されている。

40

【 0 0 3 3 】

ゲート電極 6 a 、ソース領域 4 5 、ドレイン領域 4 6 、L D D 領域 4 3 , 4 4 、G O L D 領域 4 1 , 4 2 、チャネル領域 4 0 を含んで薄膜トランジスタ T が構成される。特に、ゲート電極 6 a は、チャネル領域 4 0 の全体を覆うように形成されるとともに、G O L D 領域 4 1 および G O L D 領域 4 2 と平面的にオーバラップするように形成されている。

【 0 0 3 4 】

つまり、一方の G O L D 領域 4 1 と L D D 領域 4 3 との接合部およびゲート電極 6 a の

50

一方側部とは略同一平面 H 1 上に位置し、他方の G O L D 領域 4 2 と L D D 領域 4 4 との接合部およびゲート電極 6 a の他方側部は同一平面 H 2 上に位置している。

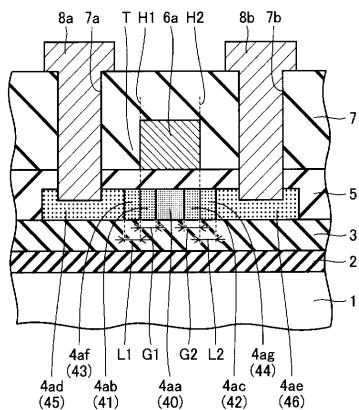

【 0 0 3 5 】

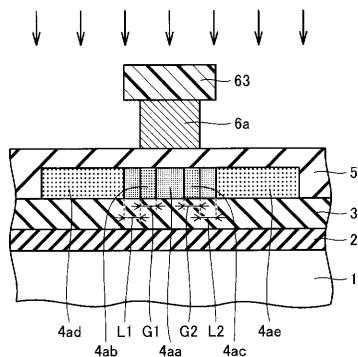

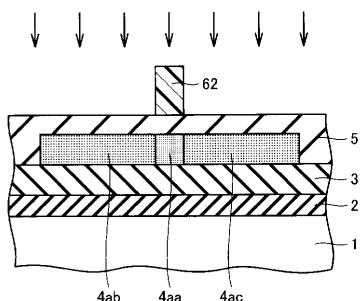

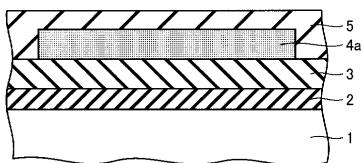

次に、上述した半導体装置の製造方法の一例について説明する。図 2 に示すように、まず、基板として、コーニング社製 1737 のガラス基板 1 の主表面上に、たとえばプラズマ C V D ( Chemical Vapor Deposition ) 法により膜厚約 100 nm のシリコン窒化膜 2 が形成される。そのシリコン窒化膜 2 上に、膜厚約 100 nm のシリコン酸化膜 3 が形成される。次に、そのシリコン酸化膜 3 上に膜厚約 50 nm の非晶質シリコン膜が形成される。

【 0 0 3 6 】

なお、シリコン窒化膜 2 はガラス基板 1 に含まれる不純物が上方に拡散するのを阻止するために形成される。この不純物の拡散を阻止するための膜としてはシリコン窒化膜の他に、SiON、SiC、AlN、Al2O3などの材料を適用してもよい。また、非晶質シリコン膜の下地膜としてシリコン窒化膜 2 とシリコン酸化膜 3 との 2 層構造としたが、2 層構造に限られるものではなく、これらの膜を省いたり、あるいはさらに膜を積層してもよい。

【 0 0 3 7 】

次に、非晶質シリコン膜を所定の真空中にて熱処理を施すことにより、非晶質シリコン膜中に存在する不要な水素が除去される。次に、非晶質シリコン膜に、たとえば XeC1 レーザによるレーザ光を照射することにより、図 2 に示すように、非晶質シリコン膜が多結晶化されて多結晶シリコン膜 4 とされる。多結晶シリコン膜 4 の粒径は約 0.5 μm 程度である。

【 0 0 3 8 】

なお、XeC1 レーザの他に、たとえば YAG レーザ、CW レーザを用いてもよい。また、熱アニールにより非晶質シリコン膜の多結晶化を行なってもよい。特に、熱アニールを施す場合には、ニッケルなどの触媒を用いることで、より粒径の大きい多結晶シリコンが得られる。その多結晶シリコン膜 4 上にレジストパターン 6 1 が形成される。

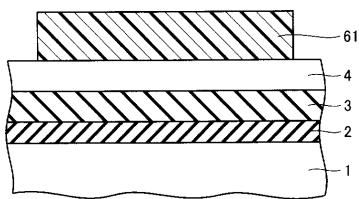

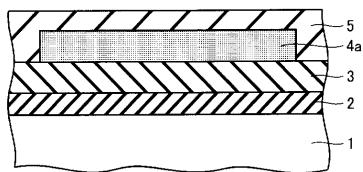

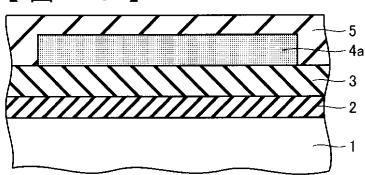

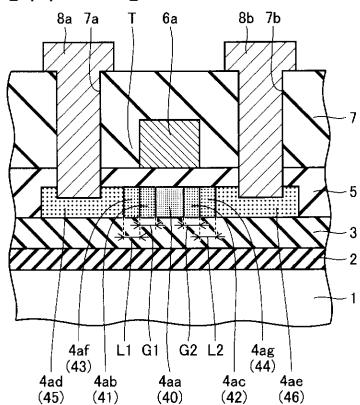

【 0 0 3 9 】

次に、図 3 に示すように、そのレジストパターン 6 1 をマスクとして多結晶シリコン膜 4 に異方性エッチングを施すことにより、アイランド状の多結晶シリコン膜 4 a が形成される。その後、アッシングと薬液処理を施すことで、レジストパターンが 6 1 が除去される。

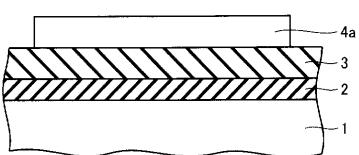

【 0 0 4 0 】

次に、図 4 に示すように、多結晶シリコン膜 4 a を覆うように、たとえばプラズマ C V D 法により膜厚約 100 nm のシリコン酸化膜からなるゲート絶縁膜 5 が形成される。なお、この場合、シリコン酸化膜の原料として液体原料の TEOS ( Tetra Ethyl Ortho Silicate ) が用いられる。

【 0 0 4 1 】

次に、薄膜トランジスタのしきい値を制御するために、たとえばドーズ量  $1 \times 10^{12}$  atom / cm<sup>2</sup> 、加速エネルギー 60 KeV にて多結晶シリコン膜 4 a にボロンが注入される。なお、この注入工程は必要に応じて行なえばよく省いてよい。

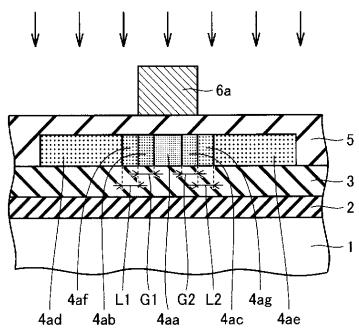

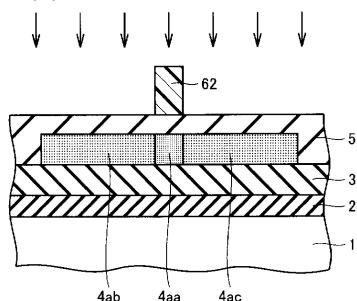

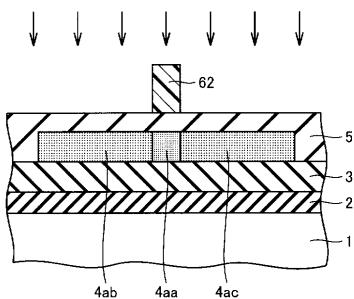

【 0 0 4 2 】

次に、図 5 に示すように、所定の写真製版処理を施すことによりレジストパターン 6 2 が形成される。次に、レジストパターン 6 2 をマスクとして、たとえばドーズ量  $5 \times 10^{12}$  atom / cm<sup>2</sup> 、加速エネルギー 80 KeV にて多結晶シリコン膜 4 a にリンを注入することにより不純物領域 4 a b , 4 a c が形成される。

【 0 0 4 3 】

この注入量が G O L D 領域における注入量 ( 不純物濃度 ) になる。不純物領域 4 a b と不純物領域 4 a c との間にはチャネルとなる不純物領域 4 a a が形成される。その後、アッシングと薬液処理を施すことで、レジストパターン 6 2 が除去される。

10

20

30

40

50

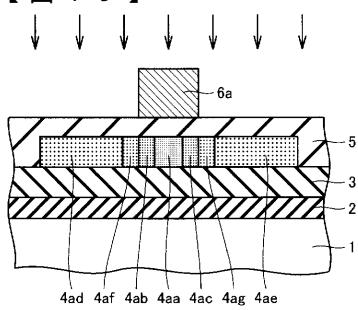

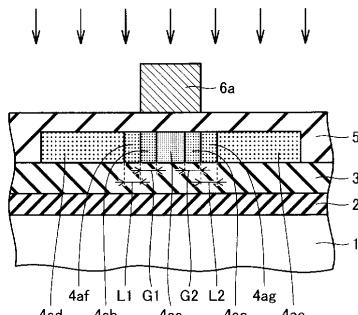

## 【0044】

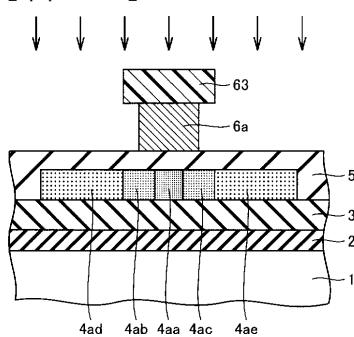

次に、図6に示すように、スパッタ法によりゲート絶縁膜5の全面に膜厚約400nmのクロム膜6が形成される。次に、所定の写真製版を行なうことによりレジストパターン63が形成される。

## 【0045】

レジストパターン63をマスクとしてクロム膜6にウエットエッティングを施すことにより、図7に示すように、ゲート電極6aが形成される。ゲート電極6aは、チャネルとなる不純物領域4aaを挟んで位置する不純物領域4abと不純物領域4acとに平面的にオーバラップするように形成されている。不純物領域4ab, 4acにおいてゲート電極6aと平面的にオーバラップする領域がGOLD領域となる。

10

## 【0046】

なお、ウェットエッティングを施す際に露出するクロム膜6の側面にサイドエッティングが施されることになるが、そのエッティングされる量はオーバーエッティングを施す時間によって制御することができる。

## 【0047】

次に、レジストパターン63をマスクとして、たとえばドーズ量 $1 \times 10^{14}$ atom/cm<sup>2</sup>、加速エネルギー80KeVにて不純物領域4ab, 4acにリンを注入することによりソース領域およびドレイン領域となる不純物領域4ad, 4aeが形成される。その後、アッシングと薬液処理を施すことで、レジストパターンが63が除去される。

20

## 【0048】

次に、図8に示すように、ゲート電極6aをマスクとして、たとえばドーズ量 $1 \times 10^{13}$ atom/cm<sup>2</sup>、加速エネルギー80KeVにてリンを注入することにより残された不純物領域4ab, 4acにLDD領域となる不純物領域4af, 4agがそれぞれ形成される。LDD領域となる不純物領域4af, 4agの不純物濃度は、当該リンの注入量と、GOLD領域を形成するためのリンの注入量とによって決まる事になる。

## 【0049】

このようして、不純物領域4af, 4agが形成されることでGOLD領域となる不純物領域4ab, 4acの不純物濃度は、LDD領域となる不純物領域4af, 4agの不純物濃度よりも低くなる。

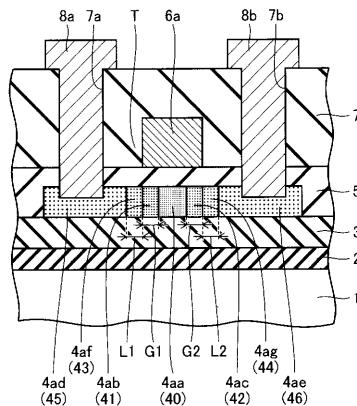

## 【0050】

次に、図9に示すように、ゲート電極6aを覆うように、たとえばプラズマCVD法により膜厚約400nmのシリコン酸化膜からなる層間絶縁膜7が形成される。次に、その層間絶縁膜7上に所定の写真製版処理を施すことにより、コンタクトホールを形成するためのレジストパターン(図示せず)が形成される。そのレジストパターンをマスクとして、層間絶縁膜7およびゲート絶縁膜5に異方性エッティングを施すことにより、不純物領域4adの表面を露出するコンタクトホール7aと、不純物領域4aeの表面を露出するコンタクトホール7bが形成される。

30

## 【0051】

次に、コンタクトホール7a, 7bを充填するように、層間絶縁膜7上にクロム膜とアルミニウム膜との積層膜(図示せず)が形成される。その積層膜上に所定の写真製版処理を施すことにより、電極を形成するためのレジストパターン(図示せず)が形成される。次に、そのレジストパターンをマスクとしてウエットエッティングを施すことにより、ソース電極8aとドレイン電極8bが形成される。

40

## 【0052】

以上のようにして薄膜トランジスタTを備えた半導体装置の主要部分が形成される。この薄膜トランジスタTでは、不純物領域4adがソース領域45となり、不純物領域4aeがドレイン領域46となり、不純物領域4af, 4agがLDD領域43, 44となり、不純物領域4ab, 4acがGOLD領域41, 42となり、不純物領域4aaがチャネル領域40となる。

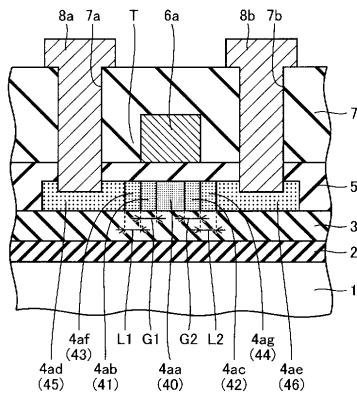

## 【0053】

50

その LDD 領域 43, 44 はそれぞれチャネル長方向に所定の長さ L1, L2 を有し、GOLD 領域 41, 42 はそれぞれチャネル長方向に所定の長さ G1, G2 を有している。LDD 領域 43, 44 の LDD 長 L1 と L2 はほぼ同じ長さとされ、GOLD 領域 41, 42 の GOLD 領域長 G1 と G2 はほぼ同じ長さとされる。

#### 【0054】

次に、上述した薄膜トランジスタについて、ソース・ドレイン耐圧を測定した結果について説明する。測定には、ゲート幅を 10 μm、実効ゲート長を 5 μm、GOLD 領域 41, 42 のチャネル長方向の長さを 1 μm、LDD 領域 43, 44 のチャネル長方向の長さを 0.5 μm、ゲート電極 6a のチャネル長方向の長さを 7 μm とした薄膜トランジスタを用いた。

10

#### 【0055】

一方、比較のために、従来の LDD 構造の薄膜トランジスタおよび GOLD 構造の薄膜トランジスタとして、ゲート幅を 10 μm、ゲート長を 5 μm、LDD 領域のチャネル長方向の長さを 0.5 μm とした LDD 構造の薄膜トランジスタと、ゲート幅を 10 μm、ゲート長を 5 μm、GOLD 領域のチャネル長方向の長さを 1 μm、ゲート電極のチャネル長方向の長さを 7 μm とした GOLD 構造の薄膜トランジスタを用いた。

#### 【0056】

図 10 に、ソース・ドレイン耐圧の測定結果を示す。測定に際してゲート電圧は 0 V に設定され、ソースは接地されている。そして、ドレイン電流が 0.1 μA となるときのドレイン電圧をソース・ドレイン耐圧と定義した。図 10 に示すように、実施の形態 1 に係る GOLD 構造の薄膜トランジスタのソース・ドレイン耐圧は、従来の GOLD 構造の薄膜トランジスタと LDD 構造の薄膜トランジスタと比べてより高いソース・ドレイン耐圧を達成できることが確認された。

20

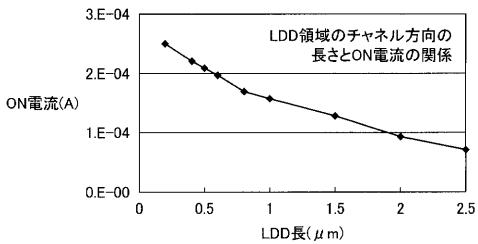

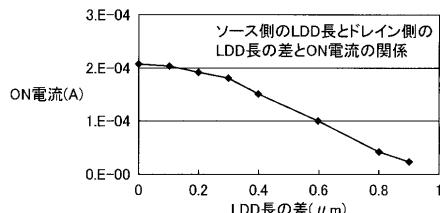

#### 【0057】

次に、ON 電流を測定した結果について説明する。測定に際して、ソースを接地して、ゲートに 8 V を、ドレインに 5 V をそれぞれ印加した。そして、このとき測定されるドレイン電流を ON 電流とした。その ON 電流の測定結果を図 11 に示す。図 11 に示すように、実施の形態 1 に係る GOLD 構造の薄膜トランジスタでは、LDD 領域として同じ長さを有する従来の LDD 構造の薄膜トランジスタの ON 電流とほぼ同じ ON 電流が得られることが確認された。

30

#### 【0058】

次に、OFF 電流を測定した結果について説明する。測定に際して、ソースを接地して、ドレインに 5 V、ゲートに -5 V をそれぞれ印加した。そして、このとき測定されるドレイン電流を OFF 電流とした。その OFF 電流の測定結果を図 12 に示す。図 12 に示すように、実施の形態 1 に係る GOLD 構造の薄膜トランジスタでは、従来の GOLD 構造の薄膜トランジスタの OFF 電流よりも低い OFF 電流が得られることが確認された。

40

#### 【0059】

次に、AC ストレス寿命について評価した結果について説明する。AC ストレス条件として、ゲート電圧  $\pm 15$  V、ソース電圧 0 V、ドレイン電圧 0 V とし、ON 電流が 80 % になるまでのストレス時間を AC ストレス寿命とした。その AC ストレス寿命の結果を図 13 に示す。

#### 【0060】

ここでは、各 AC ストレス寿命は、実施の形態 1 に係る薄膜トランジスタの AC ストレス寿命を 1 とした相対値（比率）で示されている。図 13 に示すように、実施の形態 1 に係る薄膜トランジスタの AC ストレス寿命は、従来の GOLD 構造の薄膜トランジスタおよび LDD 構造の薄膜トランジスタと比べて大幅に AC ストレス寿命が伸びていることが確認され、AC ストレスに対する信頼性を向上できることが判明した。

#### 【0061】

次に、上述した製造方法によって形成される薄膜トランジスタの GOLD 領域と LDD 領域の不純物注入量（不純物濃度）の評価について説明する。まず、評価用試料を薄膜ト

50

ランジスタを形成する場合と同様に作製した。すなわち、ガラス基板上に膜厚約100nmのシリコン窒化膜、膜厚約100nmのシリコン酸化膜および膜厚約50nmの非晶質シリコン膜を順次形成し、その非晶質シリコン膜に所定のレーザアニール処理を施した。

#### 【0062】

その後、膜厚約100nmのシリコン酸化膜を形成してGOLD領域を形成するためのリンのイオン注入とLDD領域を形成するためのリンのイオン注入とを行ない、注入された不純物の量をSIMS(Secondary Ion Mass Spectrometer)により測定した。その結果、GOLD領域に対応する不純物の量は $5 \times 10^{17}$ atom/cm<sup>3</sup>であり、LDD領域に対応する不純物の量は $1.5 \times 10^{18}$ atom/cm<sup>3</sup>であることがわかった。

#### 【0063】

そのGOLD領域は、ゲート絶縁膜5上に形成されるレジストパターン62をマスクとして注入される不純物イオンによって形成されることになる。これに対して、従来、ゲート電極を2層構造とし、上層部分をマスクとしてテーパ状の下層部分を介して不純物イオンを注入することによりGOLD領域を形成する方法がある。

#### 【0064】

ところが、この方法では、ゲート電極の上層部分を形成するためのエッチングを施す際に、下層部分にもエッチングが施されてしまい、下層部分の層厚が不均一になってしまふ。そのため、下層部分を介して不純物イオンを注入する際に注入量のばらつきが大きくなることがあった。また、ゲート電極を構成する金属材料を介して不純物イオンを注入するため、注入エネルギーをより高くする必要があり、これが不純物イオンの注入量のばらつきをさらに大きくする要因となっていた。

#### 【0065】

一方、上述した方法では、ゲート絶縁膜を形成した直後にGOLD領域を形成するための不純物イオンの注入が行なわれることで、不純物イオンの注入量に影響を与えるのはゲート絶縁膜の膜厚のばらつきのみとなる。その結果、不純物イオンの注入量のばらつきを従来の場合よりも抑えることができる。

#### 【0066】

また、従来の方法では、GOLD領域のチャネル長方向の長さ(GOLD長)は、上層電極をエッチングによって形成する際のテーパ角度によって制御される。ところが、この方法では、テーパ角度が小さい場合に、テーパ角度やエッチングレートのばらつきによってGOLD長が大きく変動するため、GOLD長の寸法制御が難しいという問題があった。また、テーパ角度を小さくするとGOLD長が制約されるという問題があった。

#### 【0067】

さらに、ゲート電極をテーパ状に形成するためには、ドライエッチング装置内において被エッチング部分に対しエッチング反応と生成物の堆積反応をバランスよく進行させる必要があり、エッチングプロセスの制御が極めて難しいという問題があった。

#### 【0068】

一方、上述した方法では、レジストパターンをマスクとしてGOLD領域を形成するための不純物イオンの注入が行なわれることで、GOLD長を自由に設定することができて、GOLD長の寸法制御性が高くなるという利点を有する。

#### 【0069】

このように、上述した薄膜トランジスタの製造方法では、ゲート絶縁膜を形成した後にレジストパターンをマスクとしてGOLD領域を形成するための不純物イオンの注入が行なわれることで、注入量の制御性が良好であり、また、GOLD長の制御性が高く、GOLD長のプロセスに対する自由度を向上することができる。

#### 【0070】

また、上述した薄膜トランジスタでは、ゲート電極を単層構造とすることで、従来の場合と比べてゲート電極を形成するためのエッチングを含めたエッチングプロセスの回数を減らすことができる。これを図14に示す。図14に示すように、本実施の形態に係る薄膜トランジスタでは、薄膜トランジスタの完成までに4回のエッチングが必要とされるの

10

20

30

40

50

に対して、従来の方法では 6 回のエッティングが必要とされる。

【 0 0 7 1 】

エッティングプロセスではパーティクル（異物）が発生しやすく、これが歩留まり低下の要因となるため、エッティングプロセスの回数を減らすことで、歩留まりの向上を図るとともにコストの削減も図ることができる。

【 0 0 7 2 】

実施の形態 2

ここでは、G O L D 領域の不純物濃度が L D D 領域の不純物濃度よりも高い場合を例に挙げる。まず、その製造方法について説明する。図 15 に示すゲート絶縁膜 5 を形成し、薄膜トランジスタのしきい値を制御するための所定の不純物を注入する工程までは、前述した図 4 に示す工程までと同様である。

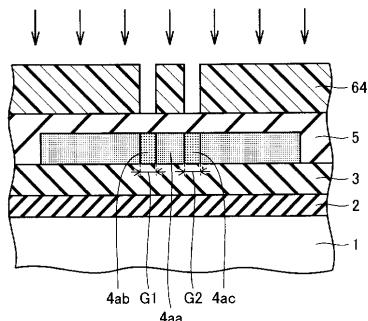

【 0 0 7 3 】

次に、図 16 に示すように、所定の写真製版処理を施すことによりゲート絶縁膜 5 上にレジストパターン 6 4 が形成される。そのレジストパターン 6 4 をマスクとして、たとえばドーズ量  $1 \times 10^{13}$  atom / cm<sup>2</sup>、加速エネルギー 80 KeV にてリンを注入することにより G O L D 領域となる不純物領域 4 a b , 4 a c が形成される。この注入量が G O L D 領域における注入量になる。その後、アッシングと薬液処理を施すことで、レジストパターンが 6 4 が除去される。

【 0 0 7 4 】

次に、図 17 に示すように、スパッタ法によりゲート絶縁膜 5 の全面に膜厚約 400 nm のクロム膜 6 が形成される。そのクロム膜 6 上に、所定の写真製版処理を施すことによりレジストパターン 6 3 が形成される。レジストパターン 6 3 は不純物領域 4 a b , 4 a c とオーバラップするように形成される。この不純物領域 4 a b , 4 a c においてレジストパターン 6 3 とオーバラップしている部分が G O L D 領域となる。

【 0 0 7 5 】

次に、図 18 に示すように、そのレジストパターン 6 3 をマスクとしてクロム膜 6 にウエットエッティングを施すことにより、ゲート電極 6 a が形成される。ウエットエッティングを施す際には、露出したクロム膜 6 の側面にサイドエッティングが施されることになるが、そのエッティングされる量は、オーバエッティングを施す時間によって制御される。

【 0 0 7 6 】

次に、レジストパターン 6 3 をマスクとして、たとえばドーズ量  $1 \times 10^{14}$  atom / cm<sup>2</sup>、加速エネルギー 80 KeV にてリンを注入することによりソース領域およびドレイン領域となる不純物領域 4 a d , 4 a e が形成される。その後、アッシングと薬液処理を施すことで、レジストパターンが 6 3 が除去される。

【 0 0 7 7 】

次に、図 19 に示すように、ゲート電極 6 a をマスクとして、たとえばドーズ量  $5 \times 10^{12}$  atom / cm<sup>2</sup>、加速エネルギー 80 KeV にてリンを注入することにより L D D 領域となる不純物領域 4 a f , 4 a g が形成される。この注入量が L D D 領域における注入量になる。この場合、G O L D 領域の不純物濃度は、L D D 領域の不純物濃度よりも高くソース領域およびドレイン領域の不純物濃度よりも低くなるように設定される。

【 0 0 7 8 】

その後、前述した図 9 に示す工程と同様の工程を経て、図 20 に示すように、n チャネル型の G O L D 構造の薄膜トランジスタが形成される。

【 0 0 7 9 】

次に、上述した薄膜トランジスタについて、ソース・ドレイン耐圧を測定した結果について説明する。測定には、ゲート幅を 10 μm、ゲート長を 5 μm、G O L D 領域 4 1 , 4 2 のチャネル長方向の長さを 1 μm、L D D 領域 4 3 , 4 4 のチャネル長方向の長さを 0.5 μm、ゲート電極 6 a のチャネル長方向の長さを 7 μm とした薄膜トランジスタを用いた。

【 0 0 8 0 】

10

20

30

40

50

一方、比較のために、従来のLDD構造の薄膜トランジスタおよびGOLD構造の薄膜トランジスタとして、ゲート幅を10μm、ゲート長を5μm、LDD領域のチャネル長方向の長さを0.5μmとしたLDD構造の薄膜トランジスタと、ゲート幅を10μm、ゲート長を5μm、GOLD領域のチャネル長方向の長さを1μm、ゲート電極のチャネル長方向の長さを7μmとしたGOLD構造の薄膜トランジスタを用いた。

#### 【0081】

図21に、ソース・ドレイン耐圧の測定結果を示す。なお、測定条件等は前述した条件と同様である。図21に示すように、実施の形態2に係るGOLD構造の薄膜トランジスタのソース・ドレイン耐圧は、従来のGOLD構造の薄膜トランジスタとLDD構造の薄膜トランジスタよりも高いソース・ドレイン耐圧を達成できることが確認された。

10

#### 【0082】

次に、ON電流を測定した結果について説明する。なお、測定条件は前述した条件と同様である。ON電流の測定結果を図22に示す。図22に示すように、実施の形態2に係るGOLD構造の薄膜トランジスタでは、LDD領域として同じ長さを有する従来のLDD構造の薄膜トランジスタのON電流とほぼ同じON電流が得られることが確認された。

#### 【0083】

次に、OFF電流を測定した結果について説明する。なお、測定条件は前述した条件と同様である。OFF電流の測定結果を図23に示す。図23に示すように、実施の形態2に係るGOLD構造の薄膜トランジスタでは、従来のGOLD構造の薄膜トランジスタのOFF電流および実施の形態1において説明した薄膜トランジスタのOFF電流のいずれよりも低いOFF電流が得られることが確認された。

20

#### 【0084】

次に、ACストレス寿命について評価した結果について説明する。なお、測定条件は前述した条件と同様である。ACストレス寿命の結果を図24に示す。図24に示すように、実施の形態2に係る薄膜トランジスタのACストレス寿命は、従来のGOLD構造の薄膜トランジスタおよびLDD構造の薄膜トランジスタと比べて大幅にACストレス寿命が延びていることが確認され、ACストレスに対する信頼性を向上できることが判明した。

#### 【0085】

なお、上述した製造方法によって形成される薄膜トランジスタのGOLD領域とLDD領域の不純物注入量（不純物濃度）について、前述した方法と同様の方法によって測定したところ、GOLD領域に対応する不純物の量は $1 \times 10^{18}$ atom/cm<sup>3</sup>であり、LDD領域に対応する不純物の量は $5 \times 10^{17}$ atom/cm<sup>3</sup>であることが確認された。

30

#### 【0086】

##### 実施の形態3

ここでは、実施の形態2において説明した薄膜トランジスタの製造方法の他の例について説明する。図25に示すゲート絶縁膜5を形成し、薄膜トランジスタのしきい値を制御するための所定の不純物を注入する工程までは、前述した図4に示す工程までと同様である。

#### 【0087】

次に、図26に示すように、所定の写真製版処理を施すことによりゲート絶縁膜5上にレジストパターン62が形成される。そのレジストパターン62をマスクとして、たとえばドーズ量 $1 \times 10^{13}$ atom/cm<sup>2</sup>、加速エネルギー80KeVにてリンを注入することによりGOLD領域となる不純物領域4ab, 4acが形成される。この注入量がGOLD領域における注入量になる。その後、アッシングと薬液処理を施すことで、レジストパターンが62が除去される。

40

#### 【0088】

その後、前述した図6および図7に示す工程と同様の工程を経て、レジストパターン63とゲート電極63aが形成される。次に、図27に示すように、レジストパターン63をマスクとして、たとえばドーズ量 $1 \times 10^{14}$ atom/cm<sup>2</sup>、加速エネルギー80KeVにてリンを注入することによりソース領域およびドレイン領域となる不純物領域4ad

50

, 4 a e が形成される。その後、アッシングと薬液処理を施すことで、レジストパターンが 6 3 が除去される。

【 0 0 8 9 】

次に、図 2 8 に示すように、ゲート電極 6 a をマスクとして、たとえばドーズ量  $4 \times 10^{12}$  atom / cm<sup>2</sup>、加速エネルギー 60 KeV にてボロンを注入することにより LDD 領域となる不純物領域 4 a f , 4 a g が形成される。

【 0 0 9 0 】

このとき、リンが注入された n 型の不純物領域 4 a b , 4 a c において p 型のボロンが注入された部分では、p 型不純物（ボロン）の注入によってキャリア濃度が下がることになり、実効的な不純物濃度が下がることになる。これにより、LDD 領域となる不純物領域 4 a f , 4 a g の不純物濃度は GOLD 領域となる不純物領域 4 a b , 4 a c の不純物濃度よりも低くなる。

【 0 0 9 1 】

つまり、LDD 領域の実効的な不純物濃度は LDD 領域を形成するためのイオン注入量と GOLD 領域を形成するためのイオン注入量との差によって決定されることになる。これにより、GOLD 領域の不純物濃度は、LDD 領域の不純物濃度よりも高くソース領域およびドレイン領域の不純物濃度よりも低くなる。

【 0 0 9 2 】

その後、前述した図 9 に示す工程と同様の工程を経て、図 2 9 に示すように、n チャネル型の GOLD 構造の薄膜トランジスタが形成される。上述した方法によって製造された薄膜トランジスタにおいても、実施の形態 2 において説明した薄膜トランジスタと同じ特性を得ることができることがわかった。

【 0 0 9 3 】

上述した GOLD 領域の不純物濃度が LDD 領域の不純物濃度よりも高く設定された半導体装置では、ドレイン近傍の電界はチャネル領域と GOLD 領域との接合部と、GOLD 領域よりも不純物濃度が低い LDD 領域とによって緩和されて、十分なソース・ドレイン耐圧と AC ストレス耐性を得ることができる。ストレスを印加した際の劣化率はストレス時間に依存し、ストレス時間が長くなるとともに劣化率も大きくなるが、ある劣化率の値において劣化の進行が飽和する。発明者らは GOLD 領域の不純物濃度をより高くすることで、劣化が少ない劣化率において劣化が飽和することを見出した。これにより、トランジスタの特性を長期にわたって安定させることができる。また、GOLD 領域はゲート電極とオーバーラップしており、チャネル形成時には GOLD 領域にもチャネルが形成されるため、GOLD 領域が ON 電流に悪影響を及ぼすこともない。さらに、チャネルがオフの時には、LDD 領域によりソース・ドレイン近傍の電界が緩和されて、OFF 電流を小さくすることができる。

【 0 0 9 4 】

なお、劣化率と飽和劣化率はそれぞれ次のように説明（定義）される。まず、薄膜トランジスタに AC ストレスを印加することによって、ON 電流は減少することになる。劣化率とは、この ON 電流の減少率をいい、ON 電流減少量（劣化量）を I、電流の初期値を I<sub>0</sub>、AC ストレス印加後の ON 電流を I とすると、劣化率（I / I<sub>0</sub>）は、I / I<sub>0</sub> = (I<sub>0</sub> - I) / I<sub>0</sub> で求められる。AC ストレスを薄膜トランジスタに印加する時間が長くなると、劣化の進行（ON 電流の減少）は飽和する。飽和劣化率とは、この劣化率が飽和するときの劣化率として定義される。この明細書では、劣化率は、あるストレス時間における ON 電流の劣化率という意味で使用される。また、飽和劣化率は、上記のように、ストレス時間に対して ON 電流が飽和するときの劣化率であり、この値は半導体装置に固有の値となる。後述する各評価結果では、この飽和劣化率の GOLD 領域の不純物濃度依存性、あるいは GOLD 長依存性が示されている。

【 0 0 9 5 】

以下、半導体装置において GOLD 領域の不純物濃度が LDD 領域の不純物濃度よりも高い場合における、GOLD 領域の不純物濃度の範囲およびチャネル長方向の長さ、L D

10

20

30

40

50

D領域のチャネル長方向の長さ、ソース側とドレイン側のLDD領域のチャネル長方向の長さの差について、実施の形態4～7において詳しく説明する。

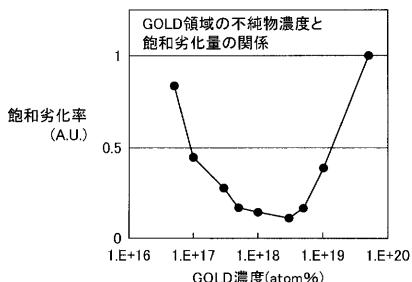

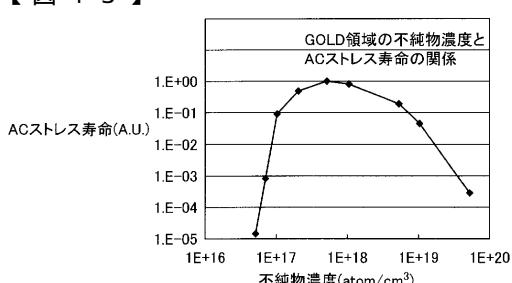

#### 【0096】

##### 実施の形態4

ここでは、薄膜トランジスタにおけるGOLD領域の不純物濃度について説明する。不純物濃度の範囲を求めるために、GOLD領域の不純物濃度を変化させた種々の薄膜トランジスタを作製してその電気的特性を評価した。その薄膜トランジスタのゲート幅を10μm、ゲート長を5μm、GOLD領域のチャネル長方向の長さを1μm、LDD領域のチャネル長方向の長さを0.5μm、ゲート電極のチャネル長方向の長さを7μmとし、また、LDD領域の不純物濃度をGOLD領域の不純物濃度の半分として、実施の形態2において説明した方法と同様の方法により作製した。

#### 【0097】

図30に、ACストレスを印加した場合における飽和劣化率のGOLD領域の不純物濃度依存性のグラフを示す。図30に示すように、GOLD領域の不純物濃度を $1 \times 10^{17}$ atom/cm<sup>3</sup>以上、 $1 \times 10^{19}$ atom/cm<sup>3</sup>以下に設定することにより飽和劣化量を抑制できることがわかる。特に、GOLD領域の不純物濃度を $5 \times 10^{17}$ atom/cm<sup>3</sup>以上、 $5 \times 10^{18}$ atom/cm<sup>3</sup>以下の範囲において飽和劣化量を抑制できることがわかる。

#### 【0098】

##### 実施の形態5

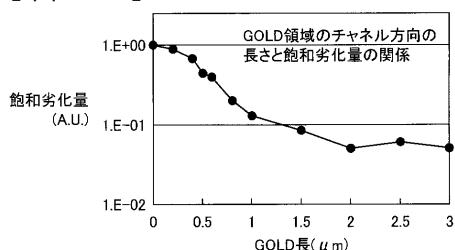

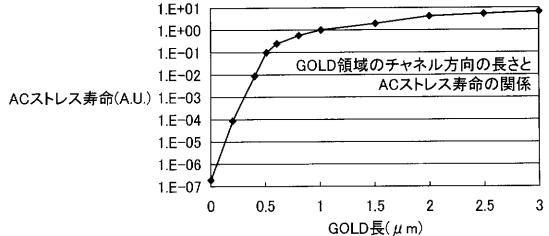

ここでは、薄膜トランジスタにおけるGOLD領域のチャネル長方向の長さについて説明する。GOLD領域のチャネル長方向の長さ(GOLD長)の範囲を求めるために、GOLD長を変化させた種々の薄膜トランジスタを作製してその電気的特性を評価した。

#### 【0099】

その薄膜トランジスタのゲート幅を10μm、ゲート長を5μm、LDD領域のチャネル長方向の長さを0.5μmとし、また、ゲート電極のチャネル長方向の長さをGOLD領域のチャネル長方向の長さに応じて変化させ、実施の形態1において説明した方法と同様の方法により作製した。また、GOLD領域の不純物濃度を $1 \times 10^{18}$ atom/cm<sup>3</sup>とし、LDD領域の不純物濃度を $5 \times 10^{17}$ atom/cm<sup>3</sup>とした。

#### 【0100】

図31に、ACストレスを印加した場合における飽和劣化率のGOLD領域のチャネル長方向の長さ(GOLD長)の依存性のグラフを示す。図31に示すように、GOLD長が0.5μmより短くなると、飽和劣化率が下がって飽和劣化量を抑制できることがわかる。飽和劣化量はGOLD長が長くなるにしたがって小さくなる傾向にあるので、GOLD長は長い方が望ましいが、GOLD長が2μmを超えると飽和劣化率は飽和する傾向を示す。また、GOLD長が長くなるとトランジスタのサイズが大きくなるため、GOLD長は2μm以下に設定することが望ましい。このように、飽和劣化量とトランジスタの占有面積の観点から、GOLD長を0.5μm以上2μm以下に設定することが望ましいことがわかる。

#### 【0101】

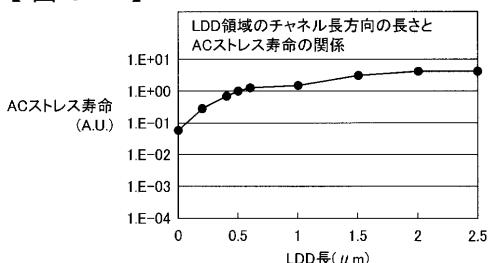

##### 実施の形態6

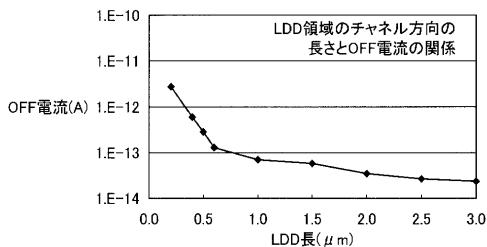

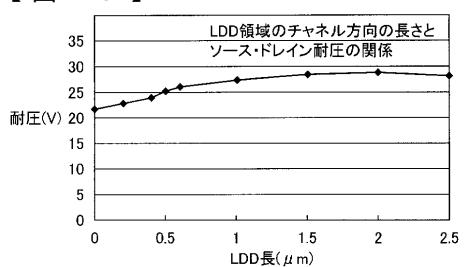

ここでは、薄膜トランジスタにおけるLDD領域のチャネル長方向の長さについて説明する。LDD領域のチャネル長方向の長さ(LDD長)の範囲を求めるために、LDD長を変化させた種々の薄膜トランジスタを作製してその電気的特性を評価した。

#### 【0102】

その薄膜トランジスタのゲート幅を10μm、ゲート長を5μm、GOLD領域のチャネル長方向の長さを1μm、ゲート電極のチャネル長方向の長さを7μmとして、実施の形態1において説明した方法と同様の方法により作製した。なお、GOLD領域の不純物濃度を $1 \times 10^{18}$ atom/cm<sup>3</sup>とし、LDD領域の不純物濃度を $5 \times 10^{17}$ atom/cm<sup>3</sup>とした。

10

20

30

40

50

## 【0103】

図32に、ACストレス寿命のLDD領域のチャネル長方向の長さ(LDD長)依存性のグラフを示す。図32に示すように、LDD長が0.5μmよりも短くなると、ACストレス寿命が短くなる傾向にあることがわかる。一方、LDD長が1.5μmを超えてもACストレス寿命はあまり変化せず、ACストレス寿命は飽和する傾向にあることがわかる。また、LDD長が長くなるとON電流が小さくなるという問題があり、LDD長は1.5μm以下に設定することが望ましい。このように、ACストレス寿命とON電流の観点から、LDD長は0.5μm以上1.5μm以下に設定することが望ましいことがわかる。

## 【0104】

実施の形態7 10

ここでは、薄膜トランジスタにおけるソース側のLDD領域におけるチャネル長方向の長さとドレイン側のLDD領域のチャネル長方向の長さとの差について説明する。LDD領域のチャネル長方向の長さが、ソース側とドレイン側とで異なるとON電流に影響を与える。

## 【0105】

ゲートおよびドレインに所定の電圧を印加し、ソースを接地した場合、ソース側のLDD領域による電圧降下によって、ゲート・ソース間にかかる電圧はゲートに印加された電圧よりも低くなる。この電圧降下はソース側のLDD領域の抵抗によるものなので、ソース側のLDD長がドレイン側のLDD領域のLDD長よりも長くなるとドレイン電流も低下することになる。このことから、ソース側のLDD長とドレイン側のLDD長との差は小さい方が好ましい。

## 【0106】

そこで、ソース側のLDD長とドレイン側のLDD長との差の範囲を求めるために、ソース側のLDD長とドレイン側のLDD長との和を一定とし、ソース側のLDD長を変化させた種々の薄膜トランジスタを作製し、その電気的特性を評価した。

## 【0107】

なお、評価に用いた薄膜トランジスタのゲート幅を10μm、ゲート長を5μm、GOLD領域のチャネル長方向の長さを1μm、ゲート電極のチャネル長方向の長さを7μmとした。また、GOLD領域の不純物濃度を $1 \times 10^{18}$ atom/cm<sup>3</sup>とし、LDD領域の不純物濃度を $5 \times 10^{17}$ atom/cm<sup>3</sup>とした。

## 【0108】

なお、薄膜トランジスタの製造方法として、実施の形態2において説明した半導体装置の製造方法では、ゲート電極を形成するためのレジストパターンをマスクとしてイオンを注入することにより、ソース・ドレイン領域となる不純物領域4ad, 4aeを形成したが(図18参照)が、ここでは、次のように形成した。すなわち、ゲート電極を形成した後にレジストパターンを除去して、ソース・ドレイン領域を形成するためのレジストパターンを形成する。次に、そのレジストパターンをマスクとしてイオン注入を行なってソース・ドレイン領域を形成した。その後、レジストパターンを除去して、半導体基板の全面にLDD領域を形成するためのイオン注入を行なうことによってLDD領域を形成した。

## 【0109】

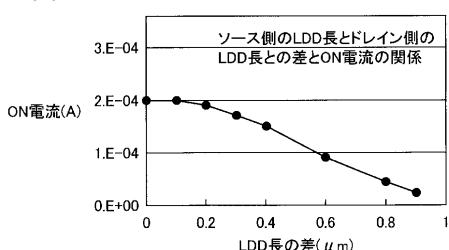

次に、このようにして作製された薄膜トランジスタについて、ON電流を測定した結果について説明する。図33に、ON電流のソース側のLDD長とドレイン側のLDD長との差(LDD長さの差)の依存性のグラフを示す。図33に示すように、LDD長さの差が0.3μmを超えるとON電流が減少する傾向が顕著になって、グラフの傾きが大きくなっていることがわかる。このことから、所定のON電流を確保するにはLDD長さの差は0.3μm以下であることが好ましい。

## 【0110】

実施の形態8

ここでは、p型の薄膜トランジスタを例に挙げる。図34に示すゲート絶縁膜を形成し 50

、薄膜トランジスタのしきい値を制御するための所定の不純物を注入する工程までは、前述した図4に示す工程までと同様である。

【0111】

次に、図35に示すように、所定の写真製版処理を施すことによりゲート絶縁膜5上にレジストパターン62が形成される。そのレジストパターン62をマスクとして、たとえばドーズ量 $1 \times 10^{13}$ atom/cm<sup>2</sup>、加速エネルギー60KeVにてボロンを注入することによりGOLD領域となる不純物領域4ab, 4acが形成される。この注入量がGOLD領域における注入量になる。その後、アッシングと薬液処理を施すことで、レジストパターンが62が除去される。

【0112】

その後、前述した図6および図7に示す工程と同様の工程を経て、レジストパターン63とゲート電極6aが形成される、次に、図36に示すように、レジストパターン63をマスクとして、たとえばドーズ量 $1 \times 10^{15}$ atom/cm<sup>2</sup>、加速エネルギー60KeVにてボロンを注入することによりソース領域およびドレイン領域となる不純物領域4ad, 4aeが形成される。その後、アッシングと薬液処理を施すことで、レジストパターンが63が除去される。

【0113】

次に、図37に示すように、ゲート電極6aをマスクとして、たとえばドーズ量 $5 \times 10^{13}$ atom/cm<sup>2</sup>、加速エネルギー60KeVにてボロンを注入することによりLDD領域となる不純物領域4af, 4agが形成される。これにより、LDD領域となる不純物領域4af, 4agの不純物濃度は、GOLD領域となる不純物領域4ab, 4acの不純物濃度よりも高く、ソース領域およびドレイン領域となる不純物領域4ad, 4aeの不純物濃度よりも低くなる。

【0114】

その後、前述した図9に示す工程と同様の工程を経て、図38に示すように、pチャネル型のGOLD構造の薄膜トランジスタが形成される。

【0115】

次に、上述した薄膜トランジスタについて、ソース・ドレイン耐圧を測定した結果について説明する。測定には、ゲート幅を20μm、実効ゲート長を5μm、GOLD領域41, 42のチャネル長方向の長さを1μm、LDD領域43, 44のチャネル長方向の長さを0.5μm、ゲート電極6aのチャネル長方向の長さを7μmとした薄膜トランジスタを用いた。

【0116】

一方、比較のために、従来のLDD構造の薄膜トランジスタおよびGOLD構造の薄膜トランジスタとして、ゲート幅を20μm、ゲート長を5μm、LDD領域のチャネル長方向の長さを0.5μmとしたLDD構造の薄膜トランジスタと、ゲート幅を20μm、ゲート長を5μm、GOLD領域のチャネル長方向の長さを1μm、ゲート電極のチャネル長方向の長さを7μmとしたGOLD構造の薄膜トランジスタを用いた。

【0117】

図39にソース・ドレイン耐圧の測定結果を示す。なお、測定条件等は前述した条件と同様である。図39に示すように、実施の形態8に係るGOLD構造の薄膜トランジスタのソース・ドレイン耐圧は、従来のGOLD構造の薄膜トランジスタとLDD構造の薄膜トランジスタよりも高いソース・ドレイン耐圧を達成できることが確認された。

【0118】

次に、ON電流を測定した結果について説明する。なお、測定条件は前述した条件と同様である。ON電流の測定結果を図40に示す。図40に示すように、実施の形態8に係るGOLD構造の薄膜トランジスタでは、LDD領域として同じ長さを有する従来のLDD構造の薄膜トランジスタのON電流とほぼ同じON電流が得られることが確認された。

【0119】

次に、OFF電流を測定した結果について説明する。なお、測定条件は前述した条件と

10

20

30

40

50

同様である。OFF電流の測定結果を図41に示す。図41に示すように、実施の形態8に係るGOLD構造の薄膜トランジスタでは、従来のGOLD構造の薄膜トランジスタのOFF電流よりも低いOFF電流が得られることが確認された。

#### 【0120】

次に、半導体装置においてGOLD領域の不純物濃度がLDD領域の不純物濃度よりも低い場合における、GOLD領域の不純物濃度の範囲、GOLD領域のチャネル長方向の長さ、LDD領域の不純物濃度の範囲、LDD領域のチャネル長方向の長さ、ソース側とドレイン側のLDD領域のチャネル長方向の長さの差について、実施の形態9～13において詳しく説明する。

#### 【0121】

実施の形態9

ここでは、薄膜トランジスタにおけるGOLD領域の不純物濃度について説明する。不純物濃度の範囲を求めるために、GOLD領域の不純物濃度を変化させた種々の薄膜トランジスタを作製してその電気的特性を評価した。その薄膜トランジスタのゲート幅を10μm、ゲート長を5μm、GOLD領域のチャネル長方向の長さを1μm、LDD領域のチャネル長方向の長さを0.5μm、ゲート電極のチャネル長方向の長さを7μmとして、実施の形態1において説明した方法と同様の方法により作製した。

#### 【0122】

また、LDD領域を形成するための不純物イオンの注入条件をドーズ量 $1 \times 10^{13}$ atom/cm<sup>2</sup>、加速エネルギー80KeVとした。GOLD領域およびLDD領域のそれぞれの不純物濃度は、実施の形態1において説明したようにSIMS測定を行なうことによって得られた、不純物イオンの注入量と不純物濃度との関係に基づいて見積もられる。

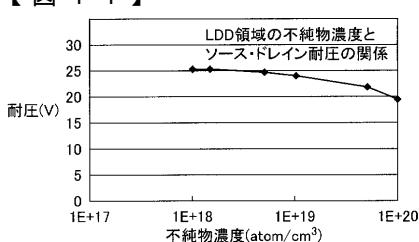

#### 【0123】

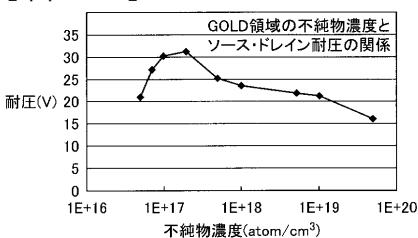

図42にソース・ドレイン耐圧のGOLD領域の不純物濃度依存性のグラフを示す。図42に示すように、GOLD領域の不純物濃度が $1 \times 10^{19}$ atom/cm<sup>3</sup>より高くなると、ソース・ドレイン耐圧が低下し従来のGOLD構造の薄膜トランジスタにおけるソース・ドレイン耐圧よりも低くなることがわかる。

#### 【0124】

このことから、GOLD領域の不純物濃度としては $1 \times 10^{19}$ atom/cm<sup>3</sup>以下に設定することが好ましく、より安定した耐圧を確保するためには、 $1 \times 10^{17}$ atom/cm<sup>3</sup>以上 $1 \times 10^{18}$ atom/cm<sup>3</sup>以下に設定することがさらに好ましい。

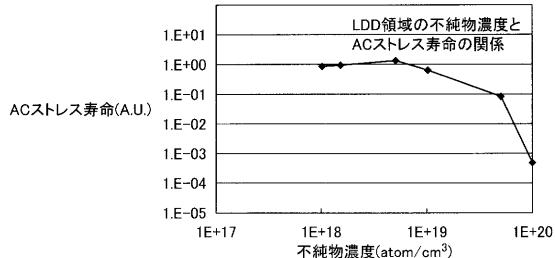

#### 【0125】

次に、図43にACストレス寿命のGOLD領域の不純物濃度依存性のグラフを示す。図43に示すように、GOLD領域の不純物濃度として、 $1 \times 10^{17}$ atom/cm<sup>3</sup>以上 $1 \times 10^{19}$ atom/cm<sup>3</sup>以下の範囲では比較的良好なACストレス寿命を得られることがわかる。そして、 $5 \times 10^{17}$ atom/cm<sup>3</sup>以上 $1 \times 10^{18}$ atom/cm<sup>3</sup>以下の範囲ではさらに良好なACストレス寿命を得られることがわかる。

#### 【0126】

このように、ソース・ドレイン耐圧およびACストレス寿命の観点から、GOLD領域の不純物濃度として、 $1 \times 10^{17}$ atom/cm<sup>3</sup>以上 $1 \times 10^{19}$ atom/cm<sup>3</sup>以下に設定することが好ましいことがわかった。

#### 【0127】

実施の形態10

ここでは、薄膜トランジスタにおけるLDD領域の不純物濃度について説明する。不純物濃度の範囲を求めるために、LDD領域の不純物濃度を変化させた種々の薄膜トランジスタを作製してその電気的特性を評価した。その薄膜トランジスタのゲート幅を10μm、ゲート長を5μm、GOLD領域のチャネル長方向の長さを1μm、LDD領域のチャネル長方向の長さを0.5μm、ゲート電極のチャネル長方向の長さを7μmとして、実施の形態1において説明した方法と同様の方法により作製した。

#### 【0128】

10

20

30

40

50

また、GOLD領域を形成するための不純物イオンの注入条件をドーズ量  $5 \times 10^{12}$  atom / cm<sup>2</sup>、加速エネルギー 80 KeV とした。GOLD領域およびLDD領域のそれぞれの不純物濃度は、実施の形態1において説明したように SIMS 測定を行なうことによって得られた、不純物イオンの注入量と不純物濃度との関係に基づいて見積もられる。

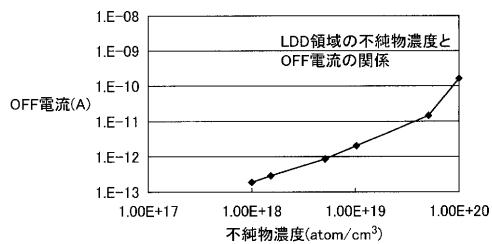

#### 【0129】

図44にソース・ドレイン耐圧のLDD領域の不純物濃度依存性のグラフを示す。図44に示すように、LDD領域の不純物濃度が  $5 \times 10^{19}$  atom / cm<sup>3</sup> より高くなると、ソース・ドレイン耐圧が低くなることがわかる。

#### 【0130】

このようにソース・ドレイン耐圧の観点から、LDD領域の不純物濃度としては  $5 \times 10^{19}$  atom / cm<sup>3</sup> 以下に設定することが好ましく、より安定した耐圧を確保するためには、 $1 \times 10^{19}$  atom / cm<sup>3</sup> 以下に設定することがさらに好ましい。

#### 【0131】

次に、図45にACストレス寿命のLDD領域の不純物濃度依存性のグラフを示す。図45に示すように、LDD領域の不純物濃度として、 $5 \times 10^{19}$  atom / cm<sup>3</sup> 以下では比較的良好なACストレス寿命を得られることがわかる。そして、 $1 \times 10^{19}$  atom / cm<sup>3</sup> ではさらに良好なACストレス寿命を得られることがわかる。

#### 【0132】

次に、図46にOFF電流のLDD領域の不純物濃度依存性のグラフを示す。図46に示すように、OFF電流はLDD領域の不純物濃度が増加するにしたがって増加しており、OFF電流を低減する観点からLDD領域の不純物濃度は低い方が好ましい。以上のことから、LDD領域の不純物濃度としては  $5 \times 10^{19}$  atom / cm<sup>3</sup> 以下に設定することが好ましい。

#### 【0133】

##### 実施の形態11

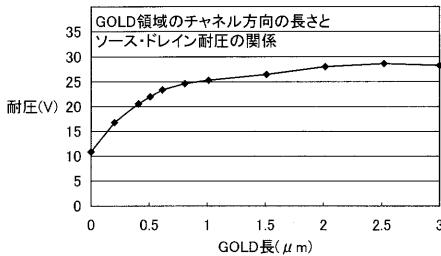

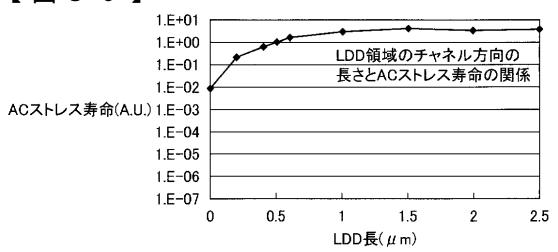

ここでは、薄膜トランジスタにおけるGOLD領域のチャネル長方向の長さについて説明する。GOLD領域のチャネル長方向の長さ（GOLD長）の範囲を求めるために、GOLD長を変化させた種々の薄膜トランジスタを作製してその電気的特性を評価した。

#### 【0134】

その薄膜トランジスタのゲート幅を  $10 \mu m$ 、ゲート長を  $5 \mu m$ 、LDD領域のチャネル長方向の長さを  $0.5 \mu m$  とし、また、ゲート電極のチャネル長方向の長さをGOLD領域のチャネル長方向の長さに応じて変化させ、実施の形態1において説明した方法と同様の方法により作製した。なお、GOLD領域の不純物濃度を  $5 \times 10^{17}$  atom / cm<sup>3</sup> とし、LDD領域の不純物濃度を  $1.5 \times 10^{18}$  atom / cm<sup>3</sup> とした。

#### 【0135】

図47にソース・ドレイン耐圧のGOLD長依存性のグラフを示す。図47に示すように、GOLD長が  $0.5 \mu m$  より短くなるとソース・ドレイン耐圧が急峻に低下することがわかる。一方、GOLD長が  $2 \mu m$  を超えてもソース・ドレイン耐圧はあまり変化せず、ソース・ドレイン耐圧は飽和する傾向にあることがわかる。

#### 【0136】

次に、図48にACストレス寿命のGOLD長依存性のグラフを示す。図48に示すように、GOLD長が  $0.5 \mu m$  よりも短くなると、ACストレス寿命が急激に短くなることがわかる。一方、GOLD長が  $2 \mu m$  を超えてもACストレス寿命はあまり変化せず、ACストレス寿命は飽和する傾向にあることがわかる。

#### 【0137】

このように、ソース・ドレイン耐圧およびACストレスの観点からは、GOLD長を  $0.5 \mu m$  以上に設定することが好ましい。一方、GOLD長が  $2 \mu m$  を超えると、ソース・ドレイン耐圧およびACストレス寿命はいずれも飽和する傾向にある。また、GOLD長が  $2 \mu m$  を超えると薄膜トランジスタのサイズが大きくなつて占有面積が増加してしまい、半導体装置の小型化を阻害する要因になつてしまつ。以上のことから、GOLD長と

しては  $0.5 \mu m$  以上  $2 \mu m$  以下に設定することが好ましい。

【0138】

実施の形態 1 2

ここでは、薄膜トランジスタにおける LDD 領域のチャネル長方向の長さについて説明する。LDD 領域のチャネル長方向の長さ (LDD 長) の範囲を求めるために、LDD 長を変化させた種々の薄膜トランジスタを作製してその電気的特性を評価した。

【0139】

その薄膜トランジスタのゲート幅を  $10 \mu m$ 、ゲート長を  $5 \mu m$ 、GOLD 領域のチャネル長方向の長さを  $1 \mu m$ 、ゲート電極のチャネル長方向の長さを  $7 \mu m$  として、実施の形態 1 において説明した方法と同様の方法により作製した。なお、GOLD 領域の不純物濃度を  $5 \times 10^{17} \text{ atom/cm}^3$  とし、LDD 領域の不純物濃度を  $1.5 \times 10^{18} \text{ atom/cm}^3$  とした。

【0140】

図 49 にソース・ドレイン耐圧の LDD 長依存性のグラフを示す。図 49 に示すように、LDD 長が  $0.5 \mu m$  よりも短くなるとソース・ドレイン耐圧は下がる傾向にあることがわかる。一方、LDD 長が  $1.5 \mu m$  を超えてもソース・ドレイン耐圧はあまり変化せず、ソース・ドレイン耐圧は飽和する傾向にあることがわかる。

【0141】

次に、図 50 に AC ストレス寿命の LDD 長依存性のグラフを示す。図 50 に示すように、LDD 長が  $0.5 \mu m$  よりも短くなると、AC ストレス寿命は短くなる傾向にあることがわかる。一方、LDD 長が  $1.5 \mu m$  を超えても AC ストレス寿命はあまり変化せず、AC ストレス寿命は飽和する傾向にあることがわかる。

【0142】

次に、図 51 に OFF 電流の LDD 長依存性のグラフを示す。図 51 に示すように、LDD 長が  $0.5 \mu m$  よりも短くなると OFF 電流が増加する傾向にあることがわかる。一方、LDD 長が長くなるにしたがって、OFF 電流は徐々に減少する傾向にあることがわかる。

【0143】

次に、図 52 に ON 電流の LDD 長依存性のグラフを示す。図 52 に示すように、LDD 長が長くなるにしたがって、ON 電流は徐々に減少する傾向にあることがわかる。OFF 電流の傾向を踏まえると、所定の ON 電流を確保して OFF 電流を抑えるには、LDD 長として  $1.5 \mu m$  以下に設定することが好ましい。

【0144】

このように、ソース・ドレイン耐圧、AC ストレス寿命および OFF 電流の観点からは、LDD 長としては  $0.5 \mu m$  以上に設定することが好ましい。一方、ON 電流および OFF 電流の観点からは、LDD 長としては  $1.5 \mu m$  以下に設定することが好ましい。以上のことから、LDD 長としては  $0.5 \mu m$  以上  $1.5 \mu m$  以下に設定することが好ましい。

【0145】

実施の形態 1 3

ここでは、薄膜トランジスタにおけるソース側の LDD 領域におけるチャネル長方向の長さとドレイン側の LDD 領域のチャネル長方向の長さとの差について説明する。LDD 領域のチャネル長方向の長さが、ソース側とドレイン側とで異なると ON 電流に影響を与える。

【0146】

ゲートおよびドレインに所定の電圧を印加し、ソースを接地した場合、ソース側の LD 領域による電圧降下によって、ゲート・ソース間にかかる電圧はゲートに印加された電圧よりも低くなる。この電圧降下はソース側の LDD 領域の抵抗によるものなので、ソース側の LDD 長がドレイン側の LDD 領域の LDD 長よりも長くなるとドレイン電流も低下することになる。このことから、ソース側の LDD 長とドレイン側の LDD 長との差は

10

20

30

40

50

小さい方が好ましい。

【0147】

そこで、ソース側のLDD長とドレイン側のLDD長との差の範囲を求めるために、ソース側のLDD長とドレイン側のLDD長との和を一定とし、ソース側のLDD長を変化させた種々の薄膜トランジスタを以下に示す手順によって作製し、その電気的特性を評価した。

【0148】

なお、その薄膜トランジスタのゲート幅を10μm、ゲート長を5μm、GOLD領域のチャネル長方向の長さを1μm、ゲート電極のチャネル長方向の長さを7μmとした。また、GOLD領域の不純物濃度を $5 \times 10^{17}$ atom/cm<sup>3</sup>とし、LDD領域の不純物濃度を $1.5 \times 10^{18}$ atom/cm<sup>3</sup>とした。

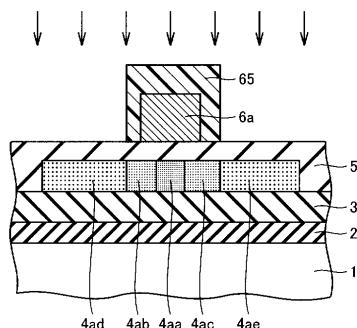

【0149】

まず、実施の形態1において説明した図2～図7に示す工程と同様の工程を経て、図53に示すように、レジストパターン63をマスクとしてゲート電極6aが形成される。その後、レジストパターン63をマスクとしてソース領域およびドレイン領域を形成するためのイオン注入を行なうことなくレジストパターン63が除去される。

【0150】

次に、図54に示すように、あらためてソース領域およびドレイン領域を形成するためのレジストパターン65が形成される。そのレジストパターン65は、ソース側のLDD長(L1)とドレイン側のLDD長(L2)との和が1μmとなり(図55参照)、ソース側のLDD長が0.5μmから0.05μmまで0.05μm刻みで変化するLDD領域が形成されるようにパターニングされる。

【0151】

そのレジストパターン65をマスクとして、リンを注入することによりソース領域およびドレイン領域となる不純物領域4ad, 4aeが形成される。その後、レジストパターン65が除去される。次に、図55に示すように、ゲート電極6aをマスクとして、リンを注入することによりLDD領域となる不純物領域4af, 4agが形成される。

【0152】

このようにして、ソース側のLDD領域となる不純物領域4afのLDD長L1と、ドレイン側のLDD領域となる不純物領域4agのLDD長L2との和が1μmとされ、不純物領域4afのLDD長が0.5μmから0.05μmまで0.05μm刻みで変化する評価用の薄膜トランジスタがそれぞれ形成される。

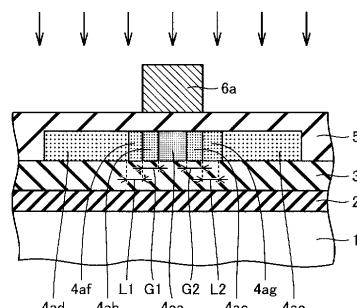

【0153】

次に、このようにして作製された薄膜トランジスタについて、ON電流を測定した結果について説明する。なお、測定条件は前述した条件と同様である。ON電流の測定結果として、図56にON電流のソース側のLDD長とドレイン側のLDD長との差(LDD長さの差)の依存性のグラフを示す。図56に示すように、LDD長さの差が0.3μmを超えるとON電流が減少する傾向が顕著になって、グラフの傾きが大きくなっていることがわかる。このことから、所定のON電流を確保するにはLDD長さの差は0.3μm以下であることが好ましい。

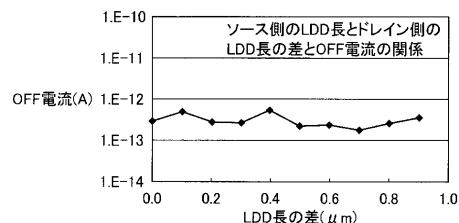

【0154】

次に、図57にOFF電流のLDD長さの差の依存性のグラフを示す。図57に示すように、OFF電流はLDD長さの差にはほとんど依存しないことがわかる。以上のことから、LDD長さの差としては0.3μm以下に設定することが好ましい。

【0155】

実施の形態14

ここでは、薄膜トランジスタとして2本のゲート電極を備えた薄膜トランジスタを例に挙げる。2本のゲート電極を備えることによって実質的に2つの薄膜トランジスタが形成されていることになるが、一方の薄膜トランジスタのドレインと他方の薄膜トランジスタのソースとを電気的に接続させるとともに、一方と他方のゲート電極を電気的に接続する

10

20

30

40

50

ことで、機能的には 1 つの薄膜トランジスタの場合と同じ機能を果たすことになる。

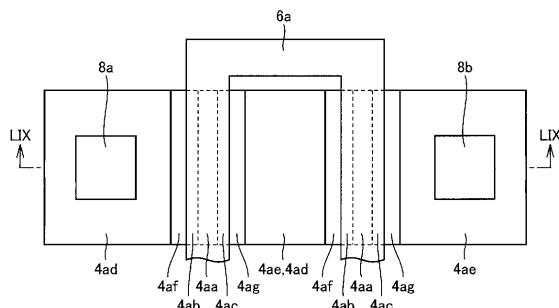

【 0 1 5 6 】

構造的には、たとえば図 1 に示される薄膜トランジスタ T が、1 つのアイランド状の多結晶シリコン膜において 2 つ形成されていることになる。すなわち、図 5 8 および図 5 9 に示すように、ソース領域となる不純物領域 4 a d 、ドレイン領域となる不純物領域 4 a e 、 L D D 領域となる不純物領域 4 a f , 4 a g 、 G O L D 領域となる不純物領域 4 a b , 4 a c 、チャネル領域となる不純物領域 4 a a およびゲート電極 6 a を含む 1 つの薄膜トランジスタ T が 2 組形成されている。これ以外の構造については、図 1 に示す構造と同様なので同一部材には同一符号を付しその説明を省略する。

【 0 1 5 7 】

なお、上述した薄膜トランジスタは、ゲート電極に対応する部分のパターンを変更するだけで、実施の形態 1 において説明した製造方法と同様の製造方法によって製造することができる。

【 0 1 5 8 】

次に、上述した薄膜トランジスタについて、O F F 電流を測定した結果について説明する。測定には、ゲート幅を  $10 \mu m$  、それぞれのゲート電極のゲート長を  $5 \mu m$  、 G O L D 領域 4 1 , 4 2 のチャネル長方向の長さを  $1 \mu m$  、 L D D 領域 4 3 , 4 4 のチャネル長方向の長さを  $0.5 \mu m$  、それぞれのゲート電極のチャネル長方向の長さを  $7 \mu m$  とした薄膜トランジスタを用いた。なお、 G O L D 領域の不純物濃度を  $5 \times 10^{17} \text{ atom/cm}^3$  とし、 L D D 領域の不純物濃度を  $1.5 \times 10^{18} \text{ atom/cm}^3$  とした。

【 0 1 5 9 】

図 6 0 に O F F 電流の測定結果を示す。図 6 0 に示すように、実施の形態 1 4 に係る薄膜トランジスタでは、実施の形態 1 において説明した薄膜トランジスタと比べると、O F F 電流をさらに低減できることがわかった。O F F 電流の他、ソース・ドレイン耐圧および A C ストレス寿命についても実施の形態 1 において説明した薄膜トランジスタと同レベルを達成できることがわかった。

【 0 1 6 0 】

なお、上述した薄膜トランジスタではゲート電極 6 a が 2 本の場合を例に挙げたが、これに限られるものではなく、薄膜トランジスタが形成される領域において、許容されるサイズのもとでゲート電極の数を増やすことで、O F F 電流のさらなる低減を図ることができる。

【 0 1 6 1 】

実施の形態 1 5

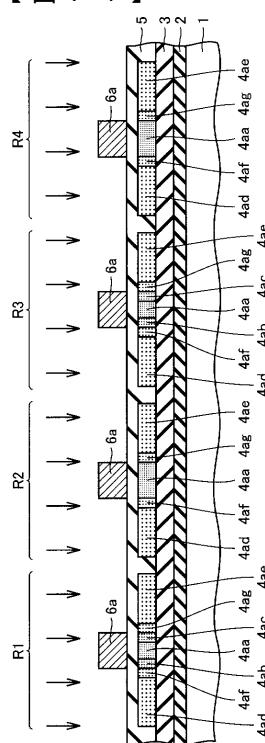

ここでは、 G O L D 構造の薄膜トランジスタ、 L D D 構造の薄膜トランジスタおよび通常の薄膜トランジスタを備えた半導体装置の一例を挙げる。まず、その製造方法について説明する。

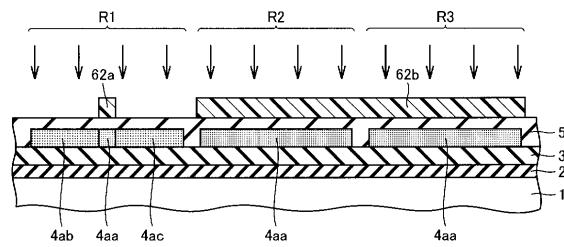

【 0 1 6 2 】

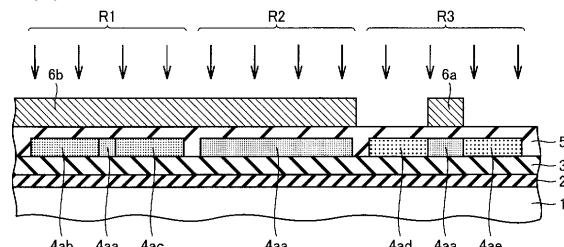

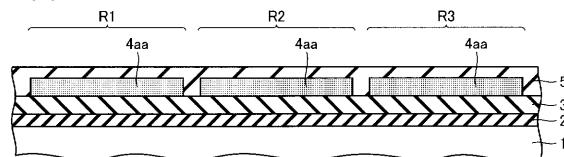

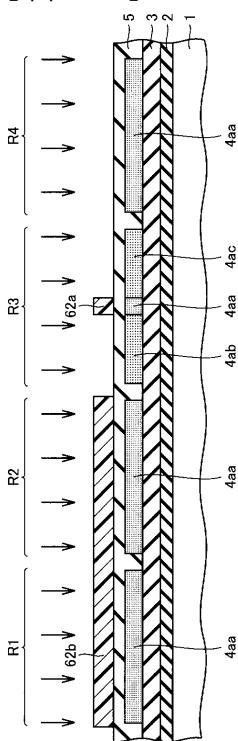

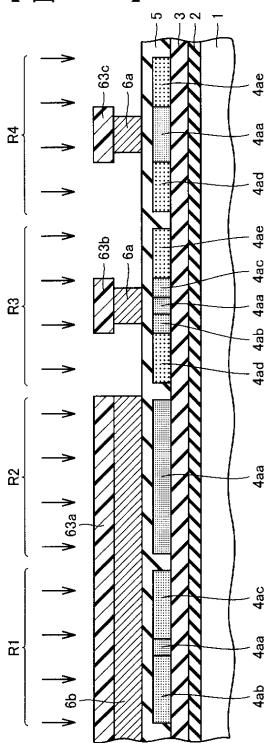

まず、実施の形態 1 において説明した方法と同様の方法によって、図 6 1 に示すように、ガラス基板 1 上にシリコン窒化膜 2 およびシリコン酸化膜 3 が形成される。ガラス基板 1 において薄膜トランジスタが形成される所定の領域 R 1 ~ R 3 に位置するシリコン酸化膜 2 上に、それぞれアイランド状の多結晶シリコン膜が形成される。領域 R 1 ~ R 3 では、それぞれ種類の異なる薄膜トランジスタが形成されることになる。

【 0 1 6 3 】

その多結晶シリコン膜を覆うように、シリコン酸化膜からなるゲート絶縁膜 5 が形成される。次に、薄膜トランジスタのしきい値を制御するために、たとえばドーズ量  $1 \times 10^{12} \text{ atom/cm}^2$  、 加速エネルギー  $60 \text{ keV}$  にて多結晶シリコン膜にボロンが注入されて、アイランド状の不純物領域 4 a a が形成される。

【 0 1 6 4 】

次に、図 6 2 に示すように、所定の写真製版処理を施すことにより領域 R 1 では n 型 G O L D 構造の薄膜トランジスタを形成するためのレジストパターン 6 2 a が形成されると

10

20

30

40

50

ともに、n型LDD構造の薄膜トランジスタが形成される領域R2および通常のp型薄膜トランジスタが形成される領域R3では、これらの領域R2, R3を覆うレジストパターン62bが形成される。

【0165】

そのレジストパターン62a, 62bをマスクとして、たとえばドーズ量 $5 \times 10^{12}$ atom/cm<sup>2</sup>、加速エネルギー80KeVにて不純物領域4aaにリンを注入することにより、領域R1に不純物領域4ab, 4acが形成される。この注入量がGOLD領域における注入量になる。その後、アッシングと薬液処理を施すことで、レジストパターン62a, 62bが除去される。

【0166】

次に、スパッタ法によりゲート絶縁膜5の全面に膜厚約400nmのクロム膜(図示せず)が形成される。次に、所定の写真製版処理を施すことにより領域R3ではゲート電極をパターニングするためのレジストパターン63bが形成されるとともに、領域R1および領域R2では、これを覆うレジストパターン63aが形成される(図63参照)。

【0167】

次に、図63に示すように、そのレジストパターン63a, 63bをマスクとしてクロム膜にウエットエッチングを施すことにより、領域R3ではゲート電極6aが形成される。また、領域R1および領域R2ではこれを覆うクロム膜6bが残される。その後、アッシングと薬液処理を施すことで、レジストパターン63a, 63bが除去される。

【0168】

次に、図64に示すように、残されたクロム膜6bとゲート電極6aをマスクとして、たとえばドーズ量 $1 \times 10^{15}$ atom/cm<sup>2</sup>、加速エネルギー60KeVにてボロンを注入することにより、領域3に位置する不純物領域4aaにはp型の薄膜トランジスタのソース領域およびドレイン領域となる不純物領域4ad, 4aeが形成される。このとき、領域R1および領域R2はクロム膜6bによって覆われているため、これらの領域R1, R2にはボロンは注入されない。

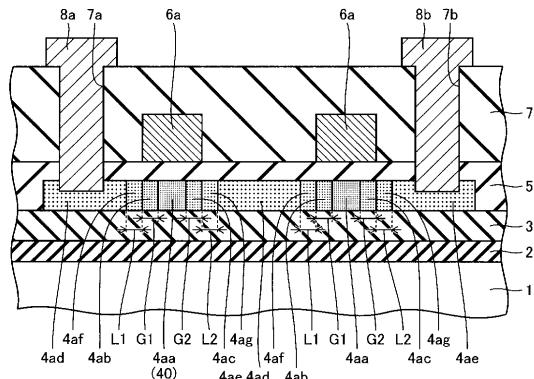

【0169】

次に、所定の写真製版処理を施すことにより領域R1、領域R2ではゲート電極をパターニングするためのレジストパターン66a, 66bがそれぞれ形成されるとともに、領域R3では、この領域R3を覆うレジストパターン66cが形成される(図65参照)。

【0170】

このとき、領域R1におけるレジストパターン66aは、不純物領域4ab, 4acと平面的にオーバラップするように形成される。このレジストパターン66aと不純物領域4ab, 4acとが平面的にオーバラップする部分がGOLD領域となる。

【0171】

次に、図65に示すように、レジストパターン66a, 66b, 66cをマスクとしてクロム膜6bにエッチングを施すことにより、領域R1および領域R2ではゲート電極6aがそれぞれ形成される。このとき、領域R1に形成されるゲート電極6aは、不純物領域4ab, 4acと平面的にオーバラップするように形成される。また、領域R3に形成されたゲート電極6aはレジストパターン66cによって覆われているため、このゲート電極6aにエッチングが施されることはない。

【0172】

なお、ウエットエッチングを施すことで、ゲート電極となるクロム膜の側面にはエッチングが施されることになるが、そのエッチングされる量はオーバエッチングを施す時間によって制御することができる。

【0173】

次に、そのレジストパターン66a, 66b, 66cを残した状態で、そのレジストパターン66a, 66b, 66cをマスクとして、たとえばドーズ量 $1 \times 10^{14}$ atom/cm<sup>2</sup>、加速エネルギー80KeVにてリンを注入することにより、領域R1に位置する不純物領域4ab, 4acに、n型GOLD構造の薄膜トランジスタのソース領域となる不

10

20

30

40

50

純物領域 4 a d およびドレイン領域となる不純物領域 4 a e がそれぞれ形成される。

【 0 1 7 4 】

また、領域 R 2 に位置する不純物領域 4 a a に、n 型 L D D 構造の薄膜トランジスタのソース領域となる不純物領域 4 a d およびドレイン領域となる不純物領域 4 a e がそれぞれ形成される。なお、領域 R 3 はレジストパターン 6 6 c によって覆われているため、領域 R 3 にはリンは注入されない。その後、アッシングと薬液処理を施すことで、レジストパターン 6 6 a , 6 6 b , 6 6 c が除去される。

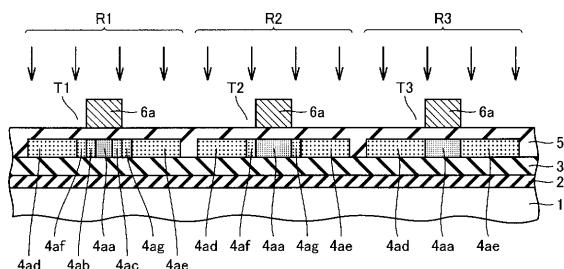

【 0 1 7 5 】

次に、図 6 6 に示すように、ゲート電極 6 a をマスクとして、たとえばドーズ量  $1 \times 10^{13}$  atom / cm<sup>2</sup>、加速エネルギー 80 KeV にてリンを注入することにより、領域 R 1 に位置する残された不純物領域 4 a b , 4 a c の部分には、n 型 G O L D 構造の薄膜トランジスタのソース側の L D D 領域となる不純物領域 4 a f およびドレイン側の L D D 領域となる不純物領域 4 a g がそれぞれ形成される。

【 0 1 7 6 】

また、領域 R 2 に位置する残された不純物領域 4 a a の部分には、n 型 L D D 構造の薄膜トランジスタのソース側の L D D 領域となる不純物領域 4 a f およびドレイン側の L D D 領域となる不純物領域 4 a g がそれぞれ形成される。

【 0 1 7 7 】

なお、このとき、領域 3 に位置する p 型の薄膜トランジスタのソース領域およびドレイン領域となるボロンが注入された不純物領域 4 a d , 4 a e にもリンが注入されることになるが、リンの注入量はボロンの注入量に比べて十分に小さいため、領域 3 に位置する不純物領域 4 a d , 4 a e へのリンの注入は問題にならない。

【 0 1 7 8 】

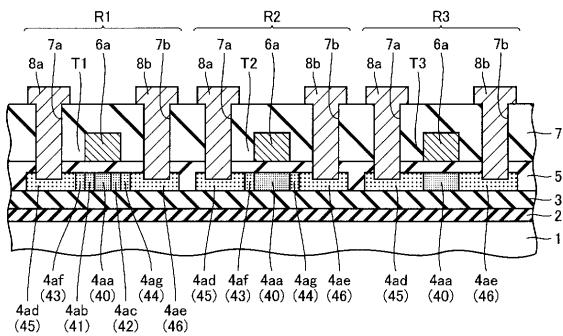

その後、実施の形態 1 において説明した方法と同様の方法によって、図 6 7 に示すように、ガラス基板 1 上にシリコン酸化膜からなる層間絶縁膜 7 が形成される。次に、その層間絶縁膜 7 上に所定の写真製版処理を施すことにより、コンタクトホールを形成するためのレジストパターン（図示せず）が形成される。

【 0 1 7 9 】

そのレジストパターンをマスクとして、層間絶縁膜 7 およびゲート絶縁膜 5 に異方性エッチングを施すことにより、領域 R 1 ~ R 3 にそれぞれ位置する不純物領域 4 a d の表面を露出するコンタクトホール 7 a と、不純物領域 4 a e の表面を露出するコンタクトホール 7 b とがそれぞれ形成される。

【 0 1 8 0 】

次に、コンタクトホール 7 a , 7 b を充填するように、層間絶縁膜 7 上にクロム膜とアルミニウム膜との積層膜（図示せず）が形成される。その積層膜上に所定の写真製版処理を施すことにより、電極を形成するためのレジストパターン（図示せず）が形成される。そのレジストパターンをマスクとしてウエットエッチングを施すことにより、領域 R 1 ~ R 3 のそれぞれにおいてソース電極 8 a とドレイン電極 8 b が形成される。

【 0 1 8 1 】

以上のようにして、領域 R 1 では n 型 G O L D 構造の薄膜トランジスタ T 1 が形成され、領域 R 2 では n 型 L D D 構造の薄膜トランジスタ T 2 が形成され、領域 R 3 では通常の p 型の薄膜トランジスタ T 3 が形成される。

【 0 1 8 2 】

n 型 G O L D 構造の薄膜トランジスタ T 1 では、不純物領域 4 a d がソース領域 4 5 となり、不純物領域 4 a e がドレイン領域 4 6 となり、不純物領域 4 a b , 4 a c が G O L D 領域 4 1 , 4 2 となり、不純物領域 4 a f , 4 a g が L D D 領域 4 3 , 4 4 となる。

【 0 1 8 3 】

また、n 型 L D D 構造の薄膜トランジスタ T 2 では、不純物領域 4 a d がソース領域 4 5 となり、不純物領域 4 a e がドレイン領域 4 6 となり、不純物領域 4 a f , 4 a g が L D D 領域 4 3 , 4 4 となる。そして、p 型の薄膜トランジスタ T 3 では、不純物領域 4 a

10

20

30

40

50

d がソース領域 4 5 となり、不純物領域 4 a e がドレイン領域 4 6 となる。

【0184】

上述した製造方法では、実施の形態 1 において説明した効果に加えて次のような効果が得られる。まず、従来の方法では、n 型 G O L D 構造の薄膜トランジスタと通常の p 型の薄膜トランジスタを形成しようとすると、p 型の薄膜トランジスタのソース領域およびドレイン領域に高濃度の n 型の不純物が注入されてしまう。そのため、p 型の薄膜トランジスタのソース領域およびドレイン領域の抵抗が大きくなってしまうという問題があった。

【0185】

これに対して、上述した方法では、p 型の薄膜トランジスタのソース領域およびドレイン領域が形成された後、n 型 G O L D 構造の薄膜トランジスタおよび n 型 L D D 構造の薄膜トランジスタのそれぞれのソース領域およびドレイン領域を形成する際に、注入マスクとなるレジストパターンは p 型の薄膜トランジスタの領域を覆うように形成される。

【0186】

これにより、p 型の薄膜トランジスタのソース領域およびドレイン領域に高濃度の n 型の不純物が注入されなくなつて、p 型の薄膜トランジスタのソース領域およびドレイン領域の抵抗が大きくなるという問題を回避することができる。

【0187】

また、従来の方法では、たとえば仕様の変更によって G O L D 領域の長さを変更する必要が生じた場合には、マスクパターンの変更に加えてゲート電極をテーパ状に形成するためのプロセス条件も変更する必要があった。つまり、ゲート電極をテーパ状にするプロセス条件は、エッチング反応と反応生成物の堆積反応とを調整する必要があり、また、これらの反応はパターンやエッチング面積によって大きく変動するため、マスクパターンを変更すると、それに合わせて最適なプロセス条件をあらためて設定する必要があった。

【0188】

これに対して、上述した方法では、マスクのパターンの変更だけで G O L D 長の変更に対応できるため、短時間に所望の半導体装置を開発することが可能になる。

【0189】

なお、上述した方法では、p 型の薄膜トランジスタとしてシングルドレイン構造の薄膜トランジスタを例に挙げたが、p 型薄膜トランジスタのゲート電極を形成した後に、レジストパターンを除去せずにソース領域およびドレイン領域の不純物注入を行ない、その後レジストパターンを除去して L D D 領域を形成するための不純物のイオン注入を行なつて、L D D 構造の p 型の薄膜トランジスタを形成することができる。

【0190】

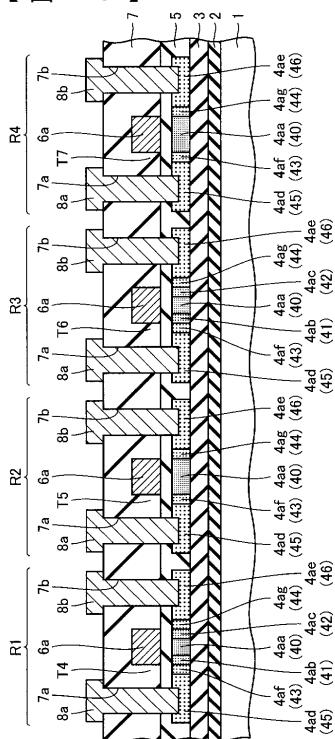

実施の形態 1 6

ここでは、G O L D 構造の薄膜トランジスタ、L D D 構造の薄膜トランジスタおよび通常の薄膜トランジスタを備えた半導体装置の他の例として、前述した n 型 G O L D 構造の薄膜トランジスタに加えて p 型 G O L D 構造の薄膜トランジスタを備えた半導体装置を例に挙げる。まず、その製造方法について説明する。

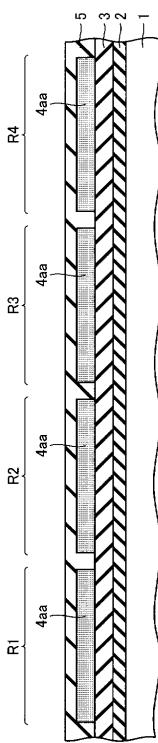

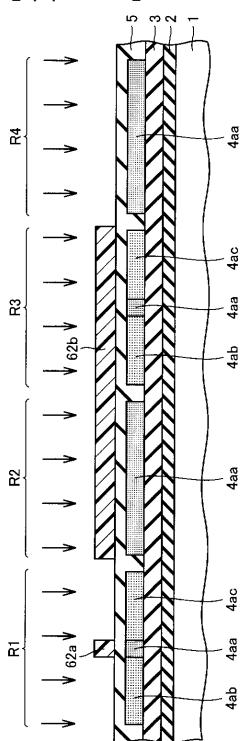

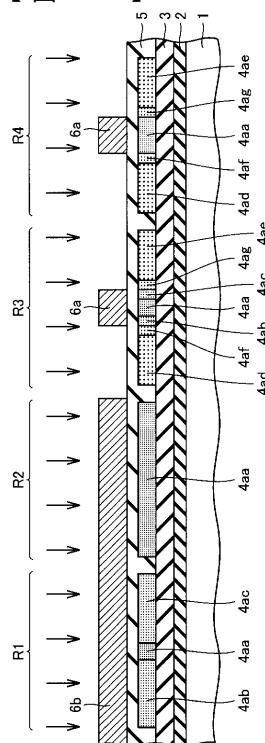

【0191】

まず、実施の形態 1 において説明した方法と同様の方法によって、図 6 8 に示すように、ガラス基板 1 上にシリコン窒化膜 2 およびシリコン酸化膜 3 が形成される。ガラス基板 1 において薄膜トランジスタが形成される所定の領域 R 1 ~ R 4 に位置するシリコン酸化膜 2 上に、それぞれアイランド状の多結晶シリコン膜が形成される。領域 R 1 ~ R 4 では、それぞれ種類の異なる薄膜トランジスタが形成されることになる。

【0192】

その多結晶シリコン膜を覆うように、シリコン酸化膜からなるゲート絶縁膜 5 が形成される。次に、薄膜トランジスタのしきい値を制御するために、たとえばドーズ量  $1 \times 10^{12}$  a t o m / cm<sup>2</sup>、加速エネルギー 60 KeV にて多結晶シリコン膜にボロンが注入されて、アイランド状の不純物領域 4 a a が形成される。

【0193】

10

20

30

40

50

次に、図69に示すように、所定の写真製版処理を施すことにより領域R3では、p型GOLD構造の薄膜トランジスタを形成するためのレジストパターン62aが形成されるとともに、n型GOLD構造の薄膜トランジスタが形成される領域R1およびn型LDD構造の薄膜トランジスタが形成される領域R2では、これらの領域R1, R2を覆うレジストパターン62bが形成される。また、p型LDD構造の薄膜トランジスタが形成される領域R4では、特に、レジストパターンは形成されない。

## 【0194】

そのレジストパターン62a, 62bをマスクとして、たとえばドーズ量 $1 \times 10^{13}$ atom/cm<sup>2</sup>、加速エネルギー60KeVにて不純物領域4aaにボロンを注入することにより、領域R3に不純物領域4ab, 4acが形成される。この注入量がp型の薄膜トランジスタのGOLD領域における注入量になる。その後、アッシングと薬液処理を施すことで、レジストパターン62a, 62bが除去される。

## 【0195】

次に、図70に示すように、所定の写真製版処理を施すことにより領域R1では、n型GOLD構造の薄膜トランジスタを形成するためのレジストパターン62aが形成されるとともに、n型LDD構造の薄膜トランジスタが形成される領域R2およびp型GOLD構造の薄膜トランジスタが形成される領域R3では、これらの領域R2, R3を覆うレジストパターン62bが形成される。また、p型LDD構造の薄膜トランジスタが形成される領域R4では、特に、レジストパターンは形成されない。

## 【0196】

そのレジストパターン62a, 62bをマスクとして、たとえばドーズ量 $5 \times 10^{12}$ atom/cm<sup>2</sup>、加速エネルギー80KeVにて不純物領域4aaにリンを注入することにより、領域R1に不純物領域4ab, 4acが形成される。この注入量がn型の薄膜トランジスタのGOLD領域における注入量になる。その後、アッシングと薬液処理を施すことで、レジストパターン62a, 62bが除去される。

## 【0197】

次に、スパッタ法によりゲート絶縁膜5の全面に膜厚約400nmのクロム膜(図示せず)が形成される。次に、所定の写真製版処理を施すことにより領域R3, R4では、ゲート電極をパターニングするためのレジストパターン63b, 63cが形成されるとともに、領域R1および領域R2では、これを覆うレジストパターン63aが形成される(図71参照)。

## 【0198】

次に、図71に示すように、そのレジストパターン63a, 63b, 63cをマスクとしてクロム膜にウエットエッチングを施すことにより、領域R3, R4ではゲート電極6aがそれぞれ形成される。また、領域R1および領域R2ではこれを覆うクロム膜6bが残される。このとき、領域R3におけるレジストパターン63bは、不純物領域4ab, 4acと平面的にオーバラップするように形成される。そして、不純物領域4ab, 4acにおいてゲート電極6aと平面的にオーバラップする部分がGOLD領域となる。

## 【0199】

なお、ウエットエッチングを施すことで、ゲート電極となるクロム膜の側面にはエッチングが施されることになるが、そのエッチングされる量はオーバエッチングを施す時間によって制御することができる。

## 【0200】

そのレジストパターン63a, 63b, 63cを残した状態で、そのレジストパターン63a, 63b, 63cをマスクとして、たとえばドーズ量 $1 \times 10^{15}$ atom/cm<sup>2</sup>、加速エネルギー60KeVにてボロンを注入することにより、領域R3に位置する不純物領域4ab, 4acに、p型GOLD構造の薄膜トランジスタのソース領域となる不純物領域4adおよびドレイン領域となる不純物領域4aeがそれぞれ形成され、領域R4に位置する不純物領域4aaに、p型LDD構造の薄膜トランジスタのソース領域となる不純物領域4adおよびドレイン領域となる不純物領域4aeがそれぞれ形成される。

10

20

30

40

50

## 【0201】

なお、n型GOLD構造の薄膜トランジスタが形成される領域R1とn型LDD構造の薄膜トランジスタが形成される領域R2はレジストパターン63aによって覆われているため、領域R1, R2にはボロンは注入されない。その後、アッシングと薬液処理を施すことで、レジストパターン63a, 63b, 63cが除去される。

## 【0202】

次に、図72に示すように、ゲート電極6aをマスクとして、たとえばドーズ量 $5 \times 10^{13}$ atom/cm<sup>2</sup>、加速エネルギー60KeVにてボロンを注入することにより、領域R3に位置する残された不純物領域4ab, 4acの部分には、p型GOLD構造の薄膜トランジスタのソース側のLDD領域となる不純物領域4afおよびドレイン側のLDD領域となる不純物領域4agがそれぞれ形成される。また、領域R4に位置する残された不純物領域4aaの部分には、p型LDD構造の薄膜トランジスタのソース側のLDD領域となる不純物領域4afおよびドレイン側のLDD領域となる不純物領域4agがそれぞれ形成される。

## 【0203】

このLDD領域となる不純物領域4af, 4agの不純物濃度は、GOLD領域となる不純物領域4ab, 4acの不純物濃度よりも高く、ソース領域およびドレイン領域となる不純物領域4ad, 4aeの不純物濃度よりも低く設定される。

## 【0204】

次に、所定の写真製版処理を施すことにより領域R1, R2では、ゲート電極をパターンングするためのレジストパターン63a, 63bがそれぞれ形成されるとともに、領域R3および領域R4では、これを覆うレジストパターン63c, 63dがそれぞれ形成される（図73参照）。

## 【0205】

次に、図73に示すように、そのレジストパターン63a, 63b, 63cをマスクとしてクロム膜にウエットエッチングを施すことにより、領域R1, R2ではゲート電極6aがそれぞれ形成される。なお、領域R3, R4はレジストパターン63c, 63dによって覆われているため、ゲート電極6aにエッチングが施されることはない。

## 【0206】

このとき、領域R1におけるレジストパターン63aは、不純物領域4ab, 4acと平面的にオーバラップするように形成される。そして、不純物領域4ab, 4acにおいてゲート電極6aと平面的にオーバラップする部分がGOLD領域となる。なお、ウエットエッチングを施すことで、ゲート電極となるクロム膜の側面にはエッチングが施されることになるが、そのエッチングされる量はオーバエッチングを施す時間によって制御することができる。

## 【0207】

そのレジストパターン63a, 63b, 63cを残した状態で、そのレジストパターン63a, 63b, 63cをマスクとして、たとえばドーズ量 $1 \times 10^{14}$ atom/cm<sup>2</sup>、加速エネルギー80KeVにてリンを注入することにより、領域R1に位置する不純物領域4ab, 4acに、n型GOLD構造の薄膜トランジスタのソース領域となる不純物領域4adおよびドレイン領域となる不純物領域4aeがそれぞれ形成され、領域R2に位置する不純物領域4aaに、n型LDD構造の薄膜トランジスタのソース領域となる不純物領域4adおよびドレイン領域となる不純物領域4aeがそれぞれ形成される。

## 【0208】

なお、p型GOLD構造の薄膜トランジスタが形成される領域R3とp型LDD構造の薄膜トランジスタが形成される領域R4はレジストパターン63c, 63dによってそれぞれ覆われているため、領域R3, R4にはリンは注入されない。その後、アッシングと薬液処理を施すことで、レジストパターン63a, 63b, 63cが除去される。

## 【0209】

次に、図74に示すように、ゲート電極6aをマスクとして、たとえばドーズ量 $1 \times 10^{14}$ atom/cm<sup>2</sup>、加速エネルギー80KeVにてリンを注入することにより、領域R1に位置する不純物領域4ab, 4acに、n型GOLD構造の薄膜トランジスタのソース領域となる不純物領域4adおよびドレイン領域となる不純物領域4aeがそれぞれ形成される。

10

20

30

40

50

$0^{13}$  atom/cm<sup>2</sup>、加速エネルギー 80 KeV にてリンを注入することにより、領域 R 1 に位置する残された不純物領域 4 a b, 4 a c の部分には、n 型 G O L D 構造の薄膜トランジスタのソース側の L D D 領域となる不純物領域 4 a f およびドレイン側の L D D 領域となる不純物領域 4 a g がそれぞれ形成される。また、領域 R 1 に位置する残された不純物領域 4 a a の部分には、n 型 L D D 構造の薄膜トランジスタのソース側の L D D 領域となる不純物領域 4 a f およびドレイン側の L D D 領域となる不純物領域 4 a g がそれぞれ形成される。

【 0 2 1 0 】

なお、このとき、領域 3 に位置する p 型 G O L D 構造の薄膜トランジスタおよび領域 4 に位置する p 型 L D D 構造の薄膜トランジスタのそれぞれのソース領域およびドレイン領域となるボロンが注入された不純物領域 4 a d, 4 a e 等にもリンが注入されることになるが、リンの注入量はボロンの注入量に比べて十分に小さいため、領域 3 および領域 4 に位置する不純物領域 4 a d, 4 a e 等へのリンの注入は問題にならない。

【 0 2 1 1 】

その後、実施の形態 1 において説明した方法と同様の方法によって、図 7 5 に示すように、ガラス基板 1 上にシリコン酸化膜からなる層間絶縁膜 7 が形成される。次に、その層間絶縁膜 7 上に所定の写真製版処理を施すことにより、コンタクトホールを形成するためのレジストパターン（図示せず）が形成される。

【 0 2 1 2 】

そのレジストパターンをマスクとして、層間絶縁膜 7 およびゲート絶縁膜 5 に異方性エッチングを施すことにより、領域 R 1 ~ R 4 にそれぞれ位置する不純物領域 4 a d の表面を露出するコンタクトホール 7 a と、不純物領域 4 a e の表面を露出するコンタクトホール 7 b とがそれぞれ形成される。

【 0 2 1 3 】

次に、コンタクトホール 7 a, 7 b を充填するように、層間絶縁膜 7 上にクロム膜とアルミニウム膜との積層膜（図示せず）が形成される。その積層膜上に所定の写真製版処理を施すことにより、電極を形成するためのレジストパターン（図示せず）が形成される。そのレジストパターンをマスクとしてウエットエッチングを施すことにより、領域 R 1 ~ R 4 のそれぞれにおいてソース電極 8 a とドレイン電極 8 b が形成される。

【 0 2 1 4 】

以上のようにして、領域 R 1 では n 型 G O L D 構造の薄膜トランジスタ T 4 が形成され、領域 R 2 では n 型 L D D 構造の薄膜トランジスタ T 5 が形成され、領域 R 3 では p 型 G O L D 構造の薄膜トランジスタ T 6 が形成され、領域 R 4 では p 型 L D D 構造の薄膜トランジスタ T 7 が形成される。

【 0 2 1 5 】

n 型 G O L D 構造の薄膜トランジスタ T 4 では、不純物領域 4 a d がソース領域 4 5 となり、不純物領域 4 a e がドレイン領域 4 6 となり、不純物領域 4 a b, 4 a c が G O L D 領域 4 1, 4 2 となり、不純物領域 4 a f, 4 a g が L D D 領域 4 3, 4 4 となる。

【 0 2 1 6 】

また、n 型 L D D 構造の薄膜トランジスタ T 5 では、不純物領域 4 a d がソース領域 4 5 となり、不純物領域 4 a e がドレイン領域 4 6 となり、不純物領域 4 a f, 4 a g が L D D 領域 4 3, 4 4 となる。

【 0 2 1 7 】

そして、p 型 G O L D 構造の薄膜トランジスタ T 6 では、不純物領域 4 a d がソース領域 4 5 となり、不純物領域 4 a e がドレイン領域 4 6 となり、不純物領域 4 a b, 4 a c が G O L D 領域 4 1, 4 2 となり、不純物領域 4 a f, 4 a g が L D D 領域 4 3, 4 4 となる。

【 0 2 1 8 】

また、p 型 L D D 構造の薄膜トランジスタ T 7 では、不純物領域 4 a d がソース領域 4 5 となり、不純物領域 4 a e がドレイン領域 4 6 となり、不純物領域 4 a f, 4 a g が L D D 領域 4 3, 4 4 となる。

10

20

30

40

50

DD領域43, 44となる。

【0219】

上述した製造方法では、p型薄膜トランジスタのゲート電極を形成するためのマスクを追加するだけで、n型GOLD構造の薄膜トランジスタ、n型LDD構造の薄膜トランジスタ、p型GOLD構造の薄膜トランジスタおよびp型LDD構造の薄膜トランジスタを同時に形成することができる。

【0220】

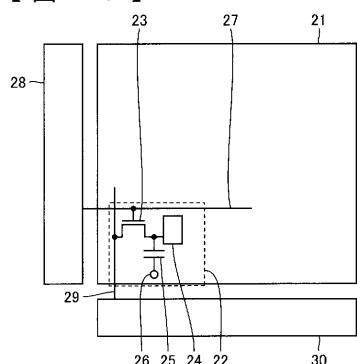

実施の形態17

ここでは、薄膜トランジスタを備えた半導体装置として液晶表示装置を例に挙げる。まず、はじめに液晶表示装置の構造について説明する。

10

【0221】

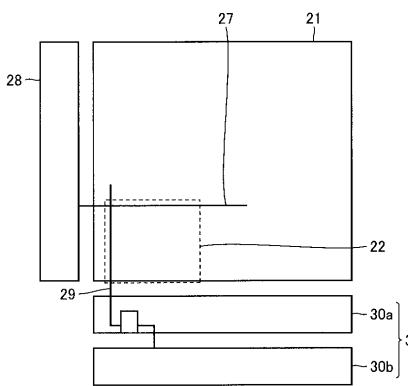

図76に示すように、液晶表示装置は、複数の画素22から構成されて画像を表示する表示部21と、その複数の画素22のそれぞれに設けられる画素部薄膜トランジスタ23の動作を制御するための走査線駆動回路部28およびデータ線駆動回路部30とを備えている。画素部としての表示部21と、その表示部の動作を制御する駆動回路部としての走査線駆動回路部28およびデータ線駆動回路部30とによって画像表示回路部が構成される。

【0222】

画素22は表示部21にアレイ状に配置されている。画素22では、画素電極24と対向電極(図示せず)との間に液晶(図示せず)が充填されて画素容量(図示せず)が形成される。画素電極24と対向電極との間に印加される電圧によって、液晶に印加される電圧が決まる。この液晶に印加される電圧によって液晶の配列状態が変化して、液晶を透過する光の強度が制御されることになる。また、画素部薄膜トランジスタ23と共通電極26との間で保持容量25が形成される。

20

【0223】

アレイ状に配列された画素22には、データ線駆動回路部30に繋がるデータ線29と、走査線駆動回路部28に繋がる走査線27がそれぞれ接続されている。データ線駆動回路部30からは画素信号が出力され、その出力された画素信号はデータ線29を介して画素22に入力される。走査線駆動回路部28からは画素選択信号が出力され、出力された画素選択信号は走査線27を介して画素22に入力される。

30

【0224】

走査線駆動回路部28は、主にシフトレジスタと出力回路とを備えて構成され、入力されたクロック信号によってレジスタをシフトさせる。レジスタがハイ(H)レベルであれば、画素22のON電圧に出力回路を切り換える。一方、レジスタがロー(L)レベルであれば、画素22のOFF電圧に出力回路を切り換える。このようにして、走査線駆動回路部28は、画素22の走査線に順次ON電圧とOFF電圧を印加する。

【0225】

データ線駆動回路部30は、入力された画素データの信号(たとえば各6ビットの画素データ)を、クロック信号のタイミングに合わせて順次ラッチして、データ線駆動回路部30に取り込む。取り込まれた画素データはデータ線駆動回路部30内のDAコンバータによってアナログ信号に変換される。アナログ信号に変換された画素データはデータ線29へ送られる。

40

【0226】

画素22の画素薄膜トランジスタ23のゲートは、走査線27から送られる信号によって制御される。ゲートにON信号が入力し、画素薄膜トランジスタのゲートがオンになったときに、データ線29から送られる信号が画素容量と保持容量25に蓄積される。蓄積された信号は、ゲートをオフして画面が書き換えられるまでの1フレームの間、画素容量と保持容量とに保持されることになる。

【0227】

このとき、画素薄膜トランジスタにおいてリーク電流が生じると液晶に印加された電圧

50

が保持時間とともに低下して、表示部 21 における表示品質を劣化させることになる。このため、表示部 21 の画素薄膜トランジスタには、リーク電流をできるだけ少なくすることが要求される。すなわち、画素薄膜トランジスタでは OFF 電流が低いことが求められる。

【 0 2 2 8 】

また、ゲートを OFF する際には画素薄膜トランジスタを完全に OFF 状態としなければならないため、ゲート電極には負電圧を印加する必要がある。このように画素薄膜トランジスタを ON する場合にはゲートに正電圧が印加される一方、OFF する場合にはゲートに負電圧が印加されるため、画素薄膜トランジスタでは OFF 電流が低いことに加えて高い AC ストレス耐性が要求される。

【 0 2 2 9 】

一方、画像表示装置の走査線駆動回路部 28 およびデータ線駆動回路部 30 のうち、CMOS 回路によって構成される部分では薄膜トランジスタのゲートに負電圧が印加されることはない。このため、そのような回路に使用される薄膜トランジスタでは高い AC ストレス耐性は特に要求されることはない。

【 0 2 3 0 】

そこで、本実施の形態に係る画像表示装置では、画素薄膜トランジスタとして、たとえば実施の形態 1 等において説明した GOLD 構造の薄膜トランジスタが適用される。一方、CMOS 回路によって構成され、高い AC ストレス耐性が要求されない回路の薄膜トランジスタとして、従来の LDD 構造の薄膜トランジスタが適用される。

【 0 2 3 1 】

実施の形態 1 等において説明した GOLD 構造の薄膜トランジスタは、従来の LDD 構造の薄膜トランジスタと比べると、薄膜トランジスタの占める占有面積が大きい。そこで、GOLD 構造の薄膜トランジスタと LDD 構造の薄膜トランジスタとを適切に配置することにより、液晶表示装置において薄膜トランジスタが形成される回路部の占める面積が大きくなるのを抑制することができる。

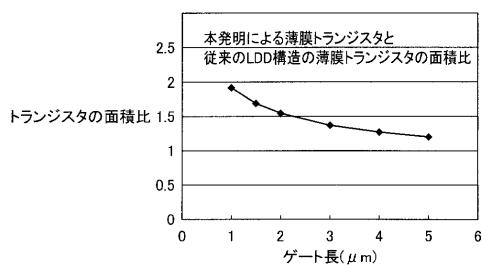

【 0 2 3 2 】

ここで、その GOLD 構造の薄膜トランジスタと LDD 構造の薄膜トランジスタの占有面積の比較を具体的に行なう。まず、GOLD 構造の薄膜トランジスタのゲート幅を 1.0  $\mu\text{m}$ 、GOLD 領域のチャネル長方向の長さを 1  $\mu\text{m}$ 、LDD 領域のチャネル長方向の長さを 0.5  $\mu\text{m}$  とする。一方、LDD 構造の薄膜トランジスタのゲート幅を 1.0  $\mu\text{m}$ 、LDD 領域のチャネル長方向の長さを 0.5  $\mu\text{m}$  とする。また、それぞれのゲートのチャネル長を 1 ~ 5  $\mu\text{m}$  とする。

【 0 2 3 3 】

図 77 に、本発明に係る GOLD 構造の薄膜トランジスタの占有面積と従来の LDD 構造の薄膜トランジスタの占有面積との面積比のゲート長依存性のグラフを示す。図 77 に示すように、ゲート長が短くなるほど、GOLD 構造の薄膜トランジスタの占有面積よりも LDD 構造の薄膜トランジスタの占有面積の方が小さくなる傾向があることがわかる。

【 0 2 3 4 】

このようにして、画素薄膜トランジスタのような低い OFF 電流と高い AC ストレス耐性が要求される薄膜トランジスタに GOLD 構造の薄膜トランジスタを適用し、CMOS 回路で構成されるような、画素薄膜トランジスタほどは高い AC ストレス耐性が要求されない回路には従来の LDD 構造の薄膜トランジスタを適用することで、画像表示装置における回路の占有面積の増大を最小限に抑えることができ、しかも、その占有面積増大の抑制効果は、ゲート長が短くなるにしたがって大きくなる。

【 0 2 3 5 】

なお、画素薄膜トランジスタとして実施の形態 1 において説明したゲート電極が 1 つの GOLD 構造の薄膜トランジスタを例に挙げたが、GOLD 構造の薄膜トランジスタとしては、たとえば図 58 および図 59 に示される 2 本のゲート電極を有する GOLD 構造の薄膜トランジスタを適用してもよい。特に、ゲート電極を 2 本備えることによって OFF

10

20

30

40

50

電流をさらに低減することができて、画素薄膜トランジスタとしてより好適である。

【0236】

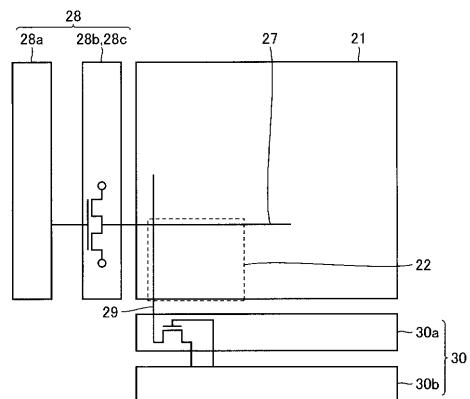

実施の形態18

ここでは、GOLD構造の薄膜トランジスタを適用した画像表示装置の他の例について説明する。前述した画像表示装置におけるデータ線駆動回路部30は、図78に示すように、アナログスイッチ回路部30aと論理回路部30bによって構成される。

【0237】

アナログスイッチ回路部30aではデータ線29にデータ信号を送るタイミングが制御される。アナログスイッチ回路部30aにおけるスイッチング素子としての薄膜トランジスタのゲートがONの状態になると、データ線29に信号が入力され、走査線27で選択されている画素22にデータ信号が書き込まれる。

【0238】

その後、アナログスイッチ回路部30aでは薄膜トランジスタはOFF状態になるが、走査線27には走査線に繋がるすべての画素22に信号が書き込まれるまでON信号が入力されている。そのため、走査線27の選択時間の間ではデータ線29と画素22に入力された信号を保持する必要があり、スイッチング素子としての薄膜トランジスタには低いOFF電流が求められることになる。

【0239】

また、ゲートをOFFする際には薄膜トランジスタを完全にOFF状態にする必要があるため、ゲート電極には負電圧を印加する必要がある。このようにスイッチング回路部30aにおける薄膜トランジスタをONする場合にはゲートに正電圧が印加される一方、OFFする場合にはゲートに負電圧が印加されるため、薄膜トランジスタではOFF電流が低いことに加えて高いACストレス耐性が要求されることになる。

【0240】

そこで、本実施の形態に係る画像表示装置では、データ線駆動回路部30を構成するアナログスイッチ回路部30aにおいて、スイッチング素子としての薄膜トランジスタとして、たとえば実施の形態1等において説明したGOLD構造の薄膜トランジスタが適用される。一方、データ線駆動回路部30を構成する論理回路部30bのような、高いACストレス耐性が要求されない回路では、薄膜トランジスタとして、たとえば従来のLDD構造の薄膜トランジスタが適用される。

【0241】

このように、アナログスイッチング回路部にOFF電流が低くACストレス耐性が高いGOLD構造の薄膜トランジスタを適用することで、画像の劣化を抑制することができる。一方、論理回路部には従来のLDD構造の薄膜トランジスタを適用することで、GOLD構造の薄膜トランジスタを適用することによる占有面積の増大を抑えることができる。

【0242】

なお、スイッチング回路部における薄膜トランジスタとしては、p型およびn型のいずれの薄膜トランジスタも適用することができる。

【0243】

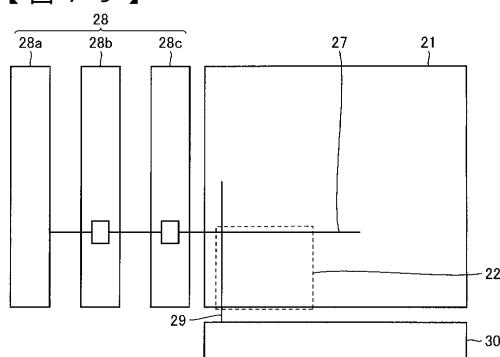

実施の形態19

ここでは、GOLD構造の薄膜トランジスタを適用した画像表示装置のさらに他の例について説明する。前述した画像表示装置における走査線駆動回路部28は、図79に示すように、論理回路部28a、昇圧回路部28bおよび出力回路部28cによって構成される。

【0244】

その論理回路部28aからはゲート選択信号が出力される。論理回路部28aから出力されるゲート選択信号は電圧としては低いために、昇圧回路部28bにおいてその信号電圧が昇圧される。このため、昇圧回路部28bにおける薄膜トランジスタには高いソース・ドレイン耐圧が要求されることになる。

【0245】

10

20

30

40

50

そして、昇圧された信号( H , L )は、出力回路部 28c においてさらに増幅されて走査線 27 に出力される。このため、出力回路部 28c における薄膜トランジスタにも高いソース・ドレイン耐圧が要求されることになる。

#### 【 0 2 4 6 】

そこで、本実施の形態に係る画像表示装置では、走査線駆動回路部 28 を構成する昇圧回路部 28b および出力回路部 28c において、薄膜トランジスタとして、たとえば実施の形態 1 等において説明した G O L D 構造の薄膜トランジスタがそれぞれ適用される。一方、走査線駆動回路部 28 を構成する論理回路部 28a のような他界 A C ストレス耐性が要求されない回路では、薄膜トランジスタとして、たとえば従来の L D D 構造の薄膜トランジスタが適用される。

10

#### 【 0 2 4 7 】

このように、昇圧回路部 28b および出力回路部 28c にソース・ドレイン耐圧が高い G O L D 構造の薄膜トランジスタを適用することで、高い駆動能力を確保することができる。一方、論理回路部等には従来の L D D 構造の薄膜トランジスタを適用することで、G O L D 構造の薄膜トランジスタを適用することによる占有面積の増大を抑えることができる。

#### 【 0 2 4 8 】

##### 実施の形態 2 0

実施の形態 18 では、画像表示装置において、データ線駆動回路部 30 におけるアナログスイッチ回路部の薄膜トランジスタとして G O L D 構造の薄膜トランジスタが適用される場合について説明した。また、実施の形態 15 では、走査線駆動回路部 28 における昇圧回路部および出力回路部のそれぞれの薄膜トランジスタとして G O L D 構造の薄膜トランジスタが適用される場合について説明した。

20

#### 【 0 2 4 9 】

ここでは、上記所定の回路部の薄膜トランジスタとして G O L D 構造の薄膜トランジスタを適用することを前提として、画素の画素薄膜トランジスタとして L D D 構造の薄膜トランジスタを適用した画像表示装置について説明する。

30

#### 【 0 2 5 0 】

図 80 に示すように、画像表示装置において、まず、データ線駆動回路部 30 におけるアナログスイッチ回路部 30a のスイッチング素子としての薄膜トランジスタに G O L D 構造の薄膜トランジスタが適用される、また、走査線駆動回路部 28 における昇圧回路部 28b および出力回路部 28c のそれぞれの薄膜トランジスタとして G O L D 構造の薄膜トランジスタが適用される。

40

#### 【 0 2 5 1 】

そして、表示部 21 の画素薄膜トランジスタとして L D D 構造の薄膜トランジスタが適用される。特に、この L D D 構造の薄膜トランジスタとしては、たとえば 2 本のゲート電極を有する薄膜トランジスタが適用される。

#### 【 0 2 5 2 】

表示部 21 では、画素容量および蓄積容量に書き込まれた信号を保持するために薄膜トランジスタには O F F 電流が低いことが要求される。そして、さらに、光の透過率を上げるために光が透過できる領域の開口率をできるだけ高くする必要がある。O F F 電流を低くするためには、薄膜トランジスタとして複数のゲート電極を有することが有効であるが、一方で、薄膜トランジスタの占有面積を増加させてしまう。

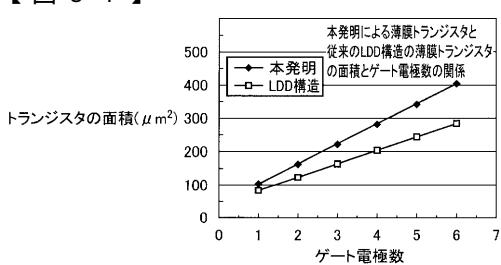

#### 【 0 2 5 3 】

図 81 に、本発明による G O L D 構造の薄膜トランジスタと従来の L D D 構造の薄膜トランジスタの占有面積のゲート電極数依存性のグラフを示す。図 81 に示されるグラフによれば、たとえば 2 本のゲート電極を有する G O L D 構造の薄膜トランジスタと、3 本のゲート電極を有する従来の L D D 構造の薄膜トランジスタとはほぼ同じ占有面積を有することがわかる。

#### 【 0 2 5 4 】

50

したがって、上述した画像表示装置では、限られた画素部の領域内において画素薄膜トランジスタとしてLDD構造の薄膜トランジスタを適用することで、より多くのゲート電極を有することができOFF電流の低減に寄与することができる。

【0255】

このように実施の形態18~20において説明した液晶表示装置においては、各回路部に要求される仕様に合わせて、GOLD構造の薄膜トランジスタとLDD構造の薄膜トランジスタ等を適切に配設することで、液晶表示装置の能力を最大限に引き出すことができるとともに、回路部の占有面積の増大を最小限に抑えることができる。

【0256】

なお、上述した各実施の形態では、薄膜トランジスタとしてソース領域およびドレイン領域等が形成される半導体層上にゲート絶縁膜を介在させてゲート電極が形成された、いわゆるプレーナ構造の薄膜トランジスタを例に挙げて説明した。

【0257】

本発明に係るGOLD構造の薄膜トランジスタとしては、このようなプレーナ構造の薄膜トランジスタに限られず、ゲート電極上にゲート絶縁膜を介在させてソース領域およびドレイン領域等となる半導体層を形成した、いわゆる逆スタガ構造の薄膜トランジスタであってもよい。このような場合においても、それぞれ一方のGOLD領域とLDD領域との接合部および電極の一方側部とは略同一平面上に位置し、それぞれ他方のGOLD領域とLDD領域との接合部および電極の他方側部は同一平面上に位置することになる。

【0258】

なお、今回開示された実施の形態は例示であってこれに制限されるものではない。本発明は上記で説明した範囲ではなく、特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲でのすべての変更が含まれることが意図される。

【図面の簡単な説明】

【0259】

【図1】発明の実施の形態1に係る半導体装置の断面図である。

【図2】同実施の形態において、図1に示す半導体装置の製造方法の一工程を示す断面図である。

【図3】同実施の形態において、図2に示す工程の後に行なわれる工程を示す断面図である。

【図4】同実施の形態において、図3に示す工程の後に行なわれる工程を示す断面図である。

【図5】同実施の形態において、図4に示す工程の後に行なわれる工程を示す断面図である。

【図6】同実施の形態において、図5に示す工程の後に行なわれる工程を示す断面図である。

【図7】同実施の形態において、図6に示す工程の後に行なわれる工程を示す断面図である。

【図8】同実施の形態において、図7に示す工程の後に行なわれる工程を示す断面図である。

【図9】同実施の形態において、図8に示す工程の後に行なわれる工程を示す断面図である。

【図10】同実施の形態において、薄膜トランジスタのソース・ドレイン耐圧の結果を示す図である。

【図11】同実施の形態において、薄膜トランジスタのON電流の結果を示す図である。

【図12】同実施の形態において、薄膜トランジスタのOFF電流の結果を示す図である。

【図13】同実施の形態において、薄膜トランジスタのACストレス耐性の結果を示す図である。

【図14】同実施の形態において、本発明によるGOLD構造の薄膜トランジスタと従来

10

20

30

40

50

の G O L D 構造の薄膜トランジスタにおけるエッチングプロセス工程を比較した図である。

【図 1 5】本発明の実施の形態 2 に係る半導体装置の製造方法の一工程を示す断面図である。

【図 1 6】同実施の形態において、図 1 5 に示す工程の後に行なわれる工程を示す断面図である。

【図 1 7】同実施の形態において、図 1 6 に示す工程の後に行なわれる工程を示す断面図である。

【図 1 8】同実施の形態において、図 1 7 に示す工程の後に行なわれる工程を示す断面図である。

【図 1 9】同実施の形態において、図 1 8 に示す工程の後に行なわれる工程を示す断面図である。

【図 2 0】同実施の形態において、図 1 9 に示す工程の後に行なわれる工程を示す断面図である。

【図 2 1】同実施の形態において、薄膜トランジスタのソース・ドレイン耐圧の結果を示す図である。

【図 2 2】同実施の形態において、薄膜トランジスタの ON 電流の結果を示す図である。

【図 2 3】同実施の形態において、薄膜トランジスタの OFF 電流の結果を示す図である。

【図 2 4】同実施の形態において、薄膜トランジスタの A C ストレス耐性の結果を示す図である。

【図 2 5】本発明の実施の形態 3 に係る半導体装置の製造方法の一工程を示す断面図である。

【図 2 6】同実施の形態において、図 2 5 に示す工程の後に行なわれる工程を示す断面図である。

【図 2 7】同実施の形態において、図 2 6 に示す工程の後に行なわれる工程を示す断面図である。

【図 2 8】同実施の形態において、図 2 7 に示す工程の後に行なわれる工程を示す断面図である。

【図 2 9】同実施の形態において、図 2 8 に示す工程の後に行なわれる工程を示す断面図である。

【図 3 0】本発明の実施の形態 4 において、飽和劣化率の G O L D 領域の不純物濃度依存性を示すグラフである。

【図 3 1】本発明の実施の形態 5 において、飽和劣化率の G O L D 長依存性を示すグラフである。

【図 3 2】本発明の実施の形態 6 において、A C ストレス寿命の L D D 長依存性を示すグラフである。

【図 3 3】本発明の実施の形態 7 において、ON 電流のソース側の L D D 長とドレイン側の L D D 長との差の依存性を示すグラフである。

【図 3 4】本発明の実施の形態 8 に係る半導体装置の製造方法の一工程を示す断面図である。

【図 3 5】同実施の形態において、図 3 4 に示す工程の後に行なわれる工程を示す断面図である。

【図 3 6】同実施の形態において、図 3 5 に示す工程の後に行なわれる工程を示す断面図である。

【図 3 7】同実施の形態において、図 3 6 に示す工程の後に行なわれる工程を示す断面図である。

【図 3 8】同実施の形態において、図 3 7 に示す工程の後に行なわれる工程を示す断面図である。

【図 3 9】同実施の形態において、薄膜トランジスタのソース・ドレイン耐圧の結果を示す

10

20

30

40

50

す図である。

【図40】同実施の形態において、薄膜トランジスタのON電流の結果を示す図である。

【図41】同実施の形態において、薄膜トランジスタのOFF電流の結果を示す図である。

【図42】本発明の実施の形態9において、ソース・ドレイン耐圧のGOLD領域の不純物濃度依存性を示すグラフである。

【図43】同実施の形態において、ACストレス寿命のGOLD領域の不純物濃度依存性を示すグラフである。

【図44】本発明の実施の形態10において、ソース・ドレイン耐圧のLDD領域の不純物濃度依存性を示すグラフである。

【図45】同実施の形態において、ACストレス寿命のLDD領域の不純物濃度依存性を示すグラフである。

【図46】同実施の形態において、OFF電流のLDD領域の不純物濃度依存性を示すグラフである。

【図47】本発明の実施の形態11において、ソース・ドレイン耐圧のGOLD長依存性を示すグラフである。

【図48】同実施の形態において、ACストレス寿命のGOLD長依存性を示すグラフである。

【図49】本発明の実施の形態12において、ソース・ドレイン耐圧のLDD長依存性を示すグラフである。

【図50】同実施の形態において、ACストレス寿命のLDD長依存性を示すグラフである。

【図51】同実施の形態において、OFF電流のLDD長依存性を示すグラフである。

【図52】同実施の形態において、ON電流のLDD長依存性を示すグラフである。

【図53】本発明の実施の形態13において、評価用半導体装置の製造方法の一工程を示す断面図である。

【図54】同実施の形態において、図53に示す工程の後に行なわれる工程を示す断面図である。

【図55】同実施の形態において、図54に示す工程の後に行なわれる工程を示す断面図である。

【図56】同実施の形態において、ON電流のソース側のLDD長とドレイン側のLDD長との差の依存性を示すグラフである。

【図57】同実施の形態において、OFF電流のLDD長さの差の依存性を示すグラフである。

【図58】本発明の実施の形態14に係る半導体装置の平面図である。

【図59】同実施の形態において、図58に示す断面線LIX-LIXにおける断面図である。

【図60】同実施の形態において、OFF電流の測定結果を示す図である。

【図61】本発明の実施の形態15に係る半導体装置の製造方法の一工程を示す断面図である。

【図62】同実施の形態において、図61に示す工程の後に行なわれる工程を示す断面図である。

【図63】同実施の形態において、図62に示す工程の後に行なわれる工程を示す断面図である。

【図64】同実施の形態において、図63に示す工程の後に行なわれる工程を示す断面図である。

【図65】同実施の形態において、図64に示す工程の後に行なわれる工程を示す断面図である。

【図66】同実施の形態において、図65に示す工程の後に行なわれる工程を示す断面図である。

10

20

30

40

50

【図67】同実施の形態において、図66に示す工程の後に行なわれる工程を示す断面図である。

【図68】本発明の実施の形態16に係る半導体装置の製造方法の一工程を示す断面図である。

【図69】同実施の形態において、図68に示す工程の後に行なわれる工程を示す断面図である。

【図70】同実施の形態において、図69に示す工程の後に行なわれる工程を示す断面図である。

【図71】同実施の形態において、図70に示す工程の後に行なわれる工程を示す断面図である。

【図72】同実施の形態において、図71に示す工程の後に行なわれる工程を示す断面図である。

【図73】同実施の形態において、図72に示す工程の後に行なわれる工程を示す断面図である。

【図74】同実施の形態において、図73に示す工程の後に行なわれる工程を示す断面図である。

【図75】同実施の形態において、図74に示す工程の後に行なわれる工程を示す断面図である。

【図76】本発明の実施の形態17に係る液晶表示装置の構成を示すブロック図である。

【図77】同実施の形態において、本発明によるGOLD構造の薄膜トランジスタの占有面積と従来のLDD構造の薄膜トランジスタの占有面積との面積比のゲート長依存性を示すグラフである。

【図78】本発明の実施の形態18に係る液晶表示装置の構成を示すブロック図である。

【図79】本発明の実施の形態19に係る液晶表示装置の構成を示すブロック図である。

【図80】本発明の実施の形態20に係る液晶表示装置の構成を示すブロック図である。

【図81】同実施の形態において、本発明によるGOLD構造の薄膜トランジスタと従来のLDD構造の薄膜トランジスタの占有面積のゲート電極数依存性を示すグラフである。

【符号の説明】

【0260】

1 ガラス基板、2 シリコン窒化膜、3 シリコン酸化膜、4 多結晶シリコン膜、

4 a a , 4 a b , 4 a c , 4 a d , 4 a e , 4 a f , 4 a g 不純物領域、5 ゲート絶

縁膜、6 クロム膜、6 a ゲート電極、7 層間絶縁膜、7 a , 7 b コンタクトホー

ル、8 a ソース電極、8 b ドレイン電極、21 表示部、22 画素、23 画素部

薄膜トランジスタ、24 画素電極、25 保持容量、26 共通電極、27 走査線、

28 走査線駆動回路部、28 a 論理回路部、28 b 昇圧回路部、28 c 出力回路

部、29 データ線、30 データ線駆動回路、30 a アナログスイッチ回路部、30

b 論理回路部、40 チャネル領域、41 , 42 GOLD領域、43 , 44 LDD

領域、45 ソース領域、46 ドレイン領域。

【図1】

【図2】

【図3】

【図7】

【図8】

【図4】

【図5】

【図6】

【図9】

【図10】

| 薄膜トランジスタのソース・ドレイン耐圧 | 耐圧    |

|---------------------|-------|

| 実施の形態1の薄膜トランジスタ     | 25.2V |

| 従来のGOLD構造の薄膜トランジスタ  | 21.8V |

| 従来のLDD構造の薄膜トランジスタ   | 10.7V |

【図11】

| 薄膜トランジスタのON電流     | ON電流    |

|-------------------|---------|

| 実施の形態1の薄膜トランジスタ   | 2.1E-4A |

| 従来のLDD構造の薄膜トランジスタ | 2.2E-4A |

【図12】

| 薄膜トランジスタのOFF電流     | OFF電流  |

|--------------------|--------|

| 実施の形態1の薄膜トランジスタ    | 3E-13A |

| 従来のGOLD構造の薄膜トランジスタ | 4E-11A |

【図13】

| 薄膜トランジスタのACストレス耐性  |                |

|--------------------|----------------|

|                    | 本実施の形態に対する寿命の比 |

| 実施の形態1の薄膜トランジスタ    | 1              |

| 従来のGOLD構造の薄膜トランジスタ | 9.0E-03        |

| 従来のLDD構造の薄膜トランジスタ  | 2.0E-07        |

【図14】

|                             |                                 |

|-----------------------------|---------------------------------|

| 本発明による薄膜トランジスタにおけるエッチングプロセス | 従来のGOLD構造の薄膜トランジスタにおけるエッチングプロセス |

| Siエッチング                     | Siエッチング                         |

| ゲート電極エッチング                  | ゲート上層電極テープエッチング                 |

| 層間絶縁膜エッチング                  | ゲート下層電極エッチング                    |

| ソース・ドレイン電極エッチング             | ゲート上層・下層電極エッチング                 |

| ——                          | 層間絶縁膜エッチング                      |

| ——                          | ソース・ドレイン電極エッチング                 |

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

| 薄膜トランジスタのソース・ドレイン耐圧 |       |

|---------------------|-------|

| 実施の形態2の薄膜トランジスタ     | 耐圧    |

| 22.5V               |       |

| 従来のGOLD構造の薄膜トランジスタ  | 21.8V |

| 従来のLDD構造の薄膜トランジスタ   | 10.7V |

【図22】

| 薄膜トランジスタのON電流     |         |

|-------------------|---------|

| 実施の形態2の薄膜トランジスタ   | ON電流    |

| 2.0E-4A           |         |

| 実施の形態1の薄膜トランジスタ   | 2.1E-4A |

| 従来のLDD構造の薄膜トランジスタ | 2.2E-4A |

【図23】

|                    | OFF電流  |

|--------------------|--------|

| 実施の形態2の薄膜トランジスタ    | 4E-14A |

| 実施の形態1の薄膜トランジスタ    | 3E-13A |

| 従来のGOLD構造の薄膜トランジスタ | 4E-11A |

【図24】

|                    | 薄膜トランジスタのACストレス耐性 |

|--------------------|-------------------|

| 本実施の形態に対する寿命の比     |                   |

| 実施の形態2の薄膜トランジスタ    | 1                 |

| 従来のGOLD構造の薄膜トランジスタ | 6.0E-02           |

| 従来のLDD構造の薄膜トランジスタ  | 1.3E-06           |

【図25】

【図26】

【図29】

【図30】

【図27】

【図28】

【図31】

【図32】

【図33】

【図3-4】

【図3-5】

【図3-6】

【図3-9】

| 薄膜トランジスタのソース・ドレイン耐圧 |       |

|---------------------|-------|

| 耐圧                  |       |

| 実施の形態8の薄膜トランジスタ     | 40.5V |

| 従来のGOLD構造の薄膜トランジスタ  | 35.1V |

| 従来のLDD構造の薄膜トランジスタ   | 19.2V |

【図4-0】

| 薄膜トランジスタのON電流     |         |

|-------------------|---------|

| ON電流              |         |

| 実施の形態8の薄膜トランジスタ   | 1.7E-4A |

| 従来のLDD構造の薄膜トランジスタ | 1.7E-4A |

【図4-1】

| 薄膜トランジスタのOFF電流     |        |

|--------------------|--------|

| OFF電流              |        |

| 実施の形態8の薄膜トランジスタ    | 8E-14A |

| 従来のGOLD構造の薄膜トランジスタ | 2E-11A |

【図4-2】

【図3-7】

【図3-8】

【図4-3】

【図4-4】

【図45】

【図46】

【図47】

【図51】

【図52】

【図53】

【図48】

【図49】

【図50】

【図51】

【図55】

【 図 5 6 】

【 図 5 7 】

〔 义 5 8 〕

( 62 )

〔 义 6 3 〕

〔 四 6 4 〕

【図59】

〔 四 6 0 〕

| 薄膜トランジスタのOFF電流   |        |

|------------------|--------|

|                  | OFF電流  |

| 実施の形態14の薄膜トランジスタ | 9E-14A |

| 実施の形態1の薄膜トランジスタ  | 3E-13A |

〔 四 61 〕

〔 四 6 5 〕

【 义 6 6 】

【 図 6 7 】

【 図 6 8 】

【図69】

【図70】

【図 7-1】

## 【図72】

【 図 7 3 】

【 図 7 4 】

【 図 7 5 】

【図76】

【図77】

【 図 7 8 】

【図 8 0】

〔 四 7 9 〕

【 図 8 1 】

## フロントページの続き

(51)Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

H 01 L 27/092

H 01 L 29/786

(72)発明者 豊田 吉彦

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72)発明者 坂本 孝雄

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72)発明者 須賀原 和之

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72)発明者 中川 直紀

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

F ターム(参考) 5F048 AA03 AC01 AC04 BA16 BB09 BC06 BC07 BC16 BD04 BF02

BF07 BF16 DA01 DA20

5F110 AA06 AA13 AA16 AA30 BB02 BB04 CC02 DD02 DD12 DD13

DD14 DD15 DD17 EE04 EE24 EE44 FF02 FF30 GG02 GG13

GG16 GG25 GG28 GG29 GG32 GG52 HJ01 HJ04 HJ13 HL03

HL04 HL11 HM15 NN04 NN23 NN35 NN72 NN73 NN78 PP01

PP03 PP34 PP35 QQ05