(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-300088

(P2007-300088A)

(43) 公開日 平成19年11月15日(2007.11.15)

(51) Int.C1.

H01L 23/50 (2006.01)

F 1

H01L 23/50

A

テーマコード(参考)

H01L 23/50

R

H01L 23/50

W

5 F O 6 7

審査請求 未請求 請求項の数 18 O L (全 16 頁)

(21) 出願番号 特願2007-104458 (P2007-104458)

(22) 出願日 平成19年4月12日 (2007.4.12)

(31) 優先権主張番号 11/416,994

(32) 優先日 平成18年5月2日 (2006.5.2)

(33) 優先権主張国 米国(US)

(71) 出願人 505253879

ジーイーエム サービシズ インコーポレーティッド

アメリカ合衆国 カリフォルニア州 サンタクララ レイクサイド ドライブ 2880 スイート 203

(74) 代理人 100102978

弁理士 清水 初志

(74) 代理人 100128048

弁理士 新見 浩一

(72) 発明者 ハーンデン ジェイムズ

アメリカ合衆国 カリフォルニア州 ホリスター ヘザーウッド エステイツ ドライブ 700

最終頁に続く

(54) 【発明の名称】複数の金属層から形成される半導体素子パッケージリードフレーム

(57) 【要約】 (修正有)

【課題】複数の金属層から形成される半導体素子パッケージリードフレームを提供する。

【解決手段】半導体素子パッケージの使用のため、隆起した形体を有するリードフレームは、少なくとも二つの金属層450、452を接合することによって作製される。第一の金属層450が、任意のダイパッドおよびリードを含めたリードフレームの横方向寸法を画定し得る。第一の金属層に接合された第二の金属層452が、リードフレームの隆起した形体、たとえばリードフレームをパッケージ本体内に物理的に固着するための段を画定し得る。複数の金属層は、非制限的に、超音波溶接、軟質はんだ付けまたはエポキシ樹脂の使用を含む多数の可能な技術によって接合することができる。接合の前または後で、金属層の一つまたは複数をコイニングまたはスタンピングして、オフセットまたは溝のようなさらなる形体を形成することもできる。

【選択図】図3A

**【特許請求の範囲】****【請求項 1】**

以下の工程を含む、半導体素子パッケージのためのリードフレームを作製する方法：

リードフレームを画定する第一の金属層を設ける工程；

リードフレームの隆起した形体を画定する第二の金属層を設ける工程；および

該第一の金属層を該第二の金属層に接合する工程。

**【請求項 2】**

超音波溶接によって第一の金属層を第二の金属層に接合する、請求項1記載の方法。

**【請求項 3】**

エポキシ樹脂によって第一の金属層を第二の金属層に接合する、請求項1記載の方法。 10

**【請求項 4】**

はんだによって第一の金属層を第二の金属層に接合する、請求項1記載の方法。

**【請求項 5】**

第二の金属層をパターン付けして、DPAK、D2PAK、T0-220、T0-247、SOT-223、TSSOP-x、SO-x、SSOP-x、TQFP、SE70-8、TSOP-8およびTSOP12からなる群より選択されるパワータイプパッケージのダイパッド上に隆起した形体を形成する、請求項1記載の方法。

**【請求項 6】**

第二の金属層をパターン付けして、リードをプラスチックの本体内に固着するための段としての隆起した形体を形成する、請求項1記載の方法。

**【請求項 7】**

第二の金属層をパターン付けして、パッケージ中の二つのダイを接続するトレースとしての隆起した形体を形成する、請求項1記載の方法。 20

**【請求項 8】**

第二の金属層をパターン付けして、パッケージの周囲にダイ接点を接続分布させるトレースとしての隆起した形体を形成する、請求項1記載の方法。

**【請求項 9】**

リードフレームを画定する第一の金属層と、

該第一の金属層に接合され、該リードフレームの隆起した形体を画定する第二の金属層とを含む、

半導体素子パッケージのためのリードフレーム。 30

**【請求項 10】**

第二の金属層が第一の金属層に溶接されている、請求項9記載のリードフレーム。

**【請求項 11】**

第一の金属層と第二の金属層との間にエポキシ樹脂をさらに含む、請求項9記載のリードフレーム。

**【請求項 12】**

第一の金属層と第二の金属層との間にはんだをさらに含む、請求項9記載のリードフレーム。

**【請求項 13】**

隆起した形体が、リードをプラスチックのパッケージ本体内に固着する段を含む、請求項9記載のリードフレーム。 40

**【請求項 14】**

隆起した形体が、パッケージ中の二つのダイを接続する導電トレースを含む、請求項9記載のリードフレーム。

**【請求項 15】**

隆起した形体が、パッケージの周囲にダイ接点を分布させる導電トレースを含む、請求項9記載のリードフレーム。

**【請求項 16】**

リードフレーム上に支持されたダイを含み、該リードフレームが、第二の金属層に接合された第一の金属層を含み、該第二の金属層が、該リードフレームの隆起した形体を画定

するものである半導体素子パッケージ。

【請求項 1 7】

第二の金属層が溶接、エポキシ樹脂またははんだによって第一の金属層に接合されている、請求項16記載のパッケージ。

【請求項 1 8】

隆起した形体が、リードをパッケージ本体内に固着する段、ダイを該パッケージ本体内の第二のダイと接続する導電トレース、または該パッケージ本体の周囲にダイ接点を分布させる導電トレースから選択される、請求項16記載のパッケージ。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、複数の金属層から形成される半導体素子パッケージリードフレームに関する。

【0 0 0 2】

関連出願の相互参照

本非仮出願は、すべての点で参照により本明細書に組み入れられる、2005年6月15日に出願された、米国特許仮出願第60/690,958号の優先権を主張する。

【背景技術】

【0 0 0 3】

発明の背景

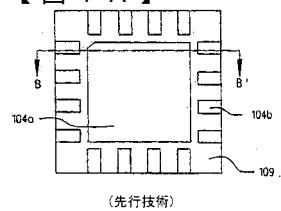

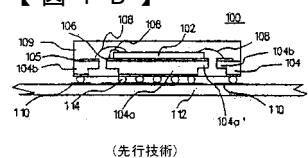

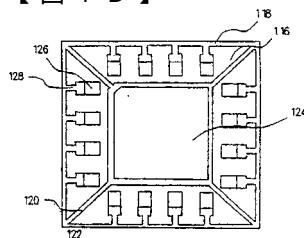

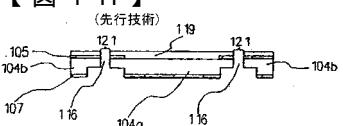

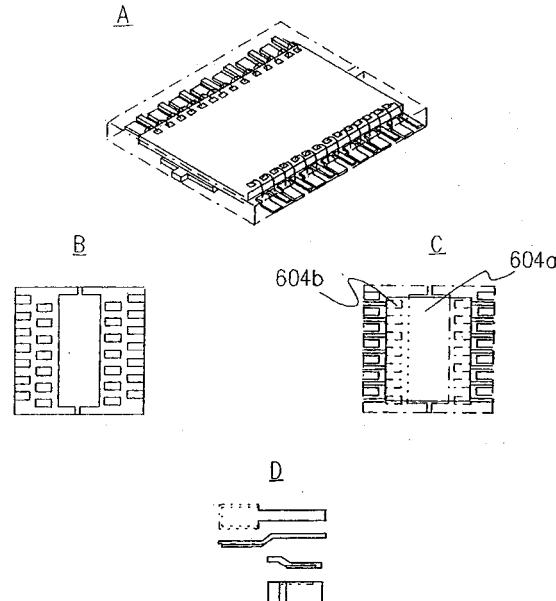

図1Aは、半導体素子を収容するために利用される従来のQFN(quad flat no-lead)パッケージの下面図を示す。図1Bは、PCボード上に配置された図1Aの従来のQFNパッケージをB-B'線から見た断面図を示す。

【0 0 0 4】

QFNパッケージ100は、その上に作製された電気的に能動的な構造を有する半導体ダイ102を含む。ダイ102は、接着剤106により、下にある、リードフレーム104のダイパッド104a部に固定されている。図1Bおよび本特許出願の他すべての図面に示すダイおよびリードフレームの相対的な厚さは、原寸に比例して描かれてはいない。リードフレーム104はまた、ボンドワイヤ108を介してダイ102と電気的に連絡した非一体化ピン部104bを含む。ボンドワイヤ108はまた、ダイ102とダイパッド104aとの間の電気的連絡を可能にする。

【0 0 0 5】

プラスチック成形物109が、リードフレーム部104aおよび104bそれぞれの露出部104a'および104b'を除くすべてを封入している。本特許出願に関して、「封入」とは、周囲材料中の要素の部分的または全体的な包み込み、典型的には、プラスチックのような周囲絶縁材料内へのリードフレームの金属の包み込みをいう。

【0 0 0 6】

リードフレーム104の上面の一部は、電気めっきによって形成された銀Ag 105を有する。リードフレーム104の下面は、電気めっきによって形成されたPd/NiまたはAu/Niの層107を有する。

【0 0 0 7】

QFNパッケージ100は、図示のように丸い形を有することが好ましいはんだ114によって下にあるPCボード112のトレース110に固着されている。はんだ114の導電性が、リードフレーム部104aおよび104bと下にあるトレース110との間で電気信号を行き来させる。

【0 0 0 8】

図1Cは、図1A～BのQFNパッケージ100のリードフレーム104のみの平面図を示す。リードフレーム104は、典型的には、均一な銅シートを完全に貫通する孔のパターンをエッチングすることによって形成される。図1Dは、銅ロール118中のそのような孔116のパターンの一例を示す。これらの孔パターンは、プロトダイパッド124およびプロト非一体化部126を含むプロトリードフレーム122を画定する。プロトダイパッド124は、タイベー120によって周囲金属フレームに固着されている。プロト非一体化ピン部126は、タブ128によって周

10

20

30

40

50

囲金属フレームに固着されている。

【0009】

図1Dに示すパターン付けされた金属部は、ダイをダイパッドに接着し、ボンドワイヤをダイと非一体化部および／またはダイパッドとの間に接続することによってパッケージへと加工される。ダイパッドおよび非一体化部がまだ周囲金属に取付けられている間に、ボンドワイヤおよびダイパッドの一部および非一体化リードフレーム部が、プラスチックのような絶縁材料内に封入される。次いで、タブおよびタイバーを切断して個々のパッケージを周囲金属フレームおよびそれと結合した他のパッケージからシンギュレーションすることにより、個々のパッケージの作製が完了する。

【0010】

上記した従来のQFNパッケージは、多くの目的には適切であるが、いくつかの欠点が想定される。想定される一つの欠点は、隆起した形体をリードフレーム上に形成することが困難であることである。

【0011】

たとえば、図1Bは、非一体化リードフレームピン部104bが、ダイパッドに隣接する肉薄の領域104b'を有することを示す。肉薄のピン領域104b'は、パッケージ本体のプラスチック封入材109によって三辺を包囲され、それにより、非一体化ピン部104bがパッケージ内に物理的に固着されている。

【0012】

そのうえ、図1Bはまた、ダイパッド部104aが、非一体化ピンに隣接する肉薄の領域104a'を有することを示す。肉薄のダイパッド領域104a'は、パッケージ本体のプラスチック封入材によって三辺を包囲され、それにより、ダイパッドがパッケージ内に物理的に固着されている。

【0013】

図1E～1Hは、肉薄部分を有するリードフレームを作製するための従来工程の断面図を示す。図1Eで、反転させたCuシート118の下面をAu/Pd/Niの組み合わせまたはAg/Niの組み合わせで電気めっきして層107を形成する。Au/Pd/Ni組み合わせの場合、Auは、厚さ約0.01～0.015μmであり、Pdは、厚さ約0.02～0.2μmであり、Niは、厚さ約0.5～2.5μmである。Ag/Ni電気めっきコーティングの場合、AgおよびNiはそれぞれ厚さ約0.5～2.5μmである。

【0014】

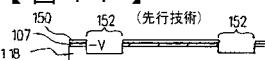

図1Fでは、フォトレジストマスク150を層107の上にパターン付けして、肉薄化される領域152を露出させる。次いで、露出領域152を、制御された期間、エッティング液に曝露することにより、Cu材料が所定の深さYまで除去される。

【0015】

図1Gでは、フォトレジストマスクを除去した後、Cuロール118を表側を上にして向け直す。次いで、Cuロール118の上面を選択的に電気めっきして銀層105を形成する。この工程で、マスク(図示せず)を利用して、銀を基材上の指定領域だけ電気めっきすることもできる。

【0016】

図1Hでは、部分的にエッティングされたCuシート118の背面をフォトレジストマスク119でパターン付けして、肉薄化領域に対応する露出区域121を残す。次いで、部分的にエッティングされたCuシート118を、露出区域121を貫通するまでエッティングして、ダイパッド104aを非一体化ピン104bから切り離すパターンの孔116を形成する。

【0017】

その後、当技術分野で周知であるように、ダイをダイパッドに固定させ、ダイとダイパッドと非一体化ピン部との間にボンドワイヤを取り付け、次いで構造体をプラスチック封入材内に包み込むことにより、QFNパッケージの作製が完了する。

【0018】

図1Fに示す、QFNパッケージ作製法のエッティング工程は、精密に制御することが比較的

10

20

30

40

50

困難である。具体的には、小さな区域でCuリードフレームをエッティングする精度は、全リードフレーム厚の約20~25%である。これは、ひとたびケミカルエッティング反応を開始すると、その進行を速やかかつ再現可能に停止させることができないことによる。上記許容差範囲外のエッティングは、結果的に多くのリードフレームの廃棄を生じさせて、パッケージコストを高めるおそれがある。

#### 【0019】

そのうえ、肉薄の形体を成形するための従来の部分的エッティング手法は、リードのピッチ、ひいては所与のQFNパッケージ本体サイズで利用可能なピンの本数を制限する。リードピッチにおけるこの制限は、材料を横方向および垂直方向に除去する、エッティング法の少なくとも部分的に等方的な特性から生じる。

10

#### 【0020】

旧来、エッティングされたリードフレームは、新製品のプロトタイプを製造し、初期の限られた数量を速やかに生産するために使用されてきた。ひとたびリードフレームが受け入れられ、製品の出荷量が増大し始めると、大部分のリードフレーム設計は、銅または他の金属のシートからリードフレームを打ち抜くようにツーリングされた。打ち抜きリードフレームを生産するためのツーリングの初期コストは、通常、エッティングされるリードフレームの最初のランよりも相当大きい。しかし、数量が大きくなればなるほど、打ち抜きリードフレームのリードフレーム1個あたりのコストは、リードフレームをエッティングする場合のコストのわずか何分の一かのコストになる。しかし、簡単な打ち抜き法では、上記「段状エッジ」形体を形成することができない。

20

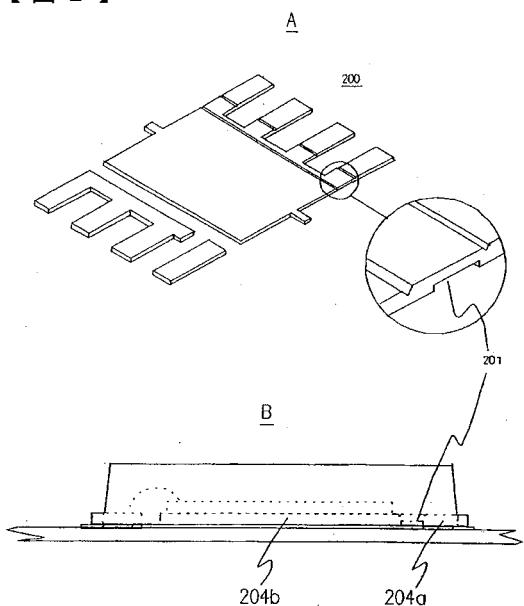

#### 【0021】

過去、スタンピングされるリードフレームで広く使用されてきたもう一つの作製法は「コイニング」である。この語は、硬貨のスタンピングと同様、金属中に形体をスタンピングする方法にちなむものである。この語は、半導体リードフレームに関して、リフロー中の軟質はんだの延展を止めるのに役立つ「凹形」のような形体、およびダイ取付エポキシ樹脂または封入材の密着力を改善する表面パターンを形成する場合に最も一般的に使用される。図2Aおよび2Bは、そのような形体を有するリードフレームの簡斜視図および断面図を示す。

20

#### 【0022】

しかし、コイニング法は、金属を除去するわけではなく、金属を単に再形成するだけである。したがって、肉薄化される区域がリードフレーム形体の相当の割合に及ぶならば、コイニングは一般的に、リードフレームにとって有用な方法ではない。

30

#### 【0023】

したがって、QFNおよび同様なリードレス半導体素子パッケージのためのリードフレームを作製するための、改良されたより費用効果の優れた技術が当技術分野で要望されている。

#### 【0024】

ノーリードパッケージより小さい熱的に強化されたプラスチックの非常に薄型および極めて非常に薄型のファインピッチ(JESD 30、識別子HVF-PDS0-NおよびHWF-PDS0-N)。例えば、特許文献1、2、3、4。長方形のダイサイズ、スタッカボールグリッドアレイファミリー、0.80mmピッチ(AF1R-PDSB.1)。例えば、特許文献5、6、7、8、9、10、11、12、13、14、15、16、17、18、19、20、21、22、23。熱的に強化されたプラスチックの非常に薄型および極めて非常に薄型のファインピッチバンブ形成されたクワッドフラットノーリードパッケージ(HP-VFQFP-NBおよびHP-WFQFP-NB)。例えば、特許文献24、25、26、27、28、29、30、31。プラスチッククワッドノーリード千鳥形多列パッケージ(H(V,W,U)F-PQFN)。例えば、特許文献32、33、34、35、36、37、38、39。熱的に強化されたプラスチックの超薄型および極薄型のファインピッチクワッドフラットノーリードパッケージ(H(U,X1)F-PQFP)。例えば、特許文献40、41、42、43、44、45。

40

#### 【0025】

50

- 【特許文献 1】米国特許第6,143,981号

【特許文献 2】米国特許第6,229,200B1号

【特許文献 3】米国特許第6,242,281B1号

【特許文献 4】米国特許第6,130,473号

【特許文献 5】米国特許第6,013,948号

【特許文献 6】米国特許第6,027,233号

【特許文献 7】米国特許第6,522,018号

【特許文献 8】米国特許第6,746,894号

【特許文献 9】米国特許第6,576,992号

【特許文献 10】米国特許第6,473,308号

【特許文献 11】米国特許第6,426,240号

【特許文献 12】米国特許第6,262,895号

【特許文献 13】米国特許出願第10/400,309号

【特許文献 14】米国特許出願第10/435,192号

【特許文献 15】米国特許出願第10/900,073号

【特許文献 16】米国特許出願第10/900,265号

【特許文献 17】米国特許出願第11/040,564号

【特許文献 18】米国特許出願第11/051,815号

【特許文献 19】米国特許出願第11/197,267号

【特許文献 20】米国特許出願第11/258,438号

【特許文献 21】米国特許出願第11/316,505号

【特許文献 22】米国特許出願第11/317,425号

【特許文献 23】米国特許出願第11/403,081号

【特許文献 24】米国特許第5,866,939号

【特許文献 25】米国特許第6,281,568号

【特許文献 26】米国特許第6,331,451号

【特許文献 27】米国特許第6,433,277号

【特許文献 28】米国特許第6,455,356号

【特許文献 29】米国特許第6,469,369号

【特許文献 30】米国特許第6,475,827号

【特許文献 31】米国特許第6,476,478号

【特許文献 32】米国特許第6,498,099号

【特許文献 33】米国特許第6,635,957号

【特許文献 34】米国特許第6,872,661号

【特許文献 35】米国特許第6,933,594号

【特許文献 36】米国特許第6,946,324号

【特許文献 37】米国特許第6,964,918号

【特許文献 38】米国特許第6,989,294号

【特許文献 39】米国特許第6,995,460号

【特許文献 40】米国特許第6,448,633号

【特許文献 41】米国特許第6,501,161号

【特許文献 42】米国特許第6,521,987号

【特許文献 43】米国特許第6,525,406号

【特許文献 44】米国特許第6,294,100B1号

【特許文献 45】米国特許第6,585,905B1号

【発明の開示】

【発明が解決しようとする課題】

【0026】

本発明は、複数の金属層から形成される半導体素子パッケージリードフレームを提供することを課題とする。

10

20

30

40

50

**【課題を解決するための手段】****【0027】****発明の概要**

半導体素子パッケージのための、隆起した形体を有する本発明のリードフレームの態様は、少なくとも二つの金属層を接合することによって作製することができる。第一の金属層が、任意のダイパッドおよびリードを含めたリードフレームの横方向寸法を画定する。第一の金属層に接合された第二の金属層が、リードフレームの隆起した形体、たとえばリードフレームをパッケージ本体内に物理的に固着するための段を画定する。複数の金属層は、非制限的に、超音波溶接、軟質はんだ付けまたはエポキシ樹脂の使用を含む多数の可能な技術によって接合することができる。接合の前または後で、金属層の一つまたは複数をコイニングまたはスタンピングして、オフセットまたは溝のようなさらなる形体を形成することもできる。

**【0028】**

半導体素子パッケージのためのリードフレームを作製するための本発明の方法の態様は、リードフレームを画定する第一の金属層を設ける工程、リードフレームの隆起した形体を画定する第二の金属層を設ける工程、および第一の金属層を第二の金属層に接合する工程を含む。

**【0029】**

半導体素子パッケージのための本発明のリードフレームの態様は、リードフレームを画定する第一の金属層と、第一の金属層に接合され、隆起した形体を画定する第二の金属層とを含む。

**【0030】**

本発明の半導体素子パッケージの態様は、リードフレーム上に支持されたダイを含み、リードフレームが第二の金属層に接合された第一の金属層を含み、第二の金属層がリードフレームの隆起した形体を画定する。

**【0031】**

本発明(1)は、以下の工程を含む、半導体素子パッケージのためのリードフレームを作製する方法である：

リードフレームを画定する第一の金属層を設ける工程；

リードフレームの隆起した形体を画定する第二の金属層を設ける工程；および

該第一の金属層を該第二の金属層に接合する工程。

本発明(2)は、超音波溶接によって第一の金属層を第二の金属層に接合する、本発明(1)の方法である。

本発明(3)は、エポキシ樹脂によって第一の金属層を第二の金属層に接合する、本発明(1)の方法である。

本発明(4)は、はんだによって第一の金属層を第二の金属層に接合する、本発明(1)の方法である。

本発明(5)は、第二の金属層をパターン付けして、DPAK、D2PAK、T0-220、T0-247、SOT-223、TSSOP-x、SO-x、SSOP-x、TQFP、SE70-8、TSOP-8およびTSOP12からなる群より選択されるパワータイプパッケージのダイパッド上に隆起した形体を形成する、本発明(1)の方法である。

本発明(6)は、第二の金属層をパターン付けして、リードをプラスチックの本体内に固着するための段としての隆起した形体を形成する、本発明(1)の方法である。

本発明(7)は、第二の金属層をパターン付けして、パッケージ中の二つのダイを接続するトレースとしての隆起した形体を形成する、本発明(1)の方法である。

本発明(8)は、第二の金属層をパターン付けして、パッケージの周囲にダイ接点を接続分布させるトレースとしての隆起した形体を形成する、本発明(1)の方法である。

本発明(9)は、

リードフレームを画定する第一の金属層と、

該第一の金属層に接合され、該リードフレームの隆起した形体を画定する第二の金属層

10

20

30

40

50

とを含む、

半導体素子パッケージのためのリードフレームである。

本発明(10)は、第二の金属層が第一の金属層に溶接されている、本発明(9)のリードフレームである。

本発明(11)は、第一の金属層と第二の金属層との間にエポキシ樹脂をさらに含む、本発明(9)のリードフレームである。

本発明(12)は、第一の金属層と第二の金属層との間にはんだをさらに含む、本発明(9)のリードフレームである。

本発明(13)は、隆起した形体が、リードをプラスチックのパッケージ本体内に固着する段を含む、本発明(9)のリードフレームである。10

本発明(14)は、隆起した形体が、パッケージ中の二つのダイを接続する導電トレースを含む、本発明(9)のリードフレームである。

本発明(15)は、隆起した形体が、パッケージの周囲にダイ接点を分布させる導電トレースを含む、本発明(9)のリードフレームである。

本発明(16)は、リードフレーム上に支持されたダイを含み、該リードフレームが、第二の金属層に接合された第一の金属層を含み、該第二の金属層が、該リードフレームの隆起した形体を画定するものである半導体素子パッケージである。

本発明(17)は、第二の金属層が溶接、エポキシ樹脂またははんだによって第一の金属層に接合されている、本発明(16)のパッケージである。

本発明(18)は、隆起した形体が、リードをパッケージ本体内に固着する段、ダイを該パッケージ本体内の第二のダイと接続する導電トレース、または該パッケージ本体の周囲にダイ接点を分布させる導電トレースから選択される、本発明(16)のパッケージである。20

### 【0032】

本発明のこれらおよび他の態様ならびにその特徴および潜在的な利点を、以下の文および添付図面と併せてさらに詳細に説明する。

### 【発明の効果】

### 【0033】

本発明により、複数の金属層から形成される半導体素子パッケージリードフレームが提供された。30

### 【発明を実施するための最良の形態】

### 【0034】

#### 発明の詳細な説明

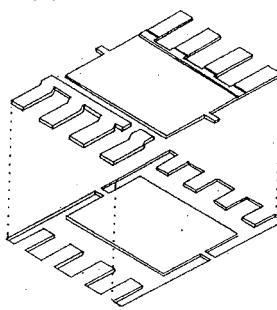

半導体素子パッケージのための、隆起した形体を有する本発明の態様のリードフレームは、少なくとも二つの金属層を接合することによって作製することができる。第一の金属層が、任意のダイパッドおよびリードを含めたリードフレームの横方向寸法を画定する。第一の金属層に接合された第二の金属層が、リードフレームの隆起した形体、たとえばリードフレームをパッケージ本体内に物理的に固着するための段を画定する。複数の金属層は、非制限的に、超音波溶接、軟質はんだ付けまたはエポキシ樹脂の使用を含む多数の可能な技術によって接合することができる。接合の前または後で、金属層の一つまたは複数をコイニングまたはスタンピングして、オフセットまたは溝のようなさらなる形体を形成することもできる。40

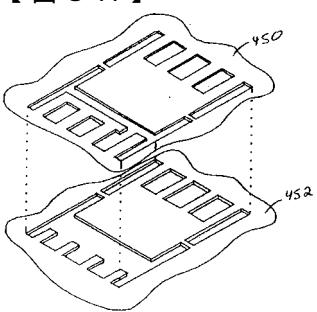

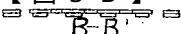

### 【0035】

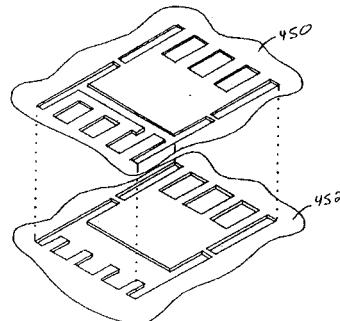

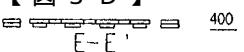

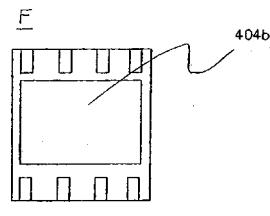

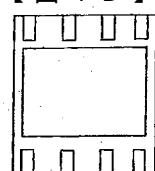

本発明の一つの態様で、ロッキングおよび耐水性は、先に例証した形体と同様な形の形体を用いて、二つのリードフレームをスタンピングして、上リードフレーム450の区域がリードフレームの上またはダイ側(図3A)の区域を形成し、下半分452が、パッケージの下面(図3B)における電気的および熱的接続に曝露される銅を形成するようにすることによって実現することができる。その結果として得られるフットプリントが図3Fに示されている。リードフレームの二つの層450および452を積層して、ピンに関して先に記載したロッキング形体を有する单一の銅リードフレームを形成することもでき、ダイパッド404a(図3E)50

のような大きな区域が単一の層であることもでき、プラスチックで封入し、パッケージ(図3E)の下面に露出させないことができる。

【0036】

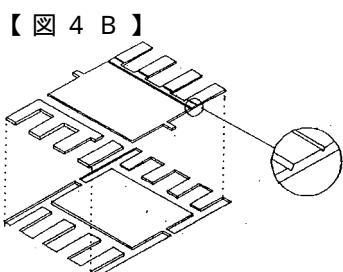

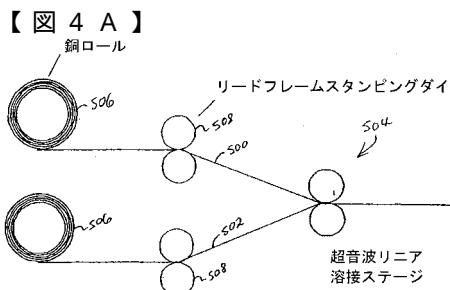

二つのリードフレーム層の積層は、いくつかの方法のいずれかを使用して達成することができる。一つの積層法は、リニアフィード超音波溶接法504を使用して融合される二つの銅リードフレーム層500および502を使用する。大量生産では、この方法は、二つの銅ロール506からリードフレーム材料を二つの平行なリニアスタンピングステージ508に直接通して取り出し、整列させ、リニア超音波溶接ステージに送り込んだのち、リードフレームを、既存の取り扱い設備に送り込む長さに切断するように構成することができる(図4A)。

【0037】

本発明の態様は、同一材料の二つの層または等しい厚さの二つの層に限定されず、さらに、二つの層にさえ限定されない。二つの異なる銅系合金を使用して、ダイもしくはPCボードへの接合を最適化するか、または露出面の起伏を増大させることが有利であるかもしれない。異なる金属の二つの層を積層することがまた有利であるかもしれない。いくつかの金属の組み合わせは、超音波溶接による積層法に好適であり、一つの表面が界面またはバリヤ材料で予備めっきされる場合には、他の多くを組み合わせることができる。

【0038】

リードフレームの表面にコイニングすることができる形体、たとえばはんだ凹形または水分浸透バリヤは、単層銅リードフレームの場合と同じプロセスに含めることができる(図4B)。積層されたリードフレームをスタンピングして、アップセットまたはダウンセットのような形体をリードフレームの積層区分上に形成することもできる(図4C)。個々の層を積層の前にコイニングまたはオフセットすることを可能にする多層リードフレーム法を設計することもできる。これらの場合、リードフレームを適当な長さに切断し、個々の標準マトリックス長さ区分またはそれらの群に熱および圧力を加えるように設計されたステージを使用して層を積層することが有利であるかもしれない。

【0039】

経済的であるかもしれない代替積層法は、リードフレームの二つの層どうしを軟質はんだ付けする方法である。二つのリードフレーム半部分の間のはんだの配置および量の入念な制御により、継ぎ目の外側に沿った「はみ出し」の量を最小限にすることができる。接合部に沿ったはんだはみ出しは、除去しにくく、最終パッケージ中のプラスチック封入材を肉薄化し、それがプラスチック材料の破損を招くおそれがある。はんだはみ出しに対してより寛容になるように、簡単なリードフレームを設計でき、かつはんだの配置および量を制御するいくつかの方法が製造環境で経済的かつ確実であり得るが、一つの態様では、軟質はんだ法は、リードフレーム材料の片方の半分を薄いはんだ層で予備めっきすることであると考えられる。次いで、リードフレーム材料をはんだリフロー温度に加熱し、制御された圧力の下でリードフレーム層どうしを合わせるリニアステージで積層を達成することができる。

【0040】

もう一つの代替態様は、エポキシ樹脂を使用してリードフレーム層を積層するものであろう。現在のエポキシ樹脂沈積制御は、簡単なリードフレームを積層するのに適切である。導電性および非導電性エポキシ樹脂両方による半導体ウェーハの「スクリーン印刷」がより通例になるにつれ、それが積層に最適な方法になると考えられる。

【0041】

エポキシ樹脂が提供する一つの利点は、二つの重複するリードフレーム層、すなわちダイ-リードフレーム界面を電気的および/または熱的に接触させながらも(図5Cに示す態様のダイパッド604aを参照されたい)、同じリードフレーム/ダイの他の二つのリードフレーム層を機械的に取り付け、かつ電気的に隔離する(図5Cに示す態様のリード604bを参照されたい)ことを可能にするパターンでプリントすることができる導電性および非導電性接合材料の選択の幅である。これは、充填して、隔離を提供するための射出成形のために層と層との間に空間を残す方法よりも薄型で、制御しやすく、かつ確実な、二つの隣接層

10

20

30

40

50

を隔離する方法であり得る。

#### 【0042】

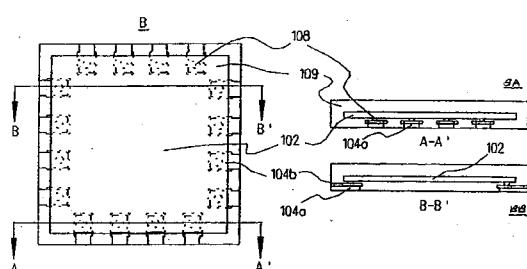

多層リードフレームをダイ取付／電気接続のためのフリップチップ法と組み合わせると、ダイパッドを完全になくすことができる。図6A～ABは、「ボール」法を使用するダイ取付を示す。図6Aは、「フリップチップ」で取り付けられたダイ(102)とで組み立てられ、各ダイボンディングパッドで標準はんだボール(108)を用いて電気的かつ機械的取付が設けられている多層リードフレーム(層104aおよび104b)アセンブリを示す。図6Aに示すフリップチップ取付構造の、同じパッケージの従前のワイヤボンディングバージョンと比較した場合の利点は、大幅に増大したダイサイズである。この構造の欠点は、ダイをPCボードのレイアウトおよびスペーシング規則に従わせるということである。PCボードへの接点はなおも0.5mmピッチであり、それを超えると、PCボード製造は大幅な費用増を要し、ダイスペーシング規則はより厳しいピッチを許し、それがダイ上の空間を無駄にする。

#### 【0043】

図6B～BBは、「バンプ」法を使用するダイ取付を示す。図6Bは、「フリップチップ」で取付けられたダイ(102)とで組み立てられ、各ダイボンディングパッドで標準はんだ「バンプ」(108)を用いて電気的かつ機械的取付が設けられている多層リードフレーム(層104aおよび104b)アセンブリを示す。

#### 【0044】

本発明の他の態様は、フリップチップ取付されたダイの下でリードフレームを使用して、ピン配列を割り振りし直すか、または二つまたはそれ以上のダイを相互接続することを可能にすることができる。たとえば、ダイ上の形体サイズはPCボードの形体サイズよりもずっと小さく、したがって、従来、ワイヤもしくはバンプのためのボンディングパッドまたはボール電気接続は、従来のパッケージの形体サイズに適合するようなスペーシングおよびサイズを付されなければならず、それには、PCボード技術と適合性であるピンスペーシングを満足させなければならなかつた。この問題を解決する一つの手法は、シリコン面積を節約するために相互接続パッド(ボールまたはバンプ)をダイ上で分布させ直す手法である。この利点は、ダイへの電気接続がワイヤボンディングされる場合に例証され得るが、ダイがバンプされ、リードフレームにフリップチップ取付される場合さらに顕著に現れる。

#### 【0045】

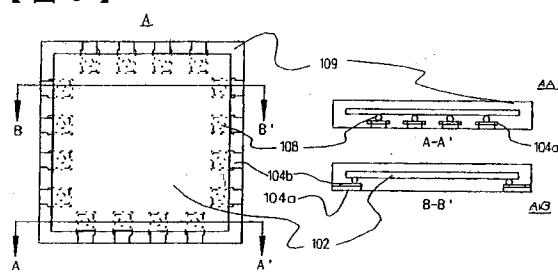

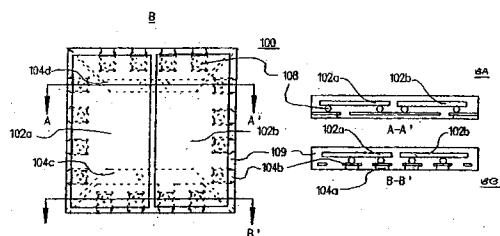

電気接点がダイ上で最小の空間しか占有しないように最適化されたバンプパッド配置およびサイズを用いると、本発明の態様にしたがってリードフレームの下面を設計して、接続を、PCボード設計規則に準拠する列に配置されたリードまで延ばすことができる。図7A～ABは、標準の0.5mmピッチのQFNパッケージ(100)を、(单一の)ダイ(102)上の空間を節約するための0.25mmピッチのボンディングパッドおよびボールもしくはバンプ(108)とともに示す。すべての「ルーティング」はリードフレームの上層(104b)で実施され、封入後にパッケージの背面に露出するリードフレームだけがリードフレームの下層(104a)である。

#### 【0046】

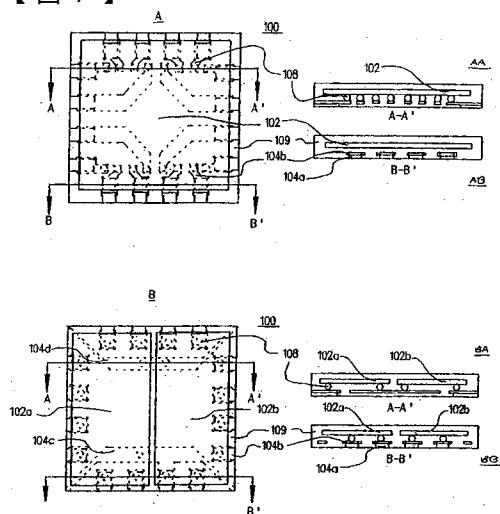

この手法を利用すると、单一のパッケージ内に収容された複数のダイへの空間効率的な接続を可能にすることもできる。図7B～BAは、標準の0.5mmピッチのQFNパッケージ(100)を、デュアルダイ(102)を物理的に支持するパターンで分布したボンディングパッドおよびボールもしくはバンプ(108)とともに示す。この例では、ダイ間の相互接続のための二つの代替方法が例証されている。相互接続部104dは、104bと同じ層であり、パッケージの外に通じるピンに接続せずに、二つのダイ上の電気ノードを電気的に接続する。他方の相互接続部104c(同じく、パッケージ背面に露出していない層104b)は、二つのダイ上のノードを電気的に接続し、外部ピンにもまた接続する。

#### 【0047】

そのうえ、マルチダイアセンブリでは、ピン上で外に送る必要のない、異なるダイ上のノードの相互接続がよく見られる。したがって、本発明のさらなる態様にしたがって、ト

10

20

30

40

50

レースをダイの下に通してマルチダイアセンブリ中の別個のダイ上のノードを相互接続することができる。相互接続トレースを単一層にすることにより、相互接続トレースを完全に封入することができる。

【0048】

図7A～Bに示す態様と類似した本発明の態様は、変調DC-DC電力変換の場合のような、周波数を連続的に増大させてコンポーネントをより小さくし、効率をより高くする用途の必要性に対応することができる。PWMコントローラ・パワーステージ・出力装置の接続を可能な限り接近させ、かつ可能な限り漂遊インダクタンスのない状態に維持する必要性が重要であるかもしれない。一部の周波数では、ダイは、共通のパッケージ内の同じ場所に配置することができ、ボンドワイヤだけがバンプまたはボール取付を必要とする。コイニングされた形体および／またはスタンピングされた「アップセット」もしくは「ダウンセット」形体を本発明の態様の多層リードフレームとともに使用すると、別個のワイヤボンディングされたパッケージでダイを使用する従来方法の場合よりも約一桁少ない漂遊インダクタンスでダイ間の隔離された相互接続を達成することができる。

10

【0049】

上記した本発明の態様の多層銅リードフレームの使用に加えて、パッケージ中の層または層の一部の隔離は、ダイを取り付け、電気的または熱的にリードフレームに接続する前に、リードフレームの層または層の一部の「予備封入」を要するかもしれない。層または層の一部の予備封入はまた、さらなる能力、たとえば相互接続のための隔離されたランディングパッドを保持する能力、ならびに高エネルギーボンディング処理および／またはアルミニウムリボンボンディングの場合に求められるような切り取りもしくは「引き裂き」処理中にリードフレームをしっかりと締め付けるための隔離された支持を提供する能力を追加することができる。

20

【0050】

本発明の態様にしたがって多金属層の使用によって作り出されるリードフレーム上の隆起したパターンは、QFNパッケージだけでなく、非制限的に、DPAK、D2PAK、T0-220、T0-247、SOT-223、TSSOP-x、SO-x、SSOP-x、TQFP、ならびにSE70-8、TSOP-8およびTSOP12を含むJリードファミリのパッケージを含む他のタイプのパッケージに有用であるかもしれない。

30

【0051】

上記は、具体的な態様を十分に説明したものであるが、様々な改変、代替構造および等価物を使用することもできる。したがって、上記説明および例示は、添付の請求の範囲によって画定される本発明の範囲を限定するものとみなされるべきではない。

【図面の簡単な説明】

【0052】

【図1A】従来のQFNパッケージの略底部平面図を示す図である。

【図1B】図1AのパッケージをB-B'線から見た略断面図を示す図である。

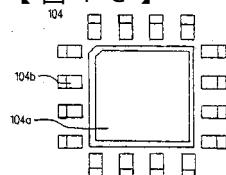

【図1C】図1A～Bの従来のパッケージの、リードフレームのみの略平面図を示す図である。

40

【図1D】図1A～Bのパッケージを作製するために使用されるようなパターンの孔を有する銅合金シートの略平面図を示す図である。

【図1E】図1Cのリードフレームを作製するための具体的な工程の略断面図を示す図である。

【図1F】図1Cのリードフレームを作製するための具体的な工程の略断面図を示す図であり、図1Eの続きである。

【図1G】図1Cのリードフレームを作製するための具体的な工程の略断面図を示す図であり、図1Fの続きである。

【図1H】図1Cのリードフレームを作製するための具体的な工程の略断面図を示す図であり、図1Gの続きである。

【図2】図2Aおよび図2Bは典型的なはんだ凹形および水分バリヤを含むリードフレームパ

50

ッケージの、それぞれ略斜視図および略断面図を示す図である。

【図3A】多層リードフレームの二つの部分の積層前の略分解図を示す図である。

【図3B】二つの金属層の積層後の図3Aのリードフレームの、略断面図を示す図である。

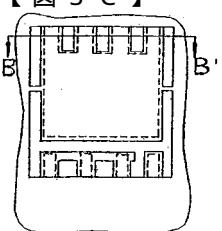

【図3C】二つの金属層の積層後の図3Aのリードフレームの、略平面図を示す図である。

【図3D】複数の金属層を含むリードフレームの代替態様の、略断面図を示す図である。

【図3E】複数の金属層を含むリードフレームの代替態様の、略平面図を示す図である。

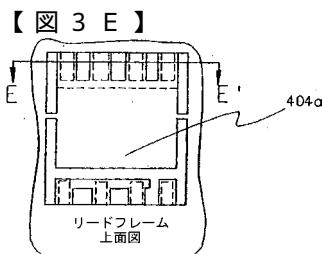

【図3F】図3D～Eのリードフレームを有するパッケージの略底部平面図を示す図である。

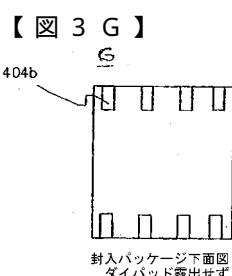

【図3G】本発明のリードフレームの代替態様を有するパッケージの略底部平面図を示す図である。

【図4A】複数の金属層からリードフレームを形成するための本発明の方法の一つの態様の略図を示す図である。

【図4B】コイニングによって形成された溝を特徴とする、本発明の態様の複数金属層リードフレームの態様の略分解図を示す図である。

【図4C】ポンディング区域をダイの厚さにほぼ等しいレベルまでダウンセットした(図中では隆起)リードレスパワーパッケージについてのリードフレームの略分解反転図を示す図である。

【図4D】図4Cのリードフレームを使用した封入パッケージの下面図を示す図である。

【図5】ダイのより厳しいレイアウト規則を活用するために分布させ直したダイへの電気接点(ボンドワイヤ)によってワイヤポンディングされたダイの種々の略図を示す図である。

【図6】図6Aは各ダイポンディングパッドで標準はんだボールを用いて設けられた電気的および機械的取付を有する、本発明の多層リードフレームを含むパッケージの態様の略平面図を示す図である。図6AAは図6AのパッケージをA-A'線から見た略断面図を示す図である。図6ABは図6AのパッケージをB-B'線から見た略断面図を示す図である。図6Bは各ダイポンディングパッドで標準はんだバンプを用いて設けられた電気的および機械的取付を有する、本発明の態様の多層リードフレームを含むパッケージの代替態様の略平面図を示す図である。図6BAは図6BのパッケージをA-A'線から見た略断面図を示す図である。図6BBは図6BのパッケージをB-B'線から見た略断面図を示す図である。

【図7】図7Aは本発明の多層リードフレームを含む単一ダイパッケージの態様の略平面図を示す図である。図7AAは図7AのパッケージをA-A'線から見た略断面図を示す図である。図7ABは図7AのパッケージをB-B'線から見た略断面図を示す図である。図7Bは本発明の態様の多層リードフレームを含む2ダイパッケージの態様の略平面図を示す図である。図7BAは図7BのパッケージをA-A'線から見た略断面図を示す図である。図7BBは図7BのパッケージをB-B'線から見た略断面図を示す図である。

【図 1 A】

(先行技術)

【図 1 B】

(先行技術)

【図 1 C】

(先行技術)

【図 1 D】

(先行技術)

【図 1 E】

(先行技術)

【図 1 F】

(先行技術)

【図 1 G】

(先行技術)

【図 1 H】

(先行技術)

【図 2】

【図 3 A】

【図 3 B】

【図 3 C】

【図 3 D】

【図 3 F】

【図 4 D】

封入パッケージ下面図

露出したダイパッド

【図 5】

【図 4 C】

【図 6】

【図7】

---

フロントページの続き

(72)発明者 チア アンソニー

シンガポール シンガポール ベドック ノース アヴェニュー #2 #7-105

(72)発明者 ウォング リミング

中華人民共和国 シャンハイ ジアディング ユミング ロード ナンバー 338 ナンバー

30 ルーム 201

(72)発明者 ヤング ホングボ

中華人民共和国 シャンハイ ジアディング ナン ユアン レジデンシャル フォース クォー

ター ナンバー 26 ルーム 301

F ターム(参考) 5F067 AA01 AB04 BD02 BD10 DA05 DA07 DA14 DA20 DF17