(12)发明专利申请

(10)申请公布号 CN 109587413 A

(43)申请公布日 2019.04.05

(21)申请号 201811117332.2

(22)申请日 2018.09.26

(30)优先权数据

2017-192056 2017.09.29 JP

(71)申请人 佳能株式会社

地址 日本东京

(72)发明人 小林秀央

(74)专利代理机构 中国国际贸易促进委员会专

利商标事务所 11038

代理人 宿小猛

(51)Int.Cl.

H04N 5/341(2011.01)

H04N 5/3745(2011.01)

H04N 5/376(2011.01)

H04N 5/378(2011.01)

权利要求书2页 说明书9页 附图13页

(54)发明名称

成像装置、成像系统和移动体

(57)摘要

本公开涉及成像装置、成像系统和移动体。设置在第一方向上的第一像素组在第一方向被读取。与第一像素组相邻的第二像素组在与第一方向相反的第二方向上被读取。

1. 一种装置，其特征在于，包括：

包含以矩阵形式布置的多个像素的像素块；

被配置为处理从所述多个像素读取的信号的处理单元；和

被配置为控制所述多个像素的读取顺序的读取单元，

其中，读取单元在第一方向上读取包含所述多个像素的一部分的第一像素组，并且，在读取第一像素组之后，在与第一方向相反的第二方向上读取第二像素组，所述第二像素组包含所述多个像素的与第一像素组相邻的部分。

2. 根据权利要求1所述的装置，包括第三像素组，所述第三像素组包含所述多个像素的与第二像素组相邻的部分，

其中，在第二像素组被读取之后，第三像素组在第一方向上被读取。

3. 根据权利要求1所述的装置，还包括：

包含多个像素块的第一芯片；和

包含多个处理单元的第二芯片，

其中，第一芯片和第二芯片被层叠在一起。

4. 根据权利要求3所述的装置，包括：

第一像素块；和

与第一像素块相邻设置的第二像素块，

其中，第一像素块的第一像素组和第二像素块的第一像素组被设置为彼此相对，以及

其中，第一像素块的第一方向和第二像素块的第一方向彼此相反。

5. 根据权利要求4所述的装置，包括：

第一处理单元；和

与第一处理单元相邻设置的第二处理单元，

其中，第一处理单元与第一像素块对应地设置，以及

其中，第二处理单元与第二像素块对应地设置。

6. 根据权利要求1所述的装置，其中，第一方向和第二方向是行方向或列方向。

7. 根据权利要求1所述的装置，

其中，所述多个像素中的每一个包含被设置为与单个微透镜对应的第一光电转换单元和第二光电转换单元，以及

其中，第一光电转换单元和第二光电转换单元彼此相邻的方向与第一方向相同。

8. 根据权利要求1所述的装置，

其中，处理单元包含被配置为将从像素块输出的模拟信号转换成数字信号的模拟数字(AD)转换单元，

其中，AD转换单元包含被配置为比较模拟信号与比较信号的比较器，

其中，箝位电容器连接到比较器的输入节点，

其中，模拟信号被输入到箝位电容器的一个节点，以及

其中，复位信号被输入到箝位电容器的另一节点。

9. 根据权利要求8所述的装置，其中，处理单元包含在箝位电容器与像素块之间的采样保持电容器。

10. 根据权利要求8所述的装置，其中，关于在其中复位信号被输入到箝位电容器的时

段,在其中关于所述多个像素中要最后读取的像素的复位信号被输入的第一时段比在其中关于所述多个像素中要最后读取的像素以外的像素的复位信号被输入的第二时段长。

11.根据权利要求8所述的装置,其中,关于复位信号被输入到箝位电容器的次数,在读取所述多个像素中要最后读取的像素之后复位信号被输入的次数大于在读取所述多个像素中要最后读取的像素以外的像素之后复位信号被输入的次数。

12.一种系统,其特征在于,包括:

根据权利要求1所述的装置;和

处理单元,被配置为处理从所述装置输出的信号,由此产生图像。

13.根据权利要求12所述的系统,

其中,所述装置还包括第三像素组,所述第三像素组包含所述多个像素的与第二像素组相邻的部分,以及

其中,在第二像素组被读取之后,第三像素组在第一方向上被读取。

14.根据权利要求12所述的系统,其中,所述装置还包括:

包含多个像素块的第一芯片;和

包含多个处理单元的第二芯片,

其中,第一芯片和第二芯片被层叠在一起。

15.根据权利要求12所述的系统,其中,第一方向和第二方向是行方向或列方向。

16.一种移动体,其特征在于,包括:

根据权利要求1所述的装置;

距离信息获取单元,被配置为从基于来自所述装置的信号的视差图像获取关于到目标物体的距离的信息;和

控制单元,被配置为基于距离信息控制移动体。

17.根据权利要求16所述的移动体,

其中,所述装置还包括第三像素组,所述第三像素组包含所述多个像素的与第二像素组相邻的部分,以及

其中,在第二像素组被读取之后,第三像素组在第一方向上被读取。

18.根据权利要求16所述的移动体,其中,所述装置还包括:

包含多个像素块的第一芯片;和

包含多个处理单元的第二芯片,

其中,第一芯片和第二芯片被层叠在一起。

19.根据权利要求16所述的移动体,其中,第一方向和第二方向是行方向或列方向。

## 成像装置、成像系统和移动体

### 技术领域

[0001] 各方面的实施例涉及成像装置、成像系统和移动体。

### 背景技术

[0002] 互补金属氧化物半导体(CMOS)传感器是已知的，其是通过在第一芯片上设置像素、在第二芯片上设置对应于像素中的一个或更多个的模拟数字转换单元(AD转换单元)、并且利用Cu-Cu接合来接合第一芯片和第二芯片获得的。在日本专利申请特开No.2014-155175中，被单个AD转换单元覆盖的部分的面积对应于被多个像素覆盖的部分的面积。因此，设置在第一芯片上的多个像素和设置在第二芯片上的单个AD转换单元被相互关联地连接在一起。

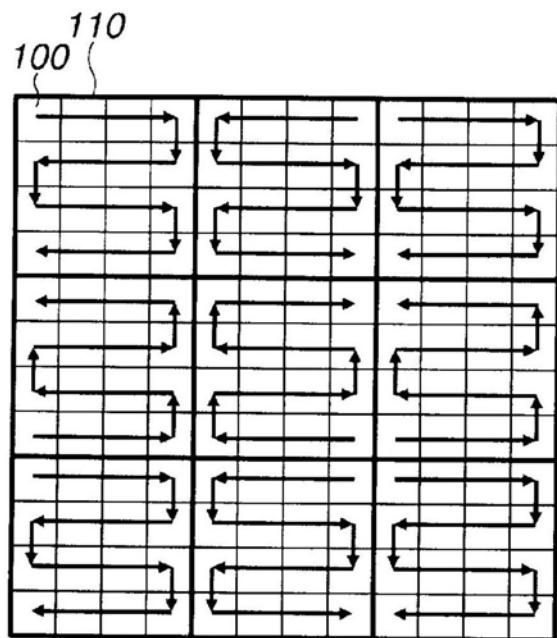

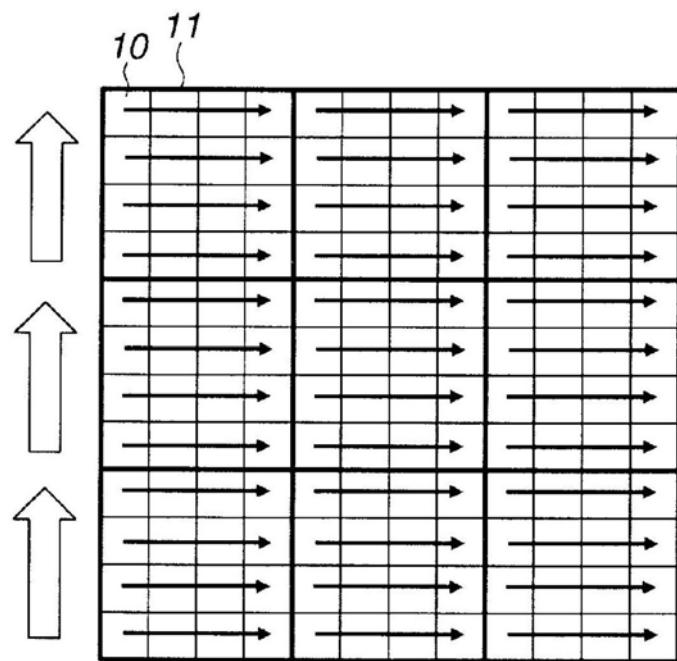

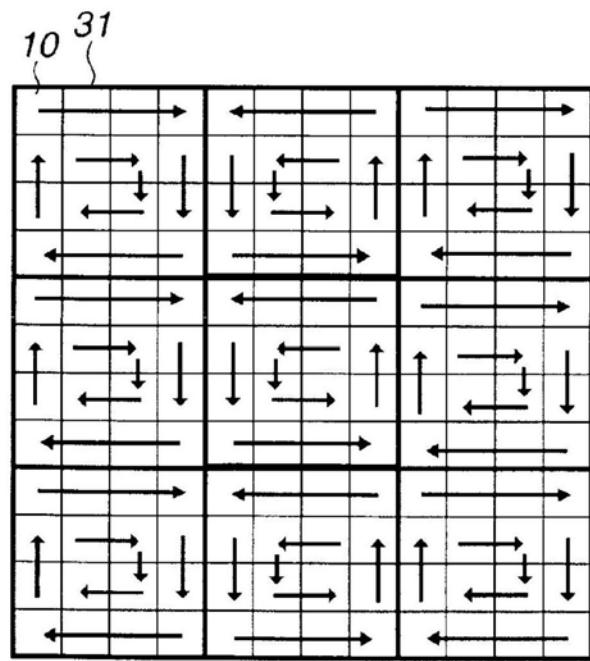

[0003] 日本专利申请公开No.2014-155175讨论了图10(对应于日本专利申请公开No.2014-155175的图1)中的读取顺序。图10示出在日本专利申请公开No.2014-155175中讨论的读取方法的概念图。细线矩形10代表像素。粗线矩形11代表像素块。单个像素块11包含 $4 \times 4$ 即总共16个像素10。图10示出设置九个像素块11的例子。在各像素块11中，以第四行第一列中的像素为开始点，在行方向上开始读取。即，在从第四行第一列到第四行第四列的方向上执行读取。然后，依次地，从第三行第一列到第三行第四列，以及从第二行第一列到第二行第四列执行读取。然后，最后读取第一行第四列的像素。

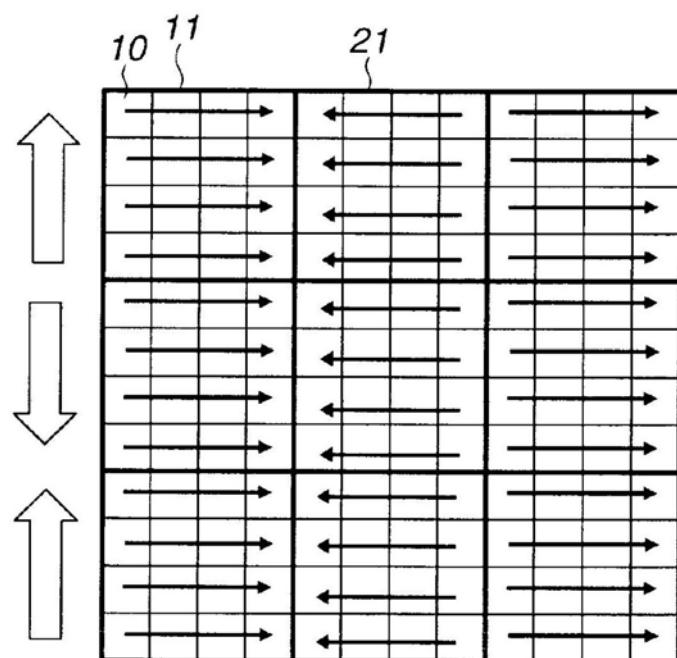

[0004] 此外，日本专利申请公开No.2014-155175还讨论了图11A(对应于日本专利申请公开No.2014-155175的图5)中的读取顺序。在图11A中，像素块11的读取顺序与像素块21的读取顺序不同。在像素块11中，执行与图10中的像素块11的读取方法类似的读取方法。另一方面，在像素块21中，以第四行第四列中的像素为开始点，从第四行第四列到第四行第一列执行读取。要读取的行依次在较小行号的方向上偏移。然后，最后读取第一行第一列中的像素。

[0005] 在图10中的读取顺序的情况下，相邻的像素块之间的边界上的像素的读取定时不相互匹配。作为其结果，在图10中的读取顺序的情况下，存在像素块之间的边界上的图像中出现不连续的可能性。另一方面，根据图11A中的读取顺序，位于相邻的像素块之间的边界上的像素的读取定时相互接近。这可以减少在像素块之间的边界上出现的不连续。

[0006] 此外，日本专利申请公开No.2014-155175还讨论了图11B(对应于日本专利申请公开No.2014-155175的图6)中的读取顺序。在图11B中的像素块31中，以像素块31的四个顶点(例如，第一行第一列、第一行第四列和第四行第四列)中的任一个为开始点，读取在行方向上被执行并然后螺旋偏移到像素块31的中心。同样，在图11B的情况下，与图11A中的读取顺序类似，位于相邻的像素块之间的边界上的像素的读取定时相互接近。这可以减少在像素块之间的边界上出现的不连续。

[0007] 在图10中的读取顺序中，在左上角的像素块11中，紧接着在读取第二行第四列中的像素之后，读取第一行第一列中的像素。类似地，在图11A中的左上角的像素块21中，紧接着在读取第二行第四列中的像素之后，读取第一行第一列中的像素。即，在读取偏移到相邻的行

的情况下,下一个读取的像素总是处于与像素块的列数对应的距离。

[0008] 顺便提及,复位残余可能在用于处理从像素输出的信号的信号处理单元中发生。即,存在应被复位的位置没有被充分复位的可能性。例如,存在设置在包含于AD转换单元中的比较器的输入处的箝位电容器的复位电势不能达到希望的值的可能性。由于此,先前读取的像素的信号影响下一个读取的像素的信号(串扰)。在使用图10和图11A中的读取顺序的情况下,并且,当强光入射于例如像素块的右端(第二行第四列)的像素时,存在如下可能性:通过用具有大于或等于正常入射光的光量的量的光照射远离右端列的在左端(第一行第一列)的像素形成图像。即使由复位残余导致的串扰非常小,但如果右端列和左端列相互远离,则与在相邻的像素中出现串扰的情况相比,作为图像,串扰更加明显。

[0009] 另一方面,图11B中的读取方法也存在问题。即,在图11B中的读取顺序中,在读取像素块31的第一行的左端处的像素的时间与读取像素块31的第二行的左端处的像素的时间之间存在大的差异。例如,在图11B的例子中,在读取第一行第一列中的像素之后11个像素处读取第二行第一列中的像素。作为其结果,相邻像素的读取定时之间的差异变大,这增加了在图像中出现不连续的可能性。

[0010] 如上所述,如果使用日本专利申请公开No.2014-155175的图1和图5(对于本申请的图10和图11A)中的读取顺序,则存在形成如下图像的可能性,在该图像中源自诸如AD转换单元的信号处理单元的复位残余的串扰明显。

[0011] 此外,如果使用日本专利申请公开No.2014-155175的图6(对于本申请的图11B)中的读取顺序,则相邻像素的读取定时之间的差异变大,并且存在物体的图像变得不连续的可能性。

[0012] 即,根据在日本专利申请公开No.2014-155175中讨论的成像装置,不能形成具有良好质量的图像。

## 发明内容

[0013] 根据实施例的某个方面,装置包括:包含以矩阵方式布置的多个像素的像素块;被配置为处理从所述多个像素读取的信号的处理单元;和被配置为控制所述多个像素的读取顺序的读取单元,其中,读取单元在第一方向上读取包含所述多个像素的一部分的第一像素组,并且,在读取第一像素组之后,在与第一方向相反的第二方向上读取第二像素组,第二像素组包含所述多个像素的与第一像素组相邻的一部分。

[0014] 参照附图阅读示例性实施例的以下说明,本发明的其它特征将变得清晰。

## 附图说明

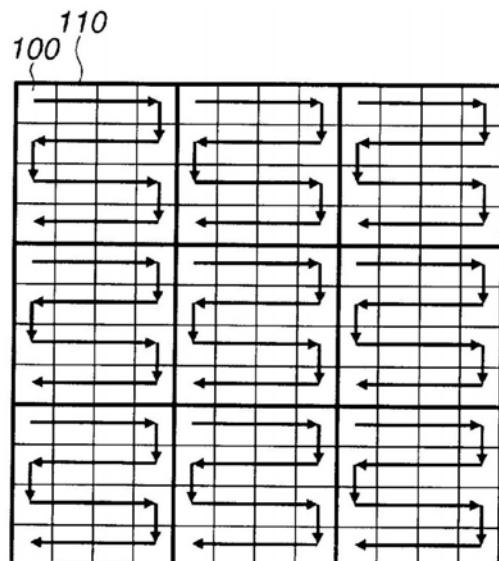

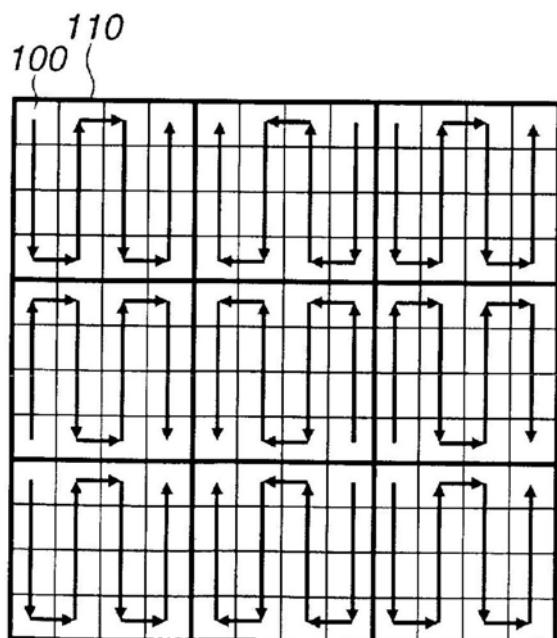

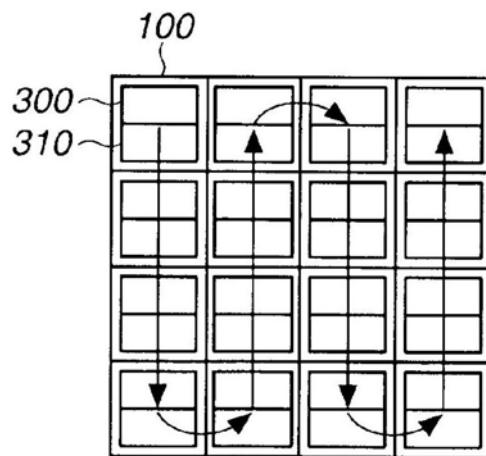

[0015] 图1A和图1B是示出根据第一示例性实施例的成像装置的示意图。

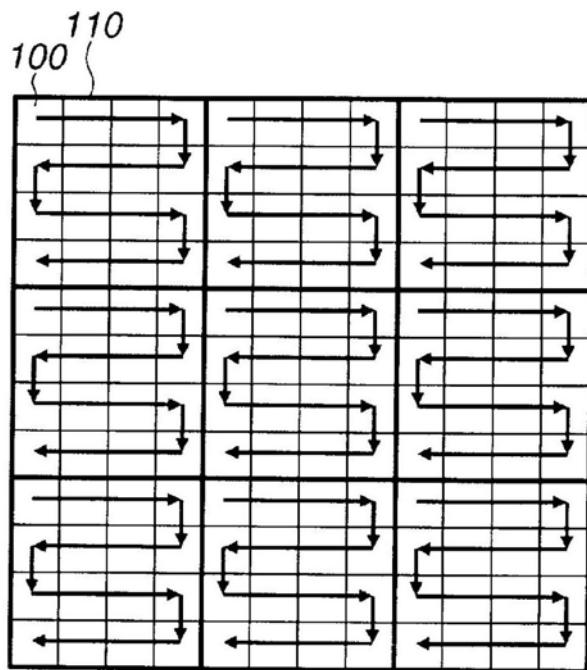

[0016] 图2A和图2B是示出根据第一示例性实施例的成像装置的示意图。

[0017] 图3A、图3B和图3C是示出根据第一示例性实施例的成像装置的示意图。

[0018] 图4是示出根据第一示例性实施例的成像装置的示意图。

[0019] 图5是根据第一示例性实施例的成像装置的定时图。

[0020] 图6是示出根据第一示例性实施例的成像装置的示意图。

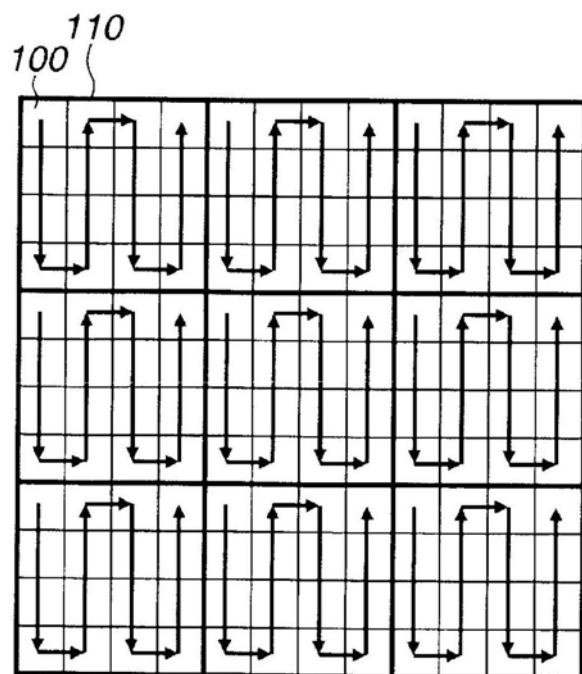

[0021] 图7A和图7B是示出根据第二示例性实施例的成像装置的示意图。

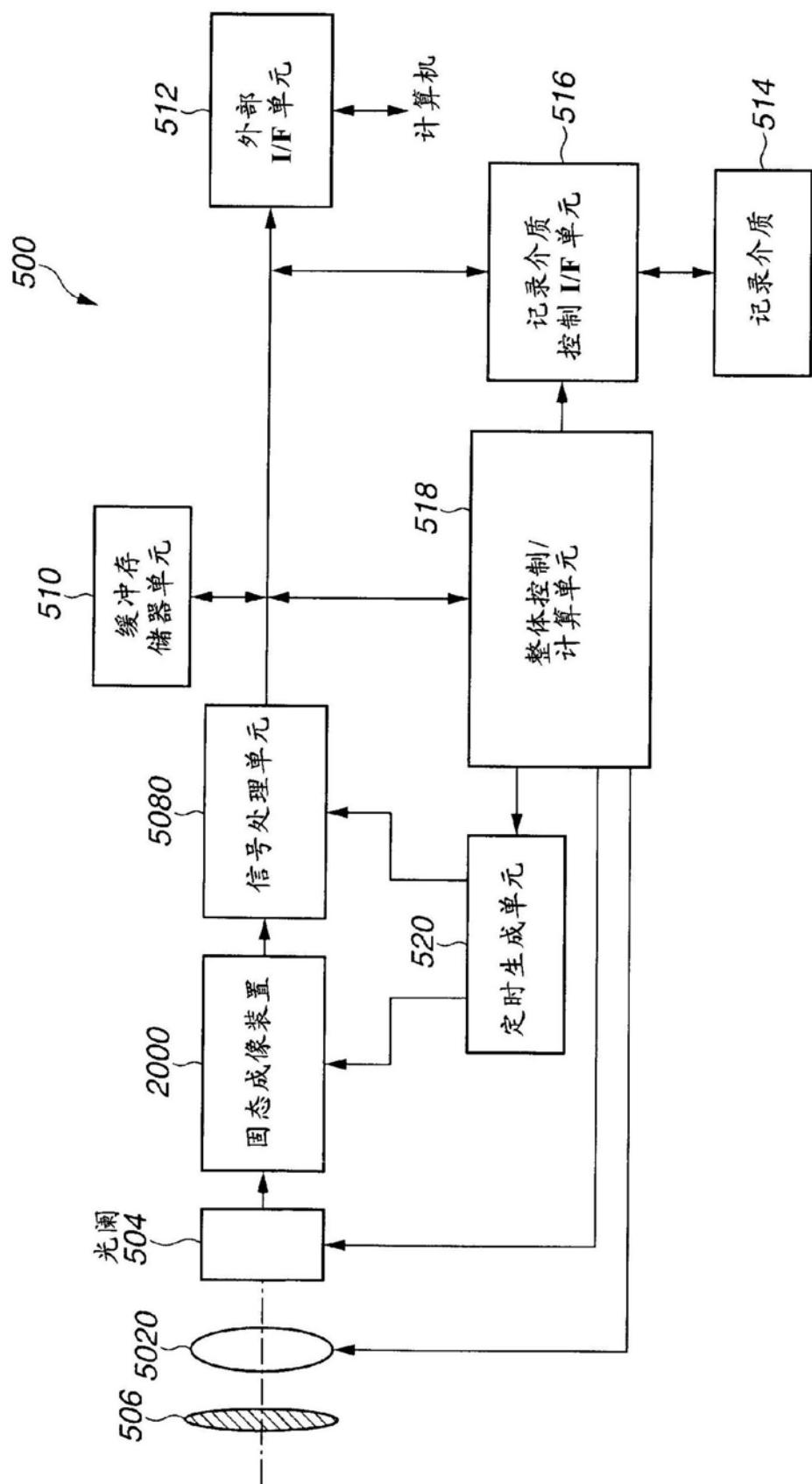

- [0022] 图8是示出根据第三示例性实施例的成像系统的配置的示图。

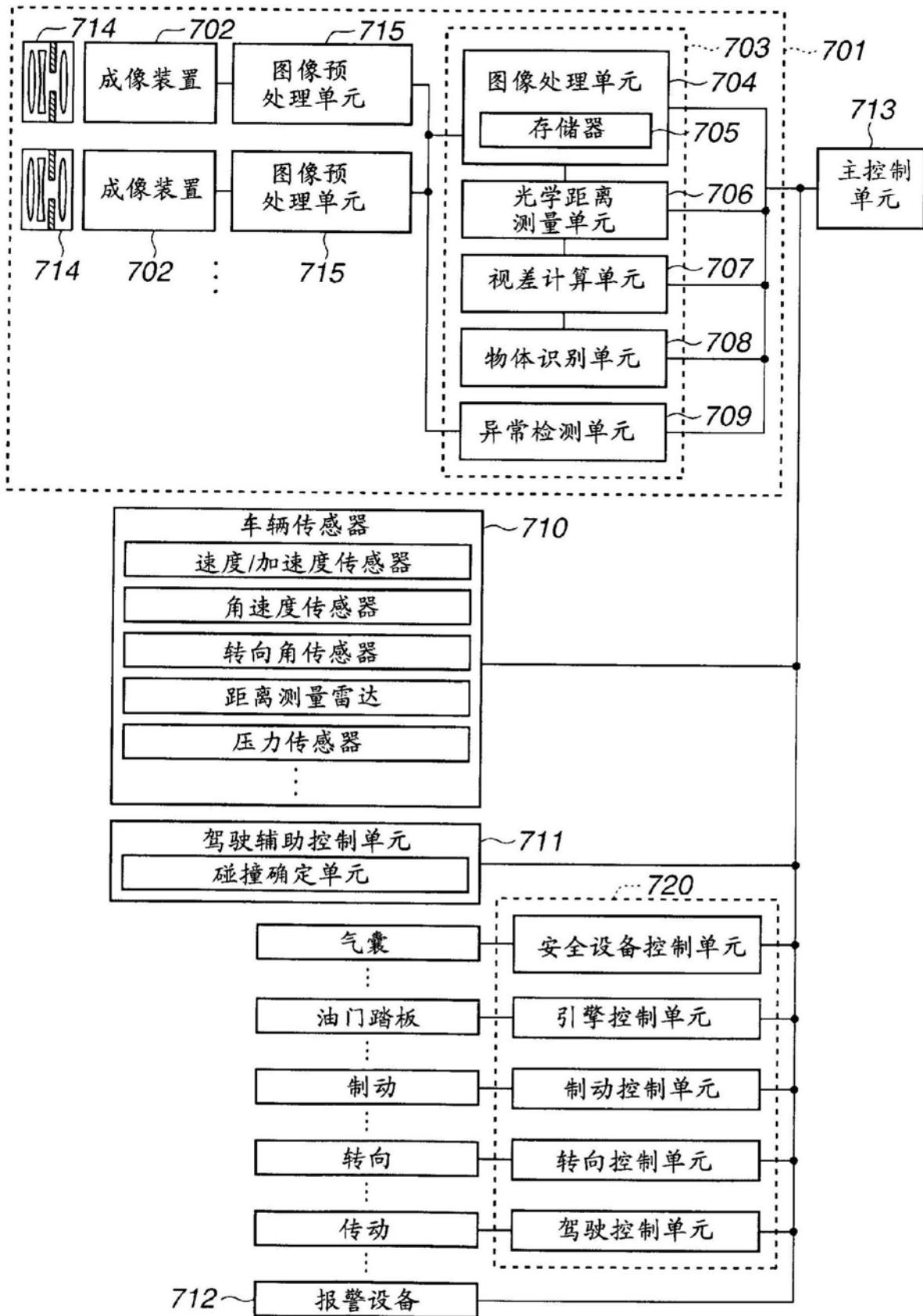

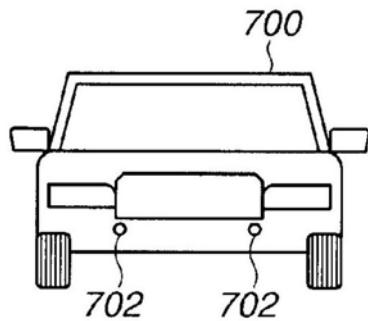

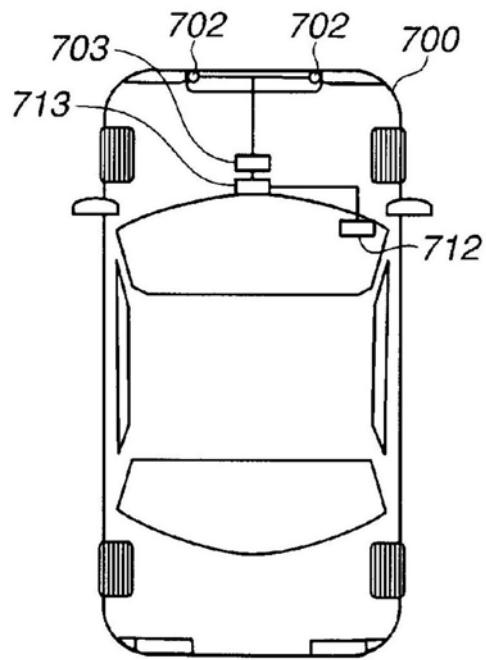

- [0023] 图9A和图9B是示出根据第四示例性实施例的移动体的配置的示图。

- [0024] 图10是示出根据日本专利申请公开No.2014-155175的成像装置的示意图。

- [0025] 图11A和图11B是示出根据日本专利申请公开No.2014-155175的成像装置的示意图。

## 具体实施方式

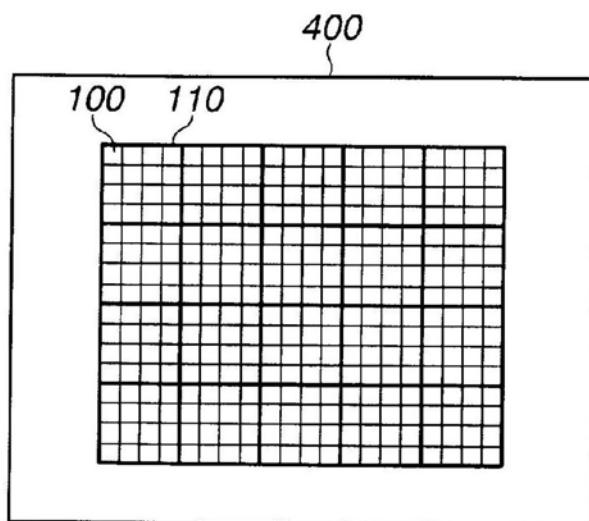

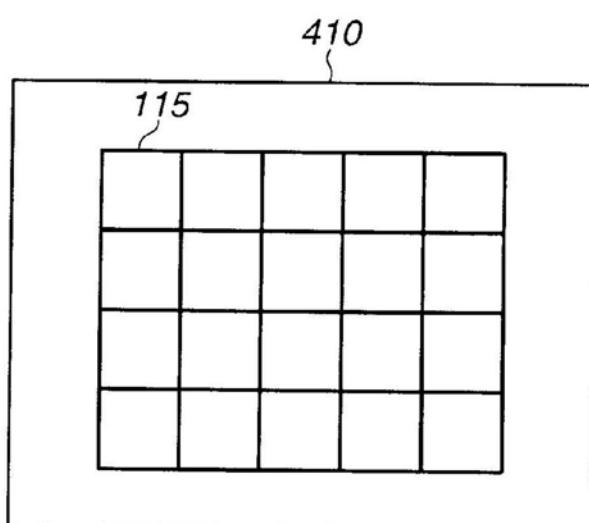

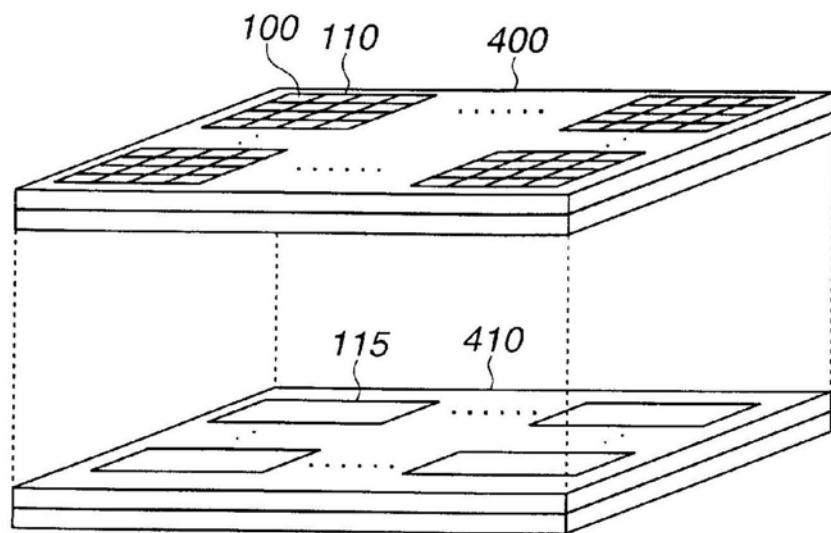

[0026] 图3A、图3B和图3C是示出根据第一示例性实施例的成像装置的示意图。第一芯片400包括分别包含多个像素100的多个像素块110。此外，第二芯片410包含多个信号处理单元115。各信号处理单元115包含用于将模拟信号转换成数字信号的模拟数字转换单元(AD转换单元)。第一芯片400和第二芯片410被层叠在一起，由此形成层叠型的成像装置。在各像素100中，设置单个光电转换单元，并且以对应于单个光电转换单元的方式设置单个微透镜(未示出)。

[0027] 像素块110和信号处理单元115在一一对的基础上相互对应。即，该配置为使得并非设置在第一芯片400上的所有像素由单个信号处理单元处理，而是像素被划分成多个像素块，并且各像素块由单个信号处理单元处理。因此，能够并行地执行AD转换。这可以加速处理。此外，与多个像素块和多个信号处理单元两者都被设置在单个基板上的情况相比，无需将各像素块与对应于该像素块的信号处理单元之间布线放置在另一像素块或另一信号处理单元附近。因此，能够减少像素块之间的串扰。

[0028] 相互对应的一对像素块110和信号处理单元115被设置为使得像素块110和信号处理单元115在平面图中相互重叠。这种放置缩短了电连接来自像素块110的输出线与信号处理单元115的通道。因此，能够减少布线容量。

[0029] 图1A示出像素块110的读取顺序。以第一行第一列为开始点，在行方向上开始读取。如果读取到达第一行第四列，则在与第一行的读取相反的方向上在行方向上从第二行第四列起执行读取。该读取被依次执行至第四行第一列。即，在第一方向上读取设置在第一行中的多个像素(第一像素组)。此外，在与第一方向相反的第二方向上读取设置在第二行中的多个像素(第二像素组)。此外，重新在第一方向上读取设置在第三行中的多个像素(第三像素组)。

[0030] 各信号处理单元115依次处理像素的信号。但是，信号的电平根据照射各像素的光量而因像素而异。在信号处理单元115对某个像素执行信号处理之后，并且如果在处理下一个像素的信号时执行的信号处理单元115的复位没有完成，则前一个像素的信号电平影响下一个像素的信号处理结果(串扰)。此时，如果如图1A所示的那样设定像素的读取顺序，则读取与前一个像素相邻的像素，因此由信号处理单元115的复位残余导致的串扰在相邻的像素中连续地出现。因此，即使出现串扰，也能够使得作为图像串扰不明显。

[0031] 此外，图1A中的读取方法能够获取质量比在日本专利申请公开No.2014-155175中讨论的读取方法高的图像。参照图11B，从第一行第一列中的像素的读取的结束到第二行第一列中的像素的读取，需要11个像素的时间。相反，在图1A中，从某个像素的读取到与该像素相邻的像素的读取，需要最多七个像素的时间。例如，从第一行第一列中的像素的读取的结束到第二行第一列中的像素的读取的结束，仅需要七个像素的时间。因此，在一个实施例

中,图1A中的读取方法需要图11B中的读取方法的时间的约三分之二。因此,当高速物体被成像时,能够减少图像的不连续性。

[0032] 此外,图1A中的读取可以通过使用比图11B中的读取更简单的选择电路实现。例如,在图1A中,可以通过一般的偏移寄存器和解码器实现行方向上的读取,并且,可以通过具有反向运行功能的偏移寄存器以及具有用于在递增和递减之间切换的功能的解码器,实现列方向上的读取。

[0033] 虽然在图1A中在行号的升序方向上执行读取,但是可以在行号的降序方向上执行读取。作为替代方案,如图1B所示,可以在列号的升序方向上执行读取。此外,虽然在图1B中在列号的升序方向上执行读取,但是可以在列号的降序方向上执行读取。

[0034] 在读取像素块中的最后一个像素之后,即,当单个帧结束时,在一个实施例中,信号处理单元115被充分地复位,然后开始下一帧的读取。这是由于,根据图1A和图1B中的读取顺序,第一帧中的最后读取的像素不与第二帧中的首先读取的像素相邻,因此,复位残余的影响巨大。为了充分地复位信号处理单元115,施加复位信号的时段可以加长。具体而言,关于设置在比较器的输入端的箝位电容器的复位时段,可以对于要最后读取的像素设定第一时段,并且,可以对要最后读取的像素以外的像素设定第二时段。然后,第一时段可以比第二时段长。作为替代方案,在要最后读取的像素被读取之后输入复位信号的次数可以大于在最后读取的像素以外的像素被读取之后输入复位信号的次数。

[0035] 如上所述,基于根据本示例性实施例的成像装置,与日本专利申请公开No.2014-155175相比,能够防止作为图像由于信号处理单元的复位残余导致的串扰明显。此外,能够减少由相邻像素的读取定时之间的差异增大而导致的物体的不连续。因此,能够提供能够与在日本专利申请公开No.2014-155175中讨论的成像装置相比形成质量更好的图像的成像装置。

[0036] (成像装置的操作与串扰之间的关系)

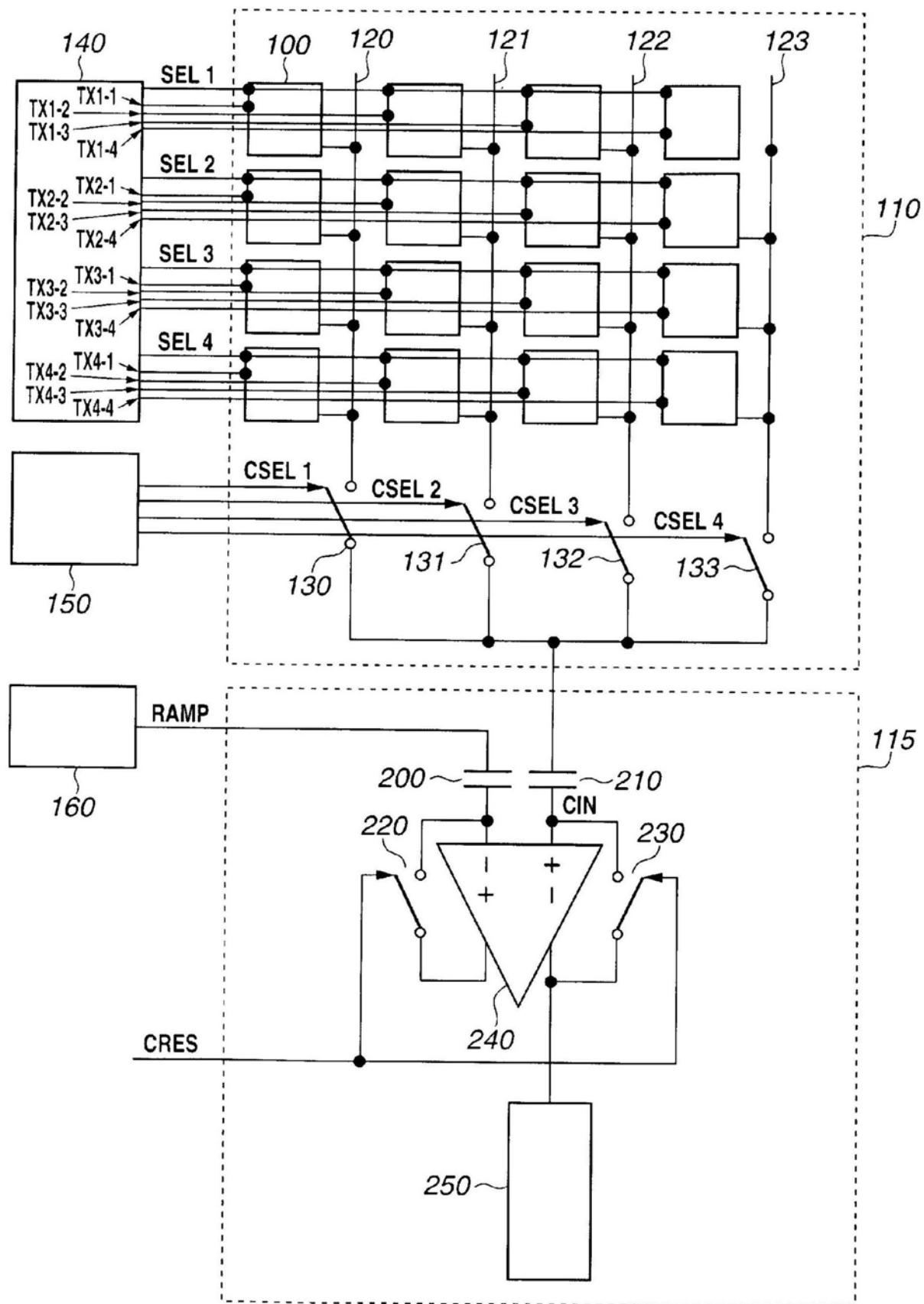

[0037] 下面,参照图4,进一步详细描述图1A和图1B中的成像装置的操作与串扰之间的关系。除了像素100以外,各像素块110还包含信号线120~123和开关130~133。成像装置包括垂直读取单元(垂直扫描单元)140、水平读取单元(水平扫描单元)150和斜坡发生器160。通过使用控制信号TX1-1~TX4-4,垂直读取单元140控制设置在像素块110中的行中的像素的蓄积时间。此外,通过使用控制信号SEL1~SEL4,垂直读取单元140依次选择像素块110的行。此外,信号处理单元115包括电容器200和210、开关220和230、比较器240和计数器250,由此形成AD转换单元。斜坡发生器160经由电容器200与比较器240的一个输入节点连接,并且输入斜坡信号(比较信号)。此外,信号线120~123经由电容器210与比较器240的另一输入节点连接。电容器210箝位像素复位电平,并因此也被称为“箝位电容器”。模拟信号通过信号线120~123被输入到电容器210的一个节点。而且,处于复位电平的信号通过CRES达到高电平而被输入到电容器210的另一节点。通过使用控制信号CSEL1~CSEL4,水平读取单元150选择信号线120~123以与信号处理单元115连接,由此依次选择像素块110的列。

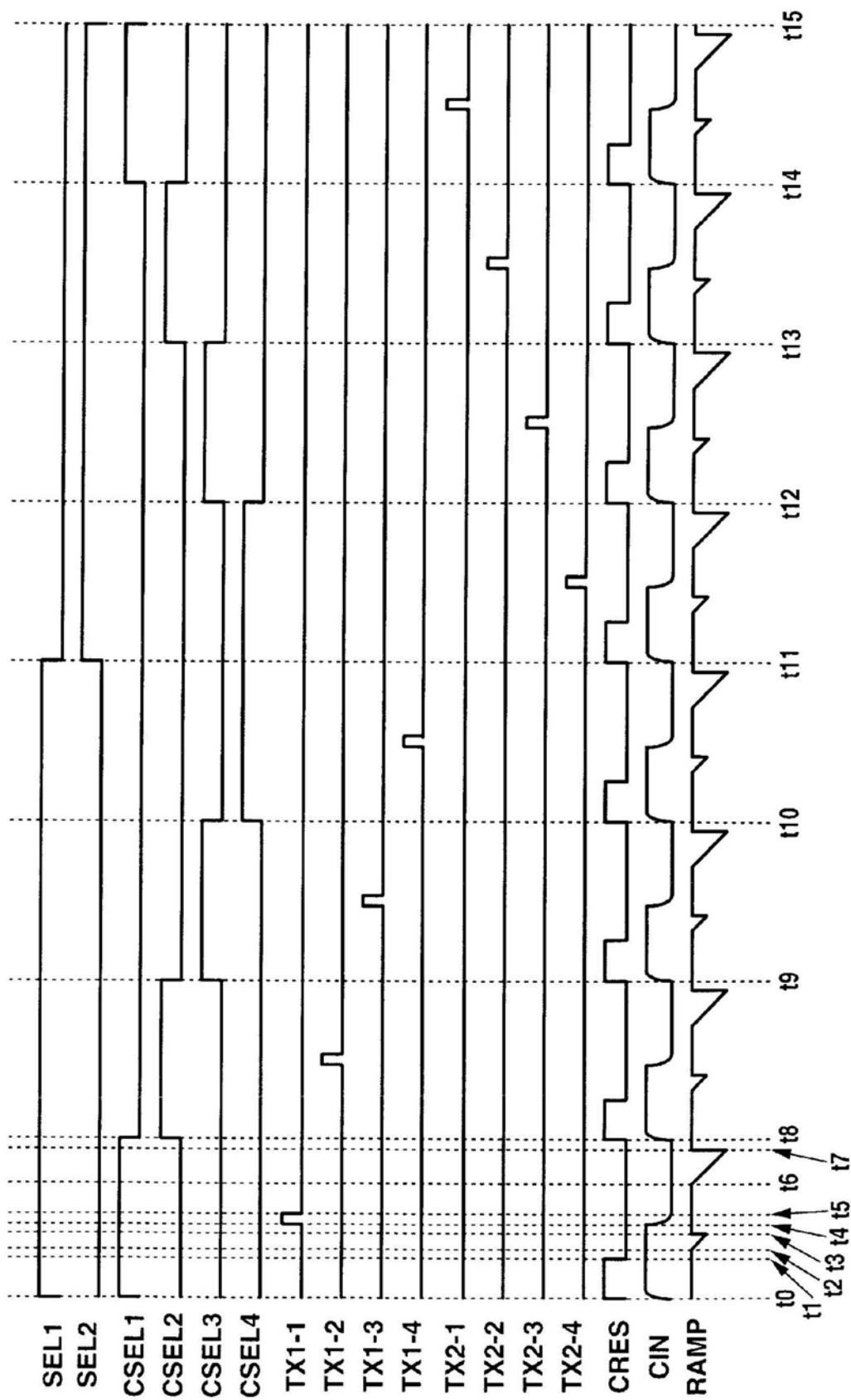

[0038] 下面,参照图5,将通过使用图4中的成像装置的操作波形的例子来描述操作。从时刻t0到时刻t11,控制信号SEL1处于高电平,控制信号SEL2、SEL3和SEL4处于低电平(控制信号SEL3和SEL4没有被示出),并且像素块110的顶行处于被选择状态。从时刻t0到时刻t8,控制信号CSEL1处于高电平。从时刻t8到时刻t9,控制信号CSEL2处于高电平。从时刻t9到时刻

t10,控制信号CSEL3处于高电平。从时刻t10到时刻t11,控制信号CSEL4处于高电平。因此,像素块110的第一至第四列被依次选择。

[0039] 从时刻t11到时刻t15,控制信号SEL2处于高电平,控制信号SEL1、SEL3和SEL4处于低电平(控制信号SEL3和SEL4没有被示出),并且像素块110的从上向下的第二行处于被选择状态。从时刻t11到时刻t12,控制信号CSEL4处于高电平。从时刻t12到时刻t13,控制信号CSEL3处于高电平。从时刻t13到时刻t14,控制信号CSEL2处于高电平。从时刻t14到时刻t15,控制信号CSEL1处于高电平。因此,此时,像素块110的第四至第一列此时被依次选择。

[0040] 下面,将描述单个像素的信号的读取和信号处理单元115的处理操作。在时刻t0,像素块110的第一行第一列中的像素100被选择并且连接到信号处理单元115。CRES达到高电平,由此开关230进入导通状态,并且比较器240的一个输入节点CIN被复位到复位电平。同时,开关220也进入导通状态,并且比较器240的另一输入节点也被复位到复位电平。

[0041] 等到时刻t1,复位完成,并且来自像素100的输出的像素复位电平也被箝位。即,在时刻t1,作为电容器210的一个节点的输入节点CIN处于比较器240的复位电平,并且电容器210的另一个节点处于像素块110的第一行第一列中的像素100的复位电平。此时,电容器200的比较器240侧的节点处于比较器240的复位电平,并且,电容器200的另一侧的节点处于RAMP的基准电平。

[0042] 在时刻t1,CRES被关断,并且比较器240的复位和像素复位电平的箝位结束。从时刻t2到时刻t3,RAMP向下倾斜,计数器250测量直到比较器240的输出反转所花费的时间,并且,获得对应于测量时间( $t_3-t_2$ )的数字值作为像素复位电平的AD转换值。在时刻t4,控制信号TX1-1达到高电平,由此接通设置在像素100中的传送晶体管。因此,光电转换单元将信号电荷传送到浮置扩散,并且像素100输出信号电平。复位电平过渡到信号电平,由此,输入节点CIN的电势也根据信号电平而降低。根据各像素被照射的光的量,信号电平因像素而异。

[0043] 从时刻t6到时刻t7,RAMP重新向下倾斜,计数器250测量直到比较器240的输出反转所花费的时间,并且,获得对应于测量时间( $t_7-t_6$ )的数字值作为像素信号电平的AD转换值。取得像素信号电平的AD转换值和像素复位电平的AD转换值之间的差值,由此获得最终的AD转换结果。

[0044] 在时刻t8,为了读取下一个像素,重新开始比较器240的复位和像素复位电平的箝位。此时,如果用高电平的CRES执行的复位比较器240的操作未完成,则输入节点CIN的电势从时刻t5到时刻t8越低,读取下一个像素时的输入节点CIN的复位电平就越低。因此,比较器240的操作点有可能由于前一个像素的信号电平而波动,并且出现从前一个读取像素到下一个读取像素的串扰。在本示例性实施例中,连续读取相邻像素,因此,与日本专利申请公开No.2014-155175相比,防止作为图像串扰明显。

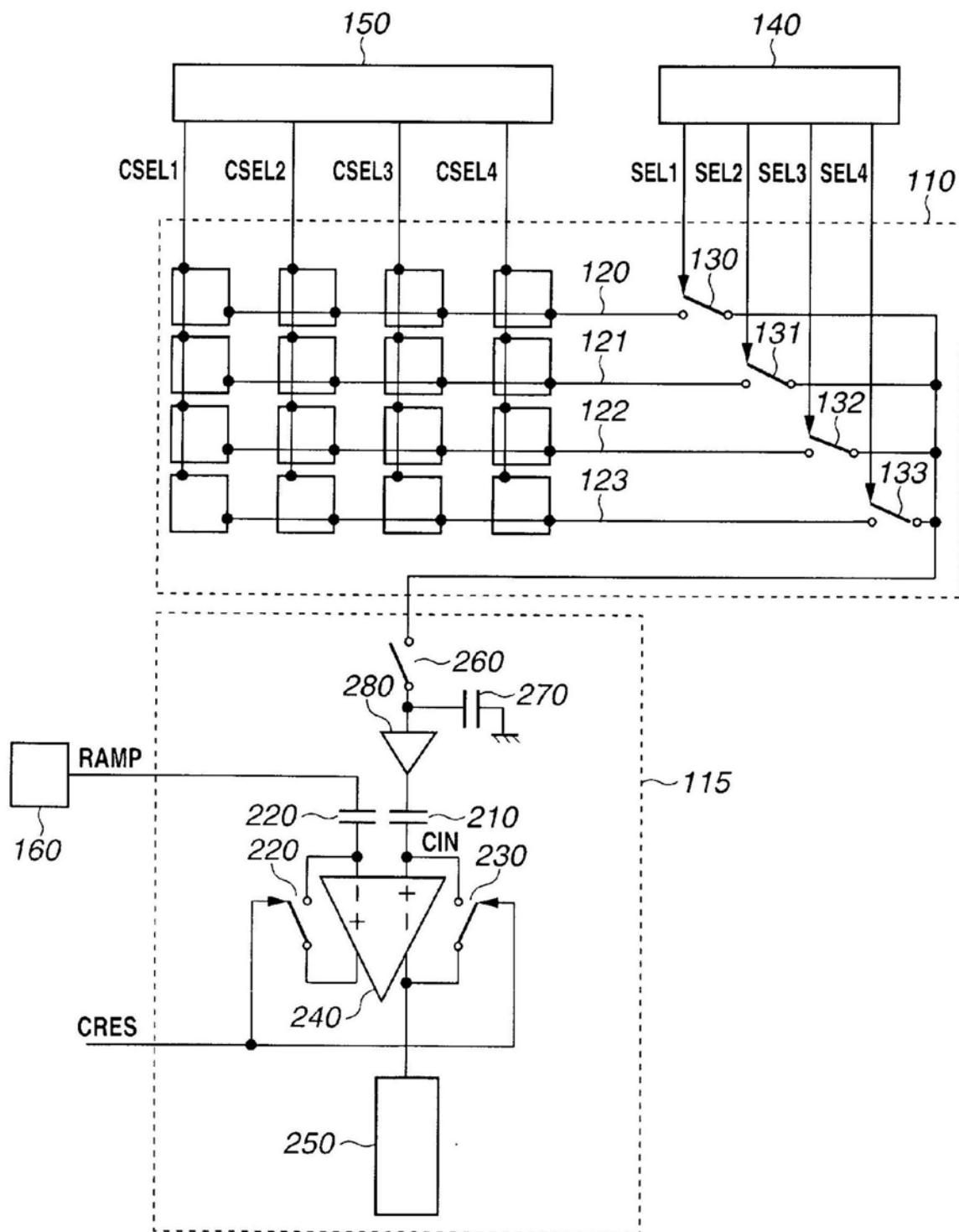

[0045] 图6是图4中的成像装置的变型例。图4所示的控制信号TX1-1～TX4-4的驱动线被省略。图4和6在以下方面是相互不同的。在图4中,在选择行之后,选择列。相反,在图6中,在选择列之后,选择行。具体而言,在图6中,信号线120～123由行方向上的像素100共享。在这种情况下,通过使用像素控制线CSEL1～CSEL4选择列,并且通过使用开关130～133选择行。此外,在图6中,包括包含开关260和电容器270的采样保持单元和缓冲器280。电容器270有时被称为“采样保持电容器”。在包括这种采样保持单元的情况下,电容器270保持某个像素

的信号电平，并且当在该状态下对信号电平执行AD转换时，像素块110可以开始读取下一个像素的复位电平。这使得能够高速操作。即，前一个像素的读取和下一个像素的读取的部分重叠，由此能够实现高速处理。但是，在这种情况下，操作的重叠增大了从前一个像素到下一个像素的串扰的风险。例如，比较器240的输出反转的定时根据前一个像素的信号电平而改变。这改变了对于下一个像素的复位电平的干扰。此外，用于采样保持的电容器270也导致串扰。要写入到电容器270的像素100的复位电平的初始值是前一个像素的信号电平。因此，如果写入不完整，则出现串扰。如上所述，能够加速处理，但是串扰的风险同时增加。在这种配置中，尤其重要的是，防止串扰出现在彼此远离的像素中并且作为图像变得明显。在本示例性实施例中描述的用于读取像素信号的方法更有效地工作。

[0046] (其他变型例)

[0047] 图2A和2B示出1A和图1B中的读取方法的变型例。在图2A和图2B中，配置为使得像素100的读取顺序在相邻像素块110之间是线对称的。换句话说，设置在第一像素块的第一行中的像素组(第一像素组)和设置在第二像素块的第一行中的像素组(第一像素组)彼此相对放置。此外，读取第一像素块的第一像素组的方向(第一方向)和读取第二像素块的第一像素组的方向(第一方向)彼此相反。因此，能够在相邻像素块110之间匹配像素的读取定时，并且减小跨着像素块110的图像的不连续性。

[0048] 此外，如图4和图6所示，以倾斜型AD转换器为例描述了本示例性实施例。但是，AD转换器不限于倾斜型。例如，斜坡发生器160和电容器200可以用二进制权重电容器组替换，由此形成逐次逼近型AD转换器。

[0049] 此外，如图1A、图1B、图2A和图2B所示，在包括多个像素块110的前提下描述了本示例性实施例。作为替代方案，其中多个像素以矩形方式排列的像素阵列可以被视为单个像素块，并且，可以对像素阵列采用以上的读取方法。

[0050] 另外，如图3A、3B和3C所示，在本示例性实施例中，描述了在第一芯片400上包含像素块110并且在第二芯片410上包含信号处理单元115的层叠型成像装置。但是，根据本示例性实施例的公开也可以应用于非层叠型的成像装置。

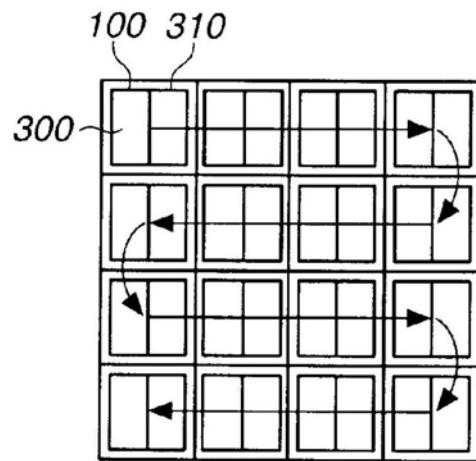

[0051] 图7A和7B是示出根据第二示例性实施例的像素块110的示意图。如图7A和7B所示，对应于单个微透镜，各像素100均包括用于相位检测的第一光电转换单元300和第二光电转换单元310。在图7A中，第一光电转换单元300和第二光电转换单元310在行方向(水平方向)上划分。将从第一光电转换单元300获得的行方向上的图像和从第二光电转换单元310获得的行方向上的图像进行比较，由此检测图像之间的相位差。此时，如果放置在行方向上的像素100的读取时间彼此大不相同，则存在用于相位检测的图像变得不连续的可能性。作为响应，在如图7A所示的那样各像素100均包括在行方向上划分的光电转换单元300和310的情况下，使用用于在行方向上读取像素并依次在列方向上偏移读取的方法。在这种情况下，例如，通过使用图4中的成像装置，选择行，并且按照列的顺序依次地执行读取。

[0052] 另一方面，在如图7B所示的那样各像素100均包括在列方向(垂直方向)上划分的光电转换单元300和310的情况下，使用用于在列方向上扫描像素并且依次在行方向上偏移该扫描的形式。在这种情况下，例如，通过使用图6中的成像装置，选择列，并且按照行的顺序依次地执行读取。

[0053] 此外，第一光电转换单元300和第二光电转换单元310的信号可以不用于相位检

测。相反,还能够通过将第一光电转换单元300和第二光电转换单元310的信号相加,通常与相位检测一起获取图像。

[0054] 此外,在本示例性实施例中,第一光电转换单元300和第二光电转换单元310的信号被依次读取。但是,如果信号处理单元115包括用于第一光电转换单元300的信号处理单元和用于第二光电转换单元310的信号处理单元,则能够同时并行读取两个信号。因此,能够确保相位检测图像的同时性,并且通过进一步减小两个图像的不连续性的影响来执行处理。

[0055] 此外,通过使用所有像素100都具有用于相位检测的二像素配置的例子描述了本示例性实施例。但是,二像素配置不限于所有像素。作为替代方案,可以采用用于相位检测的像素被离散放置的配置。

[0056] 基于根据本示例性实施例的成像装置,与日本专利申请公开No.2014-155175相比,能够防止作为图像由信号处理单元的复位残余导致的串扰明显。此外,能够减小由相邻像素的读取定时之间的差异的增大而导致的物体的不连续性。因此,能够提供与在日本专利申请公开No.2014-155175中讨论的成像装置相比能够形成具有更好质量的图像的成像装置。

[0057] 图8是示出根据第三示例性实施例的成像系统500的配置的框图。根据本示例性实施例的成像系统500包括应用上述成像装置中的任一个的配置的成像装置2000。成像系统500的具体例子包括数字静态照相机、数字摄像机和监视照相机。成像系统500包括成像装置2000、透镜5020、光阑504和保护透镜5020的遮挡件506。成像系统500包括处理从成像装置2000输出的输出信号的信号处理单元5080。信号处理单元5080执行用于在必要时对输入信号执行各种类型的校正和压缩并且输出得到的信号的信号处理操作。信号处理单元5080可以具有对从成像装置2000输出的信号执行AD转换处理的功能。成像系统500还包括临时存储图像数据的缓冲存储器单元510和用于与外部计算机通信的外部接口单元(外部I/F单元)512。此外,成像系统500包括向其记录或从其读取捕获数据的诸如半导体存储器的记录介质514、以及被用于向记录介质514记录或从记录介质514读取捕获数据的记录介质控制接口单元(记录介质控制I/F单元)516。

[0058] 此外,成像系统500包括执行各种计算并且控制数字静态照相机的整体的整体控制/计算单元518、以及向成像装置200和信号处理单元5080输出各种定时信号的定时生成单元520。成像装置2000将图像信号输出到信号处理单元5080。信号处理单元5080对从成像装置2000输出的图像信号执行预定的信号处理,并且输出图像数据。此外,信号处理单元5080通过使用图像信号生成图像。

[0059] 通过利用根据上述示例性实施例中的每一个的成像装置配置成像系统,由此能够实现能够获取具有更好质量的图像的成像系统。

[0060] 参照图9A和图9B,描述根据第四示例性实施例的成像系统和移动体。在本示例性实施例中,示出关于车载照相机的成像系统的例子。图9A和9B示出车辆系统和安装在车辆系统上的成像系统的例子。成像系统701包括成像装置702、图像预处理单元715、集成电路703和光学系统714。光学系统714在成像装置702上形成物体的光学图像。成像装置702将由光学系统714形成的物体的光学图像转换成电信号。成像装置702是根据上述示例性实施例中的任一个的成像装置。图像预处理单元715对从成像装置702输出的信号执行预定的信号

处理。在成像系统701中，设置至少两组的光学系统714、成像装置702和图像预处理单元715，使得来自各组中的图像预处理单元715的输出被输入到集成电路703。

[0061] 集成电路703是用于成像系统的集成电路，并且包括包含存储器705的图像处理单元704、光学距离测量单元706、视差计算单元707、物体识别单元708和异常检测单元709。图像处理单元704对来自各图像预处理单元715的输出信号执行显影处理或诸如缺陷校正的图像处理。存储器705主要存储捕获图像或存储捕获像素的缺陷的位置。光学距离测量单元706聚焦于物体上或测量与物体的距离。视差计算单元707从通过多个成像装置702获取的多条图像数据计算视差(视差图像之间的相位差)。物体识别单元708识别物体，诸如汽车、道路、标志或人。如果检测到成像装置702的异常，则异常检测单元709将异常通知给主控制单元713。

[0062] 集成电路703可以由专门为集成电路703设计的硬件实现，或由软件模块实现，或由它们的组合实现。作为替代方案，集成电路703可以由现场可编程门阵列(FPGA)或专用集成电路(ASIC)实现，或者由它们的组合实现。

[0063] 主控制单元713对成像系统701、车辆传感器710和控制单元720的操作执行总体控制。还能够采用如下方法，其中不包括主控制单元713，并且成像系统701、车辆传感器710和控制单元720单独地包括通信接口，分别经由通信网络(例如，控制器区域网(CAN)标准)传送和接收控制信号。

[0064] 集成电路703具有通过接收来自主控制单元713的控制信号或通过集成电路703的控制单元而向各成像装置702传送控制信号或设定值的功能。例如，集成电路703传送用于以脉冲方式驱动成像装置702中的电压开关13的设定，或者用于在每帧中切换电压开关13的设定。

[0065] 成像系统701连接到车辆传感器710，并且可以检测成像系统701被设置于其中的车辆的运行状态(诸如速度、横摆率和转向角)、车辆外部环境以及另一车辆和障碍物的状态。车辆传感器710还是用于从视差图像获取关于与目标物体的距离的信息的距离信息获取单元。此外，成像系统701连接到执行诸如自动转向、自动巡航和防撞功能的各种类型的驾驶辅助的驾驶辅助控制单元711。特别地，关于碰撞确定功能，基于成像系统701或车辆传感器710的检测结果，碰撞确定单元估计与另一车辆或障碍物的碰撞，或确定与另一车辆或障碍的碰撞的有无。因此，在估计碰撞的情况下，执行回避控制。此外，当发生碰撞时，启动安全设备。

[0066] 此外，成像系统701还连接到基于碰撞确定单元的确定结果向驾驶员发出警报的报警设备712。例如，作为碰撞确定单元的确定结果，如果碰撞的可能性高，则主控制单元713应用制动器，使油门踏板回位或抑制引擎输出，由此控制车辆以避免碰撞并减少损坏。报警设备712通过发出诸如声音的警报、在汽车导航系统或仪表板的显示单元的屏幕上显示警报信息或向安全带或方向盘施加振动，来警告用户。

[0067] 在本示例性实施例中，成像系统701对车辆的诸如前方或后方的周边进行成像。图9B示出成像系统701捕获车辆的前方方向的情况下的成像系统701的布置的例子。

[0068] 此外，在本示例性实施例中，已经描述了用于防止车辆与另一车辆碰撞的控制。作为替代方案，本示例性实施例也适用于通过跟随另一车辆而自动驾驶车辆的控制，或自动驾驶车辆以停留在车道上的控制。此外，成像系统701不仅可以应用于诸如汽车的车辆，还

可以应用于诸如船舶、飞机或工业机器人的移动体(移动装置)。另外,成像系统701不仅可以应用于运动物体,还可以应用于广泛利用物体识别的设备,例如智能交通系统(ITS)。

[0069] (其他示例性实施例)

[0070] 虽然已经描述了示例性实施例,但是本公开不限于这些示例性实施例,并且可被以各种方式改变和修改。此外,示例性实施例适用于彼此。

[0071] 虽然已参照示例性实施例描述了本发明,但应理解,本发明不限于公开的示例性实施例。以下的权利要求的范围应被赋予最宽的解释以包含所有的变型方式以及等同的结构和功能。

图1A

图1B

图2A

图2B

图3A

图3B

图3C

图4

图5

图6

110

图7A

110

图7B

图8

图9A

前视图

俯视图

后视图

图9B

图10现有技术

图11A现有技术

图11B现有技术