(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-137788

(P2012-137788A)

(43) 公開日 平成24年7月19日(2012.7.19)

| (51) Int.Cl.        | F 1                  | テーマコード (参考) |

|---------------------|----------------------|-------------|

| G09G 3/30 (2006.01) | G09G 3/30 J 5C080    |             |

| G09G 3/20 (2006.01) | G09G 3/20 611F 5C094 |             |

| G09G 3/34 (2006.01) | G09G 3/20 642D 5C380 |             |

| G09G 3/22 (2006.01) | G09G 3/20 680F       |             |

| G09F 9/30 (2006.01) | G09G 3/34 D          |             |

審査請求 有 請求項の数 2 O L (全 104 頁) 最終頁に続く

(21) 出願番号 特願2012-83551 (P2012-83551)

(22) 出願日 平成24年4月2日 (2012.4.2)

(62) 分割の表示 特願2006-75139 (P2006-75139)

の分割

原出願日 平成18年3月17日 (2006.3.17)

(31) 優先権主張番号 特願2005-80214 (P2005-80214)

(32) 優先日 平成17年3月18日 (2005.3.18)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 木村 肇

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

F ターム (参考) 5C080 AA05 AA06 AA10 AA12 AA18

BB05 CC03 DD01 DD23 JJ03

JJ04 JJ06 KK02 KK07 KK43

KK47

5C094 AA05 AA10 AA21 AA53 BA03

BA27 BA43 DB04

最終頁に続く

(54) 【発明の名称】半導体装置及び電子機器

## (57) 【要約】

【課題】画素中の発光素子の輝度が同輝度の場合、画素中の発光領域の面積が大きくなれば一画素から高い光度を得ることができる。つまり、一画素中の光を通さない領域（ブラックマトリクスともいう）を除いた光を通す領域の面積と、一画素の面積の割合で示される開口率が高ければ、高精細化により一画素の面積が小さくなっても一画素から所望の光度を得ることができる。ここで、画素を構成するトランジスタや配線の数が多いと画素の開口率が低くなってしまう。そこで、画素を構成するトランジスタや配線の数を減らし、開口率を高める。

【解決手段】ある電位が設定されている電源線の代わりに、電位を信号により制御する電位供給線を設ける。つまり、発光素子への印加電圧の供給を、スイッチを設けずに電位供給線の信号により制御することができる。

【選択図】図 7 5

**【特許請求の範囲】****【請求項 1】**

第1のトランジスタと、第1及び第2のスイッチと、容量素子と、第1及び第2の配線と、を有する半導体装置であって、

前記容量素子の第1の端子は、前記第1のトランジスタのゲートと、トランジスタを介さずに接続され、

前記容量素子の第2の端子は、前記第1の配線と、トランジスタを介さずに接続され、

前記第1のトランジスタの第1の端子は、前記第2のスイッチの第1の端子と、トランジ

スタを介さずに接続され、

前記第1のトランジスタの第2の端子は、画素電極と、トランジスタを介さずに接続され

、

前記第1のスイッチの第1の端子は、前記第1のトランジスタの第1の端子と、トランジ

スタを介さずに接続され、

前記第1のスイッチの第2の端子は、前記第1のトランジスタのゲートと、トランジスタ

を介さずに接続され、

前記第2のスイッチの第2の端子は、前記第2の配線と、トランジスタを介さずに接続さ

れていますことを特徴とする半導体装置。

**【請求項 2】**

請求項1乃至3のいずれか一項に記載の表示装置、または、請求項4に記載の表示モジ

ュールを有することを特徴とする電子機器。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は負荷に供給する電流をトランジスタで制御する機能を設けた半導体装置に係り

、特に電流によって輝度が変化する電流駆動型発光素子で形成された画素や、その信号線

駆動回路を含む表示装置に関する。また、その駆動方法に関する。また、その表示装置を

表示部に有する電子機器に関する。

**【背景技術】****【0002】**

近年、画素を発光ダイオード(LE D)などの発光素子で形成した、いわゆる自発光型

の表示装置が注目を浴びている。このような自発光型の表示装置に用いられる発光素子と

しては、有機発光ダイオード(O L E D(O rganic L ight E mit t i n g

D i o d e))、有機EL素子、エレクトロルミネッセンス(E lectro L um

i nescence: E L)素子などとも言う)が注目を集めており、E Lディスプレイ

などに用いられるようになってきている。O L E Dなどの発光素子は自発光型であるため

、液晶ディスプレイに比べて画素の視認性が高く、バックライトが不要で応答速度が速い

等の利点がある。また発光素子の輝度は、そこを流れる電流値によって制御される。

**【0003】**

このような表示装置の階調を表現する駆動方式として、デジタル方式とアナログ方式があ

る。デジタル方式はデジタル制御で発光素子をオンオフさせ、発光している時間を制御し

て階調を表現している。画素毎の輝度の均一性に優れる反面、周波数を高くする必要があり

消費電力が大きくなってしまう。一方、アナログ方式には、発光素子の発光強度をアナ

ログ制御する方式と発光素子の発光時間をアナログ制御する方式がある。発光強度をアナ

ログ制御する方式は、画素毎の薄膜トランジスタ(以下T F Tともいう)の特性のバラツ

キの影響を受けやすく、画素毎の発光にもバラツキが生じてしまう。これに対して、発光

時間をアナログ制御し、画素毎の発光の均一性に優れるアナログ時間階調方式の表示装置

が非特許文献1に記載されている(非特許文献1参照)。

**【0004】**

つまり、非特許文献1に記載の表示装置の画素は、発光素子と発光素子を駆動するトラン

ジスタによりインバータを構成している。駆動トランジスタのゲート端子がインバータの

10

20

30

40

50

入力端子となり、発光素子の陽極がインバータの出力端子となる。画素に映像信号電圧を書き込む際には、インバータをオンとオフの中間に設定する。そして、発光期間には画素に三角波電圧を入力することでインバータの出力を制御する。つまり、発光素子の陽極に設定される電位となるインバータの出力を制御することで、発光素子の発光・非発光を制御する。

【先行技術文献】

【非特許文献】

【0005】

【非特許文献1】SID 04 DIGEST P1394 ~ P1397

10

【発明の概要】

【発明が解決しようとする課題】

【0006】

表示装置の高精細化に伴って一画素から得られる光度は低下してしまう。なお、光度とは、一定の方向から得られる光源の明るさの度合いを表す量をいうものとする。そして、輝度とは光源の単位面積あたりの光度をいうものとする。

【0007】

ここで、異なる画素間において、画素中の発光素子の輝度が同輝度の場合、画素中の発光領域の面積が大きくなれば一画素から高い光度を得ることができる。つまり、一画素中の光を通さない領域（ブラックマトリクスともいう）を除いた光を通す領域の面積と、一画素の面積との割合で示される開口率が高ければ、高精細化により一画素の面積が小さくなっても、駆動電圧を高くせずに一画素から所望の光度を得ることができる。

20

【0008】

ここで、画素を構成するトランジスタや配線の数が多いと画素の開口率が低くなってしまう。そこで、画素を構成するトランジスタや配線の数を減らし、開口率を高めることを課題とする。

【課題を解決するための手段】

【0009】

ある電位が設定されている電源線の代わりに、電位を信号により制御する電位供給線を設ける。つまり、発光素子への印加電圧の供給を、スイッチを設けずに電位供給線の信号により制御することができる。

30

【0010】

本発明の半導体装置の構成は、

電極と、

ゲート端子、第1端子及び第2端子を備えるトランジスタと、

第1の配線と、

第2の配線と、

該トランジスタのゲート端子と該第1の配線との電位差を保持する保持手段と、該トランジスタのゲート端子と第2端子を導通又は非導通にする切り替え手段と、を備える画素を有し、

該トランジスタは、第1端子が該第2の配線に電気的に接続され、該第2端子が該電極と接続されている。

40

【0011】

本発明の他の構成の半導体装置は、

電極と、

ゲート端子、第1端子及び第2端子を備えるトランジスタと、

第1の配線と、

第2の配線と、

該トランジスタのゲート端子と該第1の配線との電位差を保持する容量素子と、

該トランジスタのゲート端子と第2端子を導通又は非導通にするスイッチと、を備える画素を有し、

50

該トランジスタは、第1端子が該第2の配線に電気的に接続され、該第2端子が該電極と電気的に接続されている。

【0012】

本発明の半導体装置の他の構成は、

電極と、

ゲート端子、第1端子及び第2端子を備えるトランジスタと、第1の配線と、第2の配線と、容量素子と、スイッチと、を備える画素を有し、

該トランジスタは、第1端子が該第2の配線に電気的に接続され、第2端子が該電極と電気的に接続され、

該トランジスタは、ゲート端子と該第2端子が該スイッチを介して電気的に接続され、

該トランジスタは、該ゲート端子が該容量素子を介して該第1の配線と電気的に接続され

ている。

【0013】

本発明の表示装置は、

発光素子と、

ゲート端子、第1端子及び第2端子を備え、該発光素子を駆動する駆動トランジスタと、

第1の配線と、

第2の配線と、

該駆動トランジスタのゲート端子と該第1の配線との電位差を保持する保持手段と、

該駆動トランジスタのゲート端子と第2端子を導通又は非導通にする切り替え手段と、を

備える画素を有し、

該駆動トランジスタは、第1端子が該第2の配線に電気的に接続され、該第2端子が該発

光素子の画素電極と電気的に接続されている。

【0014】

本発明の他の構成の表示装置は、

発光素子と、

ゲート端子、第1端子及び第2端子を備え、該発光素子を駆動する駆動トランジスタと、

第1の配線と、

第2の配線と、

該駆動トランジスタのゲート端子と該第1の配線との電位差を保持する容量素子と、

該駆動トランジスタのゲート端子と第2端子を導通又は非導通にするスイッチと、を備える

画素を有し、

該駆動トランジスタは、第1端子が該第2の配線に電気的に接続され、該第2端子が該発

光素子の画素電極と電気的に接続されている。

【0015】

本発明の他の構成の表示装置は、

発光素子と、ゲート端子、第1端子及び第2端子を備え、該発光素子を駆動する駆動トラ

ンジスタと、第1の配線と、第2の配線と、容量素子と、スイッチと、を備える画素を有

し、

該駆動トランジスタは、第1端子が該第2の配線に電気的に接続され、第2端子が該発光

素子の画素電極と電気的に接続され、

該駆動トランジスタは、ゲート端子と該第2端子が該スイッチを介して電気的に接続され

、

該駆動トランジスタは、ゲート端子が該容量素子を介して該第1の配線と電気的に接続さ

れている。

【0016】

また、本発明の他の構成の表示装置は、上記構成において、前記第2の配線には、2値の

状態の電位が入力される。

【0017】

本発明の電子機器は、上記構成の表示装置を表示部に有している。

10

20

30

40

50

## 【0018】

本発明の表示装置の駆動方法は、

発光素子と、

ゲート端子、第1端子及び第2端子を備え、該発光素子を駆動する駆動トランジスタと、第1の配線と、

第2の配線と、

該駆動トランジスタのゲート端子と該第1の配線との電位差を保持する保持手段と、

該駆動トランジスタの該ゲート端子と第2端子を導通又は非導通にする切り替え手段と、を備える画素を有し、

該駆動トランジスタは、第1端子が該第2の配線に電気的に接続され、該第2端子が該発光素子の画素電極と電気的に接続され、

該画素への信号書き込み期間において、該画素への信号書き込みの際には、該切り替え手段は、該駆動トランジスタの該ゲート端子と該第2端子を導通にし、

該第1の配線にはビデオ信号を入力し、

該第2の配線には、該発光素子の対向電極との電位差が該発光素子の順方向しきい値電圧以上となる第1の電位を入力し、

該画素への信号の書き込みが終了すると、該切り替え手段は該駆動トランジスタの該ゲート端子と該第2端子を非導通にし、

該第2の配線には、該発光素子の対向電極との電位差が該発光素子の順方向しきい値電圧未満となる電位を入力し、

発光期間には、該第1の配線にアナログ的に変化する電位を入力し、該第2の配線には、前記第1の電位を入力する。

## 【0019】

なお、明細書に示すスイッチは、様々な形態のものを用いることができ、一例として、電気的スイッチでも機械的なスイッチなどがある。つまり、電流の流れを制御できるものであればよく、特定のものに限定されず、様々なものを用いることができる。例えば、トランジスタでもよいし、ダイオードでもよいし、それらを組み合わせた論理回路でもよい。よって、スイッチとしてトランジスタを用いる場合、そのトランジスタは、単なるスイッチとして動作するため、トランジスタの極性（導電型）は特に限定されない。ただし、オフ電流が少ない方が望ましい場合、オフ電流が少ない方の極性のトランジスタを用いることが望ましい。オフ電流が少ないトランジスタとしては、LDD領域を設けているもの等がある。また、スイッチとして動作させるトランジスタのソース端子の電位が、低電位側電源（V<sub>SS</sub>、GND、0Vなど）に近い状態で動作する場合はNチャネル型を、反対に、ソース端子の電位が、高電位側電源（V<sub>DD</sub>など）に近い状態で動作する場合はPチャネル型を用いることが望ましい。なぜなら、ゲートソース間電圧の絶対値を大きくできるため、スイッチとして、動作しやすいからである。なお、Nチャネル型とPチャネル型の両方を用いて、CMOS型のスイッチにしてもよい。

## 【0020】

なお、本発明において接続されているとは、電気的に接続されていることと同義である。したがって、本発明が開示する構成において、所定の接続関係に加え、その間に電気的な接続を可能とする他の素子（例えば、スイッチやトランジスタや容量素子やインダクタや抵抗素子やダイオードなど）が配置されていてもよい。

## 【0021】

なお、発光素子には、様々な形態を用いることが出来る。例えば、EL素子（有機EL素子、無機EL素子又は有機物及び無機物を含むEL素子）、電子放出素子、液晶素子、電子インク、グレーティングライトバルブ（GLV）、プラズマディスプレイ（PDP）、デジタルマイクロミラーデバイス（DMD）、圧電セラミックディスプレイ、カーボンナノチューブ、など、電気磁気的作用によりコントラストが変化する表示媒体を適用することができる。なお、EL素子を用いた表示装置としてはELディスプレイ、電子放出素子を用いた表示装置としてはフィールドエミッションディスプレイ（FED）やSED方式

10

20

30

40

50

平面型ディスプレイ（S E D : Surface-conduction Electron-emitter Display）など、液晶素子を用いた表示装置としては液晶ディスプレイ、電子インクを用いた表示装置としては電子ペーパーがある。

#### 【0022】

なお、本発明において、トランジスタは、様々な形態のトランジスタを適用させることができるものである。よって、適用可能なトランジスタの種類に限定はない。したがって、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を用いた薄膜トランジスタ（TFT）、半導体基板やSOI基板を用いて形成されるMOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタ、ZnO、a-InGaZnOなどの化合物半導体を用いたトランジスタ、有機半導体やカーボンナノチューブを用いたトランジスタ、その他のトランジスタを適用することができる。また、トランジスタが配置されている基板の種類は、様々なものを用いることができ、特定のものに限定されることはない。従って例えば、単結晶基板、SOI基板、ガラス基板、プラスチック基板、紙基板、セロファン基板、石材基板などに配置することができる。また、ある基板でトランジスタを形成し、その後、別の基板にトランジスタを移動させて、別の基板上に配置するようにしてもよい。

10

#### 【0023】

なお、トランジスタの構成は、様々な形態をとることができる。特定の構成に限定されない。例えば、ゲート本数が2本以上になっているマルチゲート構造を用いてもよい。マルチゲート構造にすることにより、オフ電流を低減したり、トランジスタの耐圧を向上させて信頼性を良くしたり、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることができる。また、チャネルの上下にゲート電極が配置されている構造でもよい。チャネルの上下にゲート電極が配置されている構造にすることにより、チャネル領域が増えるため、電流値を大きくしたり、空乏層ができやすくなっているS値をよくしたりすることができる。また、チャネルの上にゲート電極が配置されている構造でもよいし、チャネルの下にゲート電極が配置されている構造でもよいし、正スタガ構造であってもよいし、逆スタガ構造でもよいし、チャネル領域が複数の領域に分かれている場合もよいし、並列に接続されている場合もよいし、直列に接続されている場合もよい。また、チャネル（もしくはその一部）にソース電極やドレイン電極が重なっていてもよい。チャネル（もしくはその一部）にソース電極やドレイン電極が重なっている構造にすることにより、チャネルの一部に電荷がたまって、動作が不安定になることを防ぐことができる。また、LDD領域があってもよい。LDD領域を設けることにより、オフ電流を低減したり、トランジスタの耐圧を向上させて信頼性を良くしたり、飽和領域で動作する時に、ドレイン・ソース間電圧が変化しても、ドレイン・ソース間電流があまり変化せず、フラットな特性にすることができる。

20

#### 【0024】

本明細書においては、一画素とは1つの色要素を示すものとする。よって、R（赤）G（緑）B（青）の色要素からなるフルカラー表示装置の場合には、画像の最小単位は、Rの画素やGの画素やBの画素との3画素から構成されるものとする。なお、色要素は、三色に限定されず、それ以上でもよく、例えば、RGBW（Wは白）がある。

30

#### 【0025】

トランジスタとは、それぞれ、ゲート電極と、ドレイン領域と、ソース領域とを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル形成領域を有する。ここで、ソース領域とドレイン領域とは、トランジスタの構造や動作条件等によって変わるため、いずれがソース領域またはドレイン領域であるかを特定することが困難である。そこで、本明細書においては、ソース領域及びドレイン領域として機能する領域を、それぞれ第1端子、第2端子と表記する。

40

#### 【0026】

なお、本明細書において、画素がマトリクスに配置されているとは、縦縞と横縞を組み合わせたいわゆる格子状にストライプ配置されている場合はもちろんのこと、三色の色要素（例えばRGB）でフルカラー表示を行う場合に、1つの画像の最小要素を表す三つの色

50

要素の画素がいわゆるデルタ配置されている場合も含むものとする。なお、色要素は三色に限定されず、それ以上でもよく、例えば、R G B W (Wは白)がある。また、色要素の画素毎にその発光領域の大きさが異なっていてもよい。

#### 【0027】

なお、本明細書において、半導体装置とは半導体素子（トランジスタやダイオードなど）を含む回路を有する装置をいう。また、半導体特性を利用して機能しうる装置全般でもよい。また、表示装置とは、表示素子（液晶素子や発光素子など）を有する装置のことと言う。なお、基板上に液晶素子やEL素子などの表示素子を含む複数の画素やそれらの画素を駆動させる周辺駆動回路が形成された表示パネル本体のことでもよい。さらに、フレキシブルプリントサーキット（FPC）やプリント配線基盤（PWB）が取り付けられたものも含んでもよい。また、発光装置とは、特にEL素子やFEDで用いる素子などの自発光型の表示素子を有している表示装置をいう。液晶表示装置とは、液晶素子を有している表示装置をいう。

10

#### 【0028】

なお、本明細書において、デジタル的とは、2の状態をいい、アナログ的とは、連続的な状態はもちろん、3以上のとびとび（離散化）の状態を含むものとする。よって、例えば、電位をアナログ的に変化させると、時間の変化と共に電位を連続的に変化させる場合はもちろん、連続的に変化する電位をサンプリング（なお、標本化又は時間的離散化ともいう。）し、所定の時間間隔でサンプリングした電位となるように電位を変化させる場合を含むものとする。なお、サンプリングとは、データ値が連続的に変化する信号において、所定の時間間隔でそのときの値をとることをいう。

20

#### 【0029】

デジタル信号とは、それ自体が直接的には2の状態を伝達するためのデータ値をもつ信号であり、アナログ信号とは、それ自体が直接的には3以上の状態を伝達するためのデータ値をもつ信号である。そして、アナログ信号には、時間の変化と共にデータ値（電位若しくは電圧又は電流など）が連続的に変化する信号はもちろん、データ値が連続的に変化する信号をサンプリング（なお、標本化又は時間的離散化ともいう。）し、所定の時間間隔でサンプリングしたデータ値となるような信号を含むものとする。なお、サンプリングとは、データ値が連続的に変化する信号において、所定の時間間隔でそのときの値をとることをいう。なお、デジタル信号は、間接的には3以上の状態を伝達する場合もある。例えば、時間の変化と共にデータ値が変化するアナログ信号をサンプリングし、サンプリングしたデータ値をさらに離散化したものもデジタル信号であるからである。つまり、アナログ信号を量子化したものもデジタル信号となるからである。

30

#### 【0030】

なお、本明細書において発光素子の陽極及び陰極とは、発光素子に順方向電圧を印加したときの電極をいうものとする。

#### 【発明の効果】

#### 【0031】

発光素子への印加電圧の供給を、スイッチを設けずに電位供給線の信号により制御することができるところから、スイッチとしてトランジスタを用いている場合には、トランジスタの数を減らすことができる。また、そのトランジスタのオンオフを制御する信号を入力する配線も削除することができる。よって、画素の開口率が向上し、高精細の表示装置を提供することができる。

40

#### 【0032】

また、開口率が向上することから、輝度を減らしても必要な光度を得られるため、発光素子の信頼性を向上させることができる。

#### 【図面の簡単な説明】

#### 【0033】

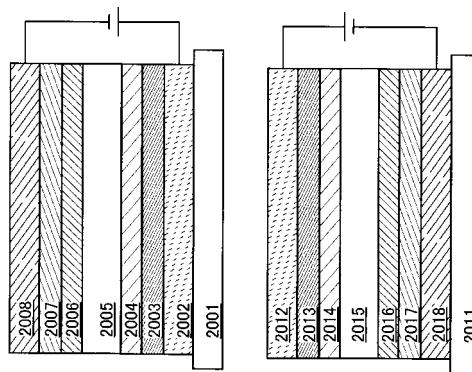

【図1】本発明の画素構成を示す図。

【図2】本発明の画素構成を有する表示装置を説明する図。

50

【図 3】本発明の画素構成を有する表示装置のタイミングチャートを示す図。

【図 4】本発明の画素構成を示す図。

【図 5】本発明の画素構成を有する表示装置のタイミングチャートを示す図。

【図 6】本発明の画素構成を示す図。

【図 7】本発明の画素構成を示す図。

【図 8】本発明の画素構成を示す図。

【図 9】本発明の画素構成を有する表示装置のタイミングチャートを示す図。

【図 10】本発明の画素構成を示す図。

【図 11】本発明の画素構成を有する表示装置のタイミングチャートを示す図。

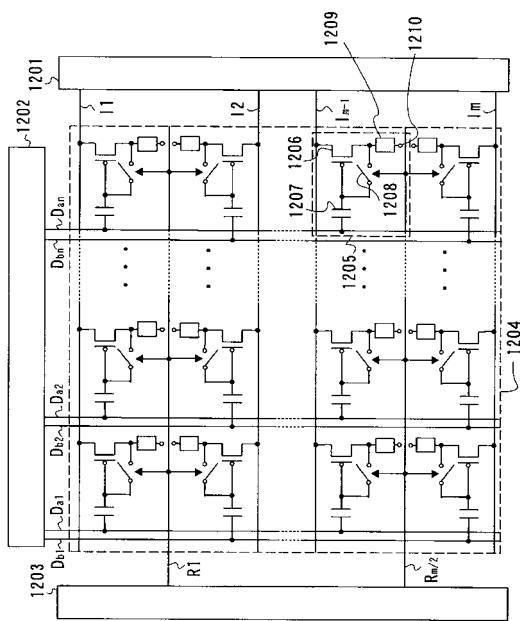

【図 12】本発明の画素構成を有する表示装置を説明する図。

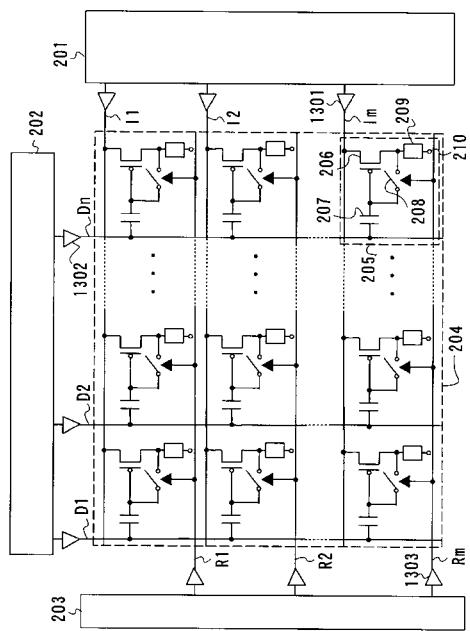

【図 13】本発明の画素構成を有する表示装置を説明する図。

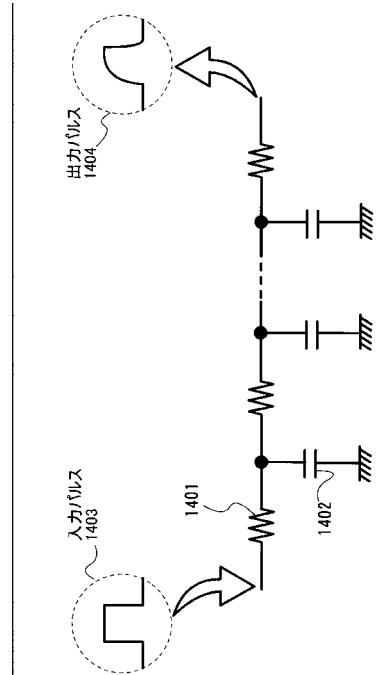

【図 14】信号の立ち上がり及び立ち下がりの遅延の発生を説明する図。

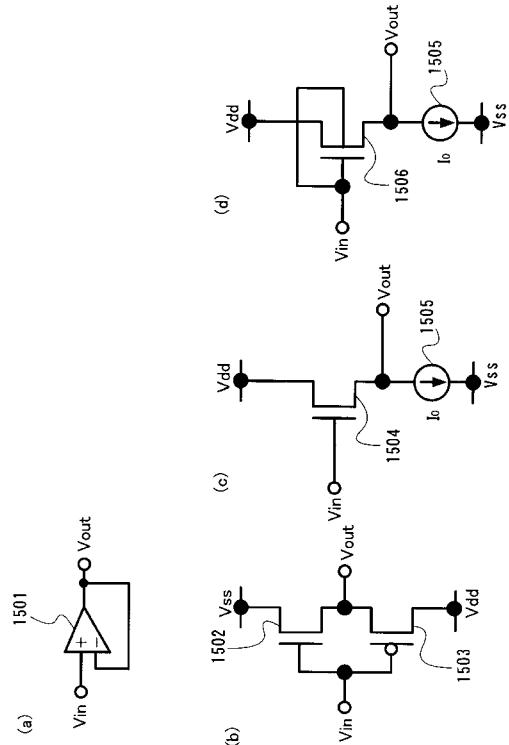

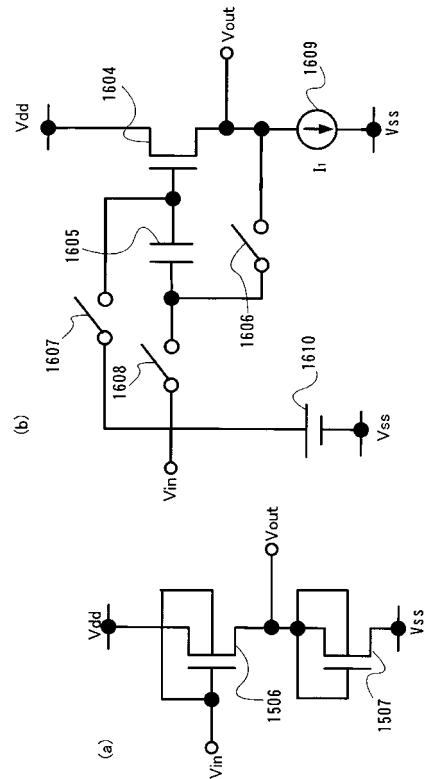

【図 15】本発明の画素構成を有する表示装置に適用可能なバッファ回路を示す図。

【図 16】本発明の画素構成を有する表示装置に適用可能なバッファ回路を示す図。

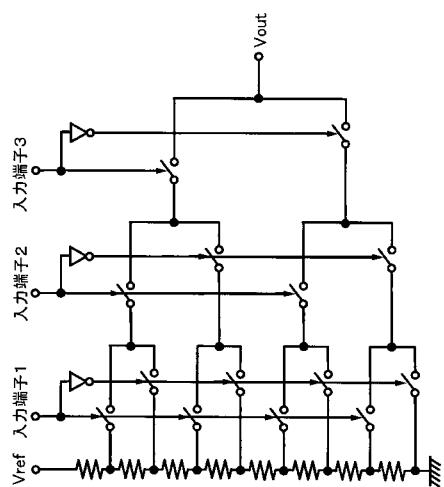

【図 17】本発明の画素構成を有する表示装置に適用可能な D A 変換回路の一例を示す図

。

【図 18】本発明の画素構成を有する表示装置に適用可能な D A 変換回路の一例を示す図

。

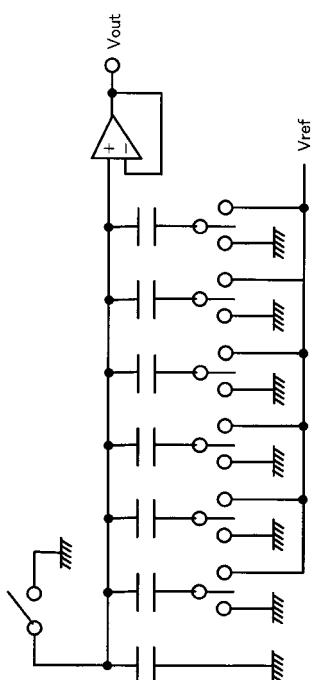

【図 19】本発明の画素構成を有する表示パネルを説明する図。

【図 20】本発明の画素構成の有する表示装置に適用可能な発光素子の例を示す図。

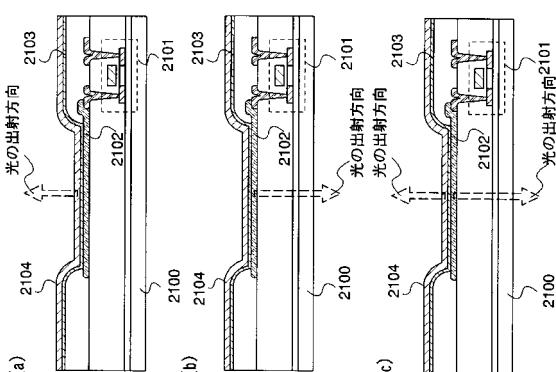

【図 21】発光素子の射出構造を説明する図。

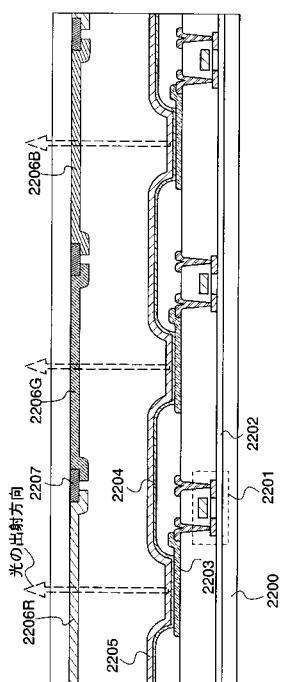

【図 22】カラーフィルターを用いてフルカラー表示を行う表示パネルの断面図。

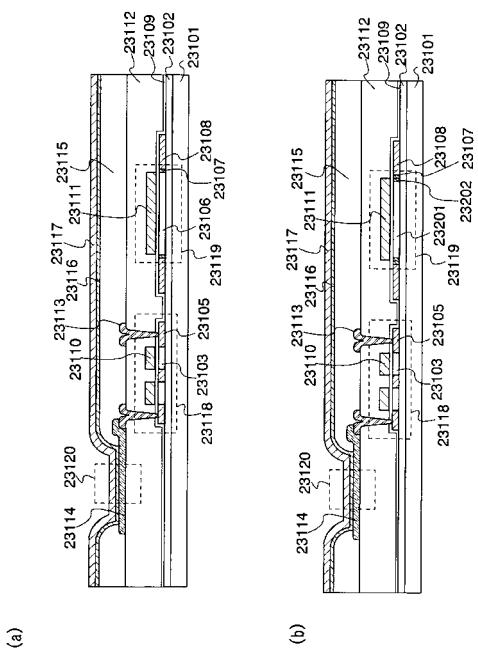

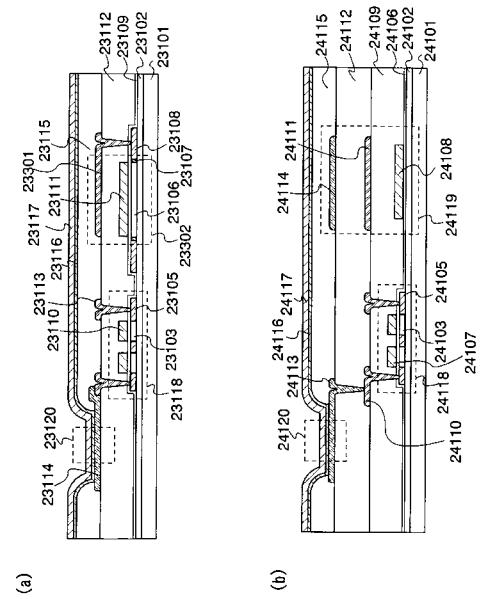

【図 23】表示パネルの部分断面図。

【図 24】表示パネルの部分断面図。

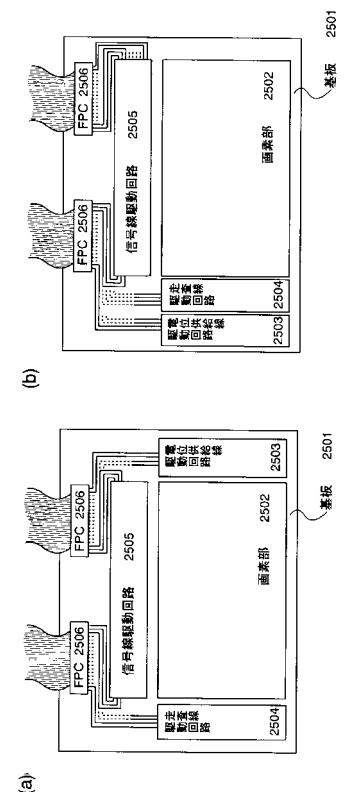

【図 25】本発明の表示装置の模式図。

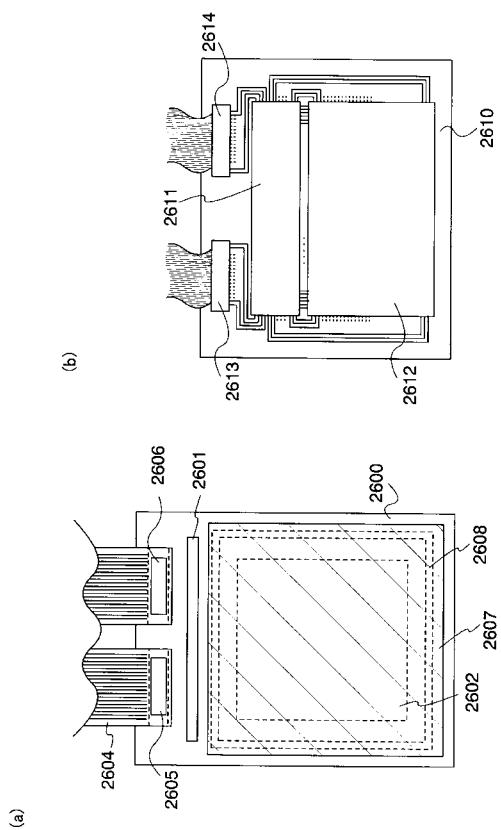

【図 26】本発明の画素構成を有する表示パネルを説明する図。

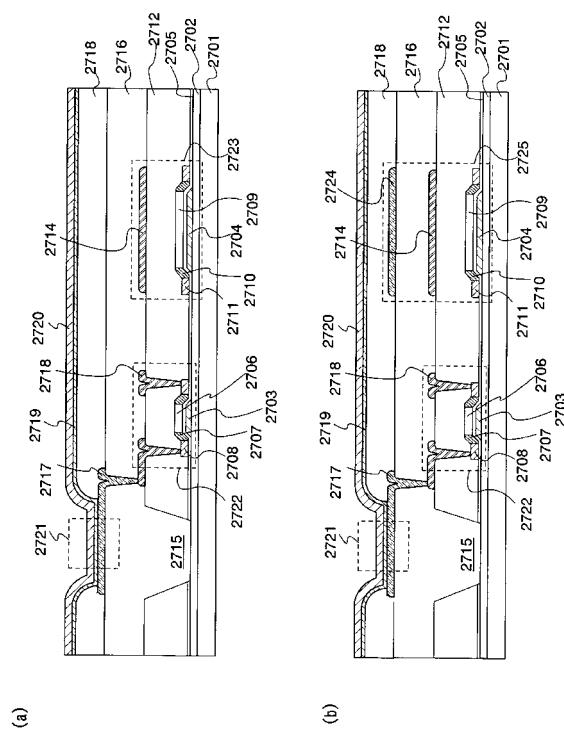

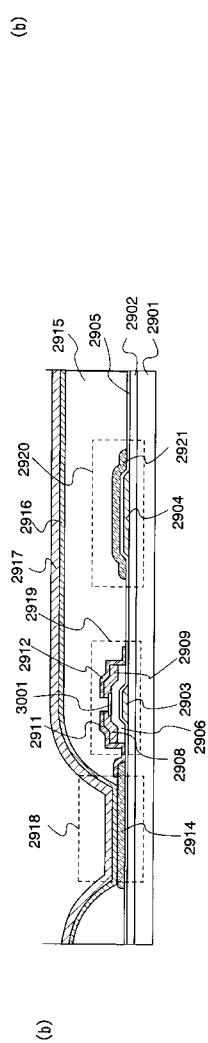

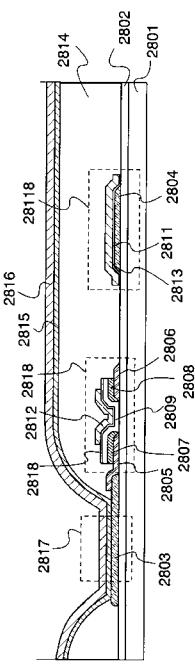

【図 27】表示パネルの部分断面図。

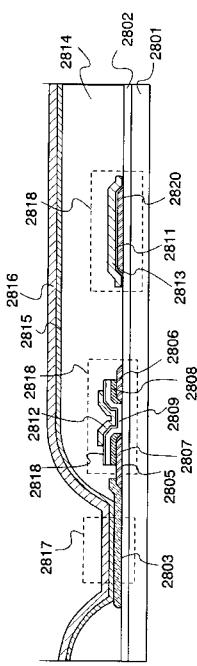

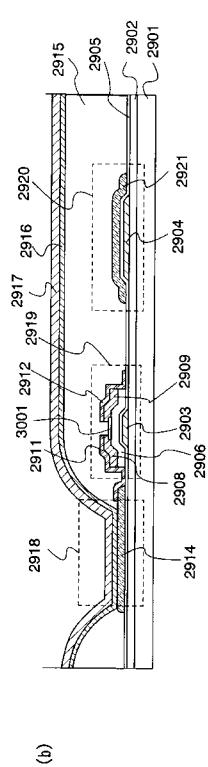

【図 28】表示パネルの部分断面図。

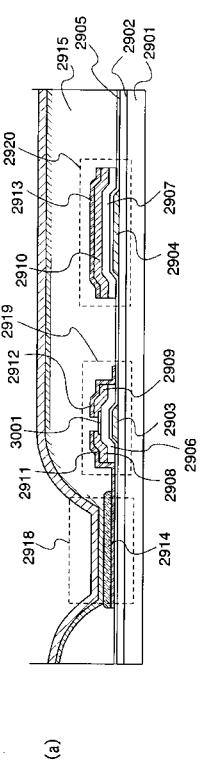

【図 29】表示パネルの部分断面図。

【図 30】表示パネルの部分断面図。

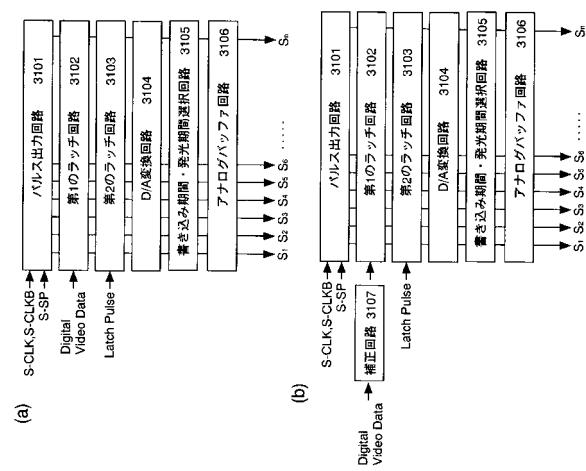

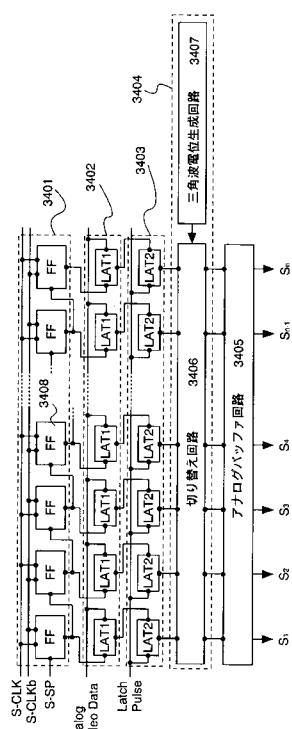

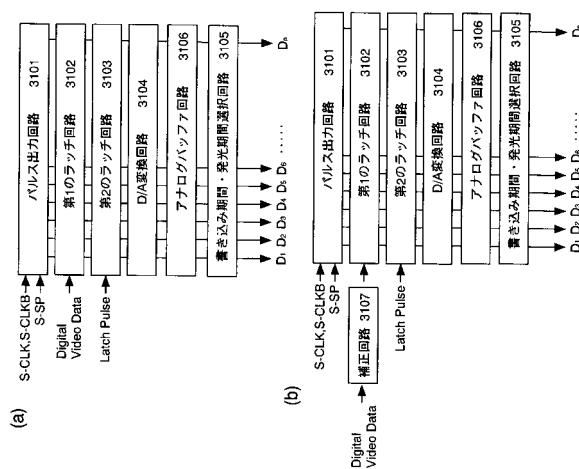

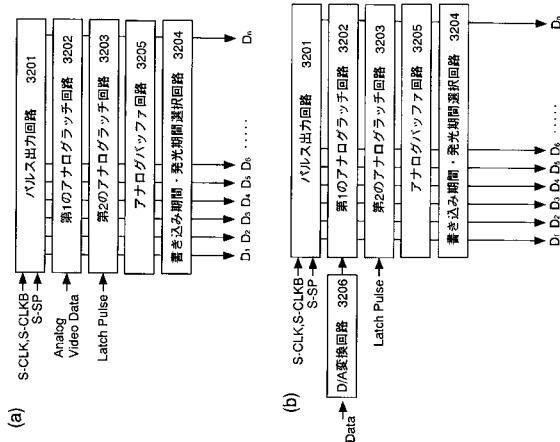

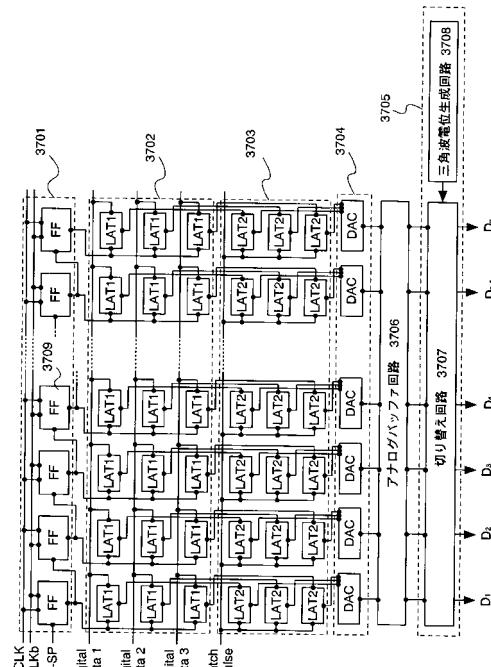

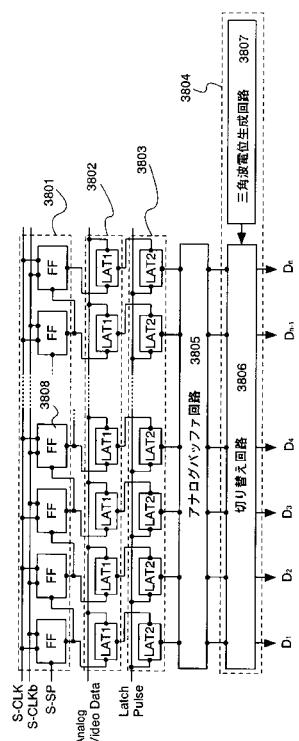

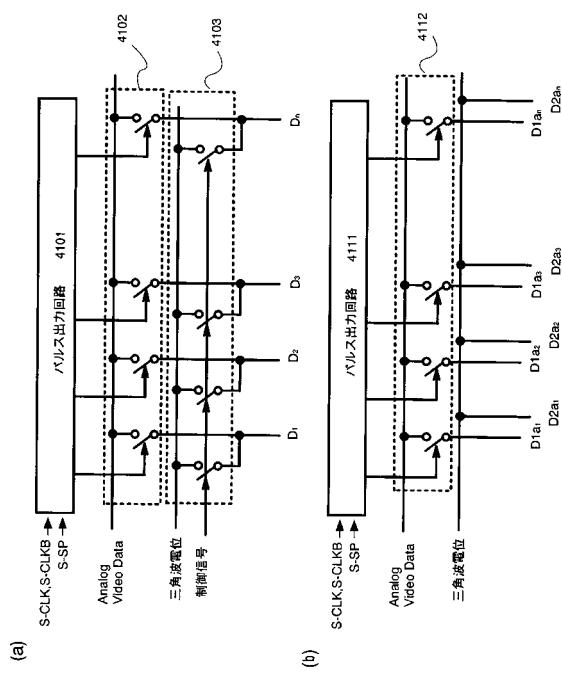

【図 31】本発明の表示装置に適用可能な信号線駆動回路の例。

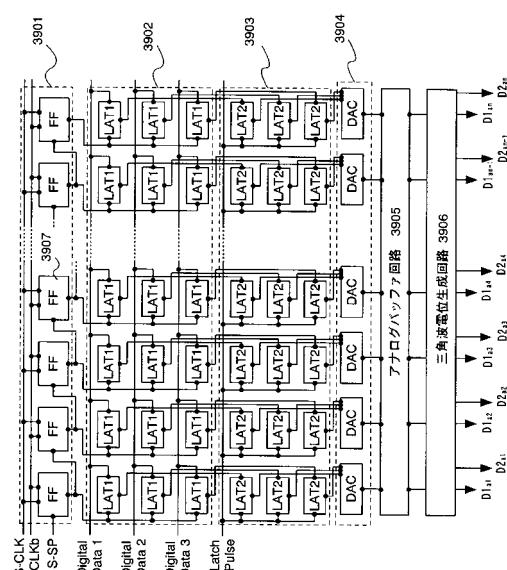

【図 32】本発明の表示装置に適用可能な信号線駆動回路の例。

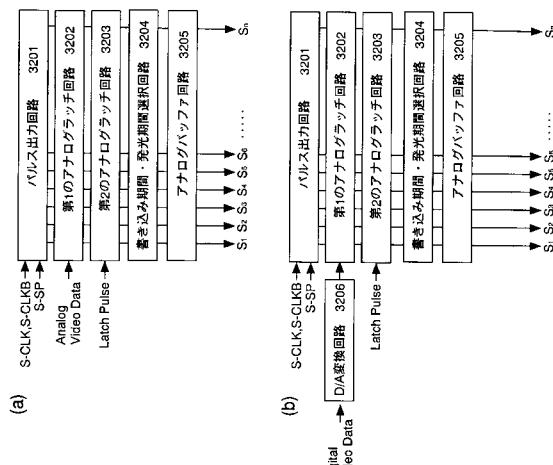

【図 33】本発明の表示装置に適用可能な信号線駆動回路の例。

【図 34】本発明の表示装置に適用可能な信号線駆動回路の例。

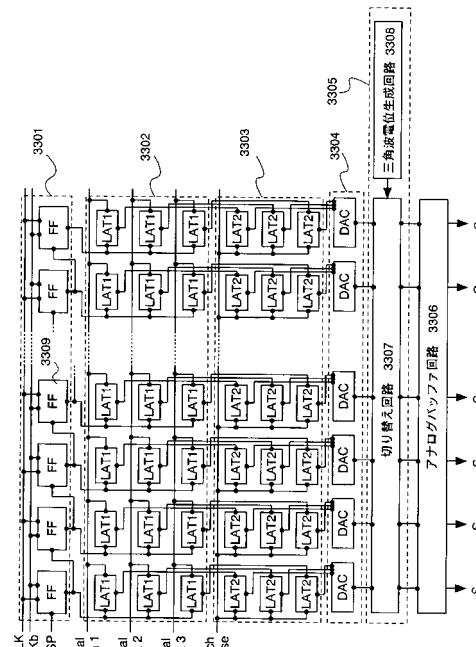

【図 35】本発明の表示装置に適用可能な信号線駆動回路の例。

【図 36】本発明の表示装置に適用可能な信号線駆動回路の例。

【図 37】本発明の表示装置に適用可能な信号線駆動回路の例。

【図 38】本発明の表示装置に適用可能な信号線駆動回路の例。

【図 39】本発明の表示装置に適用可能な信号線駆動回路の例。

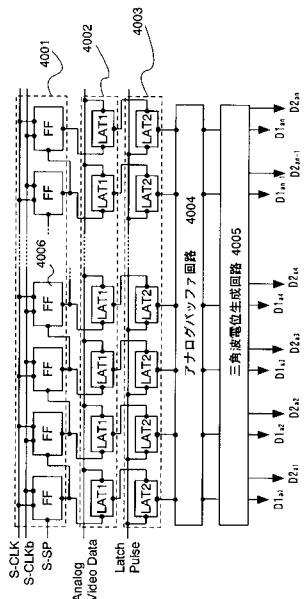

【図 40】本発明の表示装置に適用可能な信号線駆動回路の例。

【図 41】本発明の表示装置に適用可能な信号線駆動回路の例。

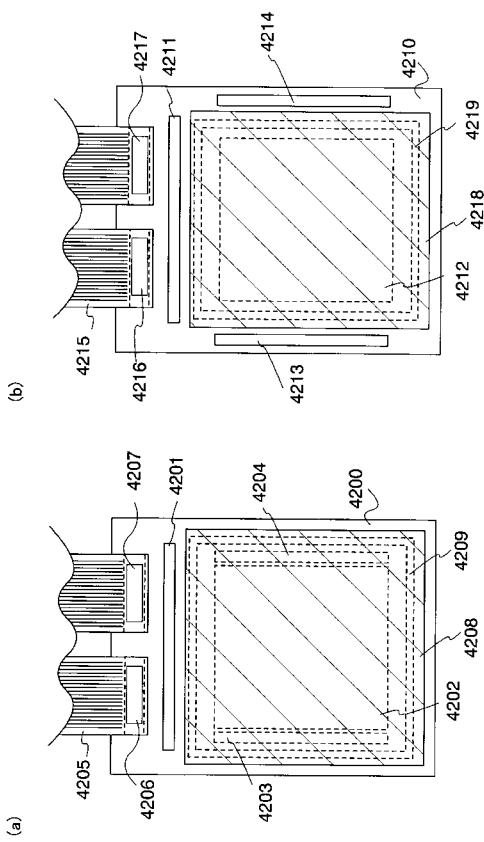

【図 42】本発明の画素構成を有する表示パネルを説明する図。

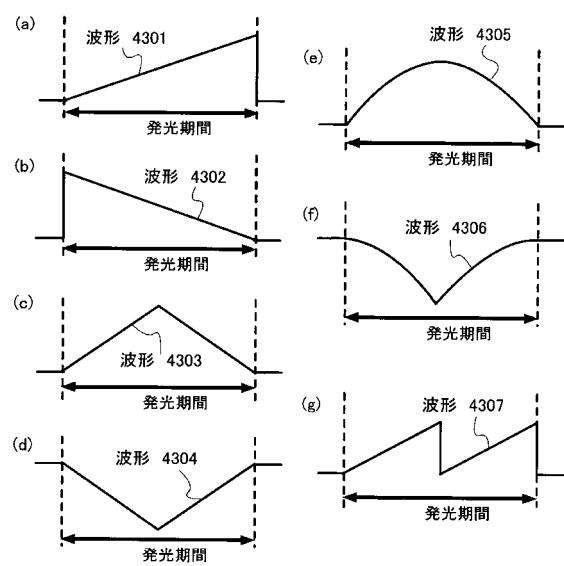

【図 43】周期的に変化する波形を説明する図。

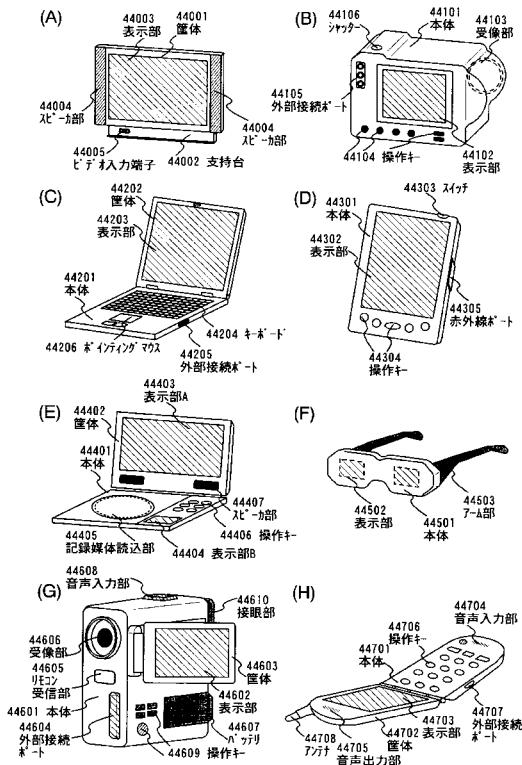

【図 44】本発明の画素構成を有する表示装置を画素部に適用可能な電子機器の例を示す図。

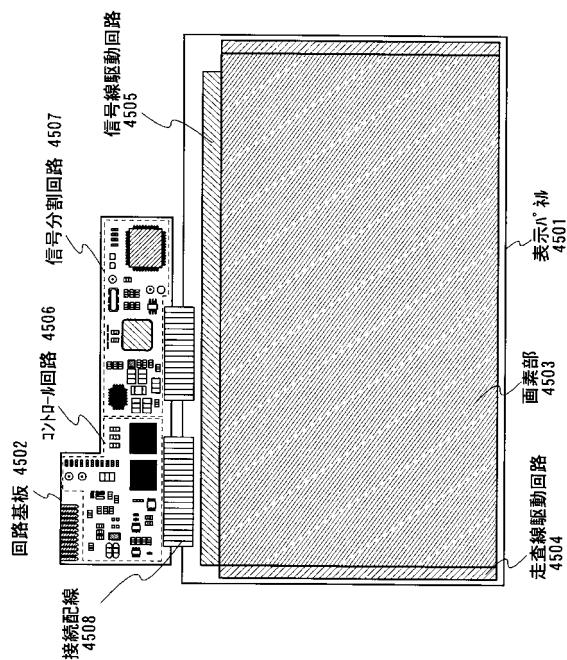

【図 45】E L モジュールの例。

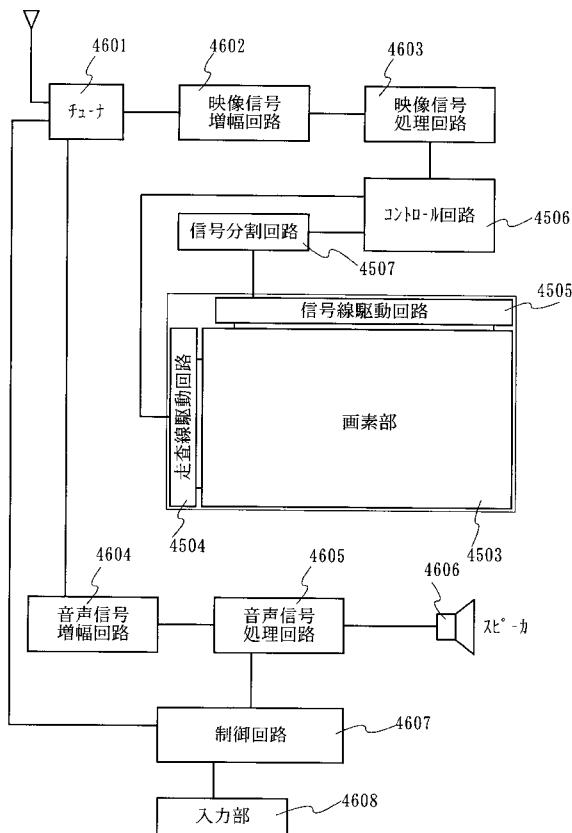

【図 46】E L テレビ受像機の主要な構成を示すブロック図。

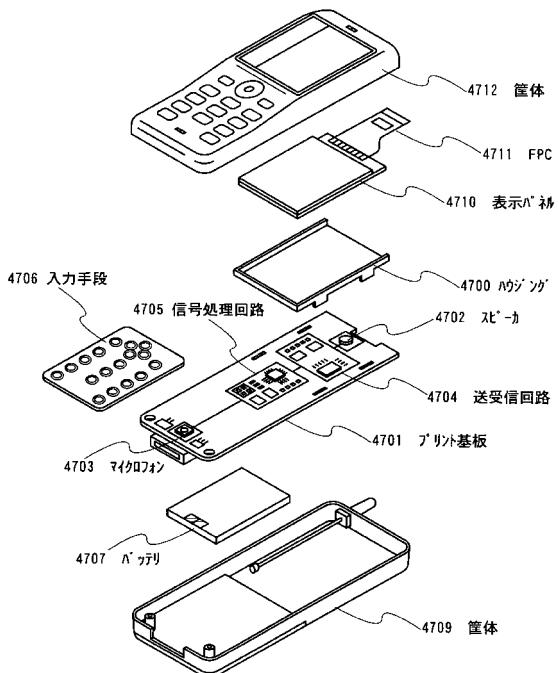

【図 47】本発明の適用可能な携帯電話機の例。

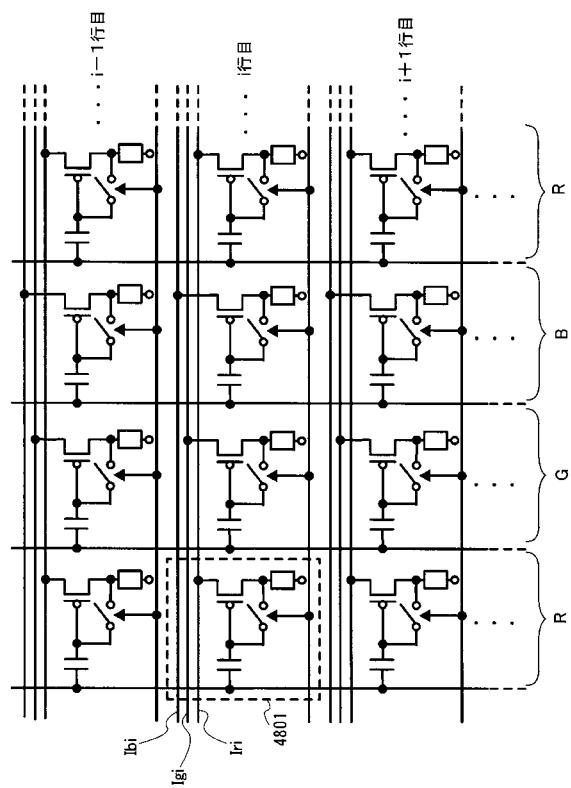

【図 48】本発明の画素構成を示す図。

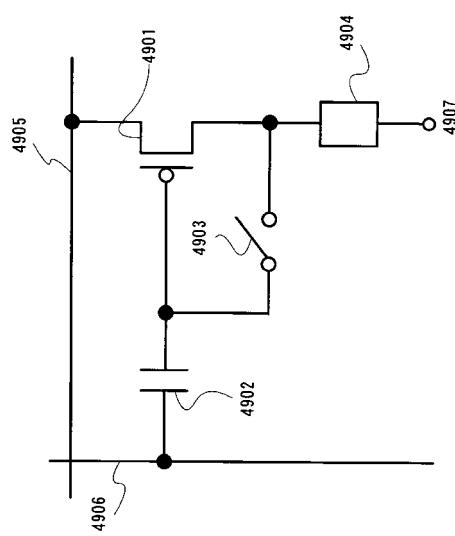

【図 49】本発明の画素構成を示す図。

10

20

30

40

50

- 【図 5 0】本発明の画素構成の動作を説明する図。

- 【図 5 1】本発明の画素構成を有する表示装置のタイミングチャートを示す図。

- 【図 5 2】本発明の画素構成を有する表示装置のタイミングチャートを示す図。

- 【図 5 3】本発明の画素構成を示す図。

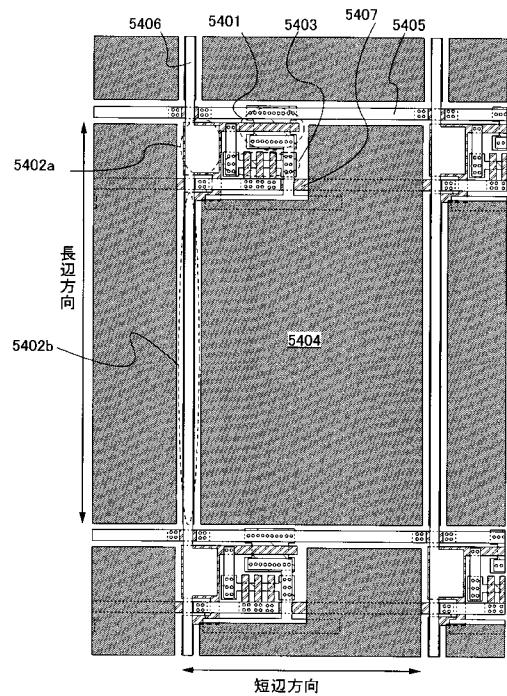

- 【図 5 4】画素のレイアウトを説明する図。

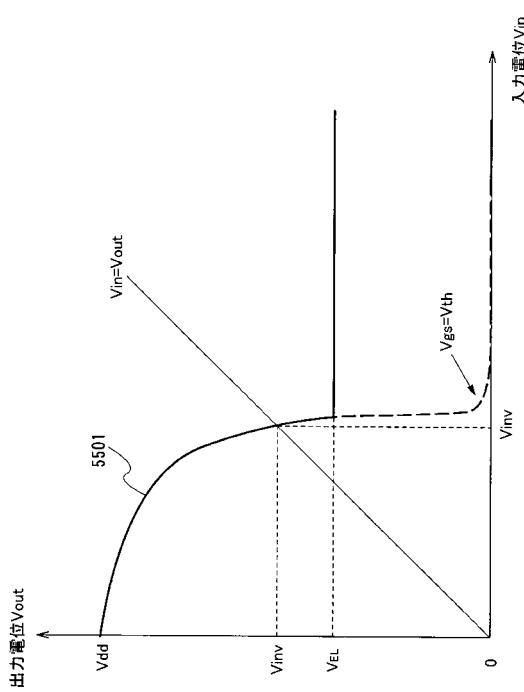

- 【図 5 5】インバータ特性を示す図。

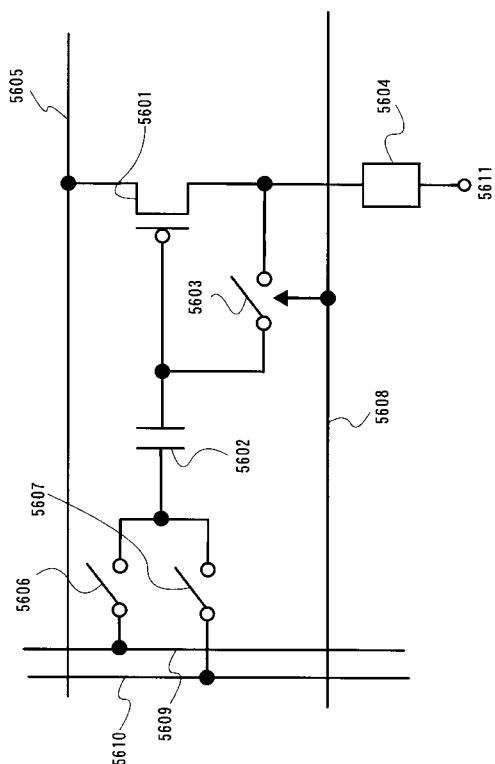

- 【図 5 6】本発明の画素構成を示す図。

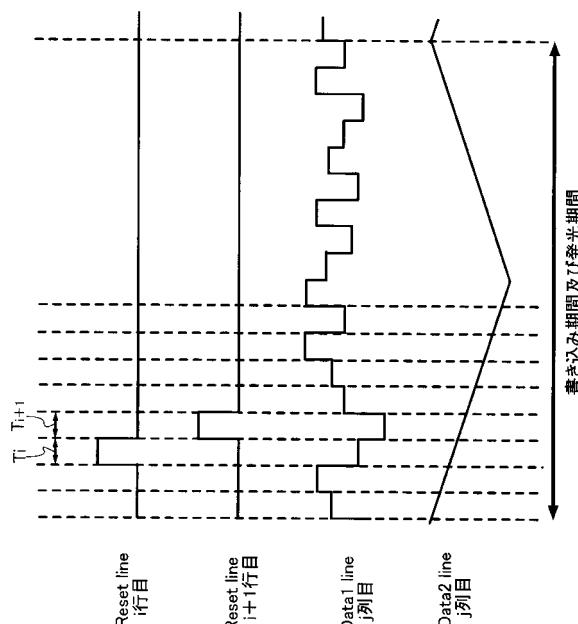

- 【図 5 7】本発明の画素構成を有する表示装置のタイミングチャートを示す図。

- 【図 5 8】本発明の表示装置の模式図。 10

- 【図 5 9】信号線に入力するビデオ信号と三角波電位との関係を説明する図。

- 【図 6 0】信号線に入力するビデオ信号と三角波電位との関係を説明する図。

- 【図 6 1】本発明の画素構成を示す図。

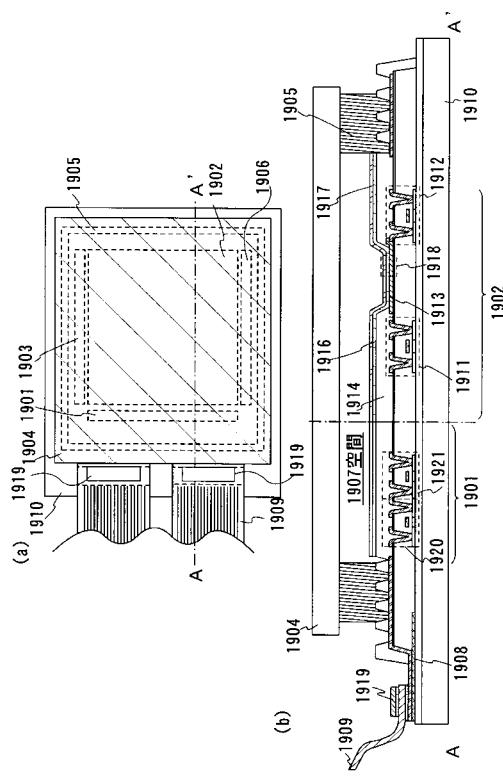

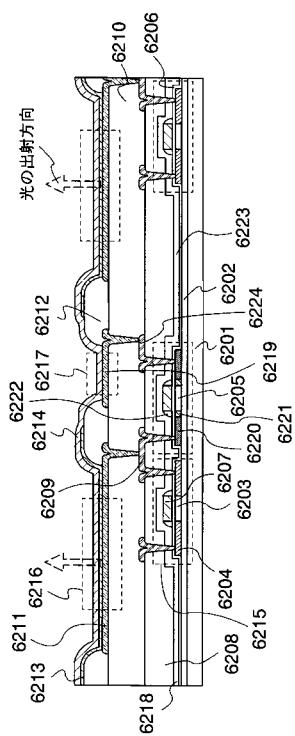

- 【図 6 2】本発明の表示パネルの断面図。

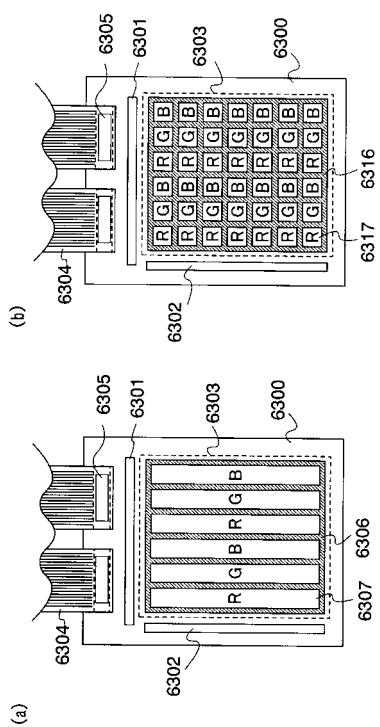

- 【図 6 3】( a ) 本発明の表示パネルの構成を示す模式図。 ( b ) 本発明の表示パネルの構成を示す模式図。

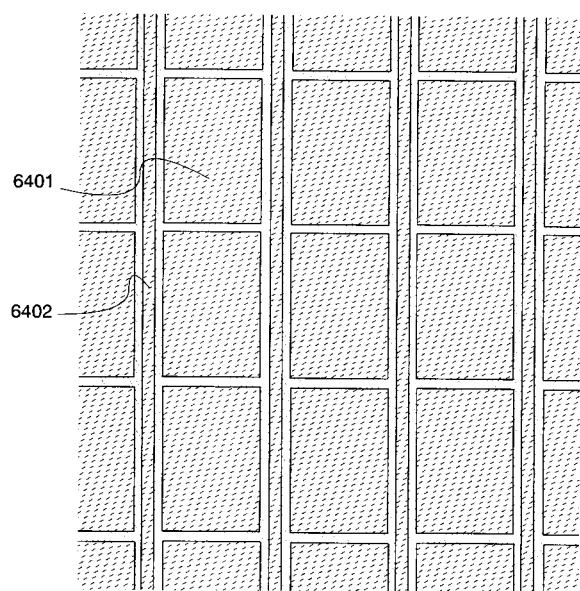

- 【図 6 4】本発明の表示パネルの画素部の模式図。

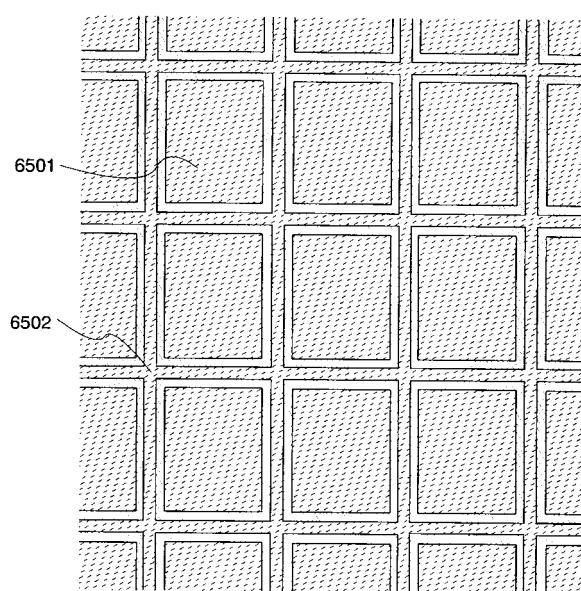

- 【図 6 5】本発明の表示パネルの画素部の模式図。

- 【図 6 6】本発明の画素構成を示す図。 20

- 【図 6 7】本発明の画素構成を示す図。

- 【図 6 8】本発明の画素構成を示す図。

- 【図 6 9】本発明の画素構成を示す図。

- 【図 7 0】本発明の画素構成を示す図。

- 【図 7 1】本発明の画素構成を示す図。

- 【図 7 2】本発明の画素構成を示す図。

- 【図 7 3】本発明の画素構成を示す図。

- 【図 7 4】本発明の画素構成を示す図。

- 【図 7 5】本発明の画素構成を示す図。

- 【図 7 6】本発明の画素構成を示す図。

- 【図 7 7】本発明の画素構成を示す図。

- 【図 7 8】本発明の画素構成を示す図。 30

- 【図 7 9】本発明の画素構成を示す図。

- 【発明を実施するための形態】

- 【0 0 3 4】

- 以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。

- 【0 0 3 5】

- (実施の形態 1)

- 本実施の形態では本発明の表示装置の画素構成とその動作原理について説明する。 40

- 【0 0 3 6】

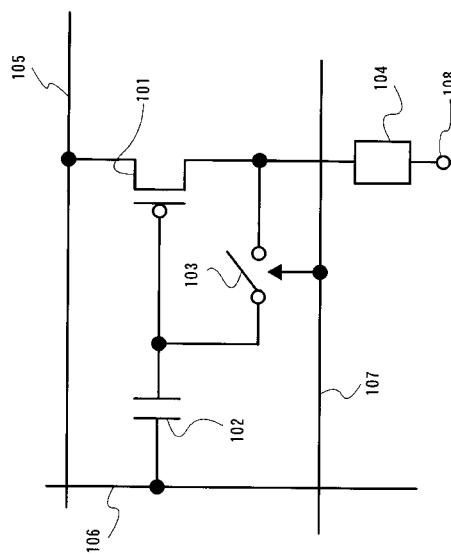

- まず、図 1 を用いて本発明の表示装置の画素構成について詳細に説明する。ここでは、一画素のみを図示しているが、表示装置の画素部は実際には行方向と列方向にマトリクスに複数の画素が配置されている。

- 【0 0 3 7】

- 画素は駆動トランジスタ 101 と、容量素子 102 と、スイッチ 103 と、発光素子 104 と、電位供給線 (Illumination line) 105 と、信号線 (Data line) 106 と、走査線 (Reset line) 107 とを有している。なお、駆動トランジスタ 101 には P チャネル型トランジスタを用いている。

- 【0 0 3 8】 50

駆動トランジスタ 101 の第 1 端子（ソース端子又はドレイン端子）は電位供給線 105 と接続され、ゲート端子は容量素子 102 を介して信号線 106 と接続され、第 2 端子（ソース端子又はドレイン端子）は発光素子 104 の陽極（画素電極）と接続されている。また、駆動トランジスタ 101 のゲート端子と第 2 端子（ソース端子又はドレイン端子）はスイッチ 103 を介して接続されている。よって、スイッチ 103 がオンしているときには駆動トランジスタ 101 のゲート端子と第 2 端子（ソース端子又はドレイン端子）は導通する。そして、スイッチ 103 がオフすると、駆動トランジスタ 101 のゲート端子と第 2 端子（ソース端子又はドレイン端子）は非導通となり、その瞬間の駆動トランジスタ 101 のゲート端子（若しくは第 2 端子）と信号線 106 との電位差（電圧）を容量素子 102 は保持することができる。なお、発光素子 104 の陰極（Cathode）108 は Vss の電位が設定されている。なお、Vss とは、画素の発光期間に電位供給線 105 に設定される電源電位 Vdd を基準として、 $Vss < Vdd$  を満たす電位である。例えば、 $Vss = GND$ （グラウンド電位）としても良い。

10

## 【0039】

次に、図 1 の画素構成の動作原理について詳しく説明する。

## 【0040】

画素への信号書き込み期間には、信号線 106 にはアナログ信号電位が設定される。このアナログ信号電位がビデオ信号に相当する。なお、このビデオ信号は 3 値以上で表される信号であり、アナログ信号電位とは、時間とともに変化し 3 値以上の状態を持つ電位である。そして、画素へビデオ信号を書き込む際には、走査線 107 に信号を入力してスイッチ 103 をオンさせ、且つ電位供給線 105 の電位を電源電位 Vdd にし、駆動トランジスタ 101 の第 1 端子に電源電位 Vdd を設定する。すると、駆動トランジスタ 101 及び発光素子 104 に電流が流れ、容量素子 102 には電荷の蓄積又は放電が行われる。

20

## 【0041】

このとき、駆動トランジスタ 101 の第 1 端子はソース端子となり、第 2 端子はドレイン端子となっている。そして、スイッチ 103 がオンになっている状態で駆動トランジスタ 101 に流れる電流が増加すると、発光素子 104 に流れる電流も大きくなるため、発光素子 104 での電圧降下は大きくなり、発光素子 104 の電極間の電位差は大きくなる。つまり、発光素子 104 の陽極の電位は電位供給線 105 の電位に近づく。すると、駆動トランジスタ 101 のゲート端子の電位も電位供給線 105 の電位に近づくため、駆動トランジスタ 101 のゲート端子とソース端子の電位差が小さくなり、駆動トランジスタ 101 に流れる電流は減少する。一方、発光素子 104 に流れる電流が小さくなると、発光素子 104 での電圧降下は小さくなり、発光素子 104 の電極間の電位差は小さくなる。つまり、発光素子 104 の陽極の電位は陰極 108 の電位に近づく。すると、駆動トランジスタ 101 のゲート端子も陰極 108 の電位に近づくため、駆動トランジスタ 101 のゲート端子とソース端子の電位差が大きくなり、駆動トランジスタ 101 に流れる電流が増加する。こうして、駆動トランジスタ 101 のゲート端子は駆動トランジスタ 101 に一定の電流が流れるような電位に落ち着く。そして、そのときの駆動トランジスタ 101 のゲート端子の電位と信号線 106 の電位との電位差分の電荷が容量素子 102 に蓄積される。

30

## 【0042】

こうしてこの画素へビデオ信号の書き込みが終了する。

## 【0043】

このように駆動トランジスタ 101 及び発光素子 104 に流れる電流が一定となり、定常状態となったところで、スイッチ 103 をオフさせる。すると、容量素子 102 は、スイッチ 103 がオフした瞬間の信号線 106 の電位と駆動トランジスタ 101 のゲート端子（若しくはドレイン端子）との電位差  $Vp$ （電圧）を保持する。

40

## 【0044】

画素への信号書き込み期間において、画素へのビデオ信号の書き込み終了後、その画素の電位供給線 105 に設定する電位を、駆動トランジスタ 101 がオンしたとしても、発光

50

素子 104 に印加される電圧が発光素子 104 のしきい値電圧  $V_{EL}$  以下となるようにする。例えば、電位供給線 105 の電位は、発光素子 104 の陰極 108 の電位  $V_{SS}$  と同じ電位、或いはそれ以下にしても良い。なお、この電位を電位供給線 105 に設定するタイミングはスイッチ 103 をオフにするタイミングと同時か、それよりも後にする。

#### 【0045】

なお、画素にビデオ信号が書き込まれ、駆動トランジスタ 101 の第 1 端子に接続された電位供給線 105 に電源電位  $V_{DD}$  が設定されているときには、その画素にビデオ信号が書き込まれた際に信号線 106 に設定されたアナログ信号電位を基準にして、信号線 106 の電位の変動に従って駆動トランジスタ 101 のオンオフが制御されるようになる。つまり、信号線 106 の電位が、画素への信号書き込み期間に画素にビデオ信号が書き込まれた際のアナログ信号電位以上のときには駆動トランジスタ 101 はオフし、画素にビデオ信号が書き込まれた際のアナログ信号電位より低くなると駆動トランジスタ 101 はオンする。

10

#### 【0046】

なぜなら、画素にビデオ信号が書き込まれると、容量素子 102 が電位差 ( $V_p$ ) を保持するため、信号線 106 の電位が、画素にビデオ信号が書き込まれた際のアナログ信号電位以上のときには、駆動トランジスタ 101 のゲート端子の電位も、画素にビデオ信号が書き込まれた際のゲート端子の電位以上となり、駆動トランジスタ 101 はオフする。一方、信号線 106 の電位が、画素への信号書き込み期間に画素にビデオ信号が書き込まれた際のアナログ信号電位より低くなると、駆動トランジスタ 101 のゲート端子の電位も、画素にビデオ信号が書き込まれた際のゲート端子の電位より低くなるため駆動トランジスタ 101 はオンする。

20

#### 【0047】

したがって、画素の発光期間には、駆動トランジスタ 101 の第 1 端子が接続された電位供給線 105 に電源電位  $V_{DD}$  を設定し、スイッチ 103 をオフにした状態で、信号線 106 に設定する電位をアナログ的に変化させることで、駆動トランジスタ 101 のオンオフを制御する。つまり、発光素子 104 に電流が流れている時間をアナログ的に制御して階調を表現することができる。

30

#### 【0048】

画素の発光期間において、信号線 106 に設定する電位について説明する。信号線 106 に設定する電位は周期的に変化する波形のアナログ電位を用いることができる。なお、このアナログ電位とは時間とともに連続的に変化する電位である。そして、好ましくはビデオ信号に相当するアナログ信号電位のとりうる範囲の最低電位から最高電位へ連続的に変化する電位、若しくは最高電位から最低電位へ連続的に変化する電位、又は最低電位と最高電位との間をくり返し連続的に変化する電位とする。

#### 【0049】

例えば、発光期間には、信号線 106 に低電位から高電位にアナログ的に変化する電位を設定する。一例として、図 43(a) の波形 4301 のように直線的に電位が上昇するようにしても良い。なお、このような波形をのこぎり波ともいう。

40

#### 【0050】

また、高電位から低電位へアナログ的に変化する電位を設定しても良い。例えば、波形 4302 のように直線的に電位が下降するようにしても良い。

#### 【0051】

また、それらを組み合わせた波形でも良い。つまり、一例として、波形 4303 のように低電位から高電位へ直線的に上昇し、高電位から低電位へ下降するような電位を設定しても良い。なお、以下このような波形 4303 を三角波電位という。または、波形 4304 のように高電位から低電位へ直線的に下降し、低電位から高電位へ直線的に上昇するような三角波電位を設定しても良い。

#### 【0052】

また、信号線 106 に設定する電位は直線的な変化でなくとも良い。波形 4305 のよう

50

に全波整流回路の出力波形の1周期に相当する波形の電位を設定しても良いし、波形4306のような電位を設定しても良い。

#### 【0053】

このような波形にすることにより、ビデオ信号に対する発光時間を自由に設定することができる。よって、ガンマ補正などを行うことも可能となる。

#### 【0054】

また、画素の発光期間において、上記の波形4301、波形4302、波形4303、波形4304、波形4305または波形4306のパルスを複数連続して設定しても良い。一例として、波形4307に示すように、波形4301のパルスを画素の発光期間において、二回連続して設定しても良い。

10

#### 【0055】

このようにすることにより、発光時間を1フレーム内で分散させることができる。その結果、フレーム周波数が見かけ上は向上したようになり、画面のちらつきを防止することができる。

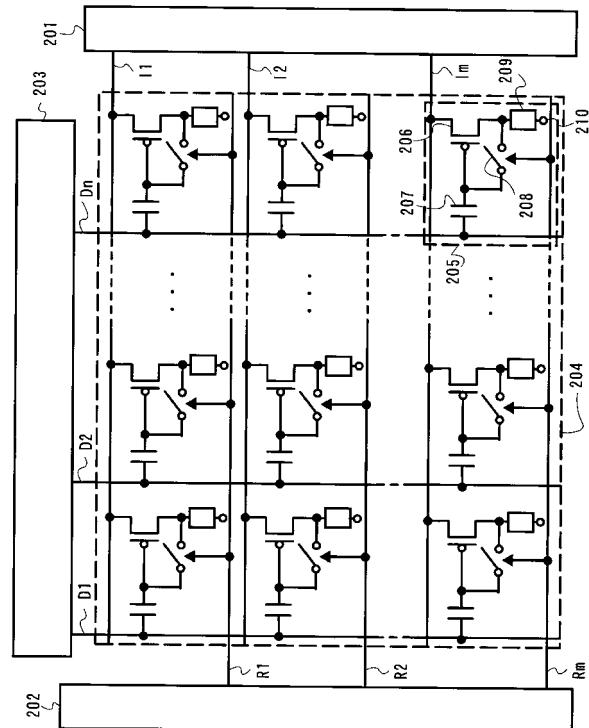

#### 【0056】

続いて画素部に図1の画素構成を有する表示装置について図2を用いて説明する。図2の表示装置は、電位供給線駆動回路201、走査線駆動回路202、信号線駆動回路203、画素部204を有し、画素部204は画素205を複数備えている。行方向に配置された走査線(Reset line)R1～Rm及び電位供給線(illumination line)I1～Imと列方向に配置された信号線(Data line)D1～Dnに対応して画素205がマトリクスに配置されている。

20

#### 【0057】

画素205は駆動トランジスタ206と、容量素子207と、スイッチ208と、発光素子209と、走査線Ri(R1～Rmのうちいずれか一つ)と、電位供給線Ii(I1～Imのうちいずれか一つ)と、信号線Dj(D1～Dnのうちいずれか一つ)とを有している。なお、駆動トランジスタ206にはPチャネル型トランジスタを用いている。なお、画素205は画素部204に複数配置された画素の一画素を示している。

30

#### 【0058】

駆動トランジスタ206の第1端子(ソース端子又はドレイン端子)は電位供給線Iiと接続され、ゲート端子は容量素子207を介して信号線Djと接続され、第2端子(ソース端子又はドレイン端子)は発光素子209の陽極(画素電極)と接続されている。なお、電位供給線I1～Imには、発光期間において、発光素子209に所望の電流を流すための電源電位Vddが設定される。

40

#### 【0059】

また、駆動トランジスタ206のゲート端子と第2端子(ソース端子又はドレイン端子)はスイッチ208を介して接続されている。よってスイッチ208がオンしているときは駆動トランジスタ206のゲート端子と第2端子(ソース端子又はドレイン端子)は導通される。そして、スイッチ208がオフすると、駆動トランジスタ206のゲート端子と第2端子(ソース端子又はドレイン端子)は非導通となり、その瞬間の駆動トランジスタ206のゲート端子(又は第2端子)と信号線Djとの電位差(電圧)を容量素子207は保持することができる。また、発光素子209の陰極(Cathode)210は低電源電位Vssが設定されている。なお、低電源電位とは電源電位Vddより低い電位である。

#### 【0060】

なお、電位供給線駆動回路201及び走査線駆動回路202は左右に配置してあるがこれに限定されない。片側にまとめて配置しても良い。

#### 【0061】

また、電位供給線I1～Imに設定する電源電位はVddに限られず、例えば、RGBの色要素からなるフルカラー表示の場合には、RGBのそれぞれの色要素の画素毎に設定する電源電位の値を変えて良い。

50

**【 0 0 6 2 】**

つまり、画素の一行毎に R、G、B の色要素毎の電位供給線を設けて、それぞれの色要素の列の画素は、その駆動トランジスタの第 1 端子（ソース端子又はドレイン端子）をそれぞれの行の色要素毎の電位供給線に接続する。ここで、色要素の画素毎に発光素子に印加する電圧を変える場合について図 4 8 を用いて説明する。

**【 0 0 6 3 】**

図 4 8 は、図 2 の画素部 2 0 4 の一部を示した図である。図 4 8 に示す画素 4 8 0 1 は電位供給線以外は図 2 の画素 2 0 5 と同じ構成であるため、それぞれの画素を構成する駆動トランジスタ、容量素子、スイッチ、発光素子の符号を省略してある。よって、画素 4 8 0 1 を構成するこれらの素子の符号は図 2 及びその説明を参照されたい。図 4 8 において、<sup>10</sup> i 行目（1 ~ m 行のいずれか一）の画素 4 8 0 1 は電位供給線 I r i 、I g i 、I b i を有している。そして、R の色要素の列の画素 4 8 0 1 は、駆動トランジスタ 2 0 6 の第 1 端子が I r i に接続され、G の色要素の列の画素 4 8 0 1 は、駆動トランジスタ 2 0 6 の第 1 端子が I g i に接続され、B の色要素の列の画素 4 8 0 1 は、駆動トランジスタ 2 0 6 の第 1 端子が I b i に接続されている。電位供給線 I r i には発光期間に R の色要素の列の画素の発光素子 2 0 9 に所望の電流を流すための電位 V d d 1 が設定される。電位供給線 I g i には発光期間に G の色要素の列の画素の発光素子 2 0 9 に所望の電流を流すための電位 V d d 2 が設定される。電位供給線 I b i には発光期間に B の色要素の列の画素の発光素子 2 0 9 に所望の電流を流すための電位 V d d 3 が設定される。こうして、色要素毎に画素 4 8 0 1 の発光素子 2 0 9 に印加する電圧を設定することができる。<sup>20</sup>

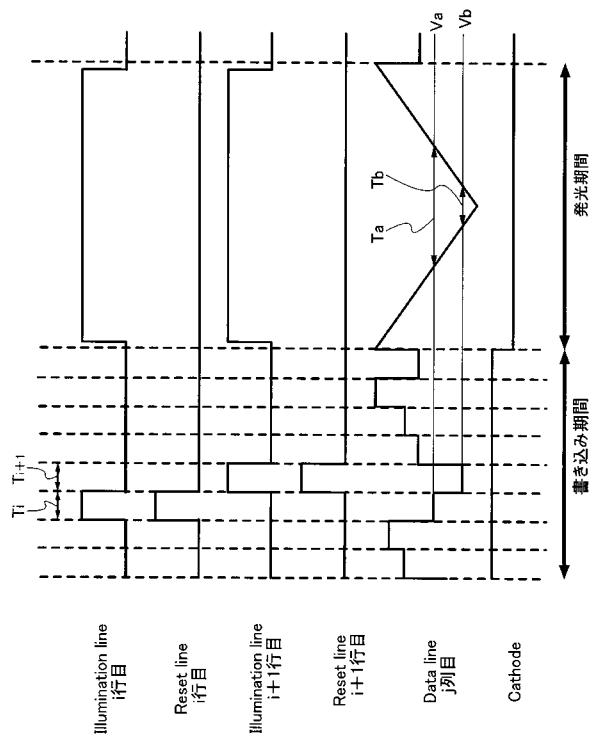

**【 0 0 6 4 】**

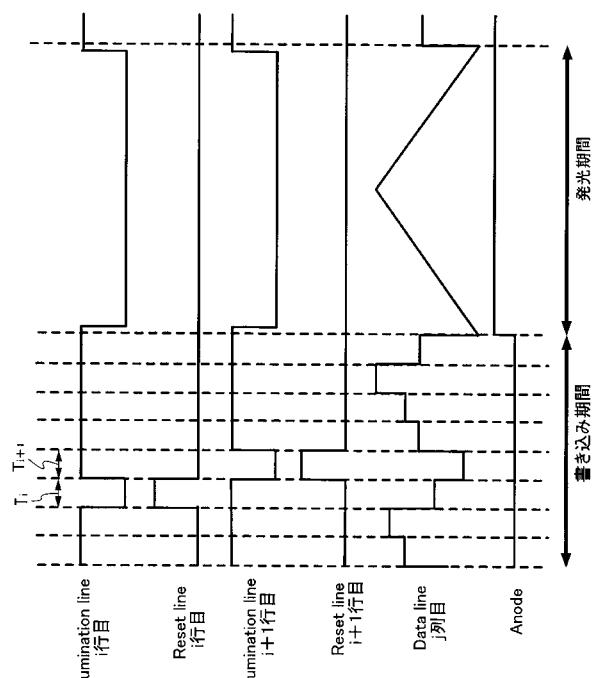

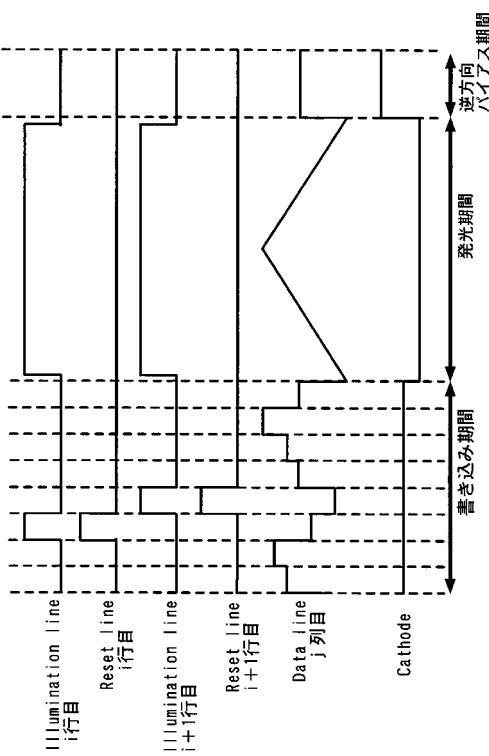

次に、図 2 及び図 3 を用いて本発明の表示装置の動作原理について説明する。図 3 は図 2 における表示装置の画素部 2 0 4 のある画素列（j 列目）のタイミングチャートを示す図である。なお、画素部 2 0 4 に複数配置されたそれぞれの画素は、画素 2 0 5 と同様の構成であるため、それぞれの画素の駆動トランジスタ、容量素子、スイッチ、発光素子は画素 2 0 5 と同様の符号を用いて説明する。

**【 0 0 6 5 】**

図 3 に示すように、書き込み期間には画素の信号線 D j （j 列目の Data line ）にアナログ信号電位が入力されている。そして、<sup>30</sup> i 行目の画素の書き込み時間 T i に、走査線 R i （i 行目の Reset line ）と電位供給線 I i （i 行目の I l l u m i n a t i o n line ）にパルス信号が入力されると、i 行目の画素のスイッチ 2 0 8 がオンし、駆動トランジスタ 2 0 6 の第 1 端子（ソース端子又はドレイン端子）には電位供給線 I i からの電源電位 V d d が設定され、容量素子 2 0 7 、駆動トランジスタ 2 0 6 及び発光素子 2 0 9 に電流が流れれる。

**【 0 0 6 6 】**

そして、容量素子 2 0 7 では電荷の蓄積若しくは放電が行われる。つまり、容量素子 2 0 7 にもともと蓄積されていた電荷と信号線 D j （Data line ）に設定された電位（V a ）との関係で電荷の蓄積か放電のどちらかが起きる。

**【 0 0 6 7 】**

やがて、容量素子 2 0 7 に電流が流れなくなり、駆動トランジスタ 2 0 6 及び発光素子 2 0 9 に流れる電流が一定となる。このとき、完全に定常状態にならなくてもよい。駆動トランジスタ 2 0 6 のオンオフを制御するのに必要なゲート電位が取得できれば良い。好ましくは、このとき駆動トランジスタ 2 0 6 は飽和領域で動作するようになっていると良い。<sup>40</sup>

**【 0 0 6 8 】**

その後、スイッチ 2 0 8 をオフにする。すると、容量素子 2 0 7 は駆動トランジスタ 2 0 6 のオンオフを制御するのに必要なゲート端子の電位と、スイッチ 2 0 8 をオフにした瞬間の信号線 D j （Data line ）に設定されているアナログ信号電位との電位差を保持する。

**【 0 0 6 9 】**

10

20

30

40

50

また、スイッチ 208 をオフにしたと同時に若しくはその後、電位供給線  $I_{i(Illumination\ line)}$  の信号が H レベル（電源電位  $V_{dd}$ ）から L レベルに立ち下がるようにする。そして、その後の書き込み期間において、駆動トランジスタ 206 がオンしているときにも発光素子 209 に印加される電圧が発光素子 209 のしきい値電圧以下となるようにする。つまり、他の行の画素の信号書き込み時間に  $i$  行目の画素の発光素子 209 が発光しないようにする。

#### 【0070】

つまり、 $i$  行目の画素の書き込み時間において、駆動トランジスタ 206 のオンオフを制御するのに必要なゲート端子の電位を取得するための間は、走査線  $R_i(R_{eset}\ line)$  と電位供給線  $I_{i(Illumination\ line)}$  の信号は H レベルとし、駆動トランジスタ 206 のオンオフを制御するのに必要なゲート端子の電位を取得後に、走査線  $R_i(R_{eset}\ line)$  と電位供給線  $I_{i(Illumination\ line)}$  の信号を同時に L レベルに立ち下がるようにするか、若しくは走査線  $R_i(R_{eset}\ line)$  の信号が L レベルに立ち下がった後、電位供給線  $I_{i(Illumination\ line)}$  の信号を L レベルに立ち下がるようにする。また、もちろん  $i$  行目の画素への信号書き込み時間  $T_i$  となる以前の画素への信号書き込み期間においても、走査線  $R_i(R_{eset}\ line)$  と電位供給線  $I_{i(Illumination\ line)}$  の信号は L レベルとしておく。

#### 【0071】

こうして、 $i$  行目の画素の書き込み時間  $T_i$  には、 $i$  行目  $j$  列の画素に信号線  $D_j(Data\ line)$  からビデオ信号が書き込まれる。そして、 $i$  行目の画素の書き込み時間  $T_i$  には、各画素列毎にそれぞれの信号線  $D_1 \sim D_n(Data\ line)$  からそれぞれのアナログ信号電位が入力され、各列の  $i$  行目の画素にビデオ信号が書き込まれる。

#### 【0072】

次に、 $i+1$  行目の画素への信号書き込み時間  $T_{i+1}$  には、走査線  $R_{i+1}(R_{eset}\ line)$  と電位供給線  $I_{i+1}(Illumination\ line)$  にパルス信号が入力され、 $i+1$  行目  $j$  列の画素の信号線  $D_j(Data\ line)$  には電位 ( $V_b$ ) が入力され、 $i+1$  行目  $j$  列の画素にビデオ信号が書き込まれる。なお、このとき、各画素列毎にそれぞれの信号線  $D_1 \sim D_n(Data\ line)$  からそれぞれのアナログ信号電位が入力され、各列の  $i+1$  行目の画素にもビデオ信号が書き込まれる。

#### 【0073】

このように、画素の各行の走査線  $R_1 \sim R_m(R_{eset}\ line)$  と電位供給線  $I_1 \sim I_m(Illumination\ line)$  にパルス信号が入力されて、それぞれの画素にビデオ信号が書き込まれると 1 フレーム期間の画素部 204 への信号書き込み時間が終了する。

#### 【0074】

続いて、発光期間には、全行の画素 205 の駆動トランジスタ 206 の第 1 端子（ソース端子又はドレン端子）に電源電位  $V_{dd}$  を設定するため、図 3 に示すように電位供給線  $I_1 \sim I_m(Illumination\ line)$  に H レベル ( $V_{dd}$ ) の信号を入力する。また、信号線  $D_1 \sim D_n(Data\ line)$  には三角波電位を設定する。すると、 $i$  行目  $j$  列の画素は信号線  $D_j(Data\ line)$  が  $V_a$  より高い電位であるときには発光素子 209 は非発光の状態を維持し、信号線  $D_j(Data\ line)$  が  $V_a$  より低い電位の間 ( $T_a$ ) は発光素子 209 は発光する。また、 $i+1$  行目  $j$  列の画素も同様に、期間 ( $T_b$ ) の間は発光素子 209 が発光する。

#### 【0075】

なお、画素への信号書き込み期間が終了した後、ビデオ信号が書き込まれたアナログ信号電位より高い電位が信号線  $D_1 \sim D_n(Data\ line)$  に設定されている間はその画素の発光素子 209 は発光せず、信号が書き込まれた際のアナログ信号電位より低くなるとその画素の発光素子 209 が発光する原理については、図 1 の画素構成を用いて説明したとおりなのでここでは説明を省略する。

10

20

30

40

50

## 【0076】

このように、発光期間においては、全画素の信号線 D<sub>1</sub> ~ D<sub>n</sub> に三角波電位が設定され、それぞれ書き込み期間にビデオ信号が書き込まれた際のアナログ信号電位にしたがって発光素子 209 の発光時間が設定される。こうして、アナログ時間階調表示が可能となる。

## 【0077】

なお、発光素子 209 の発光・非発光を制御する駆動トランジスタ 206 のオンオフは、上述したように、書き込み期間に信号線 D<sub>1</sub> ~ D<sub>n</sub> (Data line) に設定されたアナログ信号電位が、発光期間に信号線 D<sub>1</sub> ~ D<sub>n</sub> (Data line) に入力される三角波電位より高いか低いかで決まり、デジタル的に制御することができる。よって、駆動トランジスタ 206 の特性のバラツキの影響を受けることが少なく駆動トランジスタ 206 のオンオフを制御することができる。つまり、画素毎の発光のバラツキを改善することができる。10

## 【0078】

なお、発光期間において、信号線 D<sub>1</sub> ~ D<sub>n</sub> (Data line) に設定する電位は、図 43 (a)、(b)、(c)、(d)、(e)、(f)、(g) で示したように、波形 4301、波形 4302、波形 4303、波形 4304、波形 4305、波形 4306 若しくは波形 4307、又はこれらの波形を複数連続して設定しても良い。

## 【0079】

これらの波形を連続して設定することにより、発光時間を 1 フレーム内で分散させることができ。その結果、フレーム周波数が見かけ上は向上したようになり、画面のちらつきを防止することができる。20

## 【0080】

なお、陰極 210 (Cathode) に設定される低電源電位は、画素への信号書き込み期間と発光期間とで電位を異なるようにしても良い。図 3 に示すように、画素への信号書き込み期間における陰極 210 (Cathode) の電位を発光期間における陰極 210 (Cathode) の電位より高くしておくとよい。つまり、画素への信号書き込み期間における陰極 210 (Cathode) の電位を V<sub>ss2</sub> とし、発光期間における陰極 210 (Cathode) の電位を V<sub>ss</sub> とする。そして、このとき V<sub>dd</sub> > V<sub>ss2</sub> > V<sub>ss</sub> とする。例えば V<sub>ss</sub> = GND (グラウンド電位) としても良い。30

## 【0081】

このように、画素への信号書き込み期間に陰極 210 (Cathode) の電位を発光期間よりも高くしておることで、画素への信号書き込み期間における消費電力を低減することができる。

## 【0082】

また、陰極 210 (Cathode) の電位を適宜設定することにより画素の信号書き込み期間において容量素子 207 に信号を書き込む際の駆動トランジスタ 206 のゲートソース間電圧 V<sub>gs</sub> をしきい値電圧 V<sub>th</sub> に設定することができる。つまり、信号線 D<sub>1</sub> ~ D<sub>n</sub> に設定されるアナログ信号電位と、駆動トランジスタ 206 の第 1 端子に電源電位 V<sub>dd</sub> が設定されているときに駆動トランジスタ 206 のゲートソース間電圧 V<sub>gs</sub> がしきい値電圧 V<sub>th</sub> となるゲート電位との電位差をそれぞれの画素 205 の容量素子 207 は保持することができる。このように陰極 210 (Cathode) の電位を設定すると、画素への信号書き込み期間において、発光素子 209 にはほとんど電流を流すことなく信号を書き込むことができる。よって、さらなる消費電力の低減を図ることが可能となる。40

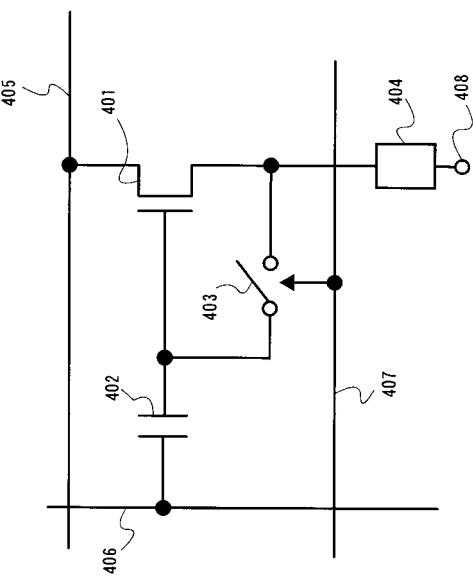

## 【0083】

また、本発明の画素構成は図 1 の構成に限られない。発光素子 104 とは逆向きに電流が流れるときに印加されている電圧が順方向電圧となる発光素子を用いて図 4 のような構成とすることができます。なお、ここでは、一画素のみを図示しているが、表示装置の画素部は実際には行方向と列方向にマトリクスに複数の画素が配置されている。

## 【0084】

画素は駆動トランジスタ 401 と、容量素子 402 と、スイッチ 403 と、発光素子 40

10

20

30

40

50

4と、電位供給線 (Illumination line) 405と、信号線 (Data line) 406と、走査線 (Reset line) 407とを有している。なお、駆動トランジスタ401にはNチャネル型トランジスタを用いている。

#### 【0085】

駆動トランジスタ401の第1端子（ソース端子又はドレイン端子）は電位供給線405と接続され、ゲート端子は容量素子402を介して信号線406と接続され、第2端子（ソース端子又はドレイン端子）は発光素子404の陰極と接続されている。また、駆動トランジスタ401のゲート端子と第2端子（ソース端子又はドレイン端子）はスイッチ403を介して接続されている。よって、スイッチ403がオンしているときには駆動トランジスタ401のゲート端子と第2端子（ソース端子又はドレイン端子）は導通する。そして、スイッチ403がオフすると、駆動トランジスタ401のゲート端子と第2端子（ソース端子又はドレイン端子）は非導通となり、その瞬間の駆動トランジスタ401のゲート端子（若しくは第2端子）と信号線406との電位差（電圧）を容量素子402は保持することができる。なお、発光素子404の陽極（Anode）408はVddの電位が設定されている。なお、Vddとは、高電位側の電源電位であり、画素の発光期間に電位供給線405に設定される電位を低電源電位Vssとすると $V_{dd} > V_{ss}$ を満たす電位である。

10

#### 【0086】

次に、図4に示す画素が、画素部にマトリクスに配置されたi行目j列の画素である場合として、その動作原理を図5に示すタイミングチャートを適宜用いて説明する。

20

#### 【0087】

画素への信号書き込み期間には、j列目の画素には図5に示すように、信号線 (Data line) 406にアナログ信号電位が設定される。このアナログ信号電位がビデオ信号に相当する。そして、i行目の画素へビデオ信号を書き込む際（書き込み時間Ti）には、走査線 (Reset line) 407にHレベルの信号を入力してスイッチ403をオンさせ、且つ電位供給線 (Illumination) 405の電位を低電源電位Vssにし、駆動トランジスタ401の第1端子に低電源電位Vssを設定する。すると、駆動トランジスタ401及び発光素子404に電流が流れ、容量素子402には電荷の蓄積又は放電が行われる。

30

#### 【0088】

このとき、駆動トランジスタ401の第1端子はソース端子となり、第2端子はドレイン端子となっている。そして、スイッチ403がオンになっている状態で駆動トランジスタ401に流れる電流が増加すると、発光素子404に流れる電流も大きくなるため、発光素子404での電圧降下は大きくなり、発光素子404の電極間の電位差は大きくなる。つまり、発光素子404の陰極の電位は電位供給線405の電位に近づく。すると、駆動トランジスタ401のゲート端子の電位も電位供給線405の電位に近づくため、駆動トランジスタ401のゲート端子とソース端子の電位差が小さくなり、駆動トランジスタ401に流れる電流は減少する。一方、発光素子404に流れる電流が小さくなると、発光素子404での電圧降下は小さくなり、発光素子404の電極間の電位差は小さくなる。つまり、発光素子404の陰極の電位は陽極408の電位に近づく。すると、駆動トランジスタ401のゲート端子も陽極408の電位に近づくため、駆動トランジスタ401のゲート端子とソース端子の電位差が大きくなり、駆動トランジスタ401に流れる電流が増加する。こうして、駆動トランジスタ401のゲート端子は駆動トランジスタ401に一定の電流が流れるような電位に落ち着く。そして、そのときの駆動トランジスタ401のゲート端子の電位と信号線406の電位との電位差分の電荷が容量素子402に蓄積される。

40

#### 【0089】

こうしてi行目の画素へビデオ信号の書き込みが終了する。

#### 【0090】

このように駆動トランジスタ401及び発光素子404に流れる電流が一定となり、定常

50

状態となったところで、走査線 (Reset line) 407 の信号を L レベルにし、スイッチ 403 をオフさせる。すると、容量素子 402 は、スイッチ 403 がオフした瞬間の信号線 (Data line) 406 の電位と駆動トランジスタ 401 のゲート端子（若しくはドレイン端子）との電位差  $V_p$  (電圧) を保持する。

#### 【0091】

画素への信号書き込み期間において、 $i$  行目の画素へのビデオ信号の書き込み終了後、 $i$  行目の画素の電位供給線 (Illumination line) 405 に設定する電位を、駆動トランジスタ 401 がオンしたとしても、発光素子 404 に印加される電圧が発光素子 404 のしきい値電圧  $V_{EL}$  以下となるようにする。例えば、電位供給線 405 の電位は、発光素子 404 陽極 408 の電位  $V_{dd}$  と同じ電位、或いはそれ以上にしても良い。なお、この電位を電位供給線 405 に設定するタイミングはスイッチ 403 をオフにするタイミングと同時か、それよりも後にする。

10

#### 【0092】

続いて、 $i+1$  行目の画素の書き込み時間  $T_{i+1}$  となり、同様に  $i+1$  行目の画素にビデオ信号が書き込まれる。そして、全行の画素の書き込み時間が終了し、1 フレーム分のビデオ信号が各画素に書き込まれると、画素への信号書き込み期間は終了する。

#### 【0093】

なお、画素にビデオ信号が書き込まれ、駆動トランジスタ 401 の第 1 端子に接続された電位供給線 405 に電源電位  $V_{ss}$  が設定されているときには、その画素にビデオ信号が書き込まれた際に信号線 406 に設定されたアナログ信号電位を基準にして、信号線 406 の電位の変動に従って駆動トランジスタ 401 のオンオフが制御されるようになる。つまり、信号線 406 の電位が、画素への信号書き込み期間に画素にビデオ信号が書き込まれた際のアナログ信号電位以下のときには駆動トランジスタ 401 はオフし、画素にビデオ信号が書き込まれた際のアナログ信号電位より高くなると駆動トランジスタ 401 はオンする。

20

#### 【0094】

なぜなら、画素にビデオ信号が書き込まれると、容量素子 402 が電位差 ( $V_p$ ) を保持するため、信号線 406 の電位が、画素にビデオ信号が書き込まれた際のアナログ信号電位以下のときには、駆動トランジスタ 401 のゲート端子の電位も、画素にビデオ信号が書き込まれた際のゲート端子の電位以下となり、駆動トランジスタ 401 はオフする。一方、信号線 406 の電位が、画素への信号書き込み期間に画素にビデオ信号が書き込まれた際のアナログ信号電位より高くなると、駆動トランジスタ 401 のゲート端子の電位も、画素にビデオ信号が書き込まれた際のゲート端子の電位より高くなるため駆動トランジスタ 401 はオンする。

30

#### 【0095】

したがって、図 5 に示すように、画素の発光期間には、駆動トランジスタ 401 の第 1 端子が接続された電位供給線 (Illumination line) 405 に  $V_{ss}$  を設定し、走査線 (Reset line) 407 は L レベルにしてスイッチ 403 をオフにした状態で、信号線 (Data line) 406 に三角波電位を設定して駆動トランジスタ 401 のオンオフを制御する。つまり、発光素子 404 の発光・非発光を制御する駆動トランジスタ 401 のオンオフは、書き込み期間に Data line (信号線 406) に設定されたアナログ信号電位が、発光期間に Data line (信号線 406) に入力される三角波電位より高いか低いかで決まり、デジタル的に制御することができる。したがって、駆動トランジスタ 401 の特性のバラツキの影響を受けることが少なく駆動トランジスタ 401 のオンオフを制御することができる。つまり、画素毎の発光のバラツキを改善することができる。

40

#### 【0096】

なお、画素の発光期間において、信号線 (Data line) 406 に設定する電位は周期的に変化する波形のアナログ電位を用いることができる。例えば、図 43 (a)、(b)、(c)、(d)、(e)、(f)、(g) で示したように、波形 4301、波形 43

50

02、波形4303、波形4304、波形4305、波形4306若しくは波形4307、又はこれらを複数連続して設定しても良い。

#### 【0097】

これらの波形を連続して設定することにより、発光時間を1フレーム内で分散させることができる。その結果、フレーム周波数が見かけ上は向上したようになり、画面のちらつきを防止することができる。

#### 【0098】

また、図5に示すように、画素への信号書き込み期間にA node(陽極408)の電位を発光期間に設定するよりも低くしておくことで、画素への信号書き込み期間における消費電力を低減することができる。

10

#### 【0099】

また、本実施の形態に示した画素構成(図1、図2、図4など)は必要とするトランジスタの数や配線の数が少なくてすむため、画素の開口率が向上し、高精細表示が可能となる。

#### 【0100】

また、開口率の高い画素と開口率の低い画素で、同様の光度を得る場合、開口率の高い画素は、開口率が低い画素に比べて発光素子の輝度を低くすることができ、発光素子の信頼性が向上する。特に、発光素子にEL素子を用いている場合、EL素子の信頼性が向上する。

#### 【0101】

また、一般にPチャネル型トランジスタよりもNチャネル型トランジスタの方が移動度 $\mu$ は大きい。よって、Pチャネル型トランジスタとNチャネル型トランジスタとで同じ大きさの電流を流すためにはPチャネル型トランジスタのチャネル幅のチャネル長に対する比の値W/LをNチャネル型トランジスタのW/Lより大きくしなければならない。よって、Nチャネル型トランジスタにすることにより、トランジスタサイズを小さくすることができる。よって、図4のような画素構成とすることで画素の開口率がさらに向上する。

20

#### 【0102】

##### (実施の形態2)

本実施の形態では、実施の形態1とは異なる構成を示す。本実施の形態に示す画素構成は、画素にビデオ信号を書き込む際に設定されるアナログ信号電位と、画素の点灯、非点灯を制御するアナログ電位とを別の配線によって画素に設定する構成としている。

30

#### 【0103】

まず、図56を用いて本発明の表示装置の画素構成について詳細に説明する。画素は駆動トランジスタ5601と、容量素子5602と、第1のスイッチ5603と、発光素子5604と、電源線5605と、第2のスイッチ5606と、第3のスイッチ5607と、走査線(Reset line)5608と、第1の信号線(Data1 line)5609と、第2の信号線(Data2 line)5610とを有している。なお、駆動トランジスタ5601にはPチャネル型トランジスタを用いている。

#### 【0104】

駆動トランジスタ5601の第1端子(ソース端子又はドレイン端子)は電源線5605と接続され、ゲート端子は容量素子5602の一方の電極と接続され、容量素子5602の他方の電極は、第2のスイッチ5606を介して第1の信号線5609と、第3のスイッチ5607を介して第2の信号線5610と接続されている。また、駆動トランジスタ5601のゲート端子と第2端子(ソース端子又はドレイン端子)は第1のスイッチ5603を介して接続されている。なお、発光素子5604の陰極(Cathode)5611はVssの電位が設定されている。なお、Vssとは、電源線5605に設定される電源電位Vddを基準として、Vss < Vddを満たす電位である。例えば、Vss = GND(グラウンド電位)としても良い。

40

#### 【0105】

次に、図56の画素構成の動作原理について図57を用いて簡単に説明する。なお、図5

50

7に示すタイミングチャートは図56に示す複数の画素がマトリクスに配置された表示装置のj列目の画素列のタイミングチャートを示している。また、図57に示すタイミングチャートにおいて、走査線5608(Reset line)の信号がHレベルのときに、第1のスイッチ5603がオンし、Lレベルのときにオフするものとする。

#### 【0106】

図56の画素では、ビデオ信号に相当するアナログ信号電位が第1の信号線5609に設定され、発光時間を制御するアナログ電位が第2の信号線5610に設定される。

#### 【0107】

なお、第2の信号線5310に設定される電位は、実施の形態1の図43(a)、(b)、(c)、(d)、(e)、(f)、(g)で示したように、波形4301、波形4302、波形4303、波形4304、波形4305、波形4306若しくは波形4307、又はこれらを複数連続して設定しても良い。

10

#### 【0108】

これらの波形を連続して設定することにより、発光時間を1フレーム内で分散させることができ。その結果、フレーム周波数が見かけ上は向上したようになり、画面のちらつきを防止することができる。

#### 【0109】

なお、本実施の形態の画素構成を有する表示装置は、画素部の行毎に信号書き込み期間と発光期間が設定される。つまり、画素部全体としては書き込み期間と発光期間が同時に進行する。なお、各行毎の画素への信号書き込み期間を書き込み時間という。

20

#### 【0110】

ここで、i行目の画素の信号書き込み時間について説明する。図5に示すTi期間がi行目の画素の信号書き込み時間を示している。そして、Ti期間以外の間はi行目の画素は発光期間となる。

#### 【0111】

まず、Ti期間には第2のスイッチ5606をオンにし、第3のスイッチ5607をオフにする。そして、走査線5608(Reset line)は、期間TiにはHレベルの信号を入力し、第1のスイッチ5603をオンにする。また、i行目の画素の駆動トランジスタ5601の第1端子(ソース端子又はドレイン端子)には電源線5605からの電源電位Vddが設定され、容量素子5602、駆動トランジスタ5601及び発光素子5604に電流が流れる。そして、容量素子5602では電荷の蓄積若しくは放電が行われる。つまり、容量素子5602にもともと蓄積されていた電荷と第1の信号線5609(Data1 line)に設定された電位との関係で電荷の蓄積か放電のどちらかが起きる。そして、走査線5608(Reset line)の信号がHレベルからLレベルに立ち下がると、第1のスイッチ5603がオフする。第1のスイッチ5603がオフすると、その瞬間の駆動トランジスタ5601のゲート端子の電位と第1の信号線5609の電位との電位差を容量素子5602は保持する。

30

#### 【0112】

こうして、i行目j列の画素に第1の信号線5609(Data1 line)からビデオ信号が書き込まれる。なお、このとき、各画素列毎にそれぞれの第1の信号線5609(Data1 line)からそれぞれのアナログ信号電位が入力され、各列のi行目の画素にビデオ信号が書き込まれる。

40

#### 【0113】

こうして、i行目の画素の信号書き込み時間であるTi期間が終了すると、i+1行目の画素の信号書き込み時間であるTi+1期間が始まり、i行目の画素は発光期間になる。

#### 【0114】

i行目の画素の発光期間にはi行目の画素の第1のスイッチ5603をオフにしたまま第2のスイッチ5606をオフにし、第3のスイッチ5607をオンにする。

#### 【0115】

なお、図57に示すように第2の信号線5610(Data2 line)には三角波電

50

位が設定されている。 $i$  行目  $j$  列の画素は第 2 の信号線 5610 (Data2\_line) が、 $i$  行目の画素の信号書き込み時間である  $T_i$  期間に第 1 の信号線 5609 (Data1\_line) に設定されたアナログ信号電位より高い電位であるときには発光素子 5604 は非発光の状態を維持し、第 2 の信号線 5610 (Data2\_line) が、 $i$  行目の画素の信号書き込み時間である  $T_i$  期間に第 1 の信号線 5609 (Data1\_line) に設定されたアナログ信号電位より低い電位の間 ( $T_a$ ) は発光素子 5604 は発光する。よって、それぞれの画素の書き込み時間にビデオ信号が書き込まれた際のアナログ信号電位にしたがって発光素子 5604 の発光時間が設定される。こうして、アナログ時間階調表示が可能となる。

## 【0116】

10

このように本実施の形態の画素構成を有する表示装置は、画素行毎に順次、信号書き込み期間となり、信号書き込み期間が終了すると画素行毎に発光期間に移る。よって、本実施の形態のように線順次でビデオ信号が画素に書き込まれる場合には、書き込み期間は一画素分の書き込み時間で良いため、発光時間を長くすることができる。つまり、デューティー比 (1 フレーム期間における発光期間の割合) が高いので、発光素子の瞬間輝度を低くすることができます。よって、発光素子の信頼性を向上することができる。

## 【0117】

また、一行毎の画素の書き込み時間を長くすることができることから、第 1 の信号線 5609 (Data1\_line) にアナログ信号電位を入力する信号線駆動回路の周波数を低くすることができます。よって、消費電力を小さくすることができます。

20

## 【0118】

なお、発光素子 5604 の発光・非発光を制御する駆動トランジスタ 5601 のオンオフは、上述したように、書き込み期間に第 1 の信号線 5609 (Data1\_line) に設定されたアナログ信号電位が、発光期間において、第 2 の信号線 5610 (Data2\_line) に入力される三角波電位より高いか低いかで決まり、デジタル的に制御することができます。よって、駆動トランジスタ 5601 の特性のバラツキの影響を受けることが少なく駆動トランジスタ 5601 のオンオフを制御することができる。つまり、画素毎の発光のバラツキを改善することができる。

## 【0119】

30

また、図 56 では駆動トランジスタ 5601 に P チャネル型のトランジスタを用いているが、N チャネル型のトランジスタを適用することもできる。その場合には、陰極 5611 から電源線 5605 に流れる電流の向きは逆になるようになる。つまり、発光素子 5604 には順方向電圧が逆になるようになる。本実施の形態の画素構成には N チャネル型のトランジスタを、発光素子の発光・非発光を制御する駆動トランジスタに用いることができる。一般に P チャネル型トランジスタよりも N チャネル型トランジスタの方が移動度  $\mu$  が大きい。よって、同じ電流を流すとすると、トランジスタサイズを小さくすることができる。よって、画素の開口率が向上し、高詳細表示や消費電力の低減された表示装置を提供することができる。

## 【0120】

40

なお、本実施の形態において、発光素子を駆動する駆動トランジスタのソース端子及びドレイン端子、並びに発光素子の陽極及び陰極とは、発光素子への順方向の電圧が印加されているときの端子及び電極をいう。

## 【0121】

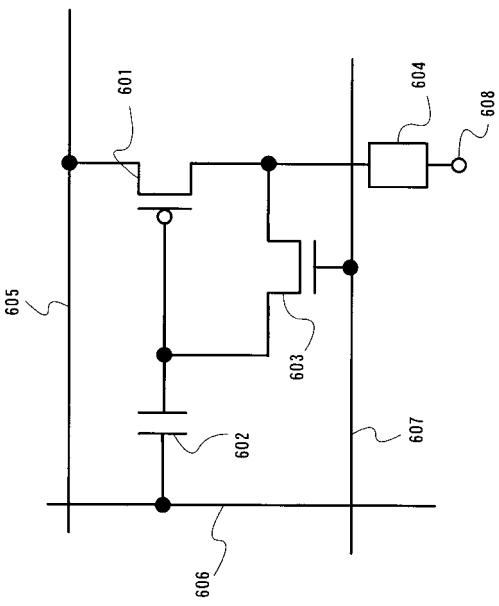

(実施の形態 3)

本実施の形態では、実施の形態 1 で示した画素のスイッチにトランジスタを適用した場合について説明する。

## 【0122】

図 6 に示す画素は図 1 に示した画素のスイッチ 103 に N チャネル型トランジスタを適用した構成である。画素は駆動トランジスタ 601 と、容量素子 602 と、スイッチング用トランジスタ 603 と、発光素子 604 と、電位供給線 (Illumination 1

50

ine) 605と、信号線(Data line) 606と、走査線(Reset line) 607とを有している。なお、駆動トランジスタ601にはPチャネル型トランジスタ、スイッチング用トランジスタ603にはNチャネル型トランジスタを用いている。

#### 【0123】

駆動トランジスタ601の第1端子(ソース端子又はドレイン端子)は電位供給線605と接続され、ゲート端子は容量素子602を介して信号線606と接続され、第2端子(ソース端子又はドレイン端子)は発光素子604の陽極(画素電極)と接続されている。また、駆動トランジスタ601のゲート端子はスイッチング用トランジスタ603の第1の端子(ソース端子又はドレイン端子)と、駆動トランジスタ601の第2端子(ソース端子又はドレイン端子)はスイッチング用トランジスタ603の第2の端子(ソース端子又はドレイン端子)と接続されている。よって、走査線607にHレベルの信号を入力し、スイッチング用トランジスタ603がオンしているときには駆動トランジスタ601のゲート端子と第2端子(ソース端子又はドレイン端子)は導通する。そして、走査線607にLレベルの信号を入力し、スイッチング用トランジスタ603がオフすると、駆動トランジスタ601のゲート端子と第2端子(ソース端子又はドレイン端子)は非導通となり、その瞬間の駆動トランジスタ601のゲート端子(若しくは第2端子)と信号線606との電位差(電圧)を容量素子602は保持することができる。なお、発光素子604の陰極(Cathode)608はVssの電位が設定されている。なお、Vssとは、画素の発光期間に電位供給線605に設定される電源電位Vddを基準として、 $V_{ss} < V_{dd}$ を満たす電位である。例えば、 $V_{ss} = GND$ (グラウンド電位)としても良い。

#### 【0124】

よって、スイッチング用トランジスタ603は図1の画素のスイッチ103と同様の機能を果たす。また、駆動トランジスタ601、容量素子602、スイッチング用トランジスタ603、発光素子604、電位供給線(Illumination line)605、信号線(Data line)606、走査線(Reset line)607は、それぞれ図1の画素の駆動トランジスタ101、容量素子102、スイッチ103、発光素子104、電位供給線(Illumination line)105、信号線(Data line)106、走査線(Reset line)107に相当する。よって、図6の画素の動作は図1の画素の動作と同様であるので、ここでは説明を省略する。

#### 【0125】

なお、容量素子602は、書き込み期間において保持した電位差を、発光期間中保持し続けなければならない。そのため、スイッチング用トランジスタ603のリーク電流(リーク電流とは、トランジスタがオフしているときにソースドレイン間に流れてしまうオフ電流、及びゲートとソース又はドレイン間に流れてしまうゲートリーク電流をいう)や駆動トランジスタ601のゲートリーク電流を低減しなければならない。

#### 【0126】

よって、スイッチング用トランジスタ603としては、図6に示すようにNチャネル型のトランジスタを用いると良い。Nチャネル型トランジスタは、低濃度不純物領域(Lightly Doped Drains: LDD領域ともいう)を容易に形成することができ、オフ電流の低減を図ることができるからである。

#### 【0127】

また、駆動トランジスタ601及びスイッチング用トランジスタ603のゲート絶縁膜の材料や膜厚を適宜選択し、ゲートリーク電流を低減させることができ望ましい。さらに、ゲート電極をマルチゲート構造にすることによっても、ゲートリーク電流を低減することができる。

#### 【0128】

また、図1に示した画素のスイッチ103にスイッチング用トランジスタとしてPチャネル型トランジスタを適用することもできる。その場合にはスイッチング用トランジスタのオンオフを制御する信号のHレベルとLレベルはNチャネル型トランジスタを適用した場合とは反転した動作となる。つまり、Lレベルのときにスイッチング用トランジスタはオ

10

20

30

40

50

ンし、H レベルのときにオフする。

#### 【 0 1 2 9 】

また、図 1 示した画素のスイッチ 103 にスイッチング用トランジスタとして P チャネル型のトランジスタを適用することで、画素部全体若しくは周辺駆動回路まで含めて P チャネル型のトランジスタのみで構成される回路を提供することができるため、工程数の削減された低コストの単極性の表示パネルを提供することができる。

#### 【 0 1 3 0 】

また、図 1 の画素のスイッチ 103 にスイッチング用トランジスタとして P チャネル型トランジスタを適用すると、図 1 に示す、電位供給線 105 に相当する配線を省略することができる。そのような構成について図 8 を用いて説明する。

10

#### 【 0 1 3 1 】

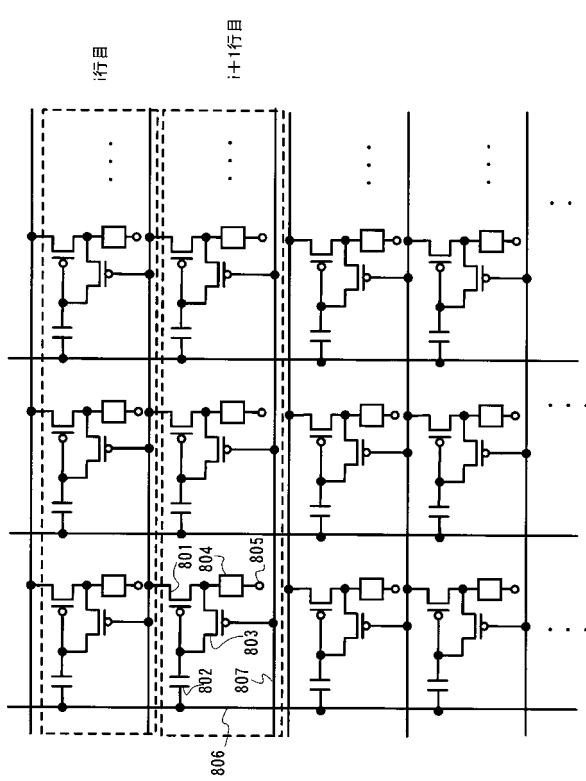

画素は駆動トランジスタ 801 と、容量素子 802 と、スイッチング用トランジスタ 803 と、発光素子 804 と、信号線 (Data line) 806 と、走査線 (Reset line) 807 とを有している。なお、駆動トランジスタ 801 及びスイッチング用トランジスタ 803 には P チャネル型トランジスタを用いている。

#### 【 0 1 3 2 】

i + 1 行目の画素の駆動トランジスタ 801 の第 1 端子 (ソース端子又はドレイン端子) は i 行目の画素の走査線 807 と接続され、ゲート端子は容量素子 802 を介して信号線 806 と接続され、第 2 端子 (ソース端子又はドレイン端子) は発光素子 804 の陽極 (画素電極) と接続されている。また、駆動トランジスタ 801 のゲート端子はスイッチング用トランジスタ 803 の第 1 の端子 (ソース端子又はドレイン端子) と、駆動トランジスタ 801 の第 2 端子 (ソース端子又はドレイン端子) はスイッチング用トランジスタ 803 の第 2 端子 (ソース端子又はドレイン端子) と接続されている。よって、走査線 807 に L レベルの信号が入力され、スイッチング用トランジスタ 803 がオンしているときには駆動トランジスタ 801 のゲート端子と第 2 端子 (ソース端子又はドレイン端子) は導通する。そして、走査線 807 に H レベルの信号が入力され、スイッチング用トランジスタ 803 がオフすると、駆動トランジスタ 801 のゲート端子と第 2 端子 (ソース端子又はドレイン端子) は非導通となり、その瞬間の駆動トランジスタ 801 のゲート端子 (若しくはドレイン端子) と信号線 806 との電位差 (電圧) を容量素子 802 は保持することができる。なお、発光素子 804 の陰極 (Cathode) 805 は Vss の電位が設定されている。なお、Vss とは、画素の発光期間に駆動トランジスタ 801 の第 1 端子 (ソース端子又はドレイン端子) に設定する電源電位 Vdd を基準として、Vss < Vdd を満たす電位である。例えば、Vss = GND (グラウンド電位) としても良い。

20

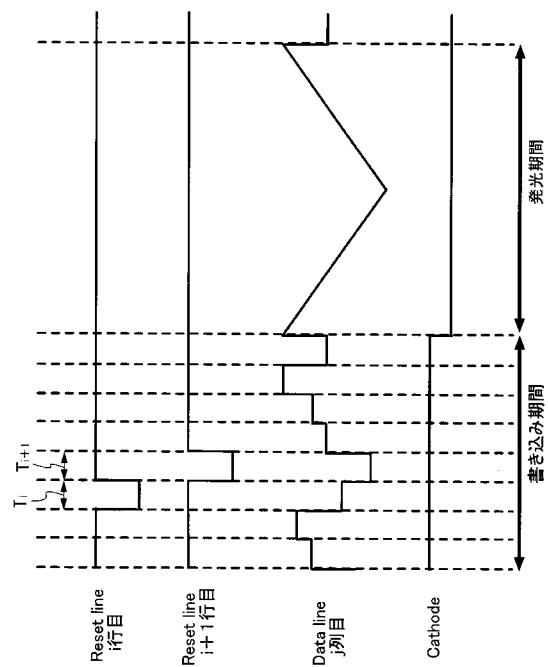

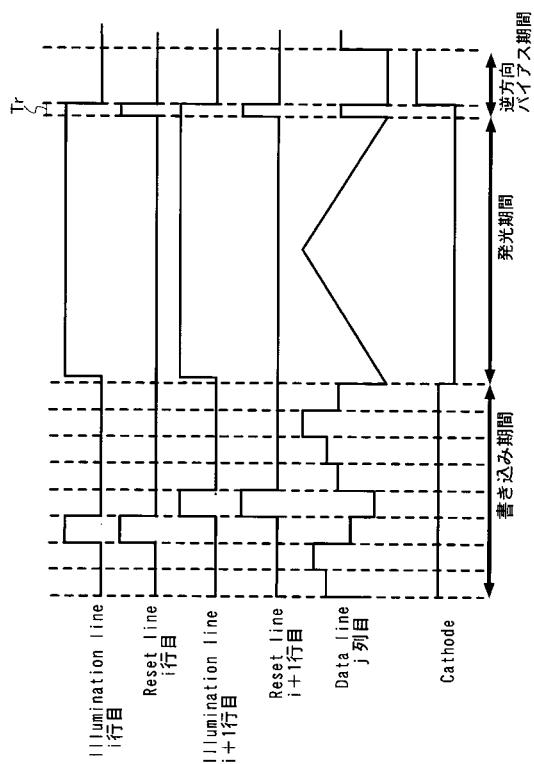

#### 【 0 1 3 3 】

図 8 の画素構成を有する表示装置のタイミングチャートを図 9 に示す。それぞれの画素の行の走査線 807 は書き込み時間に H レベルから L レベルに立ち下がり、書き込み時間が終わると L レベルから H レベルに立ち上がる。i 行目の画素は期間 Ti、i + 1 行目の画素は期間 Ti + 1 がそれぞれの書き込み時間であり、この期間の走査線 807 の信号は L レベルである。

30

#### 【 0 1 3 4 】

よって、発光期間において走査線 807 の信号は H レベルであるので、走査線 807 に信号を出力する回路の電流供給能力を高くすれば発光素子 804 に印加する電圧を設定する電位供給線として走査線 807 を用いることができる。なお、図 8 の構成では電位供給線として隣の行の走査線 807 を用いているが、他の行の走査線 807 であればこれに限られない。

40

#### 【 0 1 3 5 】

なお、図 8 の構成では、書き込み期間において、他の行の画素の書き込み時間の間も発光素子 804 が発光してしまうことがあるため、Cathode (陰極 805) の電位を発光期間より高めに設定すると良い。より好ましくは実施の形態 1 で説明したように、画素へ信号を書き込む際、駆動トランジスタ 801 のゲートソース間電圧 Vgs がしきい値電

50

圧となるようにすると良い。つまり、このとき発光素子 804 に印加される電圧が発光素子 804 の順方向しきい値電圧  $V_{E_L}$  以下となるように Cathode (陰極 805) の電位を設定するとよい。

#### 【0136】

図 8 のような構成とすれば、配線の数を減らすことができ、さらなる開口率の向上を図ることができる。

#### 【0137】

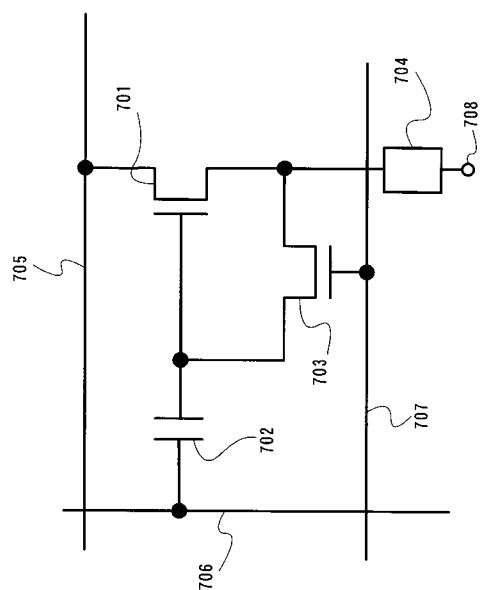

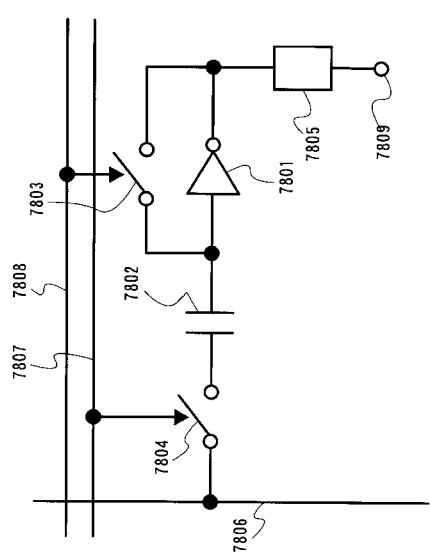

また、図 4 の画素構成のスイッチ 403 に N チャネル型トランジスタを適用した構成を図 7 に示す。

#### 【0138】

図 7 に示す画素は駆動トランジスタ 701 と、容量素子 702 と、スイッチング用トランジスタ 703 と、発光素子 704 と、電位供給線 (Illumination line) 705 と、信号線 (Data line) 706 と、走査線 (Reset line) 707 を有している。なお、駆動トランジスタ 701 及びスイッチング用トランジスタ 703 には N チャネル型トランジスタを用いている。

10

#### 【0139】

駆動トランジスタ 701 の第 1 端子 (ソース端子又はドレイン端子) は電位供給線 705 と接続され、ゲート端子は容量素子 702 を介して信号線 706 と接続され、第 2 端子 (ソース端子又はドレイン端子) は発光素子 704 の陰極と接続されている。また、駆動トランジスタ 701 のゲート端子はスイッチング用トランジスタ 703 の第 1 の端子 (ソース端子又はドレイン端子) と、駆動トランジスタ 701 の第 2 端子 (ソース端子又はドレイン端子) はスイッチング用トランジスタ 703 の第 2 の端子 (ソース端子又はドレイン端子) と接続されている。よって、走査線 707 に H レベルの信号を入力し、スイッチング用トランジスタ 703 がオンしているときには駆動トランジスタ 701 のゲート端子と第 2 端子 (ソース端子又はドレイン端子) は導通する。そして、走査線 707 に L レベルの信号を入力し、スイッチング用トランジスタ 703 がオフすると、駆動トランジスタ 701 のゲート端子と第 2 端子 (ソース端子又はドレイン端子) は非導通となり、その瞬間の駆動トランジスタ 701 のゲート端子 (若しくは第 2 端子) と信号線 706 との電位差 (電圧) を容量素子 702 は保持することができる。なお、発光素子 704 の陽極 (Anode) 708 は  $V_{dd}$  の電位が設定されている。なお、 $V_{dd}$  とは、画素の発光期間に電位供給線 705 に設定される低電源電位  $V_{ss}$  を基準として、 $V_{dd} > V_{ss}$  を満たす電位である。

20

30

40

#### 【0140】

よって、スイッチング用トランジスタ 703 は図 4 の画素のスイッチ 403 と同様の機能を果たす。また、駆動トランジスタ 701、容量素子 702、スイッチング用トランジスタ 703、発光素子 704、電位供給線 (Illumination line) 705、信号線 (Data line) 706、走査線 (Reset line) 707 は、それぞれ図 4 の画素の駆動トランジスタ 401、容量素子 402、スイッチ 403、発光素子 404、電位供給線 (Illumination line) 405、信号線 (Data line) 406、走査線 (Reset line) 407 に相当する。よって、図 7 の画素の動作は図 4 の画素の動作と同様であるので、ここでは説明を省略する。

#### 【0141】

なお、容量素子 702 は、書き込み期間において保持した電位差を、発光期間中保持し続けなければならない。そのため、スイッチング用トランジスタ 703 のリーク電流 (リーク電流とは、トランジスタがオフしているときにソースドレイン間に流れてしまうオフ電流、及びゲートとソース又はドレイン間に流れてしまうゲートリーク電流をいう) や駆動トランジスタ 701 のゲートリーク電流を低減しなければならない。

#### 【0142】

よって、スイッチング用トランジスタ 703 としては、図 7 に示すように N チャネル型のトランジスタを用いると良い。N チャネル型トランジスタは、低濃度不純物領域 (Lig

50

h t l y D o p e d D r a i n s : L D D 領域ともいう) を容易に形成することができ、オフ電流の低減を図ることができるからである。

#### 【 0 1 4 3 】

また、駆動トランジスタ 701 及びスイッチング用トランジスタ 703 のゲート絶縁膜の材料や膜厚を適宜選択し、ゲートリーク電流を低減させることができが望ましい。さらに、ゲート電極をマルチゲート構造にすることによっても、ゲートリーク電流を低減することができる。

#### 【 0 1 4 4 】

なお、一般に P チャネル型トランジスタよりも N チャネル型トランジスタの方が移動度  $\mu$  が大きい。よって、同じ電流を流すとすると、トランジスタサイズを小さくすることができる。よって、図 7 のような画素構成とすることで画素の開口率が向上する。10

#### 【 0 1 4 5 】

また、図 7 のような構成とすれば、画素部全体若しくは周辺駆動回路まで含めて N チャネル型のトランジスタのみで構成される回路を提供することができるため、工程数の削減された低コストの単極性の表示パネルを提供することができる。

#### 【 0 1 4 6 】

また、表示パネルの有する回路に用いる薄膜トランジスタを N チャネル型のトランジスタのみで構成することができることから、そのトランジスタの半導体層にアモルファス半導体やセミアモルファス半導体(若しくは微結晶半導体ともいう)などの非晶質半導体を用いることができる。例えば、アモルファス半導体として、アモルファスシリコン(a-Si : H)が挙げられる。よって、さらなる工程数の削減を図ることが可能である。20

#### 【 0 1 4 7 】

また、図 4 の画素のスイッチ 403 にスイッチング用トランジスタとして N チャネル型トランジスタを適用すると、図 4 に示す、電位供給線 405 に相当する配線を省略することができる。そのような構成について図 10 を用いて説明する。

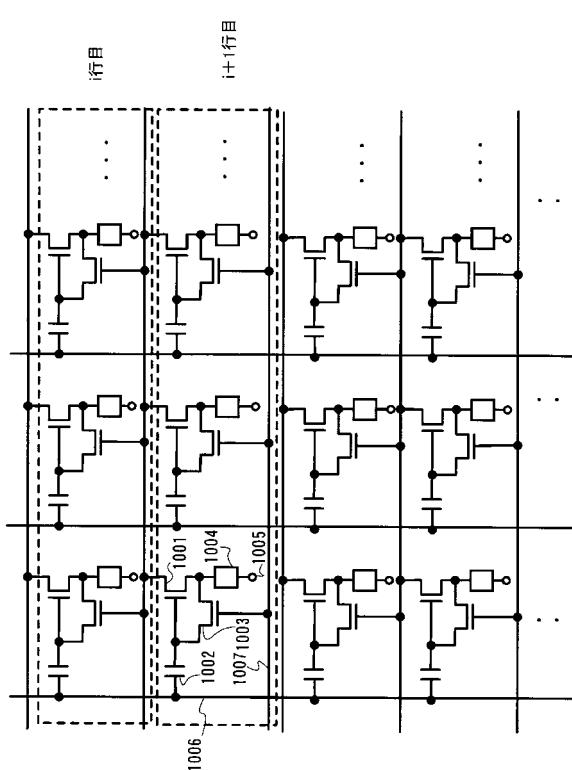

#### 【 0 1 4 8 】

画素は駆動トランジスタ 1001 と、容量素子 1002 と、スイッチング用トランジスタ 1003 と、発光素子 1004 と、信号線(Data line) 1006 と、走査線(Reset line) 1007 とを有している。なお、駆動トランジスタ 1001 及びスイッチング用トランジスタ 1003 には N チャネル型トランジスタを用いている。30

#### 【 0 1 4 9 】

$i + 1$  行目の画素の駆動トランジスタ 1001 の第 1 端子(ソース端子又はドレイン端子)は  $i$  行目の画素の走査線 1007 と接続され、ゲート端子は容量素子 1002 を介して信号線 1006 と接続され、第 2 端子(ソース端子又はドレイン端子)は発光素子 1004 の陰極と接続されている。また、駆動トランジスタ 1001 のゲート端子はスイッチング用トランジスタ 1003 の第 1 の端子(ソース端子又はドレイン端子)と、駆動トランジスタ 1001 の第 2 端子(ソース端子又はドレイン端子)はスイッチング用トランジスタ 1003 の第 2 端子(ソース端子又はドレイン端子)と接続されている。よって、走査線 1003 に H レベルの信号が入力され、スイッチング用トランジスタ 1003 がオンしているときには駆動トランジスタ 1001 のゲート端子と第 2 端子(ソース端子又はドレイン端子)は導通する。そして、走査線 1003 に L レベルの信号が入力され、スイッチング用トランジスタ 1003 がオフすると、駆動トランジスタ 1001 のゲート端子と第 2 端子(ソース端子又はドレイン端子)は非導通となり、その瞬間の駆動トランジスタ 1001 のゲート端子(若しくはドレイン端子)と信号線 1006 との電位差(電圧)を容量素子 1002 は保持することができる。なお、発光素子 1004 の陽極(Anode) 1005 は Vdd の電位が設定されている。なお、Vdd とは、画素の発光期間に駆動トランジスタ 1001 の第 1 端子(ソース端子又はドレイン端子)に設定する低電源電位 Vss を基準として、Vdd > Vss を満たす電位である。40

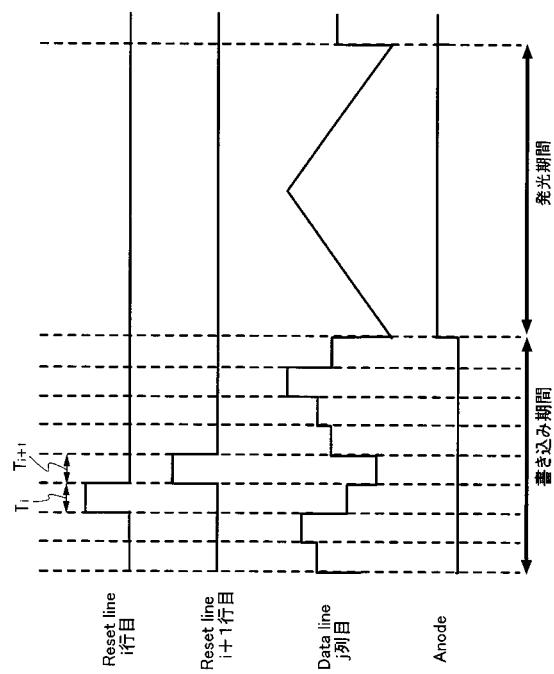

#### 【 0 1 5 0 】

図 10 の画素構成を有する表示装置のタイミングチャートを図 11 に示す。それぞれの画

素の行の走査線 1007 は書き込み時間に L レベルから H レベルに立ち上がり、書き込み時間が終わると H レベルから L レベルに立ち下がる。i 行目の画素は期間  $T_i$ 、 $i + 1$  行目の画素は期間  $T_{i+1}$  がそれぞれの書き込み時間であり、この期間の走査線 1007 の信号は H レベルである。

#### 【0151】

よって、発光期間において走査線 1007 の信号は L レベルであるので、走査線 1007 に信号を出力する回路の電流供給能力を高くすれば発光素子 1004 に印加する電圧を設定する電位供給線として走査線 1007 を用いることができる。なお、図 10 の構成では電位供給線として隣の行の走査線 1007 を用いているが、他の行の走査線 1007 であればこれに限られない。

10

#### 【0152】

なお、図 10 の構成では、書き込み期間において、他の行の画素の書き込み時間の間も発光素子 1004 が発光してしまうことがあるため、陽極 1005 (Anode) の電位を発光期間より低めに設定すると良い。より好ましくは実施の形態 1 で説明したように、画素へ信号を書き込む際、駆動トランジスタ 1001 のゲートソース間電圧  $V_{gs}$  がしきい値電圧となるようにすると良い。つまり、このとき発光素子 1004 に印加される電圧が発光素子 1004 の順方向しきい値電圧  $V_{EL}$  以下となるように陽極 1005 (Anode) の電位を設定するとよい。

#### 【0153】

図 10 のような構成とすれば、配線の数を減らすことができ、さらなる開口率の上昇を図ることができる。

20

#### 【0154】

なお、もちろん、図 4 のスイッチ 403 として P チャネル型のトランジスタを適用することもできる。

#### 【0155】

##### (実施の形態 4)

本実施の形態では、実施の形態 1 で示した画素構成において、さらに発光素子の信頼性を向上させる駆動方法と、実施の形態 1 で示した画素構成よりもさらに発光素子の信頼性の向上する画素構成及びその駆動方法について説明する。

30

#### 【0156】

まず、実施の形態 1 の図 1 で示した画素構成を用いて、本実施の形態による駆動方法を説明する。

#### 【0157】

本実施の形態においては、1 フレーム期間に順方向バイアス期間（書き込み期間及び発光期間）と逆方向バイアス期間とを有する。順方向バイアス期間の書き込み期間及び発光期間においては、実施の形態 1 で示した動作と同様であるので説明は省略する。

#### 【0158】

逆方向バイアス期間には、図 51 に示すように発光期間に電位供給線 (Illumination line) 105 に設定する電位  $V_{dd}$  と陰極 (Cathode) 108 に設定する電位  $V_{ss}$  を逆にする。つまり、逆方向バイアス期間には電位供給線 (Illumination line) 105 に低電源電位  $V_{ss}$  を設定し、陰極 (Cathode) 108 には電源電位  $V_{dd}$  を設定する。そして、スイッチ 103 をオフにする。すると、駆動トランジスタ 101 の第 1 端子及び第 2 端子はソース端子とドレイン端子が順方向バイアス期間とは逆になる。つまり、順方向バイアス期間のときには、駆動トランジスタ 101 の第 1 端子はソース端子、第 2 端子はドレイン端子として機能するが、逆方向バイアス期間のときには、駆動トランジスタ 101 の第 1 端子がドレイン端子、第 2 端子がソース端子として機能する。また、発光素子 105 の陽極又は陰極として機能していた電極も逆になる。また、このとき、信号線 106 には駆動トランジスタ 101 が十分にオンするように電位を設定する。

40

#### 【0159】

50

なお、逆方向バイアス期間の初めに駆動トランジスタ101のゲート端子の電位を設定してもよい。つまり、図52に示すように、逆方向バイアス期間の初めに、ゲート電位設定期間 $T_r$ を設ける。このとき、走査線107(Reset line)にHレベルの信号を設定し、スイッチ103をオンにする。そして、電位供給線105(Illumination line)の電位はHレベル(Vdd)に設定し、信号線106にはHレベル(ここでHレベルとは三角波電位の最低電位より高い電位を示し、より好ましくは三角波電位の中間電位より高い電位である)の電位を設定しておく。すると、駆動トランジスタ101のオンオフを制御するのに必要なゲート端子の電位と信号線106のHレベルの電位との電位差が容量素子102に保持される。

## 【0160】

逆方向バイアス期間において、ゲート電位設定期間 $T_r$ が終了すると、走査線107の電位がLレベルになり、スイッチ103はオフする。そして、信号線106の電位がHレベルからLレベル(ここでLレベルとは信号線106に設定するHレベルの電位より低い電位であり、より好ましくは三角波電位の中間の電位より低い電位である)にする。すると、容量素子102が電位差を保持したまま、信号線106の電位が低くなる。よって、逆方向バイアス期間における信号線106に設定するHレベルとLレベルの信号の電位を適宜設定することにより、駆動トランジスタ101を十分にオンすることができる。

## 【0161】

したがって、駆動トランジスタ101がオンし、発光素子104には、順方向バイアス期間とは逆の電圧を印加することができる。

## 【0162】

このように、逆方向バイアス期間において、順方向バイアス期間とは逆方向の電圧を発光素子104に印加しても、正常な発光素子104には電流は流れない(若しくは流れたとしても微少な電流である)。一方、発光素子104に短絡箇所が有る場合には、その短絡箇所に電流が流れる。そして、短絡箇所を絶縁化する。よって、逆方向バイアス期間には、この短絡箇所を絶縁するのに十分な電流を流すように逆方向の電圧を発光素子104に印加する。

## 【0163】

よって、上述したように、逆方向バイアス期間において、電位供給線105に設定する電位はVssに限られない。また、陰極108に設定する電位もVddに限られない。つまり、逆方向バイアス期間に発光素子104の短絡箇所を絶縁するのに十分な電流を流せねば良い。

## 【0164】

このように、発光素子104の短絡箇所を絶縁することにより、画素の表示不良を改善することができる。また、発光素子104の寿命を延ばすことが可能となる。

## 【0165】

また、実施の形態1の図1とは異なる画素構成により、発光素子の信頼性を高くする画素について図53を用いて説明する。なお、本構成においても順方向バイアス期間(書き込み期間及び発光期間)と逆方向バイアス期間を有する。

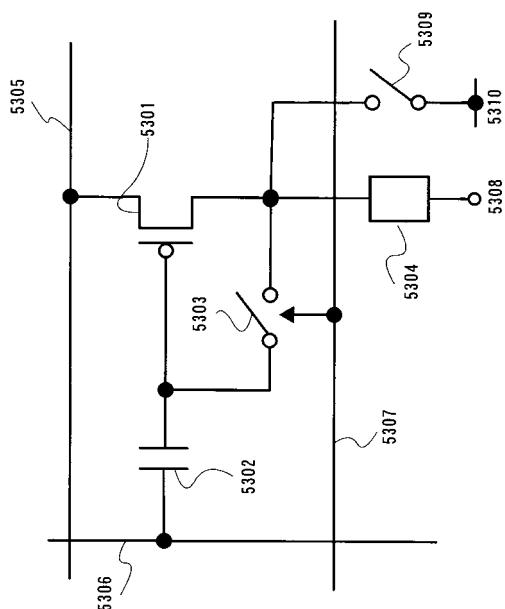

## 【0166】

画素は駆動トランジスタ5301と、容量素子5302と、スイッチ5303と、発光素子5304と、電位供給線(Illumination line)5305と、信号線(Data line)5306と、走査線(Reset line)5307と、逆バイアス用スイッチ5309と、配線5310とを有している。なお、駆動トランジスタ5301にはPチャネル型トランジスタを用いている。

## 【0167】

駆動トランジスタ5301の第1端子(ソース端子又はドレイン端子)は電位供給線5305と接続され、ゲート端子は容量素子5302を介して信号線5306と接続され、第2端子(ソース端子又はドレイン端子)は発光素子5304の陽極(画素電極)と接続されている。また、駆動トランジスタ5301のゲート端子と第2端子(ソース端子又はド

10

20

30

40

50

レイン端子)はスイッチ5303を介して接続されている。よって、スイッチ5303がオンしているときには駆動トランジスタ5301のゲート端子と第2端子(ソース端子又はドレイン端子)は導通する。そして、スイッチ5303がオフすると、駆動トランジスタ5301のゲート端子と第2端子(ソース端子又はドレイン端子)は非導通となり、その瞬間の駆動トランジスタ5301のゲート端子(若しくは第2端子)と信号線5306との電位差(電圧)を容量素子5302は保持することができる。なお、発光素子5304の陰極(Cathode)5308はVssの電位が設定されている。なお、Vssとは、画素の発光期間に電位供給線5305に設定される電源電位Vddを基準として、Vss < Vddを満たす電位である。例えば、Vss = GND(グラウンド電位)としても良い。また、発光素子5304の陽極は逆バイアス用スイッチ5309を介してVss3の電位が設定された配線5310と接続されている。なお、Vss3はVss3 < Vssを満たす電位であり、逆方向バイアス期間に逆バイアス用スイッチ5309がオンすると発光素子5304には、順方向バイアス期間とは逆の方向に電圧が印加される。よって、このとき、発光素子5304の陽極と陰極の電位の高低が逆になる。

10

## 【0168】

次に、図53の画素構成の動作原理について詳しく説明する。

## 【0169】

画素への信号書き込み期間には、逆バイアス用スイッチ5309はオフにし、信号線5306にはアナログ信号電位が設定される。このアナログ信号電位がビデオ信号に相当する。そして、画素へビデオ信号を書き込む際には、走査線5307に信号を入力してスイッチ5303をオンさせ、且つ電位供給線5305の電位を電源電位Vddにし、駆動トランジスタ5301の第1端子に電源電位Vddを設定する。すると、駆動トランジスタ5301及び発光素子5304に電流が流れ、容量素子5302には電荷の蓄積又は放電が行われる。

20

## 【0170】

なお、このとき逆バイアス用スイッチ5309をオンにしてもよい。すると、書き込みの際に発光素子5304へ電流を流さなくすることができる。

## 【0171】

このとき、駆動トランジスタ5301の第1端子はソース端子となり、第2端子はドレイン端子となっている。そして、スイッチ5303がオンになっている状態で駆動トランジスタ5301に流れる電流が増加すると、発光素子5304に流れる電流も大きくなるため、発光素子5304での電圧降下は大きくなり、発光素子5304の電極間の電位差は大きくなる。つまり、発光素子5304の陽極の電位は電位供給線5305の電位に近づく。すると、駆動トランジスタ5301のゲート端子の電位も電位供給線5305の電位に近づくため、駆動トランジスタ5301のゲート端子とソース端子の電位差が小さくなり、駆動トランジスタ5301に流れる電流は減少する。一方、発光素子5304に流れる電流が小さくなると、発光素子5304での電圧降下は小さくなり、発光素子5304の電極間の電位差は小さくなる。つまり、発光素子5304の陽極の電位は陰極5308の電位に近づく。すると、駆動トランジスタ5301のゲート端子も陰極5308の電位に近づくため、駆動トランジスタ5301のゲート端子とソース端子の電位差が大きくなり、駆動トランジスタ5301に流れる電流が増加する。こうして、駆動トランジスタ5301のゲート端子は駆動トランジスタ5301に一定の電流が流れのような電位に落ち着く。そして、そのときの駆動トランジスタ5301のゲート端子の電位と信号線5306の電位との電位差分の電荷が容量素子5302に蓄積される。

30

## 【0172】

こうしてこの画素へビデオ信号の書き込みが終了する。

## 【0173】

このように駆動トランジスタ5301及び発光素子5304に流れる電流が一定となり、定常状態となったところで、スイッチ5303をオフさせる。すると、容量素子5302は、スイッチ5303がオフした瞬間の信号線5306の電位と駆動トランジスタ530

40

50

1のゲート端子（若しくはドレイン端子）との電位差 $V_p$ （電圧）を保持する。

【0174】

画素へのビデオ信号の書き込み終了後、電位供給線5305に設定する電位を、駆動トランジスタ5301がオンしたとしても、発光素子5304に印加される電圧が発光素子5304のしきい値電圧 $V_{EL}$ 以下となるようになる。例えば、電位供給線5305の電位は、発光素子5304の陰極5308の電位 $V_{SS}$ と同じ電位、或いはそれ以下にしても良い。なお、この電位を電位供給線5305に設定するタイミングはスイッチ5303をオフにするタイミングと同時か、それよりも後にする。

【0175】

なお、画素にビデオ信号が書き込まれ、駆動トランジスタ5301の第1端子に接続された電位供給線5305に電源電位 $V_{dd}$ が設定されているときには、その画素にビデオ信号が書き込まれた際に信号線5306に設定されたアナログ信号電位を基準にして、信号線5306の電位の変動に従って駆動トランジスタ5301のオンオフが制御されるようになる。つまり、信号線5306の電位が、画素への信号書き込み期間に画素にビデオ信号が書き込まれた際のアナログ信号電位以上のときには駆動トランジスタ5301はオフし、画素にビデオ信号が書き込まれた際のアナログ信号電位より低くなると駆動トランジスタ5301はオンする。

【0176】

なぜなら、画素にビデオ信号が書き込まれると、容量素子5302が電位差（ $V_p$ ）を保持するため、信号線5306の電位が、画素にビデオ信号が書き込まれた際のアナログ信号電位以上のときには、駆動トランジスタ5301のゲート端子の電位も、画素にビデオ信号が書き込まれた際のゲート端子の電位以上となり、駆動トランジスタ5301はオフする。一方、信号線5306の電位が、画素への信号書き込み期間に画素にビデオ信号が書き込まれた際のアナログ信号電位より低くなると、駆動トランジスタ5301のゲート端子の電位も、画素にビデオ信号が書き込まれた際のゲート端子の電位より低くなるため駆動トランジスタ5301はオンする。

【0177】

したがって、画素の発光期間には、逆バイアス用スイッチ5309をオフにしたまま、駆動トランジスタ5301の第1端子が接続された電位供給線5305に $V_{dd}$ を設定し、スイッチ5303をオフにした状態で、信号線5306に設定する電位をアナログ的に変化させることで、駆動トランジスタ5301のオンオフを制御する。つまり、発光素子5304に電流が流れている時間をアナログ的に制御して階調を表現することができる。

【0178】

画素の発光期間において、信号線5306に設定する電位について説明する。信号線5306に設定する電位は周期的に変化する波形のアナログ電位を用いることができる。

【0179】

例えば、発光期間には、信号線5306に設定する電位は、実施の形態1で示したように、波形4301、波形4302、波形4303、波形4304、波形4305、波形4306若しくは波形4307、又はこれらを複数連続して設定しても良い。

【0180】

これらの波形を連続して設定することにより、発光時間を1フレーム内で分散させることができる。その結果、フレーム周波数が見かけ上は向上したようになり、画面のちらつきを防止することができる。

【0181】

そして、逆方向バイアス期間には、スイッチ5303をオフにし、電位供給線5305をLレベルにして駆動トランジスタ5301をオフする。そして、逆バイアス用スイッチ5309をオンにする。

【0182】

すると、順方向バイアス期間（書き込み期間及び発光期間のことをいう）において、発光素子5304の陽極として機能していた電極は配線5310と接続される。よって、順方

10

20

30

40

50

向バイアス期間において発光素子 5304 の陽極や陰極として機能していたそれぞれの電極に設定される電位の高低が、逆方向バイアス期間には逆になる。つまり、逆方向バイアス期間においては、発光素子 5304 に順方向バイアス期間とは逆方向の電圧を印加する。

#### 【0183】

このように、逆方向バイアス期間において、順方向バイアス期間とは逆方向の電圧を発光素子 5304 に印加しても、正常な発光素子 5304 には電流は流れない。一方、発光素子 5304 に短絡箇所が有る場合には、その短絡箇所に電流が流れる。そして、短絡箇所を絶縁化する。よって、逆方向バイアス期間には、この短絡箇所を絶縁するのに十分な電流を流すように逆方向の電圧を発光素子 5304 に印加する。

10

#### 【0184】

このように、発光素子 5304 の短絡箇所を絶縁することにより、画素の表示不良を改善することができる。また、発光素子 5304 の寿命を延ばすことが可能となる。

#### 【0185】

なお、図 52 に示すように陰極 (Cathode) 5308 の電位を順方向バイアス期間よりも逆方向バイアス期間は高くするとよい。こうすることで、発光素子 5304 の短絡箇所を絶縁するために十分な電流を得るために電圧を設定しやすくなる。

#### 【0186】

##### (実施の形態 5)

本実施の形態では、画素毎の書き込み時間を長くすることができる画素構成を有する表示装置について説明する。

20

#### 【0187】

図 12 に示す表示装置は電位供給線駆動回路 1201、信号線駆動回路 1202、走査線駆動回路 1203、画素部 1204 を有し、画素部 1204 は複数の画素 1205 を備えている。行方向に配置された電位供給線 (Illumination line) I1 ~ Im と列方向に配置された信号線 (Data line) Da1 ~ Dan 及び Db1 ~ Dbn に対応して画素 1205 がマトリクスに配置されている。行方向に配置された走査線 (Reset line) R1 ~ Rm / 2 は二行分の画素のスイッチのオンオフを制御する配線として共有されている。

30

#### 【0188】

例えば、(m - 1) 行の画素 1205 のそれぞれは駆動トランジスタ 1206 と、容量素子 1207 と、スイッチ 1208 と、発光素子 1209 と、電位供給線 Im - 1 と、それぞれの信号線 (Da1 ~ Dan) と、走査線 Rm / 2 とを有している。なお、駆動トランジスタ 1206 には P チャネル型トランジスタを用いている。なお、画素 1205 は画素部 1204 に複数配置された画素の一画素を示している。

#### 【0189】

駆動トランジスタ 1206 の第 1 端子 (ソース端子又はドレイン端子) は電位供給線 Im - 1 と接続され、ゲート端子は容量素子 1207 を介してそれぞれの信号線 (Da1 ~ Dan) と接続され、第 2 端子は発光素子 1209 の陽極 (画素電極) と接続されている。また、駆動トランジスタ 1206 のゲート端子と第 2 端子 (ソース端子又はドレイン端子) はスイッチ 1208 を介して接続されている。よって、走査線 Rm / 2 に信号が入力され、スイッチ 1208 がオンしているときには駆動トランジスタ 1206 のゲート端子と第 2 端子 (ソース端子又はドレイン端子) は導通し、スイッチ 1208 がオフすると、駆動トランジスタ 1206 のゲート端子と第 2 端子 (ソース端子又はドレイン端子) は非導通となり、その瞬間の駆動トランジスタ 1206 のゲート端子 (若しくはドレイン端子) と信号線 (Da1 ~ Dan) との電位差 (電圧) を容量素子 1207 は保持することができる。また、発光素子 1209 の陰極 (Cathode) 1210 は Vss の電位が設定されている。なお、Vss とは、画素の発光期間に電位供給線 I1 ~ Im に設定される電源電位 Vdd を基準として、Vss < Vdd を満たす電位である。例えば、Vss = GND (グラウンド電位) としても良い。

40

50

## 【0190】

つまり、 $m - 1$  行目のそれぞれの画素 1205 のスイッチ 1208 は走査線  $R_{m,2}$  に設定される信号によってオンオフが制御される。また、 $m$  行目のそれぞれの画素 1205 のスイッチ 1208 も同様に走査線  $R_{m,2}$  に設定される信号によってオンオフが制御される。そして、 $m$  行目の画素 1205 のそれぞれの駆動トランジスタ 1206 のゲート端子は信号線 ( $D_{b1} \sim D_{bn}$ ) のそれに容量素子 1207 を介して接続されている。

## 【0191】

よって、走査線  $R_{m,2}$  に設定される信号によって、 $m - 1$  行目の画素と、 $m$  行目の画素が同時に書き込み時間となる。そして、 $m - 1$  行目のそれぞれの画素はそれぞれの信号線 ( $D_{a1} \sim D_{an}$ ) からアナログ信号電位が設定されビデオ信号の書き込みが行われる。そして、 $m$  行目の画素はそれぞれの信号線 ( $D_{b1} \sim D_{bn}$ ) からアナログ信号電位が設定され、ビデオ信号の書き込みが行われる。10

## 【0192】

$m - 1$  行目の画素と  $m$  行目の画素を例に説明したが、他の行も同様に 1 つの走査線  $R_i$  ( $R_1 \sim R_{m,2}$  のうちいずれか一) により二行分の画素が選択され、同時に書き込み時間となる。よって、図 2 に示す表示装置と解像度が同じ表示装置であれば、画素の書き込み時間を 2 倍にすることができる。

## 【0193】

なお、図 12においては、2 行分の画素を同時に書き込むことができる構成について示したが、2 行に限らず、複数行の画素において走査線を共通とし、その共通とした行数分の走査線を設けることで、適宜書き込み時間を長くすることもできる。20

## 【0194】

したがって、従来の構成では高解像度になるに従って書き込み時間は減少するが、本実施の形態のような表示装置とすることで、十分な書き込み時間を確保することができる。

## 【0195】

また、本実施の形態に示した表示装置は書き込み時間を長くすることができますことから、動作周波数を低くすることができます、低消費電力化を図ることができる。

## 【0196】

なお、図 12 に示す表示装置の構成はこれに限定されない。例えば、本構成の表示装置の画素 1205 には、図 4、図 6、図 7 などの画素を適用することもできる。30

## 【0197】

(実施の形態 6)

本実施の形態では、本発明の画素構成を有するフルカラー表示の好適な表示装置の構成について説明する。

## 【0198】

実施の形態 1 で示したように、フルカラー表示の場合には、電位供給線 ( $Illumination\ line$ ) を画素の色毎に設け、それぞれの電位供給線の信号レベルの電位を色毎に設定することで、発光素子の輝度を色毎にそれぞれ調整することができる。発光素子が色毎に異なる輝度特性であっても、色合いを調整することができる。例えば、図 4 8 で示したような画素を有する場合には、R の画素の発光素子の陽極に電位を設定する  $I_{ri}$ 、G の画素の発光素子の陽極に電位を設定する  $I_{gi}$ 、B の画素の発光素子の陽極に電位を設定する  $I_{bi}$  に入力する H レベルの電位をそれぞれの色毎の輝度特性に応じて定めることができる。40

## 【0199】

しかし、RGB の色要素からなるフルカラー表示の場合にはそれぞれの行の画素に 3 本の配線が必要になり、RGBW からなるフルカラー表示の場合には 4 本の配線が必要である。

## 【0200】

本実施の形態では、さらに画素の開口率が高く、2 以上の色要素からなり、きれいなフル

カラー表示が可能な表示装置について以下に説明する。

【0201】

第1の構成として、例えば、画素の発光素子に白色(W)の発光素子を適用して、カラー フィルターを用いてフルカラー表示を行うことにより、画素の色毎から得られる輝度を概ね等しくすることができる。

【0202】

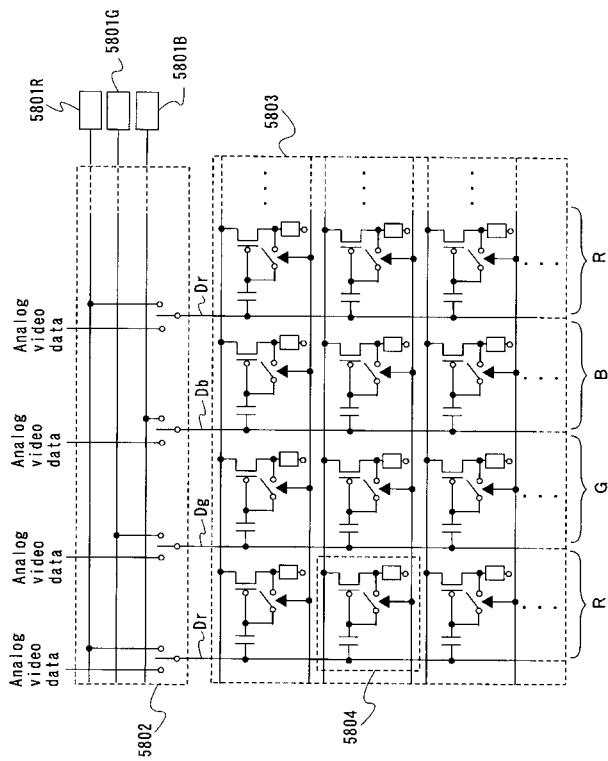

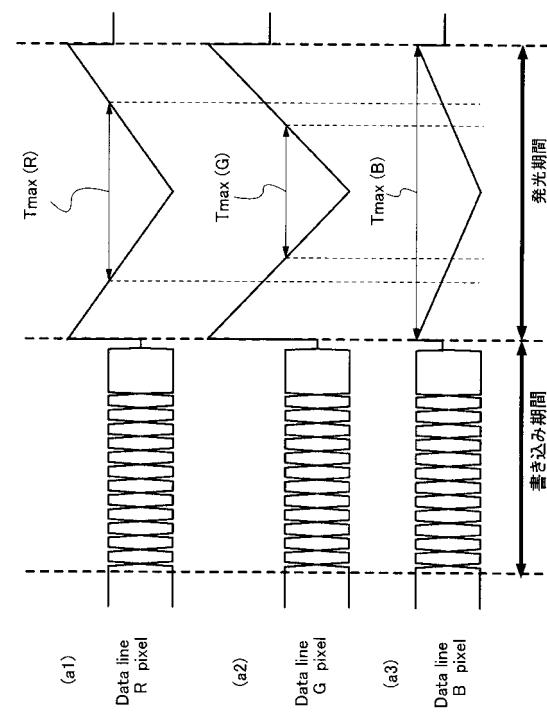

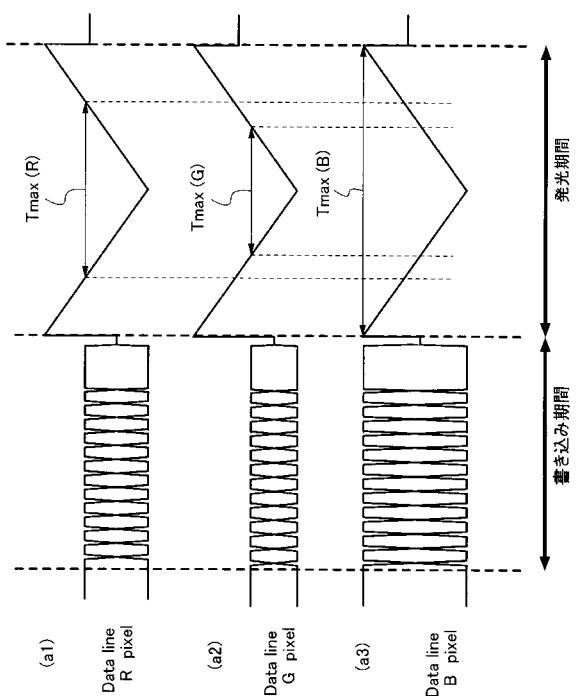

第2の構成として、図58に本実施の形態の表示装置の模式図を示す。なお、図58では一例としてRGBのそれぞれの発光素子を用いたそれぞれの色の画素からなるフルカラー表示装置の模式図を示している。表示装置は、三角波電位生成回路5801R、5801G、5801B、切り替え回路5802、画素部5803を有する。画素部5803には、複数の画素5804がマトリクスに配置されている。Rの画素列へは信号線Drから、Gの画素列へは信号線Dgから、Bの画素列へは信号線Dbから信号が入力される。

10

【0203】

また、三角波電位生成回路5801Rは、Rの画素列の三角波電位を生成する。また、三角波電位生成回路5801Gは、Gの画素列、三角波電位生成回路5801Bは、Bの画素列の三角波電位を生成する。

【0204】

画素の信号書き込み期間には、切り替え回路5802により、ビデオ信号(Analog video data)が入力される端子とそれぞれの信号線Dr、Dg、Dbを接続する。そして、発光期間になると、切り替え回路5802は、三角波電位生成回路5801Rにより三角波が入力される端子と信号線Dr、三角波電位生成回路5801Gにより三角波が入力される端子と信号線Dg、三角波電位生成回路5801Bにより三角波が入力される端子と信号線Dbとを接続する。

20

【0205】

こうして、色毎の画素によって、別々の三角波を設定することができる。したがって、色毎の発光素子の輝度特性に応じて、発光時間を制御することができるためきれいな表示のフルカラー表示を行うことができる。また、画素5804内に画素の色毎に配線を設ける必要がないため開口率も高くすることができる。

【0206】

なお、画素5804は図1の画素構成を適用しているがこれに限定されない。画素への信号書き込み期間に入力するビデオ信号の電位より発光期間に入力する三角波電位が高いか低いかで画素の点灯時間を制御することが可能な画素構成であればよい。よって、実施の形態1乃至5で示した画素を適宜適用することが可能であるし、例えば以下に示す図66～図78の画素構成を適用することもできる。

30

【0207】

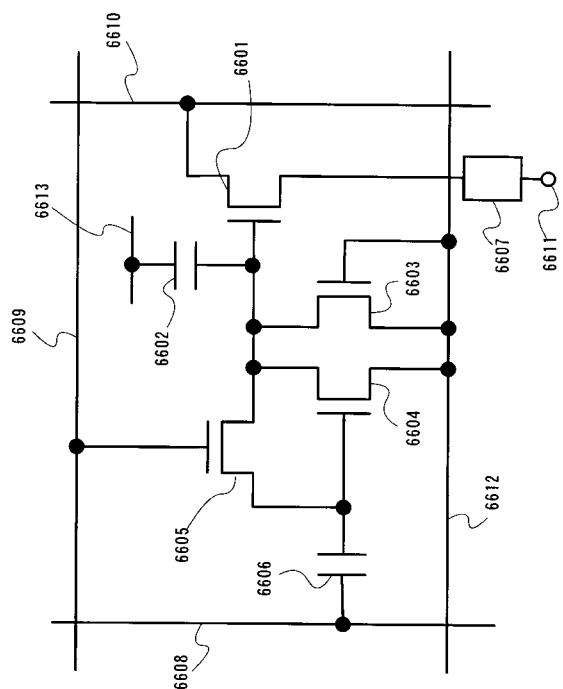

図66の画素は、トランジスタ6601と、容量素子6602と、トランジスタ6603と、トランジスタ6604と、トランジスタ6605と、容量素子6606と、発光素子6607と、信号線6608と、走査線6609と、電源線6610とを有している。

【0208】

トランジスタ6601は、第1端子(ソース端子又はドレイン端子)が発光素子6607の画素電極に接続され、第2端子(ソース端子又はドレイン端子)が電源線6610に接続されている。また、トランジスタ6601のゲート端子は容量素子6602を介して配線6613に接続されている。また、トランジスタ6603は、第1端子(ソース端子又はドレイン端子)がトランジスタ6601のゲート端子に接続され、第2端子(ソース端子又はドレイン端子)とゲート端子が配線6612に接続されている。また、トランジスタ6604は、第1端子(ソース端子又はドレイン端子)がトランジスタ6601のゲート端子に接続され、第2端子(ソース端子又はドレイン端子)が配線6612に接続され、ゲート端子が容量素子6606を介して信号線6608に接続されている。また、トランジスタ6605は、ゲート端子が走査線6609に接続され、第1端子(ソース端子又はドレイン端子)がトランジスタ6601のゲート端子に接続され、第2端子がトランジ

40

50

スタ 6 6 0 4 のゲート端子に接続されている。なお、配線 6 6 1 3 及び対向電極 6 6 1 1 には所定の電位が供給されている。

#### 【 0 2 0 9 】

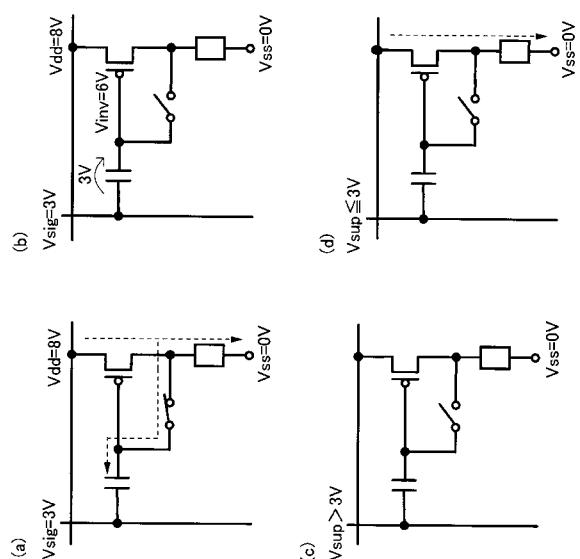

画素の動作について簡単に説明する。まず、配線 6 6 1 2 を L レベルから H レベルの電位にする。すると、配線 6 6 1 2 からトランジスタ 6 6 0 3 に電流が流れ。また、走査線 6 6 0 9 の電位を L レベルから H レベルにしてトランジスタ 6 6 0 5 をオンにする。こうして、トランジスタ 6 6 0 4 のゲート端子はトランジスタ 6 6 0 4 が十分にオンする電位となり、その電位は容量素子 6 6 0 6 の一方の電極にも印加されている。その後配線 6 6 1 2 の電位を H レベルから L レベルにすると、容量素子 6 6 0 6 に蓄積された電荷がトランジスタ 6 6 0 4 を介して配線 6 6 1 2 に流れ、トランジスタ 6 6 0 4 はしきい値電圧となる。そして、容量素子 6 6 0 6 の一方の電極の電位はそのときのトランジスタ 6 6 0 4 のゲート電位となる。このとき、信号線 6 6 0 8 にビデオ信号に相当するアナログ電位を供給しておく。すると、容量素子 6 6 0 6 には、トランジスタ 6 6 0 4 がしきい値電圧となるゲート電位と、ビデオ信号に相当するアナログ信号電位との電位差分の電荷が保持される。そして、走査線 6 6 0 9 の電位を H レベルから L レベルにすることにより、この電位差を容量素子 6 6 0 6 で保持する。10

#### 【 0 2 1 0 】

その後発光期間に配線 6 6 1 2 の電位を L レベルから H レベルにする。すると、トランジスタ 6 6 0 3 に電流が流れ、トランジスタ 6 6 0 1 が十分にオンする電位がトランジスタ 6 6 0 1 のゲート端子に入力される。そして、その電位が容量素子 6 6 0 2 の一方の電極にも印加される。こうして、トランジスタ 6 6 0 1 及び発光素子 6 6 0 7 に電流が流れ。そして、配線 6 6 1 2 の電位を H レベルから L レベルにして、信号線 6 6 0 8 に、ビデオ信号に相当するアナログ信号電位のとりうる範囲の最低電位から最高電位へ連続的に変化する電位、若しくは最高電位から最低電位へ連続的に変化する電位、又は最低電位と最高電位との間をくり返し連続的に変化する電位を入力する。すると、発光期間に信号線 6 6 0 8 に連続的に供給される電位が書き込み期間に画素へ書き込まれたビデオ信号に相当するアナログ信号電位よりも高くなると、トランジスタ 6 6 0 4 がオンする。そのため、容量素子 6 6 0 2 に蓄積された電荷がトランジスタ 6 6 0 4 を介して配線 6 6 1 2 に放電する。こうしてトランジスタ 6 6 0 1 はオフする。よって、発光期間のうち任意の時間だけ発光素子 6 6 0 7 を発光させることができるので階調表示を行うことができる。20

#### 【 0 2 1 1 】

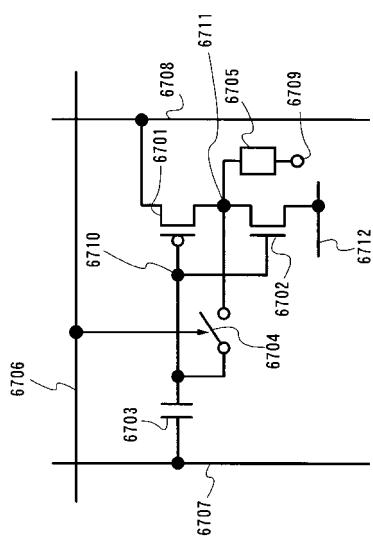

図 6 7 の画素は、駆動トランジスタ（第 1 のトランジスタ）6 7 0 1 と、相補用トランジスタ（第 2 のトランジスタ）6 7 0 2 と、容量素子 6 7 0 3 と、スイッチ 6 7 0 4 と、発光素子 6 7 0 5 と、走査線 6 7 0 6 と、信号線 6 7 0 7 と、電源線 6 7 0 8 とを有している。なお、駆動トランジスタ 6 7 0 1 には P チャネル型トランジスタ、相補用トランジスタ 6 7 0 2 には N チャネル型トランジスタを用いている。30

#### 【 0 2 1 2 】

駆動トランジスタ 6 7 0 1 は、第 1 端子（ソース端子又はドレイン端子）が電源線 6 7 0 8 と接続され、第 2 端子（ソース端子又はドレイン端子）が相補用トランジスタ 6 7 0 2 の第 2 端子（ソース端子又はドレイン端子）と接続され、ゲート端子が相補用トランジスタ 6 7 0 2 のゲート端子と接続されている。さらに、駆動トランジスタ 6 7 0 1 及び相補用トランジスタ 6 7 0 2 のゲート端子は、容量素子 6 7 0 3 を介して信号線 6 7 0 7 に接続されると共に、スイッチ 6 7 0 4 を介して駆動トランジスタ 6 7 0 1 及び相補用トランジスタ 6 7 0 2 の第 2 端子（ソース端子又はドレイン端子）と接続されている。つまり、スイッチ 6 7 0 4 をオンオフすることで、駆動トランジスタ 6 7 0 1 及び相補用トランジスタ 6 7 0 2 のゲート端子と第 2 端子（ソース端子又はドレイン端子）とを導通又は非導通にできる。そして、走査線 6 7 0 6 に信号を入力することによりスイッチ 6 7 0 4 のオンオフを制御する。また、駆動トランジスタ 6 7 0 1 及び相補用トランジスタ 6 7 0 2 の第 2 端子（ソース端子又はドレイン端子）は、発光素子 6 7 0 5 の画素電極と接続されている。そして、発光素子 6 7 0 5 の対向電極 6 7 0 9 には低電源電位 V<sub>ss</sub> が接続されている。40

10

20

30

40

50

供給されている。なお、V<sub>SS</sub>とは、電源線6708に供給される電源電位V<sub>dd</sub>を基準として、V<sub>SS</sub> < V<sub>dd</sub>を満たす電位である。例えば、V<sub>SS</sub> = GND(グラウンド電位)としても良い。また、相補用トランジスタ6702の第1端子は配線6712と接続されている。この配線6712に供給する電位は、相補用トランジスタ6702がオンするときに、発光素子6705の画素電極に印加される。そしてこのとき発光素子6705が非発光となるような電位であればなんでもよい。よって、V<sub>SS</sub>でもよい。

#### 【0213】

次に、図67の画素構成の動作原理について詳しく説明する。

#### 【0214】

画素への信号書き込み期間には、信号線6707にはアナログ信号電位が供給される。このアナログ信号電位がビデオ信号に相当する。そして、画素へビデオ信号を書き込む際には、走査線6706にHレベルの信号を入力してスイッチ6704をオンさせる。なお、駆動トランジスタ6701と相補用トランジスタ6702とはインバータとして動作する。また、インバータとして動作しているときには、駆動トランジスタ6701及び相補用トランジスタ6702のゲート端子の接続点がインバータの入力端子6710となり、駆動トランジスタ6701及び相補用トランジスタ6702の第2端子の接続点がインバータの出力端子6711となる。また、インバータとして動作しているときには、駆動トランジスタ6701及び相補用トランジスタ6702は共に第1端子がソース端子、第2端子がドレイン端子となる。

#### 【0215】

このようにスイッチ6704がオンすると、インバータの入力端子6710は出力端子6711と導通し、駆動トランジスタ6701、相補用トランジスタ6702、発光素子6705に電流が流れ、容量素子6703では電荷の放電又は蓄積が行われる。

#### 【0216】

こうして、インバータはオフセットキャンセルする。なお、オフセットキャンセルとは、入力端子6710と出力端子6711を導通し、入力電位と出力電位を等しくし、入力端子6710をインバータの論理しきい値電位V<sub>inv</sub>にすることをいう。よって、この論理しきい値V<sub>inv</sub>は、理想的にはインバータの出力のLレベルとHレベルの中間の電位である。

#### 【0217】

なお、インバータの出力のHレベルの電位は電源線6708の電源電位V<sub>dd</sub>であり、インバータのLレベルの電位は配線6712に供給される電位である。また、インバータのHレベルの出力となる電源電位V<sub>dd</sub>と、インバータのLレベルの出力となる配線6712に供給される電位は、対向電極6709の電位を基準に設定する。そして、インバータの出力がHレベルのときは、発光素子6705が発光し、インバータの出力がLレベルのときには非発光となるようとする。

#### 【0218】

つまり、発光素子6705が発光し始めるときの電圧をV<sub>EL</sub>とすると、インバータのLレベルの電位(配線6712に供給される電位)はV<sub>SS</sub> + V<sub>EL</sub>よりも低くする必要がある。また、インバータのHレベルの電位は、V<sub>SS</sub> + V<sub>EL</sub>よりも高くする必要がある。

#### 【0219】

なお、インバータのLレベルの電位が対向電極6709に供給される電位よりも低い電位とすると、発光素子6705に逆バイアス状態の電圧が加わる。よって、発光素子6705の劣化が抑制され、望ましい。

#### 【0220】

なお、容量素子6703での電荷の放電又は蓄積は、もともと容量素子6703に蓄積されていた電荷と、信号線6707に供給される電位との関係で決まる。そして、容量素子6703での電荷の放電又は蓄積が完了すると、容量素子6703には信号線6707と、論理しきい値V<sub>inv</sub>との電位差(電圧V<sub>p</sub>)分の電荷が蓄積されていることになる。

10

20

30

40

50

そして、走査線 6706 の信号を L レベルにすることにより、スイッチ 6704 をオフにし、容量素子 6703 で、この電圧  $V_p$  を保持する。

#### 【0221】

なお、書き込み期間において、対向電極 (Cathode) 6709 の電位を  $V_{ss2}$  に設定しても良い。この  $V_{ss2}$  は  $V_{ss} < V_{ss2}$  を満たす電位であり、インバータをオフセットキャンセルする際、発光素子 6705 に印加される電圧が発光素子 6705 の順方向しきい値電圧  $V_{EL}$  より小さくなるように設定する。つまり、 $V_{inv} - V_{ss2} < V_{EL}$  となるように設定する。こうすれば、書き込み期間において、発光素子 6705 が発光してしまうことにより、表示不良が発生してしまうのを防ぐことができる。また、書き込み期間において発光素子にほとんど電流が流れないようにするために、消費電力を低減することができる。10

#### 【0222】

また、 $V_{ss2}$  を大きくして、発光素子 6705 に逆バイアスの電圧が加わるようにしてもよい。逆バイアス電圧を加えることにより、発光素子 6705 の信頼性を向上させたり、発光素子 6705 の中で不具合のある部分を焼き切ったりすることができる。

#### 【0223】

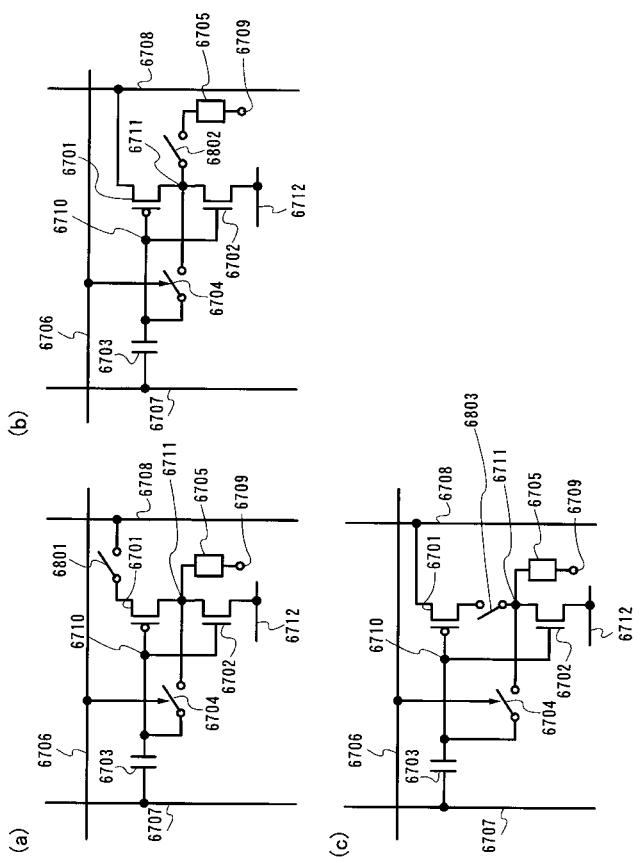

なお、対向電極 6709 に電流が流れないようにすればよいので、別な方法を用いることもできる。例えば、対向電極 6709 をフローティング状態にしてもよい。その結果、発光素子 6705 には電流は流れない。あるいは、電源線 6708 からトランジスタ 6701 を介して発光素子 6705 の画素電極までの間にスイッチを設けてもよい。このスイッチを制御することにより、発光素子 6705 に電流が流れないようにすることができます。つまり、図 68 (a) に示すようにトランジスタ 6701 の第 1 端子と電源線 6708 との間にスイッチ 6801 を接続してもよい。また、図 68 (b) に示すようにノード 6711 と発光素子 6705 の画素電極との間にスイッチ 6802 を接続してもよい。また、トランジスタ 6701 の第 2 端子とノード 6711 との間にスイッチ 6803 を接続してもよい。こうすることで画素への信号書き込み期間において、画素への信号書き込み後、他の行の画素への信号書き込み時ににおける発光素子 6705 の発光を防ぐことができる。20

#### 【0224】

こうしてこの画素へビデオ信号の書き込みが終了する。

#### 【0225】

なお、画素にビデオ信号が書き込まれた後は、その画素にビデオ信号が書き込まれた際に信号線 6707 に供給されたアナログ信号電位を基準にして、信号線 6707 の電位の変動に従ってインバータの出力のレベルが制御されるようになる。つまり、信号線 6707 の電位が、画素への信号書き込み期間に、画素にビデオ信号が書き込まれた際のアナログ信号電位より高いときにはインバータの出力は L レベルとなり、画素にビデオ信号が書き込まれた際のアナログ信号電位より低くなるとインバータの出力は H レベルとなる。30

#### 【0226】

なぜなら、画素にビデオ信号が書き込まれると、容量素子 6703 が電位差 ( $V_p$ ) を保持するため、信号線 6707 の電位が、画素にビデオ信号が書き込まれた際のアナログ信号電位より高いときには、インバータの入力端子 6710 の電位も、画素にビデオ信号が書き込まれた際の入力端子 6710 の電位より高くなり、駆動トランジスタ 6701 はオフし、相補用トランジスタ 6702 はオンし、インバータの出力は L レベルとなる。一方、信号線 6707 の電位が、画素への信号書き込み期間に画素にビデオ信号が書き込まれた際のアナログ信号電位より低くなると、インバータの入力端子 6710 の電位も、画素にアナログ信号が書き込まれた際の入力端子 6710 の電位より低くなるため、駆動トランジスタ 6701 はオンし、相補用トランジスタ 6702 はオフし、駆動インバータの出力は H レベルとなる。40

#### 【0227】

したがって、画素の発光期間には、信号線 6707 に供給する電位をアナログ的に変化させることで、画素内のインバータの出力のレベルを制御する。こうして、発光素子 67050

5に電流が流れている時間をアナログ的に制御して階調を表現することができる。

### 【0228】

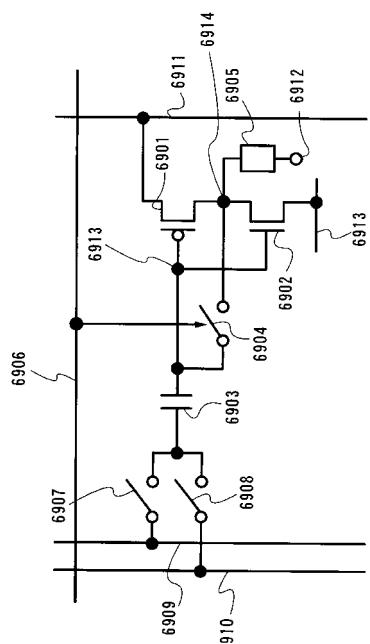

図69の画素は、駆動トランジスタ（第1のトランジスタ）6901と、相補用トランジスタ（第2のトランジスタ）6902と、容量素子6903と、スイッチ6904と、発光素子6905と、走査線6906と、第1のスイッチ6907と、第2のスイッチ6908と、第1の信号線6909と、第2の信号線6910と、電源線6911と、を有している。なお、駆動トランジスタ6901にはPチャネル型トランジスタ、相補用トランジスタ6902及びスイッチ6904にはNチャネル型トランジスタを用いている。

### 【0229】

駆動トランジスタ6901は、第1端子（ソース端子又はドレイン端子）が電源線6911と接続され、第2端子（ソース端子又はドレイン端子）が相補用トランジスタ6902の第2端子（ソース端子又はドレイン端子）と接続され、ゲート端子が相補用トランジスタ6902のゲート端子と接続されている。さらに、駆動トランジスタ6901及び相補用トランジスタ6902のゲート端子は、容量素子6903の一方の電極と接続されると共に、スイッチ6904を介して駆動トランジスタ6901及び相補用トランジスタ6902の第2端子（ソース端子又はドレイン端子）と接続されている。つまり、スイッチ6904をオンオフすることで、駆動トランジスタ6901及び相補用トランジスタ6902のゲート端子と第2端子（ソース端子又はドレイン端子）とを導通又は非導通にすることができる。そして、走査線6906に信号を入力することによりスイッチ6904のオンオフを制御する。なお、容量素子6903の他方の電極は第1のスイッチ6907を介して第1の信号線6909と、第2のスイッチ6908を介して第2の信号線6910と接続されている。また、駆動トランジスタ6901及び相補用トランジスタ6902の第2端子（ソース端子又はドレイン端子）は、発光素子6905の画素電極と接続されている。そして、発光素子6905の対向電極6912には低電源電位Vssが供給されている。なお、Vssとは、電源線6911に供給される電源電位Vddを基準として、 $V_{ss} < V_{dd}$ を満たす電位である。例えば、 $V_{ss} = GND$ （グラウンド電位）としても良い。なお、電源線6911の電位はこれに限られない。画素の色毎に電源電位の値を変えてよい。つまり、RGBの色要素の画素からなるフルカラー表示の場合には、RGBの画素毎に、RGBWの色要素の画素からなるフルカラー表示装置の場合には、RGBWの画素毎に電源線の電位を供給すればよい。

10

20

30

40

### 【0230】

次に、図69の画素構成の動作原理について詳しく説明する。

### 【0231】

まず、画素への信号書き込み動作時には、第1のスイッチ6907をオンにし、第2のスイッチ6908をオフにする。駆動トランジスタ6901と相補用トランジスタ6902とはインバータとして機能する。よって、駆動トランジスタ6901及び相補用トランジスタ6902のゲート端子の接続点がインバータの入力端子6913となり、駆動トランジスタ6901及び相補用トランジスタ6902の第2端子の接続点がインバータの出力端子6914となる。

### 【0232】

また、走査線6906にはHレベルの信号が入力されスイッチ6904がオンする。よって、インバータの入力端子6913と出力端子6914とが導通され、オフセットキャセルされる。つまり、インバータの入力端子6913はインバータの論理しきい値電位 $V_{inv}$ となっている。よって、このときインバータの入力端子6913はインバータの出力のレベルを制御するために必要な電位となっている。

### 【0233】

そして、容量素子6903には、インバータの論理しきい値電位 $V_{inv}$ と、書き込み動作時に第1の信号線6909に供給される電位Vaとの電位差分（電圧Vp）の電荷が蓄積される。

### 【0234】

50

続いて、第1のスイッチ6907をオフにし、第2のスイッチ6908をオンにする。そして、走査線6906をLレベルにする。すると、スイッチ6904がオフし、容量素子6903で電圧Vpが保持される。こうして、画素に第1の信号線6909からアナログ信号が書き込まれる。

#### 【0235】

なお、第2の信号線6910には三角波電位が供給されている。画素は第2の信号線6910が、画素の信号書き込み動作時に第1の信号線6909に供給されたアナログ信号電位より高い電位であるときは発光素子6905は非発光の状態を維持し、第2の信号線6910が、画素の信号書き込み動作時に第1の信号線6909に供給されたアナログ信号電位より低い電位の間は発光素子6905は発光する。よって、それぞれ画素への信号書き込み期間にアナログ信号が書き込まれた際のアナログ信号電位にしたがって発光素子6905の発光時間が制御される。こうして、アナログ時間階調表示が可能となる。

10

#### 【0236】

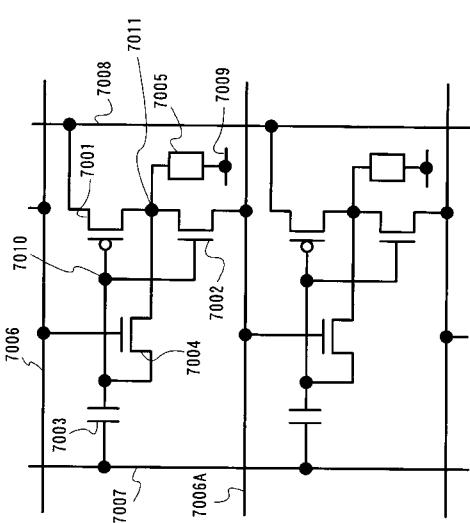

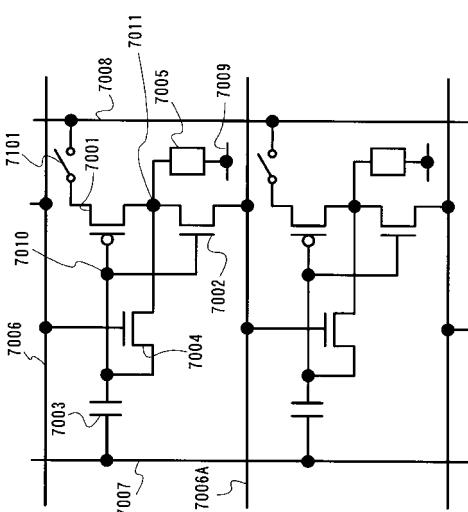

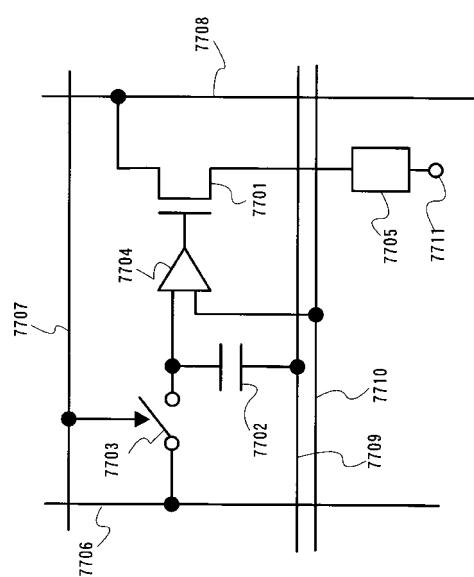

図70の画素は、駆動トランジスタ（第2のトランジスタ）7001と、相補用トランジスタ（第3のトランジスタ）7002と、容量素子7003と、スイッチング用トランジスタ（第1のトランジスタ）7004と、発光素子7005と、走査線7006と、信号線7007と、電源線7008とを有している。なお、駆動トランジスタ7001にはPチャネル型トランジスタ、相補用トランジスタ7002及びスイッチング用トランジスタ7004にはNチャネル型トランジスタを用いている。

20

#### 【0237】

駆動トランジスタ7001は、第1端子（ソース端子又はドレイン端子）が電源線7008と接続され、第2端子（ソース端子又はドレイン端子）が相補用トランジスタ7002の第2端子（ソース端子又はドレイン端子）と接続され、ゲート端子が相補用トランジスタ7002のゲート端子と接続されている。さらに、駆動トランジスタ7001及び相補用トランジスタ7002のゲート端子は、容量素子7003を介して信号線7007に接続されると共に、スイッチング用トランジスタ7004を介して駆動トランジスタ7001及び相補用トランジスタ7002の第2端子（ソース端子又はドレイン端子）と接続されている。つまり、スイッチング用トランジスタ7004は、第1端子（ソース端子又はドレイン端子）が駆動トランジスタ7001及び相補用トランジスタ7002の第2端子（ソース端子又はドレイン端子）と接続され、第2端子（ソース端子又はドレイン端子）が駆動トランジスタ7001及び相補用トランジスタ7002のゲート端子と接続されているため、スイッチング用トランジスタ7004をオンオフすることで、駆動トランジスタ7001及び相補用トランジスタ7002のゲート端子と第2端子（ソース端子又はドレイン端子）とを導通又は非導通にことができる。そして、スイッチング用トランジスタ7004のゲート端子が接続されている走査線7006に信号を入力することによりスイッチング用トランジスタ7004のオンオフを制御する。また、駆動トランジスタ7001及び相補用トランジスタ7002の第2端子（ソース端子又はドレイン端子）は、発光素子7005の画素電極と接続されている。そして、発光素子7005の対向電極7009には低電源電位Vssが供給されている。なお、Vssとは、電源線7008に供給される電源電位Vddを基準として、Vss < Vddを満たす電位である。例えば、Vss = GND（グラウンド電位）としても良い。

30

#### 【0238】

さらに、相補用トランジスタ7002の第1端子は別の行の画素の走査線7006Aに接続されている。ここで、駆動トランジスタ7001は発光素子7005を駆動するトランジスタであり、相補用トランジスタ7002は駆動トランジスタ7001とは極性が反転しているトランジスタである。つまり、この走査線7006Aの信号がLレベルのときに駆動トランジスタ7001と相補用トランジスタ7002とが相補的にオンオフするインバータを構成している。

40

#### 【0239】

次に、図70の画素構成の動作原理について詳しく説明する。

50

## 【0240】

画素への信号書き込み期間には、信号線 7007 にはアナログ信号電位が供給される。このアナログ信号電位がビデオ信号に相当する。そして、画素へビデオ信号を書き込む際には、走査線 7006 に H レベルの信号を入力してスイッチング用トランジスタ 7004 をオンさせる。なお、このとき、別の行の画素を選択する走査線 7006A には L レベルの信号が供給されている。よって、画素へ信号を書き込む際には駆動トランジスタ 7001 と相補用トランジスタ 7002 とはインバータとして動作することになる。なお、インバータとして動作しているときには、駆動トランジスタ 7001 及び相補用トランジスタ 7002 のゲート端子の接続点がインバータの入力端子 7010 となり、駆動トランジスタ 7001 及び相補用トランジスタ 7002 の第 2 端子の接続点がインバータの出力端子 7011 となる。また、インバータとして動作しているときには、駆動トランジスタ 7001 及び相補用トランジスタ 7002 は共に第 1 端子がソース端子、第 2 端子がドレイン端子となる。

10

## 【0241】

このようにスイッチング用トランジスタ 7004 がオンすると、インバータの入力端子 7010 は出力端子 7011 と導通し、駆動トランジスタ 7001、相補用トランジスタ 7002、発光素子 7005 に電流が流れ、容量素子 7003 では電荷の放電又は蓄積が行われる。

20

## 【0242】

こうして、インバータはオフセットキャンセルする。なお、オフセットキャンセルとは、入力端子 7010 と出力端子 7011 を導通し、入力電位と出力電位を等しくし、入力端子 7010 をインバータの論理しきい値電位  $V_{inv}$  にすることをいう。よって、この論理しきい値  $V_{inv}$  は、理想的にはインバータの出力の L レベルと H レベルの中間の電位である。

20

## 【0243】

なお、インバータの出力の H レベルの電位は電源線 7008 の電源電位  $V_{dd}$  であり、インバータの L レベルの電位は走査線 7006A に供給される L レベルの電位である。また、インバータの H レベルの出力となる電源電位  $V_{dd}$  と、インバータの L レベルの出力となる走査線 7006 や走査線 7006A に供給される信号の L レベルの電位は、対向電極 7009 の電位を基準に設定する。そして、インバータの出力が H レベルのときは、発光素子 7005 が発光し、インバータの出力が L レベルのときには非発光となるようとする。

30

## 【0244】

つまり、発光素子 7005 が発光し始めるときの電圧を  $V_{EL}$  とすると、インバータの L レベルの電位（走査線 7006 や走査線 7006A に供給される信号の L レベルの電位）は  $V_{ss} + V_{EL}$  よりも低くする必要がある。また、インバータの H レベルの電位は、 $V_{ss} + V_{EL}$  よりも高くする必要がある。

30

## 【0245】

なお、インバータの L レベルの電位が対向電極 7009 の電位よりも低い電位とすると、発光素子 7005 に逆バイアス状態の電圧が加わる。よって、発光素子 7005 の劣化が抑制され、望ましい。

40

## 【0246】

なお、容量素子 7003 での電荷の放電又は蓄積は、もともと容量素子 7003 に蓄積されていた電荷と、信号線 7007 に供給される電位との関係で決まる。そして、容量素子 7003 での電荷の放電又は蓄積が完了すると、容量素子 7003 には信号線 7007 と、論理しきい値  $V_{inv}$  との電位差（電圧  $V_p$ ）分の電荷が蓄積されていることになる。そして、走査線 7006 の信号を L レベルにすることにより、スイッチング用トランジスタ 7004 をオフにし、容量素子 7003 で、この電圧  $V_p$  を保持する。

40

## 【0247】

なお、書き込み期間において、対向電極（Cathode）7009 の電位を  $V_{ss2}$  に

50

設定しても良い。このV<sub>ss2</sub>はV<sub>ss</sub><V<sub>ss2</sub>を満たす電位であり、インバータをオフセットキャンセルする際、発光素子7005に印加される電圧が発光素子7005の順方向しきい値電圧V<sub>E\_L</sub>より小さくなるように設定する。つまり、V<sub>inv</sub>-V<sub>ss2</sub><V<sub>E\_L</sub>となるように設定する。こうすれば、書き込み期間において、発光素子7005が発光してしまうことにより、表示不良が発生してしまうのを防ぐことができる。また、書き込み期間において発光素子にほとんど電流が流れないようにすることができるため、消費電力を低減することができる。

#### 【0248】

また、V<sub>ss2</sub>を大きくして、発光素子7005に逆バイアスの電圧が加わるようにしてよい。逆バイアス電圧を加えることにより、発光素子7005の信頼性を向上させたり、発光素子7005の中で不具合のある部分を焼き切ったりすることができる。

10

#### 【0249】

なお、対向電極7009に電流が流れないようにすればよいので、別 の方法を用いることもできる。例えば、対向電極7009をフロー ティング状態にしてもよい。その結果、発光素子7005には電流は流れない。あるいは、電源線7008からトランジスタ7001を介して発光素子7005の画素電極までの間にスイッチを設けてもよい。このスイッチを制御することにより、発光素子7005に電流が流れないようにすることができる。つまり、図71に示すようにトランジスタ7001の第1端子と電源線7008との間にスイッチ7101を接続してもよい。また、ノード7011と発光素子7005の画素電極との間にスイッチを接続してもよい。また、トランジスタ7001の第2端子とノード7011との間にスイッチを接続してもよい。こうすることで画素への信号書き込み期間において、画素への信号書き込み後、他の行の画素への信号書き込み時ににおける発光素子7005の発光を防ぐことができる。

20

#### 【0250】

こうしてこの画素へビデオ信号の書き込みが終了する。

#### 【0251】

なお、画素にビデオ信号が書き込まれた後は、その画素にビデオ信号が書き込まれた際に信号線7007に供給されたアナログ信号電位を基準にして、信号線7007の電位の変動に従ってインバータの出力のレベルが制御されるようになる。つまり、信号線7007の電位が、画素への信号書き込み期間に、画素にビデオ信号が書き込まれた際のアナログ信号電位より高いときにはインバータの出力はLレベルとなり、画素にビデオ信号が書き込まれた際のアナログ信号電位より低くなるとインバータの出力はHレベルとなる。

30

#### 【0252】

なぜなら、画素にビデオ信号が書き込まれると、容量素子7003が電位差(V<sub>p</sub>)を保持するため、信号線7007の電位が、画素にビデオ信号が書き込まれた際のアナログ信号電位より高いときには、インバータの入力端子7010の電位も、画素にビデオ信号が書き込まれた際の入力端子7010の電位より高くなり、駆動トランジスタ7001はオフし、相補用トランジスタ7002はオンし、インバータの出力はLレベルとなる。一方、信号線7007の電位が、画素への信号書き込み期間に画素にビデオ信号が書き込まれた際のアナログ信号電位より低くなると、インバータの入力端子7010の電位も、画素にアナログ信号が書き込まれた際の入力端子7010の電位より低くなるため、駆動トランジスタ7001はオンし、相補用トランジスタ7002はオフし、駆動インバータの出力はHレベルとなる。

40

#### 【0253】

したがって、画素の発光期間には、走査線(走査線7006、走査線7006Aなど)をLレベルにした状態で、信号線7007に供給する電位をアナログ的に変化させることで、画素内のインバータの出力のレベルを制御する。こうして、発光素子7005に電流が流れている時間をアナログ的に制御して階調を表現することができる。

#### 【0254】

また、相補用トランジスタの第1端子(ソース端子又はドレイン端子)を走査線7006

50

Aに接続したことにより配線数を減らすことができ、開口率が向上する。よって、発光素子の信頼性の向上を図ることができる。また、歩留まりを向上させ、表示パネルのコストの抑制を図ることができる。

#### 【0255】

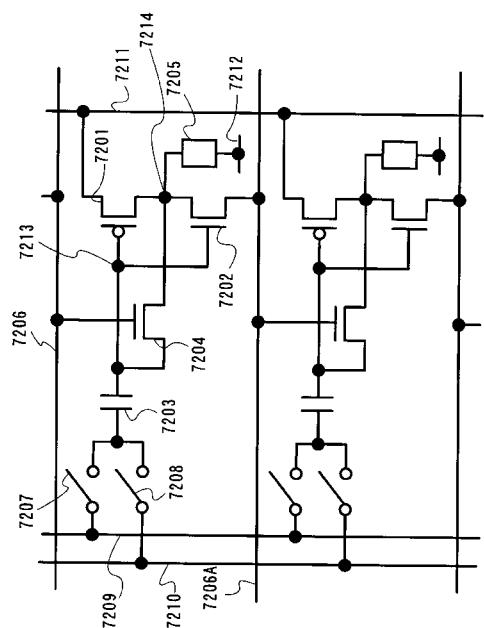

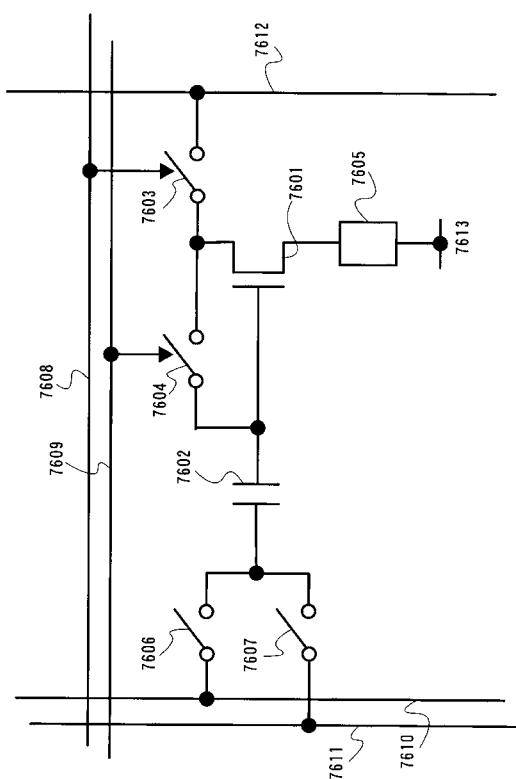

図72に示す画素は、駆動トランジスタ（第2のトランジスタ）7201と、相補用トランジスタ（第3のトランジスタ）7202と、容量素子7203と、スイッチング用トランジスタ（第1のトランジスタ）7204と、発光素子7205と、走査線7206と、第1のスイッチ7207と、第2のスイッチ7208と、第1の信号線7209と、第2の信号線7210と、電源線7211と、を有している。なお、駆動トランジスタ7201にはPチャネル型トランジスタ、相補用トランジスタ7202及びスイッチング用トランジスタ7204にはNチャネル型トランジスタを用いている。10

#### 【0256】

駆動トランジスタ7201は、第1端子（ソース端子又はドレイン端子）が電源線611と接続され、第2端子（ソース端子又はドレイン端子）が相補用トランジスタ7202の第2端子（ソース端子又はドレイン端子）と接続され、ゲート端子が相補用トランジスタ7202のゲート端子と接続されている。さらに、駆動トランジスタ7201及び相補用トランジスタ7202のゲート端子は、容量素子7203の一方の電極と接続されると共に、スイッチング用トランジスタ7204を介して駆動トランジスタ7201及び相補用トランジスタ7202の第2端子（ソース端子又はドレイン端子）と接続されている。つまり、スイッチング用トランジスタ7204は、第1端子（ソース端子又はドレイン端子）が駆動トランジスタ7201及び相補用トランジスタ7202の第2端子（ソース端子又はドレイン端子）と接続され、第2端子（ソース端子又はドレイン端子）が駆動トランジスタ7201及び相補用トランジスタ7202のゲート端子と接続されているため、スイッチング用トランジスタ7204をオンオフすることで、駆動トランジスタ7201及び相補用トランジスタ7202のゲート端子と第2端子（ソース端子又はドレイン端子）とを導通又は非導通にすることができる。そして、スイッチング用トランジスタ7204のゲート端子が接続されている走査線7206に信号を入力することによりスイッチング用トランジスタ7204のオンオフを制御する。なお、容量素子7203の他方の電極は第1のスイッチ7207を介して第1の信号線7209と、第2のスイッチ7208を介して第2の信号線7210と接続されている。また、駆動トランジスタ7201及び相補用トランジスタ7202の第2端子（ソース端子又はドレイン端子）は、発光素子7205の陽極（画素電極）と接続されている。そして、発光素子7205の陰極は低電源電位Vssが供給された配線（Cathode）7212と接続されている。なお、Vssとは、電源線7211に供給される電源電位Vddを基準として、 $V_{ss} < V_{dd}$ を満たす電位である。例えば、 $V_{ss} = GND$ （グラウンド電位）としても良い。なお、電源線7211の電位はこれに限られない。画素の色毎に電源電位の値を変えてよい。つまり、RGBの色要素の画素からなるフルカラー表示の場合には、RGBの画素毎に、RGBWの色要素の画素からなるフルカラー表示装置の場合には、RGBWの画素毎に電源線の電位を供給すればよい。2030

#### 【0257】

さらに、相補用トランジスタ7202の第1端子は別の行の画素の走査線7206Aに接続されている。ここで、駆動トランジスタ7201は発光素子7205を駆動するトランジスタであり、相補用トランジスタ7202は駆動トランジスタ7201とは極性が反転しているトランジスタである。つまり、この走査線7206Aの信号がLレベルのときに駆動トランジスタ7201と相補用トランジスタ7202とが相補的にオンオフするインバータを構成している。40

#### 【0258】

図72の画素の動作の原理については、図70の動作と同様であり、書き込み動作時に画素にビデオ信号を入力する配線と、発光期間に画素に連続的に変化する電位を供給する配線とを別にした場合の動作については、実施の形態2若しくは図69の動作の説明を参照50

されたい。

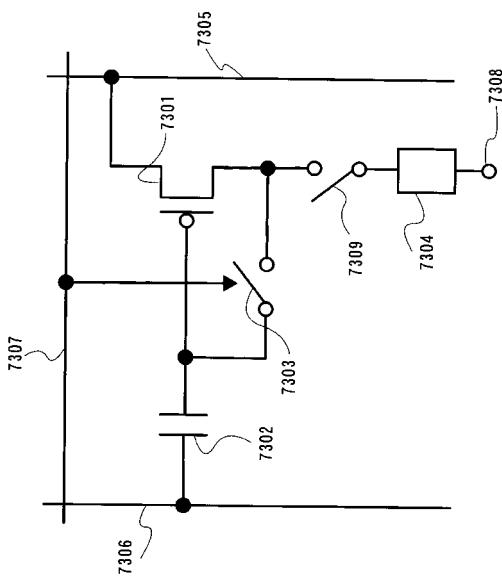

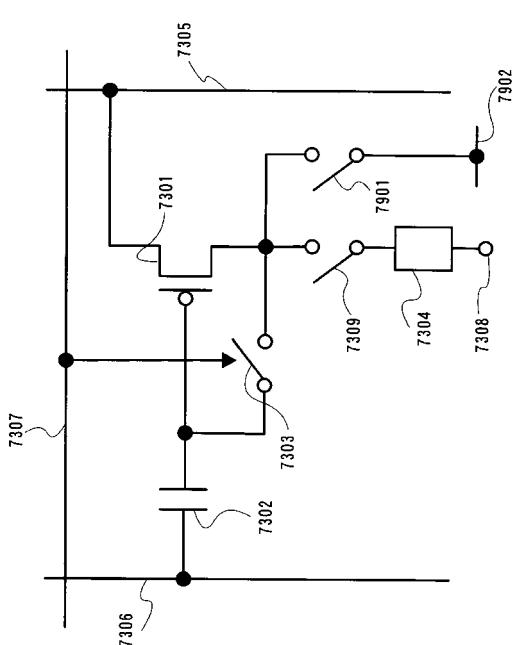

【0259】

図73の画素は駆動トランジスタ7301と、容量素子7302と、スイッチ7303と、発光素子7304と、電源線7305と、信号線7306と、走査線7307、スイッチ7309とを有している。なお、駆動トランジスタ7301にはPチャネル型トランジスタを用いている。

【0260】

駆動トランジスタ7301の第1端子（ソース端子又はドレイン端子）は電源線7305と接続され、ゲート端子は容量素子7302を介して信号線7306と接続され、第2端子（ソース端子又はドレイン端子）はスイッチ7309を介して発光素子7304の陽極（画素電極）と接続されている。また、駆動トランジスタ7301のゲート端子と第2端子（ソース端子又はドレイン端子）はスイッチ7303を介して接続されている。よって、スイッチ7303がオンしているときには駆動トランジスタ7301のゲート端子と第2端子（ソース端子又はドレイン端子）は導通する。そして、スイッチ7303がオフすると、駆動トランジスタ7301のゲート端子と第2端子（ソース端子又はドレイン端子）は非導通となり、その瞬間の駆動トランジスタ7301のゲート端子（若しくは第2端子）と信号線7306との電位差（電圧）を容量素子7302は保持することができる。なお、発光素子7304の対向電極7308はVssの電位が設定されている。なお、Vssとは、画素の発光期間に電源線7305に設定される電源電位Vddを基準として、 $V_{ss} < V_{dd}$ を満たす電位である。例えば、 $V_{ss} = GND$ （グラウンド電位）としても良い。

【0261】

次に、図73の画素構成の動作原理について説明する。

【0262】

画素への信号書き込み期間には、信号線7306にはアナログ信号電位が供給される。このアナログ信号電位がビデオ信号に相当する。なお、このビデオ信号は3値以上で表される信号であり、アナログ信号電位とは、時間とともに変化し3値以上の状態を持つ電位である。そして、画素へビデオ信号を書き込む際には、走査線7307に信号を入力してスイッチ7303をオンさせる。また、スイッチ7309をオンにする。すると、駆動トランジスタ7301及び発光素子7304に電流が流れ、容量素子7302には電荷の蓄積又は放電が行われる。

【0263】

このとき、駆動トランジスタ7301の第1端子はソース端子となり、第2端子はドレイン端子となっている。そして、スイッチ7303がオンになっている状態で駆動トランジスタ7301に流れる電流が増加すると、発光素子7304に流れる電流も大きくなるため、発光素子7304での電圧降下は大きくなり、発光素子7304の電極間の電位差は大きくなる。つまり、発光素子7304の陽極の電位は電源線7305の電位に近づく。すると、駆動トランジスタ7301のゲート端子の電位も電源線7305の電位に近づくため、駆動トランジスタ7301のゲート端子とソース端子の電位差が小さくなり、駆動トランジスタ7301に流れる電流は減少する。一方、発光素子7304に流れる電流が小さくなると、発光素子7304での電圧降下は小さくなり、発光素子7304の電極間の電位差は小さくなる。つまり、発光素子7304の陽極の電位は陰極108の電位に近づく。すると、駆動トランジスタ7301のゲート端子も陰極7308の電位に近づくため、駆動トランジスタ7301のゲート端子とソース端子の電位差が大きくなり、駆動トランジスタ7301に流れる電流が増加する。こうして、駆動トランジスタ7301のゲート端子は駆動トランジスタ7301に一定の電流が流れのような電位に落ち着く。そして、そのときの駆動トランジスタ7301のゲート端子の電位と信号線7306の電位との電位差分の電荷が容量素子7302に蓄積される。

【0264】

こうしてこの画素へビデオ信号の書き込みが終了する。

10

20

30

40

50

**【0265】**

このように駆動トランジスタ7301及び発光素子7304に流れる電流が一定となり、定常状態となったところで、スイッチ7303をオフさせる。すると、容量素子7302は、スイッチ7303がオフした瞬間の信号線7306の電位と駆動トランジスタ7301のゲート端子（若しくはドレイン端子）との電位差 $V_p$ （電圧）を保持する。

**【0266】**

画素への信号書き込み期間において、画素へのビデオ信号の書き込み終了後、他の行の画素への信号書き込みを行っている間は、スイッチ7309をオフにする。なお、このスイッチ7309をオフにするタイミングはスイッチ7303をオフにするタイミングと同時か、それよりも後にする。

10

**【0267】**

なお、画素にビデオ信号が書き込まれると、その画素にビデオ信号が書き込まれた際に信号線7306に設定されたアナログ信号電位を基準にして、信号線7306の電位の変動に従って駆動トランジスタ7301のオンオフが制御されるようになる。つまり、信号線7306の電位が、画素への信号書き込み期間に画素にビデオ信号が書き込まれた際のアナログ信号電位以上のときには駆動トランジスタ7301はオフし、画素にビデオ信号が書き込まれた際のアナログ信号電位より低くなると駆動トランジスタ7301はオンする。

**【0268】**

なぜなら、画素にビデオ信号が書き込まれると、容量素子7302が電位差( $V_p$ )を保持するため、信号線7306の電位が、画素にビデオ信号が書き込まれた際のアナログ信号電位以上のときには、駆動トランジスタ7301のゲート端子の電位も、画素にビデオ信号が書き込まれた際のゲート端子の電位以上となり、駆動トランジスタ7301はオフする。一方、信号線7306の電位が、画素への信号書き込み期間に画素にビデオ信号が書き込まれた際のアナログ信号電位より低くなると、駆動トランジスタ7301のゲート端子の電位も、画素にビデオ信号が書き込まれた際のゲート端子の電位より低くなるため駆動トランジスタ7301はオンする。

20

**【0269】**

したがって、画素の発光期間には、スイッチ7303をオフにし、スイッチ7309をオンにした状態で、信号線7306に設定する電位をアナログ的に変化させることで、駆動トランジスタ7301のオンオフを制御する。つまり、発光素子7304に電流が流れている時間をアナログ的に制御して階調を表現することができる。

30

**【0270】**

また、図73の画素構成において駆動トランジスタ7301の第2端子をスイッチを介して対向電極7308と同じ電位の供給される配線に接続してもよい。つまり、図79に示すように、駆動トランジスタ7301の第2端子をスイッチ7901を介して配線7902と接続する。画素へ信号を書き込む際にはスイッチ7901をオンにし、書き込みが終わったらオフにする。そして、他の行の画素への信号の書き込み及び発光期間にはスイッチ7901をオフにする。すると、画素への信号書き込み時において画素を発光させなくすることができる。その他については図73の動作を参照されたい。

40

**【0271】**

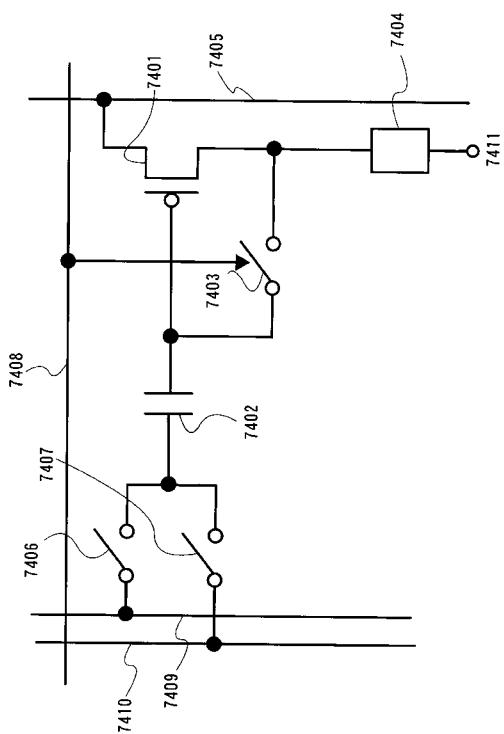

図74の画素は駆動トランジスタ7401と、容量素子7402と、第1のスイッチ7403と、発光素子7404と、電源線7405と、第2のスイッチ7406と、第3のスイッチ7407と、走査線7408と、第1の信号線7409と、第2の信号線7410ととを有している。なお、駆動トランジスタ7401にはPチャネル型トランジスタを用いている。

**【0272】**

駆動トランジスタ7401の第1端子（ソース端子又はドレイン端子）は電源線7405と接続され、ゲート端子は容量素子7402の一方の電極と接続され、容量素子7402の他方の電極は、第2のスイッチ7406を介して第1の信号線7409と、第3のスイ

50

スイッチ7407を介して第2の信号線7410と接続されている。また、駆動トランジスタ7401のゲート端子と第2端子(ソース端子又はドレイン端子)はスイッチ7403を介して接続されている。なお、発光素子7404の陰極7411はVssの電位が設定されている。なお、Vssとは、電源線7405に設定される電源電位Vddを基準として、 $V_{ss} < V_{dd}$ を満たす電位である。例えば、 $V_{ss} = GND$ (グラウンド電位)としても良い。

#### 【0273】

次に、図74の画素の動作について説明する。書き込み動作時には第2のスイッチ7406をオンにし、第3のスイッチ7407をオフにする。そして、走査線7408にはHレベルの信号を入力し、第1のスイッチ7403をオンにする。すると、容量素子7402、駆動トランジスタ7401及び発光素子7404に電流が流れる。そして、容量素子7402では電荷の蓄積若しくは放電が行われる。つまり、容量素子7402にもともと蓄積されていた電荷と第1の信号線7409に設定された電位との関係で電荷の蓄積か放電のどちらかが起きる。そして、走査線7408の信号がHレベルからLレベルに立ち下がると、第1のスイッチ7403がオフする。第1のスイッチ7403がオフすると、その瞬間の駆動トランジスタ7401のゲート端子の電位と第1の信号線7409の電位との電位差を容量素子7402は保持する。

10

#### 【0274】

こうして、画素に第1の信号線7409からビデオ信号が書き込まれる。

20

#### 【0275】

なお、発光期間には第2の信号線7410にはアナログ的に変化する電位が供給されている。画素は第2の信号線7410が、1行目の画素の信号書き込み時間に第1の信号線7409に設定されたアナログ信号電位より高い電位であるときには発光素子7404は非発光の状態を維持し、第2の信号線7410が、画素の信号書き込み時間に第1の信号線7409に設定されたアナログ信号電位より低い電位の間(Ta)は発光素子7404は発光する。よって、それぞれの画素の書き込み時間にビデオ信号が書き込まれた際のアナログ信号電位にしたがって発光素子7404の発光時間が設定される。こうして、アナログ時間階調表示が可能となる。

30

#### 【0276】

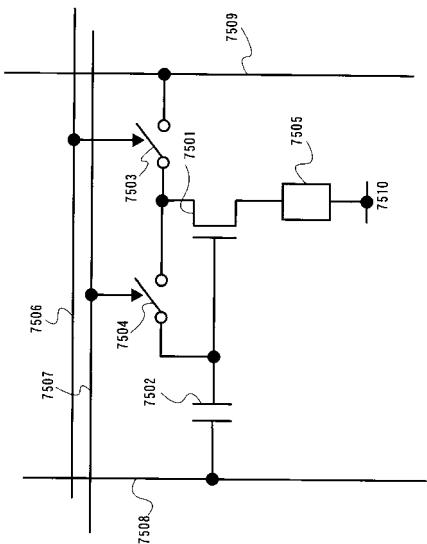

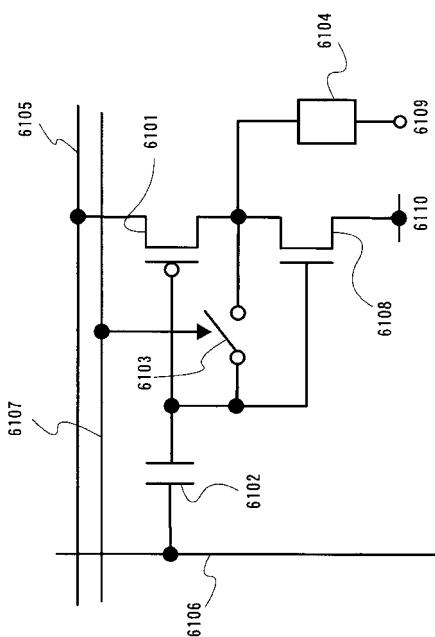

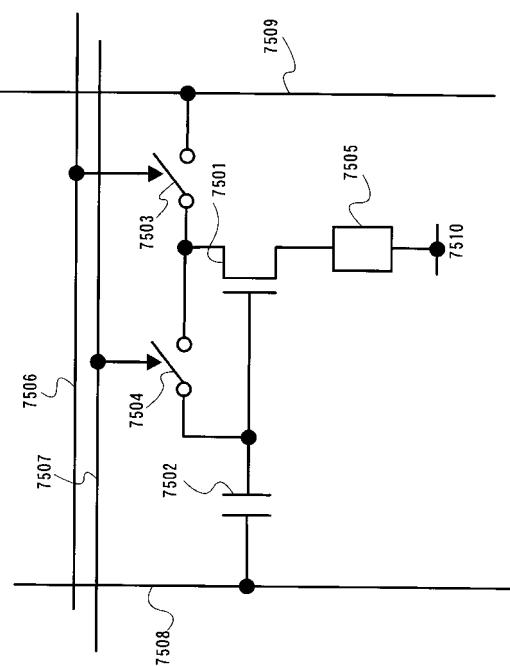

図75の画素は、駆動トランジスタ7501と、容量素子7502と、第1のスイッチ7503と、第2のスイッチ7504と、発光素子7505と、第1の走査線7506と、第2の走査線7507と、信号線7508と、電源線7509と、配線7510とを有している。なお、駆動トランジスタ7501にはNチャネル型トランジスタを用いている。

30

#### 【0277】

駆動トランジスタ7501のソース端子は発光素子7505の陽極(画素電極)と接続され、ゲート端子は容量素子7502を介して信号線7508と接続され、ドレイン端子は第1のスイッチ7503を介して電源線7509と接続されている。なお、電源線7509には電源電位Vddが設定されている。また、駆動トランジスタ7501のゲート端子とドレイン端子は第2のスイッチ7504を介して接続されている。よって第2のスイッチ7504がオンしているときには駆動トランジスタ7501のゲート端子とドレイン端子は導通する。そして、第2のスイッチ7504がオフすると、駆動トランジスタ7501のゲート端子とドレイン端子は非導通となり、その瞬間の駆動トランジスタ7501のゲート端子(ドレイン端子)と信号線7508との電位差(電圧)を容量素子7502は保持することができる。また、発光素子7505の陰極はVssの電位が設定された配線7510と接続されている。なお、Vssとは $V_{ss} < V_{dd}$ を満たす電位である。例えば、 $V_{ss} = GND$ (グラウンド電位)としても良い。

40

#### 【0278】

次に、図75の画素の動作原理について説明する。

#### 【0279】

画素の信号書き込み期間に、第1の走査線7506及び第2の走査線7507に信号を入

50

力し、第1のスイッチ7503及び第2のスイッチ7504をオンさせる。すると、駆動トランジスタ7501のドレイン端子とゲート端子に電源線7509の電源電位( $V_{dd}$ )が設定される。そして、容量素子7502、駆動トランジスタ7501及び発光素子7505に電流が流れ、容量素子7502では電荷の蓄積又は放電が行われる。なお、画素への信号書き込み期間には、信号線7508にはアナログ信号電位が設定される。このアナログ信号電位はビデオ信号に相当する。

#### 【0280】

やがて、容量素子7502には電流が流れなくなる。そして、駆動トランジスタ7501及び発光素子7505に電流が流れる。なぜなら、このとき駆動トランジスタ7501のゲート端子は、第2のスイッチ7504によってドレイン端子と導通されているため、ゲート端子の電位は、電源電位( $V_{dd}$ )となり駆動トランジスタ7501はオンしているからである。10

#### 【0281】

この状態で、第1のスイッチ7503をオフにすると、駆動トランジスタ7501と容量素子7502に電流が流れ、やがて、駆動トランジスタ7501及び容量素子7502に電流が流れなくなる。こうして、駆動トランジスタ7501はオフする。このとき、駆動トランジスタ7501のゲートソース間電圧 $V_{gs}$ はしきい値電圧 $V_{th}$ に概ね等しくなっている。

#### 【0282】

そして、この状態になったら第2のスイッチ7504をオフする。すると、容量素子7502には、駆動トランジスタ7501がオフするゲート端子の電位と、第2のスイッチ7504をオフにした瞬間の信号線7508に設定されているアナログ信号電位との電位差( $V_p$ )が保持される。こうして画素にアナログ信号が書き込まれる。20

#### 【0283】

なお、上述した第1のスイッチ7503のオンオフを制御する信号は第1の走査線7506に、第2のスイッチ7504のオンオフを制御する信号は第2の走査線7507にパルス信号を入力して行うことができる。

#### 【0284】

なお、画素にアナログ信号が書き込まれると、その際信号線7508に設定されたアナログ信号電位を基準にして、信号線7508の電位の変動に従って駆動トランジスタ7501のオンオフが制御されるようになる。つまり、信号線7508の電位が、信号書き込み期間に画素に書き込まれた際のアナログ信号電位以下のときには駆動トランジスタ7501はオフし、画素にアナログ信号が書き込まれた際のアナログ信号電位より高くなると駆動トランジスタ7501はオンする。30

#### 【0285】