(19)日本国特許庁(JP)

## (12)公開特許公報(A)

(11)公開番号

特開2023-138318

(P2023-138318A)

(43)公開日 令和5年10月2日(2023.10.2)

| (51)国際特許分類 |                   | F I    | テーマコード(参考) |         |           |

|------------|-------------------|--------|------------|---------|-----------|

| H 01 L     | 21/822 (2006.01)  | H 01 L | 27/04      | H       | 5 F 0 3 8 |

| H 01 L     | 21/8234 (2006.01) | H 01 L | 27/06      | 1 0 2 A | 5 F 0 4 8 |

| H 01 L     | 27/06 (2006.01)   | H 01 L | 27/06      | 3 1 1 B | 5 G 0 5 3 |

| H 02 H     | 7/20 (2006.01)    | H 02 H | 7/20       | F       |           |

審査請求 未請求 請求項の数 11 O L (全17頁)

|                   |                             |           |                                                  |

|-------------------|-----------------------------|-----------|--------------------------------------------------|

| (21)出願番号          | 特願2022-209355(P2022-209355) | (71)出願人   | 715010864                                        |

| (22)出願日           | 令和4年12月27日(2022.12.27)      |           | エイブリック株式会社                                       |

| (31)優先権主張番号       | 特願2022-43270(P2022-43270)   |           | 長野県北佐久郡御代田町大字御代田 4 1                             |

| (32)優先日           | 令和4年3月18日(2022.3.18)        |           | 0 6 番地 7 3                                       |

| (33)優先権主張国・地域又は機関 | 日本国(JP)                     | (72)発明者   | 津村 和宏                                            |

|                   |                             |           | 東京都港区三田三丁目 9 番 6 号 エイブ                           |

|                   |                             |           | リック株式会社内                                         |

|                   |                             | F ターム(参考) | 5F038 AV04 AV05 AV06 BH06<br>BH07 BH13           |

|                   |                             |           | 5F048 AB10 AC01 AC10 BA01<br>BG12 CC06 CC09 CC15 |

|                   |                             |           | 5G053 AA11 CA05 EC02                             |

(54)【発明の名称】 ESD保護回路及び半導体装置

## (57)【要約】

【課題】被保護回路の動作電圧及び破壊電圧に応じたESD保護回路の提供。

【解決手段】 $V_{DD}$ 端子と $V_{SS}$ 端子との間に接続され、動作電圧で動作し、かつ破壊電圧以上で破壊される内部回路Cと並列に接続して内部回路Cを静電気放電から保護するESD保護回路100であって、直列に接続されている複数のESD保護素子110, 120を有し、複数のESD保護素子110, 120は、トランジスタ、ダイオード素子又はこれらの組合せであり、動作電圧よりも高い電圧における複数のESD保護素子110, 120の電流-電圧特性の総和は、内部回路Cを保護し得る放電電流値以上になるまで、動作電圧よりも高くかつ破壊電圧よりも低い。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

第1の端子と第2の端子との間に接続され、動作電圧で動作し、かつ破壊電圧以上で破壊される被保護回路と並列に接続して前記被保護回路を静電気放電から保護するESD保護回路であって、

直列に接続されている複数のESD保護素子を有し、

前記複数のESD保護素子は、トランジスタ、ダイオード素子又はこれらの組合せであり、

前記動作電圧よりも高い電圧における前記複数のESD保護素子の電流-電圧特性の総和は、前記被保護回路を保護し得る放電電流値以上になるまで、前記動作電圧よりも高くかつ前記破壊電圧よりも低いことを特徴とするESD保護回路。10

**【請求項 2】**

前記複数のESD保護素子の電流-電圧特性の総和における降伏電圧は、前記動作電圧よりも高い、請求項1に記載のESD保護回路。

**【請求項 3】**

前記複数のESD保護素子は、前記トランジスタを含み、

前記複数のESD保護素子の電流-電圧特性の総和における保持電圧は、前記動作電圧よりも高い、請求項1に記載のESD保護回路。

**【請求項 4】**

前記トランジスタは、MOSトランジスタ又はバイポーラトランジスタである、請求項1に記載のESD保護回路。20

**【請求項 5】**

前記MOSトランジスタは、Nチャネル又はPチャネルであって、他の前記ESD保護素子とは耐圧が同等又は異なる、請求項4に記載のESD保護回路。

**【請求項 6】**

前記複数のESD保護素子は、Nチャネルの前記MOSトランジスタ及びPチャネルの前記MOSトランジスタのいずれも含む、請求項5に記載のESD保護回路。

**【請求項 7】**

前記MOSトランジスタがDMOS構造である、請求項4に記載のESD保護回路。

**【請求項 8】**

前記複数のESD保護素子は、前記トランジスタ及び前記ダイオード素子のいずれも含む、請求項1に記載のESD保護回路。30

**【請求項 9】**

前記ダイオード素子は、他の前記ESD保護素子とは耐圧が同等又は異なる、請求項1に記載のESD保護回路。

**【請求項 10】**

前記複数のESD保護素子のうち少なくとも1つの前記ESD保護素子の降伏電圧が他の前記ESD保護素子の降伏電圧と異なる、請求項1に記載のESD保護回路。

**【請求項 11】**

請求項1から10のいずれかに記載のESD保護回路と、前記ESD保護回路により静電気放電から保護される被保護回路とが並列に接続されていることを特徴とする半導体装置。40

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、ESD保護回路及び半導体装置に関する。

**【背景技術】****【0002】**

半導体集積回路は、静電気放電(ESD: Electro-Static Discharge)に弱く、容易に破壊されるおそれがある。具体的には、MOS(Metal-Oxide-Semiconductor)50

構造を有する素子が半導体集積回路に含まれていれば、ゲート絶縁膜破壊などのような電界的破壊を発生させることが多い。このため、半導体集積回路は、静電気放電から内部回路を保護するための ESD 保護回路を備えることが多い。

### 【 0 0 0 3 】

ESD 保護回路としては、例えば、降伏現象を利用したダイオード型 ESD 保護回路、NMOS (N チャネル MOS) トランジスタのスナップバック動作を利用した gg (gate grounded) NMOS 型 ESD 保護回路などが挙げられる。

### 【 0 0 0 4 】

ダイオード型 ESD 保護回路としては、例えば、内部回路と接続された外部接続端子と電源供給線などとの間に 2 以上の直列接続のダイオード列を接続することにより、ダイオードの個数に比例させて外部接続端子の許容される電圧範囲を拡大させるものが提案されている（特許文献 1 参照）。

10

### 【 0 0 0 5 】

gg NMOS 型 ESD 保護回路としては、例えば、複数の異なる電源電圧の電源端子間にそれぞれ ESD 保護素子を接続することにより、レイアウト面積を小さくできる ESD 保護回路が提案されている（特許文献 2 参照）。

20

### 【先行技術文献】

#### 【特許文献】

##### 【 0 0 0 6 】

【特許文献 1】特開 2003 - 23084 号公報

20

【特許文献 2】特開 2011 - 181848 号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

##### 【 0 0 0 7 】

そこで、本発明の一つの側面では、被保護回路の動作電圧及び破壊電圧に応じた ESD 保護回路を提供することを目的とする。

30

#### 【課題を解決するための手段】

##### 【 0 0 0 8 】

本発明の一実施形態における ESD 保護回路は、

第 1 の端子と第 2 の端子との間に接続され、動作電圧で動作し、かつ破壊電圧以上で破壊される被保護回路と並列に接続して前記被保護回路を静電気放電から保護する ESD 保護回路であって、

直列に接続されている複数の ESD 保護素子を有し、

前記複数の ESD 保護素子は、トランジスタ、ダイオード素子又はこれらの組合せであり、

前記動作電圧よりも高い電圧における前記複数の ESD 保護素子の電流 - 電圧特性の総和は、前記被保護回路を保護し得る放電電流値以上になるまで、前記動作電圧よりも高くかつ前記破壊電圧よりも低い。

30

#### 【発明の効果】

##### 【 0 0 0 9 】

本発明の一つの側面によれば、被保護回路の動作電圧及び破壊電圧に応じた ESD 保護回路を提供することができる。

40

#### 【図面の簡単な説明】

##### 【 0 0 1 0 】

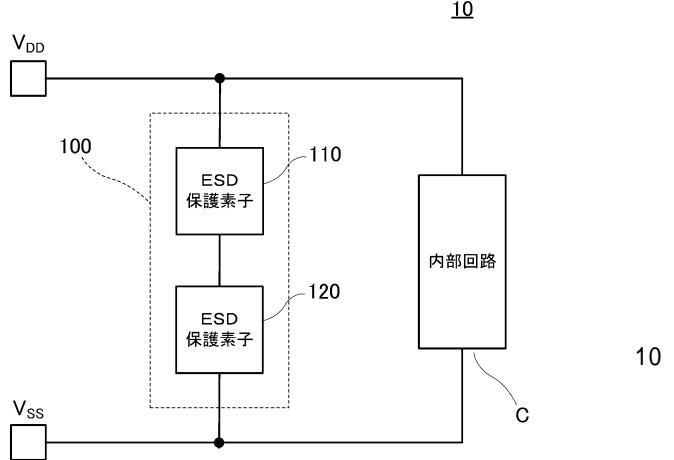

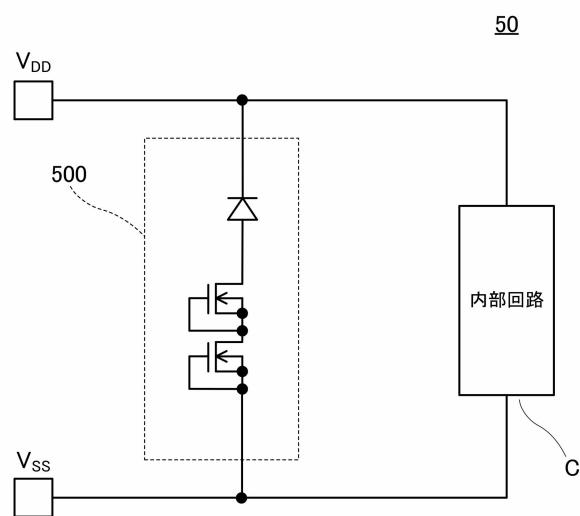

【図 1】図 1 は、本発明における ESD 保護回路及び半導体装置の一例を示す回路図である。

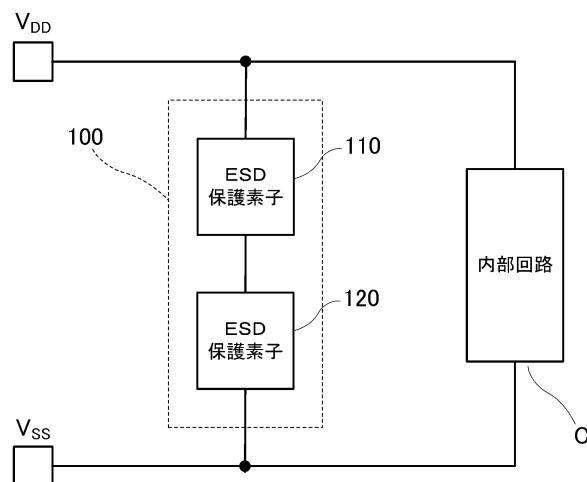

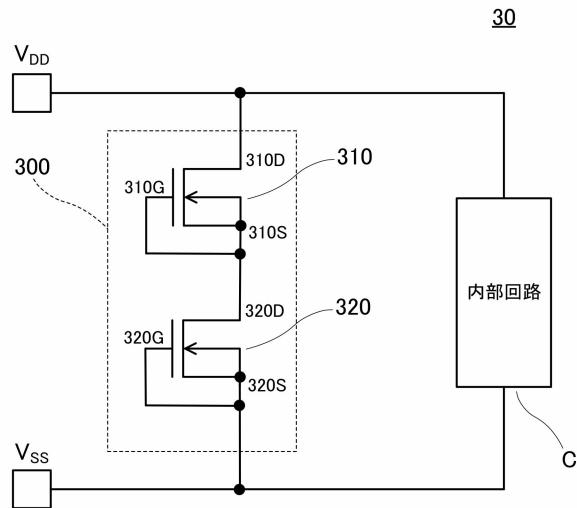

【図 2】図 2 は、第 1 の実施形態における ESD 保護回路及び半導体装置の一例を示す回路図である。

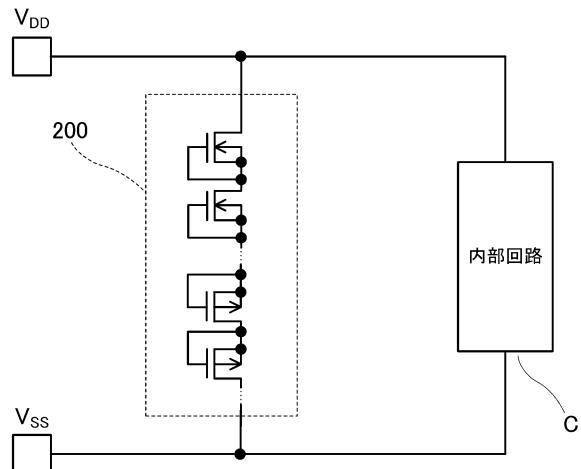

【図 3】図 3 は、ESD 保護素子が低耐圧 MOS トランジスタである場合の電流 - 電圧特性の一例を示すグラフである。

50

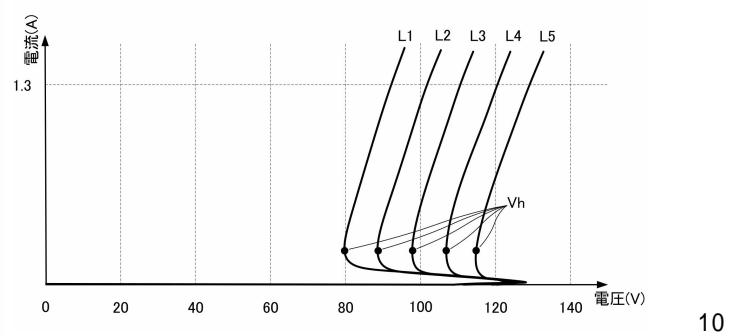

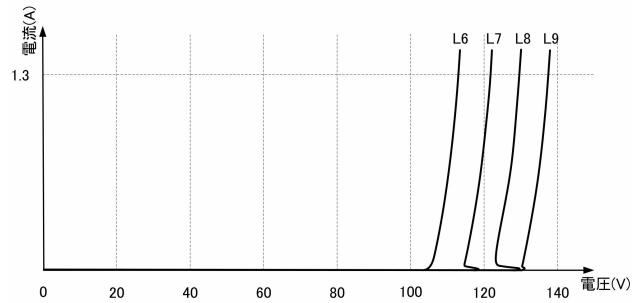

【図4】図4は、第1の実施形態におけるE S D保護回路の電流 - 電圧特性のいくつかの例を示すグラフである。

【図5】図5は、第2の実施形態におけるE S D保護回路及び半導体装置を示す回路図である。

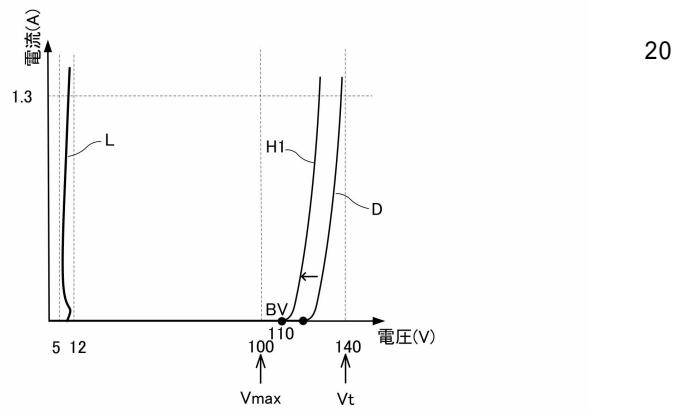

【図6A】図6Aは、第2の実施形態における高耐圧N M O Sトランジスタ及び低耐圧トランジスタの電流 - 電圧特性を示すグラフである。

【図6B】図6Bは、第2の実施形態における高耐圧N M O Sトランジスタ、低耐圧トランジスタ及びE S D保護回路の電流 - 電圧特性を示すグラフである。

【図7】図7は、第2の実施形態における高耐圧N M O Sトランジスタの構造の一例を示す概略断面図である。

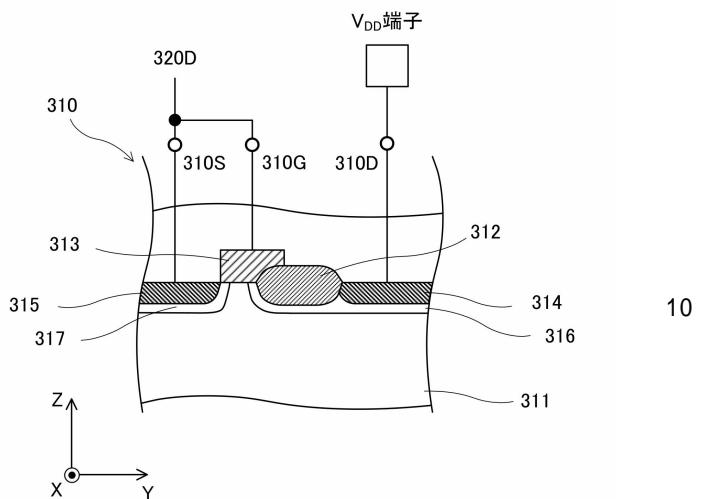

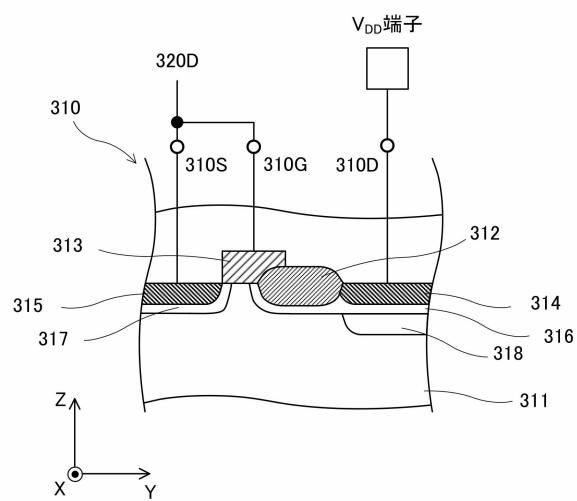

【図8】図8は、第2の実施形態における高耐圧N M O Sトランジスタの構造の別の一例を示す概略断面図である。

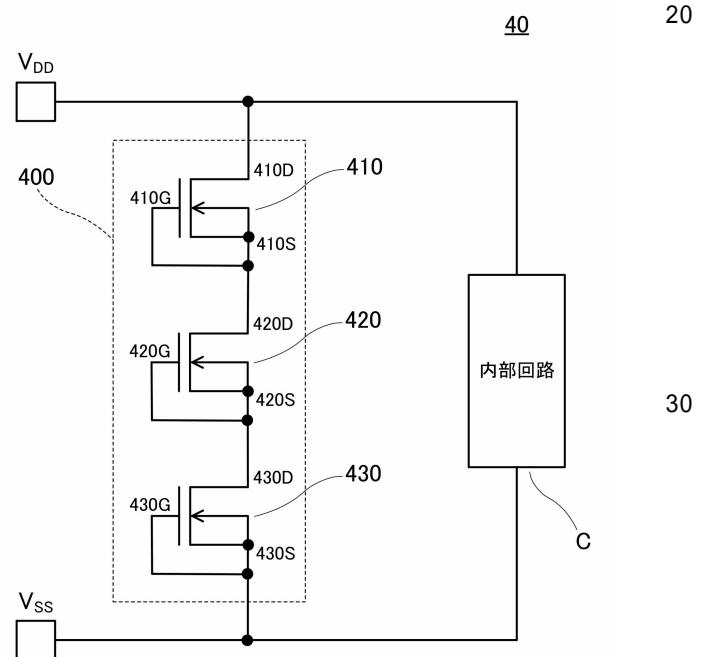

【図9】図9は、第2の実施形態の変形例におけるE S D保護回路及び半導体装置を示す回路図である。

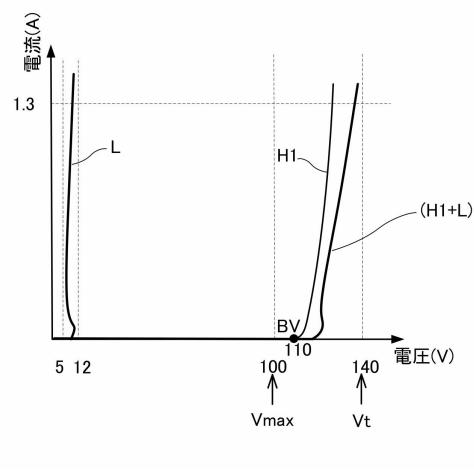

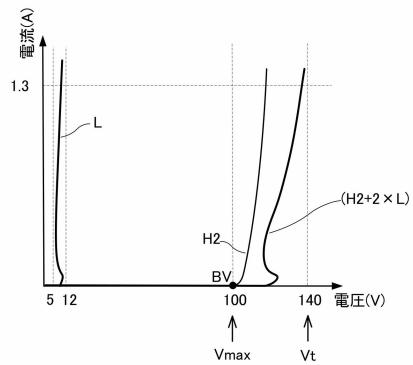

【図10】図10は、第2の実施形態の変形例における高耐圧N M O Sトランジスタ、低耐圧トランジスタ及びE S D保護回路の電流 - 電圧特性を示すグラフである。

【図11】図11は、第3の実施形態におけるE S D保護回路及び半導体装置を示す回路図である。

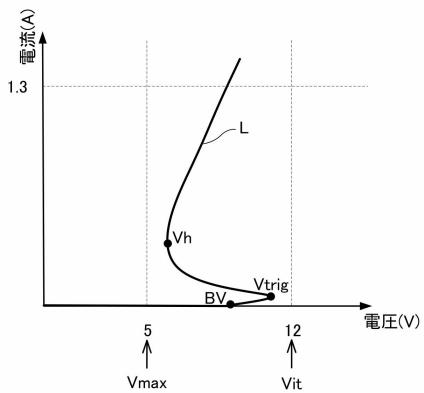

【図12】図12は、第3の実施形態におけるE S D保護回路の電流 - 電圧特性のいくつかの例を示すグラフである。

【図13】図13は、従来における低耐圧のE S D保護回路の電流 - 電圧特性を示すグラフである。

【図14】図14は、従来における低耐圧及び高耐圧のE S D保護回路の電流 - 電圧特性を示すグラフである。

#### 【発明を実施するための形態】

##### 【0011】

gg N M O S型E S D保護回路は、N M O S( NチャネルM O S )トランジスタのゲート及びソースが接地電位に接続されており、ドレインに接続された端子にプラスサージ電圧が印加されると、N M O Sトランジスタのドレイン端がブレイクダウンする。このブレイクダウンにより発生したアバランシェ電流と基板抵抗との積が、P N接合の拡散障壁電圧(約0.6V)を超えると、寄生のN P Nバイポーラトランジスタが動作する。この寄生バイポーラトランジスタの動作により、ドレイン - ソース間に放電電流が流れ始めると、ドレイン電圧は保持電圧V<sub>h</sub>まで一旦降下し、放電電流が徐々に大きくなるにつれて電圧も高くなる。

##### 【0012】

このようなスナップバック動作を利用するE S D保護回路は、スナップバック動作におけるトリガ電圧及び保持電圧を、被保護回路の動作電圧よりも高くかつ破壊電圧よりも低く設定しないと、被保護回路を保護できない場合がある。また、N M O Sトランジスタにおける寄生ダイオードの降伏電圧は、被保護回路の動作時におけるリーク電流を低減できる点で、動作電圧よりも高く設定することが好ましい。

なお、動作電圧とは、被保護回路が動作できる所定の電圧であり、例えば仕様書に記載の最小動作電圧から最大動作電圧までの範囲内に限らず、実質的に動作する電圧の範囲内も含む。具体的には、実質的な最大動作電圧が30V、E S D保護回路における最低起動電圧が35Vであるにもかかわらず、仕様書では最大動作電圧が40Vと規定されている場合には、実質的に動作する電圧を考慮する。また、破壊電圧とは、被保護回路が破壊し得る電圧をいう。降伏電圧よりも高くなるトリガ電圧は、被保護回路の破壊電圧よりも高いと被保護回路を破壊してしまう。保持電圧が最大動作電圧よりも低くなり、寄生のN P Nバイポーラトランジスタが一旦動作すると、サージ電圧の印加後も引き続き寄生のN P Nバイポーラトランジスタによる電流が流れ続ける。

##### 【0013】

10

20

30

40

50

降伏電圧、トリガ電圧及び保持電圧の全てを、被保護回路の最大動作電圧よりも高く、かつ被保護回路の破壊電圧よりも低く設定することは、低耐圧の被保護回路に対しては実現が容易であるが、高耐圧の被保護回路に対しては実現が困難なところがある。

#### 【0014】

例えば、最大動作電圧が5Vで破壊電圧が12Vである低耐圧の被保護回路に対し、図13のLで示すように、降伏電圧BV、トリガ電圧V<sub>trig</sub>及び保持電圧V<sub>h</sub>の全てを、被保護回路の最大動作電圧V<sub>max</sub>よりも高くかつ破壊電圧V<sub>int</sub>よりも低く設定することは容易である。

具体的には、耐圧が5VのN MOSトランジスタをggN MOS型ESD保護回路に適用すると、降伏電圧BVが9V、トリガ電圧V<sub>trig</sub>が11V、保持電圧V<sub>h</sub>が6Vになり、これら3つのパラメータを最大動作電圧V<sub>max</sub>の5Vよりも高くかつ破壊電圧V<sub>int</sub>の12Vよりも低くすることは容易である。このような低耐圧のESD保護回路は、レイアウト面積を70μm×70μm程度にすることができる。10

#### 【0015】

次に、最大動作電圧V<sub>max</sub>が100Vで破壊電圧V<sub>int</sub>が140Vである高耐圧の被保護回路に対し、寄生バイポーラトランジスタのコレクタ-エミッタ間抵抗を高くする構造を採用する場合を考える。この場合には、降伏電圧BVを120Vに設定すると、図14のAで示すようになり、図14のスケールで示した図13のLと比較すると、保持電圧V<sub>h</sub>は十分高くならないことが多い。20

#### 【0016】

保持電圧V<sub>h</sub>を被保護回路の最大動作電圧V<sub>max</sub>よりも高くしようとすると、スナップバック動作が生じても、寄生バイポーラトランジスタのコレクタ-エミッタ間抵抗が高くなりすぎて大きな放電電流を流せなくなるため、図14のBで示すように、被保護回路が破壊されてしまう。これに対し、寄生ダイオードの降伏電圧を高くすると、図14のCで示すように、トリガ電圧が被保護回路の破壊電圧よりも高くなってしまい、被保護回路が破壊されてしまう。20

#### 【0017】

ゲート幅Wを広くすると、図14のDで示すように、スナップバック動作が生じることなく徐々に電圧が高くなりながら電流が1.3Aに達する。このようにするとESD保護回路として機能することができるが、最大動作電圧が100V程度の高耐圧の被保護回路に対し、レイアウト面積が400μm×400μmを超えるような大きさになってしまう。30

#### 【0018】

そこで、本発明の一実施態様のESD保護回路は、被保護回路の動作電圧及び破壊電圧に応じて、複数のESD保護素子を組み合わせるようにした。

#### 【0019】

以下、本発明の実施形態について、図面を参照しながら詳細に説明する。

なお、図面においては、同一構成部分には同一符号を付し、重複した説明を省略する場合がある。

また、図面に示すX軸、Y軸及びZ軸は互いに直交するものとする。X軸方向を「幅方向」、Y軸方向を「奥行き方向」、Z軸方向を「高さ方向」又は「厚さ方向」と称する場合がある。各膜の+Z方向側の面を「表面」又は「上面」、-Z方向側の面を「裏面」又は「下面」と称する場合がある。40

さらに、図面は模式的なものであり、幅、奥行き及び厚さの比率などは示したとおりではない。複数の膜若しくは層、又はこれらを構造的に組み合わせて得られる半導体素子の数量、位置、形状、構造、大きさなどは、以下に示す実施形態に限定されず、本発明を実施する上で好ましい数量、位置、形状、構造、大きさなどにすることができる。

#### 【0020】

図1は、本発明におけるESD保護回路及び半導体装置の一例を示す回路図である。

図1に示すように、本発明の一実施態様の半導体装置10は、ESD保護回路100と50

、内部回路Cとを有する。

本発明の一実施態様のESD保護回路100は、第1の端子としてのV<sub>DD</sub>端子と第2の端子としてのV<sub>SS</sub>端子との間に接続されており、内部回路Cと並列に接続されている。

#### 【0021】

内部回路Cは、ESD保護回路100により静電気放電から保護される被保護回路であり、V<sub>DD</sub>端子と接地電位のV<sub>SS</sub>端子との間に印加されている動作電圧で動作する。内部回路Cは、所定の最大動作電圧V<sub>max</sub>以下の動作電圧で動作し、かつ所定の破壊電圧V<sub>int</sub>以上で破壊され得る。

#### 【0022】

ESD保護回路100は、内部回路Cが静電気放電で破壊しないように保護する回路である。このESD保護回路100は、直列に接続されている複数のESD保護素子110, 120を有する。

ESD保護素子110, 120は、MOSトランジスタ、ダイオード素子又はこれらの組合せである。つまり、ESD保護素子110, 120は、いずれもMOSトランジスタとしてもよく、いずれもダイオード素子としてもよく、MOSトランジスタ及びダイオード素子の組合せとしてもよい。ESD保護素子110, 120を適宜選択することにより、内部回路Cを保護し得る放電電流の範囲において、ESD保護素子110, 120の電流-電圧特性の総和を、内部回路Cの動作電圧よりも高くかつ破壊電圧よりも低くしている。

これにより、ESD保護回路100は、内部回路Cの動作電圧及び破壊電圧に応じた電流-電圧特性を得ることができ、内部回路Cの動作を妨げることなく静電気放電による破壊を回避することができる。

#### 【0023】

なお、図1では、複数のESD保護素子をESD保護素子110, 120の2つとしたが、これに限ることなく、少なくとも2以上のESD保護素子を組み合わせるようにしてもよい。

また、複数のESD保護素子の電流-電圧特性の総和を内部回路の動作電圧よりも高くかつ破壊電圧よりも低くできれば、MOSトランジスタは、NチャネルであってもPチャネルであってもよく、他のESD保護素子とは耐圧が同等であっても相違してもよい。ダイオード素子は、他のESD保護素子とは耐圧が同等であっても相違してもよい。

#### 【0024】

これらのバリエーションを説明するため、以下では3つの実施形態を挙げる。

第1の実施形態では、低耐圧NMOSトランジスタと低耐圧PMOS(PチャネルMOS)トランジスタを組み合わせたESD保護回路について説明する。

第2の実施形態及びその変形例では、高耐圧NMOSトランジスタと低耐圧NMOSトランジスタを組み合わせたESD保護回路について説明する。

第3の実施形態では、高耐圧ダイオード素子と低耐圧MOSトランジスタを組み合わせたESD保護回路について説明する。

#### 【0025】

なお、各実施形態では、「低耐圧」を5V近傍の電圧とし、「高耐圧」を100V近傍の電圧とするが、これに限ることはない。

また、各実施形態における「内部回路を保護し得る放電電流値」は、HBM(Human Body Model)で2kVの静電気放電から保護するために1.3Aの放電電流を流すことができればよいことから1.3Aとするが、これに限ることはない。

#### 【0026】

##### (第1の実施形態)

図2は、第1の実施形態におけるESD保護回路及び半導体装置の一例を示す回路図である。

第1の実施形態における半導体装置20のESD保護回路200は、低耐圧NMOSト

10

20

30

40

50

ランジスタ及び低耐圧PMOSトランジスタから適宜選択して計12個になるようにして、これらを直列に接続して形成されている。

なお、図2では、ESD保護回路200が低耐圧NMOSトランジスタ及び低耐圧PMOSトランジスタの両方を直列に接続して形成しているものを示す。低耐圧NMOSトランジスタ及び低耐圧PMOSトランジスタは、いわゆるダイオード接続をしており、ソース端子にゲート端子がそれぞれ接続されている。

また、図2では、V<sub>DD</sub>端子側に低耐圧NMOSトランジスタを配置し、V<sub>SS</sub>端子側に低耐圧PMOSトランジスタを配置しているが、V<sub>DD</sub>端子側に低耐圧PMOSトランジスタを配置し、V<sub>SS</sub>端子側に低耐圧NMOSトランジスタを配置してもよい。どちらの場合も同等の降伏電圧BV、トリガ電圧V<sub>trig</sub>及び保持電圧V<sub>h</sub>が得られる。ただし、ESD耐量は、並び順によって変わるので好みの並び順を選択する。

10

さらに、並び順については、MOSトランジスタのNチャネルかPチャネルだけではなく、各ESD保護素子の並び順によってESD耐量が異なる場合があるため、適宜選択することが好み。

#### 【0027】

図3は、ESD保護素子が低耐圧MOSトランジスタである場合の電流-電圧特性の一例を示すグラフである。

ESD保護素子が低耐圧NMOSトランジスタである場合には、その電流-電圧特性は図3中のL<sub>n</sub>に示すようになる。また、ESD保護素子が低耐圧PMOSトランジスタである場合には、図3中のL<sub>p</sub>に示すようになる。

20

L<sub>n</sub>及びL<sub>p</sub>を比較すると、NMOSトランジスタのほうがPMOSトランジスタよりもスナップバック動作が大きく保持電圧V<sub>h</sub>が低くなり、1.3Aを流す電圧が低くなる。また、その逆であるが、PMOSトランジスタのほうがNMOSトランジスタよりもスナップバック動作が小さく保持電圧V<sub>h</sub>が高くなり、1.3Aを流す電圧が高くなる。

#### 【0028】

次に、低耐圧NMOSトランジスタと低耐圧PMOSトランジスタを組み合わせたESD保護回路200の電流-電圧特性について説明する。

図4は、第1の実施形態におけるESD保護回路の電流-電圧特性のいくつかの例を示すグラフである。図4中のL1～L5は、低耐圧NMOSトランジスタ及び低耐圧PMOSトランジスタをそれぞれ以下の数量で直列に接続して形成したESD保護回路200の電流-電圧特性である。

30

L1：低耐圧NMOSトランジスタ12個

L2：低耐圧NMOSトランジスタ9個、低耐圧PMOSトランジスタ3個

L3：低耐圧NMOSトランジスタ6個、低耐圧PMOSトランジスタ6個

L4：低耐圧NMOSトランジスタ3個、低耐圧PMOSトランジスタ9個

L5：低耐圧PMOSトランジスタ12個

#### 【0029】

図4に示すように、ESD保護回路200の電流-電圧特性は、低耐圧NMOSトランジスタの割合が大きいほどスナップバック動作が大きくなるため、保持電圧V<sub>h</sub>が低くなる。

40

これにより、低耐圧NMOSトランジスタの割合が大きいESD保護回路200は、保持電圧V<sub>h</sub>が内部回路Cの動作電圧よりも高ければ、HBMで2kVの静電気放電から保護するために必要な1.3Aの放電電流を流せる電圧を内部回路Cの破壊電圧よりも容易に低くできる。さらに、ESD保護回路200は、保持電圧V<sub>h</sub>を内部回路Cの動作電圧近傍まで低く調整できれば、静電気放電による放電電圧が内部回路Cの破壊電圧に近づく前に放電電流が流れやすくなり、静電気放電から内部回路Cをより確実に保護することができる。

#### 【0030】

このような観点から、たとえば、内部回路Cの破壊電圧が140Vであり、内部回路C

の動作電圧が 70 V の場合には、図 4 中の L 1 で示した電流 - 電圧特性が最適であるため、E S D 保護回路 200 は、低耐圧 N M O S ドランジスタ 12 個により形成されていることが好ましい。また、内部回路 C の動作電圧が 90 V の場合には、図 4 中の L 3 で示した電流 - 電圧特性が最適であるため、E S D 保護回路 200 は、低耐圧 N M O S ドランジスタ 6 個及び低耐圧 P M O S ドランジスタ 6 個により形成されていることが好ましい。さらに、内部回路 C の動作電圧が 100 V の場合には、図 4 中の L 4 で示した電流 - 電圧特性が最適であるため、E S D 保護回路 200 は、低耐圧 N M O S ドランジスタ 3 個及び低耐圧 P M O S ドランジスタ 9 個により形成されていることが好ましい。

### 【 0 0 3 1 】

このように、第 1 の実施形態における E S D 保護回路 200 は、低耐圧 N M O S ドランジスタと低耐圧 P M O S ドランジスタを組み合わせることにより、内部回路 C の動作電圧及び破壊電圧に応じた電流 - 電圧特性を得ることができる。特に、E S D 保護回路 200 は、低耐圧 N M O S ドランジスタの割合を大きくするとスナップバック動作が大きくなることから、内部回路 C を保護するために必要な放電電流をより低い電圧で流すことができるため、内部回路 C をより確実に保護することができる。

なお、第 1 の実施形態では 12 個の低耐圧 M O S ドランジスタを用いたが、その個数に限ることなく、複数の M O S ドランジスタを用いて最適な電流 - 電圧特性が得られればよい。

### 【 0 0 3 2 】

#### ( 第 2 の実施形態 )

図 5 は、第 2 の実施形態における E S D 保護回路及び半導体装置を示す回路図である。

図 5 に示すように、第 2 の実施形態における半導体装置 30 は、第 1 の実施形態における半導体装置 20 の E S D 保護回路 200 を、耐圧が相違する 2 個の N M O S ドランジスタで形成された E S D 保護回路 300 に置き換えた以外は、第 1 の実施形態と同様である。このため、以下では E S D 保護回路 300 についての詳細を説明する。

### 【 0 0 3 3 】

E S D 保護回路 300 は、高耐圧 N M O S ドランジスタ 310 及び低耐圧 N M O S ドランジスタ 320 を直列に接続して形成されている。

高耐圧 N M O S ドランジスタ 310 は、V D D 端子にドレイン 310 D が接続されている。

低耐圧 N M O S ドランジスタ 320 は、高耐圧 N M O S ドランジスタ 310 のソース 310 S 及びゲート 310 G にドレイン 320 D が接続され、ソース 320 S 及びゲート 320 G が V S S 端子に接続されている。

なお、図 5 では、V D D 端子側に高耐圧 N M O S ドランジスタ 310 を配置し、V S S 端子側に低耐圧 N M O S ドランジスタ 320 を配置しているが、V D D 端子側に低耐圧 N M O S ドランジスタ 320 を配置し、V S S 端子側に高耐圧 N M O S ドランジスタ 310 を配置してもよい。どちらの場合も同等の降伏電圧 B V 、トリガ電圧 V t r i g 及び保持電圧 V h が得られる。ただし、E S D 耐量は、並び順によって変わるので好ましい並び順を選択する。

### 【 0 0 3 4 】

図 6 A は、第 2 の実施形態における高耐圧 N M O S ドランジスタ及び低耐圧トランジスタの電流 - 電圧特性を示すグラフである。

図 6 A の H 1 に示すように、高耐圧 N M O S ドランジスタ 310 は、コレクタ - エミッタ間抵抗を高くすることにより、降伏電圧 B V が 110 V に設定されている。これにより、高耐圧 N M O S ドランジスタ 310 は、降伏電圧 B V が内部回路 C の最大動作電圧 V m a x である 100 V より高いため、内部回路 C の動作時におけるリーク電流を低減することができる。

### 【 0 0 3 5 】

また、高耐圧 N M O S ドランジスタ 310 は、ゲート幅 W を広くしているためダイオードのような電流 - 電圧特性となり、内部回路 C の破壊電圧 V i t である 140 V より低い

10

20

30

40

50

範囲で電流が 1 . 3 A に達するようにしている。言い換えると、高耐圧 N M O S トランジスタ 3 1 0 の電流 - 電圧特性は、図 1 4 の D で示した電流 - 電圧特性を 1 0 V 低くシフトさせたものであり、製造プロセスの変更なく実現できる。また、高耐圧 N M O S トランジスタ 3 1 0 は、図 1 4 の D で示した電流 - 電圧特性の N M O S トランジスタよりも、電流 - 電圧特性を 1 0 V 低くシフトさせた分だけレイアウト面積を小さくすることができ、 $20 \mu m \times 200 \mu m$  程度にすることができる。

#### 【 0 0 3 6 】

図 6 A の L に示すように、低耐圧 N M O S トランジスタ 3 2 0 の電流 - 電圧特性は、図 1 3 及び図 1 4 の L で示した電流 - 電圧特性と同様である。

したがって、低耐圧 N M O S トランジスタ 3 2 0 のレイアウト面積は、 $70 \mu m \times 70 \mu m$  程度にすることができる。10

#### 【 0 0 3 7 】

E S D 保護回路 3 0 0 の電流 - 電圧特性は、高耐圧 N M O S トランジスタ 3 1 0 の電流 - 電圧特性に、低耐圧 N M O S トランジスタ 3 2 0 の電流 - 電圧特性を加算したものになり、図 6 B の ( H 1 + L ) で示すようになる。つまり、この ( H 1 + L ) で示す E S D 保護回路 3 0 0 の電流 - 電圧特性は、静電気放電から保護するために必要な 1 . 3 A に達するまで、最大動作電圧 V m a x である 1 0 0 V よりも高くかつ破壊電圧 V i t である 1 4 0 V よりも低い範囲内となる。これにより、E S D 保護回路 3 0 0 は、内部回路 C を静電気放電から保護することができる。

#### 【 0 0 3 8 】

また、E S D 保護回路 3 0 0 のレイアウト面積は、高耐圧 N M O S トランジスタ 3 1 0 の  $200 \mu m \times 200 \mu m$  ( $40,000 \mu m^2$ ) に、低耐圧 N M O S トランジスタ 3 2 0 の  $70 \mu m \times 70 \mu m$  ( $4,900 \mu m^2$ ) を加えて求めることができる。すると、図 1 4 の D で示した電流 - 電圧特性に係る M O S トランジスタのレイアウト面積である  $400 \mu m \times 400 \mu m$  ( $160,000 \mu m^2$ ) に対し、E S D 保護回路 3 0 0 のレイアウト面積のほうが 7 0 % ほど小さくすることができる。

#### 【 0 0 3 9 】

このように、E S D 保護回路 3 0 0 は、内部回路 C を静電気放電から保護することができ、かつ高耐圧の内部回路 C であってもレイアウト面積を小さくすることができる。

#### 【 0 0 4 0 】

次に、高耐圧 N M O S トランジスタ 3 1 0 の構造の例について、図 7 及び図 8 を参照しながら説明する。30

#### 【 0 0 4 1 】

図 7 は、第 2 の実施形態における高耐圧 N M O S トランジスタの構造の一例を示す概略断面図である。

図 7 に示したように、高耐圧 N M O S トランジスタ 3 1 0 は、いわゆる D M O S ( Double-diffused MOS ) 構造である。

#### 【 0 0 4 2 】

具体的には、N 型の半導体基板 3 1 1 の表面には、フィールド酸化膜としての L O C O S ( Local Oxidation of Silicon ) 3 1 2 が形成されている。ゲート電極 3 1 3 は、L O C O S 3 1 2 の一部を覆うように、ポリシリコンで形成されている。40

半導体基板 3 1 1 の上部には、平面視した際に L O C O S 3 1 2 及びゲート電極 3 1 3 を挟むように、ドレイン領域 3 1 4 及びソース領域 3 1 5 が N 型高濃度領域としてそれぞれ形成されている。N 型のドリフト層 3 1 6 は、半導体基板 3 1 1 の内部において、L O C O S 3 1 2 及びドレイン領域 3 1 4 のそれぞれの底面及び側面の周囲に接するように形成されている。P 型のウェル層 3 1 7 は、ソース領域 3 1 5 の底面及び側面の周囲に接するように形成されている。

ゲート電極 3 1 3 、ドレイン領域 3 1 4 及びソース領域 3 1 5 は、それぞれゲート 3 1 0 G 、ドレイン 3 1 0 D 及びソース 3 1 0 S に接続されている。

#### 【 0 0 4 3 】

20

30

40

50

高耐圧N MOSトランジスタ310がこのようなDMOS構造であると、LOCOS312のY軸方向における長さにより耐圧を容易に調整できる点で有利である。

#### 【0044】

また、図8に示すように、N型のドリフト層316の底面の一部に接する、又は少なくとも一部が重なるようにN型の低濃度領域318が形成されている構造としてもよい。図8に示す構造であると、LOCOS312のY軸方向における長さを変えずに、低濃度領域318のY軸方向における長さにより耐圧を調整することができるとともに、サージ電圧耐量を向上させることができる。

#### 【0045】

なお、本実施形態では、高耐圧N MOSトランジスタの構造をDMOS構造としたが、これに限ることなく、例えば、LD MOS (Laterally Double Diffused MOS)構造、LDD (Lightly Doped Drain)構造などとしてもよい。10

また、各MOSトランジスタには、サリサイドプロック領域を形成してもよい。

さらに、本実施形態では、高耐圧及び低耐圧のMOSトランジスタとしてNチャネルのMOSトランジスタを用いたが、これに限ることなく、高耐圧及び低耐圧の少なくともいずれかをPチャネルのMOSトランジスタとしてもよい。これにより、保持電圧V<sub>h</sub>を高くすることができる。

#### 【0046】

(第2の実施形態の変形例)

図9は、第2の実施形態の変形例におけるESD保護回路及び半導体装置を示す回路図である。20

図9に示すように、第2の実施形態の変形例における半導体装置40は、図5に示したESD保護回路300において高耐圧N MOSトランジスタ310の降伏電圧BVを100Vに設定し、低耐圧N MOSトランジスタ320とV<sub>SS</sub>端子との間に低耐圧N MOSトランジスタ330を更に直列接続した以外は、半導体装置30と同様である。

また、低耐圧N MOSトランジスタ420, 430は、低耐圧N MOSトランジスタ320と同様の構造及び電流-電圧特性である。

すなわち、第2の実施形態の変形例におけるESD保護回路400は、第2の実施形態のESD保護回路300において、高耐圧N MOSトランジスタ310を100Vに降伏電圧BVを設定した高耐圧N MOSトランジスタ410に置き換えるとともに、低耐圧N MOSトランジスタ320と同様の低耐圧N MOSトランジスタ430を、低耐圧N MOSトランジスタ320とV<sub>SS</sub>端子との間に更に直列接続した以外は、ESD保護回路300と同様である。30

#### 【0047】

図10は、第2の実施形態の変形例における高耐圧N MOSトランジスタ、低耐圧トランジスタ及びESD保護回路の電流-電圧特性を示すグラフである。

図10において、H2は降伏電圧BVを100Vに設定した高耐圧N MOSトランジスタ410の電流-電圧特性を示し、Lは低耐圧N MOSトランジスタ420及び低耐圧N MOSトランジスタ430の電流-電圧特性を示す。

#### 【0048】

図10のH2に示すように、高耐圧N MOSトランジスタ410は、コレクタ-エミッタ間抵抗を高耐圧N MOSトランジスタ310よりも低くすることにより、降伏電圧BVが100Vに設定されている。また、高耐圧N MOSトランジスタ410は、高耐圧N MOSトランジスタ310と同様に、ゲート幅Wを広くしているが、高耐圧N MOSトランジスタ310よりも降伏電圧BVが低い分だけ狭くしている。言い換えると、高耐圧N MOSトランジスタ410の電流-電圧特性は、図14のDで示した電流-電圧特性を20V低くシフトさせたものであり、製造プロセスの変更なく実現できる。また、高耐圧N MOSトランジスタ410は、図14のDで示した電流-電圧特性のN MOSトランジスタよりも、電流-電圧特性を20V低くシフトさせた分だけレイアウト面積を小さくすることができ、150μm × 150μm程度にすることができる。4050

## 【0049】

低耐圧N MOSトランジスタ430の電流-電圧特性は、低耐圧N MOSトランジスタ320と同様に、図6A及び図6BなどのLで示した電流-電圧特性である。

したがって、低耐圧N MOSトランジスタ430のレイアウト面積は、低耐圧N MOSトランジスタ320と同様に、 $70\mu m \times 70\mu m$ 程度にすることができる。

## 【0050】

ESD保護回路400の電流-電圧特性は、高耐圧N MOSトランジスタ410の電流-電圧特性に、低耐圧N MOSトランジスタ420, 430の電流-電圧特性を加算したものになり、図10の( $H2 + 2 \times L$ )で示すようになる。つまり、この( $H2 + 2 \times L$ )で示すESD保護回路400の電流-電圧特性は、1.3Aに達するまで、最大動作電圧 $V_{max}$ である100V以上かつ破壊電圧 $V_{hit}$ である140V以下の範囲内となる。これにより、ESD保護回路400は、内部回路Cを静電気放電から保護することができる。

## 【0051】

また、ESD保護回路400のレイアウト面積は、高耐圧N MOSトランジスタ410の $150\mu m \times 150\mu m$ に、低耐圧N MOSトランジスタ320, 330の $70\mu m \times 70\mu m$ をそれぞれ加えて求めることができ、 $32,300\mu m^2$ となる。すると、図14のDで示した電流-電圧特性に係るMOSトランジスタのレイアウト面積である $400\mu m \times 400\mu m$ ( $160,000\mu m^2$ )に対し、ESD保護回路400のレイアウト面積のほうが80%ほど小さくすることができる。

このように、第2の実施形態の変形例では、第2の実施形態よりもMOSトランジスタの数が増えてもレイアウト面積を小さくすることができる。

## 【0052】

## (第3の実施形態)

図11は、第3の実施形態におけるESD保護回路及び半導体装置を示す回路図である。

図11に示すように、第3の実施形態におけるESD保護回路500及び半導体装置50は、複数のESD保護素子として少なくともダイオード素子を含む。

なお、図11では、ESD保護回路500が高耐圧ダイオード素子及び低耐圧N MOSトランジスタの両方を直列に接続して形成されているものを示す。低耐圧N MOSトランジスタは、いわゆるダイオード接続をしており、ソース端子にゲート端子がそれぞれ接続されている。

## 【0053】

次に、複数のESD保護素子に高耐圧ダイオード素子が含まれる場合のESD保護回路500の電流-電圧特性について説明する。

図12は、第3の実施形態におけるESD保護回路の電流-電圧特性のいくつかの例を示すグラフである。図4中のL6~L9は、高耐圧ダイオード素子、及び低耐圧N MOSトランジスタ又は低耐圧PMOSトランジスタをそれぞれ以下の数量で直列に接続して形成したESD保護回路500の電流-電圧特性である。

L6：高耐圧ダイオード素子1個

L7：高耐圧ダイオード素子1個、低耐圧N MOSトランジスタ1個

L8：高耐圧ダイオード素子1個、低耐圧N MOSトランジスタ2個

L9：高耐圧ダイオード素子1個、低耐圧PMOSトランジスタ2個

## 【0054】

図12に示すように、ESD保護回路500の電流-電圧特性は、低耐圧N MOSトランジスタ又は低耐圧PMOSトランジスタの個数で調整することができる。低耐圧N MOSトランジスタ及び低耐圧PMOSトランジスタは、降伏電圧BVが同等であるが、NチャネルのほうがPチャネルよりもスイッチバック動作が大きい。このため、低耐圧N MOSトランジスタを用いたESD保護回路500は、HBMで2kVの静電気放電から保護するために必要な1.3Aの放電電流を流せる電圧を低くすることができる。

10

20

30

40

50

これにより、低耐圧N M O Sトランジスタを用いたE S D保護回路5 0 0は、静電気放電による放電電圧が内部回路Cの破壊電圧に近づく前に放電電流が流れやすくなり、静電気放電から内部回路Cをより確実に保護することができる。

#### 【0 0 5 5】

このような観点から、たとえば、内部回路Cの破壊電圧が1 4 0 Vであり、内部回路Cの動作電圧が1 1 0 Vの場合には、図1 2中のL 7で示した電流-電圧特性が最適であるため、E S D保護回路5 0 0は、高耐圧ダイオード素子1個及び低耐圧N M O Sトランジスタ1個により形成されていることが好ましい。また、内部回路Cの動作電圧が1 2 0 Vの場合には、図1 2中のL 8で示した電流-電圧特性が最適であるため、E S D保護回路5 0 0は、高耐圧ダイオード素子1個及び低耐圧N M O Sトランジスタ2個により形成されていることが好ましい。さらに、内部回路Cの動作電圧が1 3 0 Vの場合には、図1 2中のL 9で示した電流-電圧特性が最適であるため、E S D保護回路5 0 0は、高耐圧ダイオード素子1個及び低耐圧P M O Sトランジスタ2個により形成されていることが好ましい。

10

#### 【0 0 5 6】

このように、第3の実施形態におけるE S D保護回路5 0 0は、高耐圧ダイオード素子に低耐圧N M O Sトランジスタ又は低耐圧P M O Sトランジスタを組み合わせることにより、内部回路Cの動作電圧及び破壊電圧に応じた電流-電圧特性を得ることができる。特に、E S D保護回路5 0 0は、低耐圧N M O Sトランジスタの個数を増やすとスナップバック動作が大きくなることから、内部回路Cを保護するために必要な放電電流をより低い電圧で流すことができるため、内部回路Cをより確実に保護することができる。

20

#### 【0 0 5 7】

なお、第3の実施形態では高耐圧ダイオード素子に低耐圧N M O Sトランジスタ又は低耐圧P M O Sトランジスタを組み合わせたが、高耐圧ダイオード素子に低耐圧N M O Sトランジスタ及び低耐圧P M O Sトランジスタを組み合わせてもよい。

また、第3の実施形態では高耐圧ダイオード素子としたが、これに限ることなく、低耐圧ダイオード素子としてもよく、高耐圧ダイオード素子と低耐圧ダイオード素子とを組み合わせてもよい。

#### 【0 0 5 8】

以上説明したように、本発明の各実施形態におけるE S D保護回路は、第1の端子と第2の端子との間に接続されており、動作電圧で動作し、かつ破壊電圧以上で破壊される被保護回路と並列に接続されている。このE S D保護回路は直列に接続されている複数のE S D保護素子を有し、複数のE S D保護素子はトランジスタ、ダイオード素子又はこれらの組合せである。複数のE S D保護素子を適宜選択することにより、動作電圧よりも高い電圧における複数のE S D保護素子の電流-電圧特性の総和を、被保護回路を保護し得る放電電流値以上になるまで、被保護回路の動作電圧よりも高くかつ破壊電圧よりも低くしている。

30

これにより、このE S D保護回路は、被保護回路の動作電圧及び破壊電圧に応じた電流-電圧特性を得ることができ、被保護回路の動作を妨げることなく静電気放電による破壊を回避することができる。

また、複数のE S D保護素子を組み合わせ、少なくとも1つのE S D保護素子の降伏電圧が他のE S D保護素子の降伏電圧と異なるようにすると、降伏電圧や保持電圧の微調整が可能となるため、被保護回路を保護しやすくなる。具体的には、降伏電圧が1 0 Vのトランジスタのみを組み合わせる場合には降伏電圧の総和は1 0 V刻みになるが、降伏電圧が1 5 Vのトランジスタを組み合わせると5 V刻みとなり微調整が可能となる。

40

#### 【0 0 5 9】

以上、本発明の実施形態について詳述したが、本発明はこれらの実施形態に限られるものではなく、この発明の要旨を逸脱しない範囲の設計等も含まれる。

具体的には、各実施形態では、第1の端子をV D D端子としたが、これに限ることなく、例えば、信号の入力端子、出力端子などとしてもよい。

また、各実施形態では、MOSトランジスタのスナップバックを利用、即ちMOSトランジスタの寄生バイポーラトランジスタの動作を利用したが、これに限ることなく、バイポーラトランジスタとしてもよい。

### 【0060】

さらに、各実施形態ではESD保護素子の並び順の例をいくつか示したが、並び順によってラッチアップ耐性などの別の特性が変わる場合があるため、ESDに関する特性以外のこととも踏まえて適宜選択することが好ましい。また、ラッチアップ耐性を向上させることができるとでは、各ESD保護素子間のシリコン半導体基板にDeep Trench Isolationと呼ばれる深い溝を形成することが好ましく、これにより各ESD保護素子間の距離を狭くすることもできる。各ESD保護素子においても、その形状及び構造チャネル幅や接合の周辺長や面積についても適宜選択することが好ましい。10

### 【符号の説明】

#### 【0061】

- 10, 20, 30, 40, 50 半導体装置

- 100, 200, 300, 400, 500 ESD保護回路

- 110, 120 ESD保護素子

- C 内部回路（被保護回路）

### 【図面】

【図1】

10

【図2】

20

40

50

【図3】

【図4】

【図5】

【図6 A】

30

40

50

【図 6 B】

【図 7】

【図 8】

【図 9】

40

50

10

20

30

【図 1 0】

【図 1 1】

【図 1 2】

【図 1 3】

20

30

40

50

【図 1 4】

10

20

30

40

50