(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4860143号

(P4860143)

(45) 発行日 平成24年1月25日(2012.1.25)

(24) 登録日 平成23年11月11日(2011.11.11)

(51) Int.Cl.

F 1

|             |              |                  |      |      |         |

|-------------|--------------|------------------|------|------|---------|

| <b>G09G</b> | <b>3/30</b>  | <b>(2006.01)</b> | G09G | 3/30 | J       |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20 | 6 1 1 H |

| <b>H01L</b> | <b>51/50</b> | <b>(2006.01)</b> | G09G | 3/20 | 6 2 2 C |

|             |              |                  | G09G | 3/20 | 6 2 2 D |

|             |              |                  | G09G | 3/20 | 6 2 2 G |

請求項の数 7 (全 26 頁) 最終頁に続く

(21) 出願番号

特願2004-356965 (P2004-356965)

(22) 出願日

平成16年12月9日 (2004.12.9)

(65) 公開番号

特開2005-202372 (P2005-202372A)

(43) 公開日

平成17年7月28日 (2005.7.28)

審査請求日

平成19年12月4日 (2007.12.4)

(31) 優先権主張番号

特願2003-423891 (P2003-423891)

(32) 優先日

平成15年12月19日 (2003.12.19)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 納 光明

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 安西 彩

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 山崎 優

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 福本 良太

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

アノード線と、カソード線と、信号線と、走査線と、画素と、アナログスイッチと、逆電圧印加用トランジスタと、を有し、

前記画素は、

ゲート電極が前記走査線に接続され、第1の電極が前記信号線に接続される第1のトランジスタと、

ゲート電極が前記第1のトランジスタの第2の電極に接続され、第1の電極が前記アノード線に接続される第2のトランジスタと、

ゲート電極がゲート固定電位線に接続され、第1の電極が前記第2のトランジスタの第2の電極に接続される第3のトランジスタと、

第1の電極が前記第3のトランジスタの第2の電極に接続され、第2の電極が前記カソード線に接続される発光素子と、

ゲート電極が前記アノード線に接続され、第1の電極が前記発光素子の第1の電極に接続され、第2の電極が前記ゲート固定電位線に接続される逆バイアス用トランジスタと、を有し、

前記アナログスイッチは、

ゲート電極が前記アノード線に接続される第4のトランジスタと、

ゲート電極が第1の電源線に接続される第5のトランジスタと、を有し、

前記第4のトランジスタの第1の電極と前記第5のトランジスタの第1の電極とは接続

10

20

されて前記アナログスイッチの入力となり、

前記第4のトランジスタの第2の電極と前記第5のトランジスタの第2の電極とは接続されて前記アナログスイッチの出力となり、

前記逆電圧印加用トランジスタのゲート電極は第2の電源線に接続され、

第1の電極は前記アノード線に接続され、第2の電極は前記アナログスイッチの出力と前記走査線に接続され、

順電圧印加期間においては、

前記第4のトランジスタをオン又はオフとし且つ前記第5のトランジスタをオフ又はオンとし前記アナログスイッチをオンとして、前記逆電圧印加用トランジスタをオフとし、

前記第3のトランジスタを飽和領域で駆動させることで定電流源として用いて、前記発光素子に順電圧を印加し、10

逆電圧印加期間においては、

前記第4のトランジスタ及び前記第5のトランジスタをオフとし前記アナログスイッチをオフとして、前記逆電圧印加用トランジスタをオンとし、

前記アノード線の電位と前記カソード線の電位を反転することで前記発光素子に逆電圧を印加し、

発光素子の第1の電極と第2の電極とが短絡している場合に前記逆バイアス用トランジスタがオンすることを特徴とする表示装置。

#### 【請求項2】

アノード線と、カソード線と、信号線と、走査線と、画素と、クロックドインバータと、逆電圧印加用トランジスタと、を有し、20

前記画素は、

ゲート電極が前記走査線に接続され、第1の電極が前記信号線に接続される第1のトランジスタと、

ゲート電極が前記第1のトランジスタの第2の電極に接続され、第1の電極が前記アノード線に接続される第2のトランジスタと、

ゲート電極がゲート固定電位線に接続され、第1の電極が前記第2のトランジスタの第2の電極に接続される第3のトランジスタと、

第1の電極が前記第3のトランジスタの第2の電極に接続され、第2の電極が前記カソード線に接続される発光素子と、30

ゲート電極が前記アノード線に接続され、第1の電極が前記発光素子の第1の電極に接続され、第2の電極が前記ゲート固定電位線に接続される逆バイアス用トランジスタと、を有し、

前記クロックドインバータは、

第1の電極が高電位電源線に接続される第4のトランジスタと、

ゲート電極が前記アノード線に接続され、第1の電極が低電位電源線に接続される第5のトランジスタと、

第1の電極が前記第5のトランジスタの第2の電極に接続される第6のトランジスタと、を有し、

前記第4のトランジスタのゲート電極と前記第6のトランジスタのゲート電極とは接続されて前記クロックドインバータの入力となり、40

前記第4のトランジスタの第2の電極と前記第6のトランジスタの第2の電極とは接続されて前記クロックドインバータの出力となり、

前記逆電圧印加用トランジスタのゲート電極は第2の電源線に接続され、第1の電極は前記アノード線に接続され、第2の電極は前記クロックドインバータの出力と前記走査線に接続され、

順電圧印加期間においては、

前記第5のトランジスタをオンとし前記クロックドインバータをオンとして、前記逆電圧印加用トランジスタをオフとし、

前記第3のトランジスタを飽和領域で駆動させることで定電流源として用いて、前記発光素子に順電圧を印加し、50

光素子に順電圧を印加し、

逆電圧印加期間においては、

前記第5のトランジスタをオフとし前記クロックドインバータをハイインピーダンス状態として、前記逆電圧印加用トランジスタをオンとし、

前記アノード線の電位と前記カソード線の電位を反転することで前記発光素子に逆電圧を印加し、

発光素子の第1の電極と第2の電極とが短絡している場合に前記逆バイアス用トランジスタがオンすることを特徴とする表示装置。

【請求項3】

請求項1において、前記第4のトランジスタと前記第5のトランジスタの極性は異なることを特徴とする表示装置。 10

【請求項4】

請求項1乃至3のいずれか一において、前記第1のトランジスタは線形領域で動作させることを特徴とする表示装置。

【請求項5】

請求項1乃至4のいずれか一において、前記第2のトランジスタは線形領域で動作させることを特徴とする表示装置。

【請求項6】

請求項1乃至5のいずれか一において、

前記画素は、

第1の電極が前記第2のトランジスタのゲート電極に接続され、第2の電極が前記アノード線に接続される消去用トランジスタを有することを特徴とする表示装置。 20

【請求項7】

請求項6において、前記消去用トランジスタは線形領域で動作させることを特徴とする表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、発光素子を備えた表示装置及びその駆動方法に関する。

【背景技術】

【0002】

近年、発光素子（自発光素子）を用いた表示装置の研究開発が進められている。このような表示装置は、高画質、薄型、軽量などの利点を生かして、携帯電話の表示画面やパソコンのモニターとして幅広く利用されている。特に、このような表示装置は動画表示に適した速い応答速度、低電圧、低消費電力駆動などの特徴を有しているため、新世代の携帯電話や携帯情報端末（PDA）をはじめ、幅広い用途が見込まれている。 30

【0003】

発光素子は、経時変化によりその輝度が劣化してしまう。例えば、ある電圧 $V_0$ を印加すると電流 $I_0$ で所定の発光輝度が得られていたにもかかわらず、発光素子の経時変化により、電圧 $V_0$ を印加しても電流 $I_0'$ しか発光素子へ流れないと、所定の輝度が得られなくなってしまった。また例えば、ある電流を流した場合であっても、発光素子の経時劣化により同一輝度が得られなくなってしまう。 40

【0004】

これは電圧や電流を流すことで発光素子が発熱し、発光素子の膜の界面や電極の界面での性質に変化が生じるためであると考えられる。さらに発光素子の劣化状態は、各発光素子で異なるためやきつきが生じてしまう。

【0005】

発光素子の劣化を抑制し、信頼性を向上させるため、発光素子の発光時に印加される電圧とは逆方向の電圧を印加する方法がある（特許文献1参照）。

【0006】

10

20

30

40

50

【特許文献1】特開2001-117534号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

発光素子を有する画素回路は、多様な構成を取り得る。そこで本発明は、新たな画素回路を有する表示装置に対して、発光素子の劣化を制御し、信頼性を向上させるため、発光素子へ逆方向の電圧（以下、逆電圧と表記する）を印加する回路構成、及びその方法を提供することを課題とする。

【課題を解決するための手段】

【0008】

上記課題を鑑み本発明は、信号線に接続されるスイッチング用のトランジスタ（スイッチング用トランジスタと表記する）、発光素子に接続される駆動用のトランジスタ（駆動用トランジスタと表記する）、駆動用トランジスタに直列に接続される電流制御用のトランジスタ（電流制御用トランジスタと表記する）を少なくとも有する新たな画素回路において、発光素子へ逆電圧を印加する。逆電圧とは、発光素子が発光する方向と逆に、電圧を印加することをいう。

【0009】

好ましくは、駆動用トランジスタのゲート電位を固定電位とすることにより、寄生容量や配線容量によるゲート・ソース間の電圧 $V_{gs}$ が変化しないように動作させることができる。その結果、駆動用トランジスタのゲート・ソース間電圧 $V_{gs}$ のばらつきに起因する、表示ムラを抑えることができる。

【0010】

また本発明は、信号線に接続される電流制御用トランジスタをオフとする、例えば、電流制御用トランジスタに接続された容量素子の電荷を放電する消去用のトランジスタ（消去用トランジスタと表記する）を加えた画素回路において、発光素子へ逆電圧を印加する。

【0011】

駆動用トランジスタは、飽和領域及び線形領域で動作させることができ、スイッチング用トランジスタ、電流制御用トランジスタ、及び消去用トランジスタは、線形領域で動作させる。線形領域で動作させる場合、駆動用電圧を低くできるため、表示装置の低消費電力化を達成することができる。

【0012】

逆電圧（逆バイアスともいう）を印加する方法は、発光素子が有する陽極と、陰極に印加する電圧の大小関係が逆となるように電圧を印加する。つまり、陽極に導通しているアノード線と、陰極に導通しているカソード線との電位が反転する電圧を印加する。なお、アノード線、及びカソード線には、電源線が接続され、電源線により反転する電位が印加されてもよい。

【0013】

逆電圧を印加するための回路（以下、逆電圧印加用回路と表記する）は、アナログスイッチ、又はクロックドインバータ等の半導体回路と、逆電圧印加時にオンとなるトランジスタ（逆電圧印加用トランジスタとも表記する）とを有する。

【0014】

アナログスイッチは、少なくとも極性の異なる第1のトランジスタ、及び第2のトランジスタを有する。クロックドインバータは、少なくとも極性の異なる第1のトランジスタ、及び第2のトランジスタと、第3のトランジスタを有する。さらに第3のトランジスタと極性の異なる第4のトランジスタを有してもよい。

【0015】

トランジスタは、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を用いた薄膜トランジスタ（TFT）、半導体基板やSOI基板を用いて形成されるMOS型トランジスタ、接合型トランジスタ、有機半導体やカーボンナノチューブを用いたトラン

10

20

30

40

50

ジスタ、その他のトランジスタを適用することができる。

【発明の効果】

【0016】

本発明により、新たな画素回路を有する表示装置に対して、発光素子の劣化を制御し、信頼性を向上させるため逆電圧を印加する回路構成、及びその方法を提供することができる。さらに、アノード線と信号線、つまりアノード線と信号線駆動回路が有する電源線とがショートすることなく逆電圧を印加することができる。その結果、表示装置を有する電子機器の長寿命化が達成できる。

【0017】

以上により新たな画素回路を有する表示装置に対して、発光素子の劣化を制御し、信頼性を向上させるため逆電圧を印加する回路構成、及びその方法を提供することができる。 10

【発明を実施するための最良の形態】

【0018】

以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる形態で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。

【0019】

なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。 20

【0020】

また以下の実施の形態において、トランジスタはゲート、ソース、ドレインの3端子を有するが、ソース電極、ドレイン電極に関しては、トランジスタの構造上、明確に区別が出来ない。よって、素子間の接続について説明する際は、ソース電極、ドレイン電極のうち一方を第1の電極、他方を第2の電極と表記する。

【0021】

(実施の形態1)

本実施の形態では、少なくともスイッチング用トランジスタ、消去用トランジスタ、駆動用トランジスタ及び電流を有する画素回路に対し、アナログスイッチを有する逆電圧印加用回路を用いる具体例について説明する。 30

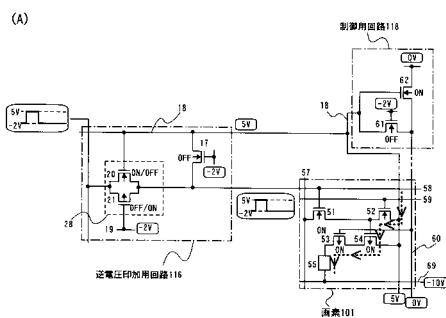

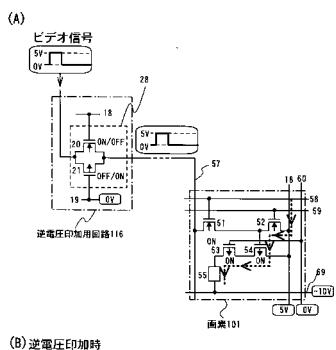

【0022】

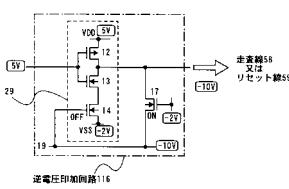

図1(A)には、順電圧(発光素子が発光する方向の電圧)を印加し、発光素子が発光している状態を示す。図1(A)に示す逆電圧印加用回路116は、nチャネル型トランジスタ20、pチャネル型トランジスタ21を有するアナログスイッチ28を有する。nチャネル型トランジスタ20のゲート電極は、アノード線18に接続され、本実施の形態ではアノード線18は、5Vに保持されている。pチャネル型トランジスタ21のゲート電極は、一定の電位に保持された電源線、又はカソード線に接続され、本実施の形態では-2Vに固定された第1の電源線19に接続されている。アナログスイッチ28の出力配線(出力端子)は、逆電圧印加用トランジスタ17の第1の電極と、走査線58、又は消去用トランジスタのゲート電極に接続されるリセット線59と、に接続される。本実施の形態ではアナログスイッチ28の出力配線は、逆電圧印加用トランジスタ17の第1の電極と、走査線58と、に接続されている。 40

【0023】

逆電圧印加用トランジスタ17は、一定の電位に保たれた電源線、又はカソード線にゲート電極が接続され、アノード線に第1の電極が接続され、アナログスイッチ28の出力配線に第2の電極が接続される。本実施の形態では逆電圧印加用トランジスタ17のゲート電極は-2Vの電位に保持されている。さらに、逆電圧印加用トランジスタ17の第1の電極は、スイッチング用トランジスタのゲート電極に接続された走査線58に接続されている。また逆電圧印加用トランジスタの第1の電極は、消去用トランジスタのゲート電極に接続されたリセット線59に接続してもよい。 50

## 【0024】

このような回路構成において、走査線駆動回路が有するバッファ回路から、例えば5V、-2Vの電圧のパルス信号が出力され、アナログスイッチ28へ入力される。すると、nチャネル型トランジスタ20、及びpチャネル型トランジスタ21のどちらかがオンとなり、逆電圧印加用トランジスタ17はオフとなる。具体的には、Lowの信号が入力される場合、pチャネル型トランジスタ21がオンとなり、Highの信号が入力される場合、nチャネル型トランジスタ20がオンとなる。そして、走査線58にはバッファ回路から出力された信号が入力される。

## 【0025】

このような信号がアナログスイッチ28に入力されるとき、画素101ではスイッチング用トランジスタ51がオンとなり、信号線57からビデオ信号が入力される。本実施の形態では、スイッチング用トランジスタ51はnチャネル型のトランジスタを用い、ビデオ信号は電圧値として入力する。スイッチング用トランジスタ51は、pチャネル型のトランジスタを用いてもよい。

10

## 【0026】

すると、駆動用トランジスタ53、電流制御用トランジスタ54がオンとなり、発光素子55が発光する。発光素子55の陰極は、-10Vに保持されたカソード線69に接続され、陽極は、5Vに保持されたアノード線18に接続されている。

## 【0027】

本実施の形態において、駆動用トランジスタ53、電流制御用トランジスタ54はpチャネル型のトランジスタを用いるが、nチャネル型のトランジスタを用いてもよい。なお、駆動用トランジスタ53と、電流制御用トランジスタ54は同一極性を用いる方が好ましい。

20

## 【0028】

このとき必要に応じて、消去用トランジスタ52を動作させて、リセット線59を選択し消去期間を設ける。本実施の形態において、消去用トランジスタ52はnチャネル型のトランジスタを用いる。消去用トランジスタ52はpチャネル型のトランジスタを用いてもよいことは言うまでもない。消去用トランジスタやその動作は、特開2001-343933号公報を参照すればよく、それらと組み合わせて用いることができる。

## 【0029】

30

また消去用トランジスタ52、及び電流制御用トランジスタ54の第1の電極が接続されるアノード線18及び駆動用トランジスタのゲート電極が接続される第2の電源線60は、制御用回路118が接続されている。なお駆動用トランジスタのゲート電極を固定電位とすると、寄生容量や配線容量によるゲート・ソース間の電圧Vgsが変化しないように動作させることができる。そのため、少なくとも順電圧印加時では、第2の電源線60の電位を固定電位とすると好ましい。

## 【0030】

制御用回路118は二つのnチャネル型トランジスタを有し、第1のnチャネル型トランジスタ61の第1の電極と、第2のnチャネル型トランジスタ62のゲート電極とが、アノード線18に接続されている。第1のnチャネル型トランジスタ61の第2の電極と、第2のnチャネル型トランジスタ62の第1の電極とが、第2の電源線60に接続されている。第1のnチャネル型トランジスタ61のゲート電極は、-2Vに固定され、第2のnチャネル型トランジスタ62の第2の電極は、0Vに固定されている。

40

## 【0031】

このような制御用回路118は、順電圧印加時では、第1のnチャネル型トランジスタ61はオフとなり、第2のnチャネル型トランジスタ62はオンとなっている。その結果、駆動用トランジスタ53のゲート電極の電位は0Vとなっている。

## 【0032】

以上のような状態のとき、駆動用トランジスタ53はオンとなり、カソード線69が-10V、アノード線18が5Vであるため、発光素子へは順電圧が印加され、発光する。

50

## 【0033】

図1(B)には、逆電圧を印加している状態を示す。本実施の形態では、アノード線18を-10V、第1の電源線19を-2Vとする。すると、アナログスイッチ28が有するnチャネル型トランジスタ20、及びpチャネル型トランジスタ21は、両方ともオフとなり、逆電圧印加用トランジスタ17はオンとなり、走査線58は-10Vとなる。それに伴い、画素101ではスイッチング用トランジスタ51がオフとなる。

## 【0034】

このときカソード線69の電圧を5Vとし、逆電圧を印加する。そして、駆動用トランジスタ53と、電流制御用トランジスタ54とをオンとし、逆電圧を効率よく印加する。特に、駆動用トランジスタ53は、飽和領域で動作させるため、L/Wが大きくなるように設計されている場合、抵抗値が高いことが懸念される。そのため、制御用回路118では、第1のnチャネル型トランジスタ61をオンとし、第2のnチャネル型トランジスタ62をオフとし、駆動用トランジスタ53のゲート電極に接続される第2の電源線60の電圧を-10Vとする。その結果、駆動用トランジスタ53のゲート電極へ印加されるゲート電圧を大きくできより効率高く逆電圧を印加することができる。その結果、駆動用トランジスタ53の抵抗による逆電圧印加時が長くなるという問題を低減することができる。

10

## 【0035】

なお駆動用トランジスタ53は、線形領域で動作させてもよい。駆動用トランジスタ53を線形領域で動作させる場合、駆動電圧を低くすることができる。そのため、表示装置の低消費電力化が期待できる。

20

## 【0036】

以上のような状態のとき、駆動用トランジスタ53、電流制御用トランジスタ54はオンとなり、カソード線69が5V、アノード線18が-10Vであるため、発光素子へは逆電圧が印加される。

## 【0037】

また、駆動用トランジスタ53や電流制御用トランジスタ54の抵抗を解消するために、発光素子の第1の電極(本実施の形態では陽極)と、アノード線18との間にダイオードを設けてもよい。なお本実施の形態では、発光素子の第1の電極は陽極とするが、第1の電極が陰極となる画素構成を用いてもよい。

30

## 【0038】

本実施の形態により、新たな画素回路を有する表示装置に対して、発光素子の劣化を低減し、信頼性を向上させるため逆電圧を印加する回路構成、及びその方法を提供することができる。

## 【0039】

さらに本実施の形態により、アノード線と信号線、つまりアノード線と信号線駆動回路が有する電源線とがショートすることなく逆電圧を印加することができる。

## 【0040】

なお、本実施の形態で示した電圧の値は一例であり、これに限定されるものではない。

## 【0041】

40

(実施の形態2)

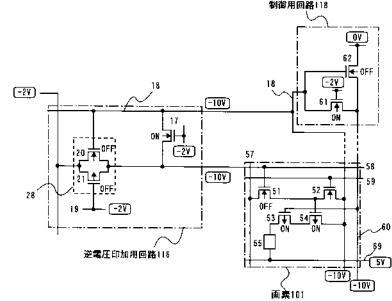

本実施の形態では、クロックドインバータを有する逆電圧印加用回路に用いる具体例について説明する。

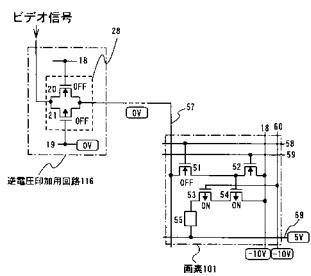

## 【0042】

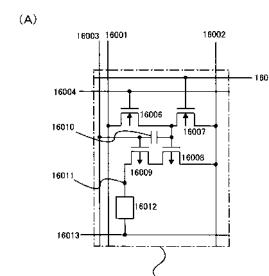

図2(A)には、順電圧を印加している状態を示す。図2(A)に示す逆電圧印加用回路116は、直列に接続されたpチャネル型トランジスタ12と、nチャネル型トランジスタ13、14を有するクロックドインバータ29を有する。なお、さらに加えてpチャネル型トランジスタを有するクロックドインバータを用いてもよい。pチャネル型トランジスタ12のゲート電極と、nチャネル型トランジスタ13のゲート電極は同電位であって、つまり接続されている。pチャネル型トランジスタ12の第1の電極は、一定の電位に

50

保持された電源線、例えば 5 V に保持された VDD (高電位電源線) に接続されている。n チャネル型トランジスタ 14 の第 1 の電極は、一定の電位に保持された電源線、例えば -2 V に保持された VSS (低電位電源線) に接続されている。またゲート電極は、一定の電位に保持された電源線、又はカソード線に接続され、本実施の形態では 5 V に保持された第 1 の電源線 19 に接続されている。クロックドインバータ 29 の出力配線は、逆電圧印加用トランジスタ 17 の第 1 の電極と、図 1 における走査線 58 又はリセット線 59 とに接続されている。本実施の形態では、クロックドインバータ 29 の出力配線は、逆電圧印加用トランジスタ 17 の第 1 の電極と、走査線 58 とに接続されている。

#### 【0043】

逆電圧印加用トランジスタ 17 は、一定の電位に保たれた電源線、又はカソード線にゲート電極が接続され、アノード線に第 1 の電極が接続され、クロックドインバータ 29 の出力配線とに第 2 の電極が接続される。本実施の形態では逆電圧印加用トランジスタ 17 のゲート電極は -2 V の電位に保たれている。また逆電圧印加用トランジスタの第 1 の電極はクロックドインバータの出力配線と接続され、第 2 の電極は第 1 の電源線 19 に接続されている。さらに本実施の形態では、逆電圧印加用トランジスタ 17 の第 1 の電極は、スイッチング用トランジスタのゲート電極に接続された走査線 58 に接続される。また逆電圧印加用トランジスタの第 1 の電極は、消去用トランジスタのゲート電極に接続されたリセット線 59 に接続してもよい。

#### 【0044】

走査線駆動回路が有するバッファ回路から、例えば 5 V、-2 V のパルス信号が出力され、クロックドインバータ 29 へ入力される。すると、n チャネル型トランジスタ 14 がオンとなり、逆電圧印加用トランジスタ 17 はオフとなる。

#### 【0045】

その結果、走査線 58 にはバッファ回路から出力された信号が入力される。本実施の形態では、図 1 (A) におけるスイッチング用トランジスタ 51 は n チャネル型トランジスタを用い、ビデオ信号は電圧値として入力する。すると、実施の形態 1 と同様に、駆動用トランジスタ 53、電流制御用トランジスタ 54 がオンとなり、発光素子 55 が発光する。

#### 【0046】

その他の画素構成、動作、制御用回路 118 は図 1 (A) と同様であるため、説明を省略する。なお駆動用トランジスタのゲート電極を固定電位とすると、寄生容量や配線容量によるゲート・ソース間の電圧  $V_{gs}$  が変化しないように動作させることができる。そのため実施の形態 1 と同様に、少なくとも順電圧印加時では、第 2 の電源線 60 の電位を固定電位とすると好ましい。

#### 【0047】

このとき必要に応じて、消去用トランジスタ 52 を動作させて、リセット線 59 を選択し消去期間を設け、高階調表示を行う。本実施の形態において、消去用トランジスタ 52 は n チャネル型トランジスタを用いる。消去用トランジスタやその動作の詳細は、特開 2001-343933 号公報を参照すればよい。

#### 【0048】

以上のような状態のとき、駆動用トランジスタ 53 はオンとなり、カソード線 69 が -10 V、アノード線 18 が 5 V であるため、発光素子へは順電圧が印加され、発光する。

#### 【0049】

図 2 (B) には、逆電圧を印加している状態を示し、第 1 の電源線 19 は -10 V に保持される。すると、クロックドインバータ 29 が有する n チャネル型トランジスタ 14 は、ハイインピーダンス状態、つまりオフとなり、逆電圧印加用トランジスタ 17 はオンとなり、走査線 58 は -10 V となる。それに伴い、画素 101 ではスイッチング用トランジスタ 51 がオフとなる。

#### 【0050】

逆電圧を効率よく印加するため、駆動用トランジスタ 53 と、電流制御用トランジスタ

10

20

30

40

50

54とをオンとする。このとき実施の形態1と同様な制御用回路118を用い、第1のnチャネル型トランジスタ61をオンとし、第2のnチャネル型トランジスタ62をオフとし、駆動用トランジスタ53のゲート電極に接続される第2の電源線60の電圧を-10Vとする。

#### 【0051】

以上のような状態のとき、駆動用トランジスタ53はオンとなり、カソード線69が5V、アノード線18が-10Vとなるため、発光素子へは逆電圧が印加される。

#### 【0052】

また、駆動用トランジスタ53や電流制御用トランジスタ54の抵抗問題を解消するために、発光素子の第1の電極と、アノード線18との間にダイオードを設けてよい。

10

#### 【0053】

本実施の形態により、新たな画素回路を有する表示装置に対して、発光素子の劣化を制御し、信頼性を向上させるため逆電圧を印加する回路構成、及びその方法を提供することができる。

#### 【0054】

さらに本実施の形態により、アノード線と信号線、つまりアノード線と信号線駆動回路が有する電源線とがショートすることなく逆電圧を印加することができる。

#### 【0055】

なお、本実施の形態で示した電圧の値は一例であり、これに限定されるものではない。

#### 【0056】

20

##### (実施の形態3)

本実施の形態では、逆電圧印加用回路を有する走査線駆動回路、信号線駆動回路、及びそれらを有する表示装置について説明する。

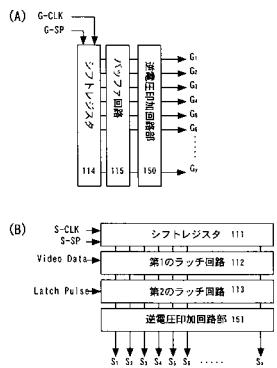

#### 【0057】

図5(A)には、走査線駆動回路の構成を示し、シフトレジスタ114、バッファ回路115、逆電圧印加用回路116を有する逆電圧印加回路部150を有する。

#### 【0058】

逆電圧印加回路部150は、図1・2に示すような走査線、又はリセット線にそれぞれ接続される複数の逆電圧印加用回路116と逆電圧印加用トランジスタ17を有する。逆電圧印加用回路116は、アナログスイッチ28、又はクロックドインバータ29を有する。

30

#### 【0059】

走査線駆動回路に逆電圧印加回路部150を設ける場合、アノード線と、一定の電位に保たれた電源線、又はカソード線の電位を反転し、発光素子に逆電圧を印加すると同時に、アナログスイッチ28、又はクロックドインバータ29をオフとし、逆電圧印加用トランジスタ17をオンとするように駆動する。そして、逆電圧印加用回路116に接続される画素が有するスイッチング用トランジスタ51、又は消去用トランジスタ52がオフとなる電位とする。その結果、アノード線18と信号線57、つまりアノード線と信号線駆動回路が有する電源線とがショートすることなく逆電圧を印加することができる。

#### 【0060】

40

逆電圧印加用回路116を、信号線駆動回路に設けることもできる。図5(B)には、信号線駆動回路の構成を示し、シフトレジスタ111、第1のラッチ回路112、第2のラッチ回路113、複数の逆電圧印加用回路116を有する逆電圧印加回路部151を有する。

#### 【0061】

信号線駆動回路に設けられた逆電圧印加用回路は、アナログスイッチ28、又はクロックドインバータ29を有し、逆電圧印加用トランジスタ17は不要となる。アナログスイッチ、又はクロックドインバータの出力配線が、画素部の複数の信号線(S1~Sx)とそれぞれ接続されている。

#### 【0062】

50

さらに、信号線駆動回路が有する電源線とアノード線のショートを防止するため、スイッチを有する。スイッチは、アノード線と一定の電位に保たれた電源線、又はカソード線の電位差を利用して、オン、又はオフとなる。

#### 【0063】

信号線駆動回路に逆電圧印加回路部150を設ける表示装置において、アノード線と一定の電位に保たれた電源線、又はカソード線の電位を反転し、発光素子に逆電圧を印加すると同時に、アナログスイッチ、又はクロックドインバータをオフとする。すると、アノード線と信号線との間に配置されたトランジスタをオフとすることができます。その結果、アノード線と信号線、つまりアノード線と信号線駆動回路が有する電源線とがショートすることなく逆電圧を印加することができる。10

#### 【0064】

また逆電圧を印加するとき、駆動用トランジスタのゲート電極が接続される電源線と、アノード線の電圧について説明する。逆電圧を印加する場合、駆動用トランジスタ、電流制御用トランジスタを介して発光素子へ逆電圧が印加される。そのため、駆動用トランジスタ、電流制御用トランジスタの抵抗は、より低くなると好ましい。しかし、特に駆動用トランジスタの場合、飽和領域で動作させる場合、チャネル形成領域のL/W比が大きくなり、抵抗が高くなることが懸念される。

#### 【0065】

そこで、駆動用トランジスタ、電流制御用トランジスタを確実にオンとし、より高い電圧を印加するように、駆動用トランジスタのゲート電極が接続される電源線の電圧を制御する制御用回路118を有する。20

#### 【0066】

制御用回路は、アノード線にゲート電極が接続され、第1の電極が電源線に接続された第6のトランジスタと、ゲート電極が固定電位に保持され、第1の電極がアノード線に接続され、第2の電極が電源線に接続された第7のトランジスタとを有する。

#### 【0067】

駆動用トランジスタに着目すると、順電圧を印加する場合、第6のトランジスタはオン、第7のトランジスタはオフとし、逆電圧を印加する場合、第6のトランジスタはオフ、第7のトランジスタはオンとする。そして逆電圧を印加する場合、電源線の電圧の絶対値を大きくし、駆動用トランジスタへ印加する電圧を大きくすることができる。30

#### 【0068】

本実施の形態により、新たな画素回路を有する表示装置に対して、発光素子の劣化を制御し、信頼性を向上させるため逆電圧を印加する回路構成、及びその方法を提供することができる。さらに、アノード線と信号線、つまりアノード線と信号線駆動回路が有する電源線とがショートすることなく逆電圧を印加することができる。その結果、表示装置の長寿命化が達成できる。

#### 【0069】

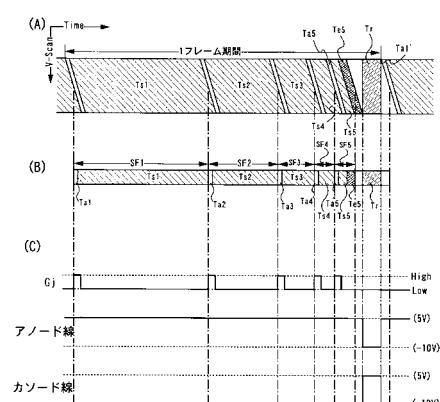

##### (実施の形態4)

本発明の表示装置をデジタル駆動する場合には、多階調の画像を表現するために時間階調方式を用いる。本実施の形態では、逆電圧を印加するタイミングについて図3を用いて説明する。図3(A)は、縦軸は走査線、横軸は時間のときのタイミングチャートを示し、図3(B)はj行目の走査線Gjのタイミングチャートを示す。40

#### 【0070】

表示装置は、そのフレーム周波数を通常60Hz程度とする。つまり、1秒間に60回程度の画面の描画が行われ、画面の描画を1回行なう期間を1フレーム期間(単位フレーム期間)と呼ぶ。時間階調方式では、1フレーム期間を複数のサブフレーム期間(m(mは2以上の自然数)個のサブフレーム期間SF1、SF2、...、SFm)に分割する。このときの分割数は、階調ビット数に等しい場合が多く、ここでは簡単のために、分割数が階調ビット数に等しい場合を示す。つまり本実施の形態では5ビット階調を例示しているので、5つのサブフレーム期間SF1～SF5に分割した例を示す。50

**【0071】**

各サブフレーム期間は、画素にビデオ信号を書き込む書き込み期間  $T_{a1}$ 、 $T_{a2}$ 、…、 $T_{am}$ と、発光素子が発光又は非発光する保持期間  $T_{s1}$ 、 $T_{s2}$ 、…、 $T_{sm}$ を有する。保持期間  $T_{s1}$ ～ $T_{s5}$ は、その長さの比を  $T_{s1} : \dots : T_{s5} = 16 : 8 : 4 : 2 : 1$  とする。つまり、 $n$  ビット階調を表現する場合、 $n$  個の保持期間は、その長さの比を  $2^{(n-1)} : 2^{(n-2)} : \dots : 2^1 : 2^0$  とする。

**【0072】**

図3において、サブフレーム期間  $SF_5$  は消去期間  $T_{e5}$  を有する例を示す。消去期間  $T_{e5}$  では、画素に書き込まれたビデオ信号をリセットする。消去期間は必要に応じて設ければよい。

10

**【0073】**

一フレーム期間に逆電圧印加期間  $T_r$  を設ける。この逆電圧印加期間  $T_r$  では、全ての画素で同時に逆電圧が印加される。本実施の形態では、消去期間  $T_{e5}$  の終了後、逆電圧印加期間  $T_r$  を設ける場合を説明する。なお、逆電圧印加期間  $T_r$  を長く設け、発光素子へ逆電圧を印加する時間を長くすると好ましい。

**【0074】**

図3(C)は図3(B)に対応する走査線  $G_j$ 、アノード線、及びカソード線の電圧値を示す。図3(C)をみると、走査線  $G_j$  には  $HIGH$  と  $LOW$  のパルス信号が印加され、例えば実施の形態1又は2で示したように5V、-2Vの電圧の信号が印加される。書き込み期間  $T_{a1}$ ～ $T_{a5}$  では、走査線  $G_j$  には  $HIGH$  の信号が印加され、逆電圧印加期間  $T_r$  では  $LOW$  の信号が印加される。

20

**【0075】**

アノード線へ5V、カソード線へ-10Vの電圧が印加され、逆電圧印加期間  $T_r$  では、アノード線へ-10V、カソード線へ5Vの電圧、つまり逆電圧が印加される。

**【0076】**

なお、表示階調数を増やしたい場合は、サブフレーム期間の分割数を増やせばよい。また、サブフレーム期間の順序は、必ずしも上位ビットから下位ビットといった順序である必要はなく、1フレーム期間中、ランダムに並んでいてもよい。さらにフレーム期間毎に、その順序が変化してもよい。また、あるサブフレーム期間をさらに分割していくよい。

30

**【0077】**

また画素毎に、逆電圧を印加するか否かを決定してもよい。この場合、画素毎にスイッチを設け、逆電圧を印加しないときはオフとなるように制御する。

**【0078】**

また、画素毎に発光素子の劣化状態が異なる場合が考えられる。メモリ回路及びカウンタ回路とにより、ビデオ信号をカウント、記録し、その情報に基づきに発光素子の劣化状態に応じて印加すべき逆電圧の値を求めることができる。そして、印加する逆電圧の値に応じて、アノード線と、一定の電位に保持された電源線、又はカソード線の電位を設定してもよい。例えば、アノード線は発光素子毎に設けられるため、アノード線の電位を画素毎に設定する。

40

**【0079】**

本実施の形態は、上記の実施の形態と自由に組み合わせることができる。

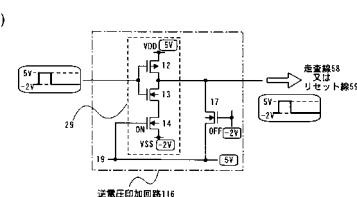

**【0080】****(実施の形態5)**

本実施の形態では、画素の動作について図4を用いて説明する。

**【0081】**

図4(A)に示す画素16100は、信号線16001、第1の電源線16002、ゲート固定電位線16003、走査線16004、リセット線16005、スイッチング用トランジスタ16006、消去用トランジスタ16007、電流制御用トランジスタ16008、駆動用トランジスタ16009、容量手段16010、画素電極16011、発

50

光素子 16012、第2の電源線 16013 を有する。画素電極は発光素子の電極として機能する。なお、ゲート固定電位線 16003 は、駆動用トランジスタ 16008 のゲート電位を固定するための線である。

#### 【0082】

次に動作について説明する。まず、走査線 16004 に選択パルス信号が入力され、スイッチング用トランジスタ 16006 がオンとなり、信号線 16001 に出力されたビデオ信号が電流制御用トランジスタ 16008 のゲート電極に入力される。ビデオ信号が High レベル（以下、H レベルと表記する）の場合、電流制御用トランジスタ 16008 はオフとなり、Low レベル（以下、L レベルと表記する）の場合、電流制御用トランジスタ 16008 はオンとなる。電流制御用トランジスタ 16008 のオン、又はオフの状態により、発光素子 16012 への電流供給が制御され、発光、非発光が決定される。このとき、消去用トランジスタ 16007 はオフとなっている。

#### 【0083】

続いて、発光素子 16012 への電流供給を強制的に遮断する場合には、リセット線 16005 に選択パルス信号が入力され、消去用トランジスタ 16007 がオンし、第1の電源線 16002 の電位が電流制御用トランジスタ 16008 のゲート電極に入力される。電流制御用トランジスタ 16008 のゲート電極とソース電極が同電位になるため、オフになる。

#### 【0084】

また、逆電圧印加期間には、第1の電源線 16002 の電位と第2の電源線 16013 の電位を入れ替わる。このとき、発光素子の成膜不良等により画素電極 16011 と第2の電源線 16013 が短絡している場合には駆動用トランジスタ 16009 がオンとなる。その結果、短絡箇所に電流が流れ、焼き切れ絶縁する。画素電極 16011 と第2の電源線 16013 が短絡している場合にはその画素は常に非発光状態であったり、所望の輝度を得られなかったり等の不良となってしまうが、前述の短絡箇所に電流を流し絶縁することでこのような不良を解消することができる。

#### 【0085】

次に、駆動用トランジスタ 16009 を電流源として用いる場合について図 4 (B) を用いて説明する。

#### 【0086】

画素 16101 は信号線 16001、第1の電源線 16002、ゲート固定電位線 16003、走査線 16004、リセット線 16005、スイッチング用トランジスタ 16006、消去用トランジスタ 16007、電流制御用トランジスタ 16008、駆動用トランジスタ 16009、容量手段 16010、画素電極 16011、発光素子 16012、第2の電源線 16013、逆バイアス用（以下、RB 用と表記する）トランジスタ 16014 を有し、画素 16100 との違いは RB 用トランジスタ 16014 が追加された点のみである。

#### 【0087】

RB 用トランジスタ 16014 のゲート電極は第1の電源線 16002 に接続され、第1の電極は画素電極 16011 に接続され、第2の電極はゲート固定電位線 16003 に接続されている。

#### 【0088】

本実施の形態では、駆動用トランジスタ 16009 を定電流源として用いるため、発光素子 16012 に流れる電流値は駆動用トランジスタ 16009 の特性によって決定する。そのため、前記電流値に合わせ、比較的インピーダンスの高いトランジスタを用いることが望ましい。

#### 【0089】

続いて、駆動について説明する。順電圧印加期間においては、前述の通りである。

#### 【0090】

次に、逆電圧印加期間には、第1の電源線 16002 の電位と第2の電源線 16013

10

20

30

40

50

の電位が入れ替わる。このとき、発光素子の成膜不良等により画素電極 16011 と第 2 の電源線 16013 が短絡している場合には、RB 用トランジスタ 16014 がオンとなる。その結果、短絡箇所に電流が流れ、焼き切れる。駆動用トランジスタ 16009 のインピーダンスが高い場合、短絡箇所を絶縁するのに充分な電流を流せないが、RB 用トランジスタ 16014 を追加することで、充分な電流を流すことができる。そして、上述のような不良を解消することができる。

#### 【0091】

また、本実施の形態では逆電圧印加期間において、第 1 の電源線 16002 と第 2 の電源線 16013 の電位を入れ替える場合のみ説明したが、本発明はこれに限らず、画素電極 16011 と第 2 の電源線 16013 の極性が入れ替わるよう、電位を設定すればよい。

10 また、本実施の形態ではスイッチング用トランジスタ 16006 及び消去用トランジスタ 16007 がN型トランジスタ、電流制御用トランジスタ 16008、駆動トランジスタ 16009 及び RB 用トランジスタ 16014 がP型トランジスタの場合で説明したが、トランジスタの極性はこれに限らず、任意に設定すればよい。

#### 【0092】

また、RB 用トランジスタ 16014 の第 1 の電極を画素電極 16011 に接続し、第 2 の電極をゲート固定電位線 16003 に接続する場合を説明したが、第 2 の電極を信号線 16001 に接続してもよいし、画素電極 16011 と第 1 の電源線 16002 との間、又は画素電極 16011 とゲート固定電位線 16003 との間にダイオードを接続してもよい。

20

#### 【0093】

また、本実施の形態では容量手段 16010 を設けたが、電流制御用トランジスタ 16008 のチャネル容量等で保持容量をまかなえる場合には、設ける必要はない。

#### 【0094】

##### (実施の形態 6)

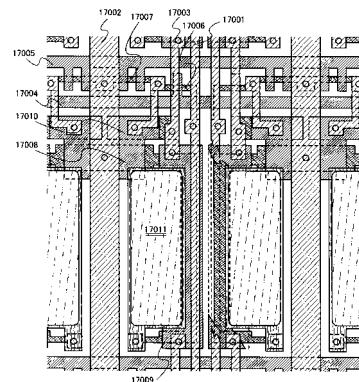

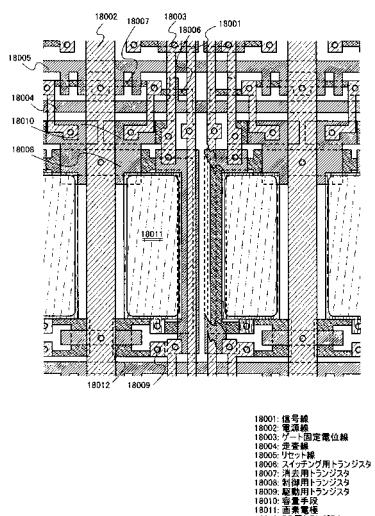

本実施の形態では、図 4 (A) の上面図の一例を、図 6 を用いて説明する。

#### 【0095】

図 6において、信号線 17001、第 1 の電源線 17002、ゲート固定電位線 17003、走査線 17004、リセット線 17005、スイッチング用トランジスタ 17006、消去用トランジスタ 17007、電流制御用トランジスタ 17008、駆動用トランジスタ 17009、容量手段 17010、画素電極 17011 を示し、それぞれ図 4 (A) で示した信号線 16001、第 1 の電源線 16002、ゲート固定電位線 16003、走査線 16004、リセット線 16005、スイッチング用トランジスタ 16006、消去用トランジスタ 16007、電流制御用トランジスタ 16008、駆動用トランジスタ 16009、容量手段 16010、画素電極 16011 にそれぞれ相当する。

30

#### 【0096】

本実施の形態では、第 1 の電源線 17002 を隣り合う画素で共有する場合について示したが、発光素子の特性がRGBによって違う場合において、各電源線の電位をRGBによって変えることでホワイトバランスを調整する場合には、隣り合う電源線を共有しなくてもよい。

40

#### 【0097】

##### (実施の形態 7)

本実施の形態では、図 4 (B) の上面図の一例を、図 7 を用いて説明する。

#### 【0098】

図 7において、信号線 18001、第 1 の電源線 18002、ゲート固定電位線 18003、走査線 18004、リセット線 18005、スイッチング用トランジスタ 18006、消去用トランジスタ 18007、電流制御用トランジスタ 18008、駆動用トランジスタ 18009、容量手段 18010、画素電極 18011、RB 用トランジスタ 18012 を示し、それぞれ図 4 (B) で示した信号線 16001、第 1 の電源線 16002、ゲート固定電位線 16003、走査線 16004、リセット線 16005、スイッチン

50

グ用トランジスタ 16006、消去用トランジスタ 16007、電流制御用トランジスタ 16008、駆動用トランジスタ 16009、容量手段 16010、画素電極 16011、R B 用トランジスタ 16014 に相当する。

#### 【0099】

本実施の形態では、第 1 の電源線 18002 を隣り合う画素で共有する場合について示したが、発光素子の特性が R G B によって違う場合において、各電源線の電位を R G B によって変えることでホワイトバランスを調整する場合には、前述の様に隣り合う電源線を共有しなくてもよい。

#### 【0100】

(実施の形態 8 )

10

本発明の表示装置の一形態である、表示領域及びドライバを搭載したパネルについて説明する。また本実施の形態においてトランジスタには、薄膜トランジスタ (TFT) を用いて説明する。

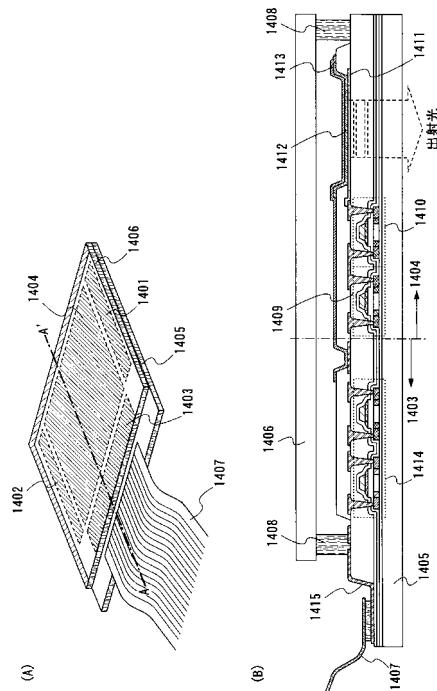

#### 【0101】

図 8 (A) には、基板 1405 上に設けられた、発光素子を含む画素を、複数有する表示領域 1404、ソースドライバ 1403、第 1 及び第 2 のゲートドライバ 1401、1402、接続端子 1415 及び接続フィルム 1407 を示す。接続端子 1415 は、異方導電性粒子等を介して、接続フィルム 1407 と接続する。接続フィルム 1407 は I C チップと接続する。

#### 【0102】

20

図 8 (B) はパネルの A - A' における断面図を示し、表示領域 1404 に設けられた電流制御用 TFT 1409 及び駆動用 TFT 1410 と、ソースドライバ 1403 に設けられた CMOS 回路 1414 を示す。また、表示領域 1404 に設けられた導電層 1411、電界発光層 1412 及び導電層 1413 を示す。導電層 1411 は駆動用 TFT 1410 のソース電極又はドレイン電極に接続する。また、導電層 1411 は画素電極として機能し、導電層 1413 は対向電極として機能する。導電層 1411、電界発光層 1412 及び導電層 1413 の積層体は発光素子に相当する。発光素子は、電界発光層が複数の層からなる積層型、電界発光層が一つの層からなる単層型、電界発光層が複数の層からなるがその境界が明確ではない混合型のいずれでもよい。また、発光素子の積層構造には、下から陽極に相当する導電層 \ 電界発光層 \ 陰極に相当する導電層を積層する順積み構造、下から陰極に相当する導電層 \ 電界発光層 \ 陽極に相当する導電層を積層する逆積み構造がある。発光素子の光の発する方向に基づいて、適切な構造を選択するとよい。電界発光層には有機材料（低分子、高分子、中分子）、有機材料と無機材料を組み合わせた材料を用いることができる。

30

#### 【0103】

また、シングレット材料、トリプレット材料又はそれらを組み合わせた材料のいずれを用いてもよい。その結果、発光素子から発せられる光には、一重項励起状態から基底状態に戻る際の発光（蛍光）と三重項励起状態から基底状態に戻る際の発光（リン光）となり、本発明はその一方又は両方を用いることができる。

#### 【0104】

40

なお、発光素子に電流が流れて発光する状態とは、発光素子の両電極間に順電圧が印加された状態である。

#### 【0105】

表示領域 1404 とドライバ 1401 ~ 1403 の周囲にはシール材 1408 が設けられ、発光素子は、該シール材 1408 と対向基板 1406 により封止される。この封止処理は、発光素子を水分から保護するための処理であり、ここではカバー材（ガラス、セラミックス、プラスチック、金属等）により封止する方法を用いるが、熱硬化性樹脂や紫外光硬化性樹脂を用いて封止する方法、金属酸化物や窒化物等のバリア能力が高い薄膜により封止する方法を用いてもよい。

#### 【0106】

50

基板 1405 上に形成される素子は、非晶質半導体に比べて移動度等の特性が良好な結晶質半導体（ポリシリコン）により形成されること好適である。結晶性半導体を用いると、同一表面上におけるモノシリック化を実現することができる。モノリシック構成を有するパネルは、接続する外部 IC の個数が減少するため、小型・軽量・薄型が実現される。

#### 【0107】

また、図 8 (B)において、導電層 1411 は透明導電膜で形成し、導電層 1413 は反射膜で形成される。よって、電界発光層 1412 から発せられる光は、矢印で示すとおり、導電層 1411 を透過して、基板 1405 側に出射される。このような構成は下面出射方式と呼ばれる。

#### 【0108】

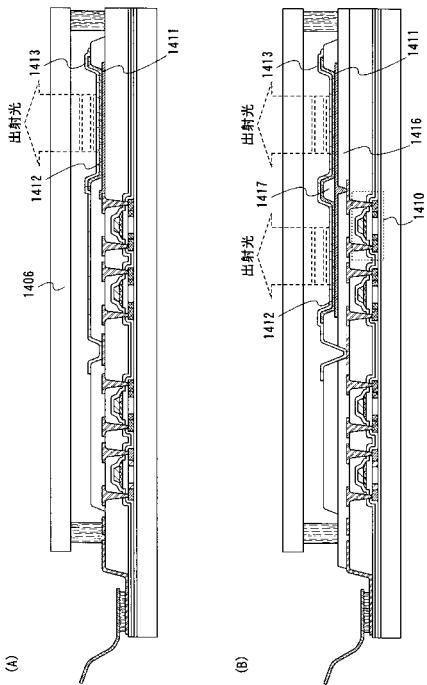

これに対し、導電層 1411 を反射膜で形成し、導電層 1413 を透明導電膜で形成することにより、図 9 (A) に示すように、電界発光層 1412 から発せられる光を対向基板 1406 側に出射させる構成も可能である。このような構成は上面出射方式と呼ばれる。

#### 【0109】

また、駆動用 TFT 1410 のソース電極又はドレイン電極と導電層 1411 とは、絶縁層を介すことなく、同一の層に積層形成され、膜の重なりによって直接接続されている。よって、導電層 1411 の形成領域は、駆動用 TFT 1410 等が配置されている領域を除いた領域となるため、画素の高精細化等に伴い、開口率の低下が避けられない。よって、図 9 (B) に示すように、層間膜 1416 を追加し、独立した層に画素電極を設け、上面出射方式とすることにより、TFT 等が形成されている領域も有効に発行領域として活用出来る。このとき、電界発光層 1412 の膜厚によっては、導電層 1411 と駆動用 TFT 1410 のソース電極又はドレイン電極とのコンタクト領域において、導電層 1411 と導電層 1413 とのショートが生ずる可能性があるので、バンク 1417 等を設け、ショートを防止する構成が望ましい。

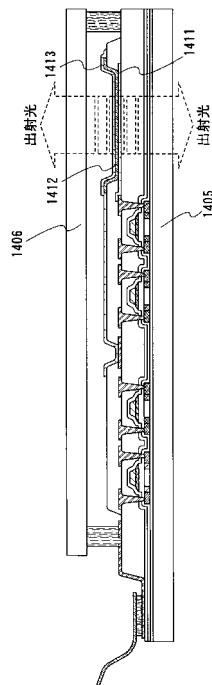

#### 【0110】

さらに、図 10 に示すように、導電層 1411 と導電層 1413 とをいずれも透明導電膜で形成することにより、基板 1405 側と対向基板 1406 側の両方に電界発光層 1412 からの出射光を取り出す構成も可能である。このような構成は両面出射方式と呼ばれる。

#### 【0111】

図 10 の場合、上面出射側と下面出射側の発光面積はおおむね等しいが、前述のように、層間膜を追加して画素電極の面積を大きくすれば、上面出射側の開口率が高く出来るることは言うまでも無い。

#### 【0112】

但し、本発明は上記の実施例に制約されない。例えば、表示領域 1404 は絶縁表面上に形成された非晶質半導体（アモルファスシリコン）をチャネル部とした TFT により構成し、ドライバ 1401 ~ 1403 は IC チップにより構成してもよい。IC チップは、COG 方式により基板上に貼り合わせたり、基板に接続する接続フィルムに貼り合わせたりしてもよい。非晶質半導体は、CVD 法を用いることで、大面積の基板に形成することができ、かつ結晶化の工程が不要であることから、安価なパネルの提供を可能とする。また、この際、インクジェット法に代表される液滴吐出法により導電層を形成すると、より安価なパネルの提供を可能とする。本実施例は、上記の実施の形態、実施例と自由に組み合わせることができる。

#### 【0113】

##### （実施の形態 9）

発光素子は、一対の電極間に、様々な材料からなる単数又は複数の層（以下電界発光層と称する）が挟まれた構造を有する。発光素子は、以下に示すような要因により、陽極と陰極が短絡する初期不良が生じることがある。第 1 の要因として、異物（ゴミ）の付着による陽極と陰極の短絡、第 2 の要因として、陽極の微細な突起（凸凹）により電界発光層

10

20

30

40

50

にピンホールが生じ、このピンホールに起因した陽極と陰極の短絡、第3の要因として、電界発光層が均一に成膜されずに、前記電界発光層にピンホールが生じ、このピンホールに起因した陽極と陰極の短絡などがある。第3の要因は、そもそも電界発光層の膜厚が薄いことも関係する。このような初期不良が発生した画素では、信号に応じた点灯及び非点灯が行われず、電流のほとんどすべてが短絡部を流れて素子全体が消光する現象が生じたり、特定の画素が点灯又は非点灯しない現象が生じたりして、画像の表示が良好に行われないという問題が発生する。上記問題を鑑み、上述したように、本発明は、発光素子に逆電圧を印加することができる表示装置及びその駆動方法を提供する。逆電圧の印加により、陽極と陰極の短絡部のみに局所的に電流が流れ、該短絡部は発熱する。そうすると、短絡部は酸化又は炭化して絶縁化する。その結果、初期不良が生じても、その不良を解消し、画像の表示を良好に行うことができる表示装置を提供することができる。なお、このような初期不良の絶縁化は、出荷前に行うとよい。

10

#### 【0114】

また、発光素子は、上述の初期不良とは別に、進行性不良が生じことがある。進行性不良とは、時間の経過に伴って、新たに発生した陽極と陰極の短絡である。このように、時間の経過に伴って新たに発生した陽極と陰極の短絡は、陽極の微細な突起により発生する。つまり、一対の電極間に電界発光層が挟まれた積層体には、時間の経過に伴って、陽極と陰極の短絡が発生する。上記問題を鑑み、上述したように、本発明は、出荷前だけではなく、定期的に逆電圧を印加する表示装置及びその駆動方法を提供する。逆電圧の印加により、陽極と陰極の短絡部のみに局所的に電流が流れ、短絡部は絶縁化する。その結果、進行性不良が生じても、その不良を解消し、画像の表示を良好に行うことができる表示装置及びその駆動方法を提供することができる。

20

#### 【0115】

また一対の電極間に電界発光層が挟まれた積層体には、順電圧を印加しても発光しない箇所がある。このような非発光性の不良はダークスポットとよばれ、また、時間の経過に伴って進行するため、進行性不良ともよばれる。ダークスポットは、電界発光層と陰極との接触不良により生じるもので、前記電界発光層と前記陰極の間に微少な空隙があり、その空隙が広がっていくことにより進行すると考えられている。しかしながら、逆電圧を印加すると、その空隙の広がりを抑制することができる。つまり、ダークスポットの進行を抑制することができる。従って、上述したように、逆電圧を印加する本発明は、ダークスポットの進行を抑制する表示装置及びその駆動方法を提供することができる。

30

#### 【0116】

##### (実施の形態10)

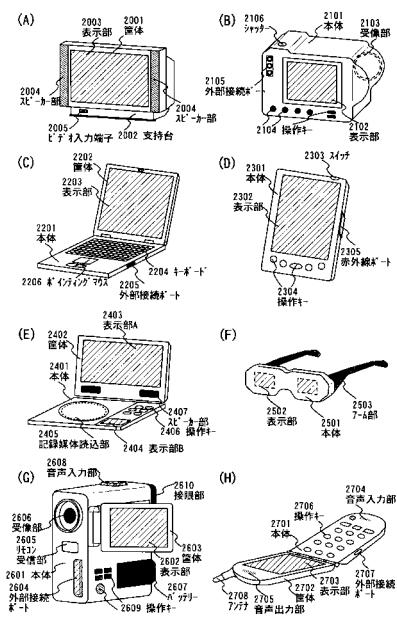

本発明を適用して作製される電子機器の一例として、デジタルカメラ、カーオーディオなどの音響再生装置、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(携帯電話、携帯型ゲーム機等)、家庭用ゲーム機などの記録媒体を備えた画像再生装置などが挙げられる。それら電子機器の具体例を図11に示す。

#### 【0117】

図11(A)は表示装置であり、筐体2001、支持台2002、表示部2003、スピーカー部2004、ビデオ入力端子2005等を含む。図11(B)はデジタルスチルカメラであり、本体2101、表示部2102、受像部2103、操作キー2104、外部接続ポート2105、シャッター2106等を含む。図11(C)はノート型パーソナルコンピュータであり、本体2201、筐体2202、表示部2203、キーボード2204、外部接続ポート2205、ポインティングマウス2206等を含む。

40

#### 【0118】

図11(D)はモバイルコンピュータであり、本体2301、表示部2302、スイッチ2303、操作キー2304、赤外線ポート2305等を含む。図11(E)は記録媒体を備えた携帯型の画像再生装置であり、本体2401、筐体2402、表示部A2403、表示部B2404、記録媒体読込部2405、操作キー2406、スピーカー部2407等を含む。表示部A2403は主として画像情報を表示し、表示部B2404は主と

50

して文字情報を表示する。図11(F)はゴーグル型ディスプレイであり、本体2501、表示部2502、アーム部2503を含む。

#### 【0119】

図11(G)はビデオカメラであり、本体2601、表示部2602、筐体2603、外部接続ポート2604、リモコン受信部2605、受像部2606、バッテリー2607、音声入力部2608、操作キー2609、接眼部2610等を含む。図11(H)は携帯端末のうちの携帯電話機であり、本体2701、筐体2702、表示部2703、音声入力部2704、音声出力部2705、操作キー2706、外部接続ポート2707、アンテナ2708等を含む。

#### 【0120】

上記の電子機器において、経時劣化する性質がある発光素子を有するパネルを具備した場合であっても、ショートすることなく逆電圧を印加することができるため、経時劣化を抑制できる。従って、エンドユーザに渡った後も、ユーザが電子機器を使用していないタイミングで逆電圧を印加することで、表示部の長寿命化が実現される。

#### 【0121】

本実施の形態は、上記の実施の形態と自由に組み合わせることができる。

#### 【0122】

##### (実施の形態11)

本実施の形態では、逆電圧印加用回路を信号線側へ接続する例を説明する。

#### 【0123】

図13(A)には、順電圧を印加し、発光素子が発光している状態を示す。図13(A)に示す逆電圧印加用回路116は、nチャネル型トランジスタ20、pチャネル型トランジスタ21を有するアナログスイッチ28を有する。nチャネル型トランジスタ20のゲート電極は、アノード線18に接続され、本実施の形態ではアノード線18は、5Vに保持されている。pチャネル型トランジスタ21のゲート電極は、一定の電位に保持された電源線、又はカソード線に接続され、本実施の形態では0Vに固定された第1の電源線19に接続されている。アナログスイッチ28の出力配線(出力端子)は、信号線57に接続されている。

#### 【0124】

このように逆電圧印加用回路116を信号線側へ接続する場合、逆電圧印加用トランジスタ17は不要となる。

#### 【0125】

その他の画素構成、及び画素が有するトランジスタは、図1(A)と同様であるため、説明を省略する。なお駆動用トランジスタのゲート電極を固定電位とすると、寄生容量や配線容量によるゲート・ソース間の電圧V<sub>gs</sub>が変化しないように動作させることができる。そのため実施の形態1と同様に、少なくとも順電圧印加時では、第2の電源線60の電位を固定電位とすると好ましい。

#### 【0126】

以上のような回路構成において、例えば信号線駆動回路が有する第2のラッチ回路113からビデオ信号が出力され、アナログスイッチ28へ入力される。本実施の形態では、ビデオ信号は、Low(例えば0V)と、High(例えば5V)のパルス状の信号を有するものとする。なお本実施の形態において、アナログスイッチ28へビデオ信号が入力されればよく、ビデオ信号はシフトレジスタ、又は第1のラッチ回路から入力されたり、さらに加えてバッファ回路等を介して入力されることもある。

#### 【0127】

このとき、アナログスイッチ28が有するnチャネル型トランジスタ20、及びpチャネル型トランジスタ21のいずれかがオンとなる。具体的には、Lowのビデオ信号が入力される場合、pチャネル型トランジスタ21がオンとなり、Highのビデオ信号が入力される場合、nチャネル型トランジスタ20がオンとなる。そして、走査線58が選択され、スイッチング用トランジスタ51がオンとなるとき、信号線57を介してビデオ信

10

20

30

40

50

号が画素 101 へ入力される。

**【0128】**

すると、駆動用トランジスタ 53、電流制御用トランジスタ 54 がオンとなり、発光素子 55 はビデオ信号に基づいて発光する。

**【0129】**

このとき必要に応じて、消去用トランジスタ 52 を動作させて、リセット線 59 を選択し消去期間を設ける。本実施の形態において、消去用トランジスタ 52 は n チャネル型のトランジスタを用いる。消去用トランジスタ 52 は p チャネル型のトランジスタを用いてもよいことは言うまでもない。消去用トランジスタやその動作は、特開 2001-343933 号公報を参考すればよく、それらと組み合わせて用いることができる。

10

**【0130】**

また、アノード線 18 及び第 2 の電源線 60 は、実施の形態 1 と同様に制御用回路 118 を接続してもよい。

**【0131】**

以上のような状態のとき、カソード線 69 が -10V、アノード線が 5V となっており、発光素子へは順電圧が印加される。

**【0132】**

図 13 (B) には、逆電圧を印加している状態を示す。逆電圧を印加するときは、ビデオ信号を Low ( 例えば 0V ) とする。すると、アナログスイッチ 28 が有するトランジスタは、両方ともオフとなり、ビデオ信号は画素へ入力されない。そのため、例え走査線 58 が選択されても、スイッチング用トランジスタ 51 へビデオ信号が入力されず、オフとなる。

20

**【0133】**

逆電圧を印加する直前のビデオ信号が High ( 例えば 5V ) であると、アナログスイッチ 28 がオンとなる恐れがある。そこで、逆電圧を印加する直前には、信号線 57 の電位を一度 Low ( 例えば 0V ) にする。具体的には、逆電圧印加期間の開始直前に、 Low ( 例えば 0V ) のビデオ信号を信号線 57 へ入力する。その後、アノード線とカソード線に逆電圧を印加する。例えば、アノード線 18 を -10V、カソード線 69 を 5V とする。

**【0134】**

30

このとき、駆動用トランジスタ 53 と、電流制御用トランジスタ 54 とをオンとし、逆電圧を効率よく印加する。特に、駆動用トランジスタ 53 を飽和領域で動作させる場合、L / W が大きくなるように設計されている場合、抵抗値が高いことが懸念される。

**【0135】**

そのため実施の形態 1 と同様な制御用回路 118 を用い、第 1 の n チャネル型トランジスタ 61 をオンとし、第 2 の n チャネル型トランジスタ 62 をオフとし、駆動用トランジスタ 53 のゲート電極に接続される第 2 の電源線 60 の電圧を -10V とすると好ましい。

**【0136】**

その結果、駆動用トランジスタ 53 のゲート電極へ印加されるゲート電圧を大きくでき、駆動用トランジスタ 53 の抵抗による逆電圧印加時の問題を低減することができる。なお駆動用トランジスタ 53 は、線形領域で動作させてもよい。

40

**【0137】**

また、駆動用トランジスタ 53 や電流制御用トランジスタ 54 の抵抗を解消するために、発光素子の第 1 の電極 ( 本実施の形態では陽極 ) と、アノード線 18 との間にダイオードを設けてもよい。

**【0138】**

このように逆電圧印加時にアナログスイッチ 28 をオフとすることにより、アノード線 18 と信号線 57 とがショートすることなく逆電圧を印加することができる。

**【0139】**

50

次に、逆電圧から順電圧を印加する状態、つまり各電位を戻す場合について説明する。逆電圧から順電圧を印加するとき、駆動用トランジスタ53のゲート電極は、-10Vに保持されているため、この状態で順電圧を印加すると、ビデオ信号と関係なく、発光素子55が発光してしまう恐れがある。

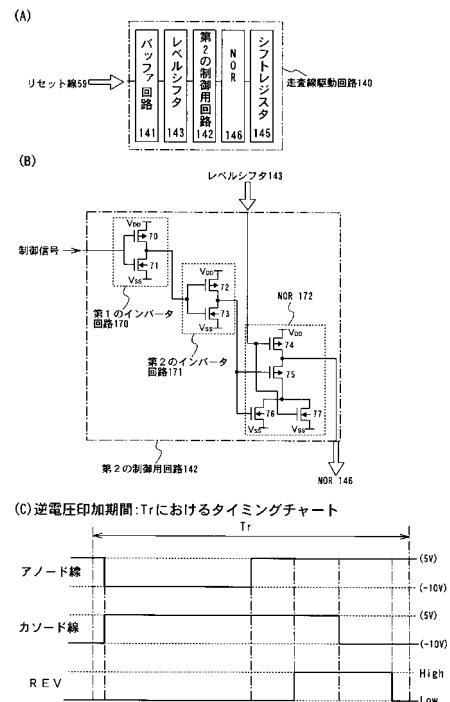

#### 【0140】

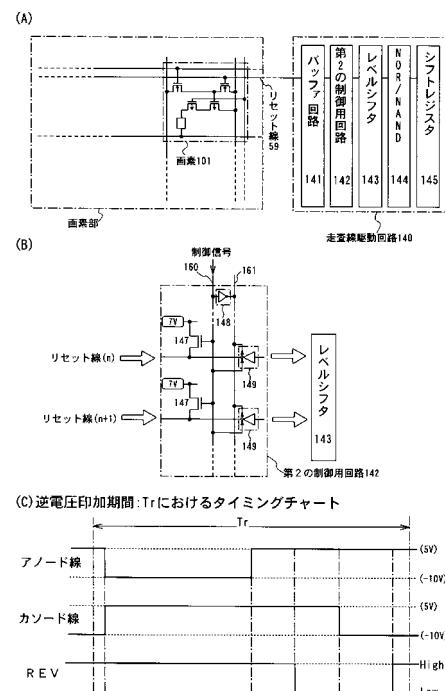

そこで例えば、図14(A)に示すように、バッファ回路141、レベルシフタ143、NOR/NAND回路144、シフトレジスタ145を有する走査線駆動回路140において、バッファ回路141と、レベルシフタ143との間に第2の制御用回路142を設ける。なお、バッファ回路141の配置は適宜設計することができるため、第2の制御用回路142は少なくとも各リセット線と接続すればよい。つまり第2の制御用回路142は、画素部とレベルシフタ143との間に設ければよい。10

#### 【0141】

第2の制御用回路は、順電圧を印加しているときに走査線駆動回路から供給される走査線を選択する信号が入力され、逆電圧から順電圧に変えるときに駆動用トランジスタ53、又は電流制御用トランジスタ54をオフとするように制御する機能を有していればよい。。

#### 【0142】

図14(B)には、第2の制御用回路142の具体的な構成を示す。第2の制御用回路142は、一つのインバータ回路148、リセット線毎に設けられたpチャネル型のトランジスタ147、及びクロックドインバータ149を有する。トランジスタ147の第1の電極はリセット線59に接続され、ゲート電極は第3の電源線160接続され、第2の電極は7Vに保持されている。インバータ回路148は、第3の電源線160、及び第4の電源線161に接続されている。クロックドインバータ149は、第1の端子と第3の電源線160が接続され、第2の端子と第4の電源線161が接続され、入力配線とりセット線59が接続され、出力配線とレベルシフタ143が接続されている。20

#### 【0143】

このような第2の制御用回路142では、第3の電源線160へ制御信号(REV)が入力され、リセット線59の電位を制御することができる。具体的には、第3の電源線160へLOWの制御信号が入力されると、トランジスタ147がオンとなり、リセット線59は7Vとなる。そして、順電圧を印加するためアノード線を5Vとする。すると、消去用トランジスタ52はオンとなり、電流制御用トランジスタ54のゲート電位は5Vとなる。このとき、電流制御用トランジスタ54はオフとなる。その後、カソード線の電位を-10Vとし、順電圧を印加する。30

#### 【0144】

このように、第2の制御用回路142により、電流制御用トランジスタ54をオフとすることにより、発光素子55はビデオ信号に基づき発光することができる。なお本実施の形態では、電流制御用トランジスタ54をオフとする場合で説明したが、駆動用トランジスタ53をオフするよう制御しても構わない。

#### 【0145】

第2の制御用回路142は、全リセット線59に接続されており、全リセット線59へ制御信号を同時に入力し、電流制御用トランジスタ54をオフとすることができます。40

#### 【0146】

また、このような動作をリセット線ごとに行ってもよい。この場合、逆電圧印加期間Trにおいて順にリセット線を選択し、順に制御信号を入力していくべき。

#### 【0147】

以上のような動作により、逆電圧から順電圧に戻す場合、ビデオ信号と関係なく、発光素子55が発光することを防止できる。すなわち、ビデオ信号に基づいて発光素子は発光する。

#### 【0148】

図14(C)には、逆電圧印加期間Trにおける、アノード線18、カソード線69に50

印加される電圧、及び第3の電源線160に入力される制御信号(REV)の具体的なタイミングチャートを示す。

#### 【0149】

まず、アノード線18と、カソード線69とに逆電圧を印加する。具体的には、アノード線18を-10Vとし、カソード線69を5Vとする。このときREVはHighとなっている。所定の時間経過後、アノード線18の電位を5Vへ戻し、次いでREVの電位をLowとすると、消去用トランジスタ52がオンとなる。そして、リセット線59の電圧を7Vとなり、電流制御用トランジスタ54がオフとなる。このとき電流制御用トランジスタ54がオフとなっているため、発光素子55が発光することはない。

#### 【0150】

なおアノード線の電位を5Vとするタイミングと、REVの電位をLowとするタイミングはどちらが先でも構わない。但し、アノード線の電位を5Vとした後、REVの電位をLowとすると、消去用トランジスタ52へ印加される電圧値を不要に大きくすることが防げるため好ましい。

#### 【0151】

なお図14では、制御信号をLowの電位を有する場合で説明したが、インバータ回路148の入力と、出力を逆の接続とし、Highの制御信号を第4の電源線161へ入力してもよい。

#### 【0152】

図12(A)には、図14と異なる第2の制御用回路を、NOR回路146とレベルシフタ143との間に設ける場合を示す。

#### 【0153】

図12(B)には、第2の制御用回路142の具体的な構成を示す。第2の制御用回路は、クロック信号が入力される第1のインバータ回路170は、pチャネル型のトランジスタ70、nチャネル型のトランジスタ71を有する。第1のインバータ回路170の出力配線に接続される第2のインバータ回路171は、pチャネル型のトランジスタ72、nチャネル型のトランジスタ73を有する。第2のインバータ回路171の出力配線と、NOR146の出力配線に接続されるNOR172は、直列に接続されたpチャネル型のトランジスタ74、75、並列に接続されたnチャネル型のトランジスタ76、77を有する。

#### 【0154】

このような第2の制御用回路では、Highの制御信号が第1のインバータ回路170の入力配線から入力されると、pチャネル型トランジスタ74がオフ、nチャネル型トランジスタ77はオンとなり、Lowの信号がバッファ回路へ出力される。このとき消去用トランジスタ52をオンとすることができます。その後カソード線69を-10Vとして順電圧を印加すると、電流制御用トランジスタ54をオフとすることができます。

#### 【0155】

このように、第2の制御用回路142により、電流制御用トランジスタ54をオフとすることにより、発光素子55はビデオ信号に基づき発光することができる。なお本実施の形態では、電流制御用トランジスタ54をオフとする場合で説明したが、駆動用トランジスタ53をオフするよう制御しても構わない。

#### 【0156】

図12(C)には、逆電圧印加期間Trにおける、アノード線18、カソード線69に印加される電圧、制御信号(REV)の具体的なタイミングチャートを示す。

#### 【0157】

まず、アノード線18と、カソード線69とに逆電圧を印加する。具体的には、アノード線18を-10Vとし、カソード線69を5Vとする。このときREVはLowとなっている。所定の時間経過後、アノード線18の電位を5Vへ戻し、次いでREVの電位をHighとすると、消去用トランジスタ52がオンとなる。そして、リセット線59の電圧を7Vとする。このとき、電流制御用トランジスタ54がオフとなっているため、発光

10

20

30

40

50

素子 5 5 が発光してしまうことはない。

【 0 1 5 8 】

なおアノード線の電位を 5 V とするタイミングと、 R E V の電位を H i g h とするタイミングはどちらが先でも構わない。但し、アノード線の電位を 5 V とした後、 R E V の電位を H i g h とすると、消去用トランジスタ 5 2 へ印加される電圧値を不要に大きくすることが防げるため好ましい。

【 0 1 5 9 】

以上のような動作により、逆電圧から順電圧に戻す場合、ビデオ信号と関係なく、発光素子 5 5 が発光することはない。すなわち、ビデオ信号に基づいて発光素子は発光する。

【 0 1 6 0 】

なお本実施の形態では、発光素子の第 1 の電極は、陽極とするが、第 1 の電極が陰極となる画素構成を用いてもよい。

【 0 1 6 1 】

本実施の形態により、新たな画素回路を有する表示装置に対して、発光素子の劣化を制御し、信頼性を向上させるため逆電圧を印加する回路構成、及びその方法を提供することができる。

【 0 1 6 2 】

なお、本実施の形態で示した電圧の値は一例であり、これに限定されるものではない。

【 図面の簡単な説明 】

【 0 1 6 3 】

【 図 1 】本発明の表示装置及びその駆動方法を説明する図。

【 図 2 】本発明の表示装置及びその駆動方法を説明する図。

【 図 3 】本発明のタイミングチャートを説明する図。

【 図 4 】画素構成を示す図。

【 図 5 】本発明の表示装置及びその駆動方法を説明する図。

【 図 6 】画素上面図の一実施例を示す図。

【 図 7 】画素上面図の一実施例を示す図。

【 図 8 】下面出射方式の表示装置の断面図を示す図。

【 図 9 】上面出射方式の表示装置の断面図を示す図。

【 図 1 0 】両面出射方式の表示装置の断面図を示す図。

【 図 1 1 】本発明の電子機器を説明する図。

【 図 1 2 】本発明の表示装置及びその駆動方法を説明する図。

【 図 1 3 】本発明の表示装置及びその駆動方法を説明する図。

【 図 1 4 】本発明の表示装置及びその駆動方法を説明する図。

10

20

30

【図1】

#### (B) 逆電圧印加時

【図3】

【図2】

(B) 逆電圧印加時

【図4】

(B)

- 16001: 借号線

- 16002: 第1の電源線

- 16003: ゲート固定電位線

- 16004: 走査線

- 16005: リセット線

- 16006: スイッチング用トランジスタ

- 16007: 消去用トランジスタ

- 16008: 制御用トランジスタ

- 16009: 駆動用トランジスタ

- 16010: 容量手段

- 16011: 表示電極

- 16012: EL素子

- 16013: 第2の電源線

【図5】

【図6】

17001 信号線

17002 電源線

17003 固定電位線

17004 先走部

17005 リセット線

17006 清除用トランジスタ

17008 制御用トランジスタ

17009 動作用トランジスタ

17010 取扱手扱

17011 固定電極

【図7】

18001 信号線

18002 電源線

18003 固定電位線

18004 先走部

18005 リセット線

18006 シフト線

18008 スイッチ用トランジスタ

18009 制御用トランジスタ

18009 动作用トランジスタ

18011 取扱手扱

18012 制御用トランジスタ

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

(B) 逆電圧印加時

【図14】

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 623C

G 09 G 3/20 623D

G 09 G 3/20 624B

G 09 G 3/20 670K

H 05 B 33/14 A

審査官 福村 拓

(56)参考文献 国際公開第2004 / 086344 (WO , A1 )

特開2003 - 208127 (JP , A)

特開2003 - 051384 (JP , A)

特開2003 - 280576 (JP , A)

特開2003 - 150110 (JP , A)

特開2005 - 031598 (JP , A)

特開2003 - 195814 (JP , A)

(58)調査した分野(Int.Cl. , DB名)

G 09 G 3 / 30

G 09 G 3 / 20