(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3851679号

(P3851679)

(45) 発行日 平成18年11月29日(2006.11.29)

(24) 登録日 平成18年9月8日(2006.9.8)

(51) Int.C1.

F 1

G02B 26/08 (2006.01)

HO4N 5/74 (2006.01)G02B 26/08

HO4N 5/74

E

B

請求項の数 2 (全 17 頁)

(21) 出願番号 特願平8-97041

(22) 出願日 平成8年4月18日(1996.4.18)

(65) 公開番号 特開平8-334709

(43) 公開日 平成8年12月17日(1996.12.17)

審査請求日 平成15年4月17日(2003.4.17)

(31) 優先権主張番号 424021

(32) 優先日 平成7年4月18日(1995.4.18)

(33) 優先権主張国 米国(US)

(73) 特許権者 590000879

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国テキサス州ダラス、ノース

セントラルエクスプレスウェイ 135

OO

(74) 代理人 100066692

弁理士 浅村 晃

(74) 代理人 100072040

弁理士 浅村 肇

(74) 代理人 100091339

弁理士 清水 邦明

(74) 代理人 100094673

弁理士 林 鉛三

最終頁に続く

(54) 【発明の名称】空間光変調器

## (57) 【特許請求の範囲】

## 【請求項1】

空間変調器であって、

基板に配置された制御回路と、

前記基板近傍に配置され、前記制御回路に接続された第1のアドレス電極と、

前記第1のアドレス電極の上方で、当該第1のアドレス電極と電気的に接続された第2のアドレス電極と、

前記第1のアドレス電極の上方に配置されたヨークと、

前記ヨークに電気的に接続された画素であって、前記ヨークに支持されて前記第2のアドレス電極上方に配置された画素と、および

前記ヨークに接続され、かつ当該ヨークを支持する少なくとも一つのヒンジと、を備え、当該ヒンジは、前記ヨークと前記第1のアドレス電極、および前記画素と前記第2のアドレス電極との間の静電力で、前記ヨークと前記画素を第1の方向へ撓み可能とし、前記静電力は前記制御回路からの信号に応答する、

ことを特徴とする空間変調器。

## 【請求項2】

請求項1に記載の空間変調器であって、さらに、

前記基板近傍に配置された第3のアドレス電極であって、前記ヨークは前記第3のアドレス電極の上方に配置され、および

前記第3のアドレス電極上方に配置されて当該第3のアドレス電極に電気的に接続され

た第4のアドレス電極と、前記ヨークに支持された前記画素は当該第4のアドレス電極上方に配置され、

前記第3及び第4のアドレス電極は前記制御回路に電気的に接続され、

前記ヒンジは、前記ヨークと前記第3のアドレス電極との間および前記画素と前記第4のアドレス電極間との静電力で、前記ヨークと前記画素を第2の方向に撓み可能とし、前記静電力は前記制御回路からの信号に応答する、

ことを特徴とする空間変調器。

【発明の詳細な説明】

【0001】

【産業上の利用分野】

10

本発明は一般的に、光学的光画像を形成する入射光を変調する光空間光変調器に関連し、更に詳細には、アドレス回路上に形成されるバイステイブル(bistable)・マイクロミラーのアレイを有するデジタル・マイクロミラー・デバイス(DMD)に関する。

【0002】

【従来の技術及びその課題】

空間光変調器(以下SLM)には、光学的情報処理の分野において、投射ディスプレイ、ビデオ・モニター、グラフィック・モニター、テレビ及び電子写真プリントなど多数の用途がある。SLMは空間パターンの入射光を変調し、電気的又は光学的入力に対応する光画像を形成する装置である。入射光は、フェーズ、強度、偏光、又は方向において変調され得る。光変調は、電子光学的又は磁気光学的効果を示す種々の材料によって、又は表面変形による光を変調する材料によって達成される。

20

【0003】

SLMは典型的に、アドレス可能な画像素子(画素)の領域又は線形アレイから形成される。ソース画素データは、まず通常SLMの外にある関連する制御回路によってフォーマットされ、その後、1度に1フレームが画素アレイにロードされる。この画素データは、種々のアルゴリズム、つまり、トップからボトムへ順に1度に1画素ラインを、あるいは一つおきの画素ライン、例えば奇数列の画素を、トップからボトムへ順にアドレス指定し、その後偶数画素ラインヘリターンすることによってインターリーブするなど、を用いて画素アレイに書き込まれ得る。陰極線管(CRT)では、このデータ書き込み技術は、高電力電子ガンが発光体の画素を左から右へ一度に横切ってスキャンするラスター化として周知である。この画素アドレス書き込み方式は液晶ディスプレイ(LCD)にも応用することができる。

30

【0004】

テキサス州ダラスのテキサス・インスツルメンツの最近のイノベーションは、デジタル・マイクロミラー・デバイス又は変形ミラー・デバイス(総称してDMD)である。DMDはディスプレイ、プロジェクタ、及びハードコピープリンタの用途に適している電子的/機械的/光学的SLMである。DMDは、モノリシック単一チップ集積回路SLMであり、17ミクロンセンター上の16ミクロン四方の可動マイクロミラーの高密度アレイを有する。これらのミラーは、SRAMアレイセル及びアドレス電極を有するアドレス回路上に形成される。各ミラーはDMDアレイの1画素を形成し、バイステイブル、つまり2つの位置のうち1つの位置で安定(ステイブル)であり、ミラー上に向けられた光源は2方向のうち一方に反射される。1つの安定“オン”状態において、そのミラーへの入射光は投射レンズへ反射され、表示スクリーン又はプリンタのフォトセンシティブ素子にフォーカスされる。他方の“オフ”ミラー位置において、ミラーへ向けられる光は光アブソーバーに偏向される。アレイの各ミラーは、投射レンズ又は光アブソーバーのいずれかへ入射光を導くよう個別に制御される。投射レンズは、表示スクリーン上へ、画素ミラーから変調された光を最終的にフォーカスし拡大し、表示する場合の画像をつくる。DMDアレイの各画素ミラーが“オン”的位置である場合、表示される画像は明るい画素のアレイであり得る。

40

【0005】

50

D M D デバイス及びその利用についてのより詳細な説明は、本発明と同じ譲渡人に譲渡されている、Hornbeckの米国特許番号第5,061,049号、発明の名称『空間光変調器およびその方法』、DeMondらの米国特許番号第5,079,544号、発明の名称『標準独立デジタル化ビデオシステム』、及びNelsonの米国特許番号第5,105,369号、発明の名称『プリンティング・システム露光モジュール整合方法及び製造方法』を参照されたい。本発明と同じ譲渡人に譲渡され、参照のためここに引用する、米国特許番号第5,278,652号、発明の名称『パルス幅変調されたディスプレイ・システムを用いるためのD M D アーキテクチャ及びタイミング』に記載されたように、画像を形成する画素のグレイ・スケールは、ミラーのパルス幅変調技術によって達成される。

## 【0006】

10

D M D はそれが真にデジタル・ディスプレイ・デバイスであり、集積回路ソリューションである点で革新的である。D M D の進歩及び変化は、共に譲渡される種々の特許を参照することによって理解され得る。D M D 空間光変調器の『第1世代』はミラーとビームが同一のものである可撓性ビームを実現した。つまり、電子静電力がミラーと下部アドレス電極との間に作られ、その撓みを誘導する。これらのミラーの撓みは可変であり、アナログモードで作動し、リーフ・スプリング又は片持ちはりビームで構成され得ることは、共に譲渡された、Hornbeckの米国特許番号第4,662,746号、発明の名称『空間光変調器およびその方法』、Hornbeckの米国特許番号第4,710,732号、発明の名称『空間光変調器およびその方法』、Hornbeckの米国特許番号第4,956,619号、発明の名称『空間光変調器』、Hornbeckの米国特許番号第5,172,262号、発明の名称『空間光変調器およびその方法』に開示されており、ここに参考のため引用する。

## 【0007】

20

この第1世代のD M D は、デジタル又はバイステイブル・デバイスとしても実施され得る。ビーム(ミラー)は、ねじれヒンジで支持され、ミラー片が着地パッド(landing pad)上に着地するまで、2方向のうち1方向に10度軸回転するミラーを有し得る。このような実施例は、共に譲渡されたHornbeckの米国特許番号第5,061,049号、発明の名称『空間光変調器およびその方法』に開示されている。ミラー片と着地パッドとの間のファン・デル・ワールスの力を制限するため、着地パッドは、着地パッド上に形成される配向(oriented)单分子層によって不活性化され得る。この单分子層は、ファン・デル・ワールの力を減少させ、ミラーが電極に膠着(stick)するのを防ぐ。この技術は、共に譲渡されたHornbeckの米国特許番号第5,331,454号、発明の名称『D M D のための低リセット電圧プロセス』に開示されており、参考のためここに引用する。

## 【0008】

30

D M D の『第2世代』は、共に譲渡された米国特許番号第5,083,857号、発明の名称『多レベル変形可能ミラー・デバイス』及び同時係属特許出願で1993年12月21日に出願された、出願番号第08/171,303、発明の名称『改良された多レベル・デジタル・マイクロミラー・デバイス』で実施されている。この第2世代のデバイスでは、ミラーはヨーク上に持ち上げられ、このヨークは一対のねじれヒンジによってアドレス回路上に懸架されている。この出願の図3cに示すように、電子静電力は、高架ミラー及び高架電極の間に生じる。回転するときに着地電極と接触するのはヨークであり、ミラー片は、どの構成物とも接触しない。ミラーの約50%である、ヨークのより短いモーメントのアームは、ミラー片が自由に動くために、リセットパルスによりエネルギーがより効果的にミラーに接続されるようにする。共振リセットパルスをミラーに提供することによって、ミラーが旋回(ピボット)構造を着地電極から自由にすることは、共に譲渡された米国特許番号第5,096,279号、発明の名称『空間光変調器およびその方法』、及び米国特許番号第5,233,456号、発明の名称『共振ミラーとその製造方法』に開示されている。しかし、ヨークがアドレス電極の表面領域をわずかに減少させるため、第1世代のデバイスに比べ、ミラーと高架アドレス電極との間に生じるアドレス・トルクが多少犠牲になる。

## 【0009】

50

より効率的なリセット動作を有する改良されたDMDを提供し、より多くのアドレス・トルク、ラッチ・トルク、及びアドレス保持トルクを有するデバイスを開発することが望まれている。改良されるデバイスは、基準の製造工程を用いることによって製造されることが好ましい。

#### 【0010】

##### 【課題を達成するための手段及び作用】

本発明は、ヨークが第1のアドレス電極対の実質的な部分を覆うように、ヒンジと平行にヨークを水平に伸ばすことによって、DMD空間光変調器としての技術的利点を達成する。第2の高架アドレス電極対が、ヨークの横およびヨークに支えられた高架ミラーの下に設けられる。アドレス・トルクは、第1のアドレス電極対とヨークの間、および第2の高架アドレス電極対と高架ミラーの間で達成される。ヨークは、ミラーが高架アドレス電極に関連して配置されるより下部アドレス電極により近接して配置される。対向部材間のユニット(単位)領域毎の力は距離の自乗分の一に比例するため、ヨークと下部の第1のアドレス電極対の間のユニット領域毎の力は、ミラーと第2の高架アドレス電極対の間のユニット領域毎の力より4倍の大きさまで大きくなる。本発明は、従来の世代に比べて、処理工程を変えることなく、高度なアドレス・トルク、ラッチ・トルク、アドレス保持トルク、及び復元力を有する。

#### 【0011】

本発明は、基板を有する空間光変調器を構成する。第1の部分を有するアドレス回路は基板に近接して提供され、更に基板上に高架される第2の部分を有する。ヨークは、アドレス回路の第1の部分上に支持される。少なくとも1つのヒンジがヨークに接続され、ヨークを支持し、ヒンジはアドレス回路の第1の部分上のヨークを撓ませ得る。画素は、ヨークの上に持ち上げられ、ヨークに支持され、この画素は高架アドレスの第2部分の上に位置する。このアドレス回路の第1及び第2の部分は、互いに電気的に接続され、それによって第1及び第2の部分に提供される電位は、2平面に電子静電力を生じさせる。まず、電子静電力はヨークとアドレス回路の第1の部分の間に、次に、高架画素と高架第2の部分との間に生じる。

#### 【0012】

ヨークと第1の部分との間の距離は、画素と高架第2の部分との間で定められる距離の約半分である。ヨークとアドレス回路の第1の部分の対向する表面領域は、高架画素と高架第2の部分との間に生じるアドレス・トルクより約4倍大きいアドレス・トルクを実現する。ネット・アドレス・トルクは付加的であり、前の世代のDMDデバイスによって生じるアドレス・トルクよりも実質的に大きい。

#### 【0013】

ヨークは、ヨーク軸の両側に一対のヨーク片を有する、蝶のような形をしていることが好ましい。回転すると、一対のヨーク片の一方が着地パッドに着地し、それにより支持され、持ち上げられる画素ミラーは、どの構造物とも離れたままになる。このように、リセット・パルスは、ミラーに提供され得、良好なリセット動作を達成するため、ミラーに共振する周波数であることが好ましい。ヨークは、実質的にヒンジと同じ平面であることが好ましく、ヒンジが正確な整合及びバランスで形成されるように、單一エッチング工程を用いて形成され得る。

#### 【0014】

空間光変調器は、アドレス回路に接続される制御回路を更に有する。この制御回路は、アドレス回路の第1及び第2の部分の両方にアドレスデータを提供し、画素を撓ませる。アドレス回路の第1の部分はパッドを有し、回転の画素軸の両側に提供され、離れているアドレス回路の第2の部分はこのヨーク軸の両側の画素の下に提供されることが好ましい。制御回路は、これらの一連のアドレス指定する部分のいずれか1つにアドレスデータを提供し、アドレス指定する部分の方へヨークとミラーを撓ませ、アドレス指定された第1及び第2の部分の方へヨークおよびミラーを撓ませる。画素はミラーであり、ヒンジに対して45度の角度でジオメトリックに配向されたの四角形であり、暗視界光学系(darkfiel

10

20

30

40

50

d optics) によって感知される画素の端に沿って生じる回折項 (diffraction terms) を最小化することが好ましい。

【0015】

一対のアドレス電極上に懸架されたヨークを有し、第2のアドレス電極対上に伸びる高架ミラーを支持するDMDデバイスは、アドレス電極と旋回構造物、つまり、ヨークとミラー、との間の引付ける (attractive) 領域を大きく増加させる。アドレス基板上の下部アドレス電極は、金属3から構成され、アトラクティブ領域を最大にするよう注意深く設計され、ミラー及びヨークと同じ電位を有する着地電極上にヨーク片を着地させる。ミラーの高架アドレス電極は、第2世代のデバイスから修正されて本発明の延長ヨークを提供 (accommodate) 一方、ミラーと高架電極の間に生じ得るトルクのほとんどを維持する。高架電極の減少された領域の結果の損失トルクはアドレス・トルク上に伸びるヨークによって補償されるよりも多く、これらのアドレス電極は、高架電極に対し位置付けられるミラーよりヨークからその半分の距離に位置付けられる。第2世代のデバイスに比べて、生じるネット・アドレス・トルクは、約2倍 (a factor of two) 大きい。本発明は更に、より大きいラッチ・トルク及びアドレス保持トルクを達成する。

【0016】

【実施例】

本発明の一実施例を図面を参照して説明する。

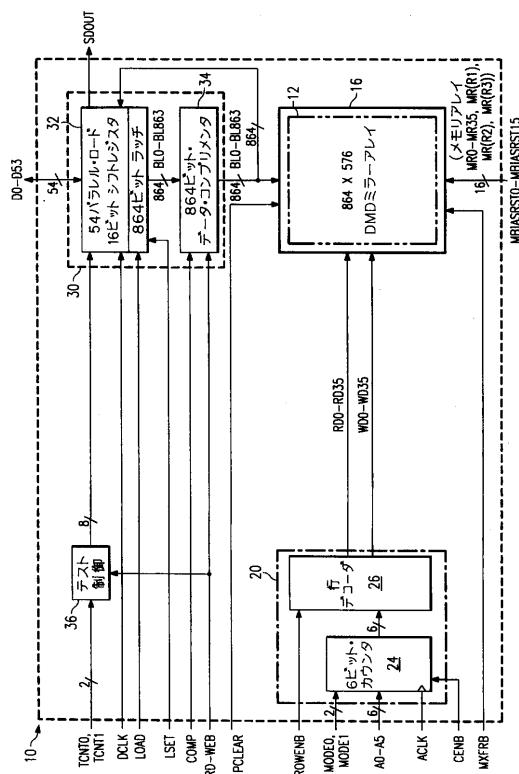

図1において、デジタル・マイクロミラー・デバイス (DMD) を有する空間光変調器を全体として10で示す。DMD10は、單一チップ集積回路であって、864×576マイクロミラー・アレイ12を有するように示されている。アレイ12は、864×36メモリセルアレイ16上にモノリシックに形成される。図2に示すように、メモリセルアレイ16を形成する36列のメモリセル (MR0 - MR35) 列の各メモリセルは、ある特定の16画素グループ (18) に関連され、制御する。各メモリセルは、次の1ビット静電ランダムアクセスメモリ (SRAM) 及びその一次セルによってフィードされる二次の1ビットSRAMセルを有する。メモリセルの各864列のそれぞれに接続される864ビットラインBL0 - BL863がある。列画素データは、関連するビットラインBL0 - BL863を介して、アドレス指定された一次メモリセル行MRnにロードされる。一次メモリセルは、それぞれWDn又はRDnとして識別される、関連する行の書き込み可能又は読み出し可能ラインをイネーブルすることによってアドレス指定され、WPnは行MRnの各一次セルのイネーブル入力に接続される。この画素データは、グローバル制御ラインMXFRBをイネーブルすることによってそれぞれ二次セルへ一次セルからラッチされ、MXFRBはアレイ16の全ての二次セルのイネーブル入力に接続されている。二次メモリセルは本質的にシャドウ・ラッチとして作動し、データは一次メモリセルから二次メモリセルへロードされ得、一次メモリセルが二次メモリセルのメモリセル内容に影響を及ぼすことなく新しい画素データを実質的に再ロードすることを可能にする。シャドウ・ラッチ技術の付加的説明は、共に譲渡された同時係属中の特許出願番号08/389,673で1995年2月16日に出願された、発明の名称『單一ビットライン・デュアル・ラッチ・メモリセルを有する空間光変調器』にされており、参照のためここに引用する。行アドレス及び列データロード回路、及びDMD10のテスト制御機能を有する制御回路の更に詳しい説明は、共に譲渡された同時係属中の特許出願番号08/373,692で1995年1月17日に出願された、発明の名称『モノリシック・プログラマブル・フォーマット・ピクセル・アレイ』にされており、参照のためここに引用する。

【0017】

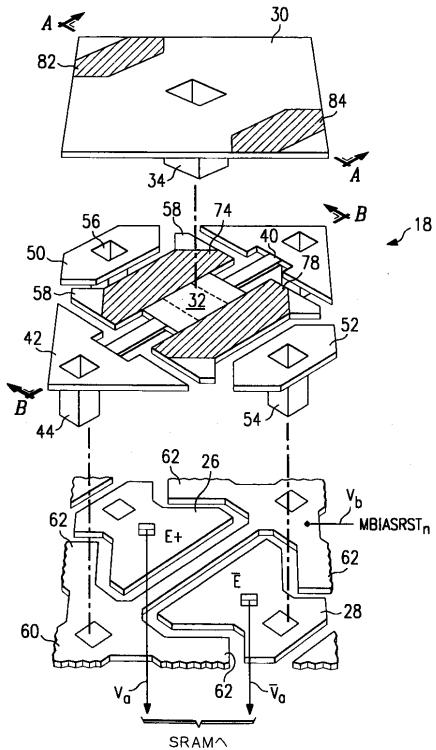

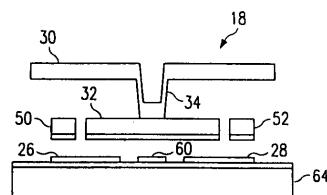

図2はミラー・アレイ12の1つの画素18を示す。二次メモリセルのデータは、一対の相補性アドレス電極ラインに提供され、各ラインは順に、アレイ12の各画素18の下に形成され、画素に関連する2つのアドレス電極26及び28のうち1つに接続される。画素18は、支持ポスト34によって、全体として32で示すヨークの上に支持され、上に持ち上げられる四角形ミラー30を有する。支持ポスト34は、ミラーの中央から下方へ伸び、図示するように、そのねじれ軸にそってヨーク32の中央に取付けられ、ヨーク32

10

20

30

40

50

上のミラー 3 0 の質量の中心のバランスをとる。ヨーク 3 2 は、通常は蝶の形であり、あとで詳細に説明するが、一対のねじれヒンジ 4 0 によって中央軸に沿って軸 ( axially ) 支持される。各ねじれヒンジ 4 0 の反対の端はそれぞれヒンジ支持ポスト 4 4 の頂点に定められているヒンジ支持ポストキャップ 4 2 に取付けられ、支持される。一対の高架ミラー・アドレス電極 5 0 及び 5 2 は、それぞれアドレス支持ポスト 5 4 及び 5 6 によって支持される。

#### 【 0 0 1 8 】

アドレス支持ポスト 5 4 及び 5 6 、及びヒンジ支持ポスト 4 4 は、アドレス電極 5 0 及び 5 2 、ねじれヒンジ 4 0 、及びヨーク 3 2 をバイアス / リセット・バス 6 0 、及び一対の基板レベルアドレス電極パッド 2 6 及び 2 8 から離して上方に支持する。ミラー 3 0 及び 10 ヨーク 3 2 が共に、ヒンジ 4 0 により定められるヨークのねじれ軸の回りを回転するとき、ヨーク 3 2 の撓んだ側の一対のヨーク片 5 8 は着地サイト ( site ) 6 2 に着地し、バイアス / リセット・バス 6 0 とエンゲージ ( engage ) する。

#### 【 0 0 1 9 】

図 3 と共に図 2 を参照して、本発明の好ましい実施例に従った画素 1 8 の利点を詳細に説明する。ミラー 3 0 及びヨーク 3 2 の回転は、2 方向のうち一方向になされ得、図 5 に示し後で説明するようなバイステイブル状態及びモジュール入射光を達成する。アドレス電圧が 2 つのアドレス電極パッド 2 6 又は 2 8 の一方に、及び関連する電極支持ポスト 5 4 及び 5 6 を介して、対応する高架ミラー・アドレス電極 5 0 又は 5 2 の一方に供給される。このアドレス電圧は、CMOS ロジック回路と互換性のある 5 ボルトであり得るが、必要であれば他のレベルであっても良い。同時に、+ 15 ボルトのバイアス電圧がバイアス / リセット・バス 6 0 に、支持ポスト 4 4 、ポストキャップ 4 2 、及びヒンジ 4 0 を介してヨーク 3 2 に、更に支持 3 4 を介してミラー 3 0 に供給される。本発明は、図 2 にハッチングされた領域で示す 2 つの場所で対向する表面間に電子静電力を供給する技術的利点を提供する。これらの電子静電引力は、図 3 の 7 0 、 7 6 、 8 0 、及び 8 2 にも示している。

#### 【 0 0 2 0 】

例示のため、図 2 及び図 3 に示されるように、ミラー 3 0 及びヨーク 3 2 が逆時計回りに回転される場合、0 ボルト電位がアドレスライン V a 上に供給され、相補性アドレスライン V a 上に + 5 ボルトが供給される。その後、+ 15 ボルト電位がバイアス / リセット・バス 6 0 へバイアスライン V b 上に供給され、ヨーク 3 2 及びミラー 3 0 上に + 15 ボルト電位を供給する。20 ボルトの電位差から電子静電引力がアドレス電極 2 6 及びヨーク 3 2 のこの基板アドレス電極の上の部分の間に生じ、この力を全体として 7 0 で示す。アドレス電極 2 6 に懸かるヨーク 3 2 の対応する部分を、ハッチングされた部分 7 4 で示す。逆に、ミラー 3 0 が時計回りに回転する場合、0 ボルト電位が相補性アドレス電極 2 8 に供給され、7 6 で引力が生じる。アドレス電極 2 8 に懸かるヨーク 3 2 の対応する部分をハッチングされた部分 7 8 で示す。

#### 【 0 0 2 1 】

ヨーク 3 2 の半分と下部アドレス電極 2 6 の間に電子静電引力が生じる一方、図 3 に 8 0 で示すような電子静電引力が高架アドレス電極 5 0 とミラー 3 0 の間にも生じる。この電子静電引力は、8 2 で示す、高架アドレス電極 5 0 上に定められるミラー 3 0 の部分の間に作られる電圧電位によって生じる。アドレス電極 5 2 上に懸けられるミラー 3 0 の部分を 8 4 で示す。従って、1 つのアドレス電極 2 6 又は 2 8 をアドレス指定することによって、対応する高架アドレス電極 5 0 又は 5 2 にアドレス電圧を順に供給し、電子静電力が 7 0 及び 8 0 又は 7 6 又は 8 2 で示す 2 つの場所で生じる。この 0 ボルトアドレス電位を 2 つのアドレス電極 2 6 又は 2 8 の一方に選択的に供給することにより、バイアス・バス 6 0 に、そして結果的にヨーク 3 2 及びミラー 3 0 に + 15 ボルト電位が供給されると、ミラー 3 0 及びヨーク 3 2 をどちらの方向に回転させるかが決定される。

#### 【 0 0 2 2 】

図 3 において、全体的にヨーク 3 2 と同平面であり、それぞれ約 1 ミクロンの距離でアド 50

レス電極 26 及び 28 の上方に位置している高架アドレス電極 50 及び 52 を示す。高架アドレス電極 50 及び 52 と上のミラー 30 との距離は、この距離の約倍、つまり約 2 ミクロンである。対向する表面間の引力が対向する表面間の距離の二乗分の一の関数として直接変化するため、ヨーク 32 とアドレス電極 26 及び 28 の間に生じるユニット領域毎の電子静電引力は、ミラー 30 と対応する高架アドレス電極 50 及び 52 の間に生じる引力の大きさの 4 倍である。ねじれ軸の両側に生じる力は、付加的であり、共にミラー 30 とヨーク 32 をアドレス電極の方向へ回転させる。

#### 【 0023 】

代替実施例において、高架電極 50 及び 52 、及び対応する支持ポストはなくてもよい。この実施例において、ヨーク 32 の上のミラー 30 の高さは、たったの約 1 ミクロンで、下部電極 26 及び 28 のディスタル・ローブ (distal lobe) により強い引力を達成する。撓むとき、ミラー 30 はアドレス電極 26 及び 28 の対応するディスタル・ローブへ向かって回転するが、まだエンゲージしない。この実施例では、ポスト 44 、ヨーク 32 及びミラー 30 を有する高架構造物は、すべて同じ電位であり、ショートの危険性が回避される。このように、1 組の高架電極の限定は意図されない。

10

#### 【 0024 】

アドレス・トルク (T<sub>a</sub>) は、ヨーク 32 及びミラー 30 と共にアドレス電圧によって生じるトルクである。このアドレス・トルクは、同様のアドレス電圧及びバイアス電位の従来の世代の DMD デバイスで生じるアドレス・トルクよりずっと大きい。このように、本発明は、バイアス電圧が供給されるとき、ミラーが適切な方向に回転することを保証する必要のあるアドレス電圧 V<sub>a</sub> と電位の間の差として定義される改良されたアドレスマージンを有する。

20

#### 【 0025 】

本発明の画素は、ミラーを反対の状態へ回転 ( 又はアップセット (upset) ) させるに役立つアドレス電圧がある場合、バイアス電圧によって生じるラッチ・トルクの大きさとして定義される増加したラッチ・トルク (T<sub>1</sub>) も有する。本発明の別の著しく改良された性能パラメータは、リセット後にバイアス電圧がオフの時間の間、その着地状態のミラーを保持するアドレス電圧の能力の大きさと定義されるアドレス保持トルク (T<sub>h</sub>) の増加である。本発明の別の改良された特徴は、単一パルスのリセットとヒンジの片によってつくられる復元力の組合せによって作られる片反応力の大きさと定義される復元力 (F<sub>r</sub>) の増加である。

30

#### 【 0026 】

これらの 4 つすべての性能パラメータは、下部アドレス電極を有する電子静電力を生じさせるヨーク 32 を、高架ミラーと高架アドレス電極との間に生じる電子静電引力と共に用いる設計により、本発明によって実質的に前の世代の DMD デバイスより改良された。アドレス電極上の回転可能なヨークと実質的にその上の対向する表面領域との近接により、上述のすべての性能パラメータが著しく増加し、DMD デバイスの電子機械的効率を向上させる。特に、ヒンジの堅さ (stiffness) を変えることなく、前の世代のデバイスより 1.8 倍高いアドレス・トルクが達成される。ラッチ・トルクは、従来の DMD デバイスの 2.6 倍に改良される。生じる復元力は前の世代の DMD デバイスの 8.8 倍に増加される。すべての改良された性能パラメータにおいて、本発明の製造工程は、後に説明するが、前の世代のデバイスとほぼ同じであり、そのため前の世代のデバイスを超える “今までになかった” 利点を提供する。

40

#### 【 0027 】

本発明の DMD デバイスは、前述のように、空間光変調器の操作に重要な、より大きなマージン、アドレス・アップセットに対するより低い感知度、より低いリセット電圧要求、より高いスイッチスピードを含む。本発明の設計において、アドレス・マージン及びラッチ・マージンを改良するために必要であれば、より堅いヒンジの、非線形ヒンジを組み込めることがある。

#### 【 0028 】

50

ファン・デル・ワールスの力による膠着の可能性を減らすため、着地電極 60、特にヨーク 32 の片 58 からの接触点に対応する領域 62、は不活性化され得る。着地電極を不活性化することにより、ヨーク 32 の付着又は膠着する傾向は減少され得る。膠着化は抑制力 (inhibiting force) であり、ミラーをフラット状態にリセットするため、又はミラーを反対側に撓ませることのできるバイステイブル状態にスイッチするために供給される大きなリセット電圧を必要とする。着地電極を不活性化する方法は、共に譲渡された Hornbeck の米国特許番号第 5,331,454、発明の名称『DMD の低リセット電圧処理』、及び共に譲渡された同時係属中の米国特許出願番号第 08/239,497 で 1994 年 5 月 9 日に出願された、発明の名称『マイクロ・メカニカル・デバイスの PFPF コーティング』に開示されており、参考のためここに引用する。ミラーのリセットを達成し、ミラーを別のバイステイブル状態の撓みに誘導するため、バイアス / リセット・ラインがミラーの共振周波数に対応する周波数の電圧、典型的に約 5MHz、でパルスされ得ることは、共に譲渡された米国特許番号第 5,096,279、発明の名称『空間光変調器およびその方法』に開示されており、ここに参考のため引用する。

## 【0029】

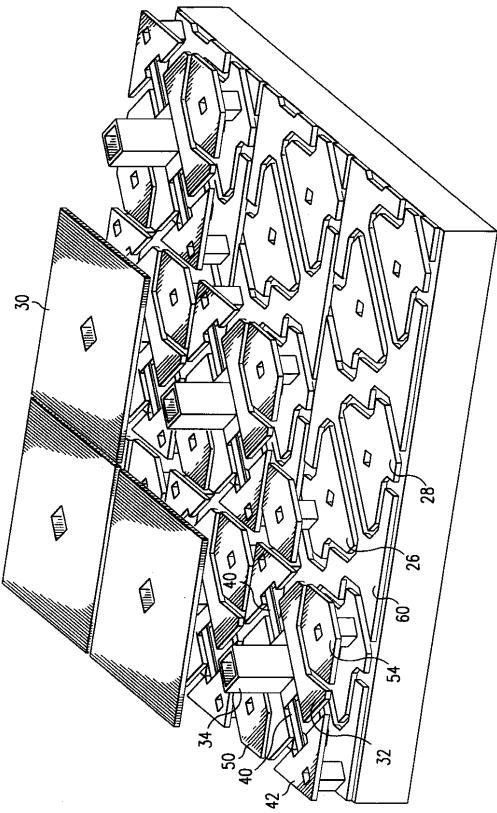

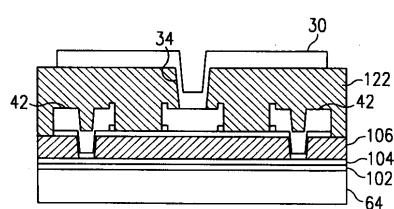

図 4 はアレイ 12 の 3 × 3 アレイ部分の断面透視図であり、シリコン基板上の金属 3 層の形成を示し、この金属 3 層はアドレス電極及びシリコン基板上のバイアス / リセット・バスを定める。さらに高架ミラーアドレス電極、ポストキャップ、及び金属 3 層上のヨーク 32 を支持するヒンジも示す。ミラー支持ポストは、画素のねじれ軸にそって、それぞれのヨークによって支持されるように示されている。

## 【0030】

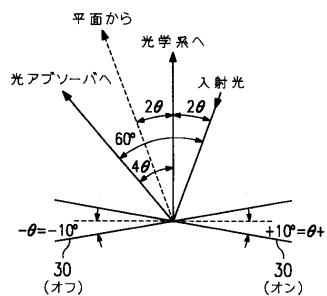

図 5 は光学的な略図であって、入射光は、ミラーが“オン”状態であるか“オフ”状態であるかによって、モジュレートされ 2 方向の一方に偏向されるように示されている。ミラー 30 がオン状態のとき、入射光は投射レンズを有する光学系に反射され、前面又は後面スクリーンプロジェクタの場合、結果的に表示スクリーンにフォーカスされ、電子写真プリンタの場合はフォトセンシティブ面上にフォーカスされる。ミラー 30 がオフ状態のとき、入射光は光アブソーバに反射され、暗視界光学系から離れる。ミラー 30 のバイステイブル状態の間の 20 度の回転は反射入射光の 40 度スイギングを成す。このように、本発明は、本発明の空間光変調器が意図した暗視界光学系システムで使用するのに重要な高コントラスト率の空間光画像を達成する。

## 【0031】

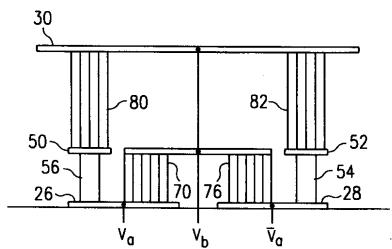

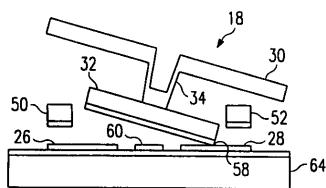

図 6 及び図 7 に関し、図 2 の線 A - A に沿ったピクセル 18 の断面図を示し、支持ポストは示されていない。図 6 に示すように、ヨーク 32 及びミラー 30 が非偏向 (フラット) 状態であり、ヨーク 32 は全体的に高架アドレス電極 50 及び 52 と同平面であり、アドレス電極 26 及び 28、及びリセット / バイアス 60 を含む金属 3 層上に約 1 ミクロンの距離にある。ミラー 30 は一対の高架アドレス電極 50 及び 52 上に、基板 64 からヨークを離している距離の約 2 倍である、約 2 ミクロン上に持ち上げられる。

## 【0032】

図 7において、図示するように、ヨーク 32 及びミラー 30 がアドレス指定され、時計方向に回転されるとき、ヨーク 32 のアドレス指定される半分の一対の着地片 58 はリセット / バイアス・バス 60 の部分 62 上に着地する。しかし、それと共に回転する高架ミラー 30 は上に位置したままであり、対応する高架アドレス電極 52 から離れている。図示するように、ヨーク 32 のモーメント・アームはねじれ軸のまわりのミラー 30 のモーメント・アームの約半分である。ミラー 30 と比較し着地ヨーク 32 の寸法がより短いとスタッカ・ミラーをリセットするために必要なトルクを減少するが、非常に短い着地ヨークを用いるとねじれヒンジ上に付加圧力を起こし得る。共に譲渡され、同時係属中の特許出願番号第 08/171,303 で 1993 年 12 月 21 日に出願された、発明の名称『マルチ・レベル・デジタル・マイクロミラー・デバイス』の記載を参照すれば上述のこれらの力をより良く理解できる。ヨーク 32 は一対の反対の片 58 上に着地し、対称的に設計されているため、アドレス電極 26 及び 28 の大きな領域は、図 2 に示すように、ヨーク 32 の下

10

20

30

40

50

に定められ得る。更に、ヨークと着地電極の部分 6 2 の間の膠着力の減少がみられるため、ミラーの状態を変化又はリセットするときに供給されるより低いリセット電圧を必要とする。

#### 【 0 0 3 3 】

図 8 ~ 1 3 を参照して、1 画素 1 8 を形成するために行なわれる半導体形成工程の詳しい説明をする。測定を目的とするのではなく、説明及び明確化のため、各図面は図 2 の線 B - B に沿った断面図を示す。

#### 【 0 0 3 4 】

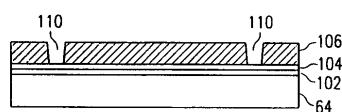

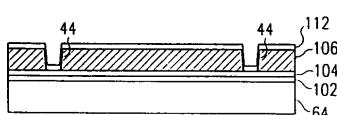

まず、図 8 において、シリコン基板 6 4 はメモリセル 1 6 のアレイ、行アドレス回路 2 0 、及び列データロード回路 3 0 を含む下部アドレス回路を形成するよう処理される。その後、基板 6 4 は保護酸化物層 1 0 2 で覆われる。次に、通常 M 3 と呼ばれる第 3 の金属化層が部分的に処理されたウェハ上にスパッタ・デポジットされ、1 0 4 で表される。この第 3 の金属化層はパターニングされ、エッチングされ、図 2 に示すようなアドレス電極 2 6 及び 2 8 、及びバイアス / リセット・バス 6 0 を定める。次に、ヒンジ・スペーサ層 1 0 6 はアドレス回路上にスピノ・デポジットされ、好ましくは 1 ミクロンの厚さを有するポジ型フォトレジストを有する。一対のバイア (via) 1 1 0 がフォトレジスト層 1 0 6 を通って開けられ、ヒンジ支持ポストの形成を容易にし、フォトレジスト層 1 0 6 は後続の処理工程の間のフロー及びバーリング (bubbling) を避けるため高温でディープ UV 硬化する。

#### 【 0 0 3 5 】

図 9 において、金属化薄膜ヒンジ層 1 1 2 はフォトレジスト層 1 0 6 上及びバイア 1 1 0 にスパッタ・デポジットされる。ヒンジ層 1 1 2 は、約 500 オングストロームの厚さを有することが好ましく、アルミニウム、アルミニウム合金、チタン化タングステン、及び本発明に適当な他の導電性金属から構成され得る。ヒンジ支持ポスト 4 4 は図示したようにこの工程で定義 (define) され、バイアス / リセット・バス 6 0 に電気的に接続される。更にこの工程の間、一対の電極支持ポスト 5 4 及び 5 6 が定められ、図示していないが、フォトレジスト層 1 0 6 に形成される、対応する一対のバイア 1 1 0 に層 1 1 2 がスパッタ・デポジットされ、これらのバイアはバイア 1 1 0 が開けられる前述の工程の間に形成されている。このように、電極支持ポスト及びヒンジ支持ポストは非常に似ている。フォトレジスト層 1 0 6 の厚さはヒンジ・エアー・ギャップを決定し、そのため、それが着地電極とエンゲージするまでのヨーク 3 2 の角度自由度によりミラー回転角度が決定する。

#### 【 0 0 3 6 】

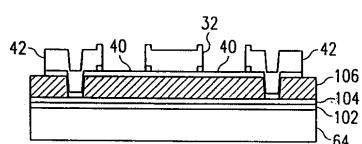

図 1 0 において、第 1 酸化マスクがプラズマ・デポジットされ、ヒンジ 4 0 の形にパターニングされる。その後、典型的に約 3 0 0 0 オングストロームの厚さであるアルミニウム合金の厚い金属化層がデポジットされる。第 2 酸化マスクはプラズマ・デポジットされ、その後ヨーク 3 2 、高架電極 5 4 及び 5 6 、及びヒンジ支持キャップ 4 2 の形にパターニングされる。その後、薄いヒンジ層 1 1 2 及びより厚い金属層は、図示するようにアドレス電極 5 0 及び 5 2 、ヒンジ支持キャップ 4 2 及びヒンジ 4 0 を定めるようにエッチングされる。これらの構造を定めるために、单一プラズマ・エッチが用いられる。2 つの酸化物層はエッチ・ストップとして機能し、それらの下の金属層を保護する。プラズマ・エッチ工程が終了した後、酸化物エッチ・ストップは、薄い金属ヒンジ、より厚い金属支持ポストキャップ 4 2 、電極 5 0 及び 5 4 から、及び図 1 0 に示すヒンジ 4 0 から除去される。

#### 【 0 0 3 7 】

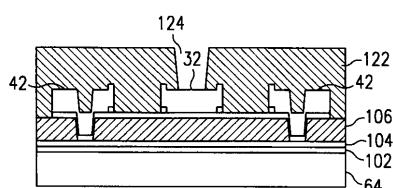

図 1 1 において、厚いミラー・スペーサ層 1 2 2 はヒンジ、電極、及び支持キャップ上にスピノ・デポジットされ、約 2 ミクロンの厚さを有するポジ型フォトレジストで構成されることが好ましい。バイア 1 2 4 がフォトレジスト・スペーサ層 1 2 2 に開けられ、図示するように、ヨーク 3 2 上の開口部を提供し、その後フォトレジスト層 1 2 2 はディープ UV 硬化される。

#### 【 0 0 3 8 】

10

20

30

40

50

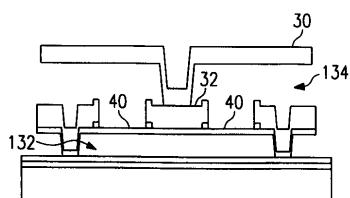

図12において、その後アルミニウム合金で構成され反射性を有するミラー金属層は、約4000オングストロームの厚さにスパッタ・デポジットされる。この層はミラー支持ポスト34とミラー30の両方を形成する。その後マスキング酸化物層が、ミラー層上にプラズマ・デポジットされ、四角ミラーの形にパターニングされる。その後、図示するように、ミラー金属層はプラズマ・エッチングされ、ミラー30及び支持ポスト34を形成する。マスキング酸化物層は、ウェハがその後処理されダイを得るために切られる間、典型的にその場に残される。図13において、チップはプラズマ・エッチング・チャンバに配置され、そこではマスキング酸化物層と両方のスペーサ層106及び122がプラズマ・エッチングされて取除かれ、ヒンジ40とヨーク32の下にヒンジ・エアー・ギャップを、高架ミラー30下にミラー・エアー・ギャップ134を残す。

10

## 【0039】

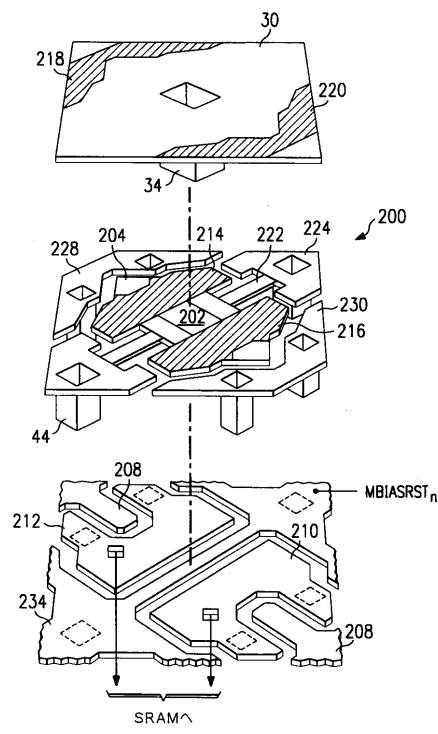

図14は、本発明の代替実施例の分割した透視図を、全体として200で示す。画素200は図1～13で示した画素18と非常に類似しており、同様の数字が同様の要素を表す。しかし、図示するように、画素200は、ねじれ軸の両側に1つの着地片204を有するように僅かに修正したヨーク202を有する。回転するとき、それが対応する着地電極208とエンゲージするか着地するまでヨーク202の一端204は回転する。ヨーク202は、基板上の金属3層から形成される一対のアドレスパッド210及び212のいずれかに実質的に重なる。電子静電力をつくる対向する表面の対応する領域はハッチングされた領域214、216、218及び220で示されている。ヒンジ222はヒンジポスト224からヨーク202を支持する。高架アドレス電極228及び230は、ヨーク202と同平面である。

20

## 【0040】

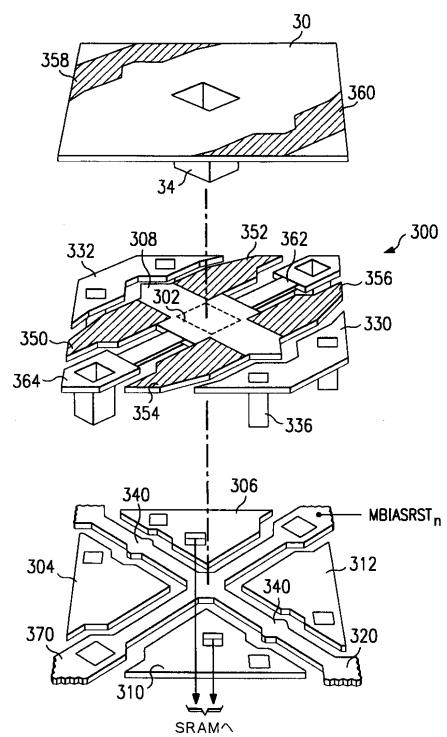

図15において、本発明の更に別の代替実施例を図300で示す。画素300は図(14の実施例示す)200、及び図1～13に示す画素18に非常に類似しており、同様の数字は同様の要素を表す。図示するように画素300は、図14の実施例に類似する、ねじれ軸の両側に提供される1つの着地片も有する。図示するように、ヨーク302はねじれ軸に実質的に平行に下部アドレス電極の上に伸び、一対のアドレス電極304及び306はヨーク302の一方の下に提供され、別の対のアドレス電極310、312はXパターンを有するバイアス/リセット・バス320の別の側上に提供される。2つのアドレス電極304及び306は互いに電気的に結び付き、別の対のアドレス電極310及び312は、電気的に結び付いている。アドレス電極の対は、図示するように、対応する支持ポスト336を介して、高架ミラー/アドレス電極330及び332に接続される。電子静電引力の領域は350、352、354、356、358及び360のハッチングされた領域で表す。ヒンジ362はポスト364からヨーク302を支持する。この実施例において、バイアス/リセット・バス620はX型を有し、図示するように、一対のアドレス電極を二股に分ける。X型を有するため、バイアス/リセット・バスは、容易にしかも簡単に基板上の金属3層の隣接する画素と相互接続ができる。これにより、共通バイアス/リセット・バスを有する複数の画素行を制御する望ましいレイアウトが達成され得、スプリット・リセット技術を促進することは、共に譲渡された米国特許出願番号第08/300,356号で1995年2月16日に出願された、発明の名称『空間光変調器のための画素制御回路』に開示されており、参照のためにここに開示する。ヨーク片の着地サイトは340で示すバイアス/リセット・バスに沿って提供される。

30

## 【0041】

要約すると、画素ミラーの撓みを誘導する、2つの位置で生じる電子静電力を有するDMD形式の空間光変調器が開示される。先ず、引力が、ヨークと下部基板アドレス電極との間に生じる。更に、電子静電力が高架ミラーと高架アドレス電極の間に生じる。これらの電子静電力は付加的であり、従来の世代のDMDデバイスを超える改良された性能パラメータを実現する。ミラーと高架アドレス電極との間のスペースの2分の1に等しい距離で、ヨークが基板アドレス電極上方に離されるため、ユニット領域毎の引力はミラーと高架アドレス電極との間に生じる力より4倍大きい。本発明の設計は、より高いアドレス・ト

40

50

ルク、より高いラッチ・トルク、より高いリセット力、及びより大きなアドレスマージンを達成する。画素はアドレス・アップセットに対する感度が低く、より低いリセット電圧を必要とし、共振リセット及び複数リセットパルスの必要性を減らし得る。より高いスイッチスピードが達成され、前述の改良された性能パラメータにより、非線形及びより堅い(stiff)なヒンジが実現され得る。画素アレイは基準の工程から大きく逸脱することなく製造することができる。このように、従来の世代を超える本発明の空間光変調器によって達成することのできる改良された性能パラメータは、従来の世代を超える“今までになかった”設計である。

#### 【0042】

本発明は特定の好ましい実施例を参照して説明されたが、本説明を参照すればこの技術の分野の習熟者にとって、種々の変形及び修正は明白である。したがって、添付の特許請求の範囲はあらゆるこれらの変形及び組合せを包含することを意図する。

#### 【0043】

以上の説明に関して更に次の項を開示する。

(1) 空間光変調器であって、

基板と、

前記基板に近接して提供される第1の部分と、前記基板上に高架される第2の部分とを有するアドレス回路と、

前記アドレス回路の第1の部分上に支持されるヨークと、

前記ヨークに接続され、前記ヨークを支持する少なくとも1つのヒンジであって、前記ヒンジは前記ヨークを撓ませ、

前記ヨーク上に高架され、ヨークによって支持され、前記高架アドレス回路の第2の部分上に位置付けられる画素

とを含む空間光変調器。

(2) 第1項に記載の空間光変調器であって、ヨーク軸に沿って前記ヨークを軸支持する一対の前記ヒンジを有する空間光変調器。

(3) 第1項に記載の空間光変調器であって、前記ヨークは、前記画素及び前記ヨークに重なる前記画素の幅より狭い幅を有する空間光変調器。

(4) 第2項に記載の空間光変調器であって、前記ヨークは、前記ヨーク軸の両側に一対のヨーク片を有する空間光変調器。

(5) 第4項に記載の空間光変調器であって、前記ヨークは、蝶の形を有する空間光変調器。

(6) 第1項に記載の空間光変調器であって、第1のスペーシングは前記ヨークと前記アドレス回路の第1の部分との間に定められ、第2のスペーシングは前記画素と前記ヨークとの間に定められ、前記第1のスペーシングは前記第2のスペーシングより狭い空間光変調器。

(7) 第1項に記載の空間光変調器であって、前記ヨークは実質的に前記アドレス回路の第2の部分と同じ平面である空間光変調器。

(8) 第2項に記載の空間光変調器であって、対向する表面領域の第1の対は前記ヨークと前記アドレス回路の第1の部分との間に定められ、対向する表面領域の第2の対は前記画素と前記アドレス回路の第2の部分との間に定められ、前記対向表面領域の第2の対が、前記ヨーク軸からの対向表面領域の前記第1の対より前記ヨーク軸からの距離より大きく、横方向へ定められる空間光変調器。

(9) 第1項に記載の空間光変調器であって、前記基板上に構成され、前記画素に電気的に接続されるバイアス/リセット・バスを更に有する空間光変調器。

(10) 第1項に記載の空間光変調器であって、前記ヒンジは、前記ヨークと実質的に同じ平面である空間光変調器。

(11) 第1項に記載の空間光変調器であって、前記アドレス回路に結合される制御回路を更に有し、前記制御回路は前記アドレス回路の第1の部分及び第2の部分にアドレスデータを供給し、前記画素を撓ませる空間光変調器。

10

20

30

40

50

(12) 第2項に記載の空間光変調器であって、前記アドレス回路に結合される制御回路を更に有し、前記制御回路は前記アドレス回路の第1の部分のひとつにアドレスデータを提供し、前記アドレス指定された第1の部分の方へ前記ヨークを撓ませる空間光変調器。

(13) 第1項に記載の空間光変調器であって、前記ヒンジに接続され前記ヒンジを支持する支持ポストを更に有する空間光変調器。

(14) 第1項に記載の空間光変調器であって、前記アドレス回路の第1の部分及び第2の部分は互いに電気的に接続される空間光変調器。

(15) 第1項に記載の空間光変調器であって、前記画素はミラーである空間光変調器。

10

(16) 第15項に記載の空間光変調器であって、前記ミラーは四角形である空間光変調器。

(17) 第16項に記載の空間光変調器であって、前記ミラーは前記ヒンジに対し45度でジオメトリックに配向される空間光変調器。

(18) 空間光変調器であって、

基板と、

前記基板に近接して提供される第1の部分と、前記第1の部分で定められる平面上にある第2の部分とを有するアドレス回路と、

前記アドレス回路の第1の部分上に支持されるヨークと、

前記ヨークに接続され、前記ヨークを支持する少なくとも1つのヒンジであって、前記ヒンジは前記ヨークを撓ませ、

20

前記ヨーク上に高架され、ヨークによって支持され、前記高架アドレス回路の第2の部分上に位置付けられる画素

とを含む空間光変調器。

(19) 増加した性能パラメータを有するDMD型の空間光変調器10である。画素ミラー30がヨーク32によって支持され、幾つかの構造体の間に電子静電引力70, 76, 80, 82が生じる。まず、高架ミラー30と高架アドレス電極50, 52の間に、次に、ヨーク32と下部アドレス電極26, 28の間に生じる。画素30は、従来の世代のデバイスに比べ、高アドレス・トルク、高ラッチ・トルク、高い復元力、及びより大きなマージンを達成する。基板アドレス電極26, 28上のヨーク32の近接により、大きな引力が実現され、画素はアドレス・アップセットに感度が低く、より小さなりセット電圧を必要とし、スイッチスピードをより早める。

30

#### 【図面の簡単な説明】

【図1】本発明の好ましい実施例に従った空間光変調器のブロック図であり、マイクロミラーを有する画素アレイを制御する列アドレス及びコラムデータロード回路を有する。

【図2】図2に示すアレイの1つのDMD画素の分解透視図であって、可撓性ヨーク上に形成された高架マイクロミラーを有し、ヨークは一対のヒンジによって順に支持され、ハッチングした領域は高架ミラーと高架アドレス電極の間の電子静電を引付ける(attraction)領域を図示し、ヨークと下部アドレス電極の間は基板上の金属3を有する。

【図3】ミラーと高架アドレス電極との間、及びヨークと下部アドレス電極との間の電子静電引力を示し、ヨーク及びミラーは、バイアス/リセット・バスに電気的に接続され、同じ電圧バイアスを有する。

40

【図4】図1に示すアレイの画素の3×3アレイの断面図であり、基板レベルアドレス電極及び基板レベルバイアス/リセットパターンを限定する金属3層を示すため、幾つかのヨーク、高架アドレス電極及びヒンジ支持ポストが取り除かれ、下部基板レベルアドレス電極の一部に重なる高架ヨークを示すため高架ミラーの幾つかが取り除かれて示されている。

【図5】図4に示す画素ミラーが2方向のうち一方に入射光を偏向させる2つのステイブル偏向状態を示す。

【図6】高架ミラー・アドレス電極及び基板アドレス電極上に支持されたヨークを示すた

50

めヒンジ軸に沿った図 1 の D M D アレイの 1 画素の断面図。

【図 7】図 6 の様に断面図であり、共に上に支持され 1 スティブル状態に回転されるヨーク及びミラーを有し、ヨーク片はそれぞれ 1 対の着地パッド上に着地し、高架ミラーは高架ミラー・アドレス電極に離れて近接して残る。

【図 8】従来のロバスト ( robust ) 半導体処理技術を用いて図 2 の画素を形成するために処理される半導体材料の種々の層を順次示す。

【図 9】従来のロバスト ( robust ) 半導体処理技術を用いて図 2 の画素を形成するために処理される半導体材料の種々の層を順次示す。

【図 10】従来のロバスト ( robust ) 半導体処理技術を用いて図 2 の画素を形成するために処理される半導体材料の種々の層を順次示す。

【図 11】従来のロバスト ( robust ) 半導体処理技術を用いて図 2 の画素を形成するために処理される半導体材料の種々の層を順次示す。

【図 12】従来のロバスト ( robust ) 半導体処理技術を用いて図 2 の画素を形成するために処理される半導体材料の種々の層を順次示す。

【図 13】従来のロバスト ( robust ) 半導体処理技術を用いて図 2 の画素を形成するために処理される半導体材料の種々の層を順次示す。

【図 14】本発明の好ましい実施例の代替例の分割透視図であって、ヨークはねじれ軸の両側で定められる 1 つの着地片のみを有する。

【図 15】本発明の好ましい実施例の別の代替例の分割透視図であって、ヨークはねじれ軸の両側に 1 つの着地片を有し、ヨークは下部基板アドレス電極上にねじれ軸に平行に伸びる。

【符号の説明】

1 0 D M D 型空間光変調器

2 6 , 2 8 下部アドレス電極

3 0 画素ミラー

3 2 ヨーク

7 0 , 7 6 , 8 0 , 8 2 電子静電引力

5 0 , 5 2 高架アドレス電極

【 図 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図13】

【図11】

【図12】

【図14】

【図15】

---

フロントページの続き

(72)発明者 ラリー ジェイ・ホーンベック

アメリカ合衆国テキサス州バン アルスタイン, ボックス 162, ルート 1

審査官 東 治企

(56)参考文献 特開平06-003607 (JP, A)

特開平05-196880 (JP, A)

特開平07-084196 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G02B 26/08

B81B 3/00

B81B 7/00