(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-363592

(P2004-363592A)

(43) 公開日 平成16年12月24日(2004.12.24)

(51) Int.Cl.<sup>7</sup>

H01L 27/12

H01L 21/20

H01L 27/08

F 1

H01L 27/12

H01L 21/20

H01L 27/08

テーマコード(参考)

5FO48

5FO52

331E

審査請求 有 請求項の数 38 O L (全 16 頁)

(21) 出願番号 特願2004-158994 (P2004-158994)

(22) 出願日 平成16年5月28日 (2004.5.28)

(31) 優先権主張番号 10/448947

(32) 優先日 平成15年5月30日 (2003.5.30)

(33) 優先権主張国 米国(US)

(71) 出願人 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESSES MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100086243

弁理士 坂口 博

(74) 代理人 100091568

弁理士 市位 嘉宏

(74) 代理人 100108501

弁理士 上野 剛史

最終頁に続く

(54) 【発明の名称】十分に格子緩和された高品質SiGeオノン・インシュレータ基板材料を製造する方法、基板材料、およびヘテロ構造

## (57) 【要約】

【課題】SiMoxおよびGe相互拡散を用いて十分に格子緩和された高品質SiGeオノン・インシュレータ基板材料を形成する方法を提供する。

【解決手段】Si含有基板内に注入リッチ領域を形成するために、Si含有基板にイオンを最初に注入する。注入リッチ領域は、高温でのアニールの間にGe拡散を妨げるバリア層が形成されるように充分なイオン濃度を有する。次に、Ge含有層は、Si含有基板の表面の上に形成され、その後、加熱工程が、バリア層の形成およびGeの相互拡散を可能にする温度で行われ、それによって、バリア層の上に十分に格子緩和された単結晶SiGe層を形成する。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

十分に格子緩和された高品質 SiGe オン・インシュレータ基板材料を製造する方法において、

Ge の拡散バリアの働きをするのに充分なイオン濃度を有する注入リッチ領域を形成するために Si 含有基板にイオンを注入する工程を含み、前記注入リッチ領域は、その上に Si 含有基板の表面層が配置され、

注入された Si 含有基板の上に Ge 含有層を形成する工程を含み、

( i ) 拡散バリア層の形成と、( i i ) 前記 Ge 含有層、および注入リッチ領域の上に配置される Si 含有基板の前記表面層に渡る Ge の相互拡散とを可能にする温度で基板を加熱する工程を含み、これにより前記拡散バリア層の上に十分に格子緩和された SiGe 層を形成する、製造方法。

**【請求項 2】**

前記注入イオンは、酸素イオン、窒素イオン、NOイオン、不活性ガスまたはこれらの混合物を含む請求項 1 に記載の製造方法。

**【請求項 3】**

前記注入イオンは、酸素イオンを含む請求項 1 に記載の製造方法。

**【請求項 4】**

前記注入する工程は、プランケット注入処理またはマスクされた注入処理を含む請求項 1 に記載の製造方法。

**【請求項 5】**

前記注入する工程は、約  $4 \times 10^{17} / \text{cm}^2$  以上のイオン・ドーズを用いて行われる高ドーズ・イオン注入処理を含む請求項 1 に記載の製造方法。

**【請求項 6】**

前記高ドーズ・イオン注入は、約 0.05 ~ 約 500 mA / cm<sup>2</sup> のビーム電流密度および約 150 ~ 約 1000 keV のエネルギーで作動するイオン注入装置内で行われる請求項 5 に記載の製造方法。

**【請求項 7】**

前記高ドーズ・イオン注入処理は、約 200 ~ 約 800 の温度で行われる請求項 5 に記載の製造方法。

**【請求項 8】**

前記高ドーズ・イオン注入処理は、ベース・イオン注入工程の後に続いて約 4 K ~ 約 200 の温度で行われる更なるイオン注入工程を含む請求項 5 に記載の製造方法。

**【請求項 9】**

前記更なるイオン注入工程は、約 0.05 ~ 約 10 mA / cm<sup>2</sup> のビーム電流密度で、約  $1 \times 10^{14} \sim 1 \times 10^{16} / \text{cm}^2$  のイオン・ドーズ、約 40 keV 以上のエネルギーを用いて行われる請求項 8 に記載の製造方法。

**【請求項 10】**

前記注入する工程は、約  $4 \times 10^{17} / \text{cm}^2$  以下のイオン・ドーズを用いて行われる低ドーズ・イオン注入処理を含む請求項 1 に記載の製造方法。

**【請求項 11】**

前記低ドーズ・イオン注入は、約 0.05 ~ 約 500 mA / cm<sup>2</sup> のビーム電流密度および約 40 ~ 約 1000 keV のエネルギーで作動するイオン注入装置内で行われる請求項 10 に記載の製造方法。

**【請求項 12】**

前記低ドーズ・イオン注入処理は、約 100 ~ 約 800 の温度で行われる請求項 10 に記載の製造方法。

**【請求項 13】**

前記低ドーズ・イオン注入処理は、ベース・イオン注入工程の後に続いて約 4 K ~ 約 200 の温度で行われる更なるイオン注入工程を含む請求項 10 に記載の製造方法。

10

20

30

40

50

**【請求項 14】**

前記更なるイオン注入工程は、約0.05～約10mA/cm<sup>2</sup>のビーム電流密度で、約1×10<sup>14</sup>～約1×10<sup>16</sup>/cm<sup>2</sup>のイオン・ドーズ、約40keV以上のエネルギーを用いて行われる請求項13に記載の製造方法。

**【請求項 15】**

前記Ge含有層は、SiGe合金層または純Geである請求項1に記載の製造方法。

**【請求項 16】**

前記Ge含有層は、最大99.99原子パーセントのGeからなるSiGe合金層である請求項1に記載の製造方法。

**【請求項 17】**

前記Ge含有層は、減圧化学気相成長、常圧化学気相成長、超高真空化学気相成長、分子線エピタキシおよびプラズマ化学気相成長からなるグループから選択されるエピタキシャル成長処理によって形成される請求項1に記載の製造方法。

**【請求項 18】**

前記加熱する工程の前に前記Ge含有層の上にSiキャップ層を形成する工程を更に含む請求項1に記載の製造方法。

**【請求項 19】**

前記Siキャップ層は、エピSi、エピSiGe、a:Si、a:SiGe、単結晶または多結晶Si、またはこれらの多層の組み合わせを含む請求項18に記載の製造方法。

**【請求項 20】**

表面酸化膜層は、前記加熱する工程の間に形成される請求項1に記載の製造方法。

**【請求項 21】**

ウェット化学エッチング処理を利用して前記表面酸化膜層を除去する工程を更に含む請求項20に記載の製造方法。

**【請求項 22】**

前記加熱する工程は、少なくとも1つの酸素含有ガスを含む酸化雰囲気中で行われる請求項1に記載の製造方法。

**【請求項 23】**

不活性ガスを更に含み、前記不活性ガスが前記少なくとも1つの酸素含有ガスを希釈するために用いられる請求項22に記載の製造方法。

**【請求項 24】**

前記加熱する工程は、約900～約1350の温度で行われる請求項1に記載の製造方法。

**【請求項 25】**

前記十分に格子緩和されたSiGe層の上に追加のSiGe層を成長する工程を更に含む請求項1に記載の製造方法。

**【請求項 26】**

前記追加のSiGe層の上に歪みSi層を形成する工程を更に含む請求項25に記載の製造方法。

**【請求項 27】**

前記十分に格子緩和されたSiGe層の上に歪みSi層を形成する工程を更に含む請求項1に記載の製造方法。

**【請求項 28】**

Si含有基板と、

前記Si含有基板の上に存在してGe拡散を妨げる絶縁領域と、

前記絶縁領域の上に存在する十分に格子緩和されたSiGe層とを備え、

前記十分に格子緩和されたSiGe層は、約2000nm以下の厚さおよび約5×10<sup>7</sup>原子/cm<sup>2</sup>以下の欠陥密度を有する基板材料。

**【請求項 29】**

前記絶縁領域は、パターニングされ、またはパターニングされていない請求項28に記

10

20

30

40

50

載の基板材料。

**【請求項 3 0】**

前記絶縁領域は、埋め込み酸化膜領域である請求項 2 8 に記載の基板材料。

**【請求項 3 1】**

前記十分に格子緩和された SiGe 層は、約 1 ~ 約 100 % の測定格子緩和を有する請求項 2 8 に記載の基板材料。

**【請求項 3 2】**

Si 含有基板と、

前記 Si 含有基板の上に存在して Ge 拡散を妨げる絶縁領域と、

前記絶縁領域の上に存在する十分に格子緩和された SiGe 層と、

前記十分に格子緩和された SiGe 層の上に形成される歪み Si 層とを備え、

前記十分に格子緩和された SiGe 層は、約 2000 nm 以下の厚さおよび約  $5 \times 10^7$  原子 / cm<sup>2</sup> 以下の欠陥密度を有するヘテロ構造。

**【請求項 3 3】**

前記絶縁領域は、パターニングされ、またはパターニングされていない請求項 3 2 に記載のヘテロ構造。

**【請求項 3 4】**

前記絶縁領域バリア層は、埋め込み酸化膜領域である請求項 3 2 に記載のヘテロ構造。

**【請求項 3 5】**

前記十分に格子緩和された SiGe 層は、約 1 ~ 約 100 % の測定格子緩和を有する請求項 3 2 に記載の基板材料。

**【請求項 3 6】**

前記歪み Si 層は、エピ Si 層を含む請求項 3 2 に記載のヘテロ構造。

**【請求項 3 7】**

格子緩和された SiGe と歪み Si の交互層は、前記歪み Si 層の上に形成される請求項 3 2 に記載のヘテロ構造

**【請求項 3 8】**

前記歪み Si 層は、GaAs と GaP からなるグループから選択される格子間不整合化合物で置き換えられる請求項 3 2 に記載のヘテロ構造。

10

20

30

40

50

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体基板材料を製造する方法に関し、特に、シリコン・オン・インシュレータ (SOI) 形成の態様と Ge 含有層の相互拡散とを組み合わせることによって絶縁層の上に十分に格子緩和された高品質 SiGe 合金結晶層を製造する方法に関する。本発明の方法は、Si エピタキシャル過成長によって、歪み Si 層を作るための格子間不整合テンプレートとして使用できる十分に格子緩和された高品質 SiGe オン・インシュレータ基板材料を提供する。このような歪み Si 層は、高キャリア移動度を有し、高性能な相補型金属酸化膜半導体 (CMOS) 応用品に有用である。本発明は、また、SiGe オン・インシュレータ基板材料、および SiGe オン・インシュレータ基板材料を少なくとも含む構造に関する。

**【背景技術】**

**【0002】**

半導体製造分野では、シリコン・オン・インシュレータ基板は、その技術分野において酸素イオン注入による分離 (SIMOX) と呼ばれる方法を用いて形成できる。従来の SIMOX 方法では、Si ウエハは、高ドーズ ( $5 \times 10^{16}$  原子 / cm<sup>2</sup> 以上のオーダー) で酸素を注入され、次に、極めて高い温度 (約 1300 以上のオーダー) でアニールおよび酸化され、Si ウエハの表面の下に明瞭に画定され、かつ連続した埋め込み酸化膜層を形成する。高温アニールは、埋め込み酸化膜層を化学的に形成すること、およびシリコ

ンの溶融点近くにアニールすることによって表面に近いシリコン層に残存する全ての欠陥を無くすことの両方に使える。

【発明の開示】

【発明が解決しようとする課題】

【0003】

歪みSiをベースにしたヘテロ構造を用いた近年の高レベル機能のために、SiGe層が十分に格子緩和され、かつ高品質であるSiGeオン・インシュレータ(SGOI)基板を提供する必要がある。SGOI基板は、例えばSIMOX方法を含み、種々の方法を用いて形成できる。従来技術では、約1～5μmの厚さを有する厚いSiGe層が、Siウエハの上に最初に付着され、次にSIMOX方法が実行される。このような従来の方法は、以下の2つの欠点を有する。1)連続した酸化膜層が形成される前に、Geがバルクに拡散しやすい。2)Ge濃度が極めて低くなれば、酸素(O)ピーク近くのGeの存在が、高品質埋め込み酸化膜層の形成を妨げる。

【0004】

SGOI基板材料を形成する従来技術のSIMOX方法の欠点から見て、連続した埋め込み絶縁層が形成される前にバルクSiに拡散するGeの傾向を低減し、埋め込み絶縁層の上に、格子緩和されかつ高品質のSiGe合金層を与える、新たな、かつ改良されたSIMOX方法を提供する必要がある。

【0005】

本発明の目的は、薄くて高品質で十分に格子緩和されたSiGeオン・インシュレータ基板材料を製造する方法を提供することにある。

【0006】

本発明の他の目的は、不整合転位(misfit)および貫通転位(threading dislocations)のような更なる欠陥の生成に対して安定な、薄くて高品質で十分に格子緩和されたSiGeオン・インシュレータ基板材料を製造する方法を提供することにある。

【0007】

本発明の更に他の目的は、CMOS処理工程に適用できる、薄くて高品質で十分に格子緩和されたSiGeオン・インシュレータ基板材料を製造する方法を提供することにある。

【0008】

本発明の更に他の目的は、歪みSi層を形成するための格子間不整合テンプレート、すなわち基板として更に使用できる、薄くて高品質で十分に格子緩和されたSiGeオン・インシュレータ基板材料を製造する方法を提供することにある。

【0009】

本発明の更に他の目的は、高キャリア移動度を有し、高性能CMOS応用品に有用である歪みSi/十分に格子緩和されたSiGeオン・インシュレータ構造を提供することにある。

【0010】

本発明の更に他の目的は、シリコン・オン・インシュレータ(SOI)形成の態様とGe含有層の相互拡散とを組み合わせることによって、絶縁層を覆って十分に格子緩和された高品質SiGe合金結晶層を製造する方法を提供することにある。

【0011】

本発明の更に他の目的は、SIMOXアニールの欠陥消滅特性を利用すると共に、Ge拡散を著しく妨げる埋め込み絶縁層を覆って、十分に格子緩和された高品質SiGe合金結晶層の形成を可能にする、十分に格子緩和された高品質SiGeオン・インシュレータ基板材料を製造する方法を提供することにある。

【課題を解決するための手段】

【0012】

これらのおよび他の目的および利点は、本発明では、Si含有基板内に注入リッチ領域

10

20

30

40

50

を形成するために Si 含有基板にイオン、例えば酸素イオンを最初に注入することを含む方法を利用することによって実現される。注入リッチ領域は、高温アニールの際に、Ge 拡散を妨げるバリア層が形成されるように充分なイオン濃度を有する。次に、Ge 含有層、例えば SiGe または純 Ge が、Si 含有基板の表面の上に形成され、その後、バリア層の形成と、バリア層の上に十分に格子緩和された単結晶 SiGe 層を形成する Ge の相互拡散を可能にする加熱工程が高温で行われる。十分に格子緩和された単結晶層が、少なくとも SiGe または純 Ge と、注入リッチ領域の上に配置される Si 含有基板の一部との均一な混合物から成ることに注意すべきである。

#### 【0013】

本発明のこれらの工程に統いて、歪み Si 層は、種々の高性能 CMOS 応用品に使用できる歪み Si / 格子緩和された SiGe 含有ヘテロ構造を形成するために、十分に格子緩和された単結晶 SiGe 層の上にエピタキシャル成長が可能である。10

#### 【0014】

本発明方法は、また、パターニングされないバリア層（すなわち、連続するバリア層）、またはパターニングされたバリア層（すなわち、半導体材料によって囲まれた、別個でかつ分離されたバリア領域すなわちアイランド）を形成することを意図している。

#### 【0015】

本発明のさらに他の実施例では、Si キャップ層は、構造を加熱する前に Ge 含有層の上に形成される。本発明のこの実施例は、（欠陥の生成を防ぐ点から）アニールの前に SiGe 層の熱力学的安定性を変える。SiGe 層は、約 2000 nm 以下の厚さ（約 10 ~ 約 200 nm の厚さが特に好ましい）を有する。20

#### 【0016】

本発明の他の態様は、上述した処理工程を利用して形成される SiGe オン・インシュレータ基板材料に関する。特に、本発明の基板材料は、Si 含有基板と、Si 含有基板の上に存在して Ge 拡散を妨げる絶縁領域と、絶縁領域の上に存在する約 2000 nm 以下の厚さを有する十分に格子緩和された SiGe 層とを備える。本発明の SiGe オン・インシュレータ基板材料の特徴は、現在の SGOI 材料に特有な欠陥密度を有するということである。特に、本発明の SiGe オン・インシュレータ基板材料は、約  $5 \times 10^7$  c / m<sup>2</sup> 以下の測定欠陥密度を有する。

#### 【0017】

本発明の更に他の態様は、上述した基板材料を少なくとも含むヘテロ構造に関する。特に、本発明のヘテロ構造は、Si 含有基板と、Si 含有基板の上に存在して Ge 拡散を妨げる絶縁領域と、絶縁領域の上に存在する約 2000 nm 以下の厚さを有する十分に格子緩和された SiGe 層と、十分に格子緩和された SiGe 層の上に形成される歪み Si 層とを備える。30

#### 【0018】

本発明の他の態様は、本発明の SiGe オン・インシュレータ基板材料を少なくとも含む、超格子構造、および他の格子間不整合構造のためのテンプレートに関する

#### 【発明を実施するための最良の形態】

#### 【0019】

本発明は、Si エピタキシャル過成長のための格子間不整合テンプレートとして更に使用できる、薄くて高品質で十分に格子緩和された SiGe オン・インシュレータ基板材料を製造する方法を提供するものであり、図面を参照して本発明を詳細に説明する。図面において、同一の構成要素および / または対応する構成要素には、同一の参照番号を付して示す。40

#### 【0020】

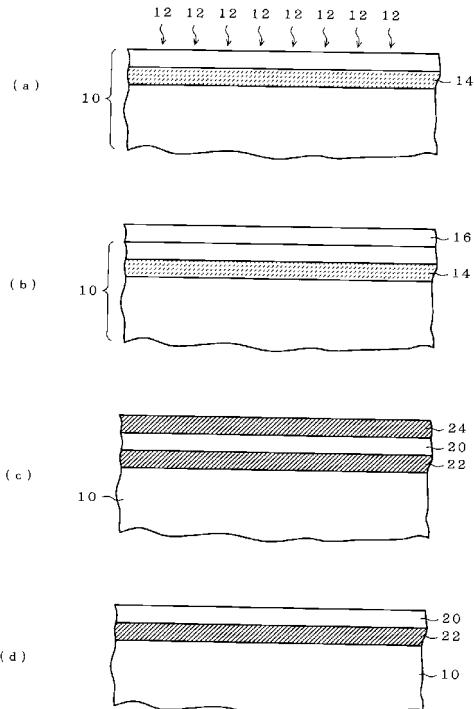

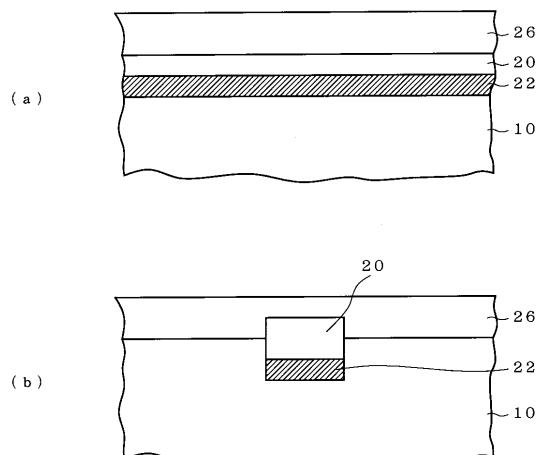

まず、本発明の基本処理工程を示す図 1 を参照する。特に、図 1 (a) は、Si 含有基板 10 内に注入リッチ領域 14 を形成するために、Si 含有基板 10 にイオン 12 が注入される本発明の最初の処理工程を示す。図に示されるように、注入リッチ領域 14 は、Si 含有基板 10 の表面層の下に配置される。ここで使用される語句 “Si 含有” は、シリ50

コンを少なくとも含む半導体基板を意味する。一例は、Si, SiGe, SiC, SiGeC, Si/Si, Si/SiC, Si/SiGeC および予め形成されたシリコン・オン・インシユレータを含むが、これらに制限されない。予め形成されたシリコン・オン・インシユレータは、その中に存在する多数の埋め込み酸化膜（連続、非連続または連続と非連続の混合）領域を含む。

## 【0021】

本発明のこの時点で Si 含有基板 10 に注入されるイオン 12 は、次の加熱工程が行われている間に Ge 拡散を妨げるバリア層を形成できるイオンである。このようなイオンの一例は、酸素イオン、窒素イオン、NO イオン、不活性ガスおよびこれらの混合物を含むが、これらに制限されない。本発明のこの時点で Si 含有基板 10 に注入される好ましいイオン 12 は、酸素イオンである。10

## 【0022】

イオン 12 は、Si 含有基板に注入リッチ領域 14 を形成する充分な濃度で Si 含有基板 10 に注入される。本発明のこの時点で形成される注入リッチ領域 14 は、次の加熱工程が行われている間に Si 含有基板内の Ge 拡散を妨げるバリア層を形成するのに充分なイオン濃度を有する。一般に、本発明のこの工程で形成される注入リッチ領域 14 は、約  $1 \times 10^{22}$  原子 /  $\text{cm}^3$  以上のイオン濃度を有する。

## 【0023】

注入リッチ領域 14 は、Si 含有材料の表面層が注入リッチ領域 14 の上にあるように、Si 含有基板 10 の上面の下に形成される。一般に、注入リッチ領域 14 は、Si 含有基板 10 の上面の下に約 5 nm 以上形成される。20

## 【0024】

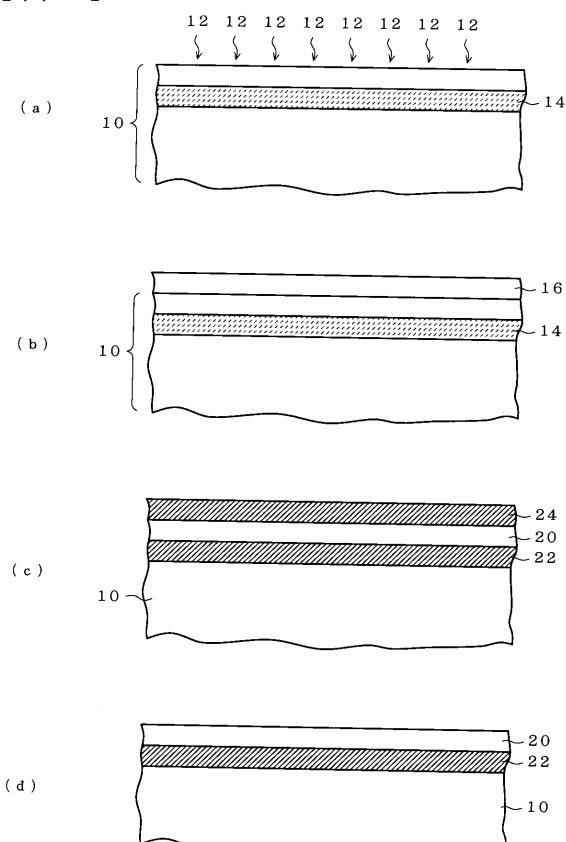

イオン 12 は、当業者に周知である従来の SIMOX 方法および条件、および 2001 年 5 月 21 日出願の米国特許出願第 09/861593 号明細書、2001 年 5 月 21 日出願の米国特許出願第 09/861594 号明細書、2001 年 5 月 21 日出願の米国特許出願第 09/861590 号明細書、2001 年 5 月 21 日出願の米国特許出願第 09/861596 号明細書、2001 年 6 月 19 日出願の米国特許出願第 09/884670 号明細書および米国特許第 930634 号明細書に述べられた種々の SIMOX 方法および条件を用いて注入される。注入は、図 1(a) に示されるプランケット注入でもよく、または図 2(a) に示されるパターニングされた注入を用いてよい。パターニングされた注入は、Si 含有基板 10 の上面に直接形成されたマスクを用いてもよく、または Si 含有基板 10 の上面からある距離に配置されるマスクを用いてよい。30

## 【0025】

種々の注入条件が本発明で用いられるが、以下の説明は、Si 含有基板 10 に注入リッチ領域 14 を形成するための一般的な注入条件を与える。

## 【0026】

## 1. 高ドーズ・イオン注入

ここで使用される語句“高ドーズ”は、約  $4 \times 10^{17}$  /  $\text{cm}^2$  以上のイオン・ドーズ（約  $4 \times 10^{17}$  ~ 約  $2 \times 10^{18}$  /  $\text{cm}^2$  のイオン・ドーズがより好ましい）を意味する。高イオン・ドーズを用いることに加えて、この注入は、一般に、約 0.05 ~ 約 500 mA /  $\text{cm}^2$  のビーム電流密度および約 150 ~ 約 1000 keV のエネルギーで作動するイオン注入装置内で行われる。より好ましくは、この注入は、約 150 ~ 約 210 keV のエネルギーを用いて行われる。40

## 【0027】

ベース・イオン注入と呼ばれるこの注入は、約 0.05 ~ 約 500 mA /  $\text{cm}^2$  のビーム電流密度、約 200 ~ 約 800 の温度で行われる。より好ましくは、ベース・イオン注入は、約 5 ~ 約 10 mA /  $\text{cm}^2$  のビーム電流密度、約 200 ~ 約 600 の温度で行われる。

## 【0028】

望むならば、ベース・イオン注入工程の後に、約  $1 \times 10^{14}$  ~ 約  $1 \times 10^{16}$  /  $\text{cm}^2$  の50

イオン・ドーズ（約 $1 \times 10^{15}$ ～約 $4 \times 10^{15}$ /cm<sup>2</sup>のイオン・ドーズが特に好ましい）を用いて行われる更なる酸素注入を続けてよい。更なるイオン注入は、約40keV以上のエネルギー（約120～約450keVのエネルギーがより好ましい）で行われる。

#### 【0029】

この更なる注入は、約0.05～約10mA/cm<sup>2</sup>のビーム電流密度、約4K～約200の温度で行われる。より好ましくは、更なるイオン注入は、約0.5～約5.0mA/cm<sup>2</sup>のビーム電流密度、約25～約100の温度で行われる。

#### 【0030】

更なるイオン注入が、ベース・イオン注入工程によって生じる損傷領域の下に非晶質領域を形成することに注意すべきである。本発明の次の加熱工程の間に、非晶質領域および損傷領域は、Ge拡散を妨げるバリア層の一部となる。

#### 【0031】

##### 2. 低ドーズ・イオン注入

本発明のこの実施例についてここで使用される語句“低ドーズ”は、約 $4 \times 10^{17}$ /cm<sup>2</sup>以下のイオン・ドーズ（約 $1 \times 10^{16}$ ～約 $3.9 \times 10^{17}$ /cm<sup>2</sup>のイオン・ドーズがより好ましい）を意味する。この低ドーズ注入は、約40～約10000keVのエネルギー（約40～約210keVの注入エネルギーが特に好ましい）で行われる。

#### 【0032】

ベース・イオン注入と呼ばれるこの注入は、約100～約800の温度で行われる。より好ましくは、ベース・イオン注入は、約0.05～約500mA/cm<sup>2</sup>のビーム電流密度、約200～約650の温度で行われる。

#### 【0033】

望むならば、ベース・イオン注入工程の後に、上述した条件を用いて行われる更なる酸素注入を続けてよい。

#### 【0034】

上述した種類の注入条件は、例示であり、本発明の範囲を制限しないことを再度強調する。代わりに、本発明は、従来のSIMOX方法で一般に用いられる全ての従来のイオン注入を意図している。

#### 【0035】

図1(b)は、Ge含有層16がSi含有基板10の上面の上に形成された後に形成される構造を示す。本発明のこの時点で形成されるGe含有層16は、SiGe合金層または純Ge層である。語句“SiGe合金層”は、最大99.99原子パーセントのGeからなるSiGe合金を含むのに対し、純Geは、100原子パーセントのGeからなる層を含む。SiGe合金層を用いる場合は、SiGe合金層内のGe含有量が約0.1～約99.9原子パーセント（約10～約35原子パーセントが特に好ましい）であることが好ましい。

#### 【0036】

本発明によれば、Ge含有層16は、当業者に周知である従来のエピタキシャル成長方法を用いてSi含有基板10の上面の上に形成される。従来のエピタキシャル成長方法は、(i)熱力学的に安定な(臨界膜厚未満の)SiGe合金層または純Ge層を成長し、(ii)準安定で格子欠陥、すなわち不整合転位およびTD転位の無いSeGe合金層または純Ge層を成長し、または(iii)部分的または全体的に格子緩和されたSiGe層を成長することを可能にする。格子緩和の程度は、成長温度、Ge濃度、厚さまたはSiキャッピング層の存在によって制御される。条件(i),(ii)または(iii)を満たすことのできる、このようなエピタキシャル成長方法の一例は、減圧化学気相成長(LPCVD)、超高真空化学気相成長(UHVCVD)、常圧化学気相成長(APCVD)、分子線エピタキシ(MBE)およびプラズマ化学気相成長(PECVD)含むが、これらに制限されない。

#### 【0037】

10

20

30

40

50

本発明のこの時点で形成されるGe含有層16の厚さは、さまざまであるが、一般にはGe含有層16は、約10～約500nmの厚さ（約20～約200nmの厚さが最も好ましい）を有する。

#### 【0038】

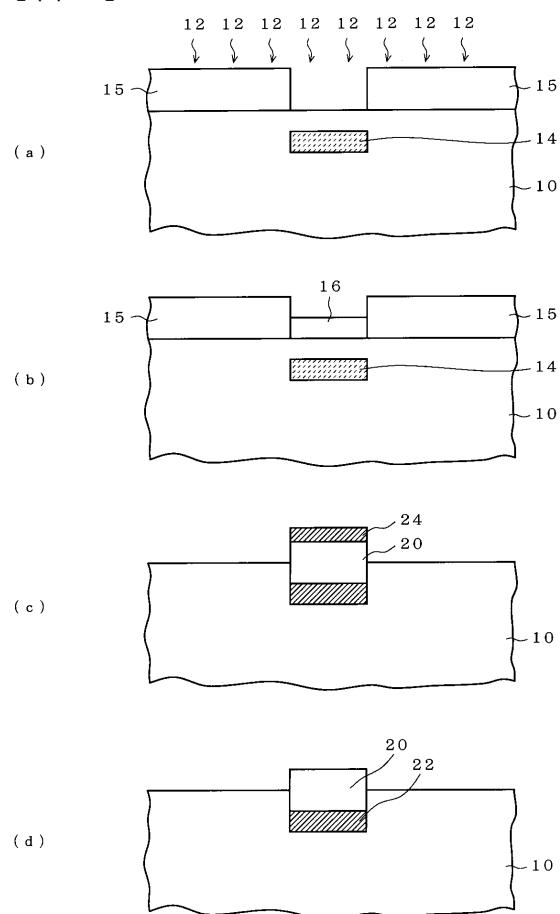

図3に示す本発明の他の実施例では、任意キャップ層18は、本発明の加熱工程を行う前にGe含有層16の上に形成される。本発明で用いられる任意キャップ層は、エピタキシャル・シリコン（エピSi）、エピタキシャル・シリコン・ゲルマニウム（エピSiGe）、アモルファス・シリコン（a:Si）、アモルファス・シリコン・ゲルマニウム（a:SiGe）、単結晶または多結晶のSi、またはこれらの多層の組み合わせを含む、SiまたはSi含有材料からなるが、これらに制限されない。好ましい実施例では、キャップ層18は、エピSiで構成される。層16および層18が同じ反応室内で形成されてもよいし、または形成されなくてもよいことに注意すべきである。10

#### 【0039】

存在するならば任意キャップ層18は、約1～約100nmの厚さ（約1～約30nmの厚さが最も好ましい）を有する。任意キャップ層18は、上述したエピタキシャル成長方法を含み、周知の付着方法を利用して形成される。

#### 【0040】

本発明の一実施では、Si含有基板10の表面の上に約1～約2000nmの厚さを有する純GeまたはSiGe合金（15～20原子パーセントのGe）層16を形成し、その後、GeまたはSiGe層の上に約1～約100nmの厚さを有するSiキャップ層18を形成することが好ましい。20

#### 【0041】

注入されたSi含有基板の上にGe含有層16（および任意キャップ層18）を形成した後、基板は、次に、表面Si含有層、Ge含有層および存在するならば任意Siキャップ層18に渡ってGeの相互拡散を可能にする温度で加熱、すなわちアニールされ、それによって、加熱工程の間に同様に形成されるバリア層22の上に、十分に格子緩和された単結晶SiGe層20を形成する。図1（c）は、本発明の加熱工程が行われた後に形成される構造を示す。酸化膜層24が、加熱工程の間に層20の上に形成されることに注意すべきである。この酸化膜層は、一般に（常にというわけではないが）、SiGeと比較して、酸化膜を除去することに対して高選択性を有するHFのような化学エッティング液が用いられる従来のウェット・エッティング方法を用いて、加熱工程後に構造から除去される。30

#### 【0042】

酸化膜層が除去されると、単結晶Si層が層20の上に形成され、本発明の上述した処理工程が多数回繰り返されて、多層の格子緩和されたSiGe基板材料を製造することに注意すべきである。

#### 【0043】

本発明の加熱工程の後に形成される酸化膜層24は、約10～約1000nmの範囲にわたる種々の厚さ（約20～約500nmの厚さが最も好ましい）を有する。

#### 【0044】

特に、本発明の加熱工程は、約900～約1350の高温（約1200～約1350の温度が最も好ましい）で行われるアニール工程である。さらに、本発明の加熱工程は、少なくとも1つの酸素含有ガス、例えばO<sub>2</sub>、NO、N<sub>2</sub>O、オゾン、空気および他の同様の酸素含有ガスを含む酸化雰囲気中で行われる。酸素含有ガスは、互いに混合されても良いし（例えばO<sub>2</sub>とNOの混合物）、またはガスは、He、Ar、N<sub>2</sub>、Xe、KrまたはNeのような不活性ガスで希釈されても良い。40

#### 【0045】

加熱工程は、一般に約10～約1800分の範囲にわたる種々の期間（約60～約600分の期間が最も好ましい）行われても良い。加熱工程は、1つの目標温度で行われても良く、または種々のランプ（ramp）速度およびソーク（soak）回数を用いる種々

のランプおよびソーケ(s o a k)サイクルが使用できる。

【0046】

加熱工程は、Ge原子に対して拡散バリアとして作用する表面酸化膜層、すなわち層24の存在を実現するために、酸化雰囲気下で行われる。したがって、酸化膜層24が、構造の表面に形成されると、Geはバリア層22と酸化膜層24の間にトラップされる。表面酸化膜は厚さが増加すると、Geは、層14、層16および任意の層18に渡って更に均一に分布するが、連続的にかつ効率的に酸化膜層に侵入することを阻止される。そこで、この加熱工程の間に(現在均一化されている)層が薄くなるにつれて、相対的なGe割合は増加する。加熱工程が、希釈された酸素含有ガス中で約1200～1320の温度で行われると、効率的な熱混合が、本発明で実現される。

10

【0047】

SiGe層の溶融点に基づく、適合した熱サイクルを使用することがここでも意図されている。このような場合、温度は、SiGe層の溶融点より低い範囲に調整される。

【0048】

酸化があまりにも急速に起こるならば、Geは、充分に早く表面酸化膜/SiGe界面から離れたところまで拡散できず、Geが酸化膜を通って運ばれ(Geは失われる)か、または、合金溶融温度に達するほどGeの界面濃度が極めて高くなることに注意すべきである。

【0049】

本発明の高温加熱工程の役割は、(1) Si含有基板内のGe拡散を妨げるバリア層22を形成すること、(2)アニールの間に均一な分布を維持しながらGe原子が更に急速に拡散できるようにすること、(3)最初の層構造に、平衡構成になることを容易にする熱供給を行うことである。この加熱工程が行われた後、構造は、バリア層22と表面酸化膜層24との間に挟まれた、均一で十分に格子緩和されたSiGe合金層、すなわち層20を含む。

20

【0050】

本発明によれば、十分に格子緩和されたSiGe層20は、約2000nm以下の厚さ(約10～約100nmの厚さが特に好ましい)を有する。本発明のアニール工程の間に形成されたバリア層22は、約500nm以下の厚さ(約50～約200の厚さが特に好ましい)を有する。本発明において形成される、十分に格子緩和されたSiGe層20が、従来のSiGeバッファ層よりも薄く、約 $5 \times 10^7$ 欠陥/cm<sup>2</sup>より小さい不整合およびTDを含む欠陥密度を有することに注意すべきである。この欠陥密度値は、現在のSGOI材料の公表されている値に近い。

30

【0051】

本発明において形成される、十分に格子緩和されたSiGe層20は、約0.1～約9.9%の原子パーセントの最終Ge含有量(約10～約35原子パーセントのGeが特に好ましい)を有する。十分に格子緩和されたSiGe層20のもう一つの特徴は、約1～約100%の測定された格子緩和(約50～約80%の測定された格子緩和が特に好ましい)を有することである。

40

【0052】

上述したように、表面酸化膜層24は、例えば図2(d)に示すSiGeオン・インシユレータ基板材料を与えるために本発明のこの時点で剥離される(キャップ層が格子緩和されたSiGe層の形成に使用されたので、基板材料がキャップ層を含まないことに注意すべきである)。

【0053】

図2は、パターニングされたバリア層が形成される本発明の実施例を示す。本発明のこの実施例では、図2(a)に示されるような、マスクされたイオン注入工程が行われる。図2(a)では、参照番号15は、本発明のこの実施例で使用される注入マスクを示す。図2(a)に示される注入マスクは、当業者に周知の従来技術を用いて形成される。注入マスク15は、図2(a)に示される注入工程後に除去されてもよいが、Ge含有層16

50

を形成している間、構造に残っていてもよい(図2(b)参照)。Ge含有層16の形成後、マスク15は、本発明のこの時点で除去されてもよい。注入マスクの除去は、当業者に周知の従来の剥離方法を用いて行われる。図2(c)は、加熱工程後の構造を示し、図2(d)は、酸化膜層24の除去後の構造を示す。注入マスクが全処理の間中、構造に残っていてもよいことに注意すべきである。

#### 【0054】

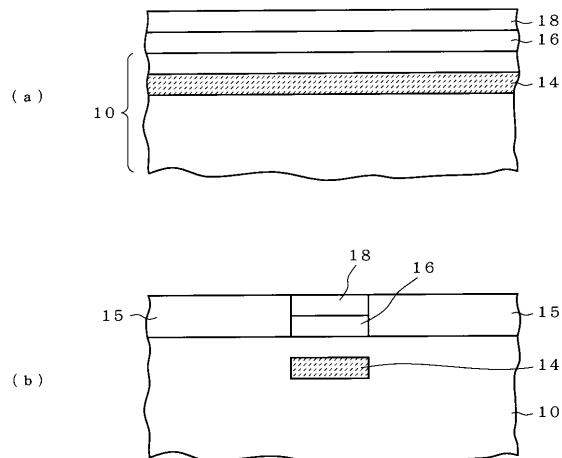

図4は、図1(d)および図2(d)のSiGe層20の上にそれぞれSi層26を形成した後に得られる構造を示す。Si層26は、周知の従来のエピタキシャル付着方法を用いて形成される。エピSi層26の厚さは、さまざまあっても良いが、一般にエピSi層26は、約1～約100nmの厚さ(約1～約30nmの厚さが特に好ましい)を有する。

#### 【0055】

幾つかの例では、追加のSiGeが、上述した処理工程を利用して、十分に格子緩和されたSiGe層20の上に形成でき、その後にエピSi層26が形成できる。層20が、エピ層26と比較して大きな面内(in-plane)格子パラメータを有するので、エピ層26は、引っ張り歪みを生じるであろう。

#### 【0056】

上述したように、本発明は、また、本発明のSiGeオン・インシュレータ基板材料を少なくとも含む超格子構造および格子間不整合構造を意図している。超格子構造の場合には、このような構造は、本発明の十分に格子緩和されたSiGeオン・インシュレータ基板材料と、基板材料の十分に格子緩和されたSiGe層の上に形成されるSiとSiGeの交互層とを少なくとも含む。

#### 【0057】

格子間不整合構造の場合には、GaAs、GaP等の化合物が、本発明のSiGeオン・インシュレータ基板材料の十分に格子緩和されたSiGe層の上に形成される。

#### 【0058】

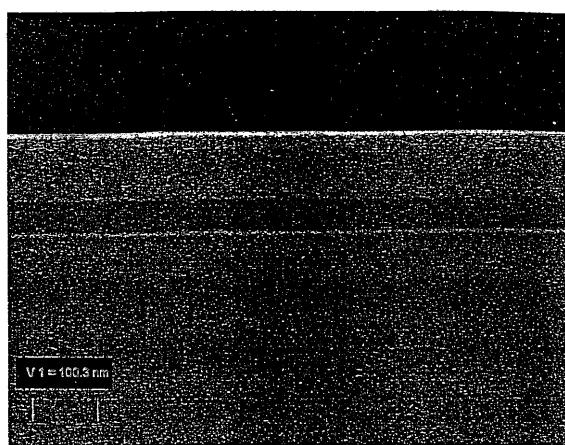

図5は、本発明の方法を用いて形成される十分に格子緩和された(表面酸化膜を剥離した)SiGeオン・インシュレータ基板材料の実際のSEM像である。特に、図5に示されるSiGeオン・インシュレータ基板材料は、上述した範囲内に入る注入条件を用いてSi含有ウエハに酸素イオンを最初に注入することによって作製された。次に60nm-17%SiGe合金層を、注入されたSi含有基板の上に成長させ、その後、1つのアニール/酸化が、Ar-O<sub>2</sub>雰囲気で、1320で行われた。この像では、最上部(黒)領域は、サンプルの上の領域(SEM室)である。

#### 【0059】

最初の薄灰色層はSGOI層であり、その下に、高温工程の間に形成された埋め込み酸化膜層(BOX)である濃い灰色帯がある。BOXの下の薄灰色層は、Si基板である。X線回折は、SiGe層(94.2nm)が4原子%のGeを含み、92%格子緩和されたことを示した。埋め込み酸化膜は、約47.10nmの厚さを有し、連続しており、かつ良好に形成された。

#### 【0060】

要するに、SiGeオン・インシュレータ基板材料は、高温SIMOXアニールの利点と、SiGeオン・インシュレータを形成するGe拡散および分離方法の簡便さとを併せ持つ統合方法としての本発明で形成される。

#### 【0061】

本発明を、好ましい実施例について特に示し、かつ説明したが、本発明の範囲と趣旨を逸脱することなく、形態および細部において上述の変更および他の変更を行うことが可能であることは、当業者には分かるであろう。したがって、説明され、かつ示された正確な形態および細部に本発明が制限されないことを意図している。

#### 【0062】

まとめとして、本発明の構成に関して以下の事項を開示する。

10

20

30

40

50

(1) 十分に格子緩和された高品質 SiGe オン・インシュレータ基板材料を製造する方法において、

Ge の拡散バリアの働きをするのに充分なイオン濃度を有する注入リッチ領域を形成するために Si 含有基板にイオンを注入する工程を含み、前記注入リッチ領域は、その上に Si 含有基板の表面層が配置され、

注入された Si 含有基板の上に Ge 含有層を形成する工程を含み、

(i) 拡散バリア層の形成と、(ii) 前記 Ge 含有層、および注入リッチ領域の上に配置される Si 含有基板の前記表面層に渡る Ge の相互拡散とを可能にする温度で基板を加熱する工程を含み、これにより前記拡散バリア層の上に十分に格子緩和された SiGe 層を形成する、製造方法。

(2) 前記注入イオンは、酸素イオン、窒素イオン、NO イオン、不活性ガスまたはこれらの混合物を含む上記(1)に記載の製造方法。

(3) 前記注入イオンは、酸素イオンを含む上記(1)に記載の製造方法。

(4) 前記注入する工程は、プランケット注入処理またはマスクされた注入処理を含む上記(1)に記載の製造方法。

(5) 前記注入する工程は、約  $4 \times 10^{17} / \text{cm}^2$  以上のイオン・ドーズを用いて行われる高ドーズ・イオン注入処理を含む上記(1)に記載の製造方法。

(6) 前記高ドーズ・イオン注入は、約 0.05 ~ 約 500 mA / cm<sup>2</sup> のビーム電流密度および約 150 ~ 約 1000 keV のエネルギーで作動するイオン注入装置内で行われる上記(5)に記載の製造方法。

(7) 前記高ドーズ・イオン注入処理は、約 200 ~ 約 800 の温度で行われる上記(5)に記載の製造方法。

(8) 前記高ドーズ・イオン注入処理は、ベース・イオン注入工程の後に続いて約 4 K ~ 約 200 の温度で行われる更なるイオン注入工程を含む上記(5)に記載の製造方法。

(9) 前記更なるイオン注入工程は、約 0.05 ~ 約 10 mA / cm<sup>2</sup> のビーム電流密度で、約  $1 \times 10^{14} \sim 1 \times 10^{16} / \text{cm}^2$  のイオン・ドーズ、約 40 keV 以上のエネルギーを用いて行われる上記(8)に記載の製造方法。

(10) 前記注入する工程は、約  $4 \times 10^{17} / \text{cm}^2$  以下のイオン・ドーズを用いて行われる低ドーズ・イオン注入処理を含む上記(1)に記載の製造方法。

(11) 前記低ドーズ・イオン注入は、約 0.05 ~ 約 500 mA / cm<sup>2</sup> のビーム電流密度および約 40 ~ 約 1000 keV のエネルギーで作動するイオン注入装置内で行われる上記(10)に記載の製造方法。

(12) 前記低ドーズ・イオン注入処理は、約 100 ~ 約 800 の温度で行われる上記(10)に記載の製造方法。

(13) 前記低ドーズ・イオン注入処理は、ベース・イオン注入工程の後に続いて約 4 K ~ 約 200 の温度で行われる更なるイオン注入工程を含む上記(10)に記載の製造方法。

(14) 前記更なるイオン注入工程は、約 0.05 ~ 約 10 mA / cm<sup>2</sup> のビーム電流密度で、約  $1 \times 10^{14} \sim 1 \times 10^{16} / \text{cm}^2$  のイオン・ドーズ、約 40 keV 以上のエネルギーを用いて行われる上記(13)に記載の製造方法。

(15) 前記 Ge 含有層は、SiGe 合金層または純 Ge である上記(1)に記載の製造方法。

(16) 前記 Ge 含有層は、最大 99.99 原子パーセントの Ge からなる SiGe 合金層である上記(1)に記載の製造方法。

(17) 前記 Ge 含有層は、減圧化学気相成長、常圧化学気相成長、超高真空化学気相成長、分子線エピタキシおよびプラズマ化学気相成長からなるグループから選択されるエピタキシャル成長処理によって形成される上記(1)に記載の製造方法。

(18) 前記加熱する工程の前に前記 Ge 含有層の上に Si キャップ層を形成する工程を更に含む上記(1)に記載の製造方法。

(19) 前記 Si キャップ層は、エピ Si、エピ SiGe、a : Si、a : SiGe、单

10

20

30

40

50

結晶または多結晶 Si、またはこれらの多層の組み合わせを含む上記(18)に記載の製造方法。

(20) 表面酸化膜層は、前記加熱する工程の間に形成される上記(1)に記載の製造方法。

(21) ウエット化学エッチング処理を利用して前記表面酸化膜層を除去する工程を更に含む上記(20)に記載の製造方法。

(22) 前記加熱する工程は、少なくとも1つの酸素含有ガスを含む酸化雰囲気中で行われる上記(1)に記載の製造方法。

(23) 不活性ガスを更に含み、前記不活性ガスが前記少なくとも1つの酸素含有ガスを希釈するために用いられる上記(22)に記載の製造方法。 10

(24) 前記加熱する工程は、約900～約1350の温度で行われる上記(1)に記載の製造方法。

(25) 前記十分に格子緩和されたSiGe層の上に追加のSiGe層を成長する工程を更に含む上記(1)に記載の製造方法。

(26) 前記追加のSiGe層の上に歪みSi層を形成する工程を更に含む上記(25)に記載の製造方法。

(27) 前記十分に格子緩和されたSiGe層の上に歪みSi層を形成する工程を更に含む上記(1)に記載の製造方法。

(28) Si含有基板と、

前記Si含有基板の上に存在してGe拡散を妨げる絶縁領域と、

前記絶縁領域の上に存在する十分に格子緩和されたSiGe層とを備え、

前記十分に格子緩和されたSiGe層は、約2000nm以下の厚さおよび約 $5 \times 10^7$ 原子/cm<sup>2</sup>以下の欠陥密度を有する基板材料。 20

(29) 前記絶縁領域は、パターニングされ、またはパターニングされていない上記(28)に記載の基板材料。

(30) 前記絶縁領域は、埋め込み酸化膜領域である上記(28)に記載の基板材料。

(31) 前記十分に格子緩和されたSiGe層は、約1～約100%の測定格子緩和を有する上記(28)に記載の基板材料。

(32) Si含有基板と、

前記Si含有基板の上に存在してGe拡散を妨げる絶縁領域と、

前記絶縁領域の上に存在する十分に格子緩和されたSiGe層と、

前記十分に格子緩和されたSiGe層の上に形成される歪みSi層とを備え、

前記十分に格子緩和されたSiGe層は、約2000nm以下の厚さおよび約 $5 \times 10^7$ 原子/cm<sup>2</sup>以下の欠陥密度を有するヘテロ構造。 30

(33) 前記絶縁領域は、パターニングされ、またはパターニングされていない上記(32)に記載のヘテロ構造。

(34) 前記絶縁領域バリア層は、埋め込み酸化膜領域である上記(32)に記載のヘテロ構造。

(35) 前記十分に格子緩和されたSiGe層は、約1～約100%の測定格子緩和を有する上記(32)に記載の基板材料。

(36) 前記歪みSi層は、エピSi層を含む上記32に記載のヘテロ構造。

(37) 格子緩和されたSiGeと歪みSiの交互層は、前記歪みSi層の上に形成される上記(32)に記載のヘテロ構造

(38) 前記歪みSi層は、GaAsとGaPからなるグループから選択される格子間不整合化合物で置き換えられる上記(32)に記載のヘテロ構造。

【図面の簡単な説明】

【0063】

【図1】薄くて高品質で十分に格子緩和されたSiGeオン・インシュレータ基板材料を製造する本発明において用いられる基本処理工程を示す断面図である。これらの図には、Ge拡散を妨げる、連続した、すなわちパターニングされていないバリア層が形成されて

10

20

30

40

50

いる。

【図2】薄くて高品質で十分に格子緩和されたSiGeオン・インシュレータ基板材料を製造する本発明の他の実施例において用いられる基本処理工程を示す断面図である。これらの図には、Ge拡散を妨げる、パターニングされたバリア層が形成されている。

【図3】図1(b)に示される構造および図2(b)に示される構造に形成されるGe含有層の上にSiキャップ層が形成される本発明の他の実施例を示す断面図である。

【図4】図1(d)および図2(d)の薄くて高品質で十分に格子緩和されたそれぞれのSiGeオン・インシュレータ基板材料の上の歪みSi層の形成を示す断面図である。

【図5】本発明の処理工程を用いて形成されたSiGeオン・インシュレータ基板材料のSEM像を示す図である。

10

20

#### 【符号の説明】

##### 【0064】

- 10 Si含有基板

- 12 イオン

- 14 注入りチ領域

- 15 注入マスク

- 16 Ge含有層

- 18 任意キャップ層

- 20 SiGe層

- 22 バリア層

- 24 酸化膜層

- 26 エビSi層

【図1】

【図2】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 ガヴァム・ジー・シャヒディ

アメリカ合衆国 10576 ニューヨーク州 パウンド リッジ バーネガット ロード 11

1

(72)発明者 ステファン・ダブリュ・ベデル

アメリカ合衆国 12590 ニューヨーク州 ワッピンガーズ フォールズ ニコル ドライブ

32

(72)発明者 デヴェンドラ・ケイ・サダナ

アメリカ合衆国 10570 ニューヨーク州 プレザントヴィル スカイ トップ ドライブ

90

(72)発明者 キース・イー・フォゲル

アメリカ合衆国 10547 ニューヨーク州 モヒガン レイク ルース レーン 4

F ターム(参考) 5F048 AC03 BA05 BA14 BA15 BA16

5F052 GC01 GC03 JA04 KA01 KA05