(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7159044号**

**(P7159044)**

(45)発行日 令和4年10月24日(2022.10.24)

(24)登録日 令和4年10月14日(2022.10.14)

(51)国際特許分類

H 0 3 K 5/134(2014.01)

F I

H 0 3 K

5/134

請求項の数 15 (全19頁)

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2018-515039(P2018-515039) |

| (86)(22)出願日       | 平成28年9月9日(2016.9.9)         |

| (65)公表番号          | 特表2018-534819(P2018-534819) |

|                   | A)                          |

| (43)公表日           | 平成30年11月22日(2018.11.22)     |

| (86)国際出願番号        | PCT/US2016/051073           |

| (87)国際公開番号        | WO2017/053090               |

| (87)国際公開日         | 平成29年3月30日(2017.3.30)       |

| 審査請求日             | 令和1年8月21日(2019.8.21)        |

| 審判番号              | 不服2021-5144(P2021-5144/J1)  |

| 審判請求日             | 令和3年4月21日(2021.4.21)        |

| (31)優先権主張番号       | 14/863,710                  |

| (32)優先日           | 平成27年9月24日(2015.9.24)       |

| (33)優先権主張国・地域又は機関 |                             |

|                   | 米国(US)                      |

|          |                                                                                        |

|----------|----------------------------------------------------------------------------------------|

| (73)特許権者 | 507364838<br>クアルコム、インコーポレイテッド<br>アメリカ合衆国 カリフォルニア 921<br>21 サン デイエゴ モアハウス ドライ<br>ブ 5775 |

| (74)代理人  | 100108453<br>弁理士 村山 靖彦                                                                 |

| (74)代理人  | 100163522<br>弁理士 黒田 晋平                                                                 |

| (72)発明者  | ジョシュア・ランス・パケット<br>アメリカ合衆国・カリフォルニア・92<br>121・サン・ディエゴ・モアハウス・<br>ドライブ・5775                |

| 合議体      |                                                                                        |

| 審判長      | 土居 仁士                                                                                  |

最終頁に続く

(54)【発明の名称】 データ電圧レベルに従ってデータをバッファリングするための反比例電圧 - 遅延バッファ

**(57)【特許請求の範囲】****【請求項1】**

データ入力信号の電圧レベルに応じて変動する集積回路内の論理経路の遅延を補償し、異なる電圧レベルにわたって前記論理経路のタイミング目標を達成するための反比例電圧-遅延バッファであって、

前記データ入力信号の反転した論理状態を有する制御信号を生成するための手段であつて、前記制御信号の遷移レートは、前記データ入力信号の電圧レベルに比例する、手段と、

前記データ入力信号および前記制御信号が第1の論理状態を有することに応答して、前記データ入力信号の弱論理状態を有するデータ出力信号を生成するための手段と、

前記制御信号が前記第1の論理状態を有し、前記データ入力信号が第2の論理状態を有することに応答して、前記データ入力信号の強論理状態を有する前記データ出力信号を生成するための手段であつて、前記第2の論理状態は、前記第1の論理状態の反対である、手段と、

前記データ入力信号および前記制御信号が前記第2の論理状態を有することに応答して、前記データ入力信号の弱論理状態を有する前記データ出力信号を生成するための手段と、

前記制御信号が前記第2の論理状態を有し、前記データ入力信号が前記第1の論理状態を有することに応答して、前記データ入力信号の強論理状態を有する前記データ出力信号を生成するための手段と

を含む、反比例電圧-遅延バッファ。

**【請求項2】**

10

20

前記データ入力信号に基づいて、前記制御信号を生成するための前記手段を遅延させるための手段をさらに含む、請求項1に記載の反比例電圧-遅延バッファ。

**【請求項3】**

請求項1に記載の反比例電圧-遅延バッファであって、

制御信号を生成するための前記手段が、前記データ入力信号の前記反転した論理状態を有する前記制御信号を生成するように構成された反転回路であって、前記制御信号の前記遷移レートは、前記データ入力信号の前記電圧レベルに比例する、反転回路を含み、

前記反比例電圧-遅延バッファがバス回路を含み、

前記バス回路は、第1のバスデバイスと第2のバスデバイスを含み、

前記第1のバスデバイスが、

前記データ入力信号および前記制御信号が前記第1の論理状態を有することに応答して、前記データ入力信号の弱論理状態を有する前記データ出力信号を生成するための前記手段と、

前記制御信号が前記第1の論理状態を有し、前記データ入力信号が前記第2の論理状態を有することに応答して、前記データ入力信号の前記強論理状態を有する前記データ出力信号を生成するための前記手段とを含み、

前記第2のバスデバイスが、

前記データ入力信号および前記制御信号が前記第2の論理状態を有することに応答して、前記データ入力信号の前記弱論理状態を有する前記データ出力信号を生成するための手段と、

前記制御信号が前記第2の論理状態を有し、前記データ入力信号が前記第1の論理状態を有することに応答して、前記データ入力信号の前記強論理状態を有する前記データ出力信号を生成するための手段とを含む、反比例電圧-遅延バッファ。

**【請求項4】**

前記第1のバスデバイスは、

前記制御信号を受信するように構成されたゲートと、

前記データ入力信号を受信するように構成されたソースと、

前記データ出力信号を提供するように構成されたドレインと

を含むp型金属酸化物半導体(PMOS)トランジスタを含み、

前記第2のバスデバイスは、

前記制御信号を受信するように構成されたゲートと、

前記データ入力信号を受信するように構成されたソースと、

前記データ出力信号を提供するように構成されたドレインと

を含むn型金属酸化物半導体(NMOS)トランジスタを含む、請求項3に記載の反比例電圧-遅延バッファ。

**【請求項5】**

前記反転回路はインバータを含む、請求項3に記載の反比例電圧-遅延バッファ。

**【請求項6】**

前記反転回路は、奇数個の直列結合されたインバータを含む、請求項3に記載の反比例電圧-遅延バッファ。

**【請求項7】**

前記反転回路および前記バス回路に電気的に結合された入力インバータであって、前記データ入力信号を生成し、前記反転回路および前記バス回路に前記データ入力信号を提供するように構成された入力インバータと、

前記バス回路に電気的に結合された出力インバータであって、前記データ出力信号を受信するように構成された出力インバータと

をさらに含む、請求項3に記載の反比例電圧-遅延バッファ。

**【請求項8】**

前記データ入力信号は、論理ゲートから受信される、請求項3に記載の反比例電圧-遅延バッファ。

10

20

30

40

50

**【請求項 9】**

前記データ出力信号は、論理ゲートに提供される、請求項3に記載の反比例電圧-遅延バッファ。

**【請求項 10】**

前記集積回路(IC)に組み込まれる、および/または

セットトップボックス、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、固定ロケーションデータユニット、モバイルロケーションデータユニット、携帯電話、セルラーフォン、スマートフォン、タブレット、ファブレット、コンピュータ、ポータブルコンピュータ、デスクトップコンピュータ、携帯情報端末(PDA)、モニタ、コンピュータモニタ、テレビ、チューナ、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、ポータブル音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビデオディスク(DVD)プレーヤ、ポータブルデジタルビデオプレーヤ、および自動車からなるグループから選択されるデバイスに組み込まれる、請求項3に記載の反比例電圧-遅延バッファ。

10

**【請求項 11】**

前記反転回路は、

前記データ入力信号の前記反転した論理状態を有する制御信号を生成するように構成されたインバータであって、前記制御信号の遷移レートは、前記データ入力信号の前記電圧レベルに比例する、インバータを含み、

前記第1のパスデバイスが、p型金属酸化物半導体(PMOS)トランジスタを含み、前記第2のパスデバイスが、n型金属酸化物半導体(NMOS)トランジスタを含み、

20

前記PMOSトランジスタが、

前記制御信号を受信するように構成されたゲートと、

前記データ入力信号を受信するように構成されたソースと、

データ出力信号を提供するように構成されたドレインとを含み、

前記NMOSトランジスタが、

前記制御信号を受信するように構成されたゲートと、

前記データ入力信号を受信するように構成されたソースと、

前記データ出力信号を提供するように構成されたドレインとを含む、

請求項3に記載の反比例電圧-遅延バッファ。

30

**【請求項 12】**

前記インバータは、PMOSトランジスタとNMOSトランジスタとを含む、請求項11に記載の反比例電圧-遅延バッファ。

**【請求項 13】**

遅延の後に前記インバータに前記データ入力信号を提供するように構成された偶数個の直列結合されたインバータをさらに含む、請求項11に記載の反比例電圧-遅延バッファ。

**【請求項 14】**

データ入力信号の電圧レベルに応じて変動する集積回路内の論理経路の遅延を、前記電圧レベルに反比例する時間量で前記データ入力信号をバッファリングすることで補償し、異なる電圧レベルにわたって前記論理経路のタイミング目標を達成するために反比例電圧-遅延バッファにより実行される方法であって、

40

データ入力信号の反転した論理状態を有する制御信号を生成するステップであって、前記制御信号の遷移レートは、前記データ入力信号の電圧レベルに比例する、ステップと、

前記データ入力信号および前記制御信号が第1の論理状態を有することに応答して、前記データ入力信号の弱論理状態を有するデータ出力信号を生成するステップと、

前記制御信号が前記第1の論理状態を有し、前記データ入力信号が第2の論理状態を有することに応答して、前記データ入力信号の強論理状態を有する前記データ出力信号を生成するステップであって、前記第2の論理状態は、前記第1の論理状態の反対である、ステップと、

前記データ入力信号および前記制御信号が前記第2の論理状態を有することに応答して

50

、前記データ入力信号の弱論理状態を有する前記データ出力信号を生成するステップと、前記制御信号が前記第2の論理状態を有し、前記データ入力信号が前記第1の論理状態を有することに応答して、前記データ入力信号の強論理状態を有する前記データ出力信号を生成するステップと

を含む方法。

【請求項 15】

前記データ入力信号に基づいて、前記制御信号を生成するステップを遅延させるステップをさらに含む、請求項14に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

優先出願

本出願は、その全体が参照により本明細書に組み込まれる、2015年9月24日に出願された「INVERSELY PROPORTIONAL VOLTAGE-DELAY BUFFERS FOR BUFFERING DATA ACCORDING TO DATA VOLTAGE LEVELS」と題する米国特許出願第14/863,710号の優先権を主張する。

【0002】

本開示の技術は、一般に、データバッファに関し、詳細には、そのようなデータバッファのバッファリング時間に関する。

【背景技術】

【0003】

デジタル論理により設計された集積回路(IC)は、データが送信され得る複数の論理経路を含む。各論理経路は、対応する遅延を有し、その結果、特定の論理経路を通じて送信されたデータが、遅延の後に意図された宛先において受信される。特定の論理経路に対応する遅延全体は、少なくとも2つのタイプの遅延、すなわち、レジスタ-キャパシタ(RC)遅延およびゲート遅延を含み得る。RC遅延は、データが送信されるワイヤなど、論理経路内の金属成分の抵抗性および容量性特性に起因する。特に、論理経路のRC遅延は、論理経路の抵抗性および容量性特性が電圧の変動に伴って変化することがないので、送信されるデータの複数の電圧レベルにわたって一定のままである。さらに、論理経路のゲート遅延は、論理経路内の論理ゲートの数、ならびに各論理ゲートの切り替え速度に基づく。したがって、論理経路のゲート遅延は、より低い入力電圧に起因して論理ゲートがより遅く切り替わる場合に増大することがあり、より高い入力電圧に起因して論理ゲートがより迅速に切り替わる場合に減少することがある。

【0004】

特に、IC内の各論理経路は、論理経路の遅延によって影響される関連タイミング目標を有し得る。たとえば、論理経路の遅延により、データが時間的にあまりに早く宛先に到着することで、ICにおいて論理工ラーが発生することがある。論理経路のタイミングは、論理工ラーを回避するために論理経路およびICが関連タイミング目標を達成するのを助けるように変更され得る。論理経路のタイミングを変更する1つの方法は、バッファが追加の遅延をもたらすように論理経路にバッファを挿入することによるものである。たとえば、データが宛先にいくつかのクロックサイクル数だけあまりに早く到着するようにする競合状態を論理経路が有する場合、データが所望の時間に宛先に提供されるように、論理経路に1つまたは複数のバッファが挿入され得る。

【0005】

論理経路にバッファを挿入することで、論理経路は、提供されたデータが特定の電圧を有するときにタイミング目標を達成することが可能であり得るが、論理経路は、他の電圧でデータを提供したときにタイミング目標を達成できないことがある。たとえば、より高い電圧での論理経路の遅延は、主にRC遅延に起因し得る。このことは、より高い電圧により、論理経路内の論理ゲートがより迅速に切り替わることで、論理経路に関連するゲート遅延が減少するので、当てはまる。代替的に、より低い電圧での論理経路の遅延は、主に

10

20

30

40

50

ゲート遅延に起因し得る。このことは、より低い電圧により、論理経路内の論理ゲートがより遅く切り替わることで、論理経路に関連するゲート遅延が増大するので、当てはまる。このようにして、論理経路の遅延は、より高い電圧およびより低い電圧にわたって変動することがあるので、バッファを挿入して、ある電圧でタイミング目標を達成しても、別の電圧ではタイミング目標を達成しないことがある。したがって、複数の電圧レベルにわたってICにおける論理経路のタイミング目標を達成するために使用され得るバッファを用いることが有利となる。

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0006】

発明を実施するための形態で開示する態様は、データ電圧レベルに従ってデータをバッファリングするための反比例電圧-遅延バッファを含む。一態様では、反比例電圧-遅延バッファは、データ信号の電圧レベルに反比例する時間量でデータ信号をバッファリングするように構成される。たとえば、反比例電圧-遅延バッファは、より短い遅延でより高い電圧のデータ信号を保持するが、より長い遅延でより低い電圧のデータ信号を保持することができる。電圧レベルに反比例する遅延をもたらすために、反比例電圧-遅延バッファは、反転回路とバス回路とを含む。反転回路は、データ信号の論理反転である制御信号を生成するように構成される。特に、制御信号は、データ信号の電圧レベルに比例するレートで遷移する。バス回路は、データ信号および制御信号が同じ論理状態を有するときに、データ信号の弱論理状態を生成するように構成される。言い換えれば、バス回路は、データ信号が別の論理状態に遷移したときに、ただし、制御信号がデータ信号の反対の論理状態に遷移する前に、弱論理状態を生成するように構成される。特に、より低い電圧のデータ信号に基づく弱論理状態は、論理経路の次の段階をトリガすることが可能ではない。さらに、バス回路は、データ信号および制御信号が反対の論理状態を有するときに、データ信号の強論理状態を生成するように構成される。言い換えれば、バス回路は、データ信号の反転論理状態である制御信号を生成する時間を反転回路が有した後に、強論理状態を生成するように構成される。より低い電圧またはより高い電圧のいずれかのデータ信号の強論理状態は、論理経路における次の段階をトリガすることが可能である。制御信号遷移レートは、データ信号の電圧レベルに比例するので、データ信号は、そのような電圧レベルに従った時間量でバッファリングされる。このようにして、複数の電圧レベルにわたってICにおける論理経路のタイミング目標を達成するために、反比例電圧-遅延バッファが使用され得る。

#### 【0007】

この点について、一態様では、反比例電圧-遅延バッファが開示される。反比例電圧-遅延バッファは、データ入力信号の反転した論理状態を有する制御信号を生成するように構成された反転回路を含み、制御信号の遷移レートは、データ入力信号の電圧レベルに比例する。反比例電圧-遅延バッファは、バス回路をさらに含む。バス回路は、第1のバスデバイスを含む。第1のバスデバイスは、データ入力信号および制御信号が第1の論理状態を有することに応答して、データ入力信号の弱論理状態を有するデータ出力信号を生成するように構成される。第1のバスデバイスは、制御信号が第1の論理状態を有し、データ入力信号が第2の論理状態を有することに応答して、データ入力信号の強論理状態を有するデータ出力信号を生成するようにさらに構成され、第2の論理状態は、第1の論理状態の反対である。バス回路は、第2のバスデバイスをさらに含む。第2のバスデバイスは、データ入力信号および制御信号が第2の論理状態を有することに応答して、データ入力信号の弱論理状態を有するデータ出力信号を生成するように構成される。第2のバスデバイスは、制御信号が第2の論理状態を有し、データ入力信号が第1の論理状態を有することに応答して、データ入力信号の強論理状態を有するデータ出力信号を生成するようにさらに構成される。

#### 【0008】

別の態様では、反比例電圧-遅延バッファが開示される。反比例電圧-遅延バッファは、データ入力信号の反転した論理状態を有する制御信号を生成するための手段を含み、制御

10

20

30

40

50

信号の遷移レートは、データ入力信号の電圧レベルに比例する。反比例電圧-遅延バッファは、データ入力信号および制御信号が第1の論理状態を有することに応答して、データ入力信号の弱論理状態を有するデータ出力信号を生成するための手段を含む。反比例電圧-遅延バッファは、制御信号が第1の論理状態を有し、データ入力信号が第2の論理状態を有することに応答して、データ入力信号の強論理状態を有するデータ出力信号を生成するための手段をさらに含み、第2の論理状態は、第1の論理状態の反対である。反比例電圧-遅延バッファは、データ入力信号および制御信号が第2の論理状態を有することに応答して、データ入力信号の弱論理状態を有するデータ出力信号を生成するための手段を含む。反比例電圧-遅延バッファは、制御信号が第2の論理状態を有し、データ入力信号が第1の論理状態を有することに応答して、データ入力信号の強論理状態を有するデータ出力信号を生成するための手段をさらに含む。

10

#### 【0009】

別の態様では、データ入力信号の電圧レベルに反比例する時間量でデータ入力信号をバッファリングするための方法が開示される。本方法は、データ入力信号の反転した論理状態を有する制御信号を生成するステップを含み、制御信号の遷移レートは、データ入力信号の電圧レベルに比例する。本方法は、データ入力信号および制御信号が第1の論理状態を有することに応答して、データ入力信号の弱論理状態を有するデータ出力信号を生成するステップをさらに含む。本方法は、制御信号が第1の論理状態を有し、データ入力信号が第2の論理状態を有することに応答して、データ入力信号の強論理状態を有するデータ出力信号を生成するステップをさらに含み、第2の論理状態は、第1の論理状態の反対である。本方法は、データ入力信号および制御信号が第2の論理状態を有することに応答して、データ入力信号の弱論理状態を有するデータ出力信号を生成するステップをさらに含む。本方法は、制御信号が第2の論理状態を有し、データ入力信号が第1の論理状態を有することに応答して、データ入力信号の強論理状態を有するデータ出力信号を生成するステップをさらに含む。

20

#### 【0010】

別の態様では、反比例電圧-遅延バッファが開示される。反比例電圧-遅延バッファは、データ入力信号の反転した論理状態を有する制御信号を生成するように構成されたインバータを含み、制御信号の遷移レートは、データ入力信号の電圧レベルに比例する。反比例電圧-遅延バッファは、パスゲートをさらに含む。パスゲートは、p型金属酸化物半導体(PMOS)トランジスタを含む。PMOSトランジスタは、制御信号を受信するように構成されたゲートと、データ入力信号を受信するように構成されたソースと、データ出力信号を提供するように構成されたドレインとを含む。パスゲートは、n型金属酸化物半導体(NMOS)トランジスタをさらに含む。NMOSトランジスタは、制御信号を受信するように構成されたゲートと、データ入力信号を受信するように構成されたソースと、データ出力信号を提供するように構成されたドレインとを含む。

30

#### 【図面の簡単な説明】

#### 【0011】

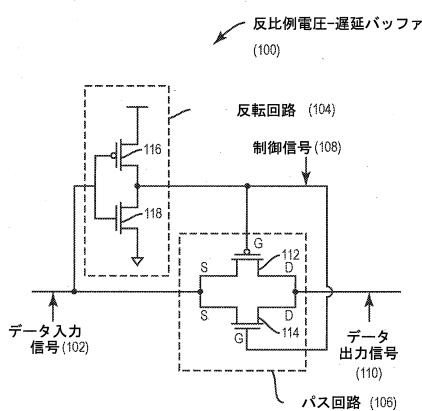

【図1A】データ入力信号の電圧レベルに反比例する時間量でデータ入力信号をバッファリングするように構成された例示的な反比例電圧-遅延バッファの回路図である。

40

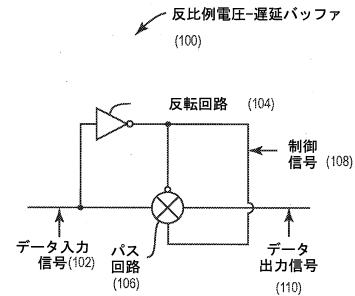

【図1B】図1Aにおける反比例電圧-遅延バッファの論理図である。

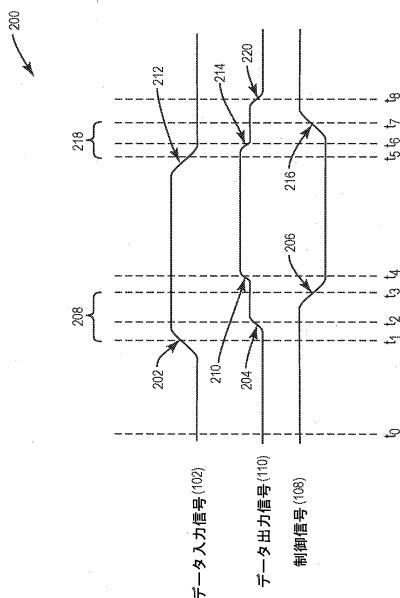

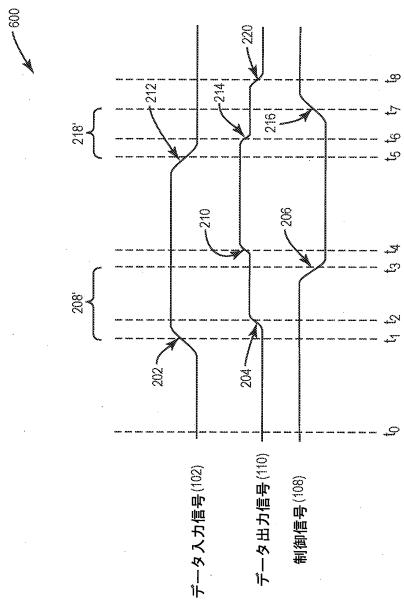

【図2】データ入力信号の遷移に応答した、図1Aにおける反比例電圧-遅延バッファの信号の例示的なタイミングを示すタイミング図である。

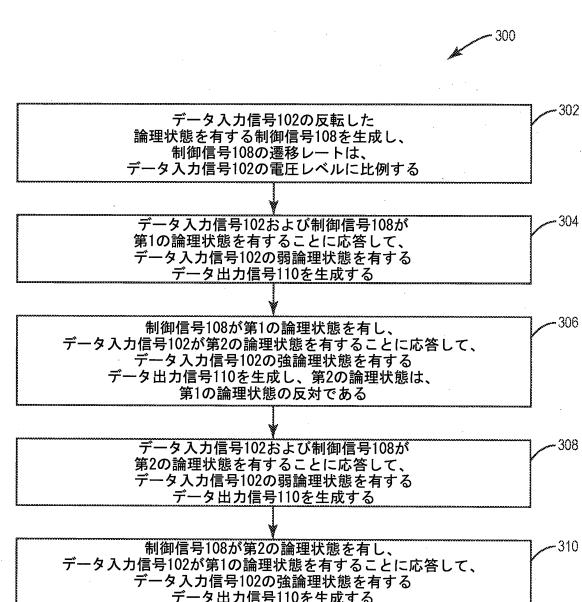

【図3】データ入力信号の電圧レベルに反比例する時間量でデータ入力信号をバッファリングするために、図1Aにおける反比例電圧-遅延バッファによって用いられる例示的なプロセスのフローチャートである。

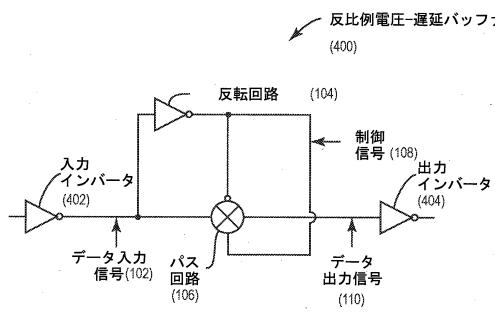

【図4】駆動強度(drive strength)目的で入力インバータおよび出力インバータを含む別の反比例電圧-遅延バッファの論理図である。

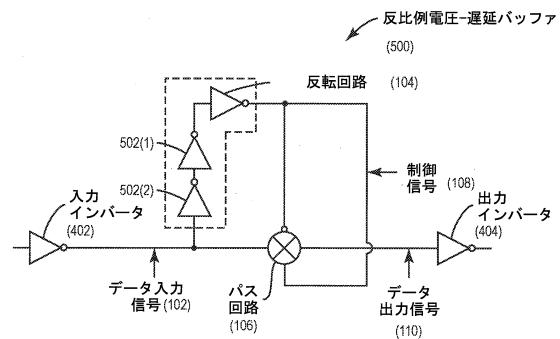

【図5】特にデータ入力信号のより低い電圧レベルで、遅延を増大させるための追加のインバータを含む別の反比例電圧-遅延バッファの論理図である。

50

【図6】データ入力信号の遷移に応答した、図5における反比例電圧-遅延バッファの信号の例示的なタイミングを示すタイミング図である。

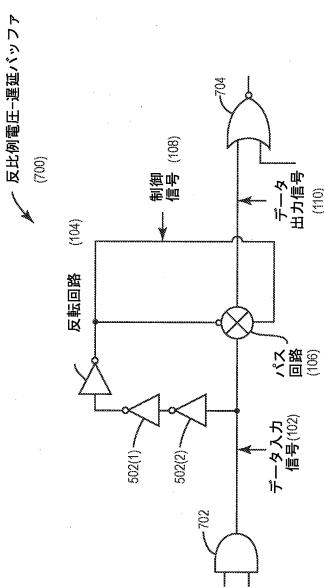

【図7】論理ゲートからデータ入力信号を受信し、別の論理ゲートにデータ出力信号を提供する、別の反比例電圧-遅延バッファの論理図である。

【図8】図1A、図1B、図4、図5、または図7における反比例電圧-遅延バッファを含むことができる例示的なプロセッサベースシステムのブロック図である。

#### 【発明を実施するための形態】

##### 【0012】

ここで図面を参照して、本開示のいくつかの例示的な態様について説明する。「例示的」という語は、本明細書では「一例、事例、または例示としての働きをすること」を意味するために使用される。本明細書で「例示的」と説明する任意の態様は、必ずしも他の態様よりも好みしい、または有利なものと解釈されるべきではない。

10

##### 【0013】

図1Aは、データ入力信号102の電圧レベルに反比例する時間量でデータ入力信号102をバッファリングするように構成された例示的な反比例電圧-遅延バッファ100の回路図である。非限定的な例として、反比例電圧-遅延バッファ100は、より短い遅延でより高い電圧レベルを有するデータ入力信号102を保持するが、より長い遅延でより低い電圧レベルを有するデータ入力信号102を保持することができる。このようにして電圧レベルに反比例する遅延をもたらすために、反比例電圧-遅延バッファ100は、反転回路104とバス回路106とを含む。反転回路104は、データ入力信号102の反転した論理状態を有する制御信号108を生成するように構成される。特に、制御信号108は、データ入力信号102の電圧レベルに比例するレートで遷移する。

20

##### 【0014】

引き続き図1Aを参照すると、バス回路106は、データ入力信号102および制御信号108が同じ論理状態を有するときに、データ入力信号102の弱論理状態を有するデータ出力信号110を生成するように構成される。言い換えれば、バス回路106は、データ入力信号102が別の論理状態に遷移したときに、ただし、制御信号108がデータ入力信号102の反対の論理状態に遷移する前に、弱論理状態を有するデータ出力信号110を生成するように構成される。さらに、バス回路106は、データ入力信号102および制御信号108が反対の論理状態を有するときに、データ入力信号102の強論理状態を有するデータ出力信号110を生成するように構成される。言い換えれば、バス回路106は、データ入力信号102の反転論理状態である制御信号108を生成する時間を反転回路104が有した後に、強論理状態を生成するように構成される。特に、より低い電圧またはより高い電圧のいずれかのデータ入力信号102の強論理状態は、論理経路における次の段階をトリガすることが可能である。

30

##### 【0015】

引き続き図1Aを参照すると、上記で説明したようにデータ出力信号110を生成するためには、バス回路106は、第1のバスデバイス112と第2のバスデバイス114とを含む。第1のバスデバイス112は、データ入力信号102および制御信号108が第1の論理状態を有することに応答して、データ入力信号102の弱論理状態を有するデータ出力信号110を生成するように構成される。逆に、第2のバスデバイス114は、データ入力信号102および制御信号108が第2の論理状態を有することに応答して、弱論理状態を有するデータ出力信号110を生成するように構成され、第2の論理状態は、第1の論理状態の反対である。特に、より低い電圧レベルを有するデータ入力信号102に基づく弱論理状態は、論理経路の次の段階をトリガすることが可能ではない。

40

##### 【0016】

さらに、第1のバスデバイス112は、制御信号108が第1の論理状態を有し、データ入力信号102が第2の論理状態を有することに応答して、データ入力信号102の強論理状態を有するデータ出力信号110を生成するように構成される。第2のバスデバイス114は、制御信号108が第2の論理状態を有し、データ入力信号102が第1の論理状態を有することに

50

応答して、データ入力信号102の強論理状態を有するデータ出力信号110を生成するよう にさらに構成される。重要なことには、より低い電圧またはより高い電圧のいずれかのデータ入力信号102の強論理状態は、論理経路における次の段階をトリガすることが可能である。制御信号108の遷移レートは、データ入力信号102の電圧レベルに比例するので、データ入力信号102は、そのような電圧レベルに従った時間量でバッファリングされる。このようにして、複数の電圧レベルにわたって集積回路(IC)における論理経路のタイミング目標を達成するために、反比例電圧-遅延バッファ100が使用され得る。

#### 【 0 0 1 7 】

引き続き図1Aを参照して、ここで、反比例電圧-遅延バッファ100の例示的な態様について説明する。この例では、第1のバスデバイス112は、p型金属酸化物半導体(PMOS)トランジスタ(本明細書では「PMOSトランジスタ112」とも呼ばれる)を使用する形で用いられる一方、第2のバスデバイス114は、n型金属酸化物半導体(NMOS)トランジスタ(本明細書では「NMOSトランジスタ114」とも呼ばれる)を使用する形で用いられる。PMOSトランジスタ112のソース(S)は、NMOSトランジスタ114のソース(S)に電気的に結合され、各ソース(S)は、データ入力信号102を受信するように構成される。さらに、PMOSトランジスタ112のドレイン(D)は、NMOSトランジスタ114のドレイン(D)に電気的に結合され、各ドレイン(D)は、データ出力信号110を提供するように構成される。PMOSトランジスタ112のゲート(G)およびNMOSトランジスタ114のゲート(G)はそれぞれ、制御信号108を受信するように構成される。特に、このようにPMOSトランジスタ112およびNMOSトランジスタ114を用いるとき、バス回路106は、バスゲート(本明細書では「バスゲート106」とも呼ばれる)としても知られ得る。さらに、この例では、反転回路104は、インバータ(本明細書では「インバータ104」とも呼ばれる)を使用する形で用いられる。インバータ104は、NMOSトランジスタ118に電気的に結合されたPMOSトランジスタ116を含む。さらなる説明をもたらすために、図1Bは、バスゲートを使用するバス回路106とインバータを使用する反転回路104とを含む、この例での反比例電圧-遅延バッファ100の論理図を示す。

#### 【 0 0 1 8 】

以下により詳細に説明するように、反比例電圧-遅延バッファ100は、バス回路106のPMOSトランジスタ112およびNMOSトランジスタ114のデバイス物理的特性によって引き起こされた弱および強の論理状態を利用する。このようにして、PMOSトランジスタ112がアクティブ化されたとき、PMOSトランジスタ112は、論理高「1」状態がソース(S)に提供されたときにドレイン(D)上に強論理高「1」状態を生成し、論理低「0」状態がソース(S)に提供されたときにドレイン(D)上に弱論理低「0」状態を生成するように構成される。非限定的な例として、PMOSトランジスタ112は、-0.2ボルト(V)に等しいしきい値電圧( $V_T$ )を有する。PMOSトランジスタ112のソース(S)に0Vが提供された場合、ゲート(G)がアクティブ化されると、PMOSトランジスタ112は、弱論理低「0」状態である0.2V(たとえば、 $0V+0.2V=0.2V$ )に等しいドレイン電圧( $V_D$ )を生成する。PMOSトランジスタ112のソース(S)に1.0Vが提供された場合、ゲート(G)がアクティブ化されると、PMOSトランジスタ112は、強論理高「1」状態である1.0Vに等しい $V_D$ を生成する。

#### 【 0 0 1 9 】

さらに、NMOSトランジスタ114がアクティブ化されたとき、NMOSトランジスタ114は、論理低「0」状態がソース(S)に提供されたときにドレイン(D)上に強論理低「0」状態を生成し、論理高「1」状態がソース(S)に提供されたときにドレイン(D)上に弱論理高「1」状態を生成するように構成される。非限定的な例として、NMOSトランジスタ114は、0.2Vに等しい $V_T$ を有する。NMOSトランジスタ114のソース(S)に1.0Vが提供された場合、ゲート(G)がアクティブ化されると、NMOSトランジスタ114は、弱論理高「1」状態である0.8V(たとえば、 $1.0V-0.2V=0.8V$ )に等しい電圧 $V_D$ を生成する。NMOSトランジスタ114のソース(S)に0Vが提供された場合、ゲート(G)がアクティブ化されると、NMOSトランジスタ114は、強論理低「0」状態である0Vに等しい $V_D$ を生成する。

#### 【 0 0 2 0 】

10

20

30

40

50

この点について、図2は、データ入力信号102の遷移に応答した、図1Aにおける反比例電圧-遅延バッファ100の信号の例示的なタイミングを示すタイミング図200を提供する。この例では、第1の論理状態は論理低「0」状態に相当し、第2の論理状態は論理高「1」状態に相当する。さらに、この例では、NMOSトランジスタ114の $V_T$ は0.2Vであると仮定される一方、PMOSトランジスタ112の $V_T$ は-0.2Vであると仮定される。また、より高い電圧レベルでのデータ入力信号102は1.0Vであると仮定される一方、より低い電圧レベルでのデータ入力信号102は0.3Vであると仮定される。

### 【0021】

引き続き図2を参照すると、時間 $t_0$ において、データ入力信号102およびデータ出力信号110は両方とも論理低「0」状態を有する一方、制御信号108は論理高「1」状態を有する。したがって、時間 $t_0$ において、NMOSトランジスタ114は、制御信号108の論理高「1」状態によってアクティブ化され、その結果、パスゲート106が、データ入力信号102(たとえば、0V)の強論理低「0」状態を有するデータ出力信号110を生成する。時間 $t_1$ において、データ入力信号102は論理高「1」状態に遷移する(矢印202)。制御信号108は、時間 $t_2$ において論理高「1」状態を有するので、NMOSトランジスタ114は、アクティブ化されたままであり、したがって、NMOSトランジスタ114は、時間 $t_2$ においてデータ入力信号102の弱論理高「1」状態を有するデータ出力信号110を生成する(矢印204)。たとえば、データ入力信号102がより高い電圧レベルの1.0Vを有する場合、データ出力信号110は、時間 $t_2$ において0.8V(たとえば、 $1.0V - 0.2V = 0.8V$ )に等しい弱論理高「1」状態を有する。特に、0.8Vに等しい弱論理高「1」状態は、データ出力信号110が論理経路における次の段階をトリガすることを可能にするほど十分に高いことがある。他方では、データ入力信号102がより低い電圧レベルの0.3Vを有する場合、データ出力信号110は、時間 $t_2$ において0.1V(たとえば、 $0.3V - 0.2V = 0.1V$ )に等しい弱論理高「1」状態を有し、この状態は、データ出力信号110が論理経路の次の段階をトリガすることを可能にするほど十分に高くはない。

### 【0022】

引き続き図2を参照すると、時間 $t_3$ において、インバータ104は、データ入力信号102が論理高「1」状態を有することに応答して、論理低「0」状態を有する制御信号108を生成する(矢印206)。特に、制御信号108の遷移レートは、データ入力信号102の電圧レベルに比例するので、時間 $t_1$ におけるデータ入力信号102の遷移から時間 $t_3$ における制御信号108の遷移までの遅延208は、データ入力信号102の電圧レベルに反比例する。言い換えるれば、データ入力信号102のより高い電圧レベルは、インバータ104のより速い切り替えに起因してより短い持続時間を有する遅延208をもたらす一方、データ入力信号102のより低い電圧レベルは、インバータ104のより遅い切り替えに起因してより長い持続時間を有する遅延208をもたらす。さらに、時間 $t_3$ における制御信号108の論理低「0」状態は、PMOSトランジスタ112をアクティブ化し、NMOSトランジスタ114を非アクティブ化する。PMOSトランジスタ112のアクティブ化に応答して、時間 $t_4$ においてデータ入力信号102の強論理高「1」状態を有するデータ出力信号110が生成される(矢印210)。たとえば、データ入力信号102がより高い電圧レベルの1.0Vを有する場合、データ出力信号110は、時間 $t_4$ において1.0Vに等しい強論理高「1」状態を有する。他方では、データ入力信号102がより低い電圧レベルの0.3Vを有する場合、データ出力信号110は、時間 $t_4$ において0.3Vに等しい強論理高「1」状態を有する。特に、1.0Vまたは0.3Vのいずれかの強論理高「1」状態は、データ出力信号110が論理経路における次の段階をトリガすることを可能にするほど十分に高い。

### 【0023】

したがって、図2に関して上述した例によって示されるように、図1Aにおける反比例電圧-遅延バッファ100は、データ入力信号102の電圧レベルに反比例する時間量でデータ入力信号102をバッファリングのように構成される。たとえば、データ入力信号102がより低い電圧レベルを有する場合、時間 $t_2$ におけるデータ出力信号110の弱論理高「1」状態は、論理経路の次の段階をトリガするほど十分に高くはない。だが、データ入力信号102が

10

20

30

40

50

より低い電圧レベルを有するとき、データ出力信号110が時間 $t_4$ において強論理高「1」状態に達すると、データ出力信号110は、論理経路の次の段階をトリガするほど十分に高い。データ入力信号102のより低い電圧レベルにより、遅延208は、より長い持続時間を有することになるので、データ出力信号110は、データ入力信号102のより低い電圧レベルに起因して、強論理高「1」状態に達するのが遅延する。逆に、データ入力信号102がより高い電圧レベルを有する場合、時間 $t_2$ におけるデータ出力信号110の弱論理高「1」状態は、論理経路の次の段階をトリガするほど十分に高いことがある。ただし、データ出力信号110の弱論理高「1」状態が時間 $t_2$ において十分に高くはない場合でも、データ出力信号110が時間 $t_4$ において強論理高「1」状態に達すると、データ出力信号110は、論理経路の次の段階をトリガするほど十分に高い。さらに、データ入力信号102のより高い電圧レベルにより、遅延208は、より短い持続時間を有することになるので、データ出力信号110は、データ入力信号102がより低い電圧レベルを有するときと比較して、より迅速に強論理高「1」状態に達する。したがって、複数の電圧レベルにわたってICにおける論理経路のタイミング目標を達成するために、図1Aにおける反比例電圧-遅延バッファ100が使用され得る。

#### 【0024】

引き続き図2を参照して、ここで、図1Aにおける反比例電圧-遅延バッファ100の、データ入力信号102の立ち下がり遷移中の例示的な信号のタイミングについて説明する。この点について、時間 $t_5$ において、データ入力信号102は論理低「0」状態に遷移する(矢印212)。制御信号108は、時間 $t_6$ において論理低「0」状態を有するので、PMOSトランジスタ112は、アクティブ化されたままであり、したがって、時間 $t_6$ においてデータ入力信号102の弱論理低「0」状態を有するデータ出力信号110が生成される(矢印214)。たとえば、前述したようにPMOSトランジスタ112のデバイス物理的特性のために、データ出力信号110は、時間 $t_6$ において0.2V(たとえば、0V+0.2V=0.2V)に等しい弱論理低「0」状態を有する。さらに、時間 $t_7$ において、インバータ104は、データ入力信号102が論理低「0」状態を有することに応答して、論理高「1」状態を有する制御信号108を生成する(矢印216)。時間 $t_5$ におけるデータ入力信号102の遷移から時間 $t_7$ における制御信号108の遷移までの時間は、本明細書では遅延218として説明される。制御信号108の論理高「1」状態は、NMOSトランジスタ114をアクティブ化し、PMOSトランジスタ112を非アクティブ化する。NMOSトランジスタ114のアクティブ化に応答して、時間 $t_8$ においてデータ入力信号102の強論理低「0」状態を有するデータ出力信号110が生成される(矢印220)。

#### 【0025】

この点について、図3は、データ入力信号102の電圧レベルに反比例する時間量でデータ入力信号102をバッファリングするために、図1Aにおける反比例電圧-遅延バッファ100によって用いられる例示的なプロセス300を示す。プロセス300は、データ入力信号102の反転した論理状態を有する制御信号108を生成すること(ブロック302)を含む。特に、制御信号108の遷移レートは、データ入力信号102の電圧レベルに比例する。プロセス300はまた、データ入力信号102および制御信号108が第1の論理状態を有することに応答して、データ入力信号102の弱論理状態を有するデータ出力信号110を生成すること(ブロック304)を含む。さらに、プロセス300は、制御信号108が第1の論理状態を有し、データ入力信号102が第2の論理状態を有することに応答して、データ入力信号102の強論理状態を有するデータ出力信号110を生成すること(ブロック306)を含む。上述のように、第2の論理状態は、第1の論理状態の反対である。プロセス300はまた、データ入力信号102および制御信号108が第2の論理状態を有することに応答して、データ入力信号102の弱論理状態を有するデータ出力信号110を生成すること(ブロック308)を含む。さらに、プロセス300は、制御信号108が第2の論理状態を有し、データ入力信号102が第1の論理状態を有することに応答して、データ入力信号102の強論理状態を有するデータ出力信号110を生成すること(ブロック310)を含む。プロセス300を用いることによって、複数の電圧レベルにわたってICにおける論理経路のタイミング目標を達成するために、図1Aにおける反比例電圧-遅延バッファ100が使用され得る。

10

20

30

40

50

### 【 0 0 2 6 】

上述のように、図1Aにおける反比例電圧-遅延バッファ100の事例は、タイミング目標を達成するためにICの様々な論理経路に配設され得る。しかしながら、図1Aにおける反比例電圧-遅延バッファ100の事例が配設される特定の論理経路の物理的力学は、反比例電圧-遅延バッファ100に提供されるか、または反比例電圧-遅延バッファ100から受信されるデータの電圧レベルに影響を与える。このように、図4は、駆動強度目的で入力インバータ402および出力インバータ404を含む例示的な反比例電圧-遅延バッファ400の論理図である。反比例電圧-遅延バッファ400は、図1Aにおける反比例電圧-遅延バッファ100と共にいくつかの構成要素を含み、それらは、図1Aと図4との間で共通する要素番号で示されているので、本明細書では再度説明しない。この例では、入力インバータ402は、論理経路からデータを受信し、データ入力信号102を生成するように構成される。さらに、入力インバータ402が反転回路104およびバス回路106にデータ入力信号102を提供するように、入力インバータ402は反転回路104およびバス回路106に電気的に結合される。出力インバータ404は、バス回路106に電気的に結合され、データ出力信号110を受信し、論理経路のためのデータを生成するように構成される。このようにして、入力インバータ402および出力インバータ404は、反比例電圧-遅延バッファ400に提供され、反比例電圧-遅延バッファ400から受信されるデータの駆動強度を増大させる。

### 【 0 0 2 7 】

さらに、より低い電圧レベルでいくつかの論理経路のタイミング目標をより容易に達成するために、図2を参照して上述した遅延208の持続時間に対する追加の制御を行うことが有益であり得る。この点について、図5は、特にデータ入力信号102のより低い電圧レベルで遅延を増大させるように構成された追加のインバータ502(1)、502(2)を含む例示的な反比例電圧-遅延バッファ500の論理図である。反比例電圧-遅延バッファ500は、図4における反比例電圧-遅延バッファ400と共にいくつかの構成要素を含み、それらは、図4と図5との間で共通する要素番号で示されているので、本明細書では再度説明しない。この例では、インバータ502(1)、502(2)は直列に接続されており、反転回路104にデータ入力信号102を提供するように構成される。インバータ502(1)、502(2)の切り替え速度は、より低い電圧レベルではより遅く、より高い電圧レベルではより速いので、インバータ502(1)、502(2)は、特にデータ入力信号102のより低い電圧レベルで遅延を増大させ得る。さらに、この態様では、インバータ502(1)、502(2)は、反転回路104内に配設される。ただし、他の態様は、反転回路104とは別個にインバータ502(1)、502(2)を実装し得る。特に、本明細書で説明する態様では、任意の偶数(N)個のインバータ502(1)～502(N)が使用され得、その結果、インバータ502(1)～502(N)に起因する遅延の増大が、用いられるインバータ502(1)～502(N)の数に基づいてより細かく制御され得る。したがって、インバータ502(1)～502(N)およびインバータ104を含む態様は、全般的に反転回路104およびインバータ502(1)～502(N)の関連する遅延のための奇数(P)個のインバータを有する。

### 【 0 0 2 8 】

この点について、図6は、データ入力信号102の遷移に応答した、図5における反比例電圧-遅延バッファ500の信号の例示的なタイミングを示すタイミング図600を提供する。タイミング図600は、図2におけるタイミング図200と共にいくつかの遷移を含み、それらは、図2と図6との間で共通する要素番号で示されているので、本明細書では再度説明しない。このようにして、図5の反比例電圧-遅延バッファ500におけるインバータ502(1)、502(2)の切り替え速度は、時間t<sub>1</sub>における論理高「1」状態へのデータ入力信号102の遷移から時間t<sub>3</sub>における論理低「0」状態への制御信号108の遷移の間の時間を増大させる。言い換れば、インバータ502(1)、502(2)は、上述の遷移間の遅延208'を生じさせる。特に、遅延208'は、インバータ502(1)、502(2)によって追加された増大した遅延に起因して、図2におけるタイミング図200で説明した遅延208よりも長い持続時間有する。同様に、インバータ502(1)、502(2)は、遅延218'が図2における遅延218よりも長い持続時間有するように、時間t<sub>5</sub>における論理低「0」状態へのデータ入力信号102の

10

20

30

40

50

遷移から時間 $t_7$ における論理高「1」状態への制御信号108の遷移の間の時間を増大させる。したがって、インバータ502(1)、502(2)は、特に図5の反比例電圧-遅延バッファ500におけるデータ入力信号102のより低い電圧レベルで遅延を増大させるために使用され得る。

#### 【0029】

特に、それぞれ図1、図4、または図5における反比例電圧-遅延バッファ100、400、または500などの反比例電圧-遅延バッファの事例が配設される特定の論理経路の回路の詳細は、様々な論理経路の間で大きく異なり得る。このように、図7は、論理ゲート702(たとえば、ANDベースゲート702)および論理ゲート704(たとえば、NORベースゲート704)を含む例示的な反比例電圧-遅延バッファ700の論理図である。反比例電圧-遅延バッファ700は、図5における反比例電圧-遅延バッファ500と共に通するいくつかの構成要素を含み、それらは、図5と図7との間で共通する要素番号で示されているので、本明細書では再度説明しない。この例では、論理ゲート702は、論理経路からデータを受信し、データ入力信号102を生成するように構成される。さらに、論理ゲート702が反転回路104およびバス回路106にデータ入力信号102を提供するように、論理ゲート702は反転回路104およびバス回路106に電気的に結合される。論理ゲート704は、バス回路106に電気的に結合され、データ出力信号110を受信し、論理経路のためのデータを生成するように構成される。このように、論理ゲート702および論理ゲート704は、反比例電圧-遅延バッファ700がデータ入力信号102を受信し得るか、または反比例電圧-遅延バッファ700がデータ出力信号110を提供し得る、例示的な回路要素を表す。

10

#### 【0030】

さらに、本明細書で説明する要素は、特定の機能を実行するための手段と呼ばれることがある。この点について、反転回路104は、本明細書では、データ入力信号102の反転した論理状態を有する制御信号108を生成するための手段と呼ばれることがある。第1のバスデバイス112は、本明細書では、データ入力信号102および制御信号108が第1の論理状態を有することに応答して、データ入力信号102の弱論理状態を有するデータ出力信号110を生成するための手段と呼ばれることがある。第1のバスデバイス112はまた、本明細書では、制御信号108が第1の論理状態を有し、データ入力信号102が第2の論理状態を有することに応答して、データ入力信号102の強論理状態を有するデータ出力信号110を生成するための手段と呼ばれることがある。第2のバスデバイス114は、本明細書では、データ入力信号102および制御信号108が第2の論理状態を有することに応答して、データ入力信号102の弱論理状態を有するデータ出力信号110を生成するための手段と呼ばれることがある。第2のバスデバイス114はまた、本明細書では、制御信号108が第2の論理状態を有し、データ入力信号102が第1の論理状態を有することに応答して、データ入力信号102の強論理状態を有するデータ出力信号110を生成するための手段と呼ばれることがある。さらに、図5におけるインバータ502(1)、502(2)は、本明細書では、データ入力信号102に基づいて制御信号108を生成するための手段を遅延させるための手段と呼ばれることがある。

20

#### 【0031】

本明細書で開示する態様による、データ電圧レベルに従ってデータをバッファリングするための反比例電圧-遅延バッファは、任意のプロセッサベースデバイスに設けられるか、または任意のプロセッサベースデバイスに組み込まれ得る。例としては、限定ではないが、セットトップボックス、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、固定ロケーションデータユニット、モバイルロケーションデータユニット、携帯電話、セルラーフォン、スマートフォン、タブレット、ファブレット、コンピュータ、ポータブルコンピュータ、デスクトップコンピュータ、携帯情報端末(PDA)、モニタ、コンピュータモニタ、テレビ、チューナ、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、ポータブル音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビデオディスク(DVD)プレーヤ、ポータブルデジタルビデオプレーヤおよび自動車が含まれる。

30

40

50

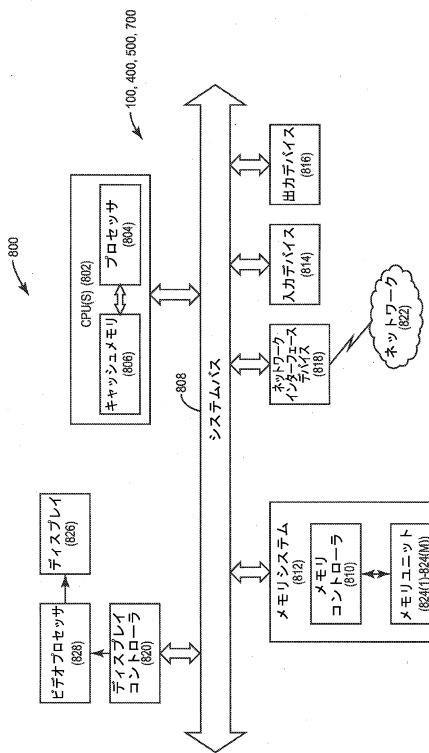

**【 0 0 3 2 】**

この点において、図8は、プロセッサベースシステム800の一例を示す。特に、プロセッサベースシステム800に関して本明細書で説明する任意の要素は、図1A、図1B、図4、図5、および図7に示す反比例電圧-遅延バッファ100、400、500、および700のいずれかを含むことができる。この例では、プロセッサベースシステム800は、各々が1つまたは複数のプロセッサ804を含む、1つまたは複数の中央処理装置(CPU)802を含む。CPU802は、一時的に記憶されているデータに迅速にアクセスするために、プロセッサ804に結合されたキャッシュメモリ806を有し得る。CPU802は、システムバス808に結合され、プロセッサベースシステム800に含まれるマスタデバイスとスレーブデバイスとを相互結合することができる。よく知られているように、CPU802は、システムバス808を介してアドレス情報、制御情報、およびデータ情報を交換することによって、これらの他のデバイスと通信する。たとえば、CPU802は、スレーブデバイスの一例として、メモリコントローラ810にバストランザクション要求を通信することができる。図8には示されていないが、複数のシステムバス808が設けられてよく、各システムバス808は異なるファブリックを構成する。

**【 0 0 3 3 】**

他のマスタデバイスおよびスレーブデバイスがシステムバス808に接続されてもよい。図8に示すように、これらのデバイスは、例として、メモリシステム812と、1つまたは複数の入力デバイス814と、1つまたは複数の出力デバイス816と、1つまたは複数のネットワークインターフェースデバイス818と、1つまたは複数のディスプレイコントローラ820とを含むことができる。入力デバイス814は、限定はしないが、入力キー、スイッチ、音声プロセッサなどを含む、任意のタイプの入力デバイスを含むことができる。出力デバイス816は、限定はしないが、オーディオ、ビデオ、他の視覚的インジケータなどを含む、任意のタイプの出力デバイスを含むことができる。ネットワークインターフェースデバイス818は、ネットワーク822との間のデータの交換を可能にするように構成された、任意のデバイスとすることができます。ネットワーク822は、限定はしないが、有線ネットワークもしくはワイヤレスネットワーク、プライベートネットワークもしくは公衆ネットワーク、ローカルエリアネットワーク(LAN)、ワイヤレスローカルエリアネットワーク(WLAN)、ワイドエリアネットワーク(WAN)、BLUETOOTH(登録商標)ネットワーク、またはインターネットを含む、任意のタイプのネットワークとすることができます。ネットワークインターフェースデバイス818は、所望の任意のタイプの通信プロトコルをサポートするように構成され得る。メモリシステム812は、1つまたは複数のメモリユニット824(1)~824(M)を含むことができる。

**【 0 0 3 4 】**

CPU802はまた、1つまたは複数のディスプレイ826に送られる情報を制御するために、システムバス808を介してディスプレイコントローラ820にアクセスするように構成され得る。ディスプレイコントローラ820は、1つまたは複数のビデオプロセッサ828を介して、表示されるべき情報をディスプレイ826に送り、1つまたは複数のビデオプロセッサ828は、表示されるべき情報を処理してディスプレイ826にとって適したフォーマットにする。ディスプレイ826は、限定はしないが、陰極線管(CRT)、液晶ディスプレイ(LCD)、プラズマディスプレイ、発光ダイオード(LED)ディスプレイなどを含む、任意のタイプのディスプレイを含むことができる。

**【 0 0 3 5 】**

本明細書で開示する態様に関して説明した様々な例示的な論理ブロック、モジュール、回路、およびアルゴリズムが、電子ハードウェア、メモリの中もしくは別のコンピュータ可読媒体の中に記憶されるとともにプロセッサもしくは他の処理デバイスによって実行される命令、または両方の組合せとして実装され得ることを、当業者はさらに諒解されよう。本明細書で説明するマスタデバイスおよびスレーブデバイスは、例として、任意の回路、ハードウェア構成要素、集積回路(IC)、またはICチップにおいて用いられてもよい。本明細書で開示するメモリは、任意のタイプおよびサイズのメモリであってもよく、所望の

任意のタイプの情報を記憶するように構成されてもよい。この互換性を明確に示すために、上記では、様々な例示的な構成要素、ブロック、モジュール、回路、およびステップは、概してそれらの機能に関して説明してきた。そのような機能がどのように実装されるかは、特定の用途、設計選択、および/またはシステム全体に課される設計制約によって決まる。当業者は、説明した機能を特定の用途ごとに様々な方法で実装し得るが、そのような実装決定は、本開示の範囲からの逸脱を引き起こすものと解釈されるべきではない。

#### 【 0 0 3 6 】

本明細書で開示する態様に関して説明した様々な例示的な論理ブロック、モジュール、および回路は、プロセッサ、デジタル信号プロセッサ(DSP)、特定用途向け集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)もしくは他のプログラマブル論理デバイス、個別ゲートもしくはトランジスタ論理、個別ハードウェア構成要素、または本明細書で説明した機能を実行するように設計されたそれらの任意の組合せを用いて実装または実行され得る。プロセッサは、マイクロプロセッサであってよいが、代替として、プロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラ、またはストレーミングマシンであってよい。プロセッサはまた、コンピューティングデバイスの組合せ(たとえば、DSPとマイクロプロセッサの組合せ、複数のマイクロプロセッサ、DSPコアと連携した1つもしくは複数のマイクロプロセッサ、または任意の他のそのような構成)として実装されてもよい。

10

#### 【 0 0 3 7 】

本明細書で開示する態様は、ハードウェアにおいて、かつハードウェアに記憶される命令において具現化されてよく、たとえば、ランダムアクセスメモリ(RAM)、フラッシュメモリ、読み取り専用メモリ(ROM)、電気的プログラマブルROM(EPROM)、電気的消去可能プログラマブルROM(EEPROM)、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野で知られている任意の他の形態のコンピュータ可読媒体の中には存在してよい。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取り記憶媒体に情報を書き込むことができるようプロセッサに結合される。代替として、記憶媒体は、プロセッサは、プロセッサと一体であってよい。プロセッサおよび記憶媒体はASICの中に存在してよい。ASICはリモート局の中に存在してよい。代替として、プロセッサおよび記憶媒体は、個別構成要素としてリモート局、基地局、またはサーバの中に存在してよい。

20

#### 【 0 0 3 8 】

本明細書の例示的な態様のいずれかにおいて説明した動作ステップが、例および説明を提供するために記載されていることにも留意されたい。説明した動作は、図示した順序以外の数多くの異なる順序で実行されてよい。さらに、単一の動作ステップにおいて説明した動作は、実際にはいくつかの異なるステップにおいて実行されてよい。追加として、例示的な態様で説明した1つまたは複数の動作ステップは組み合わせられてよい。当業者にとって容易に明らかであるように、フローチャート図に示す動作ステップが数多くの異なる修正を受けてよいことを理解されたい。情報および信号が様々な異なる技術および技法のいずれかを使用して表され得ることも、当業者は理解されよう。たとえば、上記の説明全体にわたって参照され得るデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁場もしくは磁気粒子、光場もしくは光学粒子、またはそれらの任意の組合せによって表されてよい。

30

#### 【 0 0 3 9 】

本開示の前述の説明は、いかなる当業者も本開示を作製または使用することが可能になるように提供される。本開示の様々な修正が、当業者に明らかになり、本明細書で規定する一般原理は、本開示の趣旨または範囲から逸脱することなく他の変形形態に適用され得る。したがって、本開示は、本明細書で説明した例および設計に限定されるものではなく、本明細書で開示する原理および新規の特徴と一致する最も広い範囲が与えられるべきである。

40

#### 【 符号の説明 】

50

## 【0040】

|               |                      |    |

|---------------|----------------------|----|

| 100           | 反比例電圧-遅延バッファ         |    |

| 102           | データ入力信号              |    |

| 104           | 反転回路、インバータ           |    |

| 106           | バス回路、バスゲート           |    |

| 108           | 制御信号                 |    |

| 110           | データ出力信号              |    |

| 112           | 第1のバスデバイス、PMOSトランジスタ |    |

| 114           | 第2のバスデバイス、NMOSトランジスタ |    |

| 116           | PMOSトランジスタ           | 10 |

| 118           | NMOSトランジスタ           |    |

| 200           | タイミング図               |    |

| 208           | 遅延                   |    |

| 208'          | 遅延                   |    |

| 218           | 遅延                   |    |

| 218'          | 遅延                   |    |

| 300           | プロセス                 |    |

| 400           | 反比例電圧-遅延バッファ         |    |

| 402           | 入力インバータ              |    |

| 404           | 出力インバータ              | 20 |

| 500           | 反比例電圧-遅延バッファ         |    |

| 502(1)        | インバータ                |    |

| 502(2)        | インバータ                |    |

| 502(N)        | インバータ                |    |

| 600           | タイミング図               |    |

| 700           | 反比例電圧-遅延バッファ         |    |

| 702           | 論理ゲート、ANDベースゲート      |    |

| 704           | 論理ゲート、NORベースゲート      |    |

| 800           | プロセッサベースシステム         |    |

| 802           | 中央処理装置(CPU)          | 30 |

| 804           | プロセッサ                |    |

| 806           | キャッシュメモリ             |    |

| 808           | システムバス               |    |

| 810           | メモリコントローラ            |    |

| 812           | メモリシステム              |    |

| 814           | 入力デバイス               |    |

| 816           | 出力デバイス               |    |

| 818           | ネットワークインターフェースデバイス   |    |

| 820           | ディスプレイコントローラ         |    |

| 822           | ネットワーク               | 40 |

| 824(1)~824(M) | メモリユニット              |    |

| 826           | ディスプレイ               |    |

| 828           | ビデオプロセッサ             |    |

【図面】

【図 1 A】

【図 1 B】

10

【図 2】

【図 3】

20

30

40

50

【図 4】

【図 5】

10

【図 6】

【図 7】

20

30

40

50

【図 8】

10

20

30

40

50

---

フロントページの続き

審判官 衣鳩 文彦

審判官 角田 慎治

(56)参考文献 特開昭61-53820(JP,A)

特開平5-191232(JP,A)

(58)調査した分野 (Int.Cl., DB名)

H03K 5/13