(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 600 12 957 T2 2005.08.25

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 221 262 B1

(51) Int Cl.<sup>7</sup>: H04N 9/66

(21) Deutsches Aktenzeichen: 600 12 957.8

(86) PCT-Aktenzeichen: PCT/US00/28059

(96) Europäisches Aktenzeichen: 00 973 454.2

(87) PCT-Veröffentlichungs-Nr.: WO 01/028255

(86) PCT-Anmeldetag: 11.10.2000

(87) Veröffentlichungstag

der PCT-Anmeldung: 19.04.2001

(97) Erstveröffentlichung durch das EPA: 10.07.2002

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 11.08.2004

(47) Veröffentlichungstag im Patentblatt: 25.08.2005

(30) Unionspriorität:

159149 P 13.10.1999 US

(84) Benannte Vertragsstaaten:

DE, ES, FR, GB, IT

(73) Patentinhaber:

Thomson Licensing S.A., Boulogne, Cedex, FR

(72) Erfinder:

CARLSGAARD, Stephen, Eric, Zionsville, US;

RUMREICH, Francis, Mark, Indianapolis, US;

STEWART, Sidney, John, Indianapolis, US

(74) Vertreter:

Roßmanith, M., Dipl.-Phys. Dr.rer.nat., Pat.-Anw.,

30457 Hannover

(54) Bezeichnung: Parallele Digitalisierung und Verarbeitung mehrerer analoger Fernsehsignale

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

**[0001]** Die vorliegende Erfindung betrifft Geräte zur Verarbeitung von analogen und/oder digitalen Signalen und insbesondere integrierte Schaltungen, die mehrere Taktfrequenzen für die Digitalisierung und die Verarbeitung von verschiedenen analogen und/oder digitalen Signalen benutzen.

**[0002]** Integrierte Schaltungen, oder ICs, werden in allen Arten von elektronischen Geräten in großem Umfang benutzt. Da diese elektronischen Geräte komplexer werden, nimmt die Anzahl von ICs, die zur Durchführung aller benötigten Funktionen notwendig sind, zu, und/oder es werden die Funktionen mehrerer ICs in einem einzigen IC kombiniert. Selbst wenn mehrere Funktionen in einem einzigen IC enthalten sind, ist es erwünscht, die interne Komplexität des IC zu verringern.

**[0003]** Derzeitige Fernsehgeräte benutzen viele verschiedene ICs für die Verarbeitung von analogen und digitalen Fernsehsignalen von verschiedenen terrestrischen und nicht-terrestrischen Quellen. Von der nächsten Generation von digitalen/analogen Fernsehgeräten wird jedoch erwartet, dass sie höhere Werte der Integration als derzeitige Fernsehgeräte aufweisen. Höhere Werte der Integration führen zu weniger ICs, wobei die durch mehrere einzelne ICs durchgeführten Vorgänge in einem IC kombiniert sind. Jedoch gibt es einige Hindernisse auf dem Weg zu einer Kombination der Signalverarbeitung von analogen Fernsehsignalempfängern, mit derjenigen, die für digitale Fernsehsignale benötigt wird.

**[0004]** Ein Problem bei der Integration von ICs für die Verarbeitung von analogen und digitalen Fernsehsignalen besteht darin, dass für verschiedene Videoquellen (analog und digital) Analog/Digital (A/D)-Wandler benötigt werden, die bei verschiedenen Abtastraten arbeiten. Analoge Fernsehsignale beruhen auf zeilenverkoppelten oder Farbunterträgerverkoppelten Frequenzen, während digital modulierte (digitale) Fernsehsignale auf ihren eigenen Symbolraten basieren. Ebenso erzeugt die derzeitige A/D-Technologie ein digitales Übersprechen, das die A/D-Leistungsfähigkeit nachteilig beeinträchtigt, wenn asynchrone Takte vorliegen.

**[0005]** Es ist bekannt, separate digitale Demodulatoren anzuwenden, die eine digitale Interpolation für einen sogenannten "offfrequency"-Betrieb anwenden. Ebenso kann die Verarbeitung eines zweiten Kanals für analoge Signale mit einer asynchronen Abtastfrequenz durchgeführt werden. In dem letzten Fall ist jedoch der Hauptkanal auf einen Parameter der ankommenden analogen Fernsehsignals verriegelt, wie auf Horizontalsynchronimpulse oder einen color burst (Farbsynchronsignal).

**[0006]** Die WO-A-98/46027 zeigt ein Mehrnormen-Farbdecodersystem, das einen externen asynchronen Quarztakt zur Demodulation aller Varianten des PAL/NTSC-Farbsystems enthält, ohne Digitalisierung des analogen Chrominanzsignals. In einem beschriebenen Verfahren zur Demodulation eines analogen Chrominanzsignals werden digitale Quadratursignale für die Demodulation des analogen Chrominanzsignals benutzt, um analoge demodulierte Farbdifferenzsignale zu gewinnen. Ein digitales Phasenfehlersignal wird aus wenigstens einem der analogen demodulierten Farbdifferenzsignale gebildet. Das digitale Phasenfehlersignal wird digital gefiltert, um ein Phasensteuersignal für die Erzeugung der digitalen Quadratursignale zu gewinnen.

**[0007]** Die US-A-5 367 337 zeigt eine Vorrichtung und ein Verfahren zum Empfang und zur asynchronen Abtastung eines ankommenden Videobildsignals und dann zur Verarbeitung des Signals zur Rückgewinnung des Videobildes, einschließlich des Videoformats, für die Umsetzung auf ein vorgewähltes Videoformat. Die Patentschrift zeigt eine asynchrone Abtastung und Digitalisierung des Eingangssignals zur Wiedergewinnung der Frequenz des Eingangssignals und zur Bestimmung der Videosignal-Taktrate über einen Vorgang zur Kontrastoptimierung. Das Signal wird dann unter Verwendung des resultierenden Videosignals und der abgeleiteten Parameter in ein gewünschtes Format umgesetzt. Hierzu enthält die Vorrichtung gemäß des Patents seinen stabilen Quarzoszillator, der ein Ausgangssignal liefert, welches einem Frequenzteiler zugeführt wird, wobei das Ausgangssignal des Oszillators und des Frequenzteilers einem Multiplexer für eine selektive Zuführung zu einem A/D-Wandler zugeführt werden. Eine Überabtastung wird in der Verarbeitung zur Detektierung der Signalformate angewendet.

**[0008]** Die US-A-5 808 691 beschreibt eine Vorrichtung für die Synthesierung eines periodischen digitalen Signals mit einer Frequenz, die durch die Frequenz eines periodischen Referenzsignals vorgegeben ist, das asynchron ist zu einem Abtasttakt des periodischen digitalen Signals. In einer bevorzugten Ausführungsform synthetisiert ein digitales Videosystem einen digitalen Farbunterträger, der auf eine Referenzfrequenz eines Quarzoszillators synchronisiert ist, die asynchron ist zu einem digitalen Systemtakt für das digitale Videosystem.

**[0009]** Die vorliegende Erfindung, die in den Anträgen 1 und 3 angegeben ist, betrifft ein einzelnes System-IC, das gleichzeitig die Digitalisierung und die Verarbeitung von mehreren analogen und/oder digitalen Signalen durchführt, unter Verwendung einer gemeinsamen Frequenzquelle, die nicht auf einen Parameter des ankommenden Signals verriegelt ist. Dadurch kann eine hohe Leistungsfähigkeit der Abtastung und der Verarbeitung aller ankommenden

Signale erreicht werden.

**[0010]** Die vorliegende Erfindung liefert eine übliche analoge Videodecodierung für zwei Kanäle mit einer einzigen Referenzfrequenz (Referenztakt), der mit keinem System verriegelt ist. Das heißt, der Referenztakt beruht nicht auf oder ist nicht verkoppelt mit einer verriegelbaren Eigenschaft eines der Eingangssignale. Zwei digitale Signalprozessoren, für Satelliten- und terrestrische Fernsehsignale, werden modifiziert zur Durchführung der Verarbeitung mit derselben Referenzfrequenz. Die vorliegende Erfindung ermöglicht einen Betrieb mit synchroner Frequenz aller A/Ds und digitaler Signalprozessoren der mehreren Kanäle, um eine fehlerhafte Abtastung und Verarbeitung des ankommenden Signals zu verhindern.

**[0011]** In einer Form der Erfindung wird ein einziger Referenztakt einer bestimmten Frequenz zu einem Taktgenerator zugeführt, der alle Betriebsfrequenzen (Taktsignale) erzeugt, die für die A/D-Konverter und die Decodier-Schaltung/Logik auf dem IC benötigt werden. Der Referenztakt ist unabhängig, d.h. nicht mit einer Synchronisierungseigenschaft der Eingangssignale verkoppelt.

**[0012]** Da es nur einen Referenztakt gibt, aus dem alle anderen Abtast- und Verarbeitungsfrequenzen erzeugt werden, können die A/Ds mit hoher Leistungsfähigkeit arbeiten, bis zu einer Genauigkeit von 10 Bit, mit einem geringen oder keinem digitalen Rauschen. Das ist im allgemeinen mit asynchronen Abtastfrequenzen nicht möglich, weil keine "stillen Bereiche" bestehen, die für die Abtastung des analogen Eingangs benötigt werden. Jedoch werden mit den mehreren Abtastfrequenzen basierend auf einem Signalreferenztakt (Frequenz) der vorliegenden Erfindung diese Ruhezonen zwischen digitalen Übergängen aufrechterhalten.

**[0013]** Ein Schaltungs/Logik-Bereich des vorliegenden IC, der Satelliten (digitale) Rundfunkfernsehsignale verarbeitet, benutzt einen Interpolator für die Verarbeitung eines ankommenden Signals bei einer geeigneten, mit der Symbolrate in Beziehung stehenden Frequenz (z. B. 40 MHz), obgleich die tatsächlichen Abtastungen bei einer anderen Frequenz (z. B. 54 MHz) vorgenommen werden können. Ein ähnlicher Vorgang wird für die terrestrischen digitalen oder Restseitenband (VSB)-Fernsehsignale verwendet, wo die doppelte Symbolrate eine geeignete Frequenz ist (z. B. 21,54 MHz) während die Abtastfrequenz (Taktsignal) größer ist als die jeweilige Frequenz (z. B. 27 MHz). Eine analoge Verarbeitung des Fernsehsignals erfolgt ebenfalls bei einer bestimmten Frequenz (z. B. 18 MHz) für jeden Kanal. Wenn gleich die analogen Fernsehsignalabtastungen nicht mit der ankommenden Zeilenfrequenz verkoppelt sind, wird die Horizontalfrequenz mit der Unterabtastgenauigkeit für jeden Kanal ermittelt. Ein abschlie-

ßender Abtastratenwandler hat eine Frequenz (z. B. 27 MHz), die einer Frequenz für Luma (z. B. 13,5 MHz) plus einer Frequenz für jedes der Farbdifferenzsignale (z. B. 6,75 MHz) entspricht. Das ergibt zeitfehlerfreie Zeilen von Ausgangsdaten. Außerdem benutzt ein Chromademodulator des vorliegenden IC einen digitalen zeitdiskreten Oszillator (DTO = discrete time oscillator), der für jedes der ankommenden Signale auf das ankommende Chromaburstsignal verriegelt ist. Somit wird die gesamte digitale Verarbeitung durch synchrone Takte erreicht, trotz der asynchronen Eigenschaften in den verschiedenen Verarbeitungsbereichen der Schaltung/Logik, wie sie durch vier Typen von Fernsehsignalenystemen bestimmt sind.

**[0014]** Die vorliegende Erfindung erreicht außerdem einen Doppelnutzen bei einem großen Teil der digitalen Schaltung in dem dualen NTSC-Signalverarbeitungsabschnitt. Der digitale Farbdecoder (DCD) bewirkt alle notwendigen Signalverarbeitungsfunktionen für die Decodierung des NTSC-Video, einschließlich Kammfilterung für die Trennung von Luma und Chroma, Chromademodulation für die Erzeugung der Farbdifferenzsignale, Synchronsignalabtrennung, Umsetzung der Abtastrate (SRC = sample rate conversion) auf eine übliche Schnittstellenfrequenz und eine Datenseparation für das Vertikalauslastintervall (VBI = vertical blanking interval). Das VBI enthält im allgemeinen Untertitel, "V-chip"-Kindersicherungsinformationen, Programmführer, Teletextdaten und dergleichen. Alle diese Funktionen sind für das Hauptkanalvideo und das Video des zweiten Kanals enthalten, der im allgemeinen für ein Bild-in-Bild (PIP = picture-in-picture) benutzt wird.

**[0015]** Gemäß einem anderen Aspekt der vorliegenden Erfindung kombiniert der DCD die beiden Kanäle, verdoppelt nur die tatsächlichen Datenspeicherkomponenten für die beiden Kanäle und benutzt dieselben Schaltungen für den größten Teil der Verarbeitung durch den Betrieb bei der doppelten benötigten Abtast-/Takt-Frequenz und die Umschaltung der Kanäle bei jedem Taktzyklus. Somit wird zum Beispiel jeder Kanal mit 18 MHz bei jedem zweiten Taktzyklus bei 36 MHz verarbeitet.

**[0016]** In einer anderen Form enthält die vorliegende Erfindung einen analogen Signalverarbeitungsabschnitt und einen Taktgenerator. Der analoge Signalverarbeitungsabschnitt dient zur Verarbeitung analoger Signale mit einer Synchronisierkomponente, wie einem Horizontalsynchronimpuls oder dergleichen. Der Taktgenerator erzeugt interne Taktsignale auf der Grundlage eines externen Referenzsignals, die von dem Verarbeitungsabschnitt für analoge Signale benutzt werden, wobei das externe Referenzsignal von der Synchronisierkomponente der analogen Signale unabhängig ist.

**[0017]** In einer anderen Form enthält die vorliegende Erfindung einen analogen Signalverarbeitungsabschnitt, einen digitalen Signalverarbeitungsabschnitt, einen ersten A/D-Konverter für den Verarbeitungsabschnitt für das analoge Signal, und einen zweiten A/D-Konverter für den Verarbeitungsabschnitt für das digitale Signal. Die integrierte Schaltung enthält außerdem einen Taktgenerator zur Lieferung eines ersten und eines zweiten Taktsignals für den ersten bzw. den zweiten Analog/Digital-Konverter von einem einzigen Referenztaktsignal, wobei das erste und das zweite Taktsignal einen synchronen Betrieb des ersten und des zweiten Analog/Digital-Konverters ermöglichen.

**[0018]** In einer anderen Form enthält die vorliegende Erfindung einen analogen Signalverarbeitungsabschnitt, einen digitalen Signalverarbeitungsabschnitt und einen Taktgenerator. Der Taktgenerator erzeugt mehrere Taktsignale mit verschiedenen Frequenzen für die Anwendung durch den analogen und den digitalen Verarbeitungsabschnitt, wobei der Taktgenerator ein einziges Referenztaktsignal einer bestimmten Frequenz benutzt, die unabhängig ist von einem Synchronisiermerkmal des analogen und/oder digitalen Eingangssignals. Der analoge und der digitale Signalverarbeitungsabschnitt verarbeiten ihre jeweiligen analogen und digitalen Signale gleichzeitig.

**[0019]** Die vorliegende Erfindung wird anhand der beigefügten Zeichnung beschrieben:

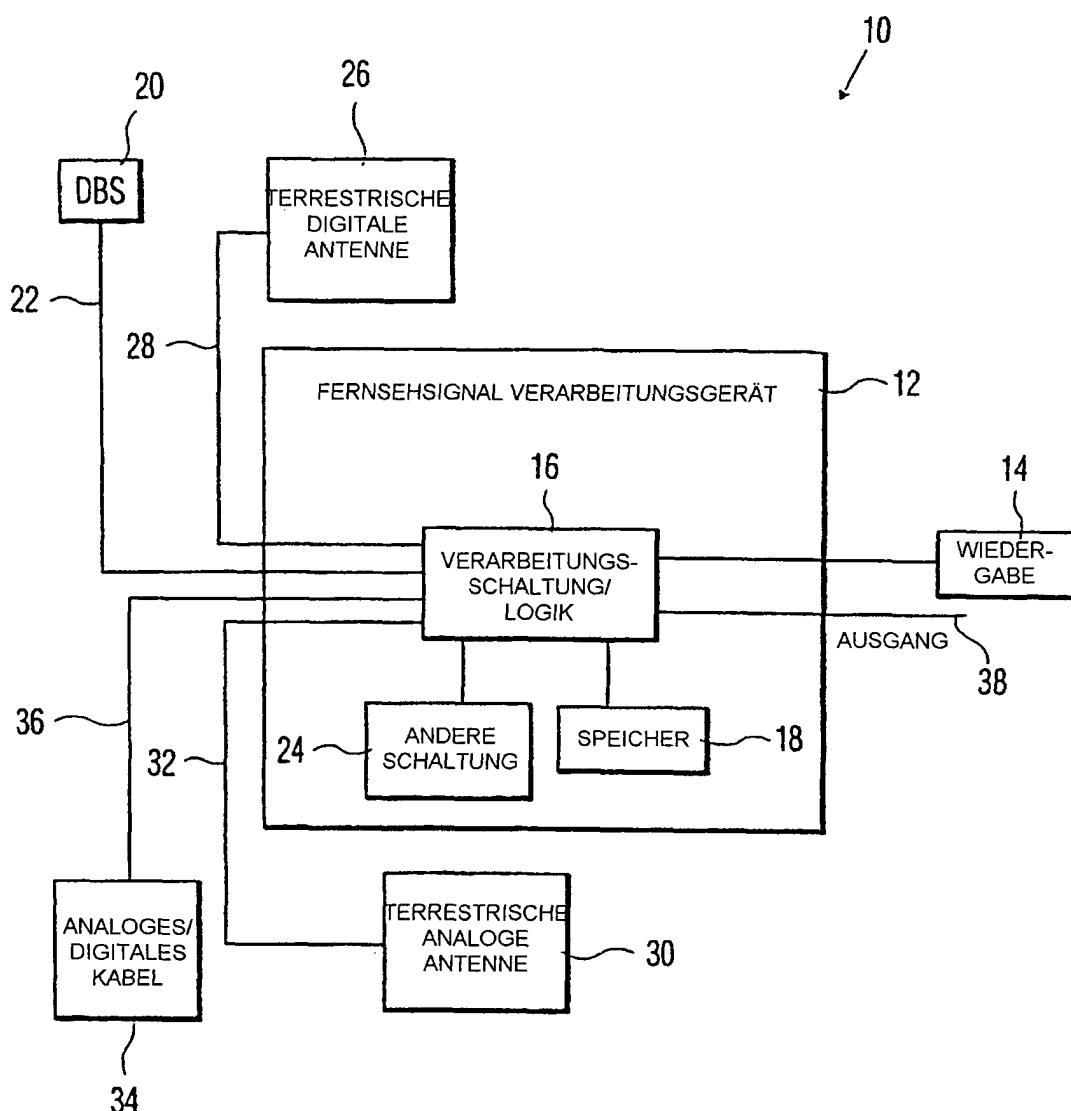

**[0020]** [Fig. 1](#) ist ein Blockschaltbild eines beispielhaften Systems, in dem das vorliegende IC angewendet werden kann,

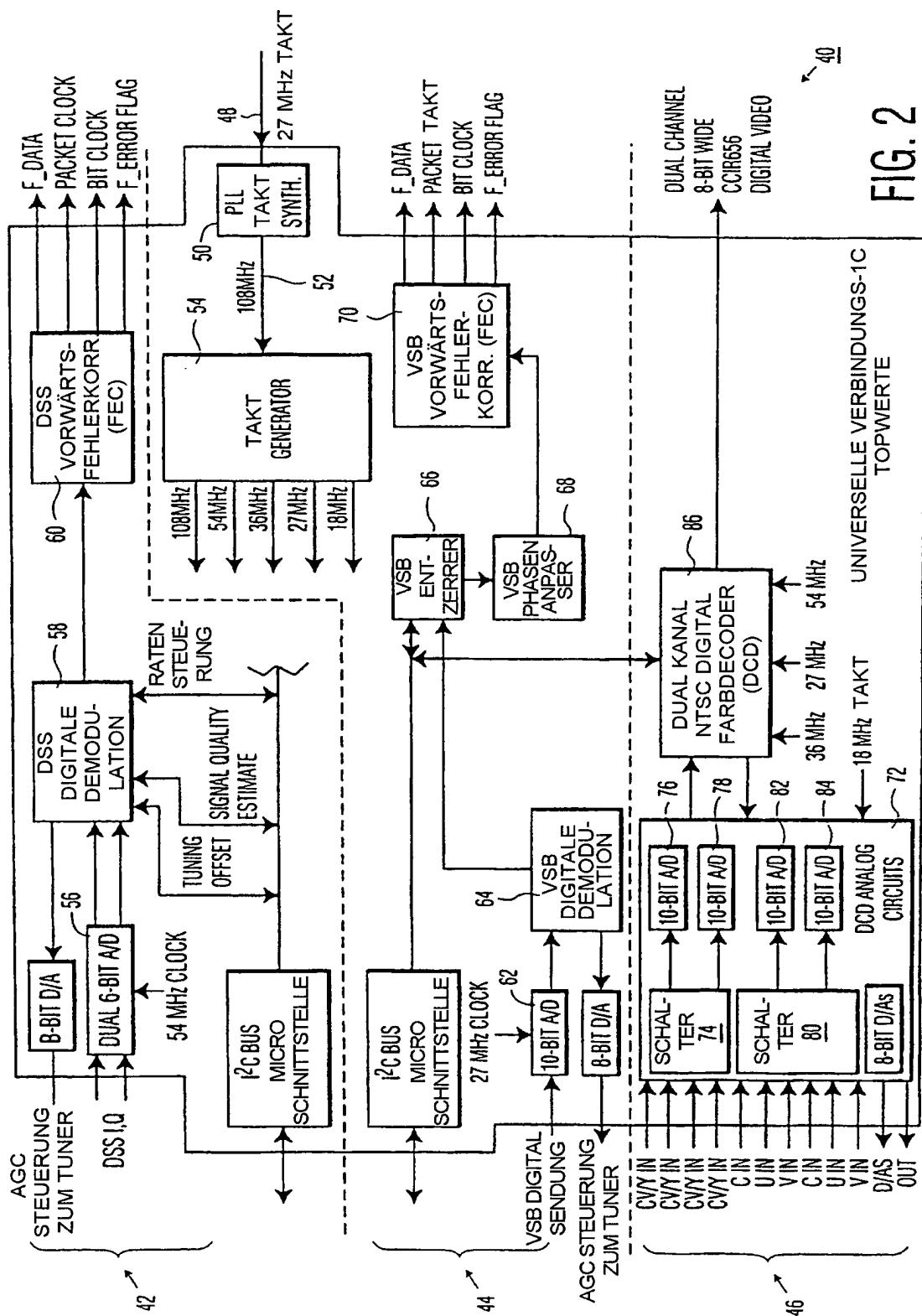

**[0021]** [Fig. 2](#) ist ein Blockschaltbild des IC, der in dem beispielhaften System von [Fig. 1](#) benutzt wird mit einer Ausführungsform der vorliegenden Erfindung,

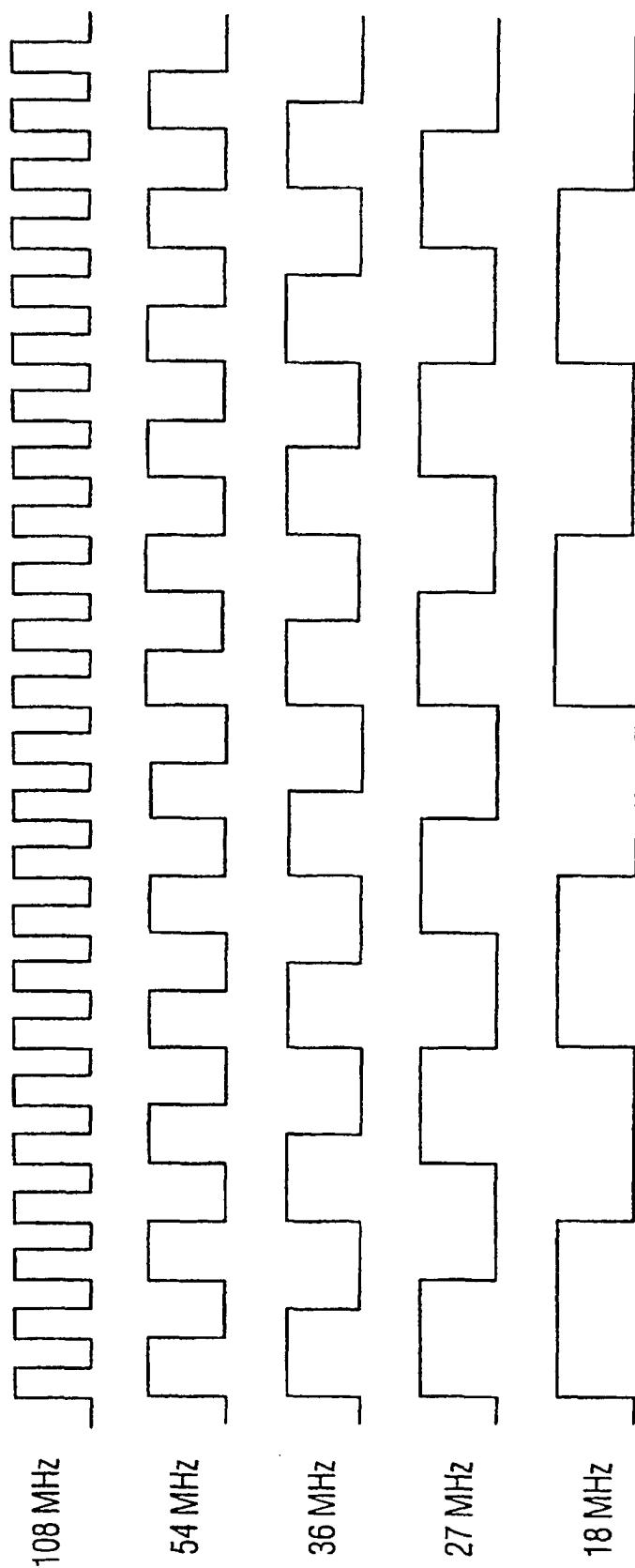

**[0022]** [Fig. 3](#) ist eine Kurvenschar und zeigt die verschiedenen, in dem IC von [Fig. 2](#) benutzten digitalen Frequenzen,

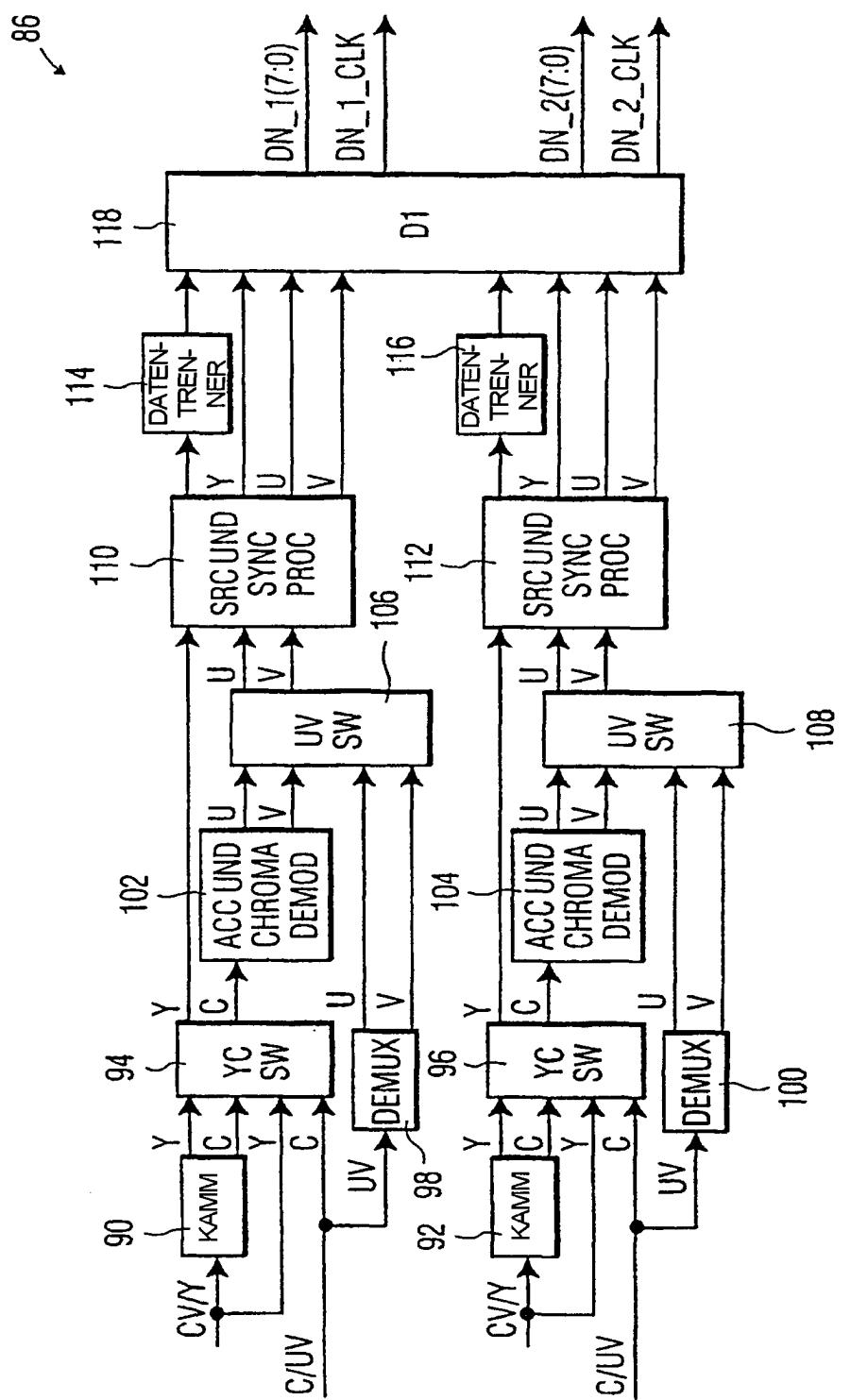

**[0023]** [Fig. 4](#) ist ein Blockschaltbild des digitalen Farbdecoders des IC von [Fig. 2](#), und

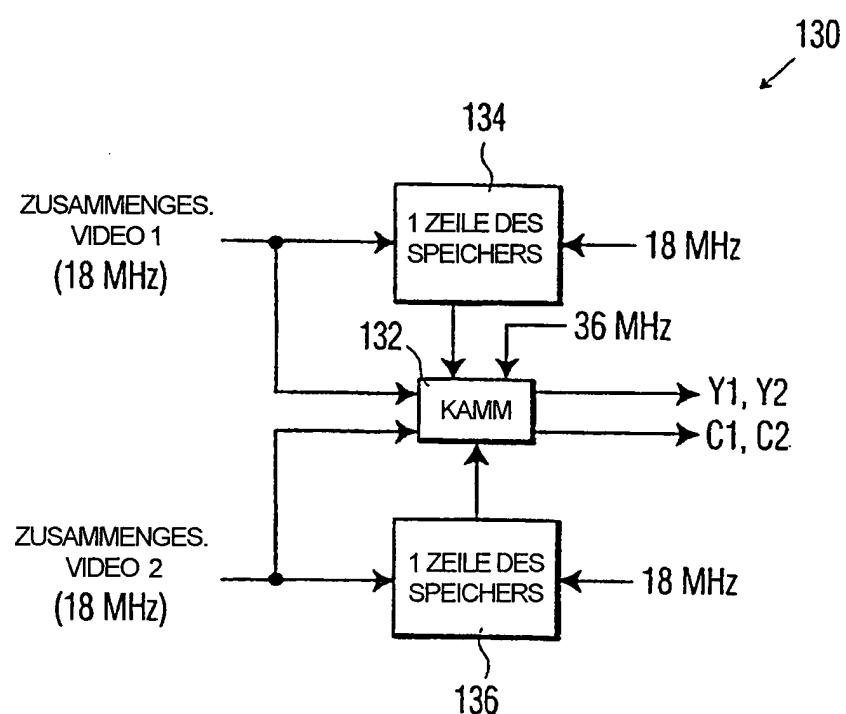

**[0024]** [Fig. 5](#) ist ein Blockschaltbild einer Kammfilterausführung des IC von [Fig. 2](#).

**[0025]** Gleiche Bezugszeichen bezeichnen gleiche oder ähnliche Teile in den verschiedenen Figuren.

**[0026]** [Fig. 1](#) zeigt ein Blockschaltbild eines Systems **10**, das für die Anwendung eines IC gemäß der vorliegenden Erfindung geeignet ist. Das System **10** enthält mehrere integrierte Schaltungen (ICs) für die Signal- und/oder Daten- und Informationsverarbeitung, wobei wenigstens ein IC mehrere Takte, Takt-

frequenzen oder Takt/Taktungssignale für die richtige Funktion benötigt. Dieser Typ des ICs kann als ein Mehrtakt-IC bezeichnet werden. Es sei bemerkt, dass das System **10** eine beispielhafte Umgebung/Anwendung ist, die das vorliegende Mehrtakt-IC benutzt. Das Mehrtakt-IC des Systems **10** kann gemäß den hier beschriebenen Prinzipien viele Formen annehmen und/oder viele Funktionen durchführen, wie es dem Fachmann auf diesem Gebiet bekannt ist.

**[0027]** In dem System **10** bewirkt das Mehrtakt-IC eine Fernsehsignalverarbeitung für eine Vielfalt von Fernsehsignalformaten von einer Vielfalt von Quellen. Kurz gesagt: Das Mehrtakt-Fernsehsignalprozessor IC, das die vorliegende Erfindung beinhaltet, dient zur Verarbeitung digitaler Satelliten-Fernsehsignale, terrestrischer (einschließlich Kabelverteilung) digitaler Fernsehsignale und terrestrischer (einschließlich Kabelverteilung) analoger Fernsehsignale. Diese analogen und digitalen Signale können in verschiedenen Kodierschemen und/oder Modulationssschemen vorliegen.

**[0028]** Das System **10** enthält ein Fernsehsignal-Verarbeitungsgerät **12**, das ein Fernsehgerät, eine Set-Top-Box oder dergleichen sein kann (durchgehend mit "Fernsehgerät" bezeichnet). Das Fernsehsignal-Verarbeitungsgerät **12** enthält eine Verarbeitungs-Schaltung/Logik **16** für die Decodierung eines empfangenen Fernsehsignals. Die Verarbeitungs-Schaltung/Logik **16** decodiert und verarbeitet digital modulierte analoge Audio- und Video-Fernsehsignale oder Übertragungen ("digitale Fernsehsignale") von einem Direct Broadcast Satelliten (DBS)-System **20**, moduliert zum Beispiel in einem QPSK (Quadrature Phase Shift Keying) Modulations/Codier-Format.

**[0029]** Die Verarbeitungs-Schaltung/Logik **16** decodiert und verarbeitet digitale Fernsehsignale von einer terrestrischen digitalen Fernseh- (DTV = Digital Television) Antenne **26**. Derartige Fernsehsignale können digital moduliert sein durch Anwendung eines VSB (Vestigial SideBand = Restseitenband)-Modulations/Codier-Formats.

**[0030]** Die Verarbeitungs-Schaltung/Logik **16** verarbeitet außerdem analoge Audio- und Video-Fernsehsignale ("analoge Fernsehsignale") von einer terrestrischen analogen Antenne **30**, empfangen über einen Signalweg oder Leitung **32**, sowie analoge Fernsehsignale von einem CATV (cable television) System **34**. Das Modulations/Codier-Format der analogen Fernsehsignale ist im allgemeinen NTSC, jedoch können andere Formate benutzt werden. Die Verarbeitung von analogen Fernsehsignalen enthält im allgemeinen eine Digitalisierung der Eingangssignale durch eine geeignete Schaltung, Software und/oder andere Bauteile. Digitale Fernsehsignale von dem

CATV-System **34** können ebenfalls decodiert und verarbeitet werden. Es sei erwähnt, dass das Fernsehgerät **12** analoge und/oder digitale Fernsehsignale von anderen Quellen empfangen und verarbeiten kann, als denen, die gezeigt sind.

**[0031]** Das Fernsehsignal-Verarbeitungsgerät **12** enthält im allgemeinen auch einen Speicher **18**, der gespeicherte Programminstruktionen (d. h. Software) für die Steuerung des Betriebs des Fernsehsignals-Verarbeitungsgerätes **12** enthält. Die Schaltung/Logik **24** ist für andere Funktionalitäten des Fernsehsignal-Verarbeitungsgerätes **12** vorgesehen. Diese Funktionalität ist für das Verständnis oder die Ausführung der vorliegenden Erfindung nicht notwendig und wird nicht im Detail beschrieben.

**[0032]** Das System **10** enthält außerdem eine Anzeigeeinheit **14**, die mit der Verarbeitungs-Schaltung/Logik **16** verbunden und für die Wiedergabe des Videoteils des Fernsehsignals (und des OSD davon) geeignet ist. In dem Fall einer Set-Top Box oder dergleichen gehört zu der Anzeigeeinheit **14** eine Anzeigeeinheit eines angeschlossenen Fernsehgerätes. Der Ausgang **38** kann außerdem vorgesehen sein, um Audio und/oder Video von dem Verarbeitungsgerät **12** einem anderen Gerät zuzuführen, einschließlich eines Videorecorders und dergleichen.

**[0033]** Das Fernsehsignal-Verarbeitungsgerät **12** kann ein analoges/digitales Fernsehgerät sein, einschließlich, aber nicht darauf beschränkt, ein DTV-320 HDTV (High Definition Television), hergestellt von Thomson Consumer Electronics Inc. of Indianapolis Indiana, ein digitales Fernsehgerät, wie ein Fernsehgerät mit hoher Auflösung (HDTV), eine Set-Top Box, die analoge/digitale Fernsehsignale verarbeiten kann, ein Fernsehsignal-Speichergerät oder jedes andere Gerät sein, das verschiedene Formen von Fernsehsignalen verarbeiten kann.

**[0034]** Gemäß einem Aspekt der vorliegenden Erfindung ist wenigstens eines der mehreren ICs in dem System **10** ein Mehrtakt-IC. Das Mehrtakt-IC, das in der Verarbeitungs-Schaltung/Logik **16** des Fernsehgerätes **12** benutzt wird, ist bekannt als ein sogenanntes Universal Link IC und ist in [Fig. 2](#) dargestellt. Das Universal Link IC **40** ist eine integrierte Schaltung für gemischte Signale, d. h. es enthält analoge und digitale Fernsehsignal-Verarbeitungs-Schaltungen und vereint mehrere Fernsehsignal-Verarbeitungsfunktionen in einem einzigen IC.

**[0035]** [Fig. 2](#) zeigt ein Blockschaltbild eines Universal Link IC **40**, das in dem Fernsehgerät **12** benutzt wird. Die Mehrtaktsignale mit verschiedenen Frequenzen werden durch das Universal Link IC **40** aus einem einzigen, extern erzeugten Referenztaktsignal mit einer bestimmten Frequenz erzeugt. Das Universal Link IC **40** enthält einen I/O Anschluss **48**, der das

extern erzeugte Referenztaktsignal empfängt. In der vorliegenden Ausführungsform verwendet das Universal Link IC **40** ein extern geliefertes Referenztaktsignal mit 27 MHz. Andere externe Referenztaktfrequenzen können gemäß den hier angegebenen Prinzipien benutzt werden.

**[0036]** Insbesondere beruht das externe Referenztaktsignal nicht auf oder ist nicht verriegelt mit einer verriegelbaren Eigenschaft, wie einem Synchronimpuls oder color burst eines ankommenden Fernsehsignals (entweder analog oder digital). Vielmehr wird das externe Referenztaktsignal so gewählt, dass eine leichte Multiplikation und Division zur Erzeugung von Taktsignalen mit geeigneten Frequenzen zur Anpassung an die Anforderung für die Taktfrequenz der verschiedenen Abschnitte oder Blöcke der Schaltung/Logik des Universal Link IC **40** gegeben ist.

**[0037]** In dem Universal Link IC **40** wird das externe Referenztaktsignal dem Synthesizer **50** mit einer phasenverkoppelten Schleife (PLL = Phase Locked Loop) zugeführt, der auf der Ausgangsleitung **52** ein Ausgangstaktsignal mit einer bestimmten Frequenz erzeugt. Hier wurde das PLL-Ausgangstaktsignal gleich 108 MHz gewählt und kann als ein internes Referenztaktsignal angesehen werden. Alle übrigen benötigten Taktsignale werden aus diesem internen Referenztaktsignal erzeugt.

**[0038]** Das interne Referenztaktsignal mit 108 MHz wird dem Taktgenerator **54** zugeführt, der die geeignete Schaltung/Logik zur Erzeugung mehrerer Taktfrequenzen enthält. Die tatsächliche Zahl der durch den Taktgenerator **54** erzeugten Taktsignale ist abhängig von den Anforderungen an das Taktignal des jeweiligen IC. In dem Universal Link IC **40** erzeugt der Taktgenerator **54** vier (4) Taktsignale mit verschiedenen Frequenzen und ein (1) Taktignal mit derselben Frequenz wie das interne Referenztaktsignal. Jedes erzeugte Taktignal wird dann dem jeweiligen Bereich oder Block der Schaltung/Logik zugeführt.

**[0039]** Vorzugsweise ist die durch den PLL-Takt-Synthesizer **50** erzeugte interne IC-Referenztaktfrequenz ein Vielfaches der externen Referenztaktfrequenz. Insbesondere ist die interne IC-Referenztaktfrequenz vorzugsweise ein ganzzahliges Vielfaches der externen Referenztaktfrequenz. Die interne IC-Referenztaktfrequenz ist außerdem so gewählt, dass sie in die mehreren IC-Taktsignale oder Frequenzen geteilt werden kann, die durch die verschiedenen Abschnitte oder Blöcke der Schaltung/Logik benutzt werden.

**[0040]** In dem vorliegenden Fall beträgt die interne Referenztakt-Signalfrequenz 108 MHz, was das Vierfache der externen Referenztakt-Signalfrequenz von 27 MHz ist. Der Taktgenerator **54** erzeugt dann ein

Taktsignal mit 54 MHz, was die Hälfte (1/2) des internen IC-Taktsignals mit 108 MHz ist, ein Taktsignal mit 36 MHz, was ein Drittel (1/3) des internen IC-Taktsignals mit 108 MHz ist, ein Taktsignal mit 27 MHz, was ein Viertel (1/4) des internen IC-Taktsignals mit 108 MHz ist, und ein Taktsignal mit 18 MHz, was ein Sechstel (1/6) des internen IC-Taktsignals 108 MHz ist. Daher erzeugt der Taktgenerator vier Untertakte **54** ohne Phasenverschiebung, die Subharmonische des internen Mastertakts sind.

**[0041]** Ein weiterer Faktor bei der Bestimmung der Frequenzen der internen Taktsignale sind die Abtastraten oder Taktraten für die verschiedenen Abschnitte oder Blöcke der Schaltung/Logik des Universal Link ICs **40**. Wie oben bemerkt, enthält das Universal Link IC **40** drei Hauptabschnitte. Die drei Hauptabschnitte sind: "Satlink" Abschnitt **42**, der durch Satelliten übertragene Fernsehsignale empfängt und demoduliert/decodiert. Der Abschnitt **44** "VSB (Vestigal SideBand) link", der terrestrisch übertragene allgemeine digitale Signale und/oder digitale Signale mit hoher Auflösung (HDTV) empfängt und demoduliert/decodiert, und der Abschnitt "DCD" (Digital Color Decoder) **46**, der ein Block der Schaltung/Logik ist, der die Umschaltung, die Chromademodulation und andere Signalverarbeitung von (analogen) NTSC-Signalen durchführt. Das Universal Link IC **40** bildet verschiedene getrennte Decoder/Demodulationssysteme, einschließlich eines ersten Systems für ein analoges Haupt-Fernsehsignal, ein zweites System für ein zusätzliches analoges Fernsehsignal (wie ein PIP oder Bild-in-Bild und/oder POP oder Bild-auf-Bild), ein drittes System für digitale Satellitenfernsehsignale und ein vieres System für digitale terrestrische Fernsehsignale. Die Abschnitte **42**, **44** und **46** arbeiten unabhängig und parallel. Wegen der Art der verschiedenen Signale benötigen verschiedene Teile der Schaltung/Logik der Abschnitte oder Blöcke der Schaltung/Logik verschiedene Takt- oder Abtastfrequenzen.

**[0042]** Der Satlink- Abschnitt **42** empfängt einen Eingang I,Q an einem geeigneten "x-Bit" A/D-Konverter. Insbesondere werden die Eingänge I und Q an einen dualen 6-Bit A/D-Konverter **56** geliefert, der durch das Taktsignal mit 54 MHz getaktet oder abgetastet wird. Der Demodulationsblock **58** und der Vorwärtsfehlerkorrektur (FEC)-Block **60** verarbeiten außerdem das digitale Satelliten-Fernsehsignal. Insbesondere benutzen der Demodulationsblock **58** und der FEC-Block **60** einen Interpolator zur Verarbeitung des (digitalen) Satelliten-Rundfunksignals bei einer geeigneten Frequenz, die in Beziehung steht zu der Symbolrate für das digitale Satelliten-Fernsehsignal. In dem vorliegenden Fall beträgt die geeignete Symbolratenfrequenz 40 MHz. Der duale 6-Bit A/D-Konverter **56** benutzt jedoch das IC-Taktsignal mit 54 MHz zur Taktung oder Abtastung (Überabtastung) des ankommenden Fernsehsignals, obwohl er nur

ein Takt- oder Abtastsignal mit 40 MHz benötigt. Der Takt mit 54 MHz stellt eine Erhöhung von 35% in der Takt- oder Abtastfrequenz gegenüber der benötigten Takt- oder Abtastfrequenz dar.

**[0043]** Ähnlich zu dem Satlink Abschnitt **42** empfängt der VSB-Abschnitt **44** das digitale VSB-Rundfunkfernsehsignal über einen geeigneten "x-Bit" A/D-Konverter. Der VSB-Abschnitt **44** empfängt das VSB-Signal über einen 10 Bit A/D-Konverter **62**, der mit dem Taktsignal von 27 MHz getaktet wird. Der Demodulationsblock **64**, der Entzerrerblock **66**, der Phasennachführblock **68** und der Vorwärtsfehlerkorrektur (FEC)-Block **70** verarbeiten außerdem das terrestrisch gesendete digitale Fernsehsignal. Insbesondere verarbeiten der Demodulationsblock **64**, der Entzerrerblock **66**, der Phasennachführblock **68** und der FEC-Block **70** das VSB-Signal bei der doppelten symbolratenbezogenen Frequenz für die VSB (d. h. terrestrischen) digitalen Fernsehsignale. In dem vorliegenden Fall beträgt die geeignete Symbolratenfrequenz 10,77 MHz, also ist das Doppelte der geeigneten Symbolratenfrequenz 21,54 MHz. Der 10-Bit A/D-Konverter **62** benutzt jedoch das IC-Taktsignal mit 27 MHz zur Taktung oder Abtastung (Überabtastung) des ankommenden Fernsehsignals, obwohl er nur ein Takt- oder Abtastsignal mit 21,54 MHz benötigt. Der Takt mit 27 MHz stellt eine Zunahme von ungefähr fünfundzwanzig Prozent (25 %) in der Takt- oder Abtastfrequenz gegenüber der benötigten Abtastfrequenz dar.

**[0044]** In dem DCD-Abschnitt **46** erfolgt die analoge Abtastung durch das Taktsignal mit 18 MHz für jeden Kanal des analogen Fernsehsignals. Wenn gleich diese Abtastungen nicht mit einem Merkmal des Eingangserneignisses verriegelt sind, wird diese HORIZONTALFREQUENZ mit der Genauigkeit einer Unterabtastung für jeden Kanal bestimmt. Der DCD-Abschnitt **46** empfängt zwei analoge Signale (d. h. eines für den Hauptkanal und das andere für das PIP oder POP) bei dem analogen Abschnitt **72** der DCD Schaltungen. Die vier (4) CV/Y-Signale davon werden an den Schalter **74** angelegt, der daraufhin die Signale zu den beiden 10-Bit A/D-Konvertern **76** und **78** liefert. Die beiden Sätze von getrennten C, U und V INS davon werden in den Schalter **80** eingegeben, der in geeigneter Weise das Signal zu den beiden 10-Bit A/D-Konvertern **82** und **84** liefert. Die Ausgänge dieser vier 10-Bit A/D-Konverter **76**, **78**, **82** und **84** werden an einen dualen Zweikanal digitalen NTSC Farbdecoder **86** angelegt. Die endgültige Umsetzung der Abtastrate erfolgt bei 27 MHz (sequentiell 13,5 MHz für Luma 6,75 MHz für jedes der Farbdifferenzsignale). Das ergibt zeitfehlerfreie Zeilen am Datenausgang. Zusätzlich benutzt der Chromademodulator einen digitalen zeitdiskreten Oszillator (DTO), der auf das ankommende Chroma Burst Signal für jedes der ankommenden Signale verriegelt ist.

**[0045]** Die gesamte A/D-Verarbeitung und die digitale Signalverarbeitung erfolgen durch Anwendung von synchronen Taktten, anstelle der asynchronen Eigenschaft in diesen vier Signalisierungssystemen. Außerdem ist jede IC-Takt signalfrequenz, die durch den Taktgenerator **54** erzeugt wird, gleich oder größer als die Takt/Abtast-Signal frequenz, die für den richtigen Betrieb des jeweiligen Teils der Schaltung/Logik benötigt wird. Eine derartige Überabtastung kann für die spätere Verarbeitung des jeweiligen Signals vorgesehen sein. Unerwünschte Wirkungen, die durch den synchronen Betrieb der A/Ds und die Signalprozessor-Abschnitte erzeugt werden, können durch die Chromademodulations-Abschnitte **102** und **104** und den SRC und die Synchronprozessoren **110** und **112** kompensiert werden. Die Lösungen zur Be seitigung derartiger Wirkungen sind dem Fachmann auf diesem Gebiet hinreichend bekannt und werden hier nicht im Detail beschrieben.

**[0046]** Da es nur ein Referenztaktsignal gibt, aus dem alle anderen Abtast- und Verarbeitungsfrequenzen erzeugt werden, sind die A/Ds imstande, mit hoher Leistungsfähigkeit zu arbeiten (d. h. bis zu 10-Bit Genauigkeit) und haben wenig oder kein digitales Rauschen. Das ist mit asynchronen Abtastfrequenzen nicht möglich weil die „stillen Bereiche“, die für die Abtastung des analogen Signals benötigt werden nicht mehr existieren. Jedoch bleiben bei mehreren, von einem Takt abgeleiteten Abtastfrequenzen die Ruhezonen zwischen den digitalen Übergängen erhalten (siehe [Fig. 3](#)).

**[0047]** Ein anderer Aspekt der vorliegenden Erfindung ist die doppelte Benutzung von Teilen der digitalen Schaltung für die Verarbeitung von NTSC-Fernseh signalen. [Fig. 4](#) zeigt ein Blockschaltbild eines DCD-Blocks **86**. Der DCD-Block **86** führt alle notwendigen Signalverarbeitungsfunktionen für zwei analoge NTSC Fernseh signalen aus. Der DCD-Block **86** enthält duale Kammfilter **90** und **92** für die Trennung von Luma und Chroma von den beiden ankommen den analogen Fernseh signalen, welche dem Luma- und Chroma-Schalter **94** bzw. **96** zugeführt werden. Der Luma- und Chroma-Schalter **94** bzw. **96** wird jeder bei 36 MHz getaktet (das Doppelte der benötigten Frequenz von 18 MHz für einen einzelnen Kanal), so dass die Chroma und Luma Komponenten der Kanäle bei jedem Takt geschaltet werden. Somit wird jeder 18 MHz Kanal bei jedem zweiten Taktzyklus von 36 MHz verarbeitet.

**[0048]** Die Chromakomponenten werden in die ACC und die Chromademodulationsblöcke **102** bzw. **109** eingegeben. Die UV-Komponenten werden in zwischen zu Demultiplexern **98** und **100** weitergeleitet, um getrennte U- bzw. V-Komponenten zu gewinnen. Die Ausgänge U und V der Chromademodulation module **102** und **104** (Farbdifferenzsignale) werden mit den U und V Ausgängen der Demultiplexer

**98** und **100** in jeweiligen UV-Schaltern **106** beziehungsweise **108** kombiniert, die wieder mit 36 MHz getaktet werden (das Doppelte der benötigten Frequenz von 18 MHz für einen einzelnen Kanal), so dass die Chroma- und die Luma-Komponente jedes Kanals bei jedem Takt geschaltet werden. Somit wird jeder 18 MHz Kanal bei jedem zweiten Taktzyklus bei 36 MHz verarbeitet.

**[0049]** Die Luma- und UV-Komponenten werden zu Abtastratenkonvertern und Blöcken **110** bzw. **112** für die Abtrennung des Synchronisier (sync) -Signals weitergeleitet und erzeugen ein Signal mit einer üblichen Schnittstellenfrequenz. Zusätzlich erfolgt eine Datenaufspaltung für das Vertikalaustastintervall (VBI) durch Datenaufspalter **114** und **116**, wobei Untertitel, "v-chip" Kindersicherungs informationen, Tele textdaten, Programmführerinformationen und der gleichen gewonnen werden. Die Ausgänge der Abtastratenkonverter und der Synchronprozessoren **110** bzw. **112** und die jeweiligen Datenaufspalter **114** und **116** werden Videoprozessoren **118** zugeführt, um den Hauptvideokanal und den zweiten (zusätzlichen) Videokanal bereitzustellen. Der zweite Videokanal wird im allgemeinen für PIP oder POP benutzt. Wie oben erwähnt, werden unerwünschte Wirkungen der Anwendung eines einzigen Referenztaktes in Chroma-Demodulationsabschnitten **102** und **104** sowie SRC- und Synchronprozessoren **110** und **112** kompensiert.

**[0050]** [Fig. 5](#) zeigt ein Blockschaltbild, im Ganzen mit **130** bezeichnet, der Kammfilterausführung mit einer Doppelbenutzung des größten Teils der logischen Schaltungen des DCD-Blocks **86** gemäß einem Aspekt der vorliegenden Erfindung. Das erste kombinierte Videosignal mit einer Taktung- oder Abtastfrequenz von 18 MHz wird in eine Datenspeichereinheit **134**, die eine Zeile des Videos speichert, und in ein Kammfilter **132** eingegeben. Zur selben Zeit wird das zweite kombinierte Videosignal mit einer Takt- oder Abtastfrequenz von 18 MHz in eine Datenspeichereinheit **136**, die eine Zeile des Videosignals hält, und in das Kammfilter **132** eingegeben. Die Datenspeichereinheiten **134** und **136** werden jede bei der Abtastrate von 18 MHz getaktet. Das Kammfilter **132** wird bei dem Doppelten von 18 MHz oder bei 36 MHz getaktet. Auf diese Weise verarbeitet das Kammfilter **132** abwechselnd den Ausgang der Datenspeichereinheiten **134** und **136**.

**[0051]** Somit kombiniert der DCD-Block **86**, anstelle zweier vollständig verschiedener Schaltungen, die beiden Kanäle, wobei nur die tatsächlichen Datenspeicherkomponenten doppelt vorhanden sind. Der DCD-Block **86** benutzt außerdem dieselben Schaltungen für den größten Teil der Verarbeitung durch den Betrieb bei der doppelten benötigten Frequenz und Umschaltung der Kanäle bei jedem Takt.

**[0052]** Insbesondere ist die vorliegende Erfindung auf andere Schaltungen anwendbar, in denen es notwendig ist, Systeme mit verschiedenen Frequenzanforderungen zu betreiben, wo es erwünscht ist, das System/Schaltungen auf demselben Chip zu betreiben, insbesondere diejenigen mit A/Ds und andere analoge Schaltungen, zusätzlich zu der digitalen Schaltung/Logik.

### Patentansprüche

1. Signalverarbeitungsvorrichtung (**49**) mit: ersten und zweiten Signaleingängen (CV/Y IN) zum Empfang erster bzw. zweiter analoger Signale mit jeweiligen Synchronisiermerkmalen, einem ersten Taktgenerator (27 MHz Takt) zur Erzeugung eines Referenztaktsignals, wobei das Referenztaktsignal von den Synchronisiermerkmalen der analogen Signale unabhängig ist, einem dem ersten Taktgenerator zugeführten zweiten Takt (**54**) zur Erzeugung mehrerer weiterer Taktsignale aus dem Referenztaktsignal und einem Signalverarbeitungsabschnitt (**46**), der mit den ersten und zweiten Signaleingängen und dem zweiten Taktgenerator verbunden ist, zur Abtastung und Verarbeitung der ersten und zweiten analogen Signale entsprechend einer Abtastrate und einem jeweiligen Signalstandard, wobei der Signal-Verarbeitungsabschnitt mehrere Analog/Digital (A/D)-Wandler (**76, 78, 82, 84**) aufweist, die durch jeweils eines der mehreren weiteren Taktsignale getaktet werden, wobei die A/D-Wandler durch jeweils eines der weiteren Taktsignale getaktet werden, die von den Synchronisiermerkmalen der analogen Eingangssignale unabhängig sind und eine Frequenz aufweisen, die im wesentlichen gleich der Abtastrate ist,

**dadurch gekennzeichnet**, dass

der Signalverarbeitungsabschnitt die ersten und zweiten analogen Signale unter Anwendung eines einzelnen dualen Zweikanalprozessors (**86**) verarbeitet, der einzelne Prozessor durch ein weiteres Taktignal (36 MHz) getaktet wird, das eine Signalfrequenz von wenigstens dem Doppelten der benötigten Taktgeschwindigkeit (18 MHz) aufweist, die zur Verarbeitung einer einzelnen der abgetasteten ersten oder zweiten digitalen Signale benötigt wird, wobei jedes der ersten und zweiten abgetasteten digitalen Signale bei jedem zweiten Taktzyklus der weiteren Taktsignale verarbeitet und an einem gemeinsamen Ausgang zusammengefasst wird.

2. Signalverarbeitungsvorrichtung nach Anspruch 1, dadurch gekennzeichnet, dass die analogen Signale Fernsehsignale sind.

3. Verfahren zur Verarbeitung erster und zweiter Signale mit jeweiligen Synchronisierkomponenten mit folgenden Schritten:

Empfang erster und zweiter analoger Signale (CV/Y IN) mit jeweiligen Synchronisierkomponenten,

Erzeugung eines Referenztaktsignals (27 MHz-Takt), wobei das Referenztaktsignal unabhängig von den Synchronisiermerkmalen der ersten oder zweiten Signale ist,

Erzeugung mehrerer weiterer Taktsignale (18MHz, 27 MHz, 36 MHz, 54 MHz, 108 MHz) aus dem Referenztaktsignal,

Umsetzung der ersten und zweiten analogen Signale in erste bzw. zweite digitale Signale durch Analog/Digital (A/D) -Wandler (**76, 78, 82, 84**), die durch eines der mehreren weiteren Taktsignale getaktet werden, und

Decodierung (**46**) der umgesetzten, digitalen Signale gemäß einer geeigneten Fernsehsignalnorm unter Anwendung der Decodier-Schaltung/Logik zur Bildung von Ausgangssignalen für die Wiedergabe, wobei die Decodier-Schaltung/Logik durch wenigstens eines der mehreren weiteren Taktsignale getaktet wird, die A/D-Wandler und die Decodier-Schaltung/Logik durch jeweils eines der mehreren weiteren Taktsignale getaktet wird, die unabhängig von den Synchronisiermerkmalen des Eingangssignals sind und eine Frequenz im wesentlichen gleich der Abtastrate aufweisen, dadurch gekennzeichnet, dass der Decodierschritt die Decodierung der ersten und zweiten digitalen Signale enthält, zur Bildung von zwei Ausgangssignalen mittels eines einzelnen Zweikanalprozessors (**86**), der durch ein weiteres Taktignal getaktet wird (36 MHz), das eine Frequenz von wenigstens dem Doppelten der benötigten Taktgeschwindigkeit von 18 MHz aufweist, welcher zur Verarbeitung eines einzelnen der abgetasteten ersten und zweiten digitalen Signale notwendig ist, wobei jedes der abgetasteten ersten und zweiten digitalen Signale bei jedem zweiten Taktzyklus des weiteren Taktsignals verarbeitet und an einem gemeinsamen Ausgang zusammengefasst wird.

4. Verfahren nach Anspruch 3, dadurch gekennzeichnet, dass der Empfangsschritt den Empfang erster und zweiter Fernsehsignale enthält.

Es folgen 5 Blatt Zeichnungen

## Anhängende Zeichnungen

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5