(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7403238号

(P7403238)

(45)発行日 令和5年12月22日(2023.12.22)

(24)登録日 令和5年12月14日(2023.12.14)

(51)国際特許分類

|        |                  |        |        |   |

|--------|------------------|--------|--------|---|

| H 03 K | 17/687 (2006.01) | H 03 K | 17/687 | A |

| H 03 K | 17/00 (2006.01)  | H 03 K | 17/00  | B |

| G 01 R | 31/50 (2020.01)  | G 01 R | 31/50  |   |

F I

請求項の数 8 (全13頁)

|          |                             |          |                                                            |

|----------|-----------------------------|----------|------------------------------------------------------------|

| (21)出願番号 | 特願2019-102665(P2019-102665) | (73)特許権者 | 509186579                                                  |

| (22)出願日  | 令和1年5月31日(2019.5.31)        |          | 日立A s t e m o 株式会社                                         |

| (65)公開番号 | 特開2020-198499(P2020-198499) |          | 茨城県ひたちなか市高場2520番地                                          |

|          | A)                          | (74)代理人  | 110000350                                                  |

| (43)公開日  | 令和2年12月10日(2020.12.10)      |          | ボレール弁理士法人                                                  |

| 審査請求日    | 令和4年3月16日(2022.3.16)        | (72)発明者  | 中川 樹生<br>東京都千代田区丸の内一丁目6番6号<br>株式会社日立製作所内                   |

|          |                             | (72)発明者  | 佐藤 勝生<br>茨城県ひたちなか市高場2520番地                                 |

|          |                             | (72)発明者  | 日立オートモティブシステムズ株式会社<br>内                                    |

|          |                             | (72)発明者  | 小田部 晃<br>茨城県ひたちなか市高場2520番地<br>日立オートモティブシステムズ株式会社<br>最終頁に続く |

(54)【発明の名称】 電子回路およびセンサシステム

## (57)【特許請求の範囲】

## 【請求項1】

電子回路であって、

前記電子回路内の電源線と出力端子との間に設けられた負荷と、

前記負荷と前記出力端子との間に設けられたトランジスタと、

前記電子回路内の電源線の電源電圧を用いて電流を生成する電流生成回路と、

前記電流生成回路で生成した電流に応じて変化する制御電圧を用いて前記トランジスタを制御する制御回路を有し、

前記電子回路内の電源線には、前記電子回路の外部から前記電源線の電源電圧を供給する電源供給線が接続され、

前記制御回路は、前記電子回路の動作時には前記トランジスタをオンにし、前記電源供給線の断線時には前記トランジスタをオフにするよう前記トランジスタのゲート端子を制御し、

前記断線時に、前記電源電圧がグラウンドレベルよりも前記トランジスタの閾値電圧以上高い所定の電圧において前記トランジスタをオフにし、

前記電流生成回路と前記トランジスタとの間に、前記電流生成回路で生成した電流変化に応じて前記制御電圧を変えるカレントミラー回路及びプルダウン抵抗を有することを特徴とする電子回路。

## 【請求項2】

請求項1に記載の電子回路において、

前記プルダウン抵抗が前記カレントミラー回路の出力とグラウンドとの間に接続されていることを特徴とする電子回路。

【請求項 3】

請求項 2 に記載の電子回路において、

前記カレントミラー回路の設計上の出力電流値と前記プルダウン抵抗の抵抗値の積が、動作時の前記電源線に供給される電圧よりも高いことを特徴とする電子回路。

【請求項 4】

請求項 1 に記載の電子回路において、

前記カレントミラー回路が PMOS FET がカスコード接続された構成であることを特徴とする電子回路。

10

【請求項 5】

請求項 4 に記載の電子回路において、

前記電子回路内の電源線に接続される電源供給線の断線時に、前記電流生成回路で生成した前記電流と比較して前記カレントミラー回路の出力電流が早く減少することを特徴とする電子回路。

【請求項 6】

請求項 1 に記載の電子回路において、

前記電子回路内の電源線に接続される電源供給線の断線時に、前記トランジスタのゲート端子と前記出力端子が接続された配線とを接続するためのスイッチを有することを特徴とする電子回路。

20

【請求項 7】

検出対象の変化に応じた電気信号を出力するセンサエレメントと、

前記電気信号を処理し、該処理の結果を、出力回路を介して出力する電子回路と、

を有するセンサシステムであって、

前記出力回路は、

前記電子回路内の電源線と出力端子との間に設けられた負荷と、

前記負荷と前記出力端子との間に設けられたトランジスタと、

前記電子回路内の電源線の電源電圧を用いて電流を生成する電流生成回路と、

前記電流生成回路で生成した電流に応じて変化する制御電圧を用いて前記トランジスタを制御する制御回路を有し、

30

前記電子回路内の電源線には、前記電子回路の外部から前記電源線の電源電圧を供給する電源供給線が接続され、

前記制御回路は、前記電子回路の動作時には前記トランジスタをオンにし、前記電源供給線の断線時には前記トランジスタをオフにするよう前記トランジスタのゲート端子を制御し、

前記断線時に、前記電源電圧がグラウンドレベルよりも前記トランジスタの閾値電圧以上高い所定の電圧において前記トランジスタをオフにし、

前記電流生成回路と前記トランジスタとの間に、前記電流生成回路で生成した電流変化に応じて前記制御電圧を変えるカレントミラー回路及びプルダウン抵抗を有することを特徴とするセンサシステム。

40

【請求項 8】

請求項 7 に記載のセンサシステムにおいて、

前記出力回路が output する信号が、SENT 信号であることを特徴とするセンサシステム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子回路およびセンサシステムに関し、例えば、車載用の半導体電子回路およびセンサシステムに関する。

【背景技術】

【0002】

50

センサなどで計測した信号を出力する出力回路を搭載した半導体電子回路が広く用いられている。例えば、車載用の半導体電子回路内の出力回路は、出力配線を介して E C U (Engine Control Unit) 等に伝送する場合がある。センサなどの半導体電子回路には、一般に電源供給線が接続され、外部より電源が供給される。

### 【 0 0 0 3 】

本技術分野における従来技術として特許文献 1 がある。特許文献 1 は、出力天洛状態の誤検出を防止することを目的とし、負荷がオープンの場合に、天洛と誤検出しないように出力端子電圧を、電流源とクランプ回路を用いて生成した電圧に制限する構成が開示されている。

### 【先行技術文献】

10

### 【特許文献】

### 【 0 0 0 4 】

### 【文献】特開 2 0 1 6 - 1 2 2 9 6 5 号公報

### 【発明の概要】

### 【発明が解決しようとする課題】

### 【 0 0 0 5 】

しかしながら、特許文献 1 は、電源供給線が断線したときについては考慮されていない。

### 【 0 0 0 6 】

電源供給線が断線した際には、E C U 側で断線したことを認識できるようにする必要がある。より具体的には、E C U 側でプルアップ抵抗により電源に接続されているような場合には、電源供給断線時に出力回路の出力インピーダンスが高インピーダンスとなり、出力端子への電流流入を防ぎ、出力端子電圧が、電源電圧とほぼ等しい電圧となることが求められる。このように出力端子電圧が電源電圧とほぼ等しくなることにより、電源供給線が断線したことを E C U 側で認識することができる。

20

### 【 0 0 0 7 】

しかしながら、電源供給線断線時に、出力回路内において出力端子と電源線に電流が流れる経路があるため、出力端子から出力回路内に電流が流入し、出力端子電圧が中間電位となる場合がある。E C U 側で電源供給線断線を認識するためには、この電流流入と中間電位を抑制し、出力インピーダンスを高インピーダンスにして出力端子電圧をハイレベルとする必要がある。

30

### 【 0 0 0 8 】

また、電源供給線断線時においても、出力回路内の電源線に電荷が残り、電源電圧がグラウンドレベルまで落ちない、あるいは、電源電圧が低下するのに非常に長い時間がかかる場合があることがある。従って電源供給線断線時においても電源電圧が中間電位となるため、電源電圧を制御電圧に用いることが困難となる。このような電源電圧が中間電位である場合にも、出力端子から出力回路内の電源線への電流流入および出力端子の中間電位を抑制し、ハイレベルを出力する課題がある。

### 【 0 0 0 9 】

本発明は、このようなことに鑑みてなされたものであり、半導体回路に供給されている電源供給線が断線した場合に、出力端子から出力回路内の電源線への電流流入および出力端子の中間電位を抑制し、出力インピーダンスを高インピーダンスとして、出力端子電圧を外部回路側で接続している電圧と略等しい電圧とする電子回路およびセンサシステムを提供することにある。

40

### 【課題を解決するための手段】

### 【 0 0 1 0 】

本発明は、上記背景技術及び課題に鑑み、その一例を挙げるならば、電子回路であって、電子回路内の電源線と出力端子との間に設けられた負荷と、負荷と出力端子との間に設けられたトランジスタと、電子回路内の電源線の電源電圧を用いて電流を生成する電流生成回路と、電流生成回路で生成した電流に応じて変化する制御電圧を用いてトランジスタを制御する制御回路を有する。

50

## 【発明の効果】

## 【0011】

本発明によれば、断線検知の精度が向上する電子回路およびセンサシステムを提供できる。

## 【図面の簡単な説明】

## 【0012】

【図1】実施例1におけるセンサシステムの概略構成図である。

【図2】従来の出力回路の概略構成図である。

【図3】従来の出力回路の動作時および電源供給線断線時の動作波形図である。

【図4】実施例1における電子回路の概略構成図である。

10

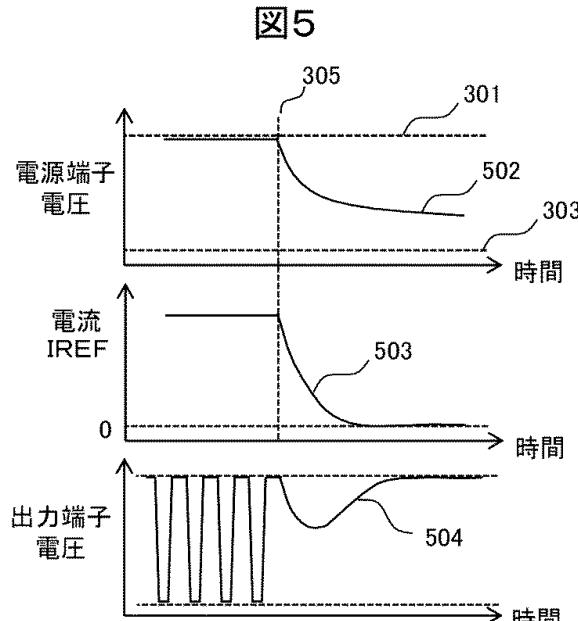

【図5】実施例1における出力回路の動作時および電源供給線断線時の動作波形図である。

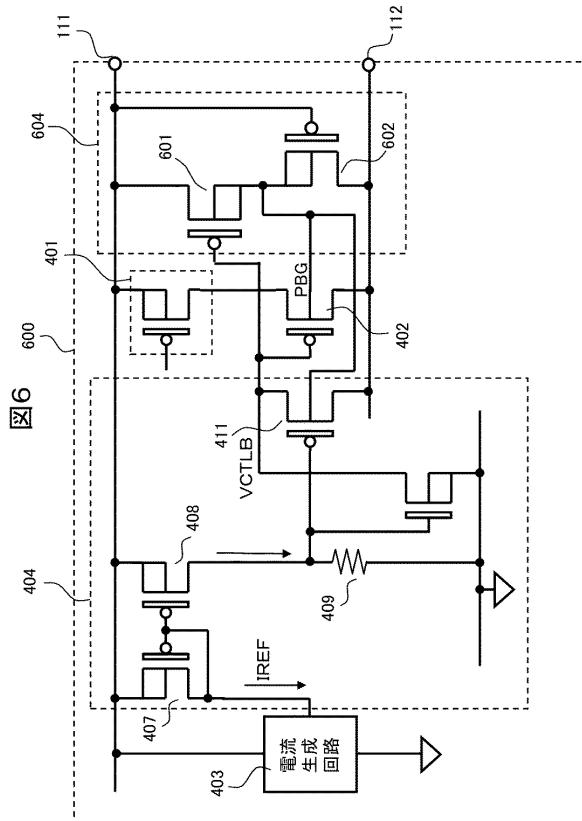

【図6】実施例2における電子回路の概略構成図である。

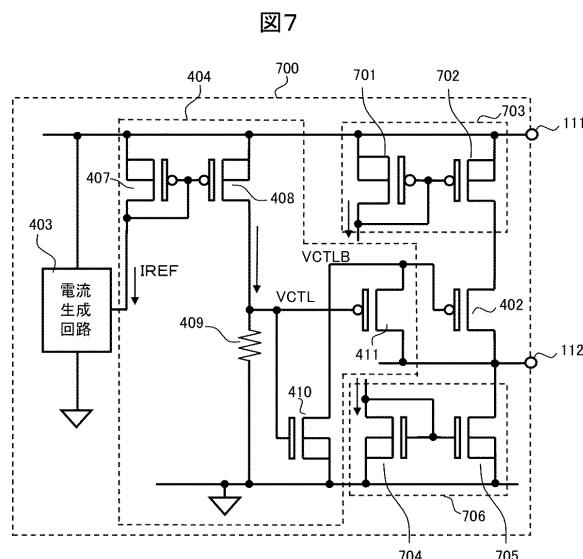

【図7】実施例3における電子回路の概略構成図である。

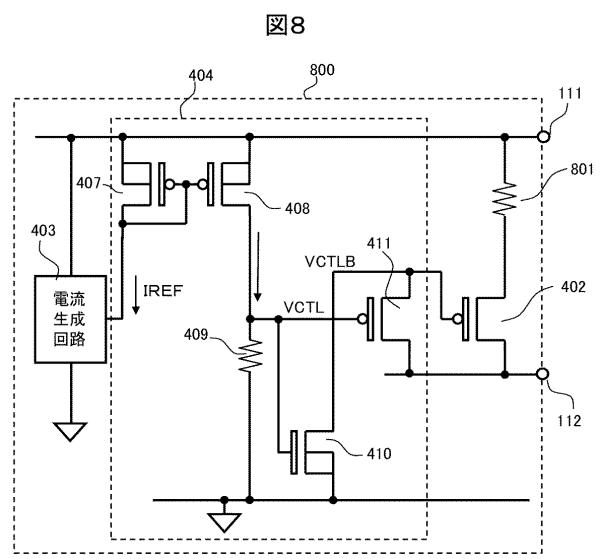

【図8】実施例4における電子回路の概略構成図である。

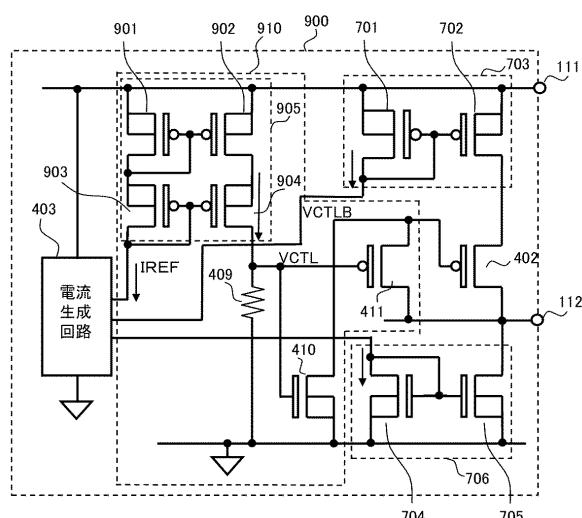

【図9】実施例5における電子回路の概略構成図である。

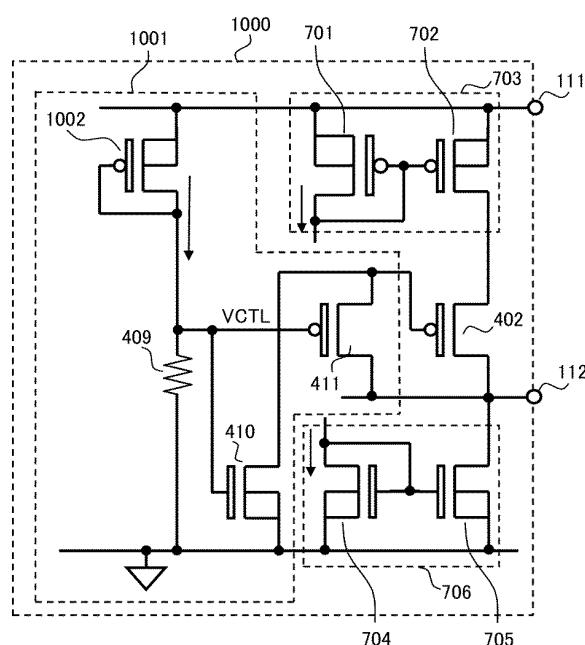

【図10】実施例6における電子回路の概略構成図である。

## 【発明を実施するための形態】

## 【0013】

以下、本発明の実施例について、図面を用いて詳細に説明する。なお、実施例の各機能ブロックを構成する回路素子は、特に制限されないが、公知のCMOS(相補型MOS)トランジスタ等の集積回路技術によって、単結晶シリコンのような半導体基板上に形成される。

20

## 【実施例1】

## 【0014】

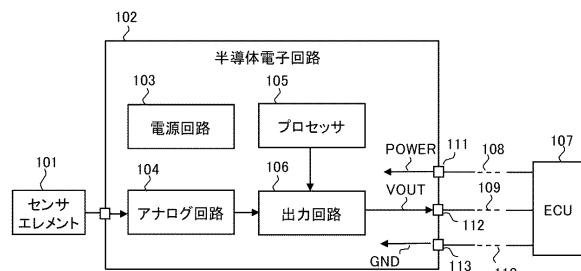

図1は、本実施例におけるセンサシステムの概略構成図である。図1に示すセンサシステムは、例えば、車載用のセンサシステムであり、センサエレメント101と、半導体電子回路102と、ECU107とを備える。

## 【0015】

センサエレメント101は、物理量に応じて電気的特性が変化する素子であり、検出対象の変化に応じた電気信号を出力する。センサエレメント101は、例えば、エンジンが吸入する空気量を測定する素子であるエアフローセンサ等であるが、特に、これに限定されない。すなわち、センサエレメント101は、空気流量、温度、湿度、圧力等の物理量を電気信号に変換して出力する。

30

## 【0016】

半導体電子回路102は、電源回路103と、アナログ回路104と、プロセッサ105と、出力回路106とを有し、例えば、一つの半導体チップで構成される。半導体電子回路102は、主に、センサエレメント101からの電気信号を処理し、その処理結果を出力回路106を介してSENT(Single Edge Nibble Transmission)信号、あるいは周波数変調出力信号等で出力する。なお、アナログ信号電圧として出力する回路もある。

40

## 【0017】

アナログ回路104は、センサエレメント101からの電気信号に対し、増幅、フィルタリング、アナログ/デジタル変換、デジタル/アナログ変換等の処理を行う。プロセッサ105は、デジタルデータの処理や周辺回路のコントロール等を行う。電源回路103は、外部電源から内部電源を生成し、各回路へ分配する。出力回路106は、アナログ回路104、あるいはプロセッサ105からの処理結果を受け、出力端子112および出力配線109を介してECU107へ出力信号(例えばSENT信号)VOUTを出力する。また、ECU107あるいはその他の外部機器から電源供給線108と電源端子111を介して電源POWERを与えられ、グラウンド端子113を介してグラウンドGNDに接続される。なお、110はグラウンド配線である。

50

## 【0018】

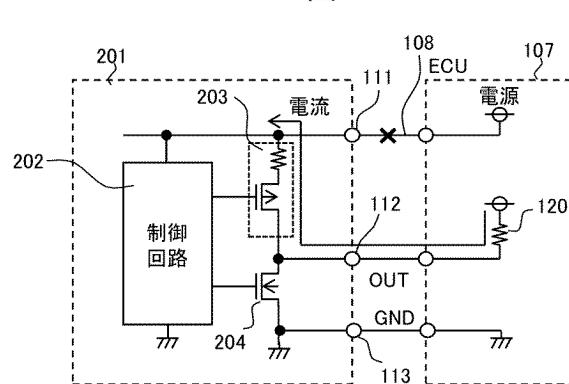

図2は、従来の出力回路の一例である。出力回路201は、制御回路202、負荷203、204、電源端子111、出力端子112により構成される。電源端子111には電源供給線108が接続され、ECUなどの外部から電源が与えられる。また、出力端子112には出力線が接続され、ECUなどの外部コントローラへ出力信号を伝える。この出力線はECUのインターフェース回路において、所定の電圧にプルアップ抵抗120を介して接続される。所定のプルアップ抵抗120は例えば、1k ~ 数10k である。通常の動作時は、センサ信号などを反映させたデータを出力するため、制御回路202により、負荷203および204が制御される。

## 【0019】

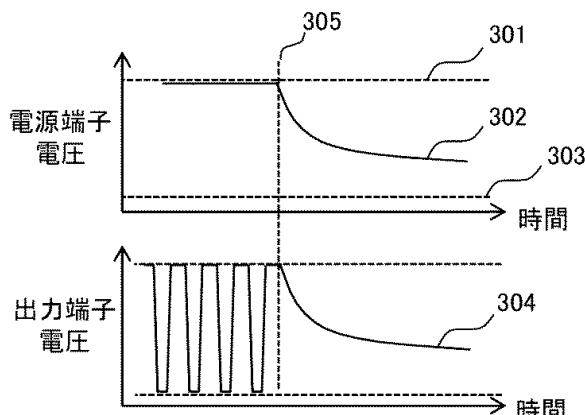

ここで、電源供給線108が外部からの物理的な力や、経年劣化などにより断線する場合が生じる。図3に動作状態から電源供給線が断線した際の電圧波形を示す。図3において、上の波形は電源端子の電圧、下の波形は出力端子の電圧を示し、動作している状態から305のタイミングにて、電源供給線が断線した際の波形を示す。

## 【0020】

電源供給線108が断線した場合には、出力回路201には電源が供給されない状態となる。しかしながら、出力線はECU側でプルアップ抵抗120を介して所定の電圧に接続されているため、図2に示すように、出力端子から負荷を介して出力回路内の電源線に電流が流入する。また、負荷がPMOSFETである場合には、ドレインとバックゲート間の寄生ダイオードを介して電流が流れる場合もある。出力端子の出力抵抗は、出力線を駆動するためやノイズ耐性を強くするため、数10 ~ 1k 程度に設計される。従って、プルアップ抵抗と比較して低抵抗であるため、出力端子電圧は、プルアップされている所定の電圧とはならず、中間電位となる(304)。

## 【0021】

センサ用電子回路には故障時の診断機能が必要である。電源供給線が断線し、センサ電子回路に電源が与えられていない場合には、外部回路により断線している状態であることを認識する必要がある。より具体的には、出力信号をハイレベルとして通常と異なる電位に固定することにより、断線状態を認識することが可能となる。

## 【0022】

ECU側では、電源供給線が断線した場合には、断線状態であることを認識するため、出力端子電圧が所定の電圧であることが求められる。具体的には、出力回路の出力抵抗が高抵抗となり、プルアップ抵抗を接続している電圧に略等しいプルアップ電圧になることが求められる。このプルアップ電圧になることで電源供給線断線状態であることを認識することができるが、上述したように、従来の回路では中間電位となり、電源供給線断線状態であることを認識することができない。

## 【0023】

また、図3に示すように、電源が供給されてセンサ回路が動作していた状態から電源供給線が断線したような場合には、出力回路の電源には電荷が蓄積されているため、電源端子において、電圧が電源電圧(301)からある程度までは下がるもの、接地レベル(303)まで低下するにはかなりの時間を要する。すなわち、電源端子電圧も中間電位の状態となる(302)。ECU側では電源供給線が断線状態であることを認識する必要があるため、電源端子電圧が低下するのを待つことなく、出力端子電圧がハイレベルとなる必要がある。すなわち、電源端子電圧が中間電位となっている状態であっても、電源供給線断線状態であることを認識することが課題である。

## 【0024】

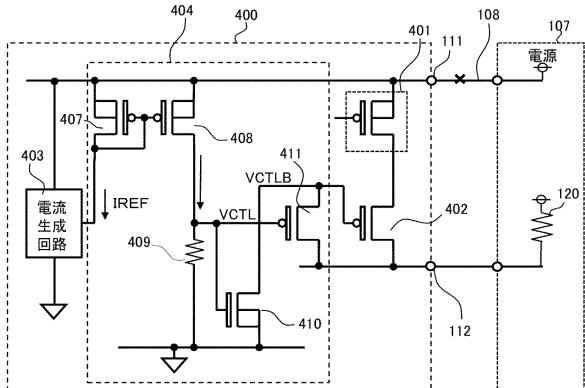

図4は、本実施例における出力回路を搭載した電子回路の概略構成図である。図4において、電子回路400は、負荷401、トランジスタ402、電流生成回路403、電流電圧変換回路404、電源端子111、出力端子112により構成される。また、電流電圧変換回路404は、PMOSFET407、408により構成されるカレントミラーレンジ、プルダウン抵抗409、NMOSFET410、PMOSFET411で構成さ

10

20

30

40

50

れる。

【 0 0 2 5 】

通常の動作時においては、電流生成回路 403 は電源端子 111 からの電力を用いて基準となる電流 IREF を生成する。基準電流はカレントミラー回路によってミラーされ、プルダウン抵抗 409 によって電流を電圧に変換する。動作時の制御信号 VCTL はハイレベルとなる。この電圧は NMOS FET 410 により反転されるため、ローレベルの信号でトランジスタ 402 のゲート電圧を制御するため、トランジスタ 402 はオンとなる。また、PMOS FET 411 はゲート電圧がハイレベルとなるため、オフとなる。従って通常動作時にはトランジスタ 402 をオンに制御し、負荷 401 によって出力線を駆動して出力端子 112 から信号を出力する。

10

【 0 0 2 6 】

次に、電源供給線が断線した場合の動作について説明する。電源供給線 108 が断線した場合には、電子回路は、電源供給線断線部分の電子回路側の容量に蓄積されていた電荷によりある程度の期間動作を継続する。そして、電子回路は、回路により電荷が消費されるため電源電圧が低下していき、電源電圧の低下に伴い、回路が動作できなくなる。出力回路は、回路の動作が止まると、電流の消費量が急激に少なくなる。回路動作が止まるのは、具体的には、電子回路内の電源電圧が、トランジスタが縦積みにされている段数分の閾値電圧付近まで下がった電圧付近である。電流消費が少なくなると、電圧自体はそれ以上下がりにくくなる。

【 0 0 2 7 】

このように電子回路内の電源電圧が下がり、回路動作が止まると、電流生成回路 403 の出力である基準電流 IREF の電流値が減少し、ゼロに近くなる。これに伴い、カレントミラー回路の出力電流も減少し、プルダウン抵抗 409 での電圧降下が小さくなり、制御信号 VCTL はローレベルとなる。そして、NMOS FET 410 のゲート電位がローレベルとなるため、オフとなる。また、PMOS FET 411 がオンとなるため、トランジスタ 402 のゲート電圧は出力端子電圧と略等しい電圧となる。従って、トランジスタ 402 はオフとなり、出力端子 112 から電子回路内の電源線へのインピーダンスが高くなり、出力端子 112 から電子回路内の電源線への電流流入を抑制でき、従って、出力端子 112 の中間電位を抑制可能となる。このため、出力端子 112 の電位は、ECU 107 側でプルアップされている電圧に略等しい電圧となり、電源供給線断線状態であることを認識することができる。すなわち、PMOS FET 411 は、断線時に、トランジスタ 402 のゲート端子と出力端子が接続された配線とを接続するためのスイッチとなる。

20

【 0 0 2 8 】

図 5 は本実施例における電子回路の動作時および電源供給線断線時の動作波形図である。図 5 において、図 3 と同じ機能は同じ符号を付し、その説明は省略する。図 5 において、上の波形は電源端子の電圧、中段の波形は、図 4 における電流 IREF、下の波形は出力端子の電圧を示す。動作時には電源電圧が与えられ、出力信号が出力される。また、基準電流 IREF (503) が生成され、制御電圧 VCTL がハイレベルとなる。電源供給線が断線すると (505)、電源端子電圧は回路の電流消費によって電圧がある程度まで低下する (502)。このため、基準電流 IREF は減少し、ほぼゼロとなる (503)。これに伴い、制御電圧 VCTL がローレベルとなり、トランジスタ 402 がオフになり、出力端子電圧はプルアップ電圧とほぼ等しいハイレベルの電圧となる。

30

【 0 0 2 9 】

このように、電子回路内の電源線に接続された電圧を用いて電流を生成し、該電流により変化する電圧を用いてトランジスタを制御することにより、電源供給線断線時の出力端子の中間電位を抑制でき、出力インピーダンスを高インピーダンス化し、ハイレベル出力とすることができます。また、電流を用いることにより、動作中に電源供給線断線するなどして電源端子電圧がある程度よりも低下しないような場合においても、出力端子をハイレベルとすることができます。

40

50

## 【0030】

このようにして、本実施例における電子回路は、プルダウン抵抗を用いて制御電圧  $V_{C_{T_L}}$  を生成することにより、電源が遮断された状態でも電圧をグラウンドレベルにすることができる。

## 【0031】

なお、本実施例で負荷はトランジスタであるとして説明したが、これに限るものではなく、例えば、抵抗であってもよい。抵抗を負荷にすることにより出力抵抗を出力電圧に依存せず、略一定の抵抗値にすることができる。また、負荷とトランジスタの位置関係はこれに限るものではない。

## 【0032】

なお、回路の動作の必要のないスタンバイ時には、基準電流  $I_{REF}$  を遮断することにより、低消費電力化が可能である。

## 【0033】

次に、電源電圧、カレントミラーの電流値、抵抗値と、その動作について説明するが、一例であるためこれに限るものではない。電源電圧を  $5V$  とする。基準電流  $I_{REF}$ 、ミラーする電流、および、プルダウン抵抗は以下のように設定する。例えば、基準電流  $I_{REF}$  として  $10\mu A$  を用いるとする。ミラー比は  $1:1$  であってもよいし、例えば 4 倍のゲインを持たせて、 $1:4$  としてもよい。ミラー電流を  $40\mu A$  にした場合に、プルダウン抵抗を  $300k$  とすると、プルダウン抵抗に  $40\mu A$  の電流が流れるとすると電圧は  $12V$  となる。実際には電源電圧が  $5V$  であるので、PMOS FET のソースドレイン間電圧が低くなり、非飽和領域に入る。制御電圧は電源電圧に近い  $5V$  弱程度の値となる。すなわち通常動作時には制御電圧は電源電圧とほぼ等しい  $5V$  となる。一方、電源供給線断線時には、電源端子電圧が降下してミラー電流が減少する。NMOS FET の閾値電圧を  $0.9V$  あるとすると電流が  $3\mu A$  程度に減少した時点で、NMOS FET の閾値を下回り、NMOS FET がオフになる。

10

20

## 【0034】

このように、カレントミラーの出力電流とプルダウン抵抗の積が電源電圧よりも十分高くなるように設計することにより、通常動作時に制御電圧をハイレベルとすることができ、トランジスタを確実にオンすることができる。

## 【0035】

電流生成回路 403 は、バンドギャップリファレンス回路を用いて生成するなど、電流として出力する回路を用いる。また、電源端子に与えられている電圧を直接用いるのではなく、レギュレータを使って電圧変換などを行った電圧を電源として電流を生成する回路でもよい。

30

## 【0036】

なお、本実施例の負荷とトランジスタの位置関係は逆であってもよい。すなわち、負荷と電子回路内の電源線の間にトランジスタを設置し、制御を行ってもよい。

## 【0037】

また、電流電圧変換回路 404 はカレントミラーと抵抗を用いる構成を説明したがこれに限るものではない。具体的には、例えば、オペアンプと抵抗を用いた電流電圧変換回路により、制御電圧を生成してもよい。

40

## 【0038】

このように、本実施例によれば、電源端子電圧を用いて生成した電流の変化に応じて変化する制御電圧を用いてトランジスタのオン・オフを制御しているため、電源供給線断線時に適切にトランジスタを制御可能となり、そのため、断線が生じている際にハイレベルの電位の出力が可能になり、断線検知の精度が向上する回路を提供可能である。

## 【実施例 2】

## 【0039】

図 6 は、本実施例における出力回路を搭載した電子回路の概略構成図である。図 6 において、図 4 と同じ機能は同じ符号を付し、その説明は省略する。図 6 において、電子回路

50

600は、負荷401、トランジスタ402、電流生成回路403、電流電圧変換回路404、電源端子111、出力端子112、基板制御回路604で構成される。基板制御回路604はPMOS FET601、602で構成される。トランジスタ402をPMOS FETで構成すると、ドレイン端子とバックゲート端子間、および、ソース端子とバックゲート端子間には寄生ダイオードが存在する。従って、寄生ダイオードがオンして電流が流れることを防ぐには、トランジスタ402のバックゲート端子を高い電位に接続する必要がある。具体的には、トランジスタ402のバックゲート端子は、動作時には電源電圧に、電源供給線断線時には出力端子の出力電圧に接続するように制御する。動作時には、制御電圧VCTLBがローレベルであるため、PMOS FET601をオンにし、トランジスタ402のバックゲート端子を電源電圧に接続し、電源電圧に保つ。また、電源供給線断線時には、出力端子電圧が電源電圧よりも高くなるため、PMOS FET601をオフにし、PMOS FET602をオンにし、トランジスタ402のバックゲート端子電圧を出力端子電圧と接続する。

#### 【0040】

また、トランジスタ402のゲート電圧は、電子回路内の電源線からの電力を用いて電流を生成する電流生成回路403の電流を用い、電流電圧変換回路404による電流電圧変換を行った電圧を用いて制御を行う。このように、トランジスタ402のバックゲート端子電圧を制御するとともに、ゲート電圧を電流生成回路403、電流電圧変換回路404を経由した電圧を用いて制御することにより、電源供給線断線時に出力端子の電子回路を高インピーダンス状態にし、ハイレベルを出力するよう制御することができる。

#### 【実施例3】

#### 【0041】

図7は、本実施例における出力回路を搭載した電子回路の概略構成図である。図7において、図4と同じ機能は同じ符号を付し、その説明は省略する。図7において、電子回路700は、負荷703、706、トランジスタ402、電流生成回路403、電流電圧変換回路404、電源端子111、出力端子112で構成される。負荷703、706は出力を定電流駆動とするカレントミラー回路である。出力用のカレントミラー回路は、シンク側は負荷706として、NMOS FET704および705で構成され、ソース側は負荷703として、PMOS FET701および702で構成される。シンク側とソース側それぞれにカレントミラー回路を設け、出力信号の立ち上がり、立下りを一定電流駆動で駆動する。定電流出力とすることにより、出力負荷を適切に駆動できる。例えば、数mAから10mA程度の電流で駆動する。出力信号の振幅を5V、出力電流を5mAとすると、電位差が5Vである場合の出力抵抗は1kΩとなる。また、例えば電位差が1Vである場合の出力抵抗は200Ωとなる。この出力抵抗の値はブルアップ抵抗と比べて小さい。従って、電源供給線断線時にはトランジスタ402をオフないし高インピーダンスの状態にする必要がある。電流生成回路403で電流を生成し、電流電圧変換回路404で電流電圧変換を行い、トランジスタ402のゲート電圧を制御することにより、動作時はトランジスタ402をオンに制御して低出力インピーダンスの状態とし、電源供給線断線時にはトランジスタ402をオフに制御して高出力インピーダンスの状態とする。このようにして電源供給線断線時に出力端子への電流流入を抑制し、ハイレベル出力が可能となる。

#### 【実施例4】

#### 【0042】

図8は、本実施例における出力回路を搭載した電子回路の概略構成図である。図8において、図4と同じ機能は同じ符号を付し、その説明は省略する。図8において、図4と異なる点は、負荷801が抵抗である点である。このように、負荷は、トランジスタのようなアクティブ素子でなくても抵抗のような受動素子でもよい。また、トランジスタと抵抗を組み合わせたような構成でもよい。

#### 【実施例5】

#### 【0043】

10

20

30

40

50

図9は、本実施例における出力回路を搭載した電子回路の概略構成図である。図9において、図7と同じ機能は同じ符号を付し、その説明は省略する。図9において、図7と異なる点は、電流電圧変換回路910はカスコード接続されたカレントミラー回路905で構成される点である。具体的には、カレントミラー回路905は、PMOS FET901、902、903、904により構成される。カスコード接続により電源電圧が低下した際に、PMOS FETが非飽和領域での動作になりやすくなり、早い段階でミラーされた電流が減少し、プルダウン抵抗によって制御電圧VCTLの電位が下がる。これに伴って制御電圧VCTLBによってトランジスタ402のゲート電圧が制御され、オフになる。

#### 【0044】

10

このようにカレントミラー回路をカスコード接続にすることで、縦積みの段数が多くなり、電源供給線断線時に電源端子電圧が下がった際に確実に電流を遮断し、ハイレベル出力をすることができる。カレントミラー回路により、電流生成回路403の電流供給能力よりも、早く電流を遮断することにより、出力端子から電子回路内の電源線に回り込んだ電流により電流生成回路が動作することを防ぐことができる。

#### 【実施例6】

#### 【0045】

20

図10は、本実施例における出力回路を搭載した電子回路の概略構成図である。図10において、図7と同じ機能は同じ符号を付し、その説明は省略する。図10において、電子回路1000は、負荷703、706、トランジスタ402、制御電圧生成回路1001で構成される。電源供給線断線時に電源端子電圧が落ちない場合であっても、ダイオード接続されたPMOS FET1002によって電位を落として制御に用いることで、制御電圧VCTLの電位をNMOS FET410の閾値電圧よりも低い電圧にすることができる。このため、電源供給線断線時に電源端子電圧が低下しない場合であっても、トランジスタ402のゲート電圧を制御でき、トランジスタ402をオフにして出力端子電圧の中間電位を抑制できる。

#### 【0046】

なお、この素子はPMOS FETに限るものではなく、定電圧ダイオードなどを用いてもよい。あるいは、抵抗を用い、電源電圧を分圧した電圧を用いて制御を行ってよい。

#### 【0047】

30

以上実施例について説明したが、本発明は上記した実施例に限定されるものではなく、様々な変形例が含まれる。例えば、上記した実施例は本発明を分かりやすく説明するために詳細に説明したものであり、必ずしも説明した全ての構成を備えるものに限定されるものではない。また、ある実施例の構成の一部を他の実施例の構成に置き換えることが可能であり、また、ある実施例の構成に他の実施例の構成を加えることも可能である。また、各実施例の構成の一部について、他の構成の追加、削除、置換をすることが可能である。

#### 【符号の説明】

#### 【0048】

101：センサエレメント、102：半導体電子回路、103：電源回路、104：アナログ回路、105：プロセッサ、106、201：出力回路、400、600、700、800、900、1000：電子回路、107：ECU、108：電源供給線、109：出力配線、110：グラウンド配線、111：電源端子、112：出力端子、113：グラウンド端子、202：制御回路、203、204、401、703、706、801：負荷、402：トランジスタ、403：電流生成回路、404、910：電流電圧変換回路、407、408、411、601、602、701、702、901、902、903、904、1002：PMOS FET、409：プルダウン抵抗、410、704、705：NMOS FET、604：基板制御回路、905：カレントミラー回路、1001：制御電圧生成回路

40

50

## 【図面】

## 【図 1】

図1

## 【図 2】

図2

## 【図 3】

図3

## 【図 4】

図4

10

20

30

40

50

【図5】

【 四 6 】

【図7】

【 四 8 】

【図9】

図9

【図10】

図10

10

20

30

40

50

---

フロントページの続き

内

審査官 及川 尚人

- (56)参考文献

- 特開平06-208693 (JP, A)

- 特開2010-216996 (JP, A)

- 特開2008-029067 (JP, A)

- 再公表特許第2017/169057 (JP, A1)

- 特開2004-294069 (JP, A)

- 特開2005-252968 (JP, A)

- (58)調査した分野 (Int.Cl., DB名)

- H03K 17/00 - 17/70

- G01R 31/50