(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5346520号

(P5346520)

(45) 発行日 平成25年11月20日(2013.11.20)

(24) 登録日 平成25年8月23日(2013.8.23)

(51) Int.Cl.

F 1

G09G 3/30 (2006.01)

H01L 51/50 (2006.01)

G09G 3/20 (2006.01)G09G 3/30 K

G09G 3/30 J

H05B 33/14 A

G09G 3/20 641 A

G09G 3/20 624 B

請求項の数 7 (全 19 頁) 最終頁に続く

(21) 出願番号

特願2008-208614 (P2008-208614)

(22) 出願日

平成20年8月13日(2008.8.13)

(65) 公開番号

特開2010-44250 (P2010-44250A)

(43) 公開日

平成22年2月25日(2010.2.25)

審査請求日

平成23年7月6日(2011.7.6)

(73) 特許権者 502356528

株式会社ジャパンディスプレイ

東京都港区西新橋三丁目7番1号

(74) 代理人 100083552

弁理士 秋田 収喜

(74) 代理人 100103746

弁理士 近野 恵一

(73) 特許権者 506087819

パナソニック液晶ディスプレイ株式会社

兵庫県姫路市飾磨区妻鹿日田町1-6

(74) 代理人 100083552

弁理士 秋田 収喜

(74) 代理人 100103746

弁理士 近野 恵一

最終頁に続く

(54) 【発明の名称】 画像表示装置

(57) 【特許請求の範囲】

## 【請求項 1】

自発光素子を有する画素をマトリクス状に設けた表示領域と、

前記自発光素子の陽極である第一電極に供給される第一電源電圧を生成する陽極電源部と、

前記自発光素子の陰極である第二電極に供給される第二電圧を生成する陰極電源部と、リセット線が接続する走査線駆動回路と、

画像信号と、発光時間の制御を行う信号を供給する信号線駆動回路とを有し、

画素容量の第一電極がゲート電極に接続され、前記第一電源電圧がソース電極に入力され、前記自発光素子の第一電極がドレイン電極に接続された駆動トランジスタと、

前記駆動トランジスタのゲート電極とドレイン電極間に、ソース電極とドレイン電極が接続されたりセットスイッチ素子を有し、

前記自発光素子の第二電極には前記第二電圧が入力され、

前記リセットスイッチ素子のゲート電極には前記リセット線が接続され、

1フレーム期間内に前記各画素に前記画像信号を書き込む書き込み期間と、前記自発光素子を発光させる発光期間とを有し、

前記書き込み期間に、前記画像信号を前記画素容量の第二電極に入力し、前記発光期間に、前記全画素の前記リセットスイッチ素子をオフとして、前記発光時間の制御を行う信号を前記画素容量の第二電極に入力する画像表示装置であって、

輝度モード制御回路で制御される2つ以上の輝度表示モードを有し、

10

20

前記輝度表示モードには、前記発光期間における前記発光時間の制御を行う信号の波形を台形波形として高輝度で表示する第一の輝度表示モードと、前記発光期間における前記発光時間の制御を行う信号の波形を前記第一の輝度表示モードよりも放物線波形に近い波形として低輝度で表示する第二の輝度表示モードを有することを特徴とする画像表示装置。

【請求項 2】

前記第一の輝度表示モードでは前記駆動トランジスタが飽和領域で前記自発光素子を発光させ、前記第二の輝度表示モードでは前記駆動トランジスタは非飽和領域で前記自発光素子を発光させることを特徴とする請求項 1 に記載の画像表示装置。

【請求項 3】

前記第二の輝度表示モードにおける前記発光時間の制御を行う信号の波形は、複数の変極点を有する多角形であることを特徴とする請求項 1 に記載の画像表示装置。

【請求項 4】

前記第二の輝度表示モードにおける前記発光時間の制御を行う信号の波形は、複数の変極点を有する放物線波形であることを特徴とする請求項 3 に記載の画像表示装置。

【請求項 5】

前記発光時間の制御を行う信号の波形は、各画素における前記自発光素子の発光色によって波形が異なることを特徴とする請求項 1 に記載の画像表示装置。

【請求項 6】

前記輝度表示モードには、前記発光期間における前記発光時間の制御を行う信号の波形の形状が異なる複数の輝度表示モードを有することを特徴とする請求項 1 に記載の画像表示装置。

【請求項 7】

前記輝度表示モードは、外光の明るさを検出して自動的に選択可能であることを特徴とする請求項 1 に記載の画像表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像表示装置に係り、特に、有機 E L 素子などを用いた有機 E L 表示装置に適用して有効な技術に関する。

【背景技術】

【0002】

従来表示装置の主流であった C R T に代わり、近年、フラットディスプレイ装置の需要が増大している。特に、有機 E L (Electro Luminescence) 素子 (O L E D ; Organic Light Emitting Diode) を用いた有機 E L 表装置は、消費電力、軽さ、薄さ、動画特性、視野角などの点で優れており、開発、実用化も進んでいる。

有機 E L 表示装置は、例えば、下記特許文献 1、特許文献 2、特許文献 3 に記載されている。

前述の特許文献 1 には、発光期間内に P W M 信号として三角波波形の信号を使用すること、および、この三角波波形信号は、様々な変更が可能であり、例えば、発光の時間軸重心が発光階調に依存しないように左右対象の三角波波形、非対称の三角波波形や、ガンマ特性変調に相当する非直線の三角波波形、複数の三角波波形などを用いてそれぞれ異なる視覚特性を得ることが記載されている。

また、前述の特許文献 2 には、判断回路の判断結果に基づいて、複数の輝度モードのうちの 1 つを選択する選択回路を備える電気光学装置が記載されている。この特許文献 2 では、低輝度部でつぶれを生じた場合などには、ガンマ補正電圧などの基準電位を調整してガンマカーブを適宜変更することにより、低輝度部で階調差を判別し易くすることができる。なお、このような処理は、例えば、ガンマ基準用電源回路を制御信号に応じて接続 / 非接続を切り替え可能な抵抗を組み込んでおくとともに、最大輝度を低下させる場合に主制御回路が先の制御信号を出力するようにプログラミングしておくことなどにより自動的

10

20

30

40

50

に実施することができる、或いは、ユーザの入力操作に応じて先の処理が実施されるよう構成してもよいと記載されている。

また一般に、アクティブ・マトリクス型有機EL表示装置(AM-OLED)に使用される赤、緑、青に発光する各有機EL素子は、発光特性(発光輝度、電圧-電流特性、電圧-発光輝度特性等)が、各色毎に異なっている。この赤、緑、青の各有機EL素子の発光特性のバラツキも、表示画面上では、前述したような微細なムラとなって見えることになる。

この赤、緑、青の各有機EL素子の発光特性のバラツキによる表示不均一を抑制するために、例えば、前述の特許文献3には、赤、緑、青の各有機EL素子に供給するR・G・Bのそれぞれの映像信号に対して、ガンマ補正するメモリを設け、R・G・B毎にガンマ補正值を変更する手法が記載されている。10

#### 【0003】

なお、本願発明に関連する先行技術文献としては以下のものがある。

【特許文献1】特開2003-5703号公報

【特許文献2】特開2005-316110号公報

【特許文献3】特開2001-92413号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0004】

有機EL表示装置は、複数の輝度表示モード(所謂、複数の発光輝度設定)が必要とされる場合があったが、輝度表示モードを切り替えるために陽極電源の電圧を制御することにより変動した階調特性を、PWM信号の変曲点を所定の階調特性に合わせて規定することは、前述の各特許文献には記載されていない。20

また、引用文献2、引用文献3では、ガンマ補正するために、A/D変換器と、D/A変換器と、補正メモリとを必要とし、構成が複雑でコストがかかるという問題点がある。その上、引用文献3では、各画素間の輝度バラツキなどの局所的な特性のバラツキについては考慮されておらず、この引用文献3では、各画素間の輝度バラツキなどの局所的な特性のバラツキを解消することは不可能である。

本発明は、前記従来技術の問題点を解決するためになされたものであり、本発明の目的は、EL素子のような電流駆動型発光素子を有する画像表示装置において、従来よりも駆動回路の構成が簡単で、しかも、発光輝度のバランスをとりつつ高輝度から低輝度まで広範囲に亘る赤、緑、青の各画素の発光輝度を制御することが可能となる技術を提供することにある。30

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述及び添付図面によって明らかにする。

#### 【課題を解決するための手段】

#### 【0005】

(1) 自発光素子を有する画素を含む画素マトリクスと、画素電源電圧を生成する画素電源電圧生成回路と、自発光素子印加電圧を生成する自発光素子印加電圧供給回路と、画素マトリクス駆動信号を生成する画素マトリクス駆動信号生成回路と、画像信号を生成する画像信号生成回路と、画素駆動信号を生成する画素駆動信号生成回路とを有し、画素容量の第一電極がゲート電極に接続され、前記画素電源電圧がソース電極に入力され、前記自発光素子の第一電極がドレイン電極に接続された駆動トランジスタと、前記駆動トランジスタのゲート電極とドレイン電極間に、ソース電極とドレイン電極が接続されたリセットスイッチトランジスタを有し、前記自発光素子の第二電極には前記自発光素子印加電圧が入力され、前記リセットスイッチトランジスタのゲート電極には前記画素マトリクス駆動信号が入力され、1フレーム期間内に前記各画素に前記画像信号を書込む書込み期間と発光期間とを有し、書込み期間に、前記画像信号を前記画素容量の第二電極に入力し、前記発光期間に、前記全画素の前記リセットスイッチトランジスタをオフとして、前記画素駆動信号を前記画素容量の第二電極に入力する画像表示装置であって、輝度モード制御回路40

50

で制御される 2 つ以上の輝度表示モードを有し、前記輝度表示モードには、前記発光期間における前記画素駆動信号波形を直流電圧波形とする第一の輝度表示モードと、前記発光期間における前記画素駆動信号波形を変動電圧波形とする第二の輝度表示モードを有する。

#### 【0006】

(2) (1)において、前記第一の輝度表示モードと、前記第二の輝度表示モードとで、画素電源電圧が異なる。

(3) (1)において、前記画像信号生成回路と前記画素駆動信号生成回路とは、同一の回路で共用する。

(4) (1)において、前記第一の輝度表示モードでは前記駆動トランジスタが飽和領域で前記自発光素子を発光させ、前記第二の輝度表示モードでは前記駆動トランジスタは非飽和領域で前記自発光素子を発光させる。

10

(5) (1)において、前記第二の輝度表示モードにおける前記画素駆動信号波形は、複数の変極点を有する多角形である。

(6) (5)において、前記第二の輝度表示モードにおける前記画素駆動信号波形は、複数の変極点を有する放物線波形である。

(7) (1)において、前記第二の輝度表示モードにおける前記画素駆動信号波形は、概略放物線波形である。

#### 【0007】

(8) (1)において、前記画素駆動信号波形は、各画素における前記自発光素子の発光色によって波形が異なる。

20

(9) (1)において、前記第一の輝度表示モードにおける前記画素駆動信号波形は、矩形波である。

(10) (1)において、前記第一の輝度表示モードにおける前記画素駆動信号波形は、台形波である。

(11) (1)において、前記輝度表示モードには、前記発光期間における前記画素駆動信号波形が変動電圧波形であり、前記変動電圧波形の形状が異なる複数の輝度表示モードを有する。

(12) (1)において、前記輝度表示モードには、前記発光期間における前記画素駆動信号波形が変動電圧波形であり、前記変動電圧波形の周期が異なる複数の輝度表示モードを有する。

30

(13) (1)において、前記輝度表示モードは、外光の明るさを検出して自動的に選択可能である。

#### 【発明の効果】

#### 【0008】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記の通りである。

本発明によれば、EL 素子のような電流駆動型発光素子を有する画像表示装置において、従来よりも駆動回路の構成が簡単で、しかも、発光輝度のバランスをとりつつ高輝度から低輝度まで広範囲に亘る赤、緑、青の各画素の発光輝度を制御することが可能となる。

40

#### 【発明を実施するための最良の形態】

#### 【0009】

以下、図面を参照して本発明の実施例を詳細に説明する。

なお、実施例を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。

#### [本発明の前提となる有機 EL 表示装置の概要]

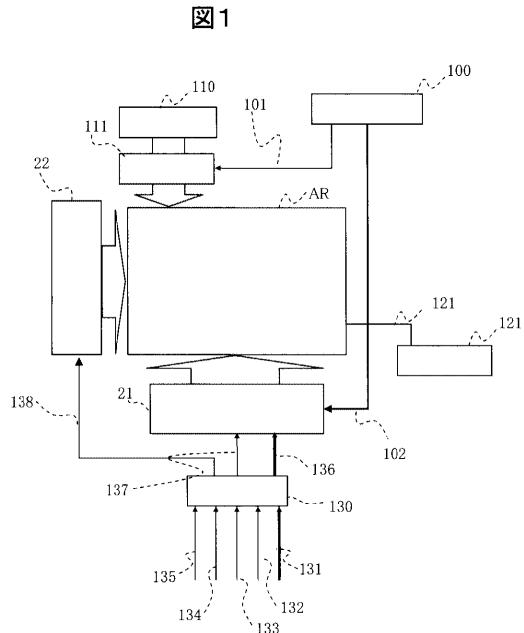

図 1 は、本発明の前提となる有機 EL 表示装置の概略構成を示すブロック図である。

図 1 において、A R は表示部、2 1 は信号線駆動回路、2 2 は走査線駆動回路、1 0 0 は輝度モード制御部、1 1 0 は陽極電源部、1 1 1 は電源制御部、1 3 0 は表示制御部である。

50

131は外部から入力される映像デジタル信号である映像データ信号であり、画像の各画素の濃淡値を表す信号である。132は垂直同期信号（VSYNC）であり、表示一画面周期（1フレーム）の信号で映像データ信号の1フレーム分の始まりを示す信号である。

133は水平同期信号（Hsync）であり、一水平周期の信号で表示データデジタル信号の1水平ライン分の始まりを示す信号である。134はデータタイネーブル信号であり、映像データ信号が有効である期間を示す信号である。

映像データ信号131、垂直同期信号132、水平同期信号133、データタイネーブル信号134は全てデータ同期クロック135に同期して入力される。

本実施例では、映像データ信号131は、一画面分が左上端の画素から順次ラスタスキヤン形式で転送されるものとして以下説明する。 10

#### 【0010】

表示制御部130は、有機EL表示装置全体をコントロールする部分で、外部から入力される映像データ信号131、垂直同期信号132、水平同期信号133、データタイネーブル信号134、および、データ同期クロック135に応じて、所定のタイミングで表示データ136、信号線駆動回路制御信号137、走査線駆動回路制御信号138を出力する。

信号線駆動回路21は、信号線駆動回路制御信号137によって制御され、信号線を介して表示部内の各画素にアナログ信号で画像信号を書き込む。

走査線駆動回路22は、走査線駆動回路制御信号138によって制御され、リセット線15と点灯スイッチ線19とを介して表示部ARに書き込み選択信号を送る。 20

陽極電源部110は有機EL素子の陽極側の電源である。陽極電源部110は、有機EL素子7が発光するために必要な電力を表示部ARに供給する。

輝度モード制御部100は、外部から設定され、輝度モード制御部100は、電圧制御信号101を電源制御部111に、発光期間制御信号102を信号線駆動回路21に出力する。

電源制御部111は各種の輝度表示モードに応じて、予め規定した有機EL素子の駆動電圧を表示部ARに供給する。なお、輝度モード制御部100は、外光の明るさに応じて、自動的に2つ以上の輝度表示モードの中の所定の輝度表示モードを選択するようにしてもよい。 30

信号線駆動回路21は、有機EL表示装置に入力される画像信号の階調に対する実際の表示輝度（即ち、階調特性）を制御する。陰極電源部120は表示部内の各画素の有機EL素子の陰極側に陰極電源線121を介して接続されている。

#### 【0011】

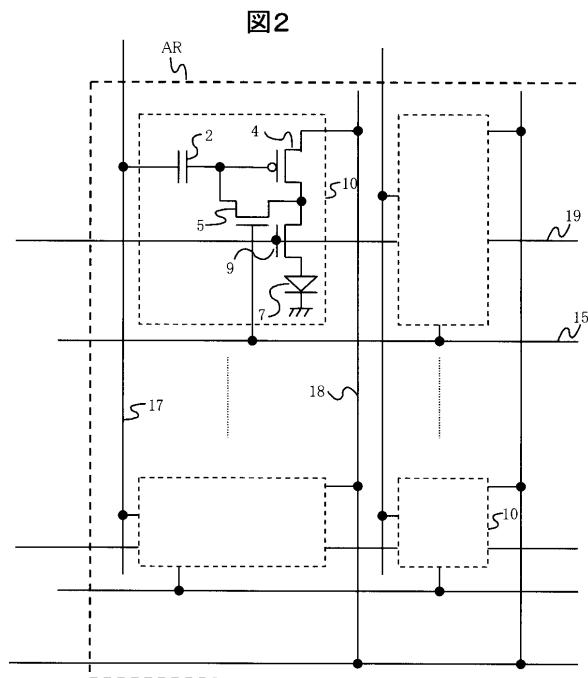

図2は、図1に示す有機EL表示装置の表示部ARの全体構成を示す図である。図2に示すように、有機EL表示パネルの表示領域内には複数の画素10がマトリクス状に設けられる。

画素10には、信号線17、リセット線15、点灯スイッチ線19、および電源線18がそれぞれ入力される。リセット線15、および、点灯スイッチ線19は、走査線駆動回路22に接続される。 40

信号線17には、信号線駆動回路21から、画像信号とPWM信号が入力される。

また、実際には画素10は、有機EL表示パネルの表示領域内に多数個配置されるが、図面の簡略化のために図1では、4画素のみを記載してある。

各画素10には、発光素子としての有機エレクトロルミネッセンス素子（以下、有機EL素子という。）7が設けられており、有機EL素子7のカソード電極は陰極電源線121に接続される。

また、アノード電極は、n型薄膜トランジスタで構成される点灯スイッチ素子9と、p型薄膜トランジスタ（以下、駆動TFTという。）4を介して電源線18に接続される。

また、駆動TFT4のゲート電極とソース電極との間には、容量素子2が接続され、駆動TFT4のドレイン電極とゲート電極との間には、薄膜トランジスタで構成されるリセ 50

ツトスイッチ素子 5 が設けられる。

なお、リセットスイッチ素子 5 のゲート電極は、リセット線 15 に接続される。また、点灯スイッチ素子 9 のゲート電極は、点灯スイッチ線 19 に接続される。

画素 10、走査線駆動回路 22、信号線駆動回路 21 等の各回路は全て、半導体層として、一般に良く知られている低温多結晶シリコン層を有する低温多結晶シリコン薄膜トランジスタを用いて構成され、これらの薄膜トランジスタは、ガラス基板上に形成される。

また、低温多結晶シリコン薄膜トランジスタ、あるいは、有機 E L 素子 7 の製造方法などに関しては、一般に報告されているものと大きな相違はないため、ここではその説明は省略する。

#### 【 0 0 1 2 】

10

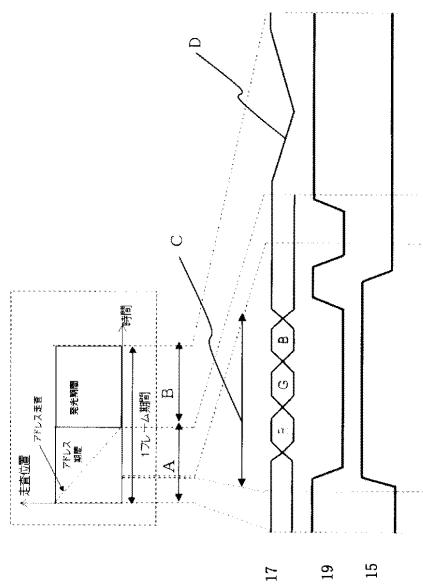

図 3 は、本発明の前提となる有機 E L 表示装置の動作を説明するためのタイミングチャートである。

図 3 に示すように、本実施例の前提となる有機 E L 表示装置では、各画素は、1 フレーム期間内に、書き込み期間（図 3 の A の期間）と発光期間（図 3 の B の期間）とを有し、書き込み期間に各画素 10 に画像信号を書き込み、発光期間に点灯して表示を行う。

画像信号の書き込みは、1 表示ライン単位、即ち、リセット線 15 毎に行なわれる。ここで、本実施例の有機 E L 表示装置の表示部 AR の画素数は、 $640 \times 480 \times 3$  画素となっているため、リセット線 15 は、垂直方向に第 1 リセット線から第 480 リセット線まで 480 本並び、信号線 17 は、R・G・B の各画素毎に、水平方向に第 1 信号線、第 2 信号線から、第 640 信号線まで 640 本並んでいるものとして、以下説明する。

さらに、電源線 18 は、R・G・B の各画素毎に、水平方向に第 1 電源線、第 2 電源線から、第 640 電源線まで 640 本並んでいるものとして、以下説明する。

以下、本実施例の有機 E L 表示装置の前提となる駆動方法の各期間の動作について説明する。

#### 【 0 0 1 3 】

##### [ 書込み期間 ]

書き込み期間においては、図 3 の C に示すように、走査線駆動回路 22 が、1 表示ライン単位に各行の複数の画素 10 を順次走査し、これと同期して、信号線駆動回路 21 から画像信号を信号線 17 に書き込む。

以下、走査線駆動回路 22 によって選択された、任意の表示ラインの画素 10 の「書き込み期間」における動作について説明する。

書き込み期間内に、信号線駆動回路 21 から信号線 17 に、画像電圧が供給される。

始めに、リセット線 15 と点灯スイッチ線 19 とが High レベル（以下、H レベル）となるので、リセットスイッチ素子 5 と点灯スイッチ素子 9 とがオンとなり、これにより、駆動 TFT 4 はゲート電極とドレイン電極とが接続されたダイオード接続になる。

次に、点灯スイッチ線 19 が Low レベル（以下、L レベル）となり、点灯スイッチ素子 9 がオフすると、駆動 TFT 4 と有機 E L 素子 7 とは強制的に電流オフ状態になるが、このとき、駆動 TFT 4 のゲート電極とドレイン電極はリセットスイッチ素子 5 で短絡されているため、容量素子 2 の一端でもある、駆動 TFT 4 のゲート電極の電圧は、電源線 18 の電圧（Vdd）よりしきい値電圧（Vth）だけ低い電圧（Vdd - Vth）に自動的にリセットされる。なお、このとき、前述したように、容量素子 2 の他端には、信号線 17 から画像信号が入力されている。

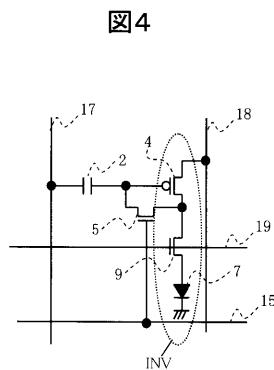

即ち、図 4 に示すように、駆動 TFT 4 と有機 E L 素子 7 とで構成される駆動インバータ（INV）の入出力が短絡されることとなり、各々の画素の駆動インバータ（INV）を構成する駆動 TFT 4 の特性に従った基準電圧（Vref）が設定され、この基準電圧を基準として、信号線 17 からの映像電圧を容量素子 2 に蓄積する。

駆動インバータ（INV）は、書き込み期間後の発光期間に入力される三角波波形の PWM 信号が、容量素子 2 に蓄積された画像電圧より高いときは、有機 E L 素子 7 をオフ状態とし、書き込み期間後の発光期間に入力される三角波波形の PWM 信号が、容量素子 2 に蓄積された画像電圧より低いときは有機 E L 素子 7 をオン状態とすることによって、画像電圧に

20

30

40

50

従った有機 E L 素子 7 の発光時間制御を行う。

【 0 0 1 4 】

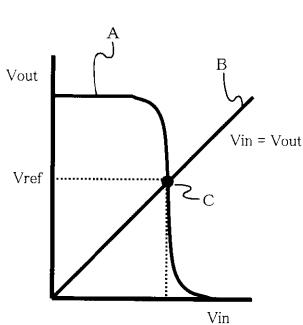

図 5 は、図 4 に示した駆動インバータ ( I N V ) における信号電圧の基準電圧の設定を説明するための図である。

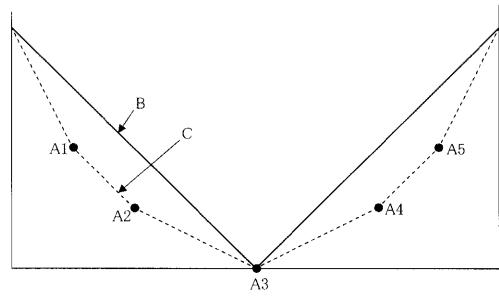

図 5 において、A は駆動インバータ ( I N V ) の入出力特性を、また B は入出力短絡条件を示し、A に示す曲線と B に示す直線の交叉点 C は駆動インバータ ( I N V ) の画像電圧書き込み基準電位 ( V r e f ) である。

駆動 T F T 4 は、画像信号の書き込み時に出入力が短絡されるため、入力、出力の電位は、入出力特性と、 $V_{i n} = V_{o u t}$  の直線で示す入出力短絡条件の交点 C である画像電圧書き込み基準電位 ( V r e f ) となる。画像電圧の書き込みはこの信号電圧書き込み基準電位 ( V r e f ) を基準として行われる。 10

【 0 0 1 5 】

[ 発光期間 ]

発光期間においては、走査線駆動回路 2 2 は停止し、リセット線 1 5 が L レベル、点灯スイッチ線 1 9 が H レベルとなるので、全画素のリセットスイッチ素子 5 がオフ、点灯スイッチ素子 9 が一斉にオンとなる。

このとき、信号線 1 7 には、信号線駆動回路 2 1 から、図 3 の D に示す三角波波形の P W M 信号が入力される。

そして、三角波波形の P W M 信号が、容量素子 2 に蓄積された画像電圧より高いときは、有機 E L 素子 7 がオフ状態となり、三角波波形の P W M 信号が、容量素子 2 に蓄積された画像電圧より低いときは有機 E L 素子 7 をオン状態となる。 20

なお、本実施例では、駆動 T F T 4 と有機 E L 素子 7 が点灯スイッチ素子 9 を介して接続されていたが、点灯スイッチ素子 9 がなくても同様の効果は得られる。

また、走査線駆動回路 2 2 、信号線駆動回路 2 1 等からなる周辺駆動回路は、低温多結晶シリコン ( ポリシリコン ) 薄膜トランジスタ回路で構成しているが、これらの周辺駆動回路あるいはその一部分を単結晶 L S I ( Large Scale Integrated circuit ) 回路で構成して実装するようにしてもよい。その場合に、駆動 T F T 4 、リセットスイッチ素子 5 、および、点灯スイッチ素子 9 等は、それぞれ半導体層にアモルファスシリコンを用いるアモルファスシリコン薄膜トランジスタを用いてガラス基板上に構成するようにしてもよい。 30

【 0 0 1 6 】

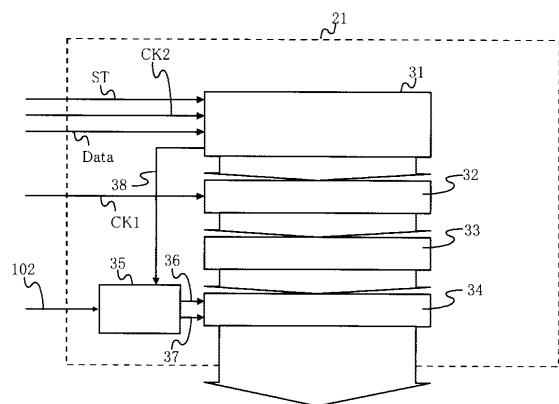

図 6 は、図 1 に示す信号線駆動回路 2 1 の内部構成を示す概略ブロック図である。

図 6 において、データシフト手段 3 1 は、データクロック C K 2 に従い、一ライン分の表示入力シリアルデータ D a t a ( 図 1 の表示データ 1 3 6 ) を、データスタート信号 S T を取り込み開始の基準として一水平期間中に取り込み、シフトデータとして出力する。

1 ラインラッチ手段 3 2 は、シフトデータを 1 ライン分ラッチし、水平ラッチクロック C K 1 に同期して 1 ラインラッチデータとして出力する。

なお、データクロック C K 2 、データスタート信号 S T 、および、水平ラッチクロック C K 1 は、図 1 に示す信号線駆動回路制御信号 1 3 7 に含まれる信号である。また、一ライン分の表示入力シリアルデータ D a t a は、図 1 の表示データ 1 3 6 に相当する。 40

階調電圧選択手段 3 3 は、1 ラインラッチデータに従って 2 5 6 レベルの階調電圧のうちの 1 レベルを選択し、1 ライン分の画像信号として出力する。

三角波生成手段 3 5 は、発光期間制御信号 1 0 2 と帰線期間信号 3 8 に従って、発光期間中に入力表示データと無関係な三角波波形の P W M 信号 3 6 を生成し、出力するとともに、三角波波形の P W M 信号 3 6 を信号線 1 7 に出力する期間を示す三角波切替信号 3 7 を生成する。

階調電圧 - 三角波切替手段 3 4 は、三角波切替信号 3 7 に従って、1 ライン分の画像信号と三角波波形の P W M 信号を切り替え、信号線 1 7 に出力する。

【 0 0 1 7 】

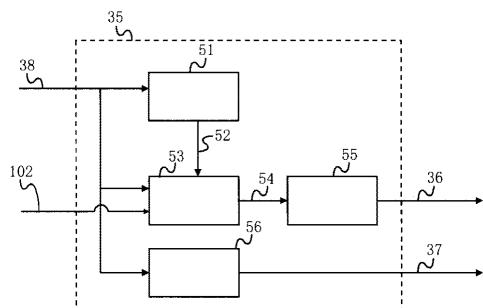

図 7 は、図 6 に示す三角波生成手段 3 5 の内部構成示す概略ブロック図である。 50

基準クロック生成手段 5 1 は、三角波波形の PWM 信号を生成するための基準クロック 5 2 を生成する。

アップダウンカウント手段 5 3 は、発光期間制御信号 102 と帰線期間信号 38 の制御の元に、基準クロック 5 2 に同期して、初期値からカウントダウン、“0”となった後再び初期値に戻るまでカウントアップを行い、カウント出力 5 4 を出力する。

デジタル／アナログ変換手段 5 5 は、デジタルデータであるカウント出力 5 4 を、アナログ信号変換し、三角波波形の PWM 信号 36 として出力する。

図 7 に示す回路では、アップダウンカウント手段 5 3 は、8 ビットのカウンタであることとし、カウント開始の初期値は“255”、デジタル／アナログ変換手段 5 5 も 8 ビットデジタルデータに対応するものとする。

三角波切替信号生成手段 5 6 は、帰線期間信号 38 に基づき三角波切替信号 37 を生成する。

#### 【0018】

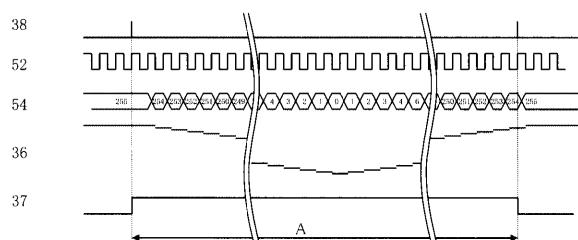

図 8 は、図 7 の三角波生成手段 35 の動作を説明するためのタイミングチャートである。

図 8 において、基準クロック 5 2 は、人力表示データ終了タイミングから人力表示データ開始タイミングまでの三角波期間（図 8 の帰線期間信号 38 の間の A の期間）の期間中に、最低限、アップダウンカウント手段 5 3 が、初期値“255”から“0”までカウントダウンし、その後再び“255”までカウントアップするために必要なサイクル数を有するクロックとなる。

アップダウンカウント手段 5 3 から出力されるカウント出力 5 4 は、基準クロック 5 2 に従って、初期値“255”からカウントダウンを開始し、“0”となった後、再び初期値である“255”までカウントアップした値となる出力である。

デジタル／アナログ変換手段 5 5 から出力される三角波波形の PWM 信号 36 は、“0”から“255”までを示す 8 ビットデジタルデータであるカウント出力 5 4 を、“0”的きを最低、“255”的きを最高レベルとするアナログ値に変換した信号である。

#### 【0019】

##### 〔実施例〕

本発明では、輝度モード制御部 100 より、複数の輝度表示モードに切り換えるが、このとき、それぞれの輝度表示モードに応じて、最適の波形の PWM 信号を使用するようにしたものである。

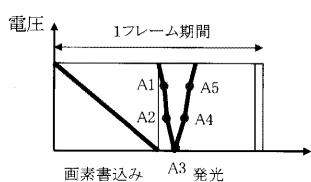

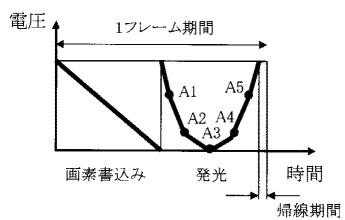

図 9 A は、本実施例の有機 EL 表示装置の標準輝度モードにおける PWM 信号を説明するための図である。なお、図 9 A ~ 図 9 D において、書き込み期間は、1 表示ライン毎（あるいは、2 表示ライン毎）に各画素に画像信号を書き込む期間である。

本実施例の標準輝度モードでは、図 9 A に示すように、発光期間に三角波波形（例えば、図 3 の C に示す波形）の PWM 信号に代えて、A1 ~ A5 の変曲点を有する放物線波形に近い波形の PWM 信号を用いる。なお、本発明では、この変曲点とは、この変曲点を境に直線の傾きが異なる点を意味している。

本実施例では、変曲点を有する放物線波形に近い波形の PWM 信号を用い、それぞれの輝度表示モードに応じて最適の変曲点を設定することにより、それぞれの輝度表示モードに応じて最適な輝度制御を行うことが可能となる。また、本実施例において、例えば、R・G・B の各画素毎に、PWM 信号の変曲点を設定することにより、赤、緑、青の各画素の発光輝度のバランスを調整することが可能となる。さらに、本実施例では、PWM 信号の変曲点を適宜設定することにより、ガンマ調整も行うことが可能となる。但し、これらの場合には、赤、緑、青の各画素毎にそれぞれ異なる PWM 信号を供給する必要があるので、赤、緑、青の各画素毎に PWM 信号を供給する信号線 17 をそれぞれ分離する必要がある。

なお、図 9 A に示すような PWM 信号を生成するには、例えば、図 7 に示す基準クロック生成手段 5 1 に、それぞれ周期の異なる複数のクロック生成回路を容易しておき、カウント数に応じて適宜切り換えて、図 7 に示す基準クロック生成手段 5 1 から出力すること

10

20

30

40

50

により容易に実現可能である。

【0020】

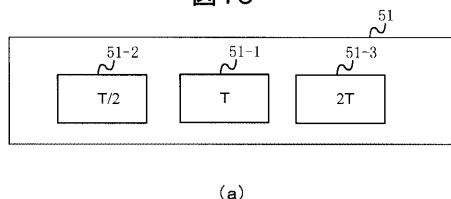

例えば、図10(a)に示すように、図7に示す基準クロック生成手段51に、周期Tのクロックを生成するクロック生成回路51-1と、クロック生成回路51-1の2倍の周期(2T)のクロックを生成するクロック生成回路51-3と、クロック生成回路51-1の1/2倍の周期(T/2)のクロックを生成するクロック生成回路51-2を用意する。

ここで、クロック生成回路51-1から出力されるクロックを用いて、16カウント数でアップダウン繰り返す場合、図10(b)のBに示すような、三角波波形のPWM信号が得られる。

また、1から4のカウント数の時に、クロック生成回路51-2から出力されるクロック、5から6のカウント数の時に、クロック生成回路51-1から出力されるクロック、7から10のカウント数の時に、クロック生成回路51-3から出力されるクロック、11から12のカウント数の時に、クロック生成回路51-1から出力されるクロック、13から16のカウント数の時に、クロック生成回路51-2から出力されるクロックを用いて、16カウント数でアップダウン繰り返す場合、図10(b)のCに示すような、A1～A5の変曲点を有する放物線波形に近い波形のPWM信号を得ることできる。

【0021】

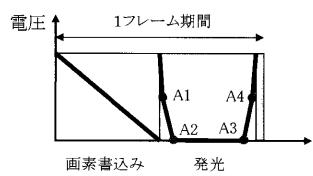

図9Bは、本実施例の有機EL表示装置の低輝度表示モードにおけるPWM信号を説明するための図である。

図9Bに示すように、本実施例の低輝度表示モードのPWM信号は、図9Aに示すPWM信号と同様に、A1～A5の変曲点を有する放物線波形に近い波形のPWM信号であるが、図9Aに示すPWM信号に比して、周期が、図9Aに示すPWM信号の周期の約半分となっている。このようなPWMを信号を用いることにより、画像信号の書き込みから発光までの期間が短くなるので低輝度制御に最適な波形となっている。

なお、図9Bに示すようなPWM信号を生成するには、例えば、図10(a)に示すクロック生成回路51-1、クロック生成回路51-2、およびクロック生成回路51-3において、周期(T)を短くする(あるいは、クロック生成回路51-1で生成されるクロックの周波数を高かい周波数とする)ことで容易に実現可能である。

【0022】

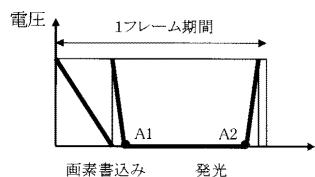

図9Cは、本実施例の有機EL表示装置の高輝度表示モードにおけるPWM信号を説明するための図である。

図9Cに示すように、本実施例の高輝度表示モードのPWM信号は、A1～A4の変曲点を有し、矩形波に近い波形のPWM信号である。また、この高輝度表示モードでは、駆動TFT4を飽和領域で動作させる。

前述したように、Vddを電源線18の電圧、Vdataを画像信号の電圧、Vdsを駆動TFT4のソースードレイン間の電圧とするとき、下記(1)式を満足する場合、駆動TFT4は飽和領域で動作する。

$$(Vdd - Vdata) \cdot Vds = \dots \dots \dots \dots \dots \dots \quad (1)$$

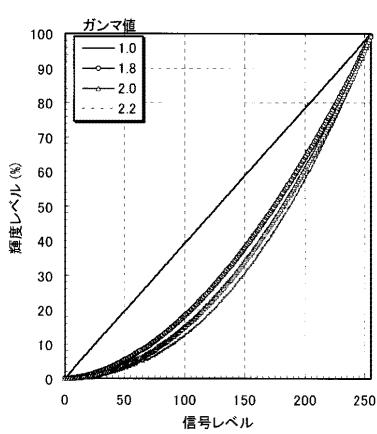

駆動TFT4が飽和領域で動作する場合、ドレイン電流(ID)は、ゲート・ソース間電圧の2乗に比例するので、ガンマ調整が容易となる。なお、図11に、ガンマ値が1.0、1.8、2.0、2.2の時の、画像信号の信号レベルと輝度レベルのグラフを示す。

なお、図9Cに示すようなPWM信号を生成するには、発光期間制御信号102に基づき、アップダウンカウント手段53のダウン動作開始時と、アップ動作時に、アップダウンカウント手段53のダウン動作を制御するアップダウン制御信号を入力するようすればよい。

【0023】

図9Dは、本実施例の有機EL表示装置の最大輝度表示モードにおけるPWM信号を説明するための図である。

10

20

30

40

50

図9Dに示すように、本実施例の最大輝度表示モードのPWM信号は、A1、A2の変曲点を有し、図9Cに示すPWM信号よりも、より矩形波に近い台形波波形のPWM信号である。また、この最大輝度表示モードでも、駆動TFT4を飽和領域で動作させる。

図9Dに示すように、この最大輝度表示モードでは、例えば、インタレース駆動により、画像信号の書込期間が、図9Cに示す高輝度表示モードの画像信号の書込期間の半分期間となっている。これにより、図9Cに示す高輝度表示モードに比して、より高輝度の画像を表示することが可能となる。

このインタレース駆動では、奇数番号の表示ライン上の画素に対する画像信号の書き込みと、偶数番号の表示ライン上の画素に対する画像信号の書き込みとが、1フレーム毎に交互に繰り返される。

例えば、奇数フレームでは、奇数番号の表示ライン上の画素に対する画像信号の書き込み行われ、偶数番号では、偶数番号の表示ライン上の画素に対する画像信号の書き込みが行われる。

#### 【0024】

本発明において、「有機EL素子」とは、カソード電極とアノード電極とで有機発光層を挟み込んで形成される1つのサブ画素を構成に備えた構造をいう。

「有機EL表示パネル」とは、サブ画素を構成する有機EL素子を備えた基板のことをいう。ここで、ドライバICが実装（実装方法は、チップオンガラス（COG）、テープキャリアパッケージ（TCP）、チップオンフィルム（COF）等）されている構造、半導体層がポリシリコンで構成される薄膜トランジスタによって基板上にドライバが内蔵されている構造、封止基板で封止された構造も含む。

「有機EL表示装置」は、有機EL表示パネルの他、この有機EL表示パネルのドライバを制御するタイミング制御回路や、電源回路などのインターフェースを含めた構造のことをいうものとする。

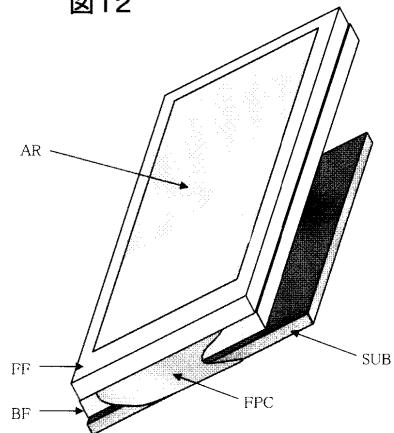

図12に、有機EL表示装置の外観を示す。

図12に示す有機EL表示装置は、有機EL表示パネル（以下、単にパネルとも称する。）の表示部ARが露出する開口を備えた前面フレーム（FF）と、有機EL表示パネルの裏面全体を覆い、前面フレーム（FF）とスナップフィットにより固定されている裏面フレーム（RF）と、裏面フレーム（RF）のさらに裏面に配置された回路基板（SUB）と有機EL表示パネルとの間に取り付けられたフレキシブル回路基板（FPC）を備えた構造である。

なお、回路基板（SUB）は、裏面フレーム（RF）に対して、接着剤や面面テープで固定してもよいし、さらに外部に設けた電子装置のフレームにねじ等で固定してもよい。

#### 【0025】

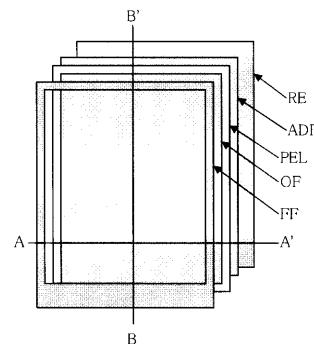

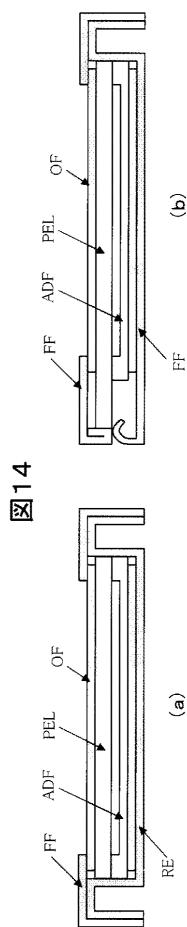

さらに、前面フレーム（FF）と裏面フレーム（RF）との間に挟まれた有機EL表示パネルの構造を図13、図14を用いて説明する。

図13は、表示面斜上方から見た有機EL表示パネルの分解図である。図14は、図13に示す有機ELパネルの断面構造を示す断面図であり、同図（a）は、図13のA-A'切断線に沿った断面構造を示す断面図、同図（b）は図13のB-B'切断線に沿った断面構造を示す断面図である。

前面フレーム（FF）の側から、光学フィルム（OF）、有機EL表示パネル（PEL）、熱拡散シート&衝撃吸収剤（ADF）、裏面フレーム（RF）の順に積層されている。

前面フレーム（FF）と裏面フレーム（RF）は、鉄とニッケルを主成分とする金属で構成され、アンバーやインバーと呼ばれる鉄を約36%含有する材料で構成された合金で構成された金属フレームである。

なお、この金属は、インバーにニッケルを含有させたスーパーインバーと呼ばれる合金で構成された金属フレームでもよい。また、ステンレスや鉄を用いた場合、廉価で容易に製造できる。前面フレーム（FF）は、裏面フレーム（RF）に向かって折り曲げられた形状をしている。

## 【0026】

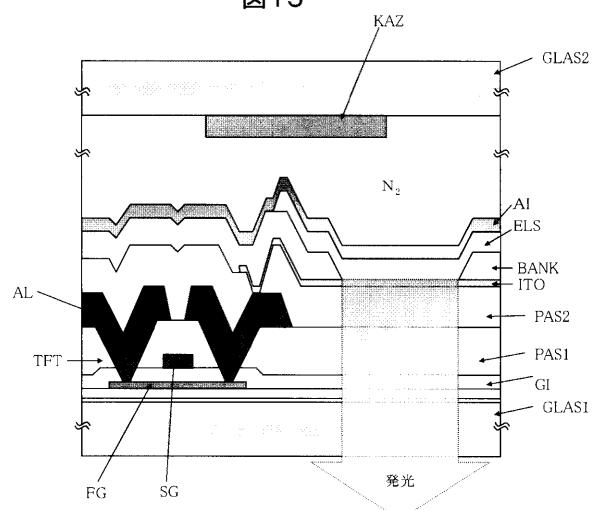

ボトムエミッション型の有機EL表示パネル(PEL)の断面構造を図15に示す。

半導体層がポリシコンから薄膜トランジスタの製造プロセスにより、ガラス基板(GLAS1)上にチャネル(FG)、ゲート絶縁膜(材料:P-TEOS)(GI)、ゲート配線(材料:MoW)(SG)、CONT絶縁膜(材料:P-TEOS)(PAS1)、SD配線(材料:金属/AlSi/金属)(AL)、パシベーション層(材料:P-SiN)(PAS2)からなる薄膜トランジスタ(TFT)を形成する。

薄膜トランジスタ(TFT)の形成については、nMOS単チャネルプロセスにカウンタードープpMOSプロセスを加えたCMOSプロセスで作製する。

薄膜トランジスタ(TFT)形成後に、有機EL素子7の下部電極の陽極(ITO)を形成する。ボトムエミッション型の有機EL表示パネル(PEL)は、光の取り出し方向を薄膜トランジスタ(TFT)基板側とするため、下部電極の陽極が透明電極であるITOとなっている。

陽極(ITO)の形成後に電極端部での陽極-陰極間のショートを防ぐためのSiNバンク(SiL2)(BANK)を形成する。

次に、有機EL素子工程(OLED工程)にてR・G・Bを打ち分けるため精密マスクを用いて有機EL層(ELS)を形成し、表示領域全体を覆う形で上部電極の陰極(AI)を形成する。陰極AIは反射層を兼ねている。

最後に有機EL素子の劣化要因となる水分の浸入を防ぐため乾燥剤(KZA)を貼り付けた封止ガラス(GLAS2)を、N<sub>2</sub>環境下で封止して有機EL表示パネル(PEL)パネルの完成となる。

## 【0027】

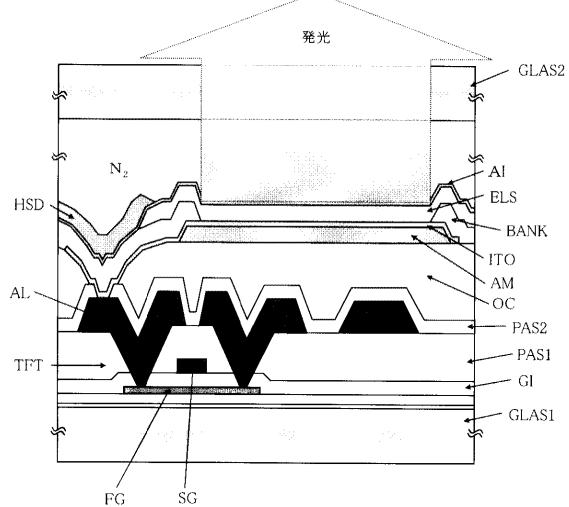

トップエミッション型の有機EL表示パネル(PEL)の断面構造を図16に示す。

半導体層がポリシコンから薄膜トランジスタの製造プロセスにより、ガラス基板(GLAS1)上にチャネル(FG)、ゲート絶縁膜(材料:P-TEOS)(GI)、ゲート配線(材料:MoW)(SG)、CONT絶縁膜(材料:P-TEOS)(PAS1)、SD配線(材料:金属/AlSi/金属)(AL)、パシベーション層(材料:P-SiN)(PAS2)からなる薄膜トランジスタ(TFT)を形成する。形成工程は、ボトムエミッション型の有機EL表示パネル(PEL)と同一である。

その後、パシベーション層(PAS2)の上に薄膜トランジスタ(TFT)の形成によって生じた段差を平坦化するための有機層(平坦化層)(OC)を形成する。

トップエミッション型の有機EL表示パネル(PEL)は、光の取り出し方向が薄膜トランジスタ(TFT)基板の上側になるため、平坦化層(OC)を挿入すると画素回路に制限されることなく画素開口を配置することができる。このため、トップエミッション型の有機EL表示パネル(PEL)は高精細化が可能となる。

平坦化層(OC)には、窒化シリコンなどの無機膜やアクリル樹脂、ポリイミド樹脂などの有機膜が適用可能である。これは、ボトムエミッション型の有機EL表示パネル(PEL)でも同様である。

## 【0028】

平坦化層(OC)の形成後に反射層(AM)、陽極ITOを形成する。

反射層にはAlSi(Si:1.0wt%以下)を用いるが、平坦化層(OC)は金属との密着性が悪いことから、MoW(Mo:80wt%,W:20wt%)を下地として追加し、AlSi/MoWの2層構造とした。

SD配線(AL)と陽極(ITO)との電気的接続に関しては反射層(AM)を介して陽極(ITO)に接続する方法と、反射層(AM)を介さずに直接SD配線(AL)と陽極(ITO)を接続する方法が考えられるが、AlSiとITOはオーミック接続とならないため、直接SD配線(AL)と陽極(ITO)を接続することとした。

SD配線(AL)は、従来から陽極(ITO)との接続を考慮してキャップ金属を用いており、陽極(ITO)との接続については問題ない。

陽極(ITO)の形成後に、電極端部での陽極-陰極間ショートを防ぐためのSiNバ

10

20

30

40

50

ンク (S i L 2) (B A N K) を形成する。

有機 E L 素子工程 (O L E D 工程) にて R · G · B を打ち分けるため精密マスクを用いて有機 E L 層 (E L S) を形成し、表示領域全体を覆う形で上部電極の透明陰極 (I Z O) を形成する。

光学干渉のため透明陰極 (I Z O) は薄膜化する必要があり、透明陰極 (I Z O) の抵抗が問題となる。そこで画素と画素の間に補助電極 (H S D) を形成する。

最後に有機 E L 素子の劣化要因となる水分の浸入を防ぐため乾燥剤 (図示せず) を貼り付けたガラス基板 (G L A S 2) を、N<sub>2</sub> 環境下で封止して有機 E L 表示パネル (P E L) パネルの完成となる。

【0029】

10

本実施例の有機 E L 表示装置は、自発光型であるため高コントラストで視野角が広く、かつ薄型・軽量である。従って、様々な電子装置の表示部として用いることができる。例えば、T V 放送等を大画面で鑑賞するには対角 30 インチ以上 (典型的には 40 インチ以上) の E L ディスプレイ (有機 E L 表示装置を筐体に組み込んだディスプレイ) の表示部として本願発明の有機 E L 表示装置を用いるとよい。

なお、E L ディスプレイには、パソコン用ディスプレイ、T V 放送受信用ディスプレイ、広告表示用ディスプレイ等の全ての情報表示用ディスプレイが含まれる。また、その他にも様々な電子装置の表示部として本発明の有機 E L 表示装置を用いることができる。その様な電子装置としては、ビデオカメラ、デジタルカメラ、カーナビゲーションシステム、カーオーディオ、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末 (モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等) 、記録媒体を備えた画像再生装置などが挙げられる。

20

特に、斜め方向から見ることの多い携帯情報端末は視野角の広さが重要視されるため、有機 E L 表示装置を用いることが望ましい。それら電子装置の具体例を以下に示す。

図 17 は、携帯電話であり、本実施例の有機 E L 表示装置は表示部に用いることができる。なお、表示部は黒色の背景に白色の文字を表示することで携帯電話の消費電力を抑えることができる。図 18 は、デジタルスチルカメラであり、本実施例の有機 E L 表示装置は表示部に用いることができる。また、有機 E L 表示装置は発光している部分が電力を消費するため、発光部分が極力少なくなるように情報を表示することが望ましい。

図 19 は、デジタルビデオカメラであり、本実施例の有機 E L 表示装置は表示部に用いることができる。図 20 はカーナビゲーションシステムであり、本実施例の有機 E L 表示装置は表示部に用いることができる。

30

以上の様に、本実施例の有機 E L 表示装置の適用範囲は極めて広く、あらゆる分野の電子装置に用いることが可能である。

【0030】

有機 E L 表示装置は、複数の輝度表示モード (所謂、複数の発光輝度設定) が必要とされる場合があった。例えば、デジタル・スチル・カメラ (以下、D S C) などのモバイル機器の表示部として使用される有機 E L 表示装置では、外光視認性を確保するために高輝度表示と、通常の表示との 2 つの輝度表示モードが設定可能であることが強く求められている。

40

本実施例の有機 E L 表示装置において、複数の発光輝度設定 (例えば、最大表示輝度 : 5 0 0 c d / m<sup>2</sup> 、輝度表示モード : R G B 各 5 0 ステップ (各ステップ内で 2 5 6 階調) : 輝度ステップ 1 0 c d / m<sup>2</sup> ) が必要な場合、電源制御部 1 1 1 での電圧制御により変動した階調特性を P W M 信号の変曲点を所定の階調特性に合わせて規定することにより、高コントラストかつ正確な階調性能を得ることができる。

また、高輝度表示モード時に、P W M 信号を飽和領域駆動に切り替えることで、所定の輝度を得ることができ屋外視認性が向上する。さらに、飽和駆動に切り替えることで、非飽和領域駆動に対して、配線抵抗による電圧降下に起因する面内輝度むら (シェーディング) や焼付き発生時間を大幅に低減することもできる。

また、R G B 各色の陽極電源部 1 1 0 が共通であっても、R G B の各画素を独立で階調

50

制御が可能となり、高品位な表示装置の提供が可能となる。

さらに、本実施例においては、各画素のガンマ調整を行うことにより、適宜制御された発光輝度で発光する E L 素子を有する有機 E L 表示装置が作製される。

以上、本発明者によってなされた発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは勿論である。

【図面の簡単な説明】

【0031】

【図1】本発明の前提となる有機 E L 表示装置の概略構成を示すブロック図である。

【図2】図1に示す有機 E L 表示装置の表示部の全体構成を示す図である。 10

【図3】本発明の前提となる有機 E L 表示装置の動作を説明するためのタイミングチャートを示す図である。

【図4】図1に示す1画素を説明するため図である。

【図5】図4に示した駆動インバータ (INV) における信号電圧の基準電圧の設定を説明するための図である。

【図6】図1に示す信号線駆動回路の内部構成を示す概略ブロック図である。

【図7】図6に示す三角波生成手段の内部構成示す概略ブロック図である。

【図8】図7の三角波生成手段の動作を説明するためのタイミングチャートである。

【図9A】本発明の実施例の有機 E L 表示装置の標準輝度モードにおける PWM 信号を説明するための図である。 20

【図9B】本発明の実施例の有機 E L 表示装置の低輝度表示モードにおける PWM 信号を説明するための図である。

【図9C】本発明の実施例の有機 E L 表示装置の高輝度表示モードにおける PWM 信号を説明するための図である。

【図9D】本発明の実施例の有機 E L 表示装置の最大輝度表示モードにおける PWM 信号を説明するための図である。

【図10】図9Aに示す PWM 信号を生成する回路構成を示す図である。

【図11】ガンマ値が 1.0、1.8、2.0、2.2 の時の、画像信号の信号レベルと輝度レベルとの間の関係を示すグラフである。

【図12】有機 E L 表示装置の外観を示す図である。 30

【図13】表示面斜上方から見た有機 E L 表示パネルの分解図である。

【図14】図13に示す有機 E L パネルの断面構造を示す断面図である。

【図15】ボトムエミッション型の有機 E L 表示パネル (PEL) の断面構造を示す断面図である。

【図16】トップエミッション型の有機 E L 表示パネル (PEL) の断面構造を示す断面図である。

【図17】本発明の実施例の有機 E L 表示装置を表示部に使用する携帯電話を示す図である。

【図18】本発明の実施例の有機 E L 表示装置を表示部に使用するデジタルステルカメラを示す図である。 40

【図19】本発明の実施例の有機 E L 表示装置を表示部に使用するデジタルビデオカメラを示す図である。

【図20】本発明の実施例の有機 E L 表示装置を表示部に使用するカーナビゲーションシステムを示す図である。

【符号の説明】

【0032】

2 容量素子

4 p 型薄膜トランジスタ (駆動 TFT)

5 リセットスイッチ素子

7 有機エレクトロルミネッセンス素子 (有機 E L 素子) 50

|                                      |    |

|--------------------------------------|----|

| 9 点灯スイッチ素子                           |    |

| 1 0 画素                               |    |

| 1 7 信号線                              |    |

| 1 5 リセット線                            |    |

| 1 9 点灯スイッチ線                          |    |

| 1 8 電源線                              |    |

| 2 1 信号線駆動回路                          | 10 |

| 2 2 走査線駆動回路                          |    |

| 3 1 データシフト手段                         |    |

| 3 2 1ラインラッチ手段                        |    |

| 3 3 階調電圧選択手段                         |    |

| 3 4 階調電圧 - 三角波切替手段                   |    |

| 3 5 三角波生成手段                          |    |

| 5 1 基準クロック生成手段                       |    |

| 5 1 - 1 , 5 1 - 2 , 5 1 - 3 クロック生成回路 |    |

| 5 3 アップダウンカウント手段                     |    |

| 5 5 デジタル / アナログ変換手段                  |    |

| 5 6 三角波切替信号生成手段                      |    |

| 1 0 0 輝度モード制御部                       | 20 |

| 1 1 0 陽極電源部                          |    |

| 1 1 1 電源制御部                          |    |

| 1 2 0 陰極電源部                          |    |

| 1 2 1 陰極電源線                          |    |

| 1 3 0 表示制御部                          |    |

| A R 表示部                              |    |

| I N V 駆動インバータ                        |    |

| F F 前面フレーム                           |    |

| R F 裏面フレーム                           |    |

| S U B 回路基板                           |    |

| F P C フレキシブル回路基板                     | 30 |

| O F 光学フィルム                           |    |

| P E L 有機EL表示パネル                      |    |

| A D F 熱拡散シート & 衝撃吸収剤                 |    |

| G L A S 1 , G L A S 2 ガラス基板          |    |

| F G チャネル                             |    |

| G I ゲート絶縁膜                           |    |

| S G ゲート配線                            |    |

| P A S 1 C O N T 絶縁膜                  |    |

| A L S D 配線                           |    |

| P A S 2 パシベーション層                     | 40 |

| T F T 薄膜トランジスタ                       |    |

| O C 有機層 (平坦化層)                       |    |

| I T O 陽極                             |    |

| B A N K S i N バンク                    |    |

| E L S 有機EL層                          |    |

| A I 陰極                               |    |

| K A Z 乾燥剤                            |    |

| A M 反射層                              |    |

| H S D 補助電極                           |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

図6

【図7】

図7

【図9B】

図9B

【図9C】

図9C

【図9D】

図9D

【図8】

図8

【図9A】

図9A

【図10】

図10

(a)

(b)

【図11】

図11

【図12】

図12

【図13】

図13

【図14】

【図15】

図15

【図16】

図16

【図17】

図17

【図18】

図18

【図19】

図19

【図20】

図20

---

フロントページの続き

(51)Int.Cl.

F I

|        |      |         |

|--------|------|---------|

| G 09 G | 3/20 | 6 2 2 D |

| G 09 G | 3/20 | 6 2 3 D |

| G 09 G | 3/20 | 6 4 2 J |

| G 09 G | 3/20 | 6 1 1 H |

| G 09 G | 3/20 | 6 2 4 Z |

(74)代理人 110000154

特許業務法人はるか国際特許事務所

(72)発明者 中村 則裕

千葉県茂原市早野3300番地 株式会社日立ディスプレイズ内

(72)発明者 谷津 靖春

千葉県茂原市早野3300番地 株式会社日立ディスプレイズ内

(72)発明者 秋元 肇

千葉県茂原市早野3300番地 株式会社日立ディスプレイズ内

審査官 武田 悟

(56)参考文献 特開2004-341144 (JP, A)

特開2009-47778 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |           |   |         |

|--------|-----------|---|---------|

| G 09 G | 3 / 0 0   | - | 3 / 3 8 |

| H 01 L | 5 1 / 5 0 |   |         |