(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4268332号

(P4268332)

(45) 発行日 平成21年5月27日(2009.5.27)

(24) 登録日 平成21年2月27日(2009.2.27)

(51) Int.Cl.

G06F 12/10 (2006.01)

F 1

G06F 12/10 505B

請求項の数 10 (全 31 頁)

(21) 出願番号 特願2000-329869 (P2000-329869)

(22) 出願日 平成12年10月30日 (2000.10.30)

(65) 公開番号 特開2001-175536 (P2001-175536A)

(43) 公開日 平成13年6月29日 (2001.6.29)

審査請求日 平成19年6月29日 (2007.6.29)

(31) 優先権主張番号 09/430793

(32) 優先日 平成11年10月31日 (1999.10.31)

(33) 優先権主張国 米国(US)

(73) 特許権者 599142110

エマージング・アキテクチャーズ・エル

エルシー

Emerging Architectu

res, L. L. C.

アメリカ合衆国 95014 カリフォルニア

州クバーチノ、ブルーンリッジ・アベニュー

19447 ヒューレット・パッカ

ド・カンパニー内

(74) 代理人 100081721

弁理士 岡田 次生

(72) 発明者 ウィリアム・アール・バイグ

アメリカ合衆国 95070 カリフォルニア

州サラトガ、ペレゴ・ウェイ 18630

最終頁に続く

(54) 【発明の名称】仮想アドレスからページ・テーブル・インデックスを計算する方法および装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ページ・テーブルのエントリを参照するエントリ・アドレスを仮想アドレスから形成する方法であって、前記仮想アドレスが、領域を識別する活動領域識別子を参照する領域部分を含み、前記ページ・テーブルが、ロング・フォーマットおよびショート・フォーマットを仮定することができ、

前記仮想アドレスをJビット右にシフトすることによって前記仮想アドレスからハッシュ・ページ番号を形成するステップであって、前記仮想アドレスの前記領域部分に関連付けられた領域の好ましいページ・サイズが $2^J$ バイトであるステップと、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記仮想アドレスの前記領域部分によって参照される前記領域識別子および前記ハッシュ・ページ番号を組み合わせることによりハッシュ・インデックスを形成するステップと、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ハッシュ・インデックスをKビット左にシフトすることによってテーブル・オフセットを形成するステップであって、各ロング・フォーマット・ページ・テーブル・エントリが $2^K$ バイト長であるステップと、

前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記ハッシュ・インデックスを前記ハッシュ・ページ番号に等しく設定することによりハッシュ・インデックスを形成するステップと、

前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記ハ

10

20

ツシュ・インデックスをレビット左にシフトすることによってテーブル・オフセットを形成するステップであって、各ショート・フォーマット・ページ・テーブル・エントリが2<sup>レバイト</sup>長であるステップと、

前記ページ・テーブルのサイズに基づきマスクを形成するステップと、

前記ページ・テーブルのベース・アドレスおよび前記マスクを使用して第1アドレス部分を形成するステップと、

前記テーブル・オフセットおよび前記マスクを使用して第2アドレス部分を形成するステップと、

少なくとも前記第1アドレス部分および前記第2アドレス部分を組み合わせることによって前記エントリ・アドレスを形成するステップと、を含む方法。 10

【請求項2】

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ページ・テーブルの前記ベース・アドレスから前記領域部分を抽出することによってページ・テーブル領域を形成するステップと、

前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記仮想アドレスから前記領域部分を抽出することによってページ・テーブル領域を形成するステップとをさらに含む方法であって、

前記少なくとも前記第1アドレス部分および前記第2アドレス部分を組み合わせることによって前記エントリ・アドレスを形成するステップが、前記ページ・テーブル領域、前記第1アドレス部分および第2アドレス部分を組み合わせることによって前記エントリ・アドレスを形成するステップであって、前記ページ・テーブル領域が前記エントリ・アドレスの領域部分に挿入されるステップを含む、請求項1に記載の方法。 20

【請求項3】

前記仮想アドレスからハッシュ・ページ番号を形成するステップが、前記仮想アドレスの実装された部分だけをレビット右にシフトすることによって前記仮想アドレスからハッシュ・ページ番号を形成するステップであって前記仮想アドレスの前記領域部分に関連付けられた領域の好ましいページ・サイズが2<sup>レバイト</sup>であるステップを含む、請求項1に記載の方法。

【請求項4】

2<sup>N</sup>バイトの最小ページ・テーブル・サイズが定義されており、前記ページ・テーブルのベース・アドレスおよび前記マスクを使用して第1アドレス部分を形成するステップが、

前記ページ・テーブルの前記ベース・アドレスの下位Nビットを含まない前記ページ・テーブルの前記ベース・アドレス、および前記マスクの下位Nビットを含まない前記マスクを使用して第1アドレス部分を形成するステップを含み、

前記テーブル・オフセットおよび前記マスクを使用して第2アドレス部分を形成するステップが、

前記テーブル・オフセットの下位Nビットを含まない前記テーブル・オフセット、および前記マスクの下位Nビットを含まない前記マスクを使用して第2アドレス部分を形成するステップを含み、 40

前記少なくとも前記第1アドレス部分および前記第2アドレス部分を組み合わせることによって前記エントリ・アドレスを形成するステップが、前記第1アドレス部分および前記第2アドレス部分を組み合わせて結果を形成し、その結果をNビット左にシフトし、その結果と前記テーブル・オフセットの下位Nビットを組み合わせることにより前記エントリ・アドレスを形成するステップを含む、請求項1に記載の方法。

【請求項5】

ページ・テーブルのエントリを参照するエントリ・アドレスを仮想アドレスから形成する方法であって、前記仮想アドレスが、領域を識別する活動領域識別子を参照する領域部分を含み、前記ページ・テーブルの最小サイズが2<sup>N</sup>バイトであり、前記ページ・テーブルが、ロング・フォーマットおよびショート・フォーマットを仮定することができ、 50

前記仮想アドレスの実装された部分だけを  $J$  ビット右にシフトすることによって前記仮想アドレスからハッシュ・ページ番号を形成するステップであって、前記仮想アドレスの前記領域部分に関連付けられた前記領域の好ましいページ・サイズが  $2^J$  バイトであるステップと、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ハッシュ・ページ番号、前記仮想アドレスの前記領域部分、および前記仮想アドレスの前記領域部分から参照される前記領域識別子を組み合わせることによってハッシュ・インデックスを形成するステップであって、前記仮想アドレスを  $J$  ビット右にシフトすることに基づき空いていることが分かっている前記ハッシュ・ページ番号のビット位置に前記仮想アドレスの前記領域部分が組み合わされて挿入されるステップと、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ハッシュ・インデックスを  $K$  ビット左にシフトすることによってテーブル・オフセットを形成するステップであって、各ロング・フォーマット・ページ・テーブル・エントリが  $2^K$  バイト長であるステップと、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ページ・テーブルのベース・アドレスから前記領域部分を抽出することによってページ・テーブル領域を形成するステップと、

前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記ハッシュ・インデックスを前記ハッシュ・ページ番号に等しく設定することによってハッシュ・インデックスを形成するステップと、

前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記ハッシュ・インデックスを  $L$  ビット左にシフトすることによってテーブル・オフセットを形成するステップであって、各ショート・フォーマット・ページ・テーブル・エントリが  $2^L$  バイト長であるステップと、

前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記仮想アドレスから前記領域部分を抽出することによってページ・テーブル領域を形成するステップと、

$2^M$  を  $M$  乗し  $1$  を引いてマスクを形成するステップであって、 $2^M$  が前記ページ・テーブルのサイズであるステップと、

前記ページ・テーブルの前記ベース・アドレスの下位  $N$  ビットを含まない前記ページ・テーブルの前記ベース・アドレス、および前記マスクの反転の下位  $N$  ビットを含まない前記マスクの反転に対して論理積演算を実行することによって第1アドレス部分を形成するステップと、

前記テーブル・オフセットの下位  $N$  ビットを含まない前記テーブル・オフセット、および前記マスクの下位  $N$  ビットを含まない前記マスクに対して論理積演算を実行することによって第2アドレス部分を形成するステップと、

前記第1アドレス部分および前記第2アドレス部分に対して論理和演算を実行して第1の結果を形成し、この第1の結果を  $N$  ビット左にシフトして第2の結果を形成し、前記ページ・テーブル領域、前記第2の結果、および前記テーブル・オフセットの下位  $N$  ビットに対して論理和演算を実行することによって前記エントリ・アドレスを形成するステップであって、前記ページ・テーブル領域が前記エントリ・アドレスの領域部分に挿入されるステップと、を含む方法。

#### 【請求項 6】

領域を識別する活動領域識別子を参照する領域部分を含む仮想アドレスによってアドレス指定される仮想アドレス空間を定義するアーキテクチャを有するコンピュータ・システムであって、

ページ・テーブル・ベース・アドレスによって固定されたページ・テーブルを含むメモリ・ユニットであって、ページ・テーブルがロング・フォーマットおよびショート・フォーマットを仮定できるメモリ・ユニットと、

命令を実行するプロセッサであって、仮想アドレスから前記ページ・テーブルにエント

10

20

30

40

50

リ・アドレスを生成することができるページ・テーブル・エントリ・アドレス生成ユニットであるプロセッサと、を有し、

前記エントリ・アドレス生成ユニットは、

前記仮想アドレスをJビット右にシフトすることによって前記仮想アドレスからハッシュユ・ページ番号を形成するハッシュ・ページ番号生成回路であって、前記仮想アドレスの前記領域部分に関連付けられた前記領域の好ましいページ・サイズが $2^J$ バイトであるハッシュ・ページ番号生成回路と、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ハッシュ・ページ番号と前記仮想アドレスの前記領域部分から参照される前記領域識別子を組み合わせることによってハッシュ・インデックスを形成し、前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記ハッシュ・インデックスを前記ハッシュ・ページ番号に等しく設定することによってハッシュ・インデックスを形成するハッシュ・インデックス生成回路と、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ハッシュ・インデックスをKビット左にシフトすることによってテーブル・オフセットを形成し、ここで各ロング・フォーマット・ページ・テーブル・エントリが $2^K$ バイト長であり、前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記ハッシュ・インデックスをLビット左にシフトすることによってテーブル・オフセットを形成し、ここで各ショート・フォーマット・ページ・テーブル・エントリが $2^L$ バイト長であるテーブル・オフセット生成回路と、

前記ページ・テーブルのサイズに基づきマスクを形成するマスク生成回路と、

前記ページ・テーブル・ベース・アドレスおよび前記マスクを使用して第1アドレス部分を形成する第1アドレス部分生成回路と、

前記テーブル・オフセットおよび前記マスクを使用して第2アドレス部分を形成する第2アドレス部分生成回路と、

少なくとも前記第1アドレス部分および前記第2アドレス部分を組み合わせることによって前記エントリ・アドレスを形成するエントリ・アドレス生成回路と、を含むコンピュータ・システム。

#### 【請求項7】

前記プロセッサの前記ページ・テーブル・エントリ・アドレス生成ユニットは、前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ページ・テーブル・ベース・アドレスから前記領域部分を抽出することによってページ・テーブル領域を形成し、前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記仮想アドレスから前記領域部分を抽出することによってページ・テーブル領域を形成するページ・テーブル領域生成回路をさらに備え、

前記エントリ・アドレス生成回路は、前記ページ・テーブル領域、前記第1アドレス部分および前記第2アドレス部分を組み合わせることによって前記エントリ・アドレスを形成するものであり、ここで前記ページ・テーブル領域が前記エントリ・アドレスの領域部分に挿入されるものである、請求項6に記載のコンピュータ・システム。

#### 【請求項8】

前記ハッシュ・ページ番号生成回路が、前記仮想アドレスの実装されている部分だけをJビット右にシフトすることによって前記仮想アドレスから前記ハッシュ・ページ番号を形成するコンピュータ・システムであって、前記仮想アドレスの前記領域部分に関連付けられた前記領域の前記好ましいページ・サイズが $2^J$ バイトである、請求項6に記載のコンピュータ・システム。

#### 【請求項9】

前記第1アドレス部分生成回路は、前記ページ・テーブル・ベース・アドレスの下位Nビットを含まない前記ページ・テーブル・ベース・アドレスおよび前記マスクの下位Nビットを含まない前記マスクを使用して前記第1アドレス部分を形成し、

前記第2アドレス部分生成回路は、前記テーブル・オフセットの下位Nビットを含まない

10

20

30

40

50

い前記テーブル・オフセット、および前記マスクの下位Nビットを含まない前記マスクを使用して前記第2アドレス部分を形成し、

前記エントリ・アドレス生成回路は、前記第1アドレス部分および前記第2アドレス部分を組み合わせて結果を形成し、前記結果をNビット左にシフトし、前記結果と前記テーブル・オフセットの下位Nビットを組み合わせることによって前記エントリ・アドレスを形成する、請求項6に記載のコンピュータ・システム。

【請求項10】

領域を識別する活動領域識別子を参照する領域部分を含む仮想アドレスによってアドレス指定される仮想アドレス空間を定義するアーキテクチャを有するコンピュータ・システムであって、

ページ・テーブル・ベース・アドレスによって固定されたページ・テーブルを含むメモリ・ユニットであって、ページ・テーブルがロング・フォーマットおよびショート・フォーマットを仮定でき、最小サイズが $2^N$ ビットであるメモリ・ユニットと、

命令を実行するプロセッサであって、仮想アドレスからページ・テーブルにエントリ・アドレスを生成することができるページ・テーブル・エントリ・アドレス生成ユニットであるプロセッサとを含み、

前記エントリ・アドレス生成ユニットは、

前記仮想アドレスの実装されている部分だけをJビット右にシフトすることによって前記仮想アドレスからハッシュ・ページ番号を形成するハッシュ・ページ番号生成回路であって、前記仮想アドレスの前記領域部分に関連付けられた領域の好ましいページ・サイズが $2^J$ バイトであるハッシュ・ページ番号生成回路と、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ハッシュ・ページ番号、前記仮想アドレスの前記領域部分、および前記仮想アドレスの前記領域部分から参照される前記領域識別子を組み合わせることによってハッシュ・インデックスを形成し、ここで前記仮想アドレスの前記領域部分が、前記仮想アドレスをJビット右にシフトすること基づき空いていることが分かっている前記ハッシュ・ページ番号のビット位置に組み合わされて挿入され、前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記ハッシュ・インデックスを前記ハッシュ・ページ番号に等しく設定することによってハッシュ・インデックスを形成するハッシュ・インデックス生成回路と、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ハッシュ・インデックスをKビット左にシフトすることによってテーブル・オフセットを形成し、ここで各ロング・フォーマット・ページ・テーブル・エントリが $2^K$ バイト長であり、前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記ハッシュ・インデックスをLビット左にシフトすることによってテーブル・オフセットを形成し、ここで各ショート・フォーマット・ページ・テーブル・エントリが $2^L$ バイト長であるテーブル・オフセット生成回路と、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ページ・テーブル・ベース・アドレスから前記領域部分を抽出することによってページ・テーブル領域を形成し、ページ・テーブルのフォーマットがショートに設定されている場合に、前記仮想アドレスから前記領域部分を抽出することによってページ・テーブル領域を形成するページ・テーブル領域生成回路と、

$2^M$ をM乗し1を引くことによってマスクを形成するマスク生成回路であって、 $2^M$ が前記ページ・テーブルのサイズであるマスク生成回路と、

前記ページ・テーブル・ベース・アドレスの下位Nビットを含まない前記ページ・テーブル・ベース・アドレス、および前記マスクの反転の下位Nビットを含まない前記マスクの反転に対して論理積演算を実行することによって第1アドレス部分を形成する第1アドレス部分生成回路と、

前記テーブル・オフセットの下位Nビットを含まない前記テーブル・オフセット、および前記マスクの下位Nビットを含まない前記マスクに対して論理積演算を実行することに

10

20

30

40

50

よって第2アドレス部分を形成する第2アドレス部分生成回路と、

前記第1アドレス部分および前記第2アドレス部分に対して論理和演算を実行して第1の結果を形成し、前記第1の結果をNビット左にシフトして第2の結果を形成し、前記ページ・テーブル領域、前記第2の結果、および前記テーブル・オフセットの下位Nビットに対して論理和演算を実行することによって前記エントリ・アドレスを形成するエントリ生成回路であって、前記ページ・テーブル領域が前記エントリ・アドレスの領域部分に挿入されるエントリ生成回路と、を含むコンピュータ・システム。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

10

本発明はコンピュータ・システム内のメモリ機構に関する。より詳細には、本発明は、ハッシュ関数を介してアクセスされるページ・テーブルを有する仮想メモリ・システムに関する。

##### 【0002】

##### 【従来の技術】

従来型のコンピュータ・システムは、実際に存在するより多くの論理メモリをシミュレートし、コンピュータがいくつかのプログラムをそのサイズに関係なく同時に実行することを可能にする、仮想メモリと呼ばれる技術を使用する。同時実行するユーザ・プログラムは、オペレーティング・システムによって割り当てられた仮想アドレスを介してメインメモリ・アドレスにアクセスする。仮想アドレスからメインメモリの物理アドレスへのマッピングは、仮想アドレス変換として知られている処理である。仮想アドレス変換を達成する技術は多数あり、それらによってプロセッサがメインメモリ内の所要の情報にアクセスすることが可能になる。

20

##### 【0003】

仮想アドレスおよび物理アドレス空間は通常、ページと呼ばれる等しいサイズのメモリ・ブロックに分割され、ページ・テーブルが仮想アドレスと物理アドレスの間の変換を提供する。各ページ・テーブル・エントリは通常、仮想アドレスおよび/または物理アドレス、ならびにそのページに関する保護およびステータス情報を含む。ステータスは通常、そのページが受けたアクセスのタイプについての情報を含む。例えばダーティ・ビットは、そのページ内のデータに変更があったことを示す。通常、ページ・テーブルは大きいのでメモリ内に格納される。従って通常のメモリ・アクセス毎に、変換を獲得する第1のアクセスおよび物理メモリ位置にアクセスする第2のアクセスという、少なくとも2つのアクセスが実際には必要とされ得る。

30

##### 【0004】

仮想アドレス変換をサポートする多数のコンピュータ・システムは、変換索引バッファ(TLB)を使用する。TLBは通常、小型で高速な連想記憶であり、普通はプロセッサ・ユニット上または近傍に置かれ、最近使用された仮想アドレスおよび物理アドレスの対を格納する。TLBはページ・テーブル内の変換のサブセットを含み、はるかに速くアクセスすることができる。処理ユニットは、メインメモリからの情報を必要とするとき、TLBに対して仮想アドレスを送る。TLBは仮想アドレス・ページ番号を受け取り、物理ページ番号を返す。物理ページ番号は、メインメモリ内の所要のバイトまたはワードにアクセスするために下位アドレス情報と組み合わされる。

40

##### 【0005】

ほとんどの場合、TLBはページ・テーブル全体を含むことができないので、TLBを更新する手順を実装する必要がある。TLB内に変換がない仮想ページがアクセスされるとき、この仮想ページ番号から物理ページ番号への変換を決定するためにページ・テーブルがアクセスされ、この情報がTLB内に入れられる。ページ・テーブルに対するアクセスは、TLBに対するアクセスより20倍長くかかる可能性があり、したがってTLB内で変換を利用し続けることでプログラムの実行速度が最適化される。

##### 【0006】

50

今日のコンピュータ・システムの大半は、コンピュータ内の物理ランダム・アクセス・メモリ（RAM）を増強するためにある種の大量記憶、通常はディスクを使用する。このメインメモリの増強により、メインメモリだけが利用可能な場合より大きなプログラムを実施することができる。さらにディスク・メモリはRAMよりかなり廉価であるが、数桁低速である。プログラムの長さおよびメインメモリに対する他のプログラムとの競合次第で、任意の特定時点においてプログラムの一部がメインメモリ内にあり、一部がディスク上にある可能性がある。直ちにアクセスする必要のあるプログラムの一部はメインメモリ内に移動されるが、現在使用されていない部分はディスク上に残される。

#### 【0007】

例えば1メガバイトのメインメモリを有するコンピュータ上で実行される2メガバイト長の単一プログラムを考慮されたい。このプログラムは2メガバイトの仮想アドレス空間を必要とする。メインメモリが1メガバイトしか保有できないので、所与のいかなる時にもメインメモリ内にはせいぜいプログラムの半分しか存在することができず、仮想アドレス空間の残りはディスク上に格納される。メインメモリ内の情報に対するアクセスは通常どおり行われる。すなわち変換を有するかどうかを見るためにTLBが最初に調べられ、TLBにない場合、ページ・テーブルからの情報を用いてTLBが更新され、次いで希望する変換情報を得るためにTLBが再度参照される。

10

#### 【0008】

メインメモリにない情報に対するアクセスが発生する場合には、その変換を求めてTLBが最初にアクセスされるが、そこにはないことになる。次いでTLBを更新する変換情報を得るためにページ・テーブルが参照される。しかしひページ・テーブルにはメインメモリ内の情報に対する変換しかないので、必要な変換情報はないことになる。この状態はページ・フォルトと呼ばれる。ページ・フォルトに応答して、ページ・フォルト・ハンドラが空き物理ページを見つけ、その物理ページにディスク上に格納されている必要な仮想ページをロードし、その変換をページ・テーブルに挿入する。全ての物理ページが他の仮想ページに既に関連付けられている場合、ページ・フォルト・ハンドラは、現在物理メモリ内に格納されているどの仮想ページをディスクにスワップ・アウトするかを選択する必要がある。このタスクを実行する、先入れ先出し、LRU (least-recently-used) アルゴリズムなど多数のアルゴリズムがある。当技術分野でよく知られているように、TLB更新処理がハードウェアまたはソフトウェアのいずれかによって処理されるのに対し、ページ・フォルト・ハンドラは通常ソフトウェアに実装される。

20

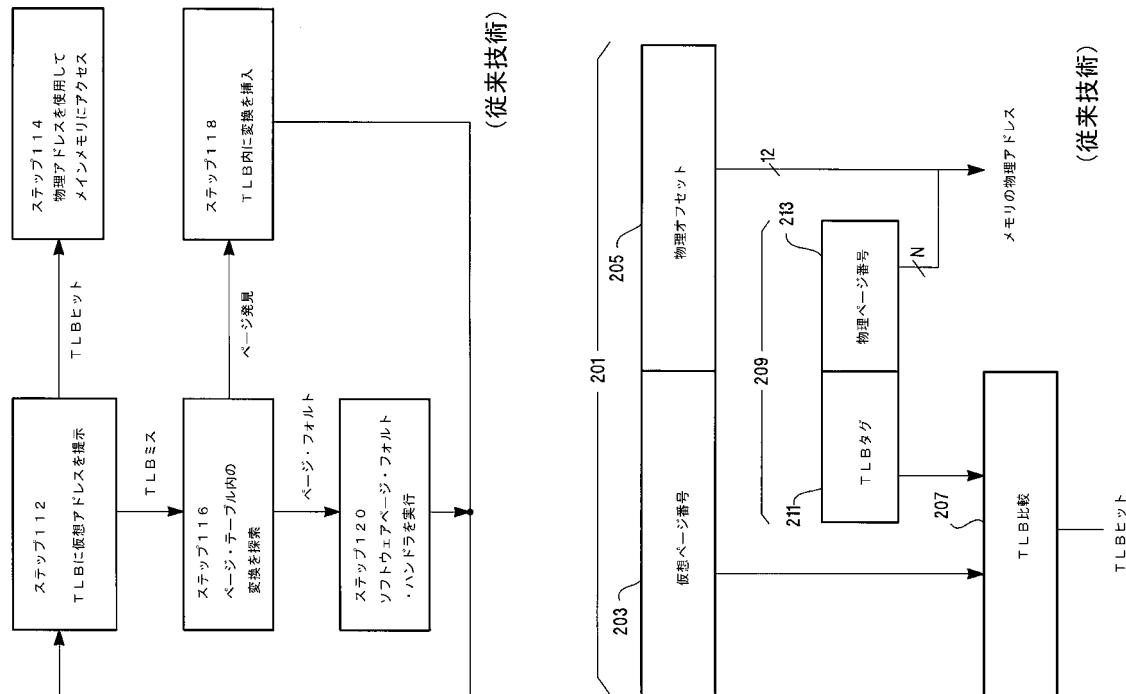

#### 【0009】

図1は上述の処理を示す。ステップ112において、TLBに仮想アドレスが提示される。この仮想アドレスに対する変換がTLB内にある場合には（TLBヒット）、関連付けられた物理アドレスがTLBから得られ、物理メモリにアクセスするために利用される（ステップ114）。この仮想アドレスに対する変換がTLBにない場合には（TLBミス）、その変換を求めてページ・テーブルがアクセスされる（ステップ116）。その変換がページ・テーブルにある場合には、この情報がTLBに挿入され（ステップ118）、仮想アドレスが再び提示される（ステップ112）。今度はTLBヒットになり、得られた物理アドレスが物理メモリにアクセスするために使用される。

30

#### 【0010】

仮想アドレスが、物理アドレス・ページが関連付けられていない仮想アドレス・ページ内にある場合には、ページ・テーブル内にこのページに対するエントリがないことになり、ページ・フォルトが発生する。この状況では、ソフトウェアのページ・フォルト・ハンドラ（ステップ120）が仮想ページに物理ページを割り当て、ディスクから物理ページにページをコピーし、ページ・テーブルを更新する。次いでTLBに仮想アドレスが再び提示される。TLBにまだ変換がないので、もう1度TLBミスが起こりページ・テーブルからTLBが更新される。その後、仮想アドレスがTLBに再び提示され、今度はTLBヒットが確実で、得られた物理アドレスが物理メモリにアクセスするために使用される。

40

#### 【0011】

50

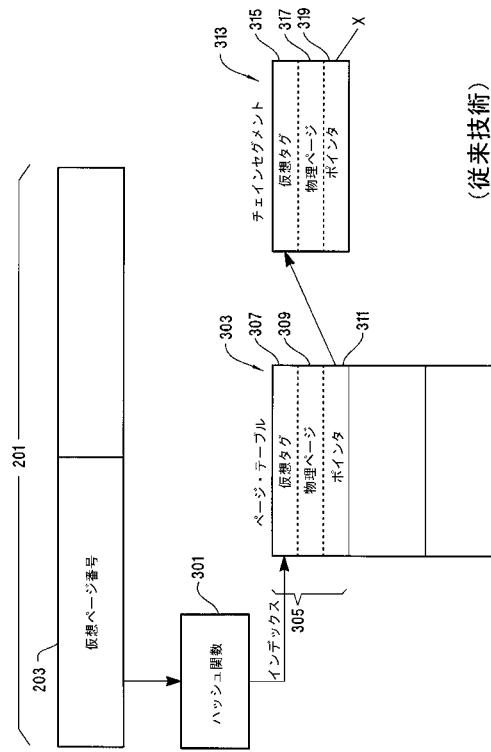

図2は、仮想アドレスの提示に応答してバッファ (TLB) 内のエントリにアクセスする方法を単純化して示したものである。普通ならTLBにはより多数のエントリがあるが、例を単純化するために、例示したTLBには1つしかエントリがない。仮想アドレスがレジスタ201にロードされる。この仮想アドレスは2つの部分、仮想ページ番号203および物理オフセット205からなる。物理オフセットはページ・サイズに対応する。4キロバイトのページ・サイズを有するコンピュータ・システムの場合、物理オフセット205はアドレスの下位12ビット(ビット11~0)であり、ページ内の特定バイトを示す。レジスタ内の残りのビットは仮想ページ番号を指す。用語「ページ・オフセット」は当業界でしばしば使用される用語であり、用語「物理オフセット」と同義である。仮想アドレスは、「アドレス空間識別子」ビット、「領域(region)識別子」ビットなど、物理ページ番号に対する変換を一意に指定する際に使用される他のビットを含むことがある。

#### 【0012】

図に示した例の場合、仮想ページ番号はTLB比較器207に対して一入力を与える仮想タグになる。TLB209は、2つの連結した部分、TLBタグ211および関連付けられた物理ページ番号213を有する。TLBタグ211はTLB比較器207に第2の入力を与え、比較器はTLBタグと仮想タグを比較する。タグが一致する場合には、比較器はTLBヒットを示し、物理(実)メモリ・アドレスを与えるために物理ページ番号213と物理オフセット205が組み合わされる。タグが一致しない場合には、TLBミスが起こっており、TLBを更新するために、図1に関連して述べたTLBミス処理が用いられる。

#### 【0013】

図3は、TLBミスの後にTLBを更新するために必要となる、仮想ページ番号が与えられた物理ページ情報を取り出す処理を示す。上述のようにページ・テーブル内で仮想から物理へのマッピングが維持される。所与の仮想アドレスを物理アドレスに変換する場合、一つの方法は、ページ・テーブルへのインデックスを形成するために仮想アドレスに対して多対一(ハッシュ)関数を実行することである。これはリンクされたエントリ・リストに対するポインタを与える。次いでこれらのエントリから一致するものが検索される。一致を判定するためには、仮想ページ番号とページ・テーブル内のエントリ(仮想タグ)が比較される。両者が等しい場合、そのページ・テーブル・エントリが物理アドレス変換を与える。

#### 【0014】

図に示した例では、インデックスを形成するために仮想ページ番号203に対してハッシュ関数301が実行される。このインデックスはページ・テーブル303へのオフセットである。図に示すように、インデックスは0、すなわちインデックスはページ・テーブル内の第1のエントリ305を指す。ページ・テーブル内の各エントリは、複数の部分からなるが、通常少なくとも仮想タグ307、物理ページ309およびポインタ311を含む。仮想ページ番号203が仮想タグ307に等しい場合、物理ページ309は所要の物理(実)メモリ・ページ・アドレスを与える。仮想タグが一致しない場合、ポインタ311は、仮想から物理への変換情報を含むメモリ内のエントリのチェイン(連鎖)を指す。同じページ・テーブル・エントリに2つ以上の仮想ページ番号が付与される(ハッシュされる)可能性があるときは、そのチェインに含まれる別の情報が必要である。

#### 【0015】

図に示すように、ポインタ311は連鎖セグメント313を指す。このチェイン・セグメントは、最初のページ・テーブル・エントリと同じタイプの情報を含む。前と同様に、一致するかどうかを見るために仮想ページ番号203と次の仮想タグ315が比較される。一致する場合には、関連付けられた物理ページ317が所要の物理メモリ・ページのアドレスを与える。一致しない場合には、もしあれば次のチェイン・セグメントを見つけるためにポインタ319が検査される。図に示すようにポインタ319が他のチェイン・セグメントを指さない場合には、ページ・フォルトが起こっている。その場合、図1に関連して述べたように、ページ・テーブルを更新するためにページ・フォルト・ソフトウェア・

10

20

30

40

50

プログラムが使用される。

【0016】

上述の方法は、仮想タグがコンピュータの基本データ・バス・サイズ以下のシステムに対してはよく機能する。しかし仮想タグがそのデータ・バス・サイズより大きい場合には、仮想タグと仮想ページ番号が同じであるかどうかをテストするために2度比較する必要がある。

【0017】

「Computer Memory Address Control Apparatus Utilizing Hashed Address Tags in Page Tables Which Are Compared to a Combined Address Tag and Index Which Are Longer than the Basic Data Width of the Associated Computer」という名称で、本明細書に参照により組み込まれたDale Morris等の米国特許第5,724,538号は、仮想タグのサイズを減らし、それによって仮想タグと仮想ページ番号がおなじであるかどうかをテストするのに必要な比較の回数を減らす方式を開示している。基本的に、Morris等は、仮想アドレスの一部は既にハッシュ・インデックスによって表されており、したがってアドレスのその部分は仮想タグによって表される必要がないことを認識した。

10

【0018】

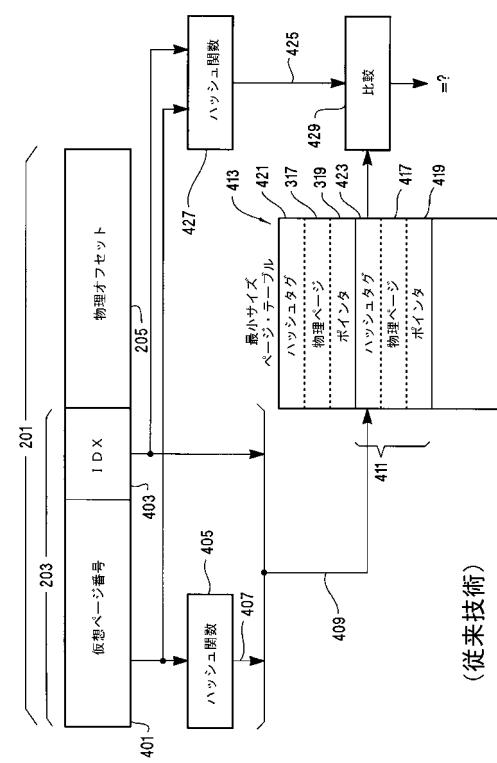

図4は、Dale Morris等によって開示された実施形態の単純化されたブロック図を示す。図4においてページ・テーブル413は、「ハッシュ・タグ」421、423を含む。ハッシュ・インデックス409は、仮想ページ番号ビット401を取り、そのビットに対してインデックス・ハッシュ関数405を実行することによって形成され、その結果は、コンピュータの基本データ幅より大きくない。同様にハッシュ・タグは、仮想ページ番号ビット401を取り、タグ・ハッシュ関数427を実行することによって形成され、その結果得られたハッシュ・タグは、コンピュータの基本データ幅より大きくない。図4はタグ・ハッシュ関数427とハッシュ・タグ421、423の間の明示的な関係を示してはいないが、タグ・ハッシュ関数427によって表されるアルゴリズムが、ハッシュ・タグ421、423が生成され、ページ・テーブル413に挿入されるときに使用されることに留意されたい。

20

【0019】

インデックス・ハッシュ関数405およびタグ・ハッシュ関数427は、所与の仮想ページ番号に対して、得られたハッシュ・インデックスおよび得られたハッシュ・タグの組合せが一意であるという範囲において望ましい(complimentary)。したがって仮想ページがアクセスされるときには、ページ・テーブル413内の(ハッシュ・タグ421、423などの)ハッシュ・タグを指すハッシュ・インデックスを生成するために、仮想ページ番号401がインデックス・ハッシュ関数405に与えられる。テーブル413から与えられたハッシュ・タグは比較関数429に回される。同時に仮想ページ番号401は、ハッシュ・タグ425を生成するためにハッシュ関数427にも与えられる。ハッシュ・タグ425とページ・テーブル413のハッシュ・タグが一致する場合には、(エントリ317、417に格納された物理ページなどの)物理ページがメモリ・アクセス動作を完了するために使用される。タグが一致しない場合、チェイン・セグメントが存在するかどうかを見るために、ページ・テーブル・エントリの(ポインタ319、419などの)ポインタがアクセスされる。チェイン・セグメントがないか、または全てのチェイン・セグメントを検索して一致するものが見つからない場合には、上述のようにオペレーティング・システムのページ・フォルト・ハンドラが呼び出される。

30

【0020】

インデックス・ハッシュ関数405およびタグ・ハッシュ関数427はハードウェアおよびソフトウェアの両方からアクセスされることに留意されたい。ハードウェアは、仮想ページ番号を物理ページ番号に変換するときにこのハッシュ関数にアクセスしなければならず、ソフトウェアは、ページ・テーブルを初期化するとき、およびページ・フォルトに対応するときに必要となるような、ページ・テーブルにアクセスし変更するときに、このハッシュ関数にアクセスしなければならない。従来の技術においてハッシュ・アルゴリズム

40

50

は、本質的に2つの形態で提供された。コンピュータ・ハードウェアは、仮想から物理への変換を迅速に進められるようにハードウェアに基づくバージョンのハッシュ・アルゴリズムを有し、オペレーティング・システムは、ページ・テーブルの初期化、アクセスまたは変更時に仮想から物理への変換を生成するためにソフトウェアに基づくバージョンのハッシュ・アルゴリズムを有した。

#### 【0021】

いくつかのコンピュータは、領域 (region) をサポートすることによって仮想アドレッシングの概念を拡大した。領域は、仮想アドレス空間を等しいサイズの領域に分割することにより、仮想アドレス空間内で独立したローカル・アドレス空間、共用アドレス空間およびグローバル・アドレス空間を効果的に作り出す機能を可能にする。通常任意の時点では、領域の1サブセットだけが活動化される。各領域には、所与の領域のアドレス変換に一意にタグを付ける領域識別子が関連付けられる。ある領域の領域識別子が特定の処理に割り当てられる場合、この領域空間は、その処理に対してローカルになる。ある領域の領域識別子が処理間で共用される場合、この領域空間は共用になる。ある領域の領域識別子が全ての処理によって共用される場合、この領域はグローバルになる。ローカル領域に対する領域識別子の変更により、仮想アドレスは1つの処理のローカル空間から別の処理のローカル空間に効果的にスワップされる。したがって領域は、処理を交換するときにTLBをフラッシュする必要を実質的になくし、それによってシステム性能全体が改善される。

#### 【0022】

##### 【発明が解決しようとする課題】

本発明は、仮想アドレスからページ・テーブル・インデックスを計算する方法および装置である。本発明は、単一のコンピュータ・アーキテクチャにおいて構成レジスタおよび事前定義数を介して2つの異なるハッシュ・ページ・テーブル構成をサポートする複合型ハッシュ・アルゴリズムによって実施される。

#### 【0023】

##### 【課題を解決するための手段】

本発明は例えば、上位3ビットが仮想領域部分を形成する64ビット仮想アドレスを有する仮想アドレス指定方式と共に使用することができる。したがって所与の任意の時点で仮想アドレスによって8領域を指定することができる。仮想アドレスの残りの61ビットは、各領域内でメモリをアドレス指定するために使用され、それによって各領域に $2^{61}$ バイトの仮想メモリを提供する。各メモリ・ページには24ビットの領域識別子が関連付けられる。したがってオペレーティング・システムは、個々の仮想アドレス空間を $2^{24}$ まで割り当てることができる。メモリ・ページは、サイズが4キロバイトから256メガバイトの範囲を取ることができる。

#### 【0024】

第1のハッシュ・ページ・テーブル構成は、領域に基づく直線的ページ・テーブルをサポートし、本明細書において「ショート・フォーマット」ページ・テーブルと呼ばれる。ショート・フォーマット・ページ・テーブルは、各仮想領域に提供され、直線的 (linear) であり、領域内の各変換に対して直線的エントリを有する。ショート・フォーマット・ページ・テーブルはチェイン・セグメントを必要とせず、ショート・フォーマット・ページ・テーブルはハッシュ・タグ・エントリを含まない。第2のハッシュ・ページ・テーブル構成は、コンピュータ・システム全体のための単一ページ・テーブルをサポートし、本明細書において「ロング・フォーマット」ページ・テーブルと呼ばれる。ロング・フォーマット・ページ・テーブルはチェイン・セグメントをサポートし、ロング・フォーマット・ページ・テーブル・エントリはハッシュ・タグ・フィールドを含む。

#### 【0025】

一実施形態において本発明の方法は、仮想アドレスからエントリ・アドレスを形成し、このエントリ・アドレスはページ・テーブルのエントリを参照する。エントリ・アドレスを形成するために、最初に仮想アドレスをJビット右にシフトすることによって仮想アドレスからハッシュ・ページ番号が形成され、ここで仮想アドレスの領域部分に関連付けられ

10

20

30

40

50

た領域の好ましいページ・サイズは、 $2^J$  バイトである。

【0026】

コンピュータ・システムがロング・フォーマット・ページ・テーブルで動作している場合、次のステップは、ハッシュ・ページ番号と仮想アドレスの領域部分から参照される領域識別子とを組み合わせることによってハッシュ・インデックスを形成すること、およびハッシュ・インデックスをKビット左にシフトすることによってテーブル・オフセットを形成することであり、ここでロング・フォーマット・ページ・テーブル・エントリはそれぞれ、 $2^K$  バイト長である。

【0027】

しかしコンピュータ・システムがショート・フォーマット・ページ・テーブルで動作している場合、次のステップは、ハッシュ・インデックスをハッシュ・ページ番号に等しく設定することによってハッシュ・インデックスを形成すること、およびハッシュ・インデックスをLビット左にシフトすることによってテーブル・オフセットを形成することであり、ここでショート・フォーマット・ページ・テーブル・エントリはそれぞれ、 $2^L$  バイト長である。

10

【0028】

次にページ・テーブルのサイズに基づきマスクが形成される。次いでページ・テーブルのベース・アドレスおよびマスクを使用して第1アドレス部分が形成され、テーブル・オフセットおよびマスクを使用して第2アドレス部分が形成される。最後に第1、第2アドレス部分を組み合わせることによってエントリ・アドレスが形成される。

20

【0029】

他の実施形態では、領域部分がエントリ・アドレス内に挿入される。フォーマットがロングに設定される場合、領域部分はページ・テーブルのベース・アドレスの領域部分から得られる。しかし領域がショートに設定される場合、領域部分は仮想アドレスの領域部分から得られる。

【0030】

他の実施形態では、フォーマットがロングに設定されるときに仮想アドレスの領域部分をハッシュ・ページ番号に挿入することによって、ロング・フォーマット・ページ・テーブルの最大サイズが増やされる。

30

【0031】

本発明は、ある実施依存パラメータに基づき本発明を実施するために使用されるロジック量を減らすいくつかの実施形態もまた含む。ロングおよびショート・フォーマット・ページ・テーブル双方のためのページ・テーブル・エントリを生成することのできる単一のアルゴリズムを提供することにより、本発明は、実行スピードに重大な影響を与えることなく、両方のページ・テーブル・フォーマットにアクセスするのに必要なロジック量を減らす。

【0032】

【発明の実施の形態】

本発明は、仮想アドレスからページ・テーブル・インデックスおよびハッシュ・タグを計算する方法および装置である。本発明は、単一のコンピュータ・アーキテクチャにおいて構成レジスタを介して2つの異なるハッシュ・テーブル構成をサポートする複合型(combined)ハッシュアルゴリズム、および仮想アドレスからハッシュ・タグを生成するアルゴリズムによって実施される。

40

【0033】

本発明をより詳細に議論する前に、本発明を実施することのできるアーキテクチャの枠組みを最初に考慮されたい。Stephen Burger等による「A Method and Apparatus for Exposing a Hardware-based Virtual Memory Hash Scheme to Software」という名称の係属中の米国特許出願を参照により本明細書に組み込む。この出願は、本発明と同じ譲受人に譲渡され、1998年10月12日に出願され、米国出願番号09/170,143が割り当てられている。Burger等は、ページ・テーブルにアクセスするためにハードウェアによって使用され

50

るハッシュ・アルゴリズムをソフトウェアに公開する2つの命令を開示している。第1の命令は、T H A S H (Translation Hashed Entry Address) 命令であり、ページ・テーブル内のエントリを指すハッシュ・インデックスを仮想アドレスから生成する。第2の命令は、T T A G (Translation Hashed Entry Tag) 命令であり、ハッシュ・インデックスから参照されるページ・テーブルのエントリ内に格納されるハッシュ・タグを仮想アドレスから生成する。この2つの命令を提供することによりB u r g e r 等は、コンピュータ・オペレーティング・システム（または他のシステム・ソフトウェア）がコンピュータ・ハードウェアによって使用されるハッシュ・アルゴリズムをコードする必要がないことを教示した。より正確には、T H A S H およびT T A G 命令は、ハードウェアによって使用されるハッシュ・アルゴリズムにソフトウェアがアクセスすることを可能にするインターフェースを提供する。本発明は、T H A S H 命令によって使用することのできる可能な1アルゴリズムを本発明が提供するという点で上記出願に関係する。さらにT T A G 命令によって使用することのできる可能な1アルゴリズムが以下に開示される。

10

#### 【 0 0 3 4 】

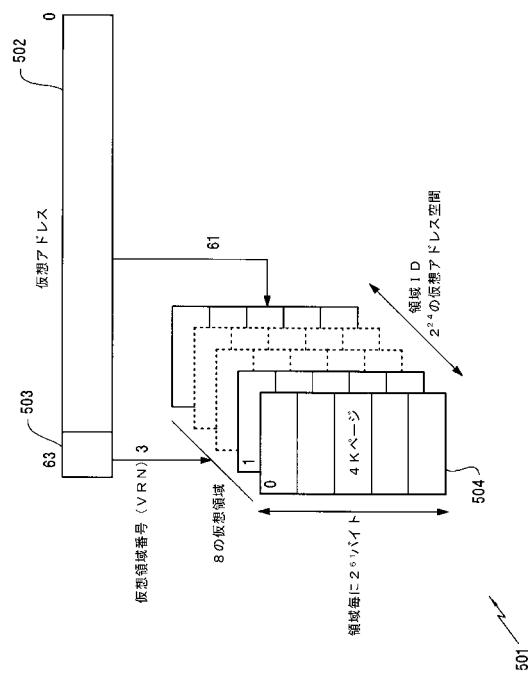

本発明は、図5に示す仮想アドレス指定方式501をサポートする。仮想アドレス502は64ビット・アドレスである。上位3ビットは仮想領域番号（V R N）503を形成する。したがって仮想アドレスにより、随時8領域を指定することができる。仮想アドレス502の残り61ビットは、各領域内でメモリをアドレス指定するために使用され、それによって各領域に $2^{61}$ バイトの仮想メモリを提供する。（ページ504などの）各メモリ・ページには24ビットの領域識別子（R I D）が関連付けられている。したがってオペレーティング・システムは、個々の仮想アドレス空間を $2^{24}$ まで割り当てることができる。以下により詳述するように、メモリ・ページはサイズが4キロバイトから256メガバイトの範囲を取ることができる。Stephen Burger等による同時係属中の「A Method and Apparatus for Pre-validating Regions in a Virtual Addressing Scheme」という名称の米国特許出願の中に仮想領域を説明する追加情報が見られる。この出願は参照により本明細書に組み込まれ、本発明と同じ譲受人に譲渡され、1998年10月12日に出願され、米国出願番号09/170,140が割り当てられている。

20

#### 【 0 0 3 5 】

本発明は、2つのページ・テーブル・フォーマットを提供するアーキテクチャをサポートする。第1のフォーマットは、領域に基づく直線的（linear）ページ・テーブルであり、本明細書において「ショート・フォーマット」ページ・テーブルと呼ばれる。ショート・フォーマット・ページ・テーブルは、図5に示すように各仮想領域に対して提供される。ショート・フォーマット・ページ・テーブルは直線的であり、領域内の各変換のための直線的エントリを有する。したがってショート・フォーマット・ページ・テーブルはチェイン・セグメントを必要とせず、ショート・フォーマット・ページ・テーブルはハッシュ・タグ・エントリを含まない。

30

#### 【 0 0 3 6 】

第2のフォーマットは、コンピュータ・システム全体のための単一の大きなページ・テーブルをサポートし、本明細書において「ロング・フォーマット」ページ・テーブルと呼ばれる。ロング・フォーマット・ページ・テーブルは、チェイン・セグメントをサポートし、ロング・フォーマット・ページ・テーブル・エントリは、ハッシュ・タグ・フィールドを含む。

40

#### 【 0 0 3 7 】

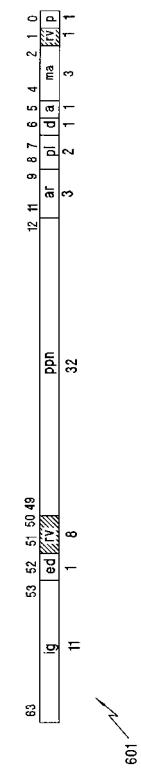

図6はショート・フォーマット・ページ・テーブル・エントリ601を示す。ショート・フォーマット・エントリ601は単一の64ビットのワードであり、したがって合計サイズ8バイトを有することに留意されたい。ショート・フォーマット・エントリ601内のフィールドを以下のテーブル1に述べる。

#### 【 0 0 3 8 】

【表1】

| エントリ・フィールド | 説明                                                                                           |    |

|------------|----------------------------------------------------------------------------------------------|----|

| p          | 存在ビット。マッピングされた物理ページがメモリ内に実際にあるかどうかを示す。                                                       | 10 |

| r v        | 予備                                                                                           |    |

| m a        | メモリ属性一マッピングされた物理ページのキャッシング可能性、コヒーレンシ、書き込みポリシおよびスペキュレーティブ属性を示す。                               |    |

| a          | アクセスト・ビット一ページ・フォルトにどのように対応するかを示す。                                                            |    |

| d          | ダーティ・ビット一ページに対するデータ書き込みによって起こるフォルトにどのように対応するかを示す。                                            |    |

| p l        | 特権レベル一ページの特権レベルを示す。                                                                          |    |

| a r        | アクセス権限一ページ・レベルの読み取り、書き込み、実行許可および特権制御。                                                        |    |

| p p n      | 物理ページ番号 (PPN) 一マッピングされた物理アドレスのうち最も重要なビット。マッピングにおいて使用されるページ・サイズ次第では、最も重要でないPPNビットのいくつかは無視される。 |    |

| i g        | オペレーティング・システムに利用可能なソフトウェア・フィールド。CPUからは無視される。                                                 |    |

| e d        | 例外延期一例外またはフォルトを延期すべきかどうかを示す。                                                                 |    |

## 【0039】

領域内の各ページに対してショート・フォーマット・エントリが存在し、仮想ハッシュ・ページ・テーブル (VHPT) 内のショート・フォーマット・エントリの位置によって変換の仮想ページ番号 (v p n) が暗示されることに留意されたい。ページ・サイズが領域内で一定であることにも留意されたい。

## 【0040】

したがって以下に述べるように、ページ・サイズは、領域に関連付けられた構成レジスタのpreferred\_page\_sizeフィールドにアクセスすることによって入手可能である。

## 【0041】

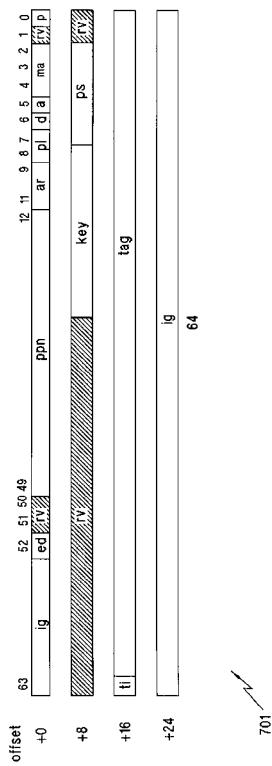

図7はロング・フォーマット・ページ・テーブル・エントリ701を示す。ロング・フォーマット・エントリ701は4つの64ビット・ワードを含み、したがって合計サイズが32バイトであることに留意されたい。ロング・フォーマット・エントリ701の第1ワードはショート・フォーマット・エントリ601と同一であり、したがって第1ワード内のフィールドは上記テーブル1に述べられている。以下のテーブル2はロング・フォーマット・エントリ701の残りのフィールドを記載する。

## 【0042】

【表2】

20

20

30

40

| エントリ・フィールド | 説明                                                                                                                                                                                                                 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| r v        | 予備                                                                                                                                                                                                                 |

| p s        | ページ・サイズマッピングのページ・サイズ。4 Kバイトより大きいページ・サイズの場合、PPNおよびVPNの下位ビットは無視される。ページ・サイズは $2^{ps}$ バイトと定義される。                                                                                                                      |

| k e y      | 保護キー—保護ドメインに対する変換に一意にタグを付ける。                                                                                                                                                                                       |

| t a g      | 変換タグ。このタグは、ロング・フォーマット・ハッシュ・インデックスと共に用いて、変換を一意に識別するために使用される。                                                                                                                                                        |

| t i        | タグ無効ビット。タグが無効であることを示す。ソフトウェアはロング・フォーマット・エントリを無効にするためにこのビットを使用することができる。                                                                                                                                             |

| i g        | オペレーティング・システムに利用可能なソフトウェア・フィールド。CPUからは無視される。ロング・フォーマットVHPTエントリの最後の64ビット（オフセット+24で開始）は通常オペレーティング・システムにより、ロング・フォーマットVHPTの同じ最初の(initial)エントリに2つ以上の仮想から物理への変換が混在する場合に別のロング・フォーマットVHPTエントリに対する関連を格納するために使用されることに留意されたい。 |

## 【0043】

全ての仮想アドレスに対して単一のロング・フォーマット・ページ・テーブルが使用されること、エントリは共にチェインすることができること、通常必ずしも全てのページに対して最初のエントリがあるわけではないことに留意されたい。したがってロング・フォーマット・ページ・テーブル・エントリは、ページ・サイズ(p s)、タグなどの追加情報を含む。VPNはハッシュ・インデックスおよびタグによって一意に表される。

## 【0044】

本発明のアルゴリズムを以下に議論する前に、次のフィールドが本発明のアルゴリズムに利用可能であることを最後に述べる。これらのフィールドのいくつかは構成レジスタに格納されるプログラム可能変数を表し、したがって特定のコンピュータ・システム上で動作するソフトウェアによって変更することができることに留意されたい。他のフィールドは、コンピュータ・システムの特定の実施態様中で変化しない定数を表し、したがって本発明のアルゴリズムの特定の実施態様中にハード・コード化されてよい。これらのフィールドを以下のテーブル3に示す。

## 【0045】

【表3】

10

20

30

40

| 構成レジスタフィールド<br>または定数 | 説明                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| page_table_format    | ロング・フォーマットまたはショート・フォーマット・ページ・テーブルが使用されているかどうかを示す。このプログラム可能フィールドはグローバルであり、メモリ内の全てのページに適用される。                                                                                                                                                                                                                                                                                                                          |    |

| preferred_page_size  | ページ内のバイト数を示す。ページ・サイズが $2^N$ バイトの場合にページ・サイズはNとコード化される。このプログラム可能フィールドは、各領域に対して指定することができる。preferred_page_sizeは各ロング・フォーマット・ページ・テーブル・エントリの(p s)フィールドにコピーされることに留意されたい。                                                                                                                                                                                                                                                     | 10 |

| page_table_size      | このプログラムの可能フィールドは、ページ・テーブルの直線部分のバイト数を示す。ショート・フォーマット・ページ・テーブルでは、page_table_sizeは各仮想領域に対して与えられ、またショート・フォーマット・ページ・テーブルは、仮想領域内のページ毎に1エントリずつ保有しなければならないので、仮想領域のサイズも決定される。ショート・テーブル・フォーマットが直線的であり成長しないので、page_table_sizeはショート・フォーマット・ページ・テーブルの正確なサイズを示す。ロング・フォーマット・ページ・テーブルにおいて、page_table_sizeはページ・テーブルの直線部分の長さを示し、チェイン・セグメントが追加されるにつれてページ・テーブルはさらに深く(deeper)成長することができる。ページ・テーブルのサイズが $2^N$ バイトの場合にページ・テーブル・サイズはNとコード化される。 | 20 |

| page_table_base      | このプログラム可能フィールドは、メモリ内の第1ページ・テーブル・エントリのアドレスを示す。ショート・フォーマット・ページ・テーブルが使用されるとき、各仮想領域は自分自身のページ・テーブルを含み、page_table_baseは各仮想領域に対して与えられる。ロング・フォーマット・ページ・テーブルが使用されるとき、単一のページ・テーブルが提供され、単一のpage_table_baseが第1ロングフォーマット・ページ・テーブル・エントリのアドレスを示す。ビット{63 : min_pt_size} (下記参照)だけしか格納する必要がないことに留意されたい。page_table_baseが $2^{\text{page\_table\_size}}$ の境界上になければならないことにも留意されたい。                                                        | 30 |

| impl_va_msb          | この定数は、特定のコンピュータ・システムによってサポートされる仮想アドレスのうち最も重要なビットを示す。                                                                                                                                                                                                                                                                                                                                                                 | 40 |

| min_pt_size          | この定数は、ロングおよびショート・フォーマット・ページ・テーブル双方の(バイト単位の)最小サイズを示す。ページ・テーブルの最小サイズ数が $2^N$ の場合、最小ページ・テーブル・サイズはNと表される。                                                                                                                                                                                                                                                                                                                |    |

## 【0046】

上述のように領域に基づくショート・フォーマットにおいて、各領域に対する直線的ページ・テーブルは、参照される領域自体の中にある。結果としてショート・フォーマットV H P Tは、各領域内でpage\_table\_baseのビット{60 : min\_pt\_size}によって固定される別々の領域毎のページ・テーブルからなる。V H P Tが利用できる領域に対してオペレ

ーティング・システムは、領域毎の直線的ページ・テーブルを維持する必要がある。以下のショート・フォーマット・アルゴリズムにおいて定義するように、ショート・フォーマットV H P Tへの直線的インデックスを計算するために、変換すべき仮想アドレス( V A )、領域のpreferred\_page\_size、page\_table\_baseおよびpage\_table\_sizeが使用される。

#### 【 0 0 4 7 】

ショート・フォーマットV H P Tのサイズ(page\_table\_size)は、マッピングされた仮想アドレス空間のサイズを定義する。ショート・フォーマットにおいてアーキテクチャに適合する最大テーブル・サイズは、領域毎に $2^{52}$ バイトである。4キロバイトのページを使用して領域全体( $2^{61}$ バイト)をマッピングするには、 $2^{(61-12)}$ (あるいは $2^{49}$ )のページがマップ可能でなければならない。ショート・フォーマットV H P Tエントリは8バイト(あるいは $2^3$ バイト)大である。結果として最大テーブル・サイズは、領域毎に $2^{(61-12+3)}$ (あるいは $2^{52}$ )バイトである。 $2^{61}$ より小さいアドレス空間をマッピングするためにショート・フォーマットが使用される場合、より小さいショート・フォーマット・テーブル(page\_table\_size < 52)を使用することができる。4キロバイトのページで $2^N$ のアドレス空間をマッピングするには、(N-9)の最小page\_table\_sizeが必要である。

#### 【 0 0 4 8 】

ショート・フォーマットV H P Tを使用するとき、(上述の)T H A S H命令は領域に基づくショート・フォーマット・インデックスを返す。T T A G命令は、これもまた上述したが、ショート・フォーマットでは使用されない。以下のショート・フォーマット・ハッシング・アルゴリズムでは、V H P Tエントリ・アドレスの要求されている仮想アドレス( V A )が関数tlb\_vhpt\_hash\_shortに渡される。この関数は、仮想アドレスに対応するエントリのアドレス(vhpt\_addr)を返す。

#### 【 0 0 4 9 】

#### 【表 4】

#### ショート・フォーマット・ハッシング・アルゴリズム

```

1:     tlb_vhpt_hash_short(VA)                                30

2:     {

3:         hash_page_number = VA{impl_va_msb:0} u>> preferred_page_size;

4:         hash_index = hash_page_number;

5:         vhpt_offset = hash_index << 3;

6:         vhpt_region= VA{63:61};

7:         pmask = 2page_table_size - 1;

8:         vhpt_addr = (vhpt_region<<61) |                      40

9:             (((page_table_base{60:min_pt_size} & ~pmask{60:min_pt_size}) |

10:              (vhpt_offset{60:min_pt_size} & pmask{60:min_pt_size})) << min_pt_size) |

11:              vhpt_offset{min_pt_size-1:0};

12:         return vhpt_addr;

13:     }

```

#### 【 0 0 5 0 】

10

20

40

50

ショート・フォーマット・ハッシング・アルゴリズムのライン1において、関数tblb\_vhpt\_hash\_shortが呼び出され、仮想アドレス(VA)がこの関数に渡される。ライン3では、preferred\_page\_sizeによってVAを除することによりhash\_page\_numberが計算される。(定数impl\_va\_msbによって定義されるように)VAのうち特定のコンピュータ・システムの実施によって使用されるビットだけしか使用されないことに留意されたい。除算演算は、VAをNビット右にシフトすることによって達成され、ここで、ページ・サイズは $2^N$ である。右へのシフトは符号なしである。上述のように一実施形態では、ページ・サイズが4キロバイトと256メガバイトの間で変化する可能性があるので、VAは12ビットないし28ビット右にシフトされる。

【0051】

10

ライン4において、hash\_indexがhash\_page\_numberに等しく設定される。ショート・フォーマット・アルゴリズムにおいてこのステップは多少冗長であるが、以下に見られるようにショート・フォーマットとロング・フォーマットのアルゴリズムを調和させるために含められている。上記の議論のように、ショート・フォーマットVHPT内の各エントリは8バイト幅である。したがってライン5において、ページ・テーブルへのオフセット(vhpt\_offset)がhash\_page\_numberに8をかけることによって計算される。これはhash\_indexを3ビット位置だけ左にシフトすることによって実行される。

【0052】

ライン6ではVHPTの領域(vhpt\_region)が計算される。上記で議論したように、ショート・フォーマットVHPTを使用するとき各領域がそれ自体のVHPTを含むので、VHPTの領域はVAの領域と同じである。したがってVHPTの領域は、単純にVAのビット{63:61}である。

20

【0053】

ライン7では、page\_table\_sizeに対応するビット数だけ2を累乗し、1を引くことによってマスク(pmask)が形成される。例えば最小4キロバイトのpreferred\_page\_sizeを用いて領域全体( $2^{61}$ バイト)をマッピングするには、 $2^{(61-12)}$ (あるいは $2^9$ )ページがマッピング可能でなければならない。各ショート・フォーマットVHPTエントリが8(あるいは $2^3$ )バイトなので、最大page\_table\_sizeは $2^{52}$ である。この第1の例では、pmaskの上位12ビットが「0」であり、下位52ビットが「1」である。同様に最大256メガバイトのpreferred\_page\_sizeを用いて領域全体( $2^{61}$ バイト)をマッピングするには、 $2^{(61-28)}$ (あるいは $2^{33}$ )ページがマッピング可能でなければならない。各ショート・フォーマットVHPTエントリが8(あるいは $2^3$ )バイトなので、(全領域をマッピングするときの)最小page\_table\_sizeは $2^{36}$ である。この第2の例では、pmaskの上位28ビットが「0」であり、下位36ビットが「1」である。もちろん $2^{61}$ バイトの領域全体より少ないバイトをマッピングすることもまた可能であり、preferred\_page\_size次第で $2^{36}$ より小さいpage\_table\_sizeになる可能性がある。以下に述べるように、マスクは、VAに対応する得られたVHPTエントリのアドレスを形成する構成要素を選択するために使用される。

30

【0054】

40

ライン8~11では、いくつかの構成要素を合わせて論理和を取ることにより、VAに対応するVHPTのエントリのアドレス(vhpt\_addr)が計算される。最初にライン8において、vhpt\_regionを61ビット左にシフトすることによって領域構成要素が計算され、それによってvhpt\_regionをvhpt\_addrの適切な位置に位置付ける。

【0055】

ライン9~11を議論する前に、min\_pt\_sizeがコンピュータ・システムの各実施態様に對して定義される定数であることを考慮されたい。この定数min\_pt\_sizeはNと表され、ここでページ・テーブルの最小サイズは $2^N$ バイトである。したがってvhpt\_addrのビット{min\_pt\_size-1:0}がvhpt\_offsetによって提供されることが常に分かる。しかしビット{60:min\_pt\_size}は、page\_table\_sizeに基づきpage\_table\_baseまたはvhpt\_offsetのいずれかによって提供される。したがってライン7で計算されたpmaskは、page\_

50

table\_sizeに基づきpage\_table\_baseおよびvhpt\_offsetの適切なビットを選択するために使用される。

【0056】

最小ページ・テーブル・サイズを定義することは、本発明によるコンピュータ・システムを実施するのに必要なロジック量を（ある程度）減らす。例えば各page\_table\_baseを保有するレジスタは、ビット{63: min\_pt\_size}しか格納する必要がない。ライン9、10を参照して以下に議論する論理積および論理和演算の幅もまたmin\_pt\_sizeビットだけ減らすことができる。一実施形態においてmin\_pt\_sizeは15であり、その結果、最小ページ・テーブル・サイズは32キロバイトとなる。

【0057】

したがってライン9において、page\_table\_baseのビット{60: min\_pt\_size}は、pmaskのビット{60: min\_pt\_size}の反転との論理積を取られ、ライン10において、vhpt\_offsetのビット{60: min\_pt\_size}は、pmaskのビット{60: min\_pt\_size}との論理積を取られる。この2つの論理積演算の結果を合わせて論理和が取られ、その結果がmin\_pt\_sizeビット位置だけ左にシフトされる。したがってライン9、10は、このvhpt\_addrの構成要素を形成するためにpmaskおよびmin\_pt\_sizeを使用し、この構成要素はV H P Tのサイズに基づき変化し、min\_pt\_sizeに基づきvhpt\_offsetだけからは与えられないことが分かる。この構成要素がライン8で計算された領域構成要素との論理和を取られることに留意されたい。

【0058】

最後にライン11において、vhpt\_offset（ビット{min\_pt\_size - 1: 0}）だけに基づくvhpt\_addrの構成要素は、vhpt\_addrを形成するために上記で計算された他の2つの構成要素との論理和を取られる。ライン12において、関数tbl\_vhpt\_hash\_shortが終了し、vhpt\_addrを呼び出しルーチンに返す。

【0059】

ショート・フォーマットV H P Tにおいて各V H P Tエントリは、仮想アドレスに一意に対応する。しかしロング・フォーマットV H P Tでは、複数の仮想アドレスがV H P Tへの第1エントリを共用する可能性があり、オペレーティング・システムによって第1エントリにチェインされたV H P Tエントリにその後の変換が格納される。第1エントリがアクセスされた後に、仮想から物理への変換に対応する（図7に示す）タグを見つけるために、第1エントリおよびリンクされたエントリを検索することにより、仮想から物理への適切な変換が見つけられる。ロング・フォーマット・アルゴリズムを以下に説明する。混乱を避けるために、全てのアルゴリズムに対して一意のライン番号が使用されていることに留意されたい。

【0060】

【表5】

10

20

30

## ロング・フォーマット・ハッシング・アルゴリズム

```

14:     tlb_vhpt_hash_long (VA, region_id)

15:     {

16:         hash_page_number = VA{impl_va_msb:0} u>> preferred_page_size;

17:         hash_index = ((VA{63:61} << 52) | hash_page_number) ^ region_id;

18:         vhpt_offset = hash_index << 5;                                10

19:         vhpt_region= page_table_base{63:61};

20:         pmask = 2page_table_size - 1;

21:         vhpt_addr = (vhpt_region<<61) |                                20

22:             (((page_table_base{60:min_pt_size} & ~pmask{60:min_pt_size}) |

23:             (vhpt_offset{60:min_pt_size} & pmask{60:min_pt_size})) << min_pt_size) |

24:             vhpt_offset{min_pt_size-1:0};

25:         return vhpt_addr;

26:     }

```

### 【 0 0 6 1 】

ロング・フォーマット・ハッシングアルゴリズムのライン 14において、関数 `tlb_vhpt_hash_long` が呼び出され、その関数に仮想アドレス (VA) および 24 ビットの `region_id` が渡される。ライン 16において、VA を `preferred_page_size` で除することにより `hash_page_number` が計算される。`(impl_va_msb` によって定義されるように) VA のうち特定のコンピュータ・システムの実施によって使用されるビットだけしか使用されないことに留意されたい。除算演算は、VA を N ビット右にシフトすることによって達成され、ここでページ・サイズは  $2^N$  である。右のシフトは符号なしである。上述のように、一実施形態においてページ・サイズは、4 キロバイトと 256 メガバイトの間で変化する可能性があるので、VA は 12 ビットないし 28 ビット右にシフトされる。 30

### 【 0 0 6 2 】

ライン 17において `hash_index` が形成される。上述のように、`hash_page_number` は VA を少なくとも 12 ビット右にシフトすることによって形成される。したがって `hash_page_number` の最大値は  $2^{5^2}$  であり、`hash_page_number` のビット {64 : 52} は「0」である。ライン 17 の最初の部分は、VA のビット {63 : 61} (VA の領域部分) を 52 ビット左にシフトし、その結果と `hash_page_number` との論理和を取る。これにより、ロング・フォーマット V H P T の最大可能サイズが  $2^{5^2}$  エントリ (`hash_page_numbers` の最大値) から  $2^{5^5}$  エントリに増える。最後に `hash_index` を形成するために、ライン 17 の最初の部分の結果と 24 ビットの `region_id` との排他的論理和が取られる。 40

### 【 0 0 6 3 】

上述のように、ロング・フォーマット V H P T エントリは 32 (あるいは  $2^5$ ) バイトである。したがってライン 18 では、`hash_index` を 5 ビット位置だけ左にシフトすることによって `vhpt_offset` が形成される。ライン 19 では、`page_table_base` のビット {63 : 61} を取り出すことによって `vhpt_region` が形成される。各領域内に存在するショート・フォーマット V H P T とは対照的に、ロング・フォーマット V H P T はシステム全体に対して 1 つしか定義されない。

### 【 0 0 6 4 】

ライン17～19においてhash\_index、vhpt\_offset、vhpt\_regionを計算したのち、ライン20～24ではpmaskおよびvhpt\_addrが計算される。ロング・フォーマット・アルゴリズムのライン20～24は、ショート・フォーマット・アルゴリズムのライン7～11と同一であることに留意されたい。したがってvhpt\_addrは、ショート・フォーマット・アルゴリズムを参照しながら上に述べたのと同じ方法で形成される。最後にライン25において、関数tblb\_vhpt\_hash\_longが終了し、vhpt\_addrを呼び出しルーチンに返す。

【0065】

ロング・フォーマットV H P Tを使用するときにvhpt\_addrは、ロング・フォーマットV H P Tエントリ内に格納されたタグと組み合わせて、仮想から物理への変換を一意に識別することに留意されたい。ロング・フォーマット・ハッシングアルゴリズムで一意性を保証するタグ・アルゴリズムを以下に説明する。

【0066】

【表6】

#### タグ・アルゴリズム

```

27:     tag(VA, region_id)

28:     {

29:         pmask = 2page_table_size - 1;

30:         tpn = VA & -pmask;

31:         tag_for_entry = (region_id << 40) | (tpn >> 12);

32:         return tag_for_entry;

33:     }

```

【0067】

本発明にしたがって設計されたコンピュータ・システムは、ロングおよびショート・フォーマットV H P Tの両方をサポートする。上に議論したように、ロングおよびショート・フォーマット・ハッシングアルゴリズムはハードウェアにて実施されることが好ましい。当技術分野で知られているように、特定の関数を実施するのに必要なトランジスタの数を最小化しながら関数の実行スピードを最小化することが常に望ましい。

【0068】

ロングおよびショート・フォーマット・アルゴリズムを検査すると、アルゴリズム間の多数の類似点が注目されよう。本発明によれば、組み合わされたショートおよびロング・フォーマット・アルゴリズムは以下に与えられる。ショートおよびロング・フォーマット・アルゴリズムを組み合わせることにより両方のアルゴリズムを実施するのに必要なトランジスタ数は、どちらのアルゴリズムの実行スピードにも大きな影響を与えることなく最小化される。複合型ハッシングアルゴリズムを以下に説明する。

【0069】

【表7】

10

20

30

40

### 複合型ハッシング・アルゴリズム

```

34:     tlb_vhpt_hash_combined (VA, region_id)

35:     {

36:         hash_page_number = VA{impl_va_msb:0} u>> preferred_page_size;

37:         if (page_table_format == long) {

38:             hash_index = ((VA{63:61} << 52) | hash_page_number) ^ region_id;      10

39:             vhpt_offset = hash_index << 5;

40:             vhpt_region= page_table_base{63:61};

41:         }

42:         else {

43:             hash_index = hash_page_number;

44:             vhpt_offset = hash_index << 3;

45:             vhpt_region= VA{63:61};      20

46:         }

47:         pmask = 2^page_table_size - 1;

48:         vhpt_addr = (vhpt_region<<61) |

49:             (((page_table_base{60:min_pt_size} & ~pmask{60:min_pt_size}) |      30

50:             (vhpt_offset{60:min_pt_size} & pmask{60:min_pt_size})) << min_pt_size) |

51:             vhpt_offset{min_pt_size-1:0};

52:         return vhpt_addr;

53:     }

```

#### 【 0 0 7 0 】

基本的に、複合型ハッシングアルゴリズムは、ロングおよびショート・フォーマット・ハッシングアルゴリズムの共通要素を組合わせ、アルゴリズムの異なる部分は、page\_table\_formatが「ロング」に設定されているかどうかをテストするIF-THEN-ELSEブロック内で与えられる。したがって複合型ハッシングアルゴリズムのライン34において、関数tlb\_vhpt\_hash\_combinedが呼び出され、その関数に仮想アドレス(VA)および24ビットのregion\_idが渡される。page\_table\_formatが「ロング」に設定されていない場合、region\_idが使用されないことに留意されたい。ライン36では、ショート・フォーマット・ハッシングアルゴリズムのライン3およびロング・フォーマット・ハッシングアルゴリズムのライン16と同様に、VAをpreferred\_page\_sizeで割ることによってhash\_page\_numberが計算される。

#### 【 0 0 7 1 】

ライン37ではpage\_table\_formatが、「ロング」に設定されているかどうかを見るためにテストされる。設定されている場合には、ロング・フォーマット・ハッシングアルゴリズムのライン17、18、19とそれぞれ同様に、hash\_index、vhpt\_offset、vhpt\_regionがライン38、39、40においてそれぞれ計算される。page\_table\_formatが「ロング」に設定されていない場合、ショート・フォーマット・ハッシングアルゴリズムのライン4、5、6とそれぞれ同様に、hash\_index、vhpt\_offset、vhpt\_regionがライン43、

44、45においてそれぞれ計算される。その後、pmaskおよびvhpt\_addrが計算され、ライン47～52において（呼び出しルーチンにvhpt\_addrを返して）関数が終了する。ライン47～52が、ショート・フォーマット・ハッシング・アルゴリズムのライン7～12と同一であり、またロングフォーマット・ハッシングアルゴリズムのライン20～25と同一であることに留意されたい。

#### 【0072】

したがって本発明は、（各V H P Tエントリが仮想から物理への変換を一意に識別する）ショート・フォーマットV H P T、または（格納されたタグと組み合わされた各最初のV H P Tが仮想から物理への変換を一意に識別する）ロングフォーマットV H P Tのいずれかに対するインデックスを生成することのできる、複合型ハッシングアルゴリズムを提供する。本発明の複合型アルゴリズムを実施する者はまた、ロングおよびショート・フォーマットに対して別々に実行される複合型ハッシングアルゴリズムの一部に別の共通点を見つけるであろう。例えばライン39、44で実行される左のシフトは、page\_table\_formatが「ロング」に設定されている場合にさらに2ビット位置左にシフトする单一のシフト回路によって実施することができる。同様にライン40、45のvhpt\_regionの計算は、page\_table\_base、またはpage\_table\_formatに基づくVAから、ビット63～61を選択するためにマルチプレクサを使用することができる。本発明の複合型ハッシングアルゴリズムを実施するために論理回路を設計する者は、本発明の実施に必要なロジックを最小化する他の方法にも気付くであろう。

#### 【0073】

好ましい実施形態を参照しながら本発明を述べて来たが、本発明の精神および範囲を逸脱することなく、形態および詳細において変更を加えることができることを当業者なら認識するであろう。

#### 【0074】

本発明は例として以下の実施態様を含む。

#### 【0075】

（1）ページ・テーブルのエントリを参照するエントリ・アドレスを仮想アドレスから形成する方法であって、前記仮想アドレスが、領域を識別する活動領域識別子を参照する領域部分を含み、前記ページ・テーブルが、ロング・フォーマットおよびショート・フォーマットを仮定することができ、

前記仮想アドレスをJビット右にシフトすることによって前記仮想アドレスからハッシュ・ページ番号を形成するステップであって、前記仮想アドレスの前記領域部分に関連付けられた領域の好ましいページ・サイズが $2^J$ バイトであるステップと、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記仮想アドレスの前記領域部分によって参照される前記領域識別子および前記ハッシュ・ページ番号を組み合わせることによりハッシュ・インデックスを形成するステップと、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ハッシュ・インデックスをKビット左にシフトすることによってテーブル・オフセットを形成するステップであって、各ロング・フォーマット・ページ・テーブル・エントリが $2^K$ バイト長であるステップと、

前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記ハッシュ・インデックスを前記ハッシュ・ページ番号に等しく設定することによりハッシュ・インデックスを形成するステップと、

前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記ハッシュ・インデックスをLビット左にシフトすることによってテーブル・オフセットを形成するステップであって、各ショート・フォーマット・ページ・テーブル・エントリが $2^L$ バイト長であるステップと、

前記ページ・テーブルのサイズに基づきマスクを形成するステップと、

前記ページ・テーブルのベース・アドレスおよび前記マスクを使用して第1アドレス部分を形成するステップと、

10

20

30

40

50

前記テーブル・オフセットおよび前記マスクを使用して第2アドレス部分を形成するステップと、

前記第1アドレス部分および前記第2アドレス部分を組み合わせることによって前記エントリ・アドレスを形成するステップと、を含む方法。

【0076】

(2) 前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ページ・テーブルの前記ベース・アドレスから前記領域部分を抽出することによってページ・テーブル領域を形成するステップと、

前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記仮想アドレスから前記領域部分を抽出することによってページ・テーブル領域を形成するステップとをさらに含む方法であって、

前記ページ・テーブル領域、前記第1アドレス部分および第2アドレス部分を組み合わせることによって前記エントリ・アドレスを形成するステップであって、前記ページ・テーブル領域が前記エントリ・アドレスの領域部分に挿入されるステップを含む前記(1)に記載の方法。

【0077】

(3) 前記仮想アドレスからハッシュ・ページ番号を形成するステップが、前記仮想アドレスの実装された部分だけをJビット右にシフトすることによって前記仮想アドレスからハッシュ・ページ番号を形成するステップであって前記仮想アドレスの前記領域部分に関連付けられた領域の好ましいページ・サイズが $2^J$ バイトであるステップを含む前記(1)に記載の方法。

【0078】

(4) 前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記仮想アドレスの前記領域部分から参照される前記領域識別子および前記ハッシュ・ページ番号を組み合わせることによってハッシュ・インデックスを形成するステップが、前記仮想アドレスの前記領域部分と前記ハッシュページ番号を組み合わせるステップを含む前記(1)に記載の方法。

【0079】

(5) 前記仮想アドレスの前記領域部分と前記ハッシュ・ページ番号を組み合わせるステップが、前記仮想アドレスの前記領域部分のビットを前記ハッシュ・ページ番号内に、前記仮想アドレスをJビット右にシフトすることに基づき空いていると分かっている前記ハッシュ・ページ番号のビット位置に挿入するステップを含む前記(4)に記載の方法。

【0080】

(6) 前記ページ・テーブルの前記サイズに基づきマスクを形成するステップが、前記マスクを $2^M - 1$ に等しく設定するステップであって、 $2^M$ が前記ページ・テーブルの前記サイズであるステップを含む前記(1)に記載の方法。

【0081】

(7) 前記ページ・テーブルのベース・アドレスおよび前記マスクを使用して第1アドレス部分を形成するステップが、

前記ページ・テーブルの前記ベース・アドレスおよび前記マスクの反転に対して論理積演算を実行することによって第1アドレス部分を形成するステップを含み、

前記テーブル・オフセットおよび前記マスクを使用して第2アドレス部分を形成するステップが、

前記テーブル・オフセットおよび前記マスクに対して論理積演算を実行することによって第2アドレス部分を形成するステップを含む前記(6)に記載の方法。

【0082】

(8) 前記第1アドレス部分および前記第2アドレス部分を組み合わせることによって前記エントリ・アドレスを形成するステップが、前記第1アドレス部分および前記第2アドレス部分に対して論理和演算を実行することによって前記エントリ・アドレスを形成するステップを含む前記(1)に記載の方法。

10

20

30

40

50

## 【0083】

(9)  $2^N$  バイトの最小ページ・テーブル・サイズが定義されており、前記ページ・テーブルのベース・アドレスおよび前記マスクを使用して第1アドレス部分を形成するステップが、

前記ページ・テーブルの前記ベース・アドレスの下位Nビットを含まない前記ページ・テーブルの前記ベース・アドレス、および前記マスクの下位Nビットを含まない前記マスクを使用して第1アドレス部分を形成するステップを含み、

前記テーブル・オフセットおよび前記マスクを使用して第2アドレス部分を形成するステップが、

前記テーブル・オフセットの下位Nビットを含まない前記テーブル・オフセット、および前記マスクの下位Nビットを含まない前記マスクを使用して第2アドレス部分を形成するステップを含み、

前記第1アドレス部分および前記第2アドレス部分を組み合わせることによって前記エントリ・アドレスを形成するステップが、

前記第1アドレス部分および前記第2アドレス部分を組み合わせて結果を形成し、その結果をNビット左にシフトし、その結果と前記テーブル・オフセットの下位Nビットを組み合わせることにより前記エントリ・アドレスを形成するステップを含む前記(1)に記載の方法。

## 【0084】

(10) ページ・テーブルのエントリを参照するエントリ・アドレスを仮想アドレスから形成する方法であって、前記仮想アドレスが、領域を識別する活動領域識別子を参照する領域部分を含み、前記ページ・テーブルの最小サイズが $2^N$  バイトであり、前記ページ・テーブルが、ロング・フォーマットおよびショート・フォーマットを仮定することができ、

前記仮想アドレスの実装された部分だけをJビット右にシフトすることによって前記仮想アドレスからハッシュ・ページ番号を形成するステップであって、前記仮想アドレスの前記領域部分に関連付けられた前記領域の好ましいページ・サイズが $2^J$  バイトであるステップと、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ハッシュ・ページ番号、前記仮想アドレスの前記領域部分、および前記仮想アドレスの前記領域部分から参照される前記領域識別子を組み合わせることによってハッシュ・インデックスを形成するステップであって、前記仮想アドレスをJビット右にシフトすることに基づき空いていることが分かっている前記ハッシュ・ページ番号のビット位置に前記仮想アドレスの前記領域部分が組み合わされて挿入されるステップと、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ハッシュ・インデックスをKビット左にシフトすることによってテーブル・オフセットを形成するステップであって、各ロング・フォーマット・ページ・テーブル・エントリが $2^K$  バイト長であるステップと、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ページ・テーブルのベース・アドレスから前記領域部分を抽出することによってページ・テーブル領域を形成するステップと、

前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記ハッシュ・インデックスを前記ハッシュ・ページ番号に等しく設定することによってハッシュ・インデックスを形成するステップと、

前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記ハッシュ・インデックスをLビット左にシフトすることによってテーブル・オフセットを形成するステップであって、各ショート・フォーマット・ページ・テーブル・エントリが $2^L$  バイト長であるステップと、

前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記仮想アドレスから前記領域部分を抽出することによってページ・テーブル領域を形成するステ

10

20

30

40

50

ップと、

2をM乗し1を引いてマスクを形成するステップであって、 $2^M$ が前記テーブルのサイズであるステップと、

前記ページ・テーブルの前記ベース・アドレスの下位Nビットを含まない前記ページ・テーブルの前記ベース・アドレス、および前記マスクの反転の下位Nビットを含まない前記マスクの反転に対して論理積演算を実行することによって第1アドレス部分を形成するステップと、

前記テーブル・オフセットの下位Nビットを含まない前記テーブル・オフセット、および前記マスクの下位Nビットを含まない前記マスクに対して論理積演算を実行することによって第2アドレス部分を形成するステップと、

前記第1アドレス部分および前記第2アドレス部分に対して論理積演算を実行して第1の結果を形成し、この第1の結果をNビット左にシフトして第2の結果を形成し、前記ページ・テーブル領域、前記第2の結果、および前記テーブル・オフセットの下位Nビットに対して論理和演算を実行することによって前記エントリ・アドレスを形成するステップであって、前記ページ・テーブル領域が前記エントリ・アドレスの領域部分に挿入されるステップと、を含む方法。

#### 【0085】

(11) 領域を識別する活動領域識別子を参照する領域部分を含む仮想アドレスによってアドレス指定される仮想アドレス空間を定義するアーキテクチャを有するコンピュータ・システムであって、

ページ・テーブル・ベース・アドレスによって固定されたページ・テーブルを含むメモリ・ユニットであって、ページ・テーブルがロング・フォーマットおよびショート・フォーマットを仮定できるメモリ・ユニットと、

命令を実行するプロセッサであって、仮想アドレスから前記ページ・テーブルにエントリ・アドレスを生成することができるページ・テーブル・エントリ・アドレス生成ユニットであるプロセッサと、を有し、

前記エントリ・アドレス生成ユニットは、

前記仮想アドレスをJビット右にシフトすることによって前記仮想アドレスからハッシュ・ページ番号を形成するハッシュ・ページ番号生成回路であって、前記仮想アドレスの前記領域部分に関連付けられた前記領域の好ましいページ・サイズが $2^J$ バイトであるハッシュ・ページ番号生成回路と、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ハッシュ・ページ番号と前記仮想アドレスの前記領域部分から参照される前記領域識別子を組み合わせることによってハッシュ・インデックスを形成し、前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記ハッシュ・インデックスを前記ハッシュ・ページ番号に等しく設定することによってハッシュ・インデックスを形成するハッシュ・インデックス生成回路と、前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ハッシュ・インデックスをKビット左にシフトすることによってテーブル・オフセットを形成し、ここで各ロング・フォーマット・ページ・テーブル・エントリが $2^K$ バイト長であり、前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記ハッシュ・インデックスをLビット左にシフトすることによってテーブル・オフセットを形成し、ここで各ショート・フォーマット・ページ・テーブル・エントリが $2^L$ バイト長であるテーブル・オフセット生成回路と、

前記ページ・テーブルの前記サイズに基づきマスクを形成するマスク生成回路と、

前記ページ・テーブル・ベース・アドレスおよび前記マスクを使用して第1アドレス部分を形成する第1アドレス部分生成回路と、

前記テーブル・オフセットおよび前記マスクを使用して第2アドレス部分を形成する第2アドレス部分生成回路と、

前記第1アドレス部分および前記第2アドレス部分を組み合わせることによって前記エントリ・アドレスを形成するエントリ・アドレス生成回路と、を含むコンピュータ・システ

10

20

30

40

50

ム。

【0086】

(12) 前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ページ・テーブル・ベース・アドレスから前記領域部分を抽出することによってページ・テーブル領域を形成し、前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記仮想アドレスから前記領域部分を抽出することによってページ・テーブル領域を形成するページ・テーブル領域生成回路と、

前記ページ・テーブル領域、前記第1アドレス部分および前記第2アドレス部分を組み合わせることによって前記エントリ・アドレスを形成する前記エントリ・アドレス生成回路であって、前記ページ・テーブル領域が前記エントリ・アドレスの領域部分に挿入されるエントリ・アドレス生成回路とを、前記プロセッサの前記ページ・テーブル・エントリ・アドレス生成ユニットがさらに備える前記(11)に記載のコンピュータ・システム。

10

【0087】

(13) 前記ハッシュ・ページ番号生成回路が、前記仮想アドレスの実装されている部分だけをJビット右にシフトすることによって前記仮想アドレスから前記ハッシュ・ページ番号を形成するコンピュータ・システムであって、前記仮想アドレスの前記領域部分に関連付けられた前記領域の前記好ましいサイズが $2^J$ バイトである前記(11)に記載のコンピュータ・システム。

【0088】

(14) 前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ハッシュ・インデックス生成ユニットが前記ハッシュ・ページ番号、前記仮想アドレスの前記領域部分から参照される前記領域識別子、および前記仮想アドレスの前記領域部分を組み合わせることによって前記ハッシュ・インデックスを形成する前記(11)に記載のコンピュータ・システム。

20

【0089】

(15) 前記ハッシュ・インデックス生成ユニットが、前記ハッシュ・ページ番号に前記仮想アドレスの前記領域部分のビットを、前記仮想アドレスをJビット右にシフトすることに基づき空いていることが分かっている前記ハッシュ・ページ番号のビット位置に挿入もする前記(14)に記載のコンピュータ・システム。

30

【0090】

(16) 前記マスク生成ユニットが、前記マスクを $2^M - 1$ に等しく設定することによって前記マスクを形成するコンピュータ・システムであって、 $2^M$ が前記ページ・テーブルのサイズである前記(15)に記載のコンピュータ・システム。

【0091】

(17) 前記第1アドレス部分生成回路が前記ページ・テーブル・ベース・アドレスと前記マスクの反転に対して論理積演算を実行することによって前記第1アドレス部分を形成し、前記第2アドレス部分生成回路が前記テーブル・オフセットと前記マスクに対して論理積演算を実行することによって前記第2アドレス部分を形成する前記(16)に記載のコンピュータ・システム。

40

【0092】

(18) 前記エントリ・アドレス生成回路が前記第1アドレス部分および前記第2アドレス部分に対して論理和演算を実行することによって前記エントリ・アドレスを形成する前記(11)に記載のコンピュータ・システム。

【0093】

(19)  $2^N$ バイトの最小ページ・テーブル・サイズが定義され、前記第1アドレス部分生成回路が、前記ページ・テーブル・ベース・アドレスの下位Nビットを含まない前記ページ・テーブル・ベース・アドレスおよび前記マスクの下位Nビットを含まない前記マスクを使用して前記第1アドレス部分を形成し、前記第2アドレス生成回路が、前記テーブル・オフセットの下位Nビットを含まない前記テーブル・オフセット、および前記マスクの下位Nビットを含まない前記マスクを使用して前記第2アドレス部分を形成し、前記工

50

ントリ・アドレス生成回路が、前記第1アドレス部分および前記第2アドレス部分を組み合わせて結果を形成し、前記結果をNビット左にシフトし、前記結果と前記テーブル・オフセットの下位Nビットを組み合わせることによって前記エントリ・アドレスを形成する前記(11)に記載のコンピュータ・システム。

【0094】

(20) 領域を識別する活動領域識別子を参照する領域部分を含む仮想アドレスによってアドレス指定される仮想アドレス空間を定義するアーキテクチャを有するコンピュータ・システムであって、

ページ・テーブル・ベース・アドレスによって固定されたページ・テーブルを含むメモリ・ユニットであって、ページ・テーブルがロング・フォーマットおよびショート・フォーマットを仮定でき、最小サイズが $2^N$ ビットであるメモリ・ユニットと、

命令を実行するプロセッサであって、仮想アドレスからページ・テーブルにエントリ・アドレスを生成することができるページ・テーブル・エントリ・アドレス生成ユニットであるプロセッサとを含み、

前記エントリ・アドレス生成ユニットは、

前記仮想アドレスの実装されている部分だけをJビット右にシフトすることによって前記仮想アドレスからハッシュ・ページ番号を形成するハッシュ・ページ番号生成回路であって、前記仮想アドレスの前記領域部分に関連付けられた領域の好ましいページ・サイズが $2^J$ バイトであるハッシュ・ページ番号生成回路と、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ハッシュ・ページ番号、前記仮想アドレスの前記領域部分、および前記仮想アドレスの前記領域部分から参照される前記領域識別子を組み合わせることによってハッシュ・インデックスを形成し、ここで前記仮想アドレスの前記領域部分が、前記仮想アドレスをJビット右にシフトすること基づき空いていることが分かっている前記ハッシュ・ページ番号のビット位置に組み合わされて挿入され、前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記ハッシュ・インデックスを前記ハッシュ・ページ番号に等しく設定することによってハッシュ・インデックスを形成するハッシュ・インデックス生成回路と、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ハッシュ・インデックスをKビット左にシフトすることによってテーブル・オフセットを形成し、ここで各ロング・フォーマット・ページ・テーブル・エントリが $2^K$ バイト長であり、前記ページ・テーブルの前記フォーマットがショートに設定されている場合に、前記ハッシュ・インデックスをLビット左にシフトすることによってテーブル・オフセットを形成し、ここで各ショート・フォーマット・ページ・テーブル・エントリが $2^L$ バイト長であるテーブル・オフセット生成回路と、

前記ページ・テーブルの前記フォーマットがロングに設定されている場合に、前記ページ・テーブル・ベース・アドレスから前記領域部分を抽出することによってページ・テーブル領域を形成し、ページ・テーブルのフォーマットがショートに設定されている場合に、前記仮想アドレスから前記領域部分を抽出することによってページ・テーブル領域を形成するページ・テーブル領域生成回路と、

$2^M$ をM乗し1を引くことによってマスクを形成するマスク生成回路であって、 $2^M$ が前記テーブルのサイズであるマスク生成回路と、

前記ページ・テーブル・ベース・アドレスの下位Nビットを含まない前記ページ・テーブル・ベース・アドレス、および前記マスクの反転の下位Nビットを含まない前記マスクの反転に対して論理積演算を実行することによって第1アドレス部分を形成する第1アドレス部分生成回路と、

前記テーブル・オフセットの下位Nビットを含まない前記テーブル・オフセット、および前記マスクの下位Nビットを含まない前記マスクに対して論理積演算を実行することによって第2アドレス部分を形成する第2アドレス部分生成回路と、

前記第1アドレス部分および前記第2アドレス部分に対して論理積演算を実行して第1の

10

20

30

40

50

結果を形成し、前記第1の結果をNビット左にシフトして第2の結果を形成し、前記ページ・テーブル領域、前記第2の結果、および前記テーブル・オフセットの下位Nビットに対して論理和演算を実行することによって前記エントリ・アドレスを形成するエントリ生成回路であって、前記ページ・テーブル領域が前記エントリ・アドレスの領域部分に挿入されるエントリ生成回路と、を含むコンピュータ・システム。

【図面の簡単な説明】

【図1】プログラムの実行中に提示される仮想アドレスに応答する従来技術の手順を示す図。

【図2】変換索引バッファ(TLB)内のエントリにアクセスする従来技術の方法を示す図。

【図3】TLBミスの後に、TLBを更新するための物理ページ情報を取り出す従来技術の方法を示す図。

【図4】ページ・テーブル内にハッシュ・タグが格納される従来技術のページ・テーブル指定方式を示す図。

【図5】本発明によってサポートされる仮想アドレス指定方式を示す図。

【図6】本発明のハッシュ関数の適用によってアクセスすることのできる「ショート・フォーマット」仮想ハッシングページ・テーブルのエントリを示す図。

【図7】本発明のハッシュ関数の適用によってアクセスすることのできる「ロング・フォーマット」仮想ハッシングページ・テーブルのエントリを示す図。

【符号の説明】

501 仮想アドレス指定方式

502 仮想アドレス

503 仮想領域番号

504 ページ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

- (72)発明者 ステファン・ジー・バーガー

アメリカ合衆国9 5 0 5 0 カリフォルニア州サンタ・クララ、フォーブス・アベニュー 2 2 5 7

- (72)発明者 ガリー・エヌ・ハモンド

アメリカ合衆国8 0 5 2 5 コロラド州フォート・コリンズ、ソウグラス・コート 5 1 0 1

- (72)発明者 ジェームス・オー・ハイズ

アメリカ合衆国9 5 1 2 5 カリフォルニア州サン・ノゼ、キャンベル・アベニュー 1 7 2 2

- (72)発明者 ジェローム・シー・ハック

アメリカ合衆国9 4 3 0 3 カリフォルニア州パロ・アルト、タリスマン・ドライブ 8 5 1

- (72)発明者 ジョナサン・ケー・ロス

アメリカ合衆国9 4 0 8 7 カリフォルニア州サニーヴェイル、ローン・ウェイ 9 7 4

- (72)発明者 スニル・サクシーナ

アメリカ合衆国9 4 0 8 7 カリフォルニア州サニーヴェイル、カーロウ・コート 1 5 6

- (72)発明者 コウイチ・ヤマダ

アメリカ合衆国9 5 1 3 4 カリフォルニア州サン・ノゼ、エラン・ヴィレッジ・レーン 3 7 1、

ナンバー 1 1 6

審査官 清木 泰

- (56)参考文献 特開2 0 0 0 - 1 2 2 9 2 8 (JP, A)

特開2 0 0 0 - 1 2 2 9 2 7 (JP, A)

特開平1 0 - 2 2 8 4 1 9 (JP, A)

特開平1 0 - 1 3 3 9 5 0 (JP, A)

特開平1 0 - 0 9 1 5 2 5 (JP, A)

特開平0 7 - 0 4 9 8 1 2 (JP, A)

特開平0 4 - 3 2 3 7 4 8 (JP, A)

特開昭6 0 - 1 2 3 9 4 7 (JP, A)

特開昭5 6 - 1 0 5 3 8 2 (JP, A)

国際公開第9 8 / 0 4 4 4 1 9 (WO, A1)

米国特許第0 5 8 0 9 5 6 3 (US, A)

- (58)調査した分野(Int.Cl., DB名)

G06F12/10