(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3568183号

(P3568183)

(45) 発行日 平成16年9月22日(2004.9.22)

(24) 登録日 平成16年6月25日(2004.6.25)

(51) Int.C1.<sup>7</sup>

F 1

HO4J 11/00

HO4J 11/00

Z

HO4B 1/16

HO4B 1/16

J

HO4L 7/00

HO4L 7/00

F

HO4L 27/00

HO4L 27/00

Z

請求項の数 4 (全 13 頁)

(21) 出願番号

特願平10-14033

(22) 出願日

平成10年1月27日(1998.1.27)

(65) 公開番号

特開平11-215093

(43) 公開日

平成11年8月6日(1999.8.6)

審査請求日

平成14年3月28日(2002.3.28)

(73) 特許権者 000001122

株式会社日立国際電気

東京都中野区東中野三丁目14番20号

(72) 発明者 宮下 敦

東京都小平市御幸町32番地 日立電子株式会社 小金井工場内

(72) 発明者 秋山 俊之

東京都小平市御幸町32番地 日立電子株式会社 小金井工場内

(72) 発明者 塚本 信夫

東京都小平市御幸町32番地 日立電子株式会社 小金井工場内

審査官 高野 洋

最終頁に続く

(54) 【発明の名称】直交周波数分割多重変調方式の伝送帯域可変方法及びその装置

## (57) 【特許請求の範囲】

## 【請求項 1】

直交周波数分割多重方式の伝送装置の伝送帯域変更方法において、

送信側では、送信側クロック発振器の出力をクロックレート変換して作成したクロックを、レート変換部、符号化部、IFFT部、ガード付加部、同期シンボル挿入部、直交変調処理部に供給する際、伝送帯域に応じてクロックレートを変更することで上記作成したクロックの周波数を切り換え、

受信側では、受信側クロック発振器の出力をクロックレート変換して作成したクロックと受信信号から検出した同期信号とに基づいて上記受信信号をFFT変換後、復号化処理し、該復号化処理により得られた出力データの状態に応じてクロックレートを変更することで上記作成したクロックの周波数を切り換え、

受信側で復調する伝送帯域を、送信側の上記伝送帯域に自動追隨させることを特徴とする直交周波数分割多重方式の伝送帯域変更方法。

## 【請求項 2】

直交周波数分割多重方式の伝送装置において、

送信側クロック発振器の出力をクロックレート変換して作成したクロックを、レート変換部、符号化部、IFFT部、ガード付加部、同期シンボル挿入部、直交変調処理部に供給するクロックレート変換部を送信装置に備え、

受信側クロック発振器の出力をクロックレート変換するクロックレート変換部と、該クロックレート変換部の出力と受信信号から検出した同期信号とに基づいて上記受信信号をF

F T変換した後に復号化する信号処理部と、該信号処理部の出力データの状態に応じて上記クロックレート変換部を制御するデータ確認部を受信装置に備え、受信側で復調する伝送帯域を、送信側の伝送帯域に自動追隨させることを特徴とする直交周波数分割多重方式の伝送装置。

### 【請求項 3】

請求項 2 記載の直交周波数分割多重方式の伝送装置において、

上記送信装置に接続され、電波使用状態を調べることにより得られた空き伝送帯域に応じて伝送帯域幅を決める回線状態監視部を備え、上記空き伝送帯域に応じて決まった上記伝送帯域幅でデータ伝送を行うことを特徴とする直交周波数分割多重方式の伝送装置。

#### 【請求項4】

請求項 2 乃至 3 記載の直交周波数分割多重方式の伝送装置において、

ここで用いる変調方式をQAM方式としたことを特徴とする直交周波数分割多重方式の伝送装置。

## 【発明の詳細な説明】

【 0 0 0 1 】

## 【発明の属する技術分野】

本発明は、直交周波数分割多重変調方式のディジタル伝送装置に関する。

【 0 0 0 2 】

## 【従来の技術】

近年、ヨーロッパやアメリカ及び日本では、テレビジョン放送のディジタル化が検討されているが、その変調方式としては、OFDM(Orthogonal Frequency Division Multiplex)変調方式の採用が有力視されている。該OFDM変調方式は、マルチキャリア変調方式の一種で、多数のディジタル変調波を加え合わせたもので、このときの各キャリアの変調方式には、QPSK(Quadrature Phase Shift Keying)方式等が用いられる。

そして、このRFIDM信号を式で表現すると、以下のように表される。

まず、各キャリアのOPS K信号を  $\tau_1$  (も) とすると、これは式(1)で表せる。

$$_k(t) = a_k(t) \times \cos(2\pi k f t) + b_k(t) \times \sin(2\pi k f t) \quad (1)$$

ここで、 $k$  はキャリアの番号を示し、 $a_k(t)$ 、 $b_k(t)$  は、 $k$  番目のキャリアのデータで、「-1」または「1」の値をとる。 30

次に、キャリアの本数を  $N$  とすると、OFDM 信号は  $N$  本のキャリアの合成であり、これを  $\psi(t)$  とすると、これは次の式(2)で表すことができる。

$$k^-(t) = -k^+(t) \quad \dots \dots \dots \quad (3)$$

ここで、 $k = 1 \sim N$  の値をとる。

[ 0 0 0 3 ]

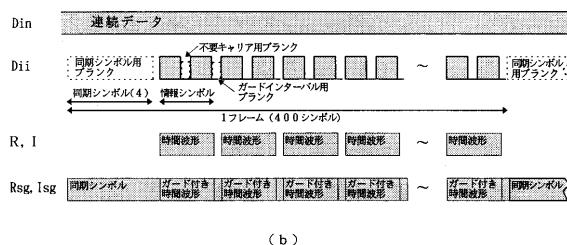

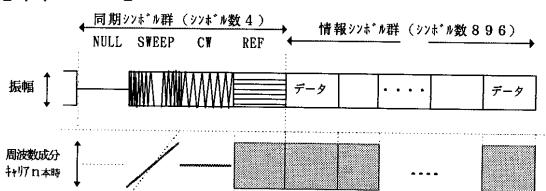

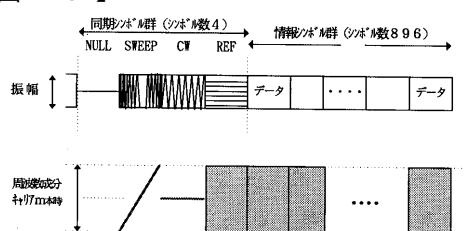

O F D M 信号は、上記信号単位から構成される。この信号単位シンボルは、例えば、有効サンプル 1 0 2 4 サンプルのデータに、ガードインターバルデータ 3 2 サンプルを付加した、1 0 5 6 サンプルのシンボル 3 9 6 組に、4 組の同期シンボルを付加した全 4 0 0 シンボルからなるフレームと呼ぶ、ストリーム単位の繰り返しで構成されている。

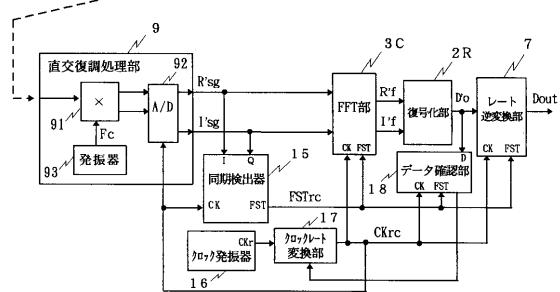

図 6 は、OFDM 变復調装置の基本構成を示すブロック図である。

以下、O F D M 変復調装置の構成と動作について、図 7 も用いて説明する。

連続的に入力されるデータ D\_in は、レート変換部 1 でレート変換され、例えば 400 シンボルからなるフレーム周期毎に、後述の同期シンボル期間に対応する 4 シンボル期間と、各情報シンボルにおける、273 から 752 サンプルまでの期間に対応する不要キャリア用ブランクを除いた期間に、データ D\_in として出力される。

なおレート変換部1は、他の各部に同期シンボル期間の開始を示すFST信号をフレーム周期である400シンボル毎に出力する。

符号化部 2 T は、入力データを符号化し、I と Q の 2 軸にマッピングした符号化データ R<sub>f</sub> と I<sub>f</sub> を出力する。

## 【0004】

I F F T ( I n v e r s e F a s t F o u r i e r T r a n s f o r m : 逆フーリエ変換 ) 部 3 A は、符号化データ R f と I f を周波数成分と見なし、1024 サンプルからなる時間軸信号 R と I に変換する。

ガード付加部 3 B は、1024 サンプルからなる信号 R と I の開始期間波形の例えは最初の 32 サンプルの波形を 1024 サンプル後に付加し、合計 1056 サンプルの時間波形信号 R g と I g を出力する。

同期シンボル挿入部 5 は、当該情報シンボル m 個ごとに、予めメモリ等に記憶された、例えは 4 シンボルからなる同期シンボルの挿入された信号 R s g と I s g を作成、出力する。

この信号は、直交変調処理部 8 にて直交変調され、図 7 の ( b ) に示すようなフレーム構成の O F D M 变調波信号となり、送信側から受信側に送信される。

なお、クロック発振器 11 からのクロック C K は各部に供給される。

送信された O F D M 变調波は、受信側の直交復調処理部 9 にて、ベースバンドの O F D M 信号に直交復調され、時間軸信号 R ' s g と I ' s g となり出力される。

当該信号 R ' s g と I ' s g は、同期検出器 4 に入力され、ここで同期シンボル群が検出され、フレーム周期を表す F S T ' r パルスが各部に出力される。

また、時間軸信号 R ' s g と I ' s g は F F T 部 3 C に入力され、時間波形信号から周波数成分信号 R ' f と I ' f に変換される。

この信号 R ' f と I ' f は、復号化部 2 R で復号され、信号 D ' o が出力される。

そして、レート逆変換部 7 で連続したデータ信号 D o u t に変換後、出力される。

## 【0005】

次に、各部の詳細な構成、動作について述べる。

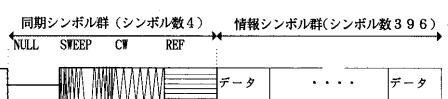

まず、レート変換部 1 の一例を図 8 に示し、説明する。

レート変換部 1 に入力されたクロック C K は P L L / V C O 1 - 2 に入力され、P L L / V C O 1 - 2 は、N / G 倍の周波数のクロック C K m を出力する。

また、クロック C K は、F S T カウンタ 1 - 4 にも入力され、ここで送信側における処理のフレーム基準となる F S T パルスを発生、出力する。

なお、この F S T パルスは、F I F O メモリ 1 - 3 の W R S T 端子と R R S T 端子に入力され、書き込みと読み出しのリセットの基準になる。

そして、入力された連続データ D i n は、シリアル / パラレル ( S / P ) 変換器 1 - 1 にてパラレル信号となり、F I F O メモリ 1 - 3 に入力され、ここで前述のごときブランク期間を有するデータ信号 D i i ( 図 7 ( a ) ) が出力される。

## 【0006】

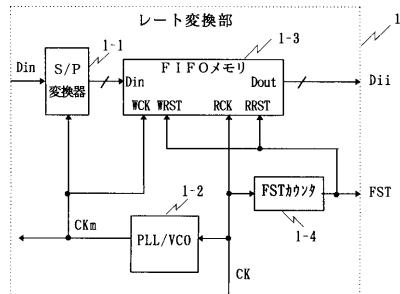

次に、符号化部 2 T の一例を図 9 に示し、説明する。

上記レート変換部 1 出力の信号 D i i は、マッピング R O M 2 - 1 , 2 - 2 に入力され、I , Q 軸の所定点の信号に変換される。図 7 の ( a ) に示す、不要キャリアに相当する期間の信号は、選択器 2 - 3 , 2 - 4 にて " 0 " に置換され、前述の信号 R f と I f が作成される。この選択器 2 - 3 , 2 - 4 は、上記クロック C K と F S T パルスに基づきタイミングの定められたコントローラ 2 - 5 により制御される。

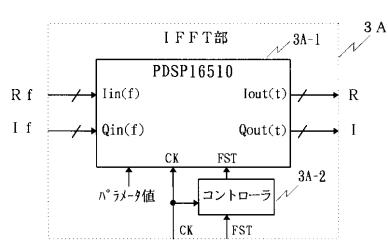

次に、I F F T 変換部 3 A の一例を図 10 に示し、説明する。

上記クロック C K と F S T パルスとでタイミングを決められたコントローラ 3 A - 2 により、ガード期間を含めたシンボル周期の信号を基準とし、上記入力信号 R f と I f を、上記時間波形信号 R と I に変換する。これは、具体的には例えば、プレッシー社の P D S P 1 6 5 1 0 等を用いれば実現できる。

## 【0007】

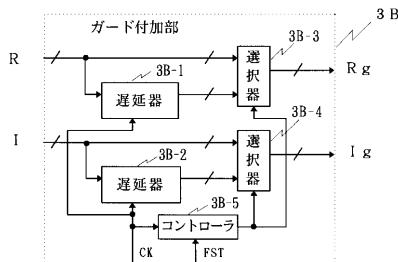

次に、ガード付加部 3 B の一例を図 11 に示し、説明する。

ここに入力された上記信号 R と I は、1024 サンプルだけ信号を遅延する遅延器 3 B - 1 , 3 B - 2 と選択器 3 B - 3 , 3 B - 4 にそれぞれ入力され、各選択器 3 B - 3 , 3 B - 4 において、1 から 1024 サンプル目までは遅延されない信号 R と I が、1025 サ

10

20

30

40

50

ンブルから 1056 サンブル目までは遅延器 3B-1, 3B-2 で 1024 サンブル遅延された信号が選択され、出力される。

その結果、出力される 1 シンボルが 1056 サンブルからなる信号 Rg, Ig は、1025 サンブル目から 1056 サンブル目に 1 サンブルから 32 サンブル間の時間波形が付加される。この選択器 3B-3, 3B-4 は、上記クロック CK と FST パルスとでタイミングを決められたコントローラ 3B-5 によって制御される。

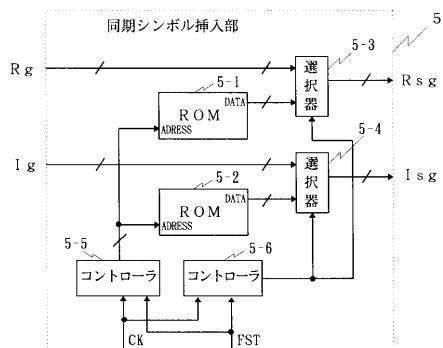

次に、同期シンボル挿入部 5 の一例を図 12 に示し、説明する。

上記クロック CK と FST パルスによってタイミングを決められたコントローラ 5-5 によって制御される ROM5-1, 5-2 は、前述の同期シンボル信号を FST パルスに応じたタイミングで発生する。

同様に、クロック CK と FST パルスとでタイミングを決められたコントローラ 5-6 により制御される選択器 5-3, 5-4 は、上記ガード付加部 3B で作成されたガード付時間信号 Rg と Ig の現段階では無信号期間である、4 シンボル期間のみ、ROM5-1, 5-2 からの同期シンボル信号を選択して出力する。その結果、同期シンボル信号の挿入された、図 7 の (a) に示す時間波形信号 Rsg と Isg が出力される。

#### 【0008】

ここで、図 7 の (b) に記載の NULL シンボルは、同期シンボル群の存在を大まかに見つけるためのもので、このシンボル期間は信号を一切出力しない。また、SWEET シンボルは、各シンボルの切り替わり点を正確に求めるためのものであり、1 シンボル期間に伝送帯域の下限周波数から上限周波数に変化する波形からなる。

そして、直交変調処理部 8 の D/A 変換器 8-1 において、上記時間波形信号の実数部信号 Rsg と虚数部信号 Isg の D/A 変換を行ない、直交変調器 8-2 で実数部信号に対してはローカル発振器 8-3 からの周波数 fc のキャリア信号で、一方、虚数部信号に対してはローカル発振器 8-3 の周波数 fc のキャリア信号を 90° 移相した信号で直交変調し、これらの信号を合成し OFDM 信号を得る。

#### 【0009】

次に、受信側の構成、動作について説明する。

まず、前述伝送されたフレーム構成の信号が直交復調処理部 9 に入力される。ここでの処理は、送信側とは逆に、直交復調器 9-1 にて、電圧制御発振器 9-3 のキャリア信号で復調したものを実数部信号、90° 移相したキャリア信号で復調した出力を虚数部信号として取り出すものである。これら実数部、虚数部の各復調アナログ信号は、A/D 変換器 9-4 にてデジタル信号に変換される。

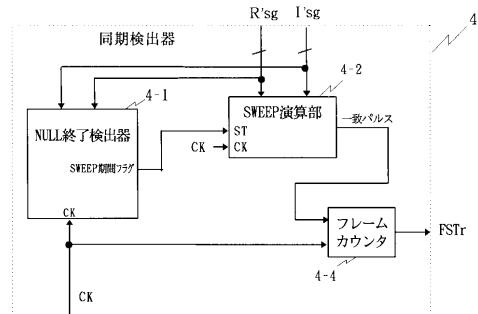

次に、同期検出器 4 の一例を図 13 に示し、説明する。

上記直交復調されたデジタル信号 R'sg と I'sg は、NULL 終了検出器 4-1 と SWEET 演算部 4-2 とに入力される。

NULL 終了検出器 4-1 は、フレーム構成のシンボル群の中から、無信号の期間である NULL シンボルを検出し、同期シンボルの大まかな位置を検出し、NULL 終了時点から図示しないタイマ回路にて SWEET シンボル開始時期を推定して SWEET 期間フラグパルスを出力する。

SWEET 演算部 4-2 は、SWEET 期間フラグパルスを参照し、NULL シンボルの後に存在する SWEET シンボルによって、各シンボルの正確な切り替わりタイミングを検索する。具体的には、予め SWEET シンボルのパターンを内蔵メモリに記憶しておき、入力された OFDM 信号と該メモリに記憶された信号を相關演算し、メモリの信号パターンと OFDM 信号のパターンが一致した時点で、一致パルスをフレームカウンタ 4-4 のリセット端子に入力する。

#### 【0010】

フレームカウンタ 4-4 は、カウント数がフレーム周期を構成する値、例えば 422400 (= 1056 × 400) に到達すると、その値を 0 に戻すとともに、フレーム開始時期を示す FSTr パルスを出力し、再びカウントを開始する。

以後は、一定カウント、即ちフレーム開始点毎に FSTr パルスが出力され、フレーム開

始時期を示す。受信側では、このF S T r パルスをF F T部3 C、復号化部2 R、レート逆変換部7における開始タイミングとする。

F F T変換部5は、F S T r パルスを基にシンボルを区切り、フーリエ変換を行うことでO F D M復調を行い、上記周波数成分信号R' fとI' fを出力する。

復号化部2 Rは、例えばR O Mテーブル手法にて、これら信号R' fとI' fを識別し、復号化信号D' oを算出する。

レート逆変換部7は、上記クロックC K rとF S T r パルスによって動作タイミングが決定され、レート変換部1の構成を反転(逆に)した構成である。

ところで、伝送されるO F D M信号の帯域幅は、ベースバンド信号R s g, I s gの帯域の2倍となる。ベースバンド信号R s g, I s gの帯域は、I F F T部3 Aに入力するキャリアに相当するデータに依存して決定される。10

#### 【0011】

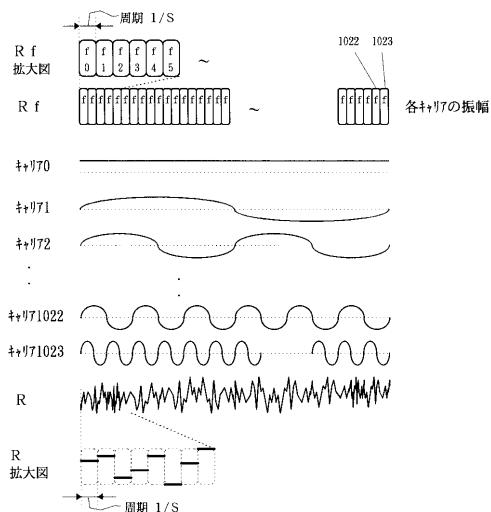

ここで、I F F T部3 Aの動作について、図14を使い説明する。

周波数成分である信号R fは、周期1/Sのクロックに同期し順次入力される。

1番目のデータf 0は、直流成分であるキャリア0の振幅レベルを決定する。2番目のデータf 1は、周期1024/Sのキャリア1の振幅レベルを決定し、3番目のデータf 2は、周期512/Sのキャリア2の振幅レベルを決定する。

このようにして入力された最高周波数成分がI F F T変換によって作成される時間波形の最高周波数、すなわち帯域幅を決定する。

なお、このようにして個別の振幅を決定されて変換作成された各キャリアは、これらが総加算されて、時間波形信号Rが作成される。20

ただし、この時間波形信号Rは、計1024サンプルのデータから構成されており、各サンプルデータは周期1/Sのクロックに同期して出力される。即ち、キャリア1は、入力クロック周期の1024倍の周波数となる。

#### 【0012】

##### 【発明が解決しようとする課題】

以上説明した従来構成の伝送装置において、伝送帯域幅の変更を行なう場合、以下の部分の変更が必要となる。

1) 伝送容量の変更に伴い、送信側のレート変換部1のP L L / V C O 1 - 4のN/G特性。30

2) 送信側の符号化部2 Tにおいて、不要キャリア振幅を0にするため置換する0の期間の変更をするコントローラ2-5の制御特性。

3) 帯域変更に伴い、送信側の同期挿入部5において、S W E E Pシンボルに対応する周波数パターンを記憶しているR O M 5-1, 5-2のデータ。

4) 受信側の同期検出器4のS W E E P演算部4-2の内蔵メモリに記憶されたS W E E Pシンボルパターン。

5) 受信側のレート逆変換部7のP L L / V C O 特性。

このように従来の伝送装置では、伝送帯域幅を変更しようとしても、送信側と受信側の双方で変更しなければならない部分が多く、また、送信側で行った帯域可変処理に受信側が追随しないため、伝送帯域幅を容易に、かつ瞬時に変更することができない。40

本発明はこれらの欠点を除去し、帯域幅の可変を容易に行える伝送システムの実現を目的とする。

#### 【0013】

##### 【課題を解決するための手段】

本発明は、上記目的を達成するため、送信側において各部に供給するクロックレートを変更し、受信側では、受信信号から検出した同期信号と受信側クロックを分周して作成したフレーム信号とを位相比較し、その結果により受信クロック発振部のクロック周波数を制御し、受信側で復調する帯域を送信側の帯域に自動追隨させて伝送帯域を可変するようにしたものである。

即ち、送信側のI F F T変換において、n番目のデータf nは、n番目のキャリアの周期50

1024 / (n · S) の振幅レベルを決定する。ここで、IFFT変換部に供給されるクロックの周期を変更すれば、n番目のキャリアの周波数も変更される。伝送帯域幅は、発生するキャリアの最高周波数で決定される。

すなわち、帯域の可変が、クロックの周期を変更することにより実現できる。また、クロックの周期の変更でシンボル周期も変更され、このシンボル数で決定されるフレーム周期も変更される。

受信側では、受信信号から検出したNULLシンボルとSWEPEシンボルの周期、すなわち、送信側のフレーム周期と、フレームカウンタで定められているFSTR周期とを比較し、差分を解消するように、受信側クロックの周期を制御する。

これにより、送信側で行った帯域可変処置に自動追隨する伝送システムを構築できる。

10

#### 【0014】

##### 【発明の実施の形態】

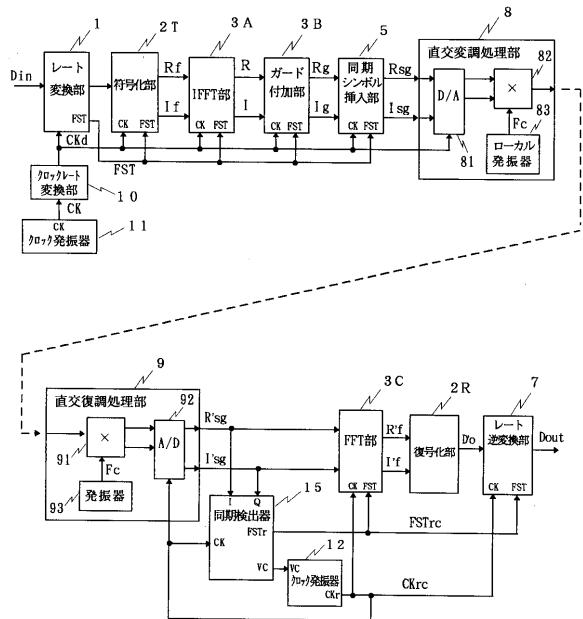

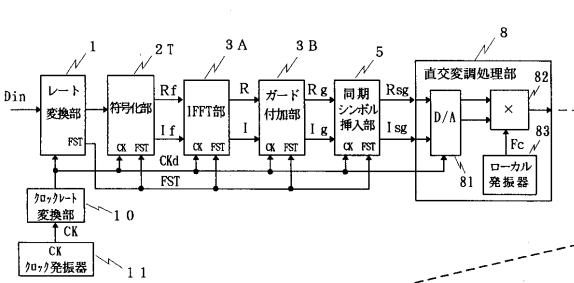

本発明の帯域可変伝送システムの一実施例の全体ブロック構成を図1に示し、説明する。送信側において、クロック発振器11のクロック出力端子は、クロックレート変換部10に接続される。クロックレート変換部10のクロック出力端子は、レート変換部1、符号化部2T、IFFT部3A、ガード付加部3B、同期シンボル挿入部5、直交変調処理部8の各クロック端子に接続される。

受信側において、同期検出器15の出力VCは、電圧制御クロック発振器12の端子VCに接続される。同期検出器15の出力FSTRは、FFT部3C、レート逆変換部7のFST端子に接続される。電圧制御クロック発振器12の出力CKrは、FFT部3C、レート逆変換部7、直交復調処理部9、同期検出器15のクロックCK端子に接続される。

20

#### 【0015】

まず、送信側における帯域可変処理動作について説明する。

伝送帯域幅の変更を行う場合、クロックレート変換部10において、クロック発振器11からのクロックCKを、変更する帯域幅に応じたレートのクロックに変換する。すなわち、クロックレート変換部10は、クロックCKのレートの(V/NR)倍したレートのクロックCKdを出力する。

ここで、レート変換部1から出力される前述のフレーム周期パルスFSTは、例えば、上記クロックCKdの $1056 \times 400$ カウント毎に出力されるため、クロックCKdとフレーム周期パルスFSTとを基準に動作する符号化部2T、IFFT部3A、ガード付加部3B、同期シンボル挿入部5、直交変調処理部8では、それぞれサンプルレートが(V/NR)倍となった出力データを、それぞれ(NR/V)倍の期間をかけて出力することになる。

30

また、レート変換部1内のPLL/VCO1-4(図8)は、入力するクロックレートが(V/NR)倍になるため、N/Gの比率のクロックCKmも(V/NR)倍となり、取り込まれるデータDinのレートも(V/NR)倍になる。

ここで、例えば、(V/NR)を1/2とした場合について説明する。

この場合、IFFT部3Aにおいて、サンプルクロックCKdが1/2になると各キャリア間隔は1/2に、またシンボル周期は2倍になる。

40

このとき、キャリアの本数を変更していないため、(V/NR)が1/2の本例の場合、帯域幅は、キャリア間隔×キャリア本数で決定され、半分となる。

即ち、クロックレートを(V/NR)倍にすることにより、帯域幅を(V/NR)倍に変更することができる。

#### 【0016】

次に、受信側における帯域可変処理動作について説明する。

同期検出器15は、前述のようにして、入力された信号R'sgとI'sgから検出したNULL期間を基準としてSWEPEシンボルを探し、受信フレーム周期を示す一致パルスと位相比較してクロックCKrcの周波数を制御する。また、このクロックCKrcを、例えば $1056 \times 400$ カウントして作成したフレーム周期パルスFSTRcを出力す

50

る。

ここで、FFT部3C、レート逆変換部7は、このパルスFSTrcとクロックCKrcにより動作するため、送信側でのサンプルレートがV/NR倍されている場合、FSTrcパルスとの位相比較基準である一致パルスは、NR/V倍の周期であるから、このクロックCKrcが、通常時のV/NR倍の周波数にまで変更された場合に、FSTrcパルスと一致パルスの周期及び位相が合致する。

#### 【0017】

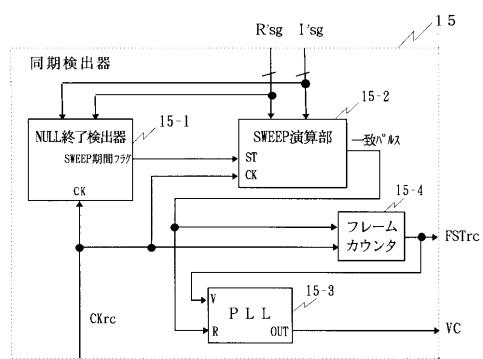

図2に、この同期検出器15の具体的構成を示し、説明する。

入力される信号R'sgとI'sgは、NULL終了検出器15-1とSWEET演算部15-2に入力される。NULL終了検出器15-1出力であるSWEET期間フラグパルスは、SWEET演算部15-2のST端子に入力される。

10

NULL終了検出器15-1、SWEET演算部15-2、フレームカウンタ15-4のCK端子には、クロックCKrcが入力される。

SWEET演算部4-2の出力である一致パルスは、PLL15-3のR端子に入力される。

また、クロックCKrcを $1056 \times 400$ 数えるフレームカウンタ15-4の出力FSTrcは、後段の回路およびPLL15-3のV端子に入力される。

PLL15-3は、V端子とR端子にそれぞれ入力されるパルスの位相に応じて電圧が変化する信号VCを出力する。

そして、電圧制御型のクロック発振器12は、同期検出器15から印加される上記信号VCの電圧の高低に応じて、即ち、送信側のクロックCKdのクロックレート変換に応じて、出力するクロックCKrcの周波数を上下させる。

20

以上説明した処理によって、受信側において用いるクロックCKrcとフレーム周期パルスFSTrcを、送信側において変更したクロックCKdとフレーム周期パルスFSTに追随させることができる。

#### 【0018】

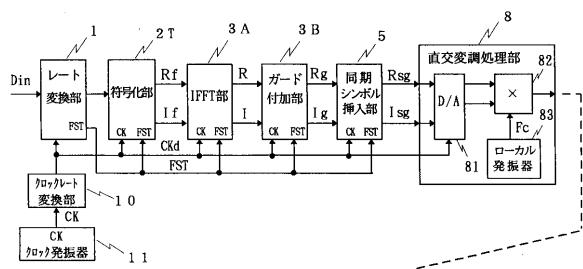

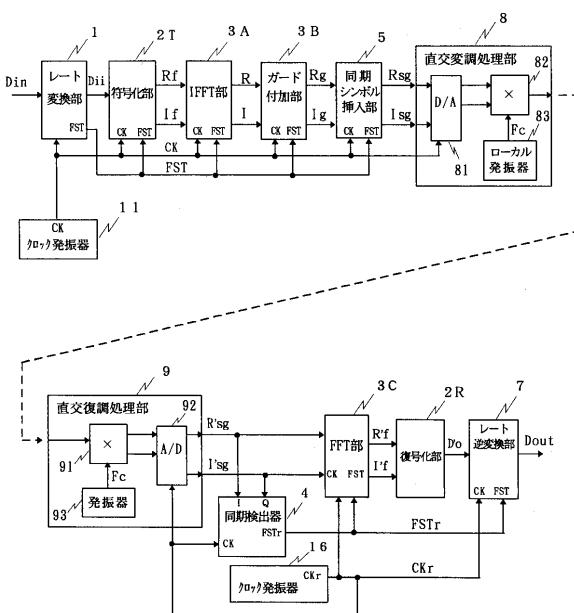

次に、本発明の帯域可変伝送システムの第2の実施例のブロック構成を図3に示し、上記図1と異なる部分を中心にして説明する。

受信側のクロック発振器16の出力クロックCKrcは、クロックレート変換部17に入力される。クロックレート変換部17の出力クロックCKrcは、FFT部3C、レート逆変換部7、データ確認部18のCK端子に接続される。

30

データ確認部18のFST端子には、同期検出器15のFSTrcパルスが入力され、D端子には復号化部2Rの出力D'oが入力される。

前述の如く、送信側で伝送帯域幅を、V/NR(例えば、1/2)にした場合、キャリア本数を変更しないため、キャリア間隔はV/NRになる。

ここで、受信側において、元々のクロックレートでFFT変換動作を行うと、即ち、キャリア間隔が1倍のままFFT変換を行うと、その結果として復号化部2Rから得られる出力D'oは、1本おきに"0"となる歯抜け状態となる。また、逆に送信側のクロックレートが1倍で、受信側がV/NR倍のクロックレートで動作すると、復号化部2Rから得られる出力D'oは、周波数の高い方のキャリアのデータが無い状態となってしまう。

40

そこで、データ確認部18にて、この出力D'oの状態を調べ、送信側におけるクロックレートの変更状態を確認する。

#### 【0019】

そして、データ確認部18では、受信側におけるクロックレートが、送信側のクロックレート変更に対応するクロックレートになる様、クロックレート変換部17に対し、クロックレートの変更を指示する制御信号を出力する。

これにより、クロックレート変換部17は、受信側におけるクロックCKrcをデータ確認部18からの制御信号に基づき、送信側のクロックレート変更に対応したクロックレートに変更する。

ここで、送信側のクロックレート変換を、単純な1/2倍や1/3倍等とすることにより

50

、受信側のデータ確認部18の確認動作において、誤検出することが少なくなる。以上説明した構成によって、受信側において用いるクロックCKrcとフレーム周期パルスFSTrcを、送信側において変更したクロックCKdとフレーム周期パルスFSTに追随させることができる。

#### 【0020】

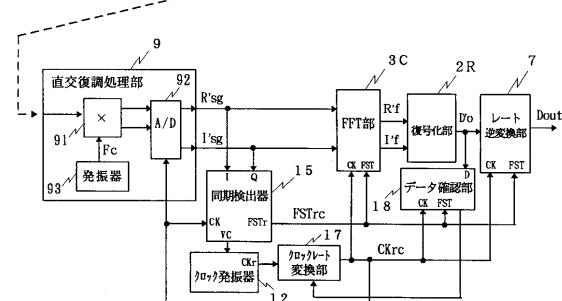

次に、本発明の帯域可変伝送システムの第3の実施例のブロック構成を図4に示す。これは、図1の構成に、レート変換部17とデータ確認部18を追加した構成であり、動作説明を省略する。

ここで、クロックレート変換部10, 17は、論理素子による分周動作のみにより、クロックレートを、1/2, 1/3, 1/4等に変える機能のみとする。これは、受信側の電圧制御型のクロック発振器12の周波数変化幅が狭い範囲でしか可変できない場合に、主に用いられる構成である。

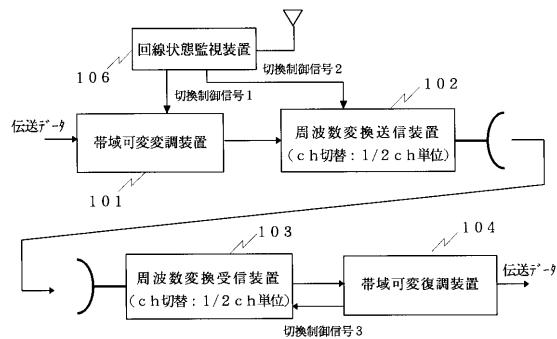

次に、本発明を適用した帯域自動可変伝送システムの構成を図5に示す。

回線状態監視装置106は、使用する回線の電波使用状態を調べ、空き具合に応じて使用する周波数と使える帯域幅を決定するもので、切換制御信号S1を帯域可変変調装置101の制御端子に出力する。また、切換制御信号S2を周波数変換送信装置102の制御端子に出力する。

帯域可変変調装置101、周波数変換送信装置102は、図1、図3、図4の送信側の構成を大きくブロック化して示したもので、帯域可変変調装置101はレート変換部1～同期シンボル挿入部5等に対応し、周波数変換送信装置102は、直交変調処理部8に対応する。いずれも、外部から切換コントロール可能な機能が付加されたものである。

また、帯域可変復調装置104は、キャリアの有無等の復調状態から切換制御信号S3を、周波数変換受信装置103に送る。

周波数変換受信装置103、帯域可変復調装置104は、図1、図3、図4の受信側の構成を大きくブロック化して示したもので、周波数変換受信装置103は直交復調処理部9に対応し、帯域可変復調装置104はFFT部3C～レート逆変換部7等に対応するものである。

#### 【0021】

以下、この動作について述べる。

まず、伝送開始に先立ち、送信側では、回線状態監視装置106により、使用回線の電波使用状態を調べ、回線の空き具合に応じて、使用する周波数と使える帯域幅を決定する。そして、切換制御信号S1により使用する帯域幅を、切換制御信号S2により使用する周波数を、それぞれ帯域可変変調装置101、周波数変換送信装置102に指定する。

これにより、帯域可変変調装置101では、使用する帯域幅になるよう、前述のようなクロックレート変更が行われ、使用する帯域幅になる。また、周波数変換送信装置102では、使用する周波数となるように、ローカル発振周波数が制御され、使用する周波数となる。そして、使用する周波数、帯域幅となった送信信号が、受信側に送出される。

一方、受信側では、帯域可変復調装置104において、全てのキャリアが存在しない状態、キャリアの一部のみが存在する状態、予定したキャリアがおおよそ存在する状態のいずれであるかを判別し、対応する切換制御信号S3を周波数変換受信装置103に出力する。

周波数変換受信装置103では、この切換制御信号S3によって、受信周波数が切換えられ、送信側からの送信信号を受信できるようになる。

これら構成をとることで、空きチャネルを自動探索してその空き帯域に応じた伝送帯域幅でデータ伝送を行うシステムを構築できる。

#### 【0022】

ここで、図15に、クロックレートを1倍とした場合のフレーム周期時間と、その際の周波数成分の関係を示す。また、図16に、クロックレートを高めた場合のフレーム周期時間と、その際の周波数成分の関係を示す。

前述のように、クロックレートを1/2に下げればフレーム周期は2倍になるが、周波数

10

20

30

40

50

帯域は 1 / 2 になる。

従って、図 15 の場合の 1 チャネル ( c h ) 分の帯域を、図 16 の場合は、別個に利用することができる。

つまり、図 5 に示す伝送システムにおいて、送信および受信周波数を、1 / 2 c h 単位に変更できる周波数変換送信装置 102 と、周波数変換受信装置 103 を組み合わせる。これにより、1 c h 分の帯域を複数伝送に利用することができるようになり、限られた伝送帯域を有効に利用することができる。

### 【0023】

#### 【発明の効果】

以上説明したように、本発明によれば、送信側にてクロックレートを変更することで帯域可変は可能となり、かつ、受信側はその変更に自動的に追尾する伝送システムを実現できる。

10

#### 【図面の簡単な説明】

【図 1】本発明のデータ伝送システムの全体構成を示すブロック図

【図 2】本発明で用いる同期検出器 15 の構成を示すブロック図

【図 3】本発明の他のデータ伝送システムの全体構成を示すブロック図

【図 4】本発明の他のデータ伝送システムの全体構成を示すブロック図

【図 5】本発明を適用した帯域自動可変伝送システムの全体構成を示すブロック図

【図 6】従来のデータ伝送システムの全体構成を示すブロック図

【図 7】本発明の各部の波形タイムチャートおよびフレーム構成波形図

20

【図 8】レート変換部 1 の構成を示すブロック図

【図 9】符号化部 2 T の構成を示すブロック図

【図 10】I F F T 部 3 A の構成を示すブロック図

【図 11】ガード付加部 3 B の構成を示すブロック図

【図 12】同期シンボル挿入部 5 の構成を示すブロック図

【図 13】同期検出器 4 の構成を示すブロック図

【図 14】I F F T 部 3 A の動作を説明する図

【図 15】クロックレート 1 倍の場合のフレーム周期時間と周波数成分の関係を示す図

【図 16】クロックレートのアップ時のフレーム周期時間と周波数成分の関係を示す図

#### 【符号の説明】

30

1 : レート変換部、2 T : 符号化部、3 A : I F F T 部、3 B : ガード付加部、5 : 同期シンボル挿入部、3 C : F F T 部、2 R : 復号化部、7 : レート逆変換部、8 : 直交変調処理部、9 : 直交復調処理部、10, 17 : クロックレート変換部、11, 12, 16 : クロック発振器、15 : 同期検出器、18 : データ確認部、15 - 1 : N U L L 終了検出器、15 - 2 : S W E E P 演算部、15 - 4 : フレームカウンタ、15 - 3 : P L L。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

(a)

(b)

【図8】

【図9】

【図10】

【図11】

【図13】

【図12】

【図14】

【図16】

【図15】

---

フロントページの続き

(56)参考文献 特開平08-228163(JP,A)

特開平09-214463(JP,A)

特開平09-233047(JP,A)

特開平10-022973(JP,A)

特開平11-032026(JP,A)

特開平10-173625(JP,A)

米国特許第05680388(US,A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H04J 11/00

H04B 1/16

H04L 7/00

H04L 27/00