(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 601 07 174 T2 2005.11.10

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 187 141 B1

(51) Int Cl.<sup>7</sup>: G11C 11/22

(21) Deutsches Aktenzeichen: 601 07 174.3

(96) Europäisches Aktenzeichen: 01 120 724.8

(96) Europäischer Anmeldetag: 05.09.2001

(97) Erstveröffentlichung durch das EPA: 13.03.2002

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 17.11.2004

(47) Veröffentlichungstag im Patentblatt: 10.11.2005

(30) Unionspriorität:

2000269223 05.09.2000 JP

(84) Benannte Vertragsstaaten:

DE, FR, GB

(73) Patentinhaber:

Kabushiki Kaisha Toshiba, Tokio/Tokyo, JP

(72) Erfinder:

Takashima, Daisaburo, Yokohama-shi,

Kanagawa-ken, JP

(74) Vertreter:

HOFFMANN & EITLE, 81925 München

(54) Bezeichnung: Halbleiterspeicheranordnung

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****HINTERGRUND DER ERFINDUNG**

**[0001]** Diese Erfindung betrifft eine Halbleiterspeichervorrichtung und insbesondere eine nicht-flüchtige ferroelektrische Speichervorrichtung.

**[0002]** Speichervorrichtungen werden gegenwärtig in allen elektronischen Produkten verwendet, einschließlich in Hauptspeichervorrichtungen von Großcomputern, Personal Computern, elektrischen Haushaltsgeräten, zellulären Telefonen und anderem.

**[0003]** Verschiedene Arten von Halbleiterspeichern wie beispielsweise flüchtige DRAM (dynamische RAM), SRAM (statische RAM) nichtflüchtige MROM (MaskenROM), Flash EEPROM (elektrisch lösbarer programmierbarer Speicher), und so weiter, sind kommerziell verfügbar. Von diesen ist der DRAM flüchtig, belegt jedoch momentan fast den gesamten Markt aufgrund der Vorteile hinsichtlich dahin, dass der Speicherbereich im Vergleich mit SRAM 1/4 ist und die Geschwindigkeit äquivalent zum Flash EEPROM ist.

**[0004]** Auf der anderen Seite, da der elektrisch löschbare programmierbare Flash EEPROM nicht-flüchtig ist, erlaubt dieser ein Abschalten der Energieversorgung. Jedoch hat er auch Nachteile wie beispielsweise dass die Überschreibfrequenz (W/E Frequenz) bei nur 106 ist, und es daher im Bereich von Mikrosekunden dauert, um zu schreiben, und eine hohe Spannung (12V bis 22V) ist zum Schreiben erforderlich, und der Marktanteil ist noch nicht so groß wie der von DRAM.

**[0005]** Demgegenüber wurden nicht-flüchtige Speicher vor der Verwendung eines ferroelektrischen Kondensators (ferroelektrischer Speicher) von verschiedenen Herstellern entwickelt, seitdem diese 1980 vorgeschlagen wurden, da sie Vorteile haben, nämlich Nicht-Flüchtigkeit, Überschreibfrequenz bei 1012, eine Lese- und Schreibdauer äquivalent zu der vom DRAM, Betriebsfähigkeit unter 3V bis 5V, und so weiter, und er könnte möglicherweise den gesamten Speichermarkt ersetzen.

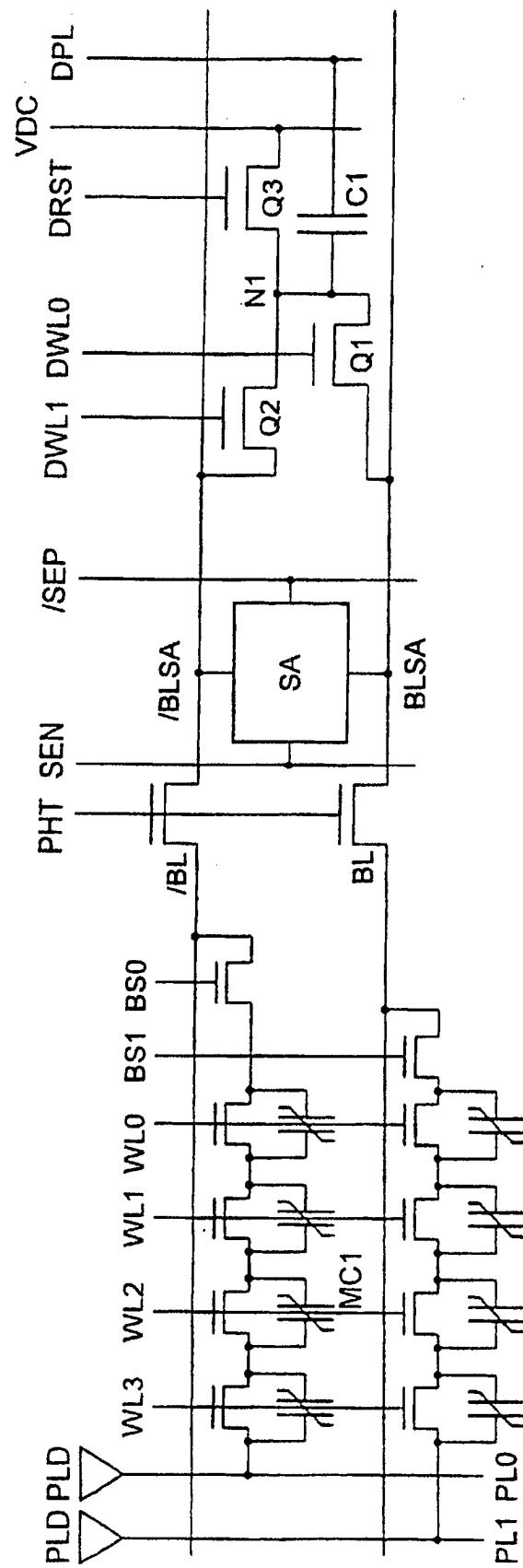

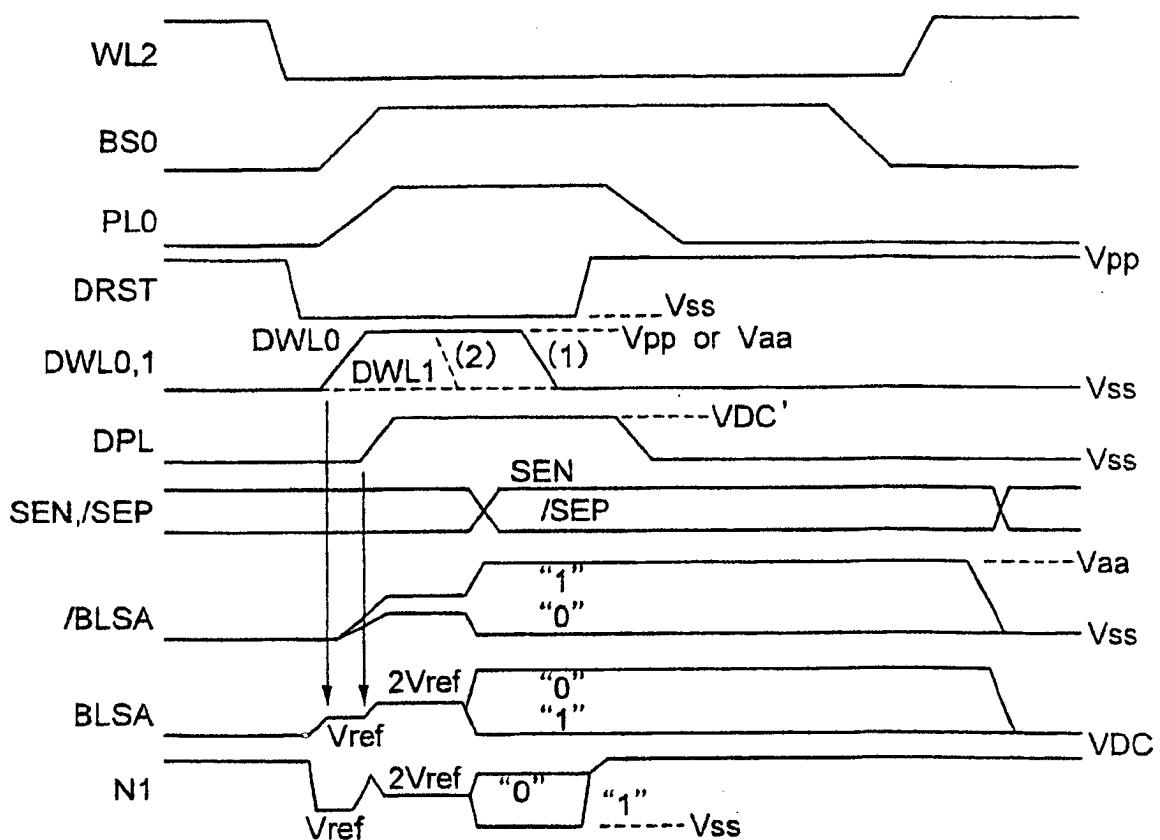

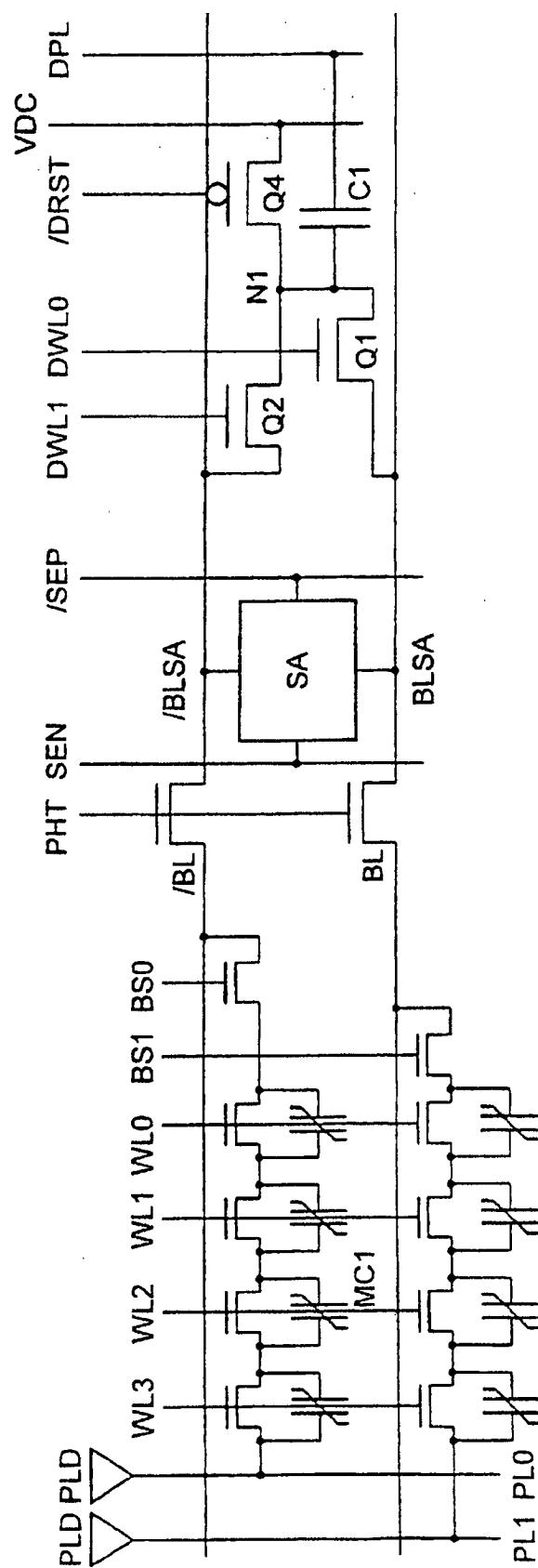

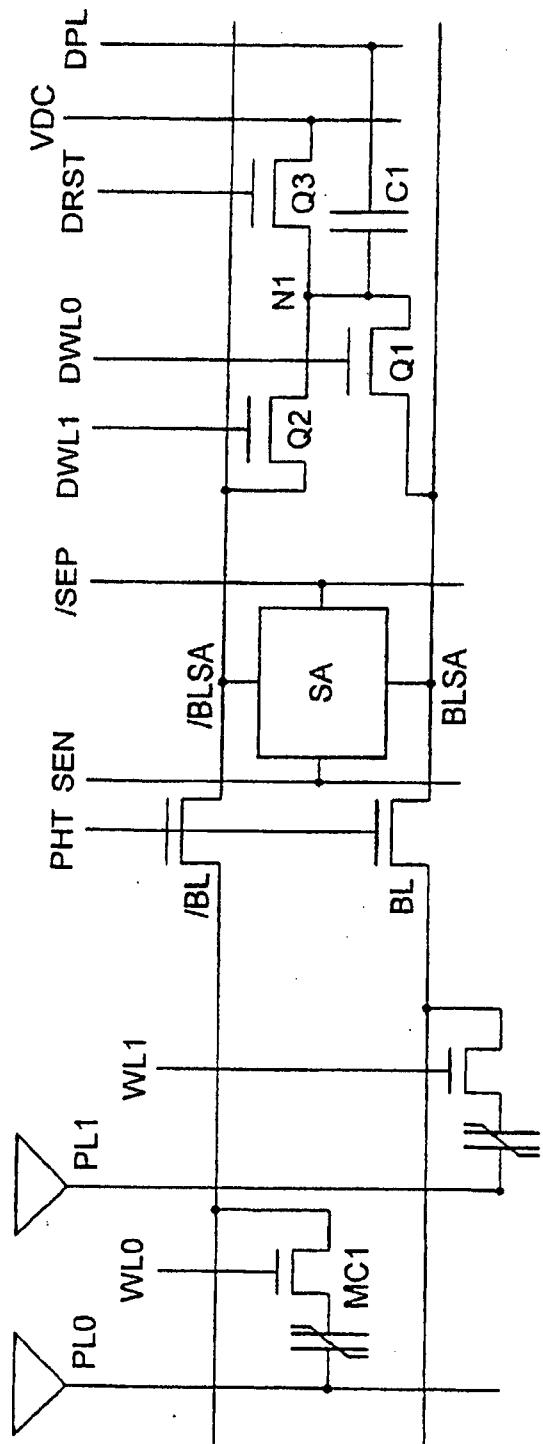

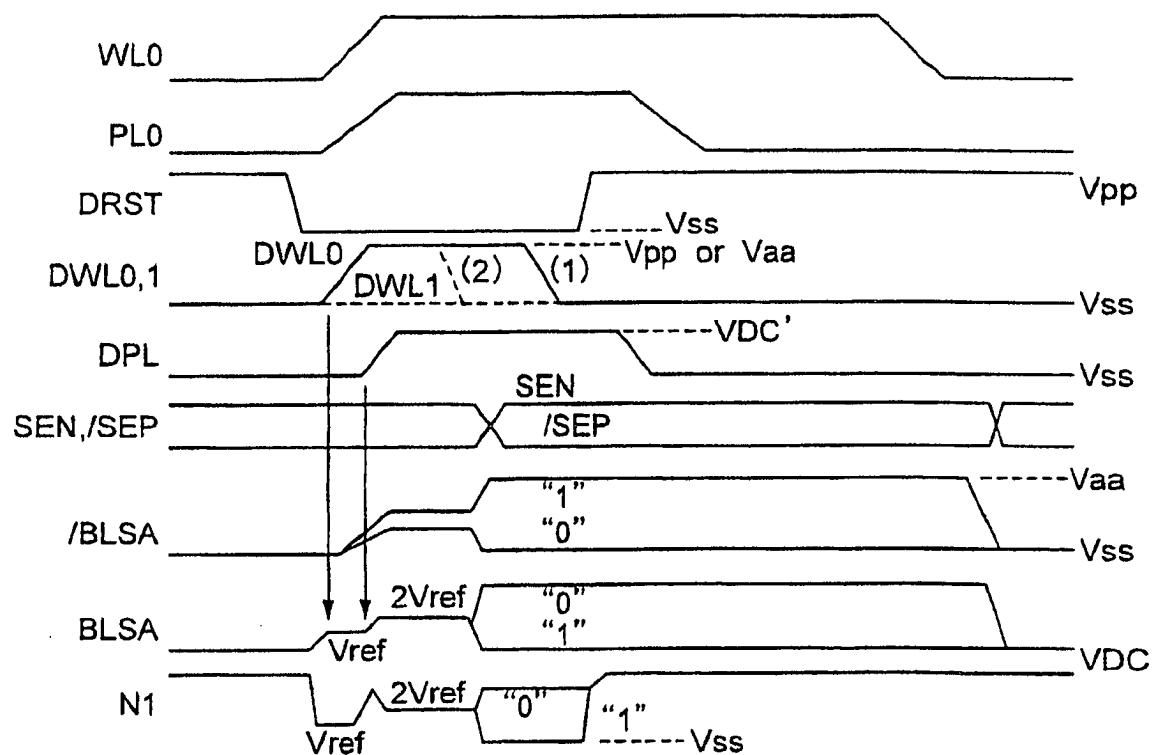

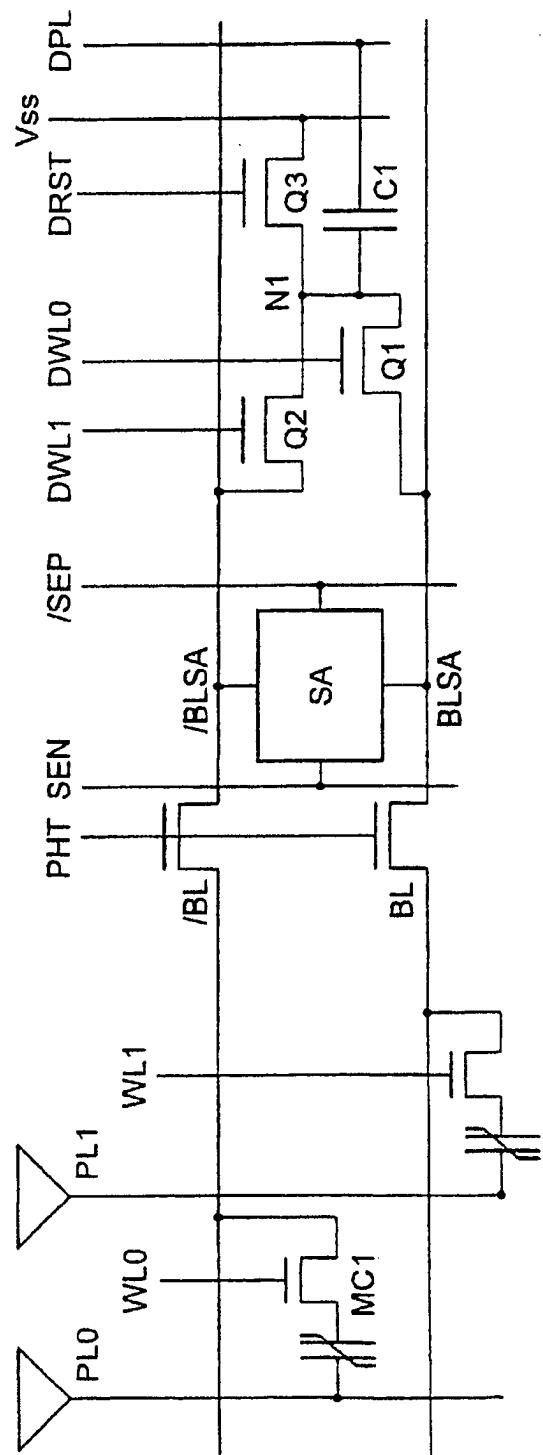

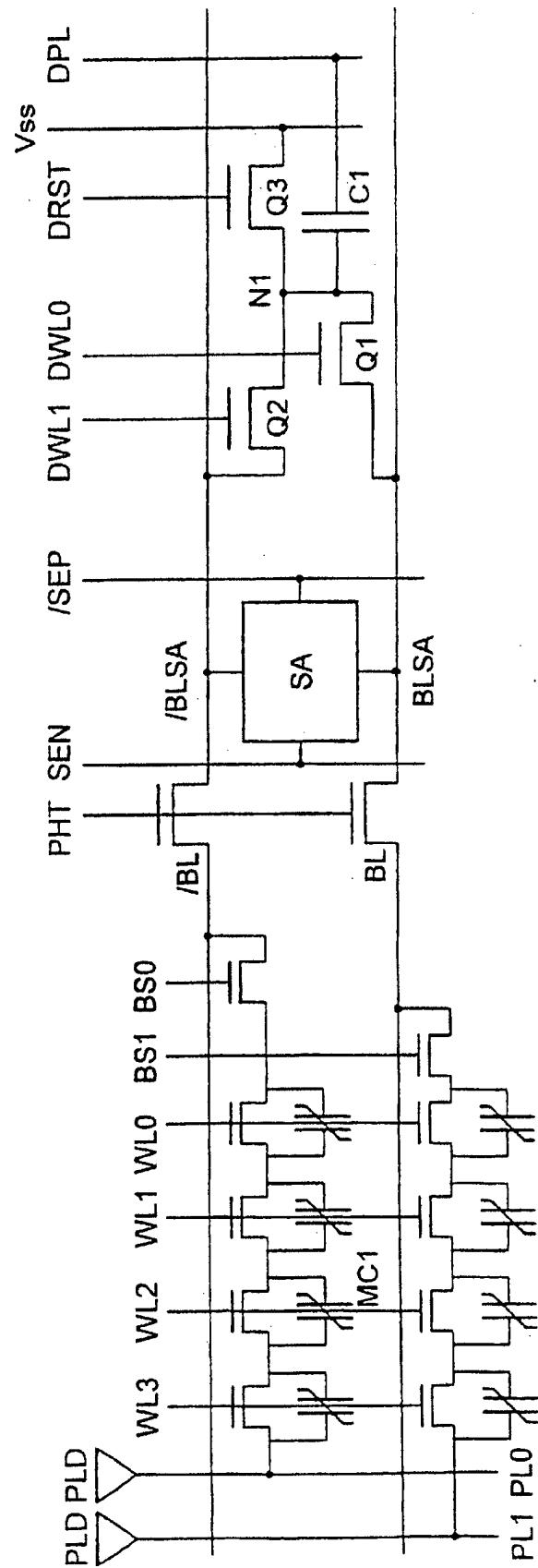

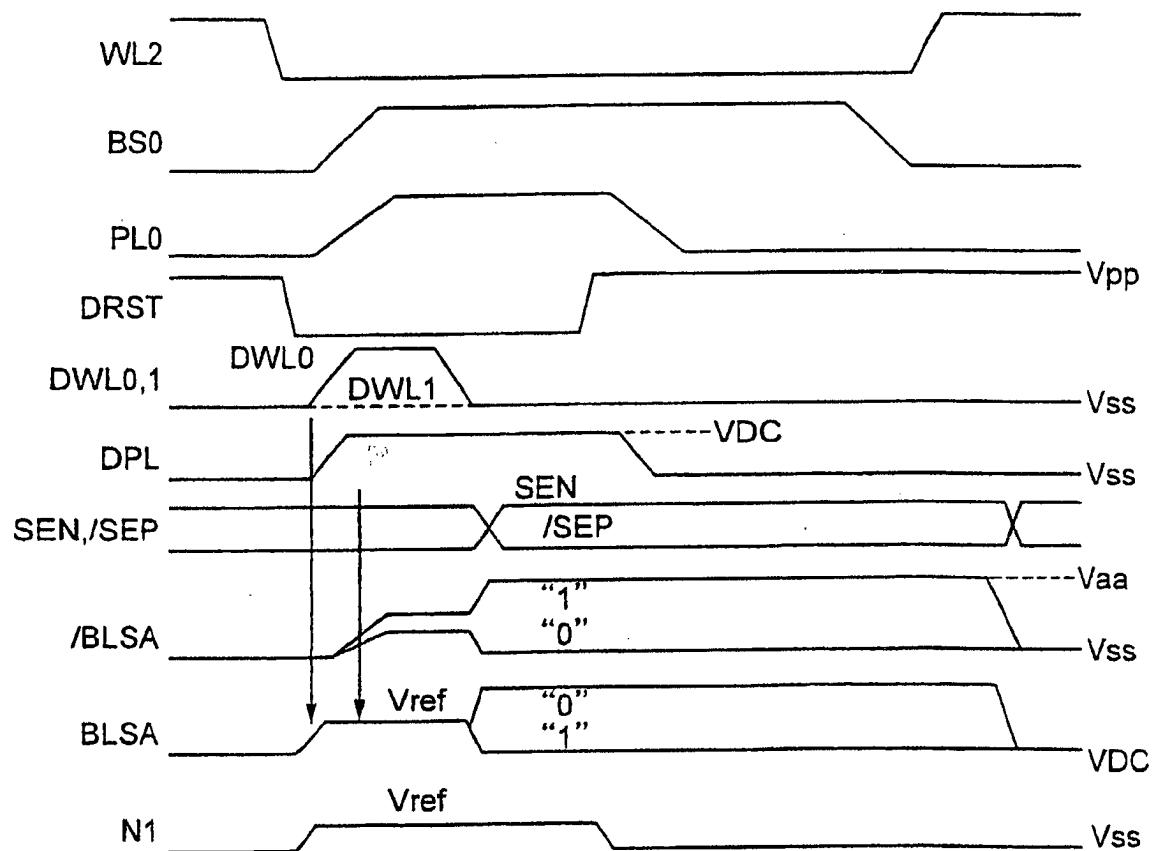

**[0006]** [Fig. 18](#) zeigt eine herkömmliche ferroelektrische Speicherzelle MC1 mit einem Transistor und einem Kondensator, seiner Zellenanordnung, seinem Abtastverstärker und Dummyzellenschaltung. [Fig. 19](#) zeigt ein Zeitablaufdiagramm der Verhaltensweisen.

**[0007]** Wie es sich aus [Fig. 18](#) ergibt, besteht jede Speicherzelle des herkömmlichen ferroelektrischen Speichers aus einem in Serie verbundenen Transistor und Kondensator. Eine Zellenanordnung ist eine Matrixanordnung von solchen Speicherzellen, und

enthält Bitleitungen/BL, BL zum Lesen von Daten, Wortleitungen WL0, WL1 zum Auswählen eines Speicherzellentransistors, und Plattenleitungen PL0, PL1, jeweils zum Ansteuern eines Endes eines ferroelektrischen Kondensators. Der Abtastverstärker ist mit den Bitleitungen verbunden, und die Dummyzellenschaltung ist symmetrisch zur Speicherzelle angeordnet.

**[0008]** Verhaltensweisen des ferroelektrischen Speichers werden mit Bezug auf [Fig. 19](#) beschrieben.

**[0009]** In einem aktiven Modus, in dem beispielsweise die Speicherzelle MC1 ausgewählt wurde, liegt die mit MC1 verbundene Wortleitung auf HOCH und die Plattenleitung PL0 liegt auf HOCH. Als eine Folge werden Speicherzellendaten zu einer eines Paars von Bitleitungen ausgelesen, die auf VSS vorgeladen sind. Im Falle dieses Beispiels, werden Zellendaten zur Bitleitung/BL (BLSA) ausgelesen, und das Potential der Bitleitung erhöht sich. Falls die Speicherzellendaten "1" sind, wird die Polarisation des ferroelektrischen Kondensators umgekehrt, und die Bitleitung wird auf ein hohes Potential angehoben. Falls die Speicherzellendaten "0" sind, tritt die Polarisationsumkehrung nicht auf, sondern das Potential der Bitleitung erhöht sich so viel wie die paraelektrische Komponente des ferroelektrischen Kondensators und das Kapazitanzverhältnis der Bitleitungskapazität.

**[0010]** Auf diese Weise, obwohl sich das Bitleitungspotential von VSS für sowohl Daten "1" und "0" erhöht, ergibt sich ein Unterschied zwischen den Potentialen. Daher ist es möglich, wenn die Referenzbitleitung BL (BLSA) auf ein Zwischenpotential zwischen diesen Potentialen eingestellt werden kann, festzustellen, ob die Zellendaten "1" oder "0" sind, durch Verstärken des Unterschieds zwischen der Bitleitung und der Referenzbitleitung mit dem Abtastverstärker.

**[0011]** Herkömmlicher Weise wurde ein Potential der Bezugsbitleitung unter Verwendung einer Dummyzellenschaltung erzeugt, wie in [Fig. 18](#) gezeigt. In einem Bereitschaftsmodus werden die Transistoren Q1 und Q2, bei denen Dummywortleitungen SWL0, DWL1 mit Gates verbunden sind, AUS geschaltet, und ein Ende N1 des paraelektrischen Kondensators C1 wird auf das Quellenpotential von Q3 vorgeladen, d.h. VSS, durch AN schalten des Transistors Q3. In einem Aktivmodus wird ein Transistor einer Dummywortleitung, der mit der Referenzbitleitung verbunden ist, welches im Beispiel der Transistor Q1 ist, AN geschaltet, um BL und N1 zu verbinden, und dann wird das Potential der Dummyplattenleitung, welches das andere Ende von C1 ist, von VSS auf das VDC Potential angehoben. Mittels dieser Betriebsvorgänge kann das Potential Vref der Referenz BL von VSS auf

das Zwischenpotential zwischen denen entsprechend "1" und "0" Daten mittels des Koppeln des paraelektrischen Kondensators C1 angehoben werden.

**[0012]** Das Dummyzellenschaltungssystem von [Fig. 18](#), oben betrachtet, hat jedoch die folgenden Probleme. Beispielsweise ist in der 0,5 µm Regelklasse die Bitleitungskapazitanz CB ungefähr 1000 fF. Falls ein Speicherzellenkondensator mit dem Bereich von 3 µ<sup>2</sup> verwendet wird, und wenn das Potential auf der HOCH-Seite der Bitleitungsamplitude 3V (=Vaa) ist, dann ist das Auslesepotential an der Bitleitung von "1" Daten im Mittel ungefähr 1,2V für alle Zellen, wohingegen das Auslesepotential der Bitleitung für "0" Daten im Mittel ungefähr 0,4V für alle Zellen ist. Daher ist 0,8V als Bezugsbitleitungspotential erforderlich, und unter Berücksichtigung einer Fluktuation von ferroelektrischen Kondensatoren ist ein Bezugspotential für den Pegel von 1,5V (=1/2Vaa) einschließlich einer Abschätzung für eine Verteilung erforderlich.

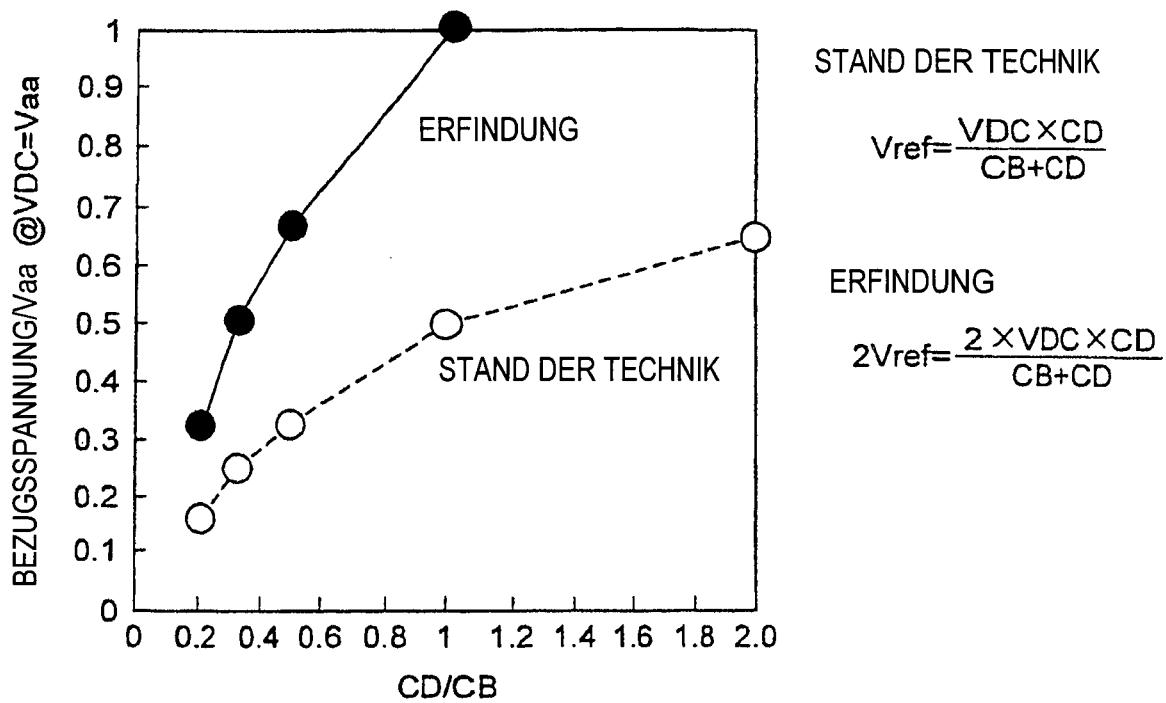

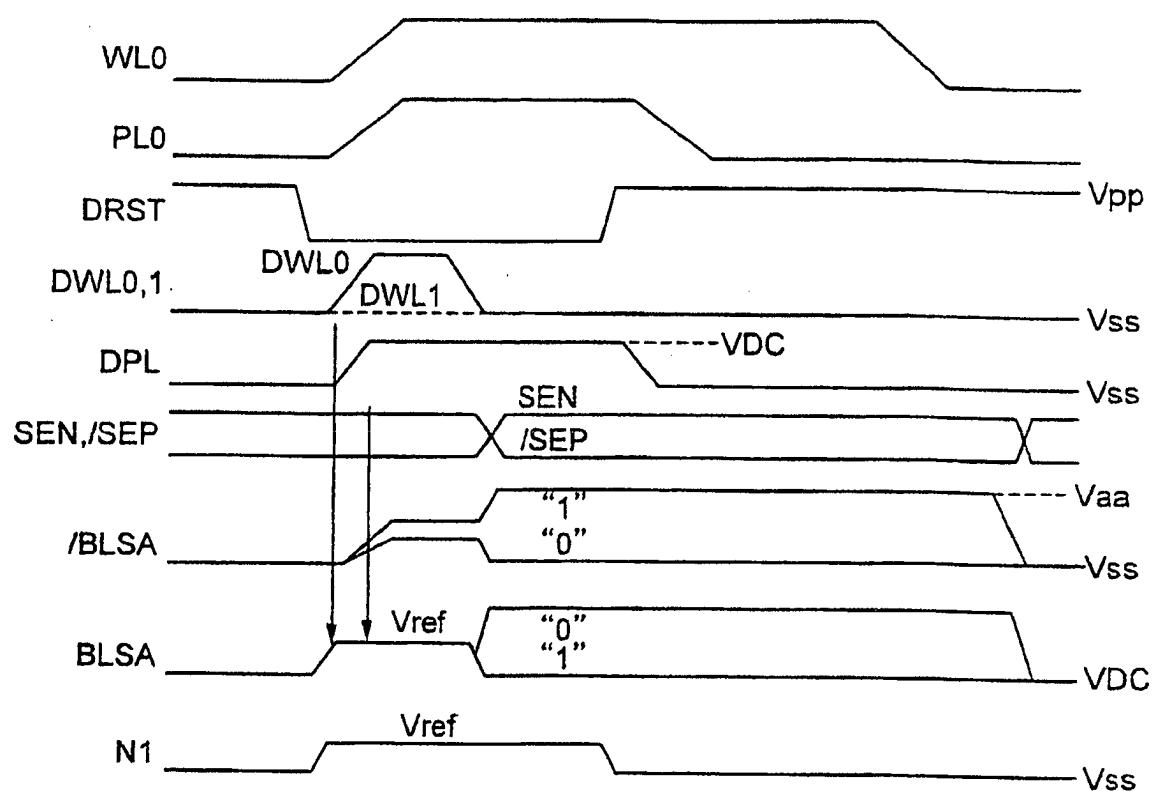

**[0013]** Um das Bitleitungspotential mit 1/2Vaa unter Verwendung der in [Fig. 18](#) gezeigten herkömmlichen Dummyzellenschaltung zu erzeugen, ist ein sehr großer paraelektrischer Kondensator erforderlich. Der Grund dafür wird unterhalb erläutert.

**[0014]** [Fig. 20](#) zeigt einen Wert eines Bezugsbegleitungspotentials Vref unter der Annahme, dass die Kapazitanz des paraelektrischen Kondensators C1 der Dummyzellenschaltung CD ist, eine Bitleitungskapazitanz CB ist und ein Quellenpotential für die Dummyzelle VDC ((0 < VDC < -Vaa): dabei lasse man den Maximalwert Vaa sein) ist. Das Bezugsbitleitungspotential ist ein Wert, der durch ein Teilen von VDC×CD, welches die Ladung des Überschusses zum an jedem des paraelektrischen Kondensators CD von VSS auf VDC ist, durch die Gesamtkapazitanz (CB+CD) erhalten wird. Daher ist zum Erlangen eines 1/2Vaa Potentials eine große paraelektrische Kondensatorkapazitanz CD (=1000fF) gleich der Bitleitungskapazitanz CB erforderlich. Wenn dabei MOS Kondensatoren mit 8 nm verwendet werden, ist ein Dummyzellenkondensator mit einer Größe von 225 µm<sup>2</sup> erforderlich, und die Chipgröße wird sich signifikant erhöhen. Genauer gesagt ist zur Erzeugung von einem Vref von 1V eine Kapazitanz erforderlich, die bei CD=1/2CB liegt, und zur Erzeugung von einem Vref von 1/2Vaa oder mehr, CB<CD. Somit wird CD selbst zu einer Lastkapazitanz und es ergibt sich eine große Schwierigkeit.

**[0015]** Diese Probleme wurden herkömmlicher Weise unter Verwendung von zwei anderen Verfahren vermieden.

**[0016]** Eines dieser Verfahren verwendet einen ferroelektrischen Kondensator, der in einer Speicherzelle verwendet wird, um solch einen Dummykondensa-

tor bereitzustellen, ohne einen paraelektrischen Kondensator wie beispielsweise einen MOS Kondensator mit einer kleinen dielektrischen Konstante zu verwenden. Da das ferroelektrische Material eine sehr große dielektrische Konstante aufweist, kann mit diesem Verfahren eine kleine Dummyzellenschaltung realisiert werden.

**[0017]** Dieses Verfahren hat jedoch unter anderem die folgenden Nachteile,

- 1) der Kapazitanzwert des ferroelektrischen Kondensators selbst ist sehr variabel;

- 2) der ferroelektrische Kondensator ändert sich in seinem Wert aufgrund Alterung, falls er einer Polarisationsumkehrung unterzogen wird;

- 3) der Kapazitanzwert des ferroelektrischen Materials vermindert sich, wenn eine Polarisierung stattfindet; und

- 4) die Charakteristik des ferroelektrischen Kondensators ändert sich aufgrund einer Erzeugung einer Einprägung.

**[0018]** Somit ist es vorzuziehen, dass der paraelektrische Kondensator verwendbar ist.

**[0019]** Das zweite dieser Verfahren erhöht das Plattenpotential im Auslesemodus, um eine Polarisationsumkehrung der Speicherzelle zu bewirken und ein Signal auszulesen, und verwendet das Bitleitungspotential als das Auslesepotential, nachdem es auf VSS vermindert wurde.

**[0020]** Da in diesem Fall das Plattenleitungspotential zum ursprünglichen Wert vorher zurückkehrt, ergibt sich der Effekt, dass keine paraelektrische Komponente des Speicherzellenkondensators erkannt wird. Daher werden sowohl das "1" Datenpotential als auch das "0" Datenpotential zu niedrigen Potentialen, und eine Dummyzelle, auch mit einem kleinen paraelektrischen Kondensator, kann ein ausreichendes Bezugsbitleitungspotential erzeugen.

**[0021]** Dieses Verfahren hat jedoch die folgenden Nachteile.

- 1) Da nach einem Erhöhen und Vermindern der Plattenleitung der Abtastverstärkungsbetrieb stattfindet, wird eine Nurlese-Zeitdauer sehr lang, und

- 2) da Betriebsvorgänge zum Erhöhen und Vermindern der Plattenleitung bei einem Neuschreiben von Daten benötigt werden, ergibt sich eine Erhöhung und Verminderung der Plattenleitung doppelt, und die Zykluszeit wird sehr lang.

**[0022]** Der Erfinder hat bereits hat bereits in der US Patentveröffentlichung Nr. 5 903 492 als nicht-flüchtigen ferroelektrischen Speicher einen neuen Typ von ferroelektrischem Speicher vorgeschlagen, der gleichzeitig drei Anforderungen erfüllt, nämlich:

- 1) Speicherzelle mit kleiner Größe,

- 2) Planartransistor, der einfach herzustellen ist, und

- 3) flexible Lese/Schreibzugriffsfunktion.

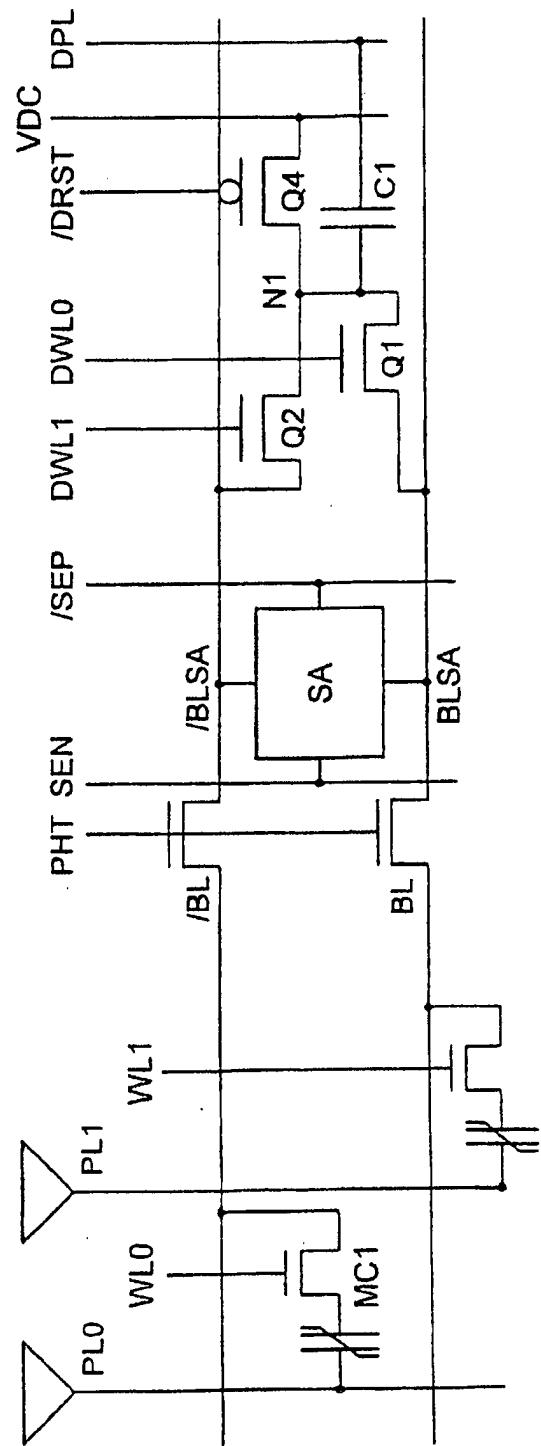

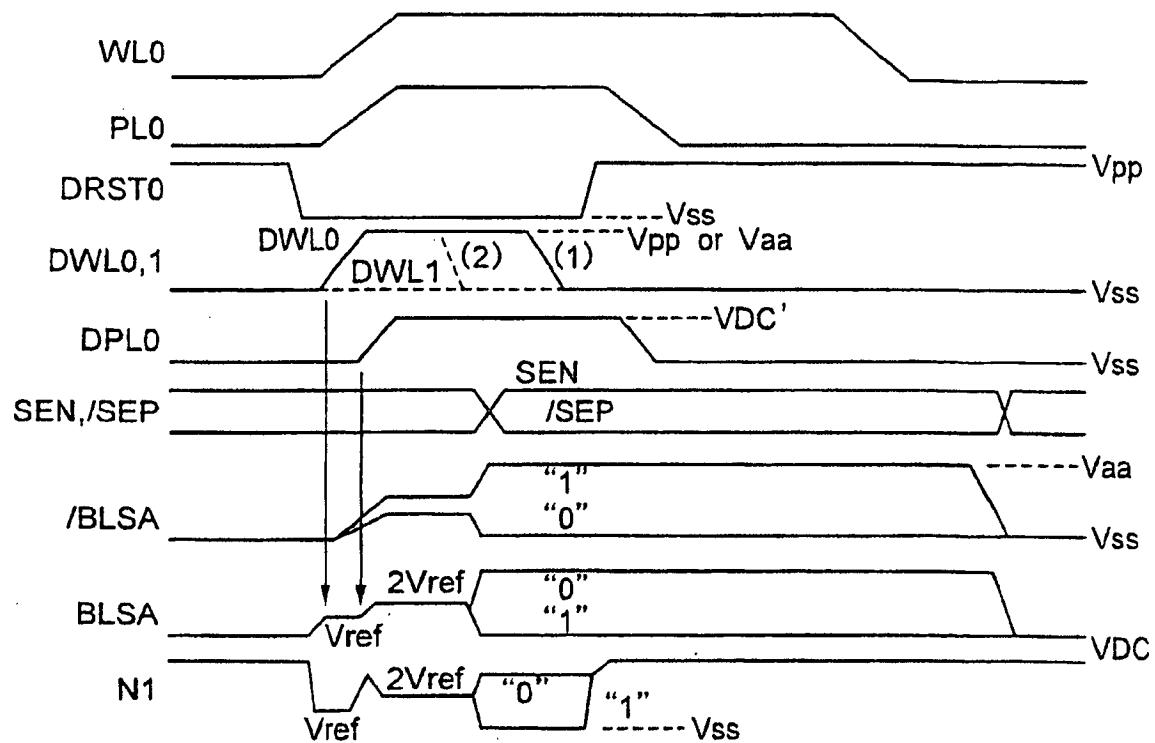

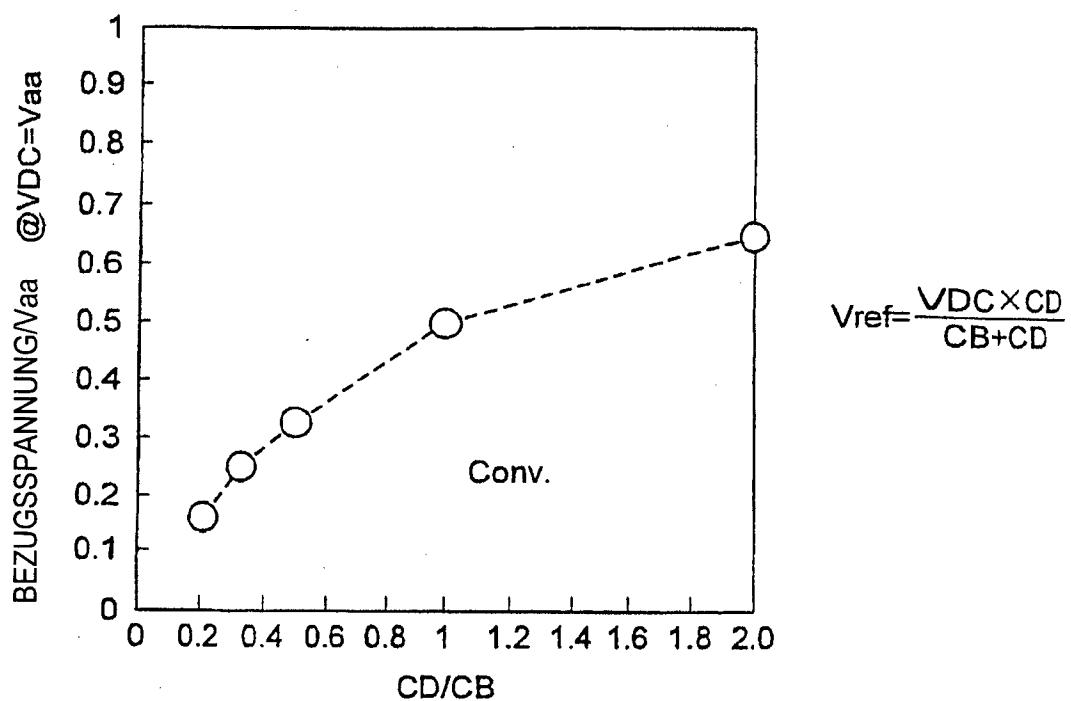

**[0023]** [Fig. 21](#) zeigt eine Konfiguration dieses früheren ferroelektrischen Speichers, und [Fig. 22](#) zeigt ein Beispiel seiner Betriebsvorgänge. Da diese frühere Erfindung das gleiche Ausleseprinzip wie der konventionelle ferroelektrische Speicher verwendet, verwendet es auf ähnliche Weise die in [Fig. 21](#) gezeigte Dummyzellenschaltung, die ähnlich der in [Fig. 18](#) ist, zum Erzeugen des Bezugsbitleitungspotentials.

**[0024]** Im Bereitschaftsmodus sind die Transistoren Q1, Q2 der Dummywortleitungen AUS geschaltet, und der Transistor Q3 wird AN gehalten, ein Ende N1 des paraelektrischen Kondensators C1 wird auf das Quellenpotential von Q3, d.h. das VSS Potential vorgeladen.

**[0025]** In einem Aktivmodus wird ein Transistor einer Dummywortleitung, die mit der Bezugsbitleitung verbunden ist, welches in diesem Beispiel der Transistor Q1 ist, AN geschaltet, um BL und N1 zu verbinden, und dann wird das Potential der Dummyplattenleitung, welches das andere Ende von C1 ist, von VSS auf das VDC Potential angehoben. Durch diesen Betrieb kann das Potential Vref der Bezugs-BL von Vss auf das Zwischenpotential zwischen denen entsprechend "1" und "0" Daten angehoben werden, durch Koppeln des paraelektrischen Kondensators C1.

**[0026]** Daher treten ebenso wie in der früheren Anmeldung Probleme auf, die in [Fig. 19](#) und [Fig. 20](#) gezeigt sind. Im Vergleich mit dem herkömmlichen ferroelektrischen Speicher ist die Bitleitungskapazitanz in der früheren Anwendung ungefähr 1/4 pro Zelle, und die Anzahl von Zellen für jeden Abtastverstärker (Bitleitung) kann auf das vierfache angehoben werden. In diesem Fall kann die Anzahl von Dummyzellenschaltungen auf 1/4 reduziert werden, und Einflüsse des Bereichs der Dummyzellen sind nicht so groß wie bei dem herkömmlichen ferroelektrischen Speicher. Nichtsdestoweniger werden immer noch mehrere Prozent des Chipbereichs benötigt, und eine Reduktion des Dummyzellbereichs ist erwünscht. Beispielsweise ist, falls die Anzahl von Zellen pro Bitleitung 1/2 ist und eine reduzierte Größe für CB für ein Verbessern von Signalen verwendet wird, CB ungefähr 500 fF in der 0,5 µm Regelklasse und falls ein Speicherzellenkondensator mit dem Bereich von 3 µm<sup>2</sup> verwendet wird und das HOCH-seitige Potential der Bitleitungsamplitude 3V (=Vaa) ist, ist das Auslesepotential zur Bitleitung für "1" Daten ungefähr 1,5 V im Mittel für alle Zellen, und das Auslesepotential zur Bitleitung für "0" Daten ist ungefähr 0,5 V im Mittel für alle Zellen. Daher ist 1 V als Bezugsbitleitungspotential erforderlich, und unter Berücksichtigung einer Fluktuation von ferroelektrischen Kondensatoren ist

ein Bezugspotential im Pegel von 1,5 V (=1/2Vaa) erforderlich. Um das Bezugsbitleitungspotential von 1/2Vaa unter Verwendung der herkömmlichen Dummyzellenschaltung aus [Fig. 21](#) zu erzeugen, ist ein sehr großer paraelektrischer Kondensator, wie in [Fig. 20](#) gezeigt, ähnlich wie beim herkömmlichen ferroelektrischen Speicher erforderlich. Um ein 1/2Vaa Potential zu erzielen, muss eine große paraelektrische Kondensatorkapazitanz CD (=500 fF) des gleichen Wertes wie die Bitleitungskapazitanz CB verwendet werden. Damit, falls MOS Kondensatoren mit 8 nm verwendet werden, ein Dummyzellenkondensator mit einer Größe von 112 µm<sup>2</sup> erforderlich, und die Chipgröße wird sich signifikant erhöhen. Weiter ist zur Erzeugung einer Vref von 1 V eine Kapazitanz so groß wie CD=1/2CB erforderlich, und zum Erzeugen von Vref mit 1/2Vaa oder mehr, CB<CB. Somit wird CD selbst zur Lastkapazitanz, und es ergibt sich eine große Schwierigkeit.

**[0027]** Wie oben betrachtet hat der herkömmliche ferroelektrische Speicher und der ferroelektrische Speicher der früheren Anmeldung das Problem einer Erhöhung der Chipgröße aufgrund der Notwendigkeit eines großen Kondensatorbereichs, wenn ein paralektrischer Kondensator zur Erzeugung eines hohen Bezugsbitleitungspotentials verwendet wird. Das Verfahren zur Erzeugung des Bezugsbitleitungspotentials unter Verwendung eines ferroelektrischen Kondensators bei Vermeidung dieses Problems ergibt Probleme einer Varianz, Verschlechterung, Veränderung und von Fluktuationen, und hatte das Problem unerwünschter Änderung beim Bezugsbitleitungspotential und einer Veränderung der Signalauslesespanne. Zusätzlich, obwohl es ein Verfahren zum Vermeiden dieser Probleme gibt, durch ein doppeltes Erhöhen und Vermindern der Plattenleitung, und dadurch Vermindern des Bezugsbitleitungspotentials, wies dieses Verfahren das Problem eines langsamen Betriebs auf.

## ZUSAMMENFASSUNG DER ERFINDUNG

**[0028]** In Übereinstimmung mit der Erfindung wird eine HalbleiterSpeichervorrichtung bereitgestellt, umfassend:

- eine Mehrzahl von Speicherzellen, einschließlich einer seriellen Verbindung von Zelltransistoren und ferroelektrischen Kondensatoren;

- eine Mehrzahl von mit den Zelltransistoren verbundenen Wortleitungen;

- eine Mehrzahl von mit den Speicherzellen verbundenen Bitleitungspaaren;

- eine Mehrzahl von Verstärkerschaltungen, die mit den Bitleitungspaaren verbunden sind, um eine Signaldifferenz zwischen Bitleitungen in jedem Bitleitungspaar zu verstärken; und

- eine Dummyzellenschaltung zur Erzeugung eines Potentials für eine Bitleitung eines der Bitleitungspaare, welche eine Bezugsbitleitung ist, an die Daten

von den Speicherzellen nicht ausgelesen werden, wobei die Dummyzellenschaltung mindestens einen paraelektrischen Kondensator umfasst; wobei in einem Bereitschaftsmodus ein erster Anschluss des paraelektrischen Kondensators auf ein erstes Potential vorgeladen ist, das höher als Massepotential ist, und ein zweiter Anschluss des paraelektrischen Kondensators auf Massepotential vorgeladen ist; und in einem Aktivmodus der erste Anschluss mit der Bezugsbegleitung verbunden ist und der zweite Anschluss vom Massepotential auf ein zweites Potential angehoben ist, das höher als das Massepotential ist.

**[0029]** In Übereinstimmung mit einem Ausführungsbeispiel der Erfindung wird die Halbleiterspeichervorrichtung in Übereinstimmung mit Anspruch 1 bereitgestellt, wobei der erste Anschluss mit einer von Bitleitungen in jedem Bitleitungspaar über einen ersten Transistor angeschlossen ist, mit den anderen Bitleitungen in jedem Bitleitungspaar über einen zweiten Transistor verbunden ist, und mit dem dritten Potential über einen dritten Transistor verbunden ist.

**[0030]** In Übereinstimmung mit einem weiteren Ausführungsbeispiel der Erfindung wird die Halbleiterspeichervorrichtung gemäß Anspruch 2 bereitgestellt, wobei der dritte Transistor in entgegengerichteter Phase zum ersten und zweiten Transistor arbeitet.

**[0031]** In Übereinstimmung mit einem weiteren Ausführungsbeispiel der Erfindung wird die Halbleiterspeichervorrichtung nach Anspruch 1 bereitgestellt, wobei der erste Anschluss mit einer von Bitleitungen jedes Bitleitungspaares über einen ersten Transistor verbunden ist, und mit dem ersten Potential über einen dritten Transistor verbunden ist.

**[0032]** In Übereinstimmung mit einem weiteren Ausführungsbeispiel der Erfindung wird die Halbleiterspeichervorrichtung nach Anspruch 4 bereitgestellt, wobei der dritte Transistor in entgegengerichteter Phase zum ersten Transistor arbeitet.

**[0033]** In Übereinstimmung mit einem weiteren Ausführungsbeispiel der Erfindung wird die Halbleiterspeichervorrichtung nach Anspruch 1 bereitgestellt, wobei das erste Potential und das zweite Potential gleich sind.

**[0034]** In Übereinstimmung mit einem weiteren Ausführungsbeispiel der Erfindung wird die Halbleiterspeichervorrichtung nach Anspruch 1 bereitgestellt, wobei der zweite Anschluss von Massepotential auf das zweite Potential angehoben ist, höher als Massepotential, nachdem der erste Anschluss mit der Bezugsbegleitung verbunden ist.

**[0035]** Gemäß einem weiteren Ausführungsbeispiel der Erfindung wird eine Halbleiterspeichervorrichtung

nach Anspruch 1 bereitgestellt, wobei die Dummyzellenschaltung einen ersten Dummyzellenabschnitt mit einem ersten paraelektrischen Kondensator umfasst, zur Erzeugung eines ersten Potentials einer ersten Bitleitung des Bitleitungspaares, und einen zweiten Dummyzellenabschnitt mit einem zweiten paraelektrischen Kondensator zur Erzeugung eines zweiten Potentials einer zweiten Bitleitung des Bitleitungspaares, und wobei ein erster Anschluss des ersten paraelektrischen Kondensators mit der ersten Bitleitung über einen ersten Transistor verbunden ist, und mit einem ersten Dummyzellenenergieversorgungspotential über einen zweiten Transistor, und wobei ein zweiter Anschluss des ersten paraelektrischen Kondensators mit einer ersten Dummyplattenleitung verbunden ist, und ein erster Anschluss des zweiten paraelektrischen Kondensators mit der zweiten Bitleitung über einen dritten Transistor und mit einem zweiten Dummyzellenenergieversorgungspotential über einen vierten Transistor verbunden ist, und wobei ein zweiter Anschluss des zweiten paraelektrischen Kondensators mit einer zweiten Dummyplattenleitung verbunden ist, und wobei das erste und zweite Dummyzellenenergiopotential höher als das Massepotential ist.

**[0036]** In Übereinstimmung mit einem weiteren Ausführungsbeispiel der Erfindung wird die Halbleiterspeichervorrichtung nach Anspruch 8 bereitgestellt, wobei dann, wenn die erste Bitleitung die Bezugsbitleitung ist, der erste und zweite Transistor gesteuert werden, und falls die zweite Bitleitung die Bezugsbitleitung ist, der dritte und vierte gesteuert werden.

**[0037]** In Übereinstimmung mit einem weiteren Ausführungsbeispiel der Erfindung wird die Halbleiterspeichervorrichtung nach Anspruch 9 bereitgestellt, wobei in einem Bereitschaftsmodus ein erster Anschluss des ersten und zweiten paraelektrischen Kondensators auf das erste Potential höher als Massepotential vorgeladen ist, und ein zweiter Anschluss des ausgewählten paraelektrischen Kondensators auf Massepotentials vorgeladen ist; und in einem aktiven Modus der erste Anschluss des ausgewählten paraelektrischen Kondensators mit der Bezugsbitleitung verbunden ist, und der zweite Anschluss des ausgewählten paraelektrischen Kondensators von Massepotential auf ein zweites Potential höher als Massepotential angehoben ist.

**[0038]** In Übereinstimmung mit einem weiteren Ausführungsbeispiel der Erfindung wird die Halbleiterspeichervorrichtung nach einem der Ansprüche 1 bis 10 bereitgestellt, wobei die Mehrzahl von Speicherzellen eine Mehrzahl von Speicherzellenblöcken bereitstellen, jeweils mit einer seriellen Verbindung mit mindestens einer Mehrzahl von Speicherzellen, die jeweils einen Zelltransistor und einen ferroelektrischen Kondensator umfassen, parallel verbunden

zwischen Source- und Drainanschlüssen des Zellentransistors.

**[0039]** In Übereinstimmung mit einem weiteren Ausführungsbeispiel der Erfindung wird die Halbleiter-speichervorrichtung nach Anspruch 1 bereitgestellt, wobei der erste Anschluss mit einer von Bitleitungen in jedem Bitleitungspaar über den ersten Transistor verbunden ist, und mit der anderen von Bitleitungen in jedem Bitleitungspaar über einen zweiten Transistor verbunden ist, und mit dem ersten Potential über einen dritten Transistor verbunden ist.

#### KURZE BESCHREIBUNG DER ZEICHNUNGEN

**[0040]** In den begleitenden Zeichnungen:

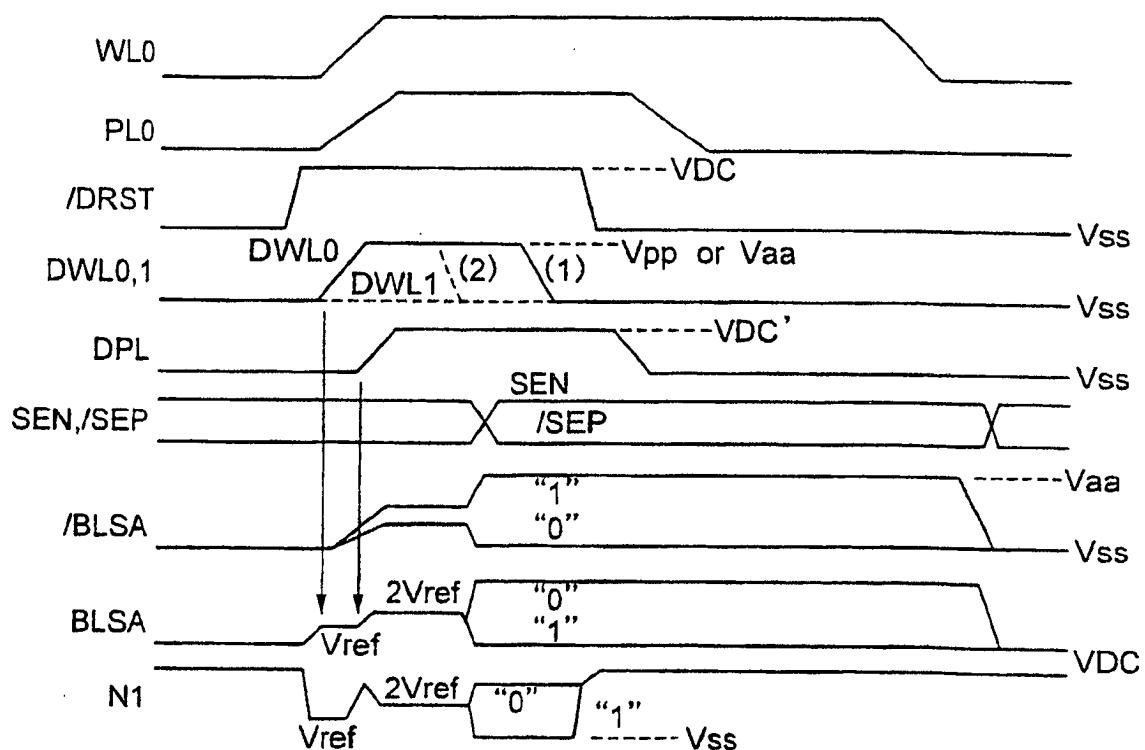

**[0041]** [Fig. 1](#) zeigt ein Schaltdiagramm einer Konfiguration eines Arrays, Abtastverstärkers und Dummyzellenschaltung des ferroelektrischen Speichers gemäß dem ersten Ausführungsbeispiel der Erfindung;

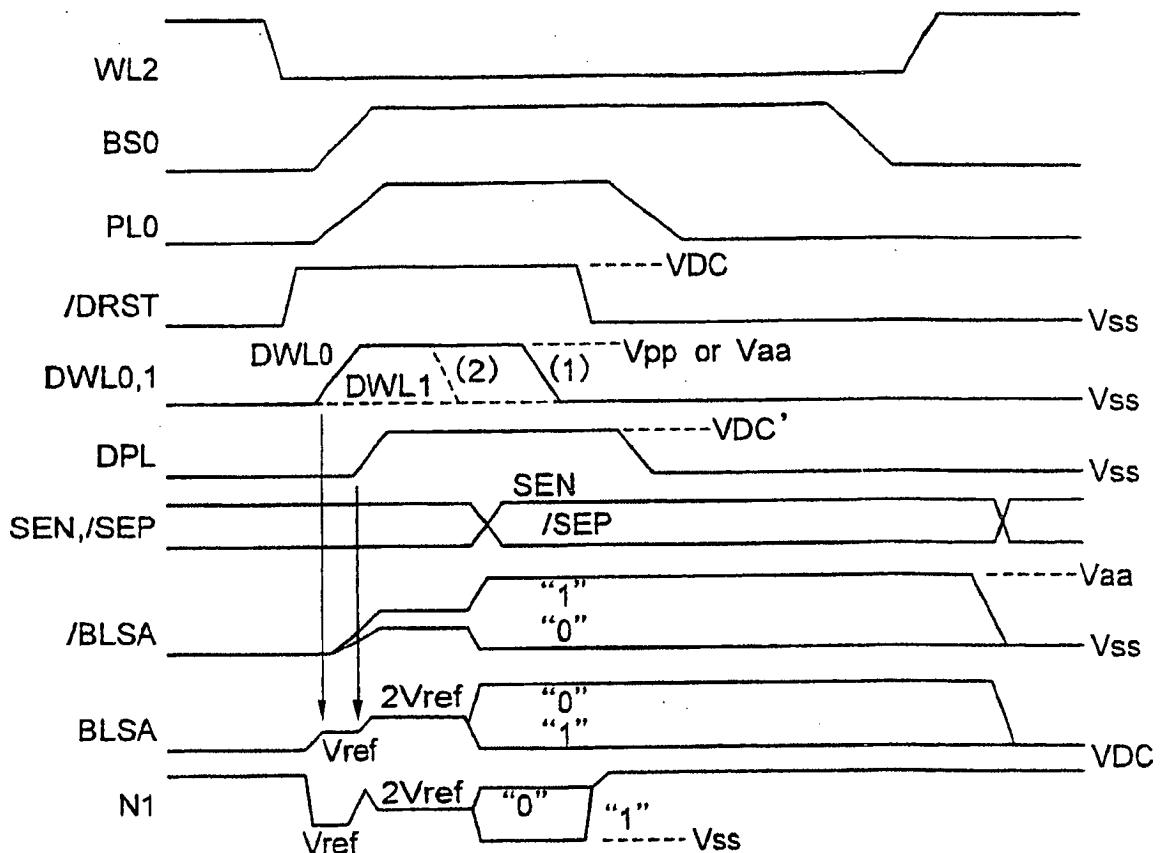

**[0042]** [Fig. 2](#) zeigt ein Zeitablaufdiagramm eines Beispiels einer Betriebszeitvorgabe der Konfiguration von [Fig. 1](#);

**[0043]** [Fig. 3](#) zeigt in einem Diagramm eine Wirkung des ersten Ausführungsbeispiels der Erfindung;

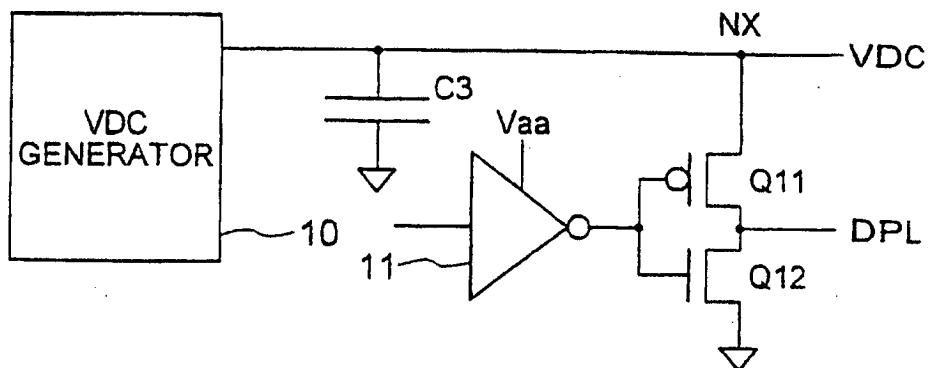

**[0044]** [Fig. 4](#) zeigt ein Schaltdiagramm einer Steuerschaltung der Dummyzelle von [Fig. 1](#);

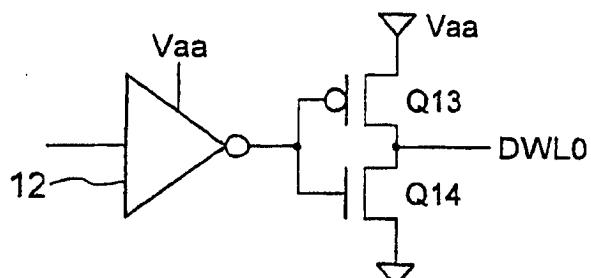

**[0045]** [Fig. 5](#) zeigt ein Schaltdiagramm einer Erzeugungsschaltung für DWLO;

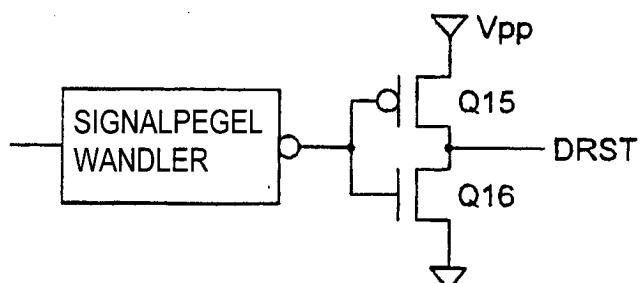

**[0046]** [Fig. 6](#) zeigt ein Schaltdiagramm einer Treiberschaltung eines DRST Signals;

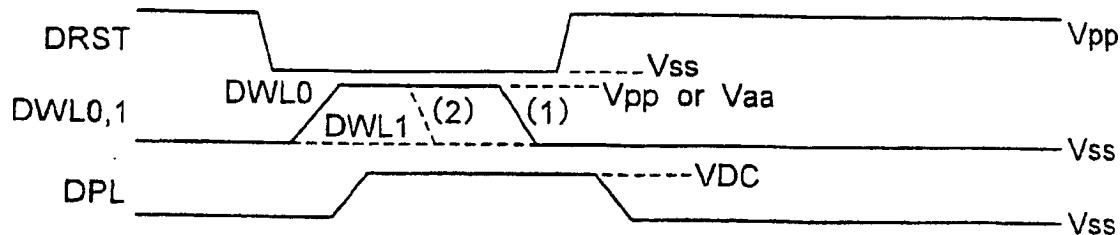

**[0047]** [Fig. 7](#) zeigt ein Zeitablaufdiagramm eines Bezuges unter Signalen die in [Fig. 4](#) bis [Fig. 6](#) ausgegeben werden;

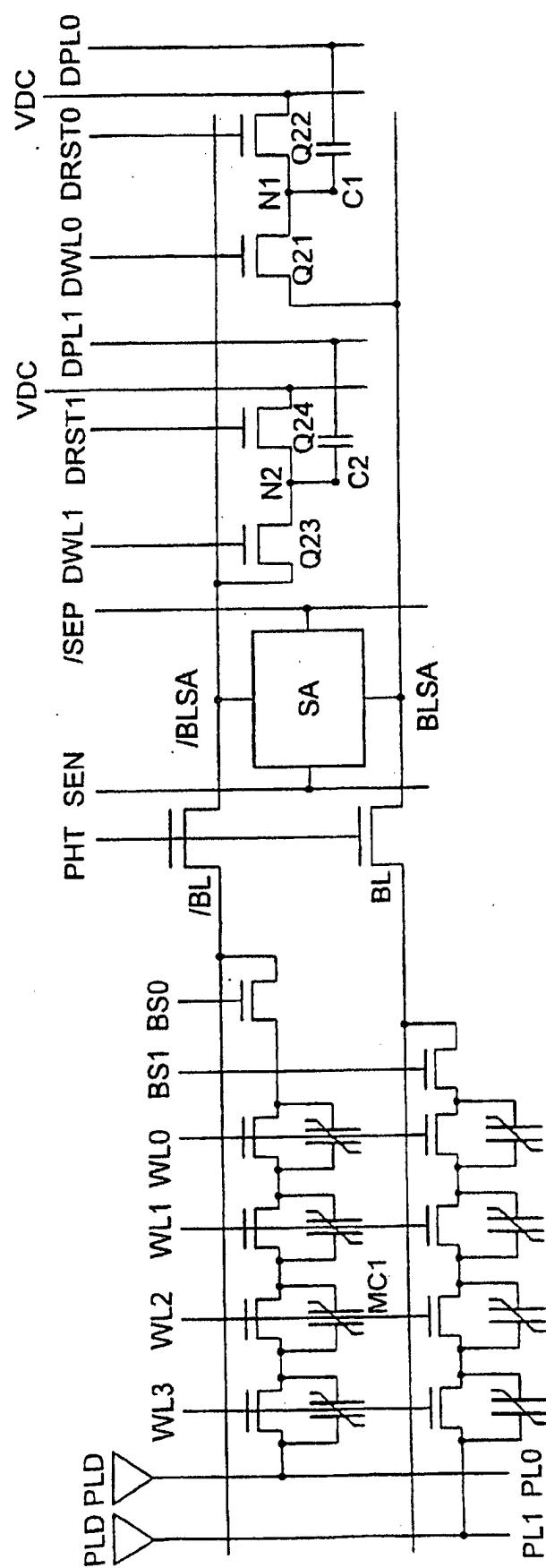

**[0048]** [Fig. 8](#) zeigt ein Schaltdiagramm einer Konfiguration eines Arrays, eines Abtastverstärkers und einer Dummyzellenschaltung eines ferroelektrischen Speichers, im zweiten Ausführungsbeispiel der Erfindung;

**[0049]** [Fig. 9](#) zeigt ein Zeitablaufdiagramm eines Beispiels einer Betriebszeitvorgabe der Schaltung von [Fig. 8](#);

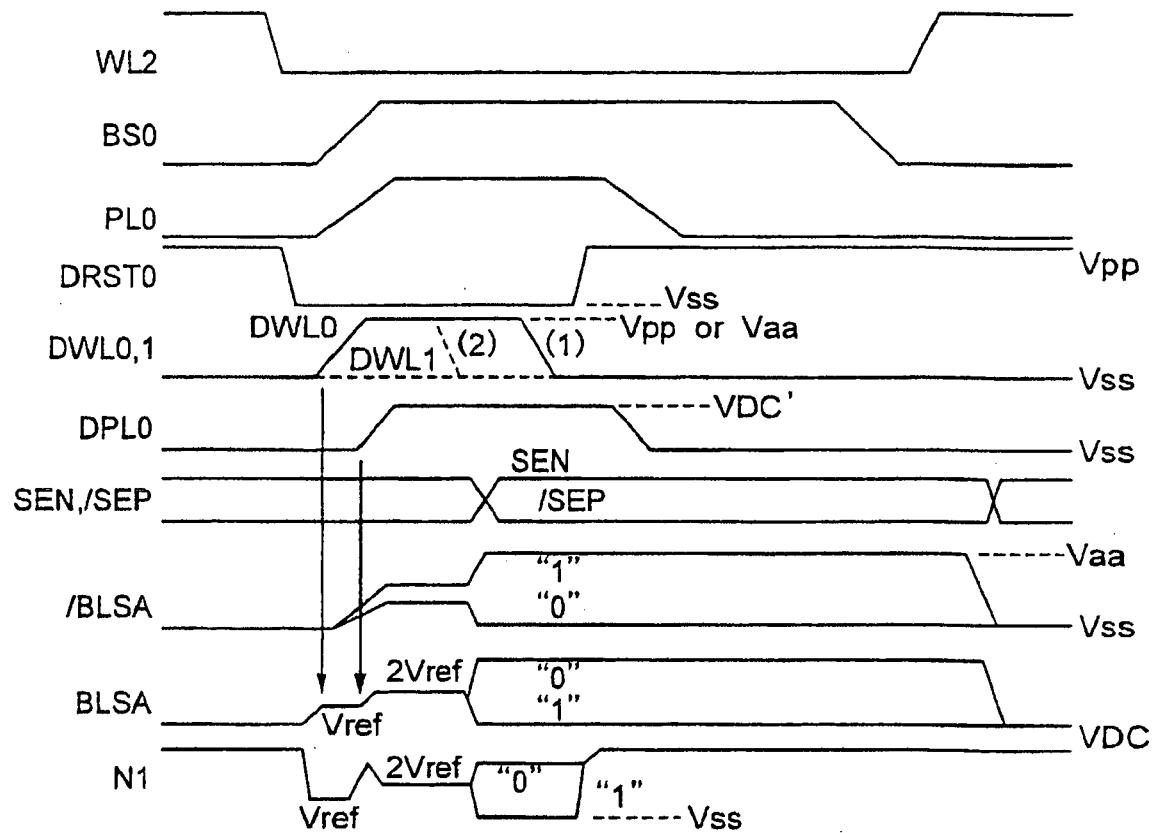

**[0050]** [Fig. 10](#) zeigt ein Schaltdiagramm einer Konfiguration eines Arrays, des Verstärkers und Dummyzellenschaltung eines ferroelektrischen Speichers im dritten Ausführungsbeispiel der Erfindung;

**[0051]** [Fig. 11](#) zeigt ein Zeitablaufdiagramm eines Beispiels einer Betriebszeitvorgabe der Schaltung

von [Fig. 10](#);

**[0052]** [Fig. 12](#) zeigt ein Schaltdiagramm einer Konfiguration eines Arrays, des Verstärkers und einer Dummyzellenschaltung eines ferroelektrischen Speichers im vierten Ausführungsbeispiel der Erfindung;

**[0053]** [Fig. 13](#) zeigt ein Zeitablaufdiagramm eines Beispiels einer Betriebszeitvorgabe der Schaltung von [Fig. 12](#);

**[0054]** [Fig. 14](#) zeigt ein Schaltdiagramm einer Konfiguration eines Arrays, Abtastverstärkers und einer Dummyzellenschaltung eines ferroelektrischen Speichers im fünften Ausführungsbeispiel der Erfindung;

**[0055]** [Fig. 15](#) zeigt ein Zeitablaufdiagramm einer Beispielsbetriebszeitvorgabe der Schaltung von [Fig. 14](#);

**[0056]** [Fig. 16](#) zeigt ein Schaltdiagramm einer Konfiguration eines Arrays, Abtastverstärkers und einer Dummyzellenschaltung eines ferroelektrischen Speichers im sechsten Ausführungsbeispiel der Erfindung;

**[0057]** [Fig. 17](#) zeigt ein Zeitablaufdiagramm einer Beispielsbetriebsablaufzeitvorgabe der Schaltung von [Fig. 16](#);

**[0058]** [Fig. 18](#) zeigt ein Schaltdiagramm einer Konfiguration eines Arrays, Abtastverstärker und einer Dummyzellenschaltung eines ferroelektrischen Speichers mittels herkömmlicher Technik;

**[0059]** [Fig. 19](#) zeigt ein Zeitablaufdiagramm eines Beispiels einer Betriebsablaufzeitvorgabe der Schaltung von [Fig. 18](#);

**[0060]** [Fig. 20](#) zeigt in einem Diagramm Werte eines Bezugsbitleitungspotentials Vref in einer herkömmlichen Dummyzellenschaltung;

**[0061]** [Fig. 21](#) zeigt ein Schaltdiagramm einer Konfiguration eines ferroelektrischen Speichers einer früheren Anmeldung; und

**[0062]** [Fig. 22](#) zeigt ein Zeitdiagramm eines Beispiels von perationen in [Fig. 21](#).

#### BESCHREIBUNG DER BEVORZUGTEN AUSFÜHRUNGSBEISPIELE

**[0063]** Mit Bezug auf die Zeichnungen werden nun Ausführungsbeispiele der Erfindung unterhalb beschrieben.

**[0064]** Die [Fig. 1](#) und [Fig. 2](#) veranschaulichen eine Konfiguration des ersten Ausführungsbeispiels der Erfindung, wobei [Fig. 1](#) eine Konfiguration eines Ar-

rays, Abtastverstärkers und einer Dummyzellschaltung der Erfindung zeigt, und [Fig. 2](#) das Betriebszeitablaufdiagramm. [Fig. 3](#) zeigt ein Diagramm von Wirkungen.

**[0065]** Eine einzelne Speicherzelle besteht aus einem Zellentransistor und einem parallel angeschlossenen ferroelektrischen Kondensator. Ein einzelner Speicherzellenblock besteht aus einer seriellen Verbindung einer Mehrzahl solcher parallel verbundener Speicherzellen, wobei ein Ende davon mit einer Bitleitung über einen Blockauswahltransistor verbunden ist, und das andere mit einer Platte verbunden ist. Mit dieser Konfiguration können unter Verwendung von Planartransistoren Speicherzellen mit 4F2 Größe realisiert werden.

**[0066]** Wie in [Fig. 1](#) gezeigt können durch Bereitstellen zweier Arten von Blockauswahltransistoren und Blockauswahlsignalen BS0, BS1 für /BL beziehungsweise BL und durch ein Legen eines der Blockauswahltransistoren (BS0, BS1) auf HOCH, gefaltete Bitleitungen realisiert werden, wobei Daten von nur einer der zwei Zellenblöcke zur Bitleitung ausgelesen werden und die andere des Paar von Bitleitungen als Bezugsbitleitung verwendet wird, und eine 1T/1C Zelle, die nur einen Zellentransistor und einen ferroelektrischen Kondensator zur Speicherung von Ein-Bitdaten kann bereitgestellt werden. Weiter kann durch ein Vorbereiten von zwei Arten von Datenleitungen und durch ein Ansteuern von nur einer der Plattenleitungen in Hinblick auf die ausgewählte Bitleitung eine Anlegung einer Spannung an die nicht ausgewählte Zelle auf der Bezugsseite verhindert werden.

**[0067]** Ein Verhalten der Schaltung wird kurz erläutert. In einem Bereitschaftsmodus werden alle (Sub)Wortleitungen WL0 bis WL3 auf HOCH gehalten, Speicherzellentransistoren werden AN gehalten, die Blockauswahlsignale BS0, BS1 sind auf NIEDRIG eingestellt, und der Blockauswahltransistor wird AUS gehalten. Auf diese Weise wird, da gegenüberliegende Seiten des ferroelektrischen Kondensators elektrisch kurzgeschlossen sind, mittels des AN gehaltenen Transistors, keine Potentialdifferenz zwischen gegenüberliegenden Enden erzeugt, und die Speicherpolarisation wird stabil gehalten.

**[0068]** In einem Aktivmodus wird das auf Vss vorgeladene Paar von Bitleitungen in den schwebenden Zustand geändert. Dann wird durch ein Ausschalten von nur dem Speicherzellentransistor, der parallel mit dem ferroelektrischen Kondensator verbunden ist, der auszulesen ist, der Blockauswahltransistor AN geschaltet. Beispielsweise wir im Falle eines Auswählens des ferroelektrischen Speicherzellenkondensators MC1 in [Fig. 1](#) WL2 auf NIEDRIG gestellt. Danach wird durch ein Einstellen der Plattenleitung BL0 hinsichtlich MC1 auf HOCH und durch ein Stellen des Blockauswahlsignals BS0 hinsichtlich MC1

auf HOCH eine Potentialdifferenz zwischen PL0 und/BL nur an gegenüberliegende Enden des ferroelektrischen Kondensators MC1 angelegt, der parallel mit dem Speicherzellentransistor verbunden ist, der AUS geschaltet wurde, und die Polarisationsinformation des ferroelektrischen Kondensators wird zur Bitleitung/BL ((BLSA) ausgelesen, die auf Vss schwebt. Daher kann, auch wenn Zellen in Serie verbunden sind, durch ein Auswählen einer erwünschten Sub-Wortleitung Zelleninformation eines erwünschten ferroelektrischen Kondensators ausgelesen werden, und ein vollständiger Zufallszugriff wird realisiert.

**[0069]** Wenn Daten "1" sind, tritt eine Polarisationsumkehr im ferroelektrischen Kondensator auf, und die Bitleitung wird auf ein hohes Potential (BLh) angehoben. Wenn die Daten "0" sind, tritt eine Polarisationsumkehr nicht auf, und die Bitleitung (BL1) erhöht sich soweit wie die paraelektrische Komponente des ferroelektrischen Kondensators und das Kapazitanzverhältnis der Bitleitungskapazitanz. Auf diese Weise ist, obwohl das Bitleitungs-Potential sich von Vss für sowohl Daten "1" als auch "0" erhöht, eine Differenz zwischen diesen Potentialen. Daher ist es, falls die Bezugsbitleitung BLA (BLSA) auf ein Zwischenpotential zwischen diesen Potentialen eingestellt werden kann, möglich, zu unterscheiden, ob die Zellendaten "1" oder "0" sind, durch Verstärken der Differenz zwischen der Bitleitung und der Bezugsbitleitung mit dem Abtastverstärker.

**[0070]** Die Dummyzellenschaltung, die das Bezugsbitleitungs-Potential erzeugt, wird durch Verwendung der in [Fig. 1](#) gezeigten Schaltung konfiguriert.

**[0071]** In einem Bereitschaftsmodus werden die Transistoren Q1, Q2 der Dummywortleitungen AUS geschaltet, und ein Ende N1 des paraelektrischen Kondensators C1 wird auf das Quellenpotential von Q3 vorgeladen, d.h. VDC (>Vss) Potential, durch ein Halten des Transistors Q3 auf AN. Die Dummyplattenleitung DPL am anderen Ende des paraelektrischen Kondensators wird auf dem Vss Potential gehalten. Das heißt, die Spannung VDC wird an gegenüberliegende Enden des paraelektrischen Kondensators angelegt, damit dieser die Ladung CDxVDC hält.

**[0072]** In einem aktiven Modus wird ein Transistor einer mit der Bezugsbitleitung verbundenen Dummywortleitung, welcher in diesem Beispiel der Transistor Q1 ist, AN geschaltet, um WL und N1 zu verbinden. Als eine Folge werden die im paraelektrischen Kondensator gespeicherten Ladungen zur Bezugsbitleitung entladen. Danach wird das Potential der Dummyplattenleitung DPL, welches das andere Ende von C1 ist, von Vss auf das VDC' Potential angehoben. Mittels dieser Operationen wird ein Wert entsprechend der Ladung von CDxVDC' gebildet, durch ein

Koppeln des paraelektrischen Kondensators C1, und die Ladung wird von der Bezugsbitleitung und dem paraelektrischen Kondensator geteilt.

**[0073]** Mittels dieser Abläufe von Operationen kann das BezugsBL-Potential: Vref von Vss auf das Zwischenpotential zwischen denen entsprechend "1" und "0" Daten angehoben werden. Als eine Folge wird das Bezugsbitleitungspotential zu einem Wert, der durch Teilen der Gesamtladung =  $(CD \times VDC' + CD \times VDC)$  durch die Lastkapazitanz  $(CD + CB)$  erhalten wird.

**[0074]** Im Falle von  $VDC=VDC'$ , wie in [Fig. 2](#) gezeigt, hat dies  $Vref' = (2CD \times VDC) / (CD + CB) = 2Vref = 2 \times (CD \times VDC) / (CD + CB)$  zur Folge, und es ist möglich, mit der gleichen paraelektrischen Kondensatorkapazitanz ein Bezugsbitleitungspotential zu erzeugen, das das Doppelte dessen im herkömmlichen Dummyzellsystem ist, d.h.  $Vref = (CD \times VDC) / (CD + CB)$ .

**[0075]** Vor diesem Hintergrund kann, während das herkömmliche System einen großen CD Wert erforderte, da  $Vref = 1/2VDC$ , wenn  $CD = CB$ , das erste Ausführungsbeispiel der Erfindung einen Dummykondensator mit einem Bereich von nur 1/3 des herkömmlichen Systems verwenden, da  $Vref = 1/2VDC$ , wenn  $CD = 1/3CB$ , und die Chipgröße kann signifikant reduziert werden.

**[0076]** Wenn beispielsweise  $CB = 500 \text{ fF}$  verwendet wird, erfordert das herkömmliche System eine Dummykondensatorkapazitanz von 500 fF, und ein MOS Kondensator mit einem 8 nm dicken Oxidfilm benötigt einen Kondensatorbereich in der Größe von  $112 \mu\text{m}^2$  für jede Dummyzelle. Dem gegenüber kann das erste Ausführungsbeispiel der Erfindung den Kondensatorbereich pro Dummyzelle auf  $37 \mu\text{m}^2$  mit der Kapazität von  $500 \text{ fF}/3 = 167 \text{ fF}$  signifikant reduzieren.

**[0077]** Zusätzlich ist zur Erzeugung eines Potentials, das größer als  $1/2VDC$  ist, im herkömmlichen System  $CB < CD$ . Daher wirkt CD selbst als Lastkapazitanz, und es ist möglich, ein Potential zu erzeugen. Das erste Ausführungsbeispiel der Erfindung kann jedoch das Potential in einer Größe von  $Vref = VDC = Vaa$  erzeugen, wenn  $CD = CB$ . Daher kann das Ausführungsbeispiel den ferroelektrischen Speicher realisieren, ohne einen ferroelektrischen Kondensator zu verwenden, der aufgrund von Fluktuationen, Deformationen und so weiter eine Betriebsreserve vermindert. Zur gleichen Zeit kann es einen ferroelektrischen Speicher mit einem kleinen Dummykondensatorbereich realisieren, ohne die Platte doppelt anzuheben und abzusenken. Daher ist ein Hochgeschwindigkeitsbetrieb möglich.

**[0078]** Das erste Ausführungsbeispiel der Erfindung, oben erläutert, ist dazu ausgebildet, den para-

elektrischen Kondensator mittels des Paares von Bitleitungen gemeinsam zu nutzen, und dadurch den Dummyzellenkondensatorbereich zu reduzieren. Der paraelektrische Kondensator kann ein Gatekondensator eines MOS Transistors sein. In diesem Fall ist ein Verarmungstytransistor vorzuziehen.

**[0079]** Die Dummywortleitungen DWL0, DWL1 können vor einem Abtastbetrieb auf NIEDRIG geändert werden, um die Dummyzelle und die Bezugsbitleitung abzutrennen, wie durch (2) im Zeitablaufdiagramm gezeigt. Es ist auch annehmbar, dieses nach dem Abtastbetrieb (1) durchzuführen. Danach wird das Knotenrücksetzsignal DRST auf HOCH geändert, und DPL wird auf NIEDRIG vermindert, nach einem Vorladen des Knotens N1 auf VDC, um zum gleichen Zustand wie im Bereitschaftsmodus zurückzukehren. Es ist vorzuziehen, DPL nach einem Ändern von DWLO auf HOCH anzuheben, und einen gewissen Anteil der gespeicherten Ladung zur VDC Spannung zur Bezugsbitleitung zu entladen. Für eine Einfachheit der Schaltung ist  $VDC = VDC'$  ebenso erwünscht. Andere Verfahren sind auch anwendbar, wie beispielsweise ein Verfahren zum Festlegen von  $VDC = Vaa$  und ein Verändern von nur  $VDC'$  hinsichtlich des Potentials, um das Bezugsbitleitungspotential zu erzeugen, ein Verfahren zum Festlegen von  $VDC = Vaa$  und ein Ändern von nur  $VDC$  hinsichtlich Potential, um das Bezugsbitleitungspotential zu erzeugen, und so weiter. Es ist weiter vorzuziehen, dass das Amplitudenpotential des DRST Signals nicht niedriger als  $VDC + Vt$  zum Schreiben von  $VDC$  bei N1 ist, d.h. das angehobene Potential  $Vpp$ . Das Potential von DWLO und DWL1 kann  $Vpp$  sein, oder kann die  $Vaa$  Amplitude sein, falls das Bezugsbitleitungspotential  $+Vt < Vaa$  ist.

**[0080]** Die [Fig. 4](#) bis [Fig. 7](#) sind Schaltdiagramme, die Konfigurationen von Ansteuerschaltungen jeweiliger Steuersignale zeigen, die in der Schaltung von [Fig. 1](#) verwendet werden.

**[0081]** Die in [Fig. 4](#) gezeigte Schaltung ist eine Schaltung zum Ansteuern der Dummyzellenquellenspannung  $VDC$  zum Vorladen des Knotens N1 und der Dummyplattenleitung DPL. Eine stabile Kapazität C3 ist mit Vss zwischen einem VDC Generator **10** und dem Knoten N1 angeschlossen. Ein PMOS Transistor Q11 und ein NMOS Transistor Q12 sind in Serie zwischen dem Knoten Nx und Vss angeschlossen. Am gemeinsamen Verbindungspunkt dieser Gates ist ein Inverter **11**, gesteuert durch das HOCH-seitige Potential Vss der Leitungsamplitude, angeschlossen, und der Verbindungspunkt beider Transistoren gibt der Dummyplattenleitung DPL ein Ansteuerpotential.

**[0082]** Dies ist eine Schaltung für den Fall von  $VDC = VDC'$ , oben diskutiert, und falls  $Vaa \geq VDC$ , kann die Ausgabe der  $Vaa$  Amplitude direkt an den

Treiber der VDC Quelle eingegeben werden.

**[0083]** [Fig. 5](#) ist ein Schaltdiagramm einer Konfiguration einer Schaltung zum Erzeugen eines Potentials der Dummywortleitung DWLO.

**[0084]** Diese Schaltung ist ein Beispiel einer Erzeugungsschaltung eines Ansteuerpotentials der Dummywortleitung DWLO, die einen PMOS Transistor Q13 und einen NMOS Transistor Q14 seriell zwischen dem HOCH-seitigen Potential Vaa der Bitleitungsspannung und Vss verbindet, und die mit dem gemeinsamen Verbindungspunkt der Gates einen Inverter 12 verbindet, gesteuert durch das HOCH-seitige Potential Vaa der Bitleitungsspannung, so dass der Verbindungspunkt beider Transistoren der Dummywortleitung DWLO ein Treiberpotential bereitstellt. In dieser Schaltung ist die Amplitude des DWLO Treiberpotentials Vss.

**[0085]** [Fig. 6](#) zeigt ein Schaltdiagramm eines Beispiels einer Treiberschaltung des Knotenrücksetzungssignals DRST.

**[0086]** In dieser Schaltung sind ein PMOS Transistor Q15 und ein NMOS Transistor Q16 seriell zwischen dem angehobenen Potential Vpp und Vss verbunden, und ein invertierter Ausgang des Signalpegelwandlers ist mit dem gemeinsamen Verbindungspunkt der Gates verbunden, sodass der Verbindungspunkt beider Transistoren das DRST Signal liefert. Die Signalamplitudenwandlerschaltung wird dazu verwendet, die Amplitude des DRST Signals auf Vpp zu erweitern.

**[0087]** [Fig. 7](#) zeigt ein Zeitablaufdiagramm eines Verhältnisses zwischen Signalen, die in den [Fig. 4](#) bis [Fig. 6](#) ausgegeben werden. Es ist offensichtlich, dass das Verhältnis genau das gleiche wie das in [Fig. 2](#) gezeigte ist.

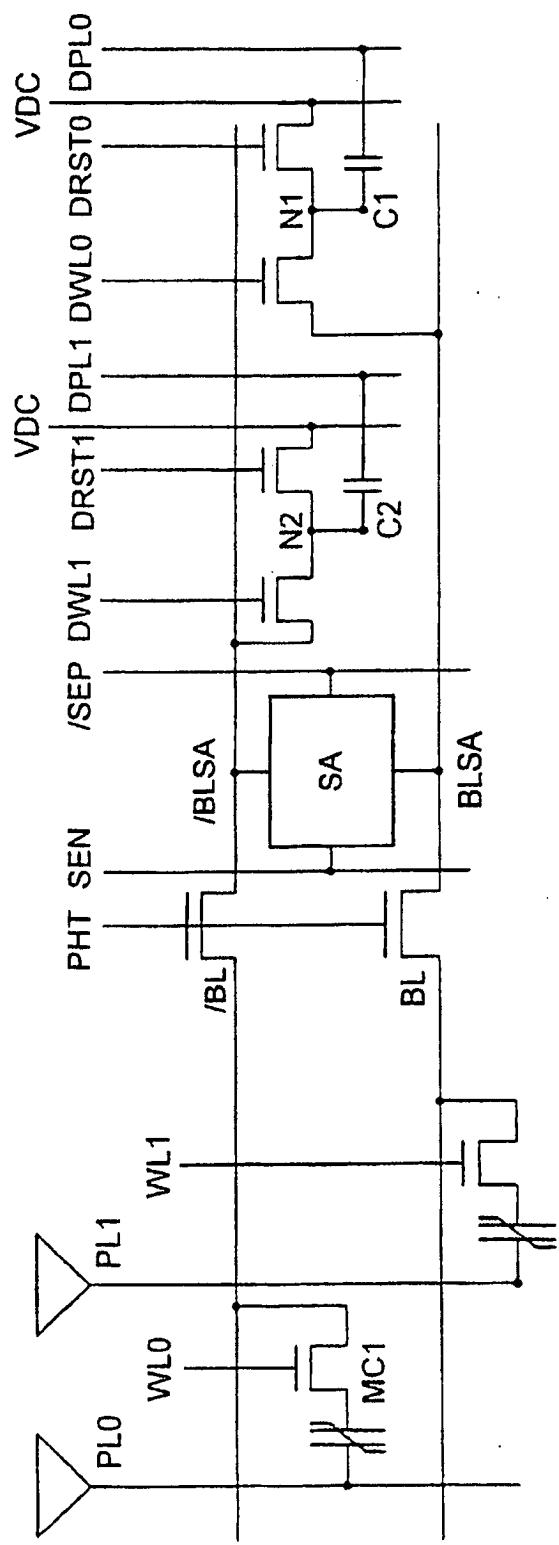

**[0088]** [Fig. 8](#) zeigt ein Schaltdiagramm einer Konfiguration eines Arrays, eines Abtastverstärkers und einer Dummyzellenschaltung eines ferroelektrischen Speichers gemäß dem zweiten Ausführungsbeispiel der Erfindung, und [Fig. 9](#) zeigt ein Zeitablaufdiagramm der Betriebsvorgänge.

**[0089]** Die in [Fig. 8](#) gezeigte Schaltung weist im wesentlichen die gleiche Schaltungskonfiguration wie in [Fig. 1](#) auf, unterscheidet sich jedoch darin, dass während der Transistor Q3 von [Fig. 1](#) zum Vorladen des N1 Knotens auf VDC ein NMOS ist, hier ein PMOS verwendet wird, und das entgegengerichtete Phasensignal/DRST in [Fig. 8](#) verwendet wird.

**[0090]** Wie in [Fig. 9](#) gezeigt, weist diese Schaltung im wesentlichen die gleichen Betriebsvorgänge wie die Schaltung von [Fig. 1](#) auf. Während jedoch die Schaltung von [Fig. 1](#) das DRST Signal auf Vaa anhe-

ben oder verstärken muss, falls  $VDC+Vt > Vaa$ , wenn der N1 Knoten auf VDC vorgeladen wird, kann die hier gezeigte Schaltung unter Verwendung eines PMOS auf VDC vorladen, durch ein Einstellen von /DRST auf Vss, falls  $VDC < Vaa$ , und es ist möglich, die Amplitude von /DRST auf Vaa zu begrenzen „, und man kann die Verstärkerschaltung entfernen.

**[0091]** Die [Fig. 10](#) und [Fig. 11](#) zeigen das dritte Ausführungsbeispiel der Erfindung, wobei [Fig. 10](#) das Schaltdiagramm ist und [Fig. 11](#) ein Zeitablaufdiagramm der Betriebsvorgänge.

**[0092]** Mit Bezug auf [Fig. 10](#) ist die Schaltungsanordnung im wesentlichen die gleiche wie von [Fig. 1](#), unterscheidet sich jedoch darin, dass die Dummyzellenschaltung für jede des Paares von Bitleitungen bereitgestellt ist.

**[0093]** Die erste Dummyzellenschaltung weist einen ersten paraelektrischen Kondensator C1 auf, und der erste Anschluss ist mit der Bitleitung BL über einen Transistor Q21 verbunden, der durch DWL0 gesteuert wird, und ist mit VDC über einen zweiten Transistor Q22 verbunden, der durch DRST0 gesteuert ist. Der zweite Anschluss des ersten paraelektrischen Kondensators C1 ist mit DPL0 verbunden. Auf ähnliche Weise weist die zweite Dummyzellenschaltung einen zweiten paraelektrischen Kondensator C2 auf, und dessen erster Anschluss ist mit der Bitleitung /BL über einen Transistor Q23 verbunden, der durch DWL1 gesteuert ist, und ist mit VDC über einen Transistor Q24 verbunden, der durch DRST1 gesteuert ist. Der zweite Anschluss des zweiten paraelektrischen Kondensators ist mit DPL1 verbunden.

**[0094]** Falls /BL die Bezugsbitleitung ist, kann DWL1, DRST1 und DPL1 aktiviert werden. Falls BL die Bezugsbitleitung ist, kann DWL0, DRST0 und DPL0 aktiviert werden.

**[0095]** Die [Fig. 12](#) und [Fig. 13](#) zeigen das vierte Ausführungsbeispiel der Erfindung, wobei [Fig. 12](#) das Schaltdiagramm ist, das eine Konfiguration des Arrays, des Abtastverstärkers und der Dummyzellenschaltung des vierten Ausführungsbeispiels der Erfindung zeigt, und wobei [Fig. 13](#) ein Zeitablaufdiagramm der Betriebsvorgänge zeigt.

**[0096]** Mit Bezug auf [Fig. 12](#) betrifft das vorliegende Ausführungsbeispiel eine Dummyzelle in einem ferroelektrischen Speicher herkömmlichen Typs. Eine einzelne Speicherzelle ist vom 1T1C Typ, bestehend aus einem Zellentransistor und einem ferroelektrischen Kondensator.

**[0097]** Ein Verhalten dieser Schaltung wird unterhalb kurz erläutert. Im Bereitschaftsmodus sind alle (Sub)Wortleitungen WL0 bis WL1 auf NIEDRIG eingestellt, Plattenleitungen PL0 und PL1 sind ebenso

auf NIEDRIG eingestellt, und die Bitleitungen sind ebenso auf Vss vorgeladen.

**[0098]** In einem Aktivmodus wird das auf Vss vorgeladene Paar von Bitleitungen in den schwebenden Zustand geändert. Dann wird nur der Speicherzellentransistor, der parallel zum paraelektrischen Kondensator angeschlossen ist, der auszulesen ist, AN geschaltet. Zum Beispiel wird, falls der ferroelektrische Speicherzellenkondensator MC1 in [Fig. 12](#) ausgelesen ist, WL0 auf HOCH eingestellt. Danach wird, wenn die Plattenleitung PL0 im Abschnitt von MC1 auf HOCH eingestellt ist, eine Potentialdifferenz zwischen PL0 und /BL an gegenüberliegenden Enden des ferroelektrischen Kondensators MC1 angelegt, und eine Polarisationsinformation des ferroelektrischen Kondensators wird auf die Bitleitung /BL (/BLSA) ausgelesen, die schwebend gehalten wird. Daher kann, auch wenn die Zellen in Serie verbunden sind, Zelleninformation eines beliebigen erwünschten ferroelektrischen Kondensators ausgelesen werden, indem eine erwünschte (Sub)Wortleitung ausgewählt wird, und ein vollständig beliebiger Zugriff wird realisiert.

**[0099]** Wenn die Daten "1" sind, tritt eine Polarisationsumkehrung im ferroelektrischen Kondensator auf, und die Bitleitung wird auf ein hohes Potential (BLh) angehoben. Wenn die Daten "0" sind, tritt keine Polarisationsumkehr auf, jedoch wird die Bitleitung (BL1) genauso weit wie die paraelektrische Komponente des ferroelektrischen Kondensators und das Kapazitanzverhältnis der Bitleitungskapazitanz angehoben. Auf diese Weise besteht, obwohl das Bitleitungspotential sich von Vss für sowohl Daten "1" als auch "0" anhebt, eine Differenz zwischen diesen Potentialen. Wenn daher die Bezugsbitleitung BL (BLSR) auf ein Zwischenpotential zwischen diesen Potentialen eingestellt werden kann, ist es möglich, festzustellen, ob die Zellendaten "1" oder "0" sind, indem die Differenz zwischen der Bitleitung und der Bezugsbitleitung mit dem Abtastverstärker verstärkt wird.

**[0100]** Die Dummyzellenschaltung, die das Bezugsbitleitungspotential erzeugt, weist die in [Fig. 12](#) gezeigte Schaltungsanordnung auf.

**[0101]** In einem Bereitschaftsmodus sind die Transistoren Q1, Q2 der Dummywortleitungen AUS geschaltet, und ein Ende N1 des paraelektrischen Kondensators C1 ist auf das Qellenpotential von Q3 vorgeladen, d.h.  $VDC (>Vss)$  Potential, in dem der Transistor Q3 AN gehalten wird. Die Dummyplattenleitung DOL am anderen Ende des paraelektrischen Kondensators wird auf Vss Potential gehalten. Das heißt, die Spannung  $VDC$  wird an gegenüberliegende Enden des paraelektrischen Kondensators angelegt, dass dieser die Ladung  $CD \times VDC$  erhält.

**[0102]** In einem Aktivmodus wird ein Transistor ei-

ner Dummywortleitung, der mit der Bezugsleitung verbunden ist, welches in diesem Beispiel der Transistor Q1 ist, AN geschaltet, um BL und N1 zu verbinden. Als eine Folge wird die in dem paraelektrischen Kondensator gespeicherte Ladung auf die Bezagsbitleitung entladen. Danach wird das Potential der Dummyplattenleitung DPL, welches das andere Ende des C1 ist, von Vss auf das  $VDC'$  Potential angehoben. Mittels dieser Betriebsvorgänge wird ein Wert entsprechend der Ladung von  $CD \times VDC'$  erzeugt, indem der paraelektrische Kondensator C1 gekoppelt wird, und die Ladung wird durch die Bezagsbitleitung und den paraelektrischen Kondensator geteilt. Durch diesen Ablauf von Betriebsvorgängen kann das Bezugs-BL-Potential:  $Vref$  von Vss auf das Zwischenpotential zwischen denen entsprechend "1" und "0" Daten angehoben werden. Als eine Folge wird das Bezugsbitleitungspotential zu einem Wert, der durch ein Teilen der Gesamtladung  $= (DC \times VDC' + CD \times VDC)$  durch die Lastkapazitanz  $(CD + CB)$  erhalten wird.

**[0103]** Falls  $VDC = VDC'$ , wie in [Fig. 3](#) gezeigt, resultiert dies in  $Vref = (2CD \times VDC) / (CD + CB) = 2Vref = 2 \times (CD \times VDC) / (CD + CB)$ , und es ist möglich, ein Bezugsbitleitungspotential zu erzeugen, das das Doppelte des herkömmlichen Dummyzellsystems ist, d.h.  $Vref = (CD \times VDC) / (CD + CB)$ , mit der gleichen paraelektrischen Kondensatorkapazitanz.

**[0104]** Vom entgegengesetzten Standpunkt aus gesehen, kann, während das herkömmliche System einen großen CD Wert erforderte, da  $Vref = 1/2VDC$ , wenn  $DC = CB$ , in Übereinstimmung mit dem vierten Ausführungsbeispiel der vorliegenden Erfindung ein Dummykondensator mit einem Bereich von nur 1/3 des herkömmlichen Systems verwendet werden, da  $Vref = 1/2VDC$ , wenn  $CD = 1/3CB$ , und die Chipgröße kann signifikant reduziert werden. Wenn beispielsweise  $CB = 1000 \text{ fF}$ , erforderte das herkömmliche System eine Dummykondensatorkapazitanz von  $1000 \text{ fF}$ , und ein MOS Kondensator mit einem 8 nm dicken Oxidfilm benötigt einen Kondensatorbereich im Größenbereich von  $225 \mu\text{m}^2$  pro Dummyzelle. Dem gegenüber kann das erste Ausführungsbeispiel der Erfindung den Kondensatorbereich pro Dummyzelle auf  $75 \mu\text{m}^2$  mit der Kapazität von  $1000 \text{ fF} / 3 = 333 \text{ fF}$  signifikant reduzieren.

**[0105]** Zusätzlich ist zur Erzeugung eines Potentials, das größer als  $1/2VDC$  ist, im herkömmlichen System  $CB < CD$ . Daher wirkt CD selbst als eine Lastkapazitanz, und es ist möglich, ein Potential zu erzeugen. In Übereinstimmung mit dem vierten Ausführungsbeispiel der Erfindung kann jedoch das Potential in der Größe von  $Vref = VDC = Vaa$  erzeugt werden, wenn  $CD = CB$ . Dieses System ermöglicht eine Realisierung eines ferroelektrischen Speichers ohne Verwendung eines ferroelektrischen Kondensators, der sich in einer Betriebsreserve aufgrund von Fluktuationen, Deformationen und so weiter vermindert.

Es ist weiter möglich, einen ferroelektrischen Speicher mit einem kleinen Dummykondensatorbereich ohne ein doppeltes Anheben und Vermindern der Platte zu realisieren. Daher ist ein Hochgeschwindigkeitsbetrieb möglich.

**[0106]** Das vierte Ausführungsbeispiel der vorliegenden Erfindung ist dazu ausgebildet, den paraelektrischen Kondensator mit dem Paar von Bitleitungen gemeinsam zu nutzen, unter Verwendung der Transistoren Q1 und Q2, und um dadurch den Dummyzellenkondensatorbereich zu vermindern. Der paraelektrische Kondensator kann ein Gatekondensator eines MOS Transistors sein. Ein Verarmungstyptransistor ist vorzuziehen. Die Dummywortleitungen DWLO, DWL1 können vor einem Abtastbetrieb auf NIEDRIG geändert werden, um die Dummyzelle und die Bezugsbitleitung abzutrennen, wie durch (2) im Zeitablaufdiagramm von [Fig. 13](#) gezeigt. Es ist weiter annehmbar, dieses nach einem Abtastbetrieb (1) durchzuführen. Danach wird das DRST Signal auf HOCH geändert, und DPL wird nach einem Vorladen des Knotens N1 auf VDC auf NIEDRIG vermindert, um zum gleichen Zustand wie im Bereitschaftsmodus zurückzukehren. Es ist vorzuziehen, DPL nach einem Ändern von DWLO auf HOCH anzuheben, und einen gewissen Anteil der gespeicherten Ladung zur VDC Spannung zur Bezugsbitleitung zu entladen. Für eine Einfachheit der Schaltung ist weiter  $VDC=VDC'$  erwünscht. Andere Verfahren sind ebenso anwendbar, wie beispielsweise ein Verfahren zum Festlegen von  $VDC=Vaa$  und zum Ändern von nur  $VDC'$  hinsichtlich des Potentials zur Erzeugung des Bezugsbitleitungspotentials, ein Verfahren zum Festlegen von  $VDC'=Vaa$  und Ändern von nur  $VDC$  hinsichtlich des Potentials, zur Erzeugung des Bezugsbitleitungspotentials, und so weiter. Es ist weiter vorzuziehen, dass das Amplitudenpotential des DRST Signals nicht niedriger als  $VDC+Vt$  ist, zum Schreiben von VDC bei N1, d.h. das angehobene Potential Vpp. Das Potential von DWL0 und DWL1 kann Vpp sein, oder kann die Vaa Amplitude sein, falls das Bezugsbitleitungspotential  $+Vt < Vaa$  ist.

**[0107]** Es ist nicht notwendig zu erwähnen, dass die in den [Fig. 4](#) bis [Fig. 6](#) gezeigten Treiberschaltungen ebenso auf das System von [Fig. 12](#) anwendbar sind.

**[0108]** [Fig. 14](#) zeigt ein Schaltdiagramm des fünften Ausführungsbeispiels der Erfindung, und [Fig. 15](#) zeigt ein Zeitablaufdiagramm dessen Verhaltens. Diese Schaltung weist im wesentlichen die gleiche Schaltungskonfiguration wie [Fig. 12](#) auf, unterscheidet sich jedoch darin, dass, während der Transistor Q3 von [Fig. 12](#) zum Vorladen des N1 Knotens auf VDC ein NMOS ist, die Schaltung von [Fig. 16](#) einen PMOS und das entgegengerichtete Phasensignal/DRST verwendet.

**[0109]** Für das Vorladen des N1 Knotens auf VDC

muss die Schaltung von [Fig. 12](#) das DRST Signal auf über Vaa anheben oder verstärken, falls  $VDC+Vt > Vaa$ . Die hier gezeigte Schaltung, die einen PMOS Verwendet, kann jedoch auf VDC vorladen durch ein Einstellen von /DRST auf Vss, falls  $VDC < Vaa$ , und es ist möglich, die Amplitude von /DRST auf Vaa zu vermindern, und die Verstärkerschaltung zu entfernen.

**[0110]** [Fig. 16](#) zeigt ein Schaltdiagramm des sechsten Ausführungsbeispiels der Erfindung, und [Fig. 17](#) zeigt ein Zeitablaufdiagramm des Verhaltens.

**[0111]** Die in [Fig. 16](#) gezeigte Schaltung weist im wesentlichen die gleiche Schaltungskonfiguration wie [Fig. 12](#) auf, unterscheidet sich jedoch darin, dass die Dummyzellenschaltung für jede des Paares von zwei Bitleitungen bereitgestellt ist. Falls /BL die Bezugsbitleitung ist, können DWL, DRST1 und DPL aktiviert werden. Falls BL die Bezugsbitleitung ist können DWL0, DRST0 und DPL0 aktiviert werden.

**[0112]** Wie oben erläutert, da die Erfindung das an den Anschluss des paraelektrischen Kondensators der Dummyzelle angelegte Potential auf einen optimalen Wert in sowohl einem Bereitschaftsmodus als auch einem Aktivmodus steuert, kann ein ferroelektrischer Speicher realisiert werden, der keinen ferroelektrischen Kondensator benötigt, der großen Fluktuationen unterliegt und eine Verminderung einer Betriebsreserve aufgrund von beispielsweise einer Deformation neigt, und es kann ein ferroelektrischer Speicher mit einem kleinen Dummyzellenbereich ohne Notwendigkeit eines Anhebens und Verminderns des Plattenpotentials auf komplizierte Weise realisiert werden.

**[0113]** Daher wird ein Hochgeschwindigkeitsbetrieb ermöglicht.

## Patentansprüche

1. Eine HalbleiterSpeichervorrichtung, umfassend:

eine Vielzahl von Speicherzellen mit einer seriellen Verbindung von Zellentransistoren und ferroelektrischen Kondensatoren;

eine Vielzahl von Wortleitungen, (WL bis WL3), die mit den Zellentransistoren verbunden sind;

eine Vielzahl von Bitleitungspaaren, die mit den Speicherzellen verbunden sind;

eine Vielzahl von Verstärkerschaltungen, die mit den Bitleitungspaaren verbunden sind, um eine Signaldifferenz zwischen Bitleitungen (BL) in jedem Bitleitungspaar zu verstärken; und

eine Dummy-Zellenschaltung zur Erzeugung eines Potentials für eine Bitleitung eines der Bitleitungspaare, welche eine Bezugsbitleitung ist, an die für die Speicherzellen keine Daten ausgelesen werden, wobei die Dummy-Zellenschaltung mindestens einen

paraelektrischen Kondensator (C1) umfasst; wobei in einem Bereitschaftsmodus ein erster Anschluss des paraelektrischen Kondensators (C1) auf ein erstes Potential vorgeladen ist, das höher als Massepotential ist, und wobei ein zweiter Anschluss des paraelektrischen Kondensators (C1) auf Massepotential vorgeladen ist; und in einem Aktivmodus der erste Anschluss mit der Bezugsbitleitung verbunden ist und der zweite Anschluss vom Massepotential auf ein zweites Potential erhöht wird, das höher als Massepotential ist.

2. Die Halbleiterspeichervorrichtung nach Anspruch 1, wobei der erste Anschluss mit einer von Bitleitungen (BL) in jedem Bitleitungspaar über einen ersten Transistor verbunden ist, mit der anderen von Bitleitungen (BL) in jedem Bitleitungspaar über einen zweiten Transistor verbunden ist, und mit dem ersten Potential über einen dritten Transistor verbunden ist.

3. Die Halbleiterspeichervorrichtung nach Anspruch 2, wobei der dritte Transistor in entgegengesetzter Phase zu der des ersten und zweiten Transistors arbeitet.

4. Die Halbleiterspeichervorrichtung nach Anspruch 1, wobei der erste Anschluss mit einer von Bitleitungen (BL) eines jeden Bitleitungspaares über einen ersten Transistor verbunden ist, und mit dem ersten Potential über einen dritten Transistor verbunden ist.

5. Die Halbleiterspeichervorrichtung nach Anspruch 4, wobei der dritte Transistor in der entgegengerichteten Phase von der des ersten Transistors arbeitet.

6. Die Halbleiterspeichervorrichtung nach Anspruch 1, wobei das erste Potential und das zweite Potential gleich sind.

7. Die Halbleiterspeichervorrichtung nach Anspruch 1, wobei der zweite Anschluss vom Massepotential auf ein zweites Potential angehoben ist, das höher als das Massepotential ist, nachdem der erste Anschluss mit der Bezugsbitleitung verbunden ist.

8. Die Halbleiterspeichervorrichtung nach Anspruch 1, wobei die Dummy-Zellenschaltung einen ersten Dummy-Zellenabschnitt umfasst, mit einem ersten paraelektrischen Kondensator (C1), um ein erstes Potential einer ersten Bitleitung (BL) des Bitleitungspaares zu erzeugen und einem zweiten Dummy-Zellenabschnitt, mit einem zweiten paraelektrischen Kondensator (C1), um ein zweites Potential einer zweiten Bitleitung (BL) des Bitleitungspaares zu erzeugen, und wobei ein erster Anschluss des ersten paraelektrischen Kondensators (C1) mit der ersten Bitleitung (BL) über einen ersten Transistor verbunden ist, und

mit einer ersten Dummy-Zellen-Energieversorgung über einen zweiten Transistor, und wobei ein zweiter Anschluss des ersten paraelektrischen Kondensators (C1) mit einer ersten Dummy-Plattenleitung verbunden ist, und ein erster Anschluss des zweiten paraelektrischen Kondensators (C1) mit der zweiten Bitleitung (BL) über einen dritten Transistor und mit einem zweiten Dummy-Zellen-Energieversorgungspotential über einen vierten Transistor verbunden ist, und ein zweiter Anschluss des zweiten paraelektrischen Kondensators (C1) mit einer zweiten Dummy-Plattenleitung verbunden ist, wobei das erste und zweite Dummy-Zellenenergiopotential höher als das Massepotential ist.

9. Die Halbleiterspeichervorrichtung nach Anspruch 8, wobei dann, wenn die erste Bitleitung (BL) die Bezugsbitleitung ist, der erste und zweite Transistor gesteuert werden, und falls die zweite Bitleitung (BL) die Bezugsbitleitung ist, der dritte und vierte gesteuert werden.

10. Die Halbleiterspeichervorrichtung nach Anspruch 9, wobei in einem Bereitschaftsmodus ein erster Anschluss des ersten und zweiten paraelektrischen Kondensators (C1) auf ein erstes Potential vorgeladen ist, das höher als ein Massepotential ist, und ein zweiter Anschluss des ausgewählten paraelektrischen Kondensators (C1) auf Massepotential vorgeladen ist; und in einem Aktivmodus der erste Anschluss des ausgewählten paraelektrischen Kondensators (C1) mit der Bezugsbitleitung verbunden ist, und der zweite Anschluss des ausgewählten paraelektrischen Kondensators (C1) vom Massepotential auf ein zweites Potential angehoben ist, das höher als Massepotential ist.

11. Die Halbleiterspeichervorrichtung nach einem der Ansprüche 1 bis 10, wobei die Vielzahl von Speicherzellen eine Vielzahl von Speicherzellenblöcken bilden, jeweils mit einer seriellen Verbindung mindestens einer Vielzahl von Speicherzellen, die jeweils einen Zellentransistor und einen ferroelektrischen Kondensator umfassen, die parallel zwischen Source- und Drainanschlüssen der Zellentransistoren angelassen sind.

12. Die Halbleiterspeichervorrichtung nach Anspruch 1, wobei der erste Anschluss mit einer von Bitleitungen (BL) in einem jeden Bitleitungspaar über einen ersten Transistor verbunden ist, mit der anderen der Bitleitungen (BL) in jedem Bitleitungspaar über einen zweiten Transistor verbunden ist, und mit dem ersten Potential über einen dritten Transistor verbunden ist.

Es folgen 19 Blatt Zeichnungen

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 15

FIG. 16

FIG. 17

FIG. 18

FIG. 19

FIG. 20

FIG. 21

FIG. 22