(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6220597号

(P6220597)

(45) 発行日 平成29年10月25日(2017.10.25)

(24) 登録日 平成29年10月6日(2017.10.6)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 29/786  | (2006.01) | HO1L 29/78 | 618E |

| HO1L 21/336  | (2006.01) | HO1L 29/78 | 618B |

| HO1L 21/8242 | (2006.01) | HO1L 29/78 | 626C |

| HO1L 27/108  | (2006.01) | HO1L 29/78 | 617U |

| HO1L 27/10   | (2006.01) | HO1L 29/78 | 617T |

請求項の数 3 (全 34 頁) 最終頁に続く

(21) 出願番号

特願2013-161530 (P2013-161530)

(22) 出願日

平成25年8月2日(2013.8.2)

(65) 公開番号

特開2014-57052 (P2014-57052A)

(43) 公開日

平成26年3月27日(2014.3.27)

審査請求日

平成28年7月27日(2016.7.27)

(31) 優先権主張番号

特願2012-178641 (P2012-178641)

(32) 優先日

平成24年8月10日(2012.8.10)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 市川 武宜

最終頁に続く

(54) 【発明の名称】半導体装置

(57) 【特許請求の範囲】

## 【請求項1】

半導体基板上方の第1の酸化物絶縁層と、

前記第1の酸化物絶縁層上方の金属酸化物層と、

前記金属酸化物層上方の第2の酸化物絶縁層と、

前記第2の酸化物絶縁層を介して前記金属酸化物層と重なるゲート電極層と、を有し、

前記金属酸化物層は、第1乃至第3の金属酸化物層が順に積層された構造を有し、

前記第1乃至前記第3の金属酸化物層は少なくともインジウムを含み、

前記第2の金属酸化物層は、前記第1及び前記第3の金属酸化物層よりもインジウムの含有率が多く、

前記第2の金属酸化物層は結晶構造を有することを特徴とする半導体装置。

## 【請求項2】

半導体基板上方の第1の窒化物絶縁層と、

前記第1の窒化物絶縁層上方の第1の酸化物絶縁層と、

前記第1の酸化物絶縁層上方の金属酸化物層と、

前記金属酸化物層上方の第2の酸化物絶縁層と、

前記第2の酸化物絶縁層上方の第2の窒化物絶縁層と、

前記第2の酸化物絶縁層及び前記第2の窒化物絶縁層を介して前記金属酸化物層と重なるゲート電極層と、を有し、

前記金属酸化物層は、第1乃至第3の金属酸化物層が順に積層された構造を有し、

10

20

前記第1乃至前記第3の金属酸化物層は少なくともインジウムを含み、前記第2の金属酸化物層は、前記第1及び前記第3の金属酸化物層よりもインジウムの含有率が多く、

前記第2の金属酸化物層は結晶構造を有することを特徴とする半導体装置。

【請求項3】

請求項1または請求項2において、

前記金属酸化物層は、局在準位による吸収係数が $3 \times 10^{-3} / \text{cm}$ 以下であること特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

10

【0001】

本発明は半導体装置及び半導体装置の作製方法に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路及び電気機器は全て半導体装置である。

【背景技術】

【0003】

絶縁表面を有する基板上に形成された半導体薄膜を用いてトランジスタ（薄膜トランジスタともいう）を構成する技術が注目されている。該トランジスタは集積回路（IC）や画像表示装置（表示装置）のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体薄膜としてシリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

20

【0004】

例えば、In（インジウム）、Ga（ガリウム）、Zn（亜鉛）を含む酸化物半導体を用いたトランジスタが特許文献1に開示されている。

【0005】

また、酸化物半導体膜はスパッタリング法などの薄膜形成技術によって成膜することが可能であり、シリコン半導体等と比べて、比較的低温での形成が可能であるため、他のトランジスタ上に重畠して形成することが可能である。例えば、特許文献2には、シリコンを用いたトランジスタ上に酸化物半導体層をチャネル形成領域とするトランジスタを重畠して設けることによって、セル面積が縮小された半導体装置が開示されている。

30

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2006-165528号公報

【特許文献2】特開2012-15500号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

酸化物半導体層をチャネル形成領域に用いたトランジスタは、酸化物半導体層から酸素が脱離することによって生じる酸素欠損（酸素欠陥）によってキャリアが発生する。また、酸化物半導体層に水素等の不純物が入り込むことによって、キャリアが発生する。

40

【0008】

酸化物半導体層にキャリアが生じることによって、トランジスタのオフ電流の増大、閾値電圧のばらつきの増大が起こり、トランジスタの電気特性が変動するため、半導体装置の信頼性が低下する。

【0009】

このような問題に鑑み、本発明の一態様は、信頼性が高く、安定した電気特性を示す半導体装置を提供することを目的のーとする。また、信頼性の高い半導体装置を作製することを目的のーとする。

50

## 【課題を解決するための手段】

## 【0010】

本発明の一態様の半導体装置は、第1の酸化物半導体層、第2の酸化物半導体層、及び第3の酸化物半導体層が積層された酸化物半導体積層と、酸化物半導体積層を挟む第1の酸化物絶縁層及び第2の酸化物絶縁層とを有し、第1の酸化物半導体層乃至第3の酸化物半導体層は少なくともインジウムを含み、第2の酸化物半導体層は第1の酸化物半導体層及び第3の酸化物半導体層よりもインジウムの含有率が多く、第1の酸化物半導体層及び第3の酸化物半導体層は非晶質であり、第2の酸化物半導体層は結晶構造を有する。

## 【0011】

第2の酸化物半導体層は、第1の酸化物半導体層及び第3の酸化物半導体層よりもインジウムの割合が大きいため、キャリアの移動度が高く、第2の酸化物半導体層がキャリアパスとなる。したがって、酸化物半導体積層の下方または上方に配置される酸化物絶縁層から離間された領域においてキャリアが流れるため、酸化物絶縁層から混入する不純物等の影響を低減することができる。

## 【0012】

酸化物半導体積層は、第2の酸化物半導体層の伝導帯（コンダクションバンドとも呼ぶ）下端が最も低いエネルギー準位である井戸型構造（ウェル構造とも呼ぶ）を構成するように適宜材料を選択する。具体的には、第1の酸化物半導体層の伝導帯下端及び第3の酸化物半導体層の伝導帯下端に比べて第2の酸化物半導体層の伝導帯下端が真空準位から最も深くなるような材料を選択すればよい。

## 【0013】

また、第14族元素の一つであるシリコンや炭素が不純物として酸化物半導体層に含まれてしまうとドナーを作りn型化することがあるため、酸化物半導体層に含まれるシリコンの濃度は $3 \times 10^{18}$  atoms/cm<sup>3</sup>以下、好ましくは $3 \times 10^{17}$  atoms/cm<sup>3</sup>以下とする。また、炭素の濃度は、 $3 \times 10^{18}$  atoms/cm<sup>3</sup>以下、好ましくは $3 \times 10^{17}$  atoms/cm<sup>3</sup>以下とする。特に第2の酸化物半導体層に第14族元素が多く混入しないように、第1の酸化物半導体層及び第3の酸化物半導体層で、キャリアパスとなる第2の酸化物半導体層を挟む、または囲む構成とすることが好ましい。即ち、第1の酸化物半導体層及び第3の酸化物半導体層は、シリコンなどの第14族元素が第2の酸化物半導体層に混入することを防ぐバリア層とも呼べる。

## 【0014】

また、水素や水分が不純物として酸化物半導体積層に含まれてしまうとドナーを作りn型化することがあるため、酸化物半導体積層に水素や水分が外部から混入することを防止する保護膜（窒化シリコン膜など）を、酸化物半導体層の上方または下方に設けることは、井戸型構造を実現する上で有用である。

## 【0015】

酸化物半導体層を上記積層構成とすることにより、チャネルが形成される領域は、一定電流測定法（CPM: Constant Photocurrent Method）により測定された局在準位による吸収係数を $3 \times 10^{-3}$ /cm以下（状態密度に換算すると $3 \times 10^{13}$ /cm<sup>3</sup>以下）とすることができる。

## 【0016】

したがって、本発明の一態様の半導体装置は、半導体基板上に形成された第1酸化物絶縁層と、第1の酸化物絶縁層上の第1の酸化物半導体層、第2の酸化物半導体層、及び第3の酸化物半導体層が積層された酸化物半導体積層と、酸化物半導体積層上の第2の酸化物絶縁層と、第2の酸化物絶縁層を介して酸化物半導体積層と重畠する第1のゲート電極層とを有し、第1の酸化物半導体層、第2の酸化物半導体層及び第3の酸化物半導体層は少なくともインジウムを含み、第2の酸化物半導体層は、第1の酸化物半導体層及び第3の酸化物半導体層よりもインジウムの含有率が多く、第2の酸化物半導体層は結晶構造を有し、第1の酸化物半導体層及び第3の酸化物半導体層は非晶質である半導体装置である。

## 【0017】

10

20

30

40

50

上記構造に加えて、第1の酸化物絶縁層の下方に第1の窒化物絶縁層と、第2の酸化物絶縁層の上方に第2の窒化物絶縁層を有していてもよい。第1及び第2の窒化物絶縁層は酸化物半導体積層に水素や水分等が混入することを防止する。

【0018】

第1の酸化物絶縁層及び第2の酸化物絶縁層は化学量論的組成よりも過剰な酸素を含むとよい。化学量論的組成よりも過剰に酸素を含むことで、酸化物半導体積層に酸素を供給し、酸素欠損を補填することができる。

【0019】

第1の酸化物半導体層及び第3の酸化物半導体層は、少なくともインジウムの濃度が $1 \times 10^{19}$  atoms/cm<sup>3</sup>以上であるとよい。また、酸化物半導体積層は、局在準位による吸収係数が $3 \times 10^{-3}$ /cm以下であるとよい。

10

【0020】

例えば、第1の酸化物半導体層、第2の酸化物半導体層及び第3の酸化物半導体層は、インジウム、亜鉛及びガリウムを含む酸化物とする。第1の酸化物半導体層、第2の酸化物半導体層及び第3の酸化物半導体層が同一の元素からなると、各酸化物半導体層間における界面散乱を低減することができる。

【0021】

半導体装置は第1の酸化物絶縁層を介して、酸化物半導体積層と重畳する第2のゲート電極層を有していてもよい。

20

【0022】

第2の酸化物半導体層は、表面と略垂直な方向にc軸が配向した結晶を有しているとよい。

【0023】

また、第1の酸化物半導体層及び第3の酸化物半導体層に含まれるシリコンの濃度は $3 \times 10^{18}$  atoms/cm<sup>3</sup>以下であり、第1の酸化物半導体層及び第3の酸化物半導体層に含まれる炭素の濃度は $3 \times 10^{18}$  atoms/cm<sup>3</sup>以下であるとよい。

【0024】

また、本発明の別の一態様は、半導体基板上に第1の酸化物絶縁層を形成し、第1の酸化物絶縁層上に非晶質の第1の酸化物半導体層及び結晶構造を有する第2の酸化物半導体層を形成し、酸素及び窒素雰囲気下で第1の加熱処理を行い、第2の酸化物半導体層上に非晶質である第3の酸化物半導体層を形成し、第3の酸化物半導体層上に第2の酸化物絶縁層を形成し、酸素及び窒素雰囲気下で第2の加熱処理を行う半導体装置の作製方法である。また、半導体基板にはトランジスタが設けられていてもよい。

30

【発明の効果】

【0025】

本発明の一態様によって、信頼性が高く、安定した電気特性を示す酸化物半導体を用いた半導体装置を提供することができる。信頼性の高い半導体装置を作製できる。

【図面の簡単な説明】

【0026】

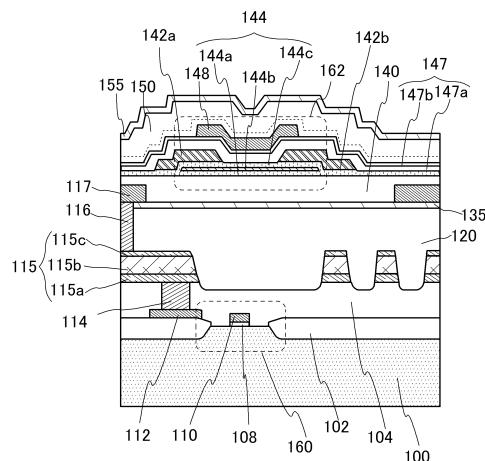

【図1】本発明の一態様の半導体装置の断面図。

40

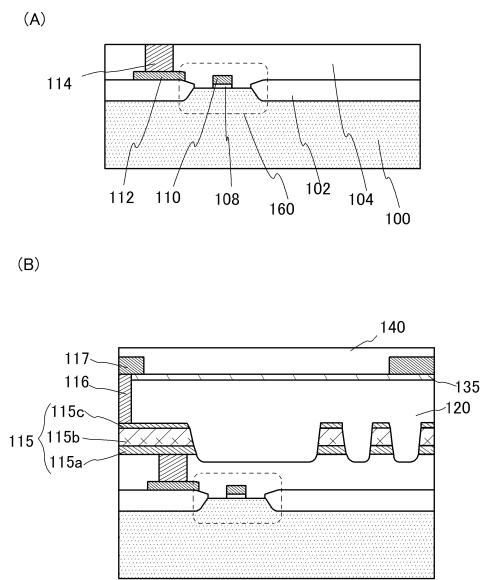

【図2】本発明の一態様の半導体装置の作製方法を説明する図。

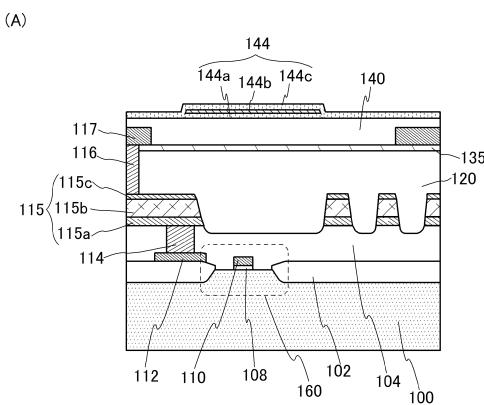

【図3】本発明の一態様の半導体装置の作製方法を説明する図。

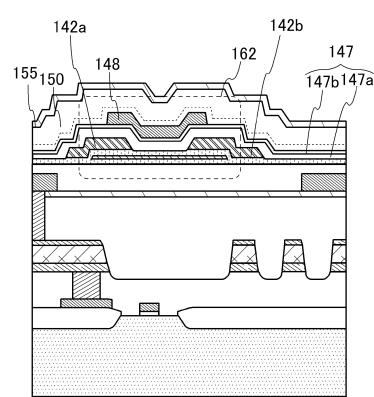

【図4】本発明の一態様の半導体装置の断面図。

【図5】本発明の一態様の半導体装置の断面図。

【図6】本発明の一態様の半導体装置の回路図。

【図7】本発明の一態様の半導体装置の回路図及び概念図。

【図8】本発明の一態様の半導体装置のブロック図。

【図9】本発明の一態様の半導体装置のブロック図。

【図10】本発明の一態様の半導体装置のブロック図。

【図11】本発明の一態様の半導体装置を適用することができる電子機器。

50

【図12】本発明の一態様の半導体装置が有する酸化物半導体積層のバンド図。

【図13】半導体装置の製造装置の一例を示す上面図。

【図14】酸化物半導体積層の真空準位から伝導帯下端までのエネルギー及びバンド図。

【発明を実施するための形態】

【0027】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態及び詳細を様々に変更しうることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0028】

10

以下に説明する実施の形態において、同じものを指す符号は異なる図面間で共通して用いる場合がある。なお、図面において示す構成要素、すなわち層や領域等の厚さ、幅、相対的な位置関係等は、実施の形態において説明する上で明確性のため、誇張して示される場合がある。

【0029】

なお、本明細書等において「上」という用語は、構成要素の位置関係が「直上」であることを限定するものではない。例えば、「絶縁層上のゲート電極層」の表現であれば、絶縁層とゲート電極層との間に他の構成要素を含むものを除外しない。「下」についても同様である。

【0030】

20

また、本明細書等において「電極層」や「配線層」という用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極層」は「配線層」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極層」や「配線層」という用語は、複数の「電極層」や「配線層」が一体となって形成されている場合なども含む。

【0031】

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」という用語は、入れ替えて用いることができるものとする。

【0032】

30

なお、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。

【0033】

例えば、「何らかの電気的作用を有するもの」には、電極や配線などが含まれる。

【0034】

(実施の形態1)

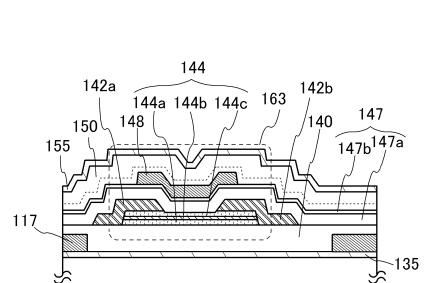

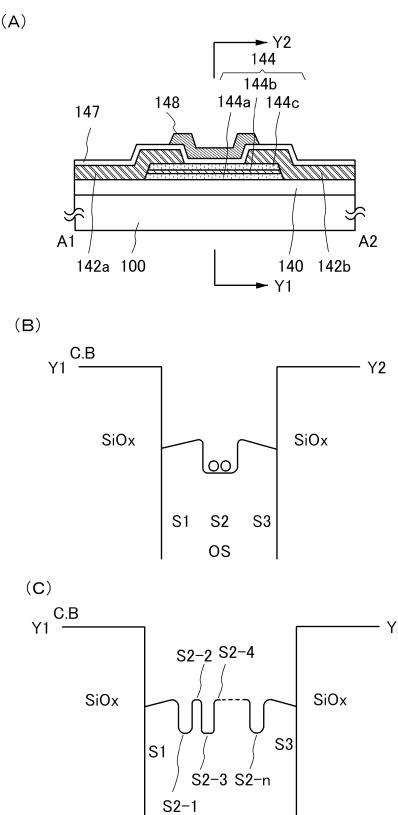

本実施の形態では、本発明の一態様の半導体装置について、図面を用いて詳細に説明する。図1に本発明の一態様の半導体装置を示す。

【0035】

40

半導体装置は、基板100上に第1の半導体材料を用いたトランジスタ160と、トランジスタ160上に形成された第2の半導体材料を用いたトランジスタ162と、を有する。

【0036】

ここで、トランジスタ160とトランジスタ162に用いる半導体材料は異なる禁制帯幅を持つ材料とすることが好ましい。例えば第1の半導体材料にシリコン系半導体（単結晶シリコン、多結晶シリコン等）を用い、第2の半導体材料に酸化物半導体を用いることができる。シリコン系半導体を用いたトランジスタは高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、その特性によりオフ電流が小さい。

【0037】

50

図1に示すトランジスタ160は、基板100上のゲート絶縁層108と、ゲート絶縁層108上のゲート電極層110と、を有する。なお、基板100にはチャネル形成領域、ソース領域、ドレイン領域が形成されている。また、トランジスタ160を囲うように、素子分離絶縁層102が設けられ、素子分離絶縁層102上にはトランジスタ160と電気的に接続する配線層112が設けられる。

【0038】

なお、トランジスタ160が有するゲート電極層110の側面に接して側壁絶縁層を設けてもよい。図1に示すように、側壁絶縁層を有さない構成とすると高集積化を図ることができる。

【0039】

トランジスタ160、素子分離絶縁層102、配線層112上には絶縁層104が形成されている。絶縁層104には、配線層112に達する開口が形成され、該開口に配線層114が形成される。配線層114は、絶縁層104に開口を形成した後、該開口に導電膜を成膜し、絶縁層104及び導電膜を化学的機械研磨(Chemical Mechanical Polishing: CMP)法などによって平坦化することで形成することができる。

【0040】

絶縁層104上には配線層115が形成されている。配線層115は配線層115a、配線層115b、及び配線層115cの積層構造としたが、この構造に限らず、必要とされる特性に応じて、配線層を設ければよい。配線層115上には絶縁層120が設けられている。絶縁層120は、上面が平坦となっており、トランジスタ160、配線層115に起因する凹凸が低減されている。

【0041】

絶縁層120上には絶縁層135が設けられている。絶縁層135はトランジスタ162から水素等が放出され、トランジスタ160の特性が低下することを抑制すると共に、トランジスタ162にトランジスタ160起因の不純物が入り込まないようにするために、プロッキング性を有する膜を用いる。ここで、トランジスタ162に入り込む不純物としては、水素、水分、窒素等がある。したがって、絶縁層135としては、これらの不純物を透過させない膜を用いることが好ましい。

【0042】

絶縁層135及び絶縁層120に形成された開口において、配線層116が形成され、配線層115と接している。絶縁層135上には、配線層116と接する配線層117が形成されている。配線層117上には絶縁層140が形成されている。

【0043】

絶縁層140は、化学量論的組成に対して過剰に酸素を含む膜であるとよい。絶縁層140が化学量論的組成に対して過剰に酸素を含んでいることで、絶縁層140と接する酸化物半導体積層144へ酸素を供給し、酸化物半導体積層144の酸素欠損を低減することができる。

【0044】

絶縁層140の上面は化学的機械研磨法などによって平坦化処理されており、トランジスタ160及び配線層115、配線層117等に起因する凹凸が低減されている。絶縁層140の上面の平坦性を向上させておくことによって、酸化物半導体積層144の膜厚分布を均一にすることができ、トランジスタ162の特性を向上させることができる。

【0045】

絶縁層140上には、トランジスタ162が形成されている。トランジスタ162は、酸化物半導体積層144と、酸化物半導体積層144に接するソース電極層142a及びドレイン電極層142bと、酸化物半導体積層144、ソース電極層142a及びドレイン電極層142b上のゲート絶縁層147と、ゲート絶縁層147上のゲート電極層148と、ゲート電極層148上の絶縁層150と、絶縁層155と、を有する。

【0046】

10

20

30

40

50

酸化物半導体積層 144 は、第 1 の酸化物半導体層 144a、第 2 の酸化物半導体層 144b 及び第 3 の酸化物半導体層 144c が積層されている。第 2 の酸化物半導体層 144b は第 1 の酸化物半導体層 144a 及び第 3 の酸化物半導体層 144c よりも、キャリア密度が高い酸化物半導体を用いる。そのため、キャリア密度の高い第 2 の酸化物半導体層 144b にチャネルが形成され、チャネルが形成される領域を、酸化物半導体積層 144 と絶縁層との界面から遠ざけることができる。

【0047】

また、第 1 の酸化物半導体層 144a 及び第 3 の酸化物半導体層 144c は非晶質構造とし、第 2 の酸化物半導体層 144b は結晶構造を有する。第 2 の酸化物半導体層 144b に結晶構造を有する半導体膜を適用することで、チャネル形成領域における酸素欠損の影響を低減することができる。10

【0048】

なお、第 1 の酸化物半導体層 144a と第 3 の酸化物半導体層 144c は同様の結晶性を有しており、界面が明確でない場合があるため、図面では、第 1 の酸化物半導体層 144a と第 3 の酸化物半導体層 144c の界面を点線で示す。

【0049】

次に、本発明の一態様の半導体装置の作製方法について説明する。まず、基板 100 上にゲート絶縁層 108 となる絶縁膜を形成する。

【0050】

基板 100 としてはシリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板等を用いてもよい。また、SOI 基板、半導体基板上に半導体素子が設けられたものなどを用いることができる。20

【0051】

また、バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板、セラミック基板、石英基板、サファイア基板などにプラズマ CVD 法等の気相成長法またはスパッタリング法等を用いて半導体層を形成したものを用いてもよい。半導体層としては、非晶質シリコン、非晶質シリコンをレーザーアニールなどの処理により結晶化させた多結晶シリコン、単結晶シリコンウエハーに水素イオン等を注入して表層部を剥離した単結晶シリコンなどを用いることができる。これらの半導体層をフォトリソグラフィ工程を用いて、島状に加工すればよい。30

【0052】

素子分離絶縁層を形成するためのマスクとなる保護層を形成し、保護層をマスクとしてエッチングを行い、保護層に覆われていない領域の基板 100 の一部を除去する。これにより基板 100 の上方に、分離された複数の半導体領域を形成する。分離された半導体領域を覆うように絶縁層を形成した後、当該半導体領域に重畳する絶縁層を選択的に除去することで、素子分離絶縁層 102 を形成する。

【0053】

次に、ゲート絶縁層 108 及びゲート電極層 110 の積層を形成する。ゲート絶縁層 108 はスパッタリング法、MBE (Molecular Beam Epitaxy) 法、CVD (Chemical Vapor Deposition)、パルスレーザ堆積法 (Pulsed Laser Deposition: PLD 法)、ALD (Atomic Layer Deposition) 法等を適宜用いて作製することができる。なお、ゲート絶縁層 108 をスパッタリング法を用いて形成すると、水素等の不純物元素を低減することができる。40

【0054】

ゲート絶縁層 108 としては、無機絶縁膜を用いればよい。例えば、酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、酸化ハフニウム膜、酸化ガリウム膜、窒化シリコン膜、窒化アルミニウム膜、窒化酸化シリコン膜、窒化酸化アルミニウム膜等を用いるとよい。また、これらの化合物を単層構造または 2 層以上の積層構造で形成して用いることができる。50

## 【0055】

ゲート電極層110（及びゲート電極層110と同一の導電膜で形成される配線層112等）としては、プラズマCVD法またはスパッタリング法等により、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて形成することができる。また、ゲート電極層110としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜、ニッケルシリサイドなどのシリサイド膜を用いてもよい。さらに、インジウムスズ酸化物、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウムスズ酸化物、インジウム亜鉛酸化物、酸化シリコンを添加したインジウムスズ酸化物などの導電性材料を適用することもできる。また、上記導電性材料と、上記金属材料の積層構造とすることもできる。10

## 【0056】

ここで、ゲート電極層110をマスクとして、基板100にn型の導電性を付与する不純物元素や、p型の導電性を付与する不純物元素を導入することで、ソース領域及びドレイン領域を形成する。不純物元素の導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いることができる。

## 【0057】

導入する不純物元素は、リン、ホウ素、窒素、ヒ素、アルゴン、アルミニウム、またはこれらを含む分子イオンなどを用いることができる。これらの元素のドーズ量は、 $1 \times 10^{13} \sim 5 \times 10^{16}$  ions/cm<sup>2</sup>とするのが好ましい。また、不純物元素としてリンを導入する場合、加速電圧を0.5~80kVとするのが好ましい。20

## 【0058】

なお、不純物元素を導入する処理は、複数回行ってもよい。不純物元素を導入する処理を複数回行う場合、不純物元素は複数回すべてにおいて同じであってもよいし、1回の処理毎に変えてよい。

## 【0059】

以上の工程で、トランジスタ160を作製することができる。

## 【0060】

次に、ゲート電極層110、ゲート絶縁層108、素子分離絶縁層102、配線層112を覆うように絶縁層104を形成する。絶縁層104はゲート絶縁層108と同様の方法、材料を用いて形成することができる。30

## 【0061】

さらに、絶縁層104に開口を形成し、該開口に配線層114を形成する（図2（A）参照）。配線層114は、配線層112と同様の材料及び方法を用いて形成することができる。

## 【0062】

続いて、絶縁層104上に配線層115を形成する。配線層115は、配線層112と同様の方法及び材料を用いて形成することができる。

## 【0063】

ここでは、配線層115の抵抗を下げ、かつ耐熱性を確保するために、配線層115を3層構造とし、配線層115bを抵抗率の低いアルミニウム膜とし、その上側及び下側に配線層115a及び配線層115cとして高融点のチタン膜を形成する。40

## 【0064】

なお、配線層115となる導電膜を形成した後、該導電膜をエッティングする工程において、絶縁層104も同時にエッティングされ、膜厚が減少する場合がある。したがって、絶縁層104の配線層115と重畳する領域は、他の領域と比較して膜厚が厚い場合がある。したがって、絶縁層104の表面は凹凸を有している場合がある。

## 【0065】

続いて、絶縁層104及び配線層115上に絶縁層120を形成する。絶縁層120は、50

トランジスタ 160 や、絶縁層 104、配線層 115 に起因する凹凸を低減するために、ゲート絶縁層 108 と同様の無機材料や、ポリイミド樹脂、アクリル樹脂、ベンゾシクロブテン系樹脂等の有機材料を用いることができる。また、上記有機材料の他に、低誘電材料 (low-k 材料) 等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、形成してもよい。

【0066】

続いて、絶縁層 120 上に絶縁層 135 を形成する。

【0067】

絶縁層 135 は、トランジスタ 162 に対して、トランジスタ 160 起因の不純物が入り込まないよう、ブロッキング性を有する膜を用いることが好ましい。例えば、絶縁層 135 として窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等を含む膜を用いてもよい。

10

【0068】

また、絶縁層 135 に低密度な部分、または膜が形成されていない部分（以下、これらの部分を総称して「鬆」とも呼ぶ）が存在した場合、鬆を介して不純物が入り込むことがある。

【0069】

絶縁層 135 に鬆が形成されないように、予め絶縁層 120 の平坦性を向上させておくとよい。例えば、絶縁層 135 の形成前に絶縁層 120 の表面に対して、化学的機械的研磨処理、プラズマ処理等の平坦化処理を行ってもよい。

20

【0070】

絶縁層 135 の形成後、絶縁層 135 及び絶縁層 120 において、配線層 115 に達する開口を形成し、該開口に配線層 116 を形成し、絶縁層 135 上に配線層 116 と接する配線層 117 を形成する。配線層 116 及び配線層 117 は、ゲート電極層 110 と同様の材料及び方法を用いて形成することができる。

【0071】

続いて、配線層 117 上に絶縁層 140 を形成する（図 2 (B) 参照）。絶縁層 140 としては、酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、酸化ハフニウム膜、又は酸化ガリウム膜等の酸化物絶縁層又は窒素を含む酸化物絶縁層を用いるとよい。また、これらの化合物を単層構造または 2 層以上の積層構造で形成して用いることができる。絶縁層 140 は、後に形成される酸化物半導体積層 144 に対して酸素を供給することができるよう、化学量論的組成に対して、酸素を過剰に含む膜とするとよい。

30

【0072】

また、後に形成される酸化物半導体積層 144 の膜厚分布を均一にし、結晶性を向上させるため、絶縁層 140 を化学的機械研磨処理等によって、平坦化させておいてもよい。

【0073】

続いて、絶縁層 140 上に酸化物半導体積層 144 を形成する。

40

【0074】

第 1 の酸化物半導体層 144a 乃至第 3 の酸化物半導体層 144c は、少なくともインジウム (In) を含み、AC スパッタリング法または DC スパッタリング法で成膜することができるスパッタリングターゲットを用いて成膜する。スパッタリングターゲットにインジウムを含ませることで導電性が高まるため、AC スパッタリング法または DC スパッタリング法で成膜することを容易なものとする。少なくとも成膜後に膜中のインジウムの濃度が  $1 \times 10^{19} \text{ atoms/cm}^3$  以上となるようなターゲットであるとよい。第 1 の酸化物半導体層 144a 及び第 3 の酸化物半導体層 144c を構成する材料は、 $In_x Zn_y O_z$  ( $X > 1$ 、 $Y > 0$ 、 $M1 = Ga$ 、 $Hf$  等) で表記できる材料を用いる。ただし、第 1 の酸化物半導体層 144a 及び第 3 の酸化物半導体層 144c を構成する材料に Ga を含ませる場合、含ませる Ga の割合が多い、具体的には  $In_x Zn_y$

50

$O_z$  で表記できる材料で  $X = 10$  を超えると成膜ゴミが発生する恐れがあり、ACスパッタリング法またはDCスパッタリング法で成膜することが困難となり、不適である。

#### 【0075】

また、第2の酸化物半導体層144bを構成する材料は、 $InM_{2-x}Z_{n_y}O_z$  ( $X = 1$ 、 $Y = X, Z > 0$ 、 $M_2 = Ga, Sn$ 等) で表記できる材料を用いる。

#### 【0076】

特に、第2の酸化物半導体層144bが $In - M_2 - Z_n$ 酸化物 ( $M_2$ は $Ga, Sn$ 等) の場合、第2の酸化物半導体層144bを成膜するために用いるターゲットにおいて、金属元素の原子数比を $In : M_2 : Z_n = x_1 : y_1 : z_1$  とすると、 $x_1 / y_1$  は、1/3以上6以下、さらには1以上6以下であって、 $z_1 / y_1$  は、1/3以上6以下、さらには1以上6以下であることが好ましい。なお、 $z_1 / y_1$  を1以上6以下とすることで、第2の酸化物半導体層144bとして後述するCAC-OS膜が形成されやすくなる。ターゲットの金属元素の原子数比の代表例としては、 $In : M_2 : Z_n = 1 : 1 : 1$ 、 $In : M_2 : Z_n = 3 : 1 : 2$  等がある。

#### 【0077】

また特に、第1の酸化物半導体層144a及び第3の酸化物半導体層144cが $In - M_1 - Z_n$ 酸化物 ( $M_1$ は $Ga, Hf$ 等) の場合、第1の酸化物半導体層144a及び第3の酸化物半導体層144cを成膜するために用いるターゲットにおいて、金属元素の原子数比を $In : M_1 : Z_n = x_2 : y_2 : z_2$  とすると、 $x_2 / y_2 < x_1 / y_1$  であって、 $z_2 / y_2$  は、1/3以上6以下、さらには1以上6以下であることが好ましい。なお、 $z_2 / y_2$  を1以上6以下とすることで、第1の酸化物半導体層144a及び第3の酸化物半導体層144cとして後述するCAC-OS膜が形成されやすくなる。ターゲットの金属元素の原子数比の代表例としては、 $In : M_1 : Z_n = 1 : 3 : 2$ 、 $In : M_1 : Z_n = 1 : 3 : 4$ 、 $In : M_1 : Z_n = 1 : 3 : 6$ 、 $In : M_1 : Z_n = 1 : 3 : 8$  等がある。

#### 【0078】

第1の酸化物半導体層144a乃至第3の酸化物半導体層144cとしては、 $In : Ga : Z_n = 1 : 1 : 1$  ( $= 1/3 : 1/3 : 1/3$ )、 $In : Ga : Z_n = 2 : 2 : 1$  ( $= 2/5 : 2/5 : 1/5$ )、あるいは $In : Ga : Z_n = 3 : 1 : 2$  ( $= 1/2 : 1/6 : 1/3$ )、 $In : Ga : Z_n = 1 : 3 : 2$  ( $= 1/6 : 1/2 : 1/3$ )、 $In : Ga : Z_n = 1 : 4 : 3$  ( $= 1/8 : 1/2 : 3/8$ )、 $In : Ga : Z_n = 1 : 5 : 4$  ( $= 1/10 : 1/2 : 2/5$ )、 $In : Ga : Z_n = 1 : 6 : 6$  ( $= 1/13 : 6/13 : 6/13$ ) の原子数比の酸化物等を用いればよい。なお、第1の酸化物半導体層144a及び第3の酸化物半導体層144cとしては、ガリウムの代わりにハフニウムを用いてよい。また、第2の酸化物半導体層144bとしては、ガリウムの代わりにスズを用いてよい。

#### 【0079】

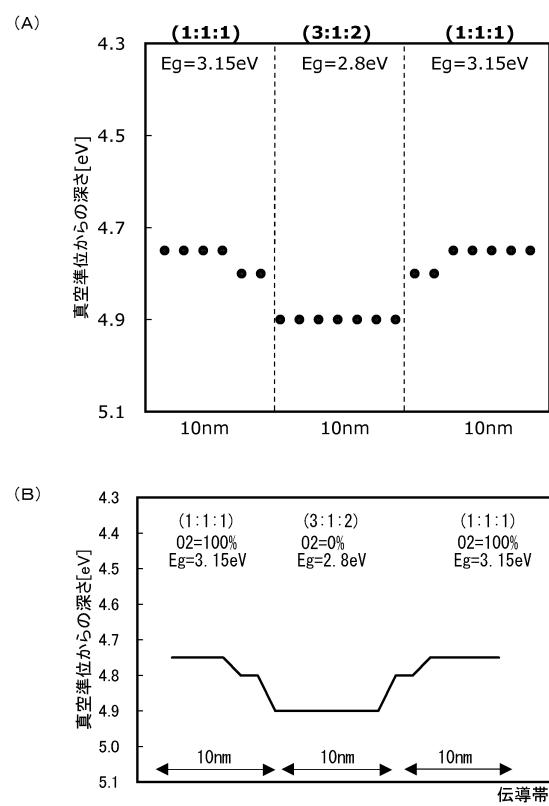

第1の酸化物半導体層144aの伝導帯下端及び第3の酸化物半導体層144cの伝導帯下端に比べて第2の酸化物半導体層144bの伝導帯下端が真空準位から最も深くなるような井戸型構造を構成するように、第1、第2、及び第3の酸化物半導体層の材料を選択する。真空準位からの伝導帯下端の深さ(電子親和力とも表現できる。)は、真空準位と価電子帯上端とのエネルギー差(いわゆる、イオン化ポテンシャル。)から、伝導帯下端と価電子帯上端とのエネルギー差(いわゆる、バンドギャップ。)を差し引いた値として求めることができる。

#### 【0080】

なお、電子親和力の導出に用いる酸化物半導体のイオン化ポテンシャルは紫外線光電子分光分析(UPS: Ultraviolet Photoelectron Spectroscopy)等で測定することができる。代表的なUPSの測定装置としてはVersa Probe (PHI社製)を用いる。また、電子親和力とは、真空準位( $E_\infty$ )から伝導帯端( $E_c$ )までのエネルギー差である。また、エネルギー・バンドギャップ( $E_g$ )は

10

20

30

40

50

、全自動分光エリプソメーターUT-300を用いて測定することができる。イオン化ポテンシャルの値からエネルギー・バンドギャップを差し引くことで伝導帯下端のエネルギーを算出し、単層または積層のバンド構造を作成することができる。この手法により、本明細書において開示する積層構造を用いることで埋め込みチャネルが形成されていることを確認することができる。図14(A)及び図14(B)にその一例を示す。

#### 【0081】

図14(A)は、酸素100%雰囲気下でIn:Ga:Zn=1:1:1[原子数比]の組成を有するIn-Ga-Zn酸化物のスパッタリングターゲットを用いて膜厚10nm成膜した後、アルゴン100%雰囲気下でIn:Ga:Zn=3:1:2[原子数比]の組成を有するIn-Ga-Zn酸化物のスパッタリングターゲットを用いて膜厚10nm成膜し、さらに酸素100%雰囲気下でIn:Ga:Zn=1:1:1[原子数比]の組成を有するIn-Ga-Zn酸化物のスパッタリングターゲットを用いて膜厚10nm成膜して積層させたサンプルを用いて調べたイオン化ポテンシャルから、全自動分光エリプソメーターUT-300を用いて測定したエネルギー・バンドギャップを差し引くことで、真空準位から伝導帯下端までのエネルギーを算出したデータであり、そのデータに基づいて作成したバンド構造を図14(B)に示す。図14(B)では、第1の酸化物半導体層の伝導帯下端及び第3の酸化物半導体層の伝導帯下端に比べて第2の酸化物半導体層の伝導帯下端が真空準位から最も深くなるような井戸型構造を構成していることがわかる。

#### 【0082】

また、第1の酸化物半導体層144a乃至第3の酸化物半導体層144cとして、In-Ga-Zn酸化物を用いた場合、第1の酸化物半導体層144a乃至第3の酸化物半導体層144cの構成元素は同一であるため、第1の酸化物半導体層144aと第2の酸化物半導体層144b、及び第2の酸化物半導体層144bと第3の酸化物半導体層144cの界面におけるトラップ準位が少なく、トランジスタの経時変化やストレス試験によるしきい値電圧の変動量を低減することができる。

#### 【0083】

GaはInと比較して酸素欠損の形成エネルギーが大きく酸素欠損が生じにくいため、InがGaと同等または少ない組成となる酸化物はInがGaよりも多い組成となる酸化物と比較して安定した特性を備える。そのため、第1の酸化物半導体層144a及び第3の酸化物半導体層144cは、シリコン絶縁層と安定した界面を形成することができ、信頼性の高い半導体装置とすることができます。

#### 【0084】

酸化物半導体では主として重金属のs軌道がキャリア伝導に寄与しており、Inの含有率を多くすることにより、より多くのs軌道が重なるため、InがGaよりも多い組成となる酸化物はInがGaと同等または少ない組成となる酸化物と比較して高い移動度を備える。そのため、インジウムを多く含む第2の酸化物半導体層144bにキャリアが形成されることによって、高い移動度を実現することができる。

#### 【0085】

第2の酸化物半導体層144bは、伝導帯(コンダクションバンドとも呼ぶ)下端が井戸型構造(ウェル構造とも呼ぶ)を構成するように適宜材料を選択する。なお、井戸型構造の一例を図12(B)に示す。図12(B)は、図12(A)に示すトランジスタのY1-Y2間ににおけるエネルギー・バンド図である。なお、図12(A)に示すトランジスタは、図4(A)に示すトランジスタ163と同様の構成であるため、詳細な説明は省略する。

#### 【0086】

また、第14族元素の一つであるシリコンや炭素が不純物として酸化物半導体層に含まれてしまうとドナーを作りn型化することがあるため、各酸化物半導体層に含まれるSiの濃度は $3 \times 10^{18}$ atoms/cm<sup>3</sup>以下、好ましくは $3 \times 10^{17}$ atoms/cm<sup>3</sup>以下とする。特に第2の酸化物半導体層144bに第14族元素が多く混入しないように、第1の酸化物半導体層144a及び第3の酸化物半導体層144cで、キャリアパス

10

20

30

40

50

となる第2の酸化物半導体層144bを挟む、または囲む構成とすることが好ましい。即ち、第1の酸化物半導体層144a及び第3の酸化物半導体層144cは、シリコンなどの第14族元素が第2の酸化物半導体層144bに混入することを防ぐバリア層とも呼べる。

【0087】

また、酸化物半導体積層144に含まれる水素は、金属と結合する酸素と反応して水となると共に、酸素が脱離した格子（あるいは酸素が脱離した部分）には欠損が形成されてしまう。また、水素の一部が酸素と結合することで、キャリアである電子が生じてしまう。これらのため、酸化物半導体積層144の成膜工程において、水素を含む不純物を極めて減らすことにより、酸化物半導体積層144の水素濃度を低減することが可能である。このため、水素をできるだけ除去し、高純度化させた酸化物半導体積層144をチャネル形成領域とすることにより、しきい値電圧のマイナスシフトを低減することができ、またトランジスタのソース及びドレインにおけるリーク電流（代表的には、オフ電流等）を数yA /  $\mu$ m ~ 数zA /  $\mu$ m にまで低減することが可能であり、トランジスタの電気特性を向上させることができる。

10

【0088】

トランジスタの半導体層となる酸化物半導体膜を上記積層構成とすることにより、チャネルが形成される領域は、一定電流測定法（CPM: Constant Photocurrent Method）により測定された局在準位による吸収係数を  $3 \times 10^{-3} / \text{cm}$  以下（状態密度に換算すると  $3 \times 10^{13} / \text{cm}^3$  以下）とすることができます。

20

【0089】

また、上記積層構成では、第1、第2、及び第3の酸化物半導体層を用いて一つの井戸型構造を形成する構成例を示したが、特に限定されず、第2の酸化物半導体層を多層として複数の井戸型構造を構成してもよく、その一例を図12（C）に示す。

【0090】

スパッタリングガスは、希ガス（代表的にはアルゴン）雰囲気、酸素雰囲気、希ガス及び酸素の混合ガスを適宜用いる。なお、希ガス及び酸素の混合ガスの場合、希ガスに対して酸素のガス比を高めることが好ましい。

【0091】

酸化物半導体層の成膜時に用いるターゲットは、形成する酸化物半導体層の組成に合わせて適宜選択すればよい。

30

【0092】

ターゲットの一例として、In-Ga-Zn酸化物ターゲットについて以下に示す。

【0093】

InO<sub>x</sub>粉末、GaO<sub>y</sub>粉末およびZnO<sub>z</sub>粉末を所定のmol数で混合し、加圧処理後、1000以上1500以下の温度で加熱処理をすることで多結晶であるIn-Ga-Zn酸化物ターゲットとする。なお、X、YおよびZは任意の正数である。ここで、所定のmol数比は、例えば、InO<sub>x</sub>粉末、GaO<sub>y</sub>粉末およびZnO<sub>z</sub>粉末が、2:2:1、8:4:3、3:1:1、1:1:1、4:2:3または3:1:2である。なお、粉末の種類、およびその混合するmol数比は、作製するターゲットによって適宜変更すればよい。

40

【0094】

ここで、CAAC-OS膜について説明する。CAAC-OS膜は、c軸配向した複数の結晶部を有する酸化物半導体膜の一つである。また、透過型電子顕微鏡（TEM: Transmission Electron Microscope）による観察像では、CAAC-OS膜には粒界（グレインバウンダリーともいう。）は確認できない。そのため、CAAC-OS膜は、粒界に起因する電子移動度の低下が起こりにくいといえる。

【0095】

ここで、本明細書において、「平行」とは、二つの直線が-10°以上10°以下の角度で配置されている状態をいう。従って、-5°以上5°以下の場合も含まれる。また、「

50

「垂直」とは、二つの直線が  $80^\circ$  以上  $100^\circ$  以下の角度で配置されている状態をいう。従って、 $85^\circ$  以上  $95^\circ$  以下の場合も含まれる。

【0096】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

【0097】

CAAC-OS膜を、試料面と概略平行な方向からTEMによって観察（断面TEM観察）すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、CAAC-OS膜の膜を形成する面（被形成面ともいう。）または上面の凹凸を反映した形状であり、CAAC-OS膜の被形成面または上面と平行に配列する。

10

【0098】

一方、CAAC-OS膜を、試料面と概略垂直な方向からTEMによって観察（平面TEM観察）すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

【0099】

断面TEM観察および平面TEM観察より、CAAC-OS膜の結晶部は配向性を有していることがわかる。

【0100】

なお、CAAC-OS膜に含まれるほとんどの結晶部は、一辺が  $100\text{ nm}$  未満の立方体内に収まる大きさである。従って、CAAC-OS膜に含まれる結晶部は、一辺が  $10\text{ nm}$  未満、 $5\text{ nm}$  未満または  $3\text{ nm}$  未満の立方体内に収まる大きさの場合も含まれる。ただし、CAAC-OS膜に含まれる複数の結晶部が連結することで、一つの大きな結晶領域を形成する場合がある。例えば、平面TEM像において、 $2500\text{ nm}^2$  以上、 $5\mu\text{m}^2$  以上または  $1000\mu\text{m}^2$  以上となる結晶領域が観察される場合がある。

20

【0101】

CAAC-OS膜に対し、X線回折（XRD：X-Ray Diffraction）装置を用いて構造解析を行うと、例えば $\text{InGaZnO}_4$ の結晶を有するCAAC-OS膜のout-of-plane法による解析では、回折角（ $2\theta$ ）が  $31^\circ$  近傍にピークが現れる場合がある。このピークは、 $\text{InGaZnO}_4$ の結晶の（009）面に帰属されることから、CAAC-OS膜の結晶がc軸配向性を有し、c軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

30

【0102】

一方、CAAC-OS膜に対し、c軸に概略垂直な方向からX線を入射させるin-plane法による解析では、 $2\theta$  が  $56^\circ$  近傍にピークが現れる場合がある。このピークは、 $\text{InGaZnO}_4$ の結晶の（110）面に帰属される。 $\text{InGaZnO}_4$ の単結晶酸化物半導体膜であれば、 $2\theta$  を  $56^\circ$  近傍に固定し、試料面の法線ベクトルを軸（c軸）として試料を回転させながら分析（スキャン）を行うと、（110）面と等価な結晶面に帰属されるピークが6本観察される。これに対し、CAAC-OS膜の場合は、 $2\theta$  を  $56^\circ$  近傍に固定してスキャンした場合でも、明瞭なピークが現れない。

40

【0103】

以上のことから、CAAC-OS膜では、異なる結晶部間ではa軸およびb軸の配向は不規則であるが、c軸配向性を有し、かつc軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。従って、前述の断面TEM観察で確認された層状に配列した金属原子の各層は、結晶のab面に平行な面である。

【0104】

なお、結晶部は、CAAC-OS膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶のc軸は、CAAC-OS膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えば、CAAC-OS膜の形状をエッティングなどによって変化させた場合、結晶のc軸がCAAC-OS膜の被形成面

50

または上面の法線ベクトルと平行にならないこともある。

【0105】

また、CAAC-OS膜において、c軸配向した結晶部の分布が均一でなくてもよい。例えば、CAAC-OS膜の結晶部が、CAAC-OS膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりもc軸配向した結晶部の割合が高くなることがある。また、CAAC-OS膜に不純物を添加する場合、不純物が添加された領域が変質し、部分的にc軸配向した結晶部の割合の異なる領域が形成されることもある。

【0106】

なお、 $InGaZnO_4$ の結晶を有するCAAC-OS膜のout-of-plane法による解析では、 $2\theta$ が $31^\circ$ 近傍のピークの他に、 $2\theta$ が $36^\circ$ 近傍にもピークが現れる場合がある。 $2\theta$ が $36^\circ$ 近傍のピークは、CAAC-OS膜中の一部に、c軸配向性を有さない結晶が含まれることを示している。CAAC-OS膜は、 $2\theta$ が $31^\circ$ 近傍にピークを示し、 $2\theta$ が $36^\circ$ 近傍にピークを示さないことが好ましい。

10

【0107】

CAAC-OS膜は、不純物濃度の低い酸化物半導体膜である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体膜の主成分以外の元素である。特に、シリコンなどの、酸化物半導体膜を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体膜から酸素を奪うことで酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径（または分子半径）が大きいため、酸化物半導体膜内部に含まれると、酸化物半導体膜の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体膜に含まれる不純物は、キャリアトラップやキャリア発生源となる場合がある。

20

【0108】

また、CAAC-OS膜は、欠陥準位密度の低い酸化物半導体膜である。例えば、酸化物半導体膜中の酸素欠損は、キャリアトラップとなることや、水素を捕獲することによってキャリア発生源となることがある。

【0109】

不純物濃度が低く、欠陥準位密度が低い（酸素欠損の少ない）ことを、高純度真性または実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリア発生源が少ないため、キャリア密度を低くすることができる。従って、当該酸化物半導体膜を用いたトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリーオンともいう。）になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、キャリアトラップが少ない。そのため、当該酸化物半導体膜を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。なお、酸化物半導体膜のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体膜を用いたトランジスタは、電気特性が不安定となる場合がある。

30

【0110】

また、CAAC-OS膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

【0111】

また、CAAC-OS膜のように結晶部を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましい。

【0112】

なお、CAAC-OS膜を形成する際は、例えば、多結晶である酸化物半導体ターゲットを用い、スパッタリング法によって成膜する。当該ターゲットにイオンが衝突すると、タ

40

50

一ゲットに含まれる結晶領域が a - b 面から劈開し、 a - b 面に平行な面を有する平板状またはペレット状のスパッタリング粒子として剥離することがある。この場合、当該平板状のスパッタリング粒子が、結晶状態を維持したまま基板に到達することで、 C A A C - O S 膜を成膜することができる。

【 0 1 1 3 】

また、 C A A C - O S 膜を成膜するために、以下の条件を適用することが好ましい。

【 0 1 1 4 】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物濃度（水素、水、二酸化炭素および窒素など）を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が - 80 以下、好ましくは - 100 以下である成膜ガスを用いる。 10

【 0 1 1 5 】

また、成膜時の基板加熱温度を高めることで、基板到達後にスパッタリング粒子のマイグレーションが起こる。具体的には、基板加熱温度を 100 以上 740 以下、好ましくは 200 以上 500 以下として成膜する。成膜時の基板加熱温度を高めることで、平板状のスパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起こり、スパッタリング粒子の平らな面が基板に付着する。

【 0 1 1 6 】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、 30 体積 % 以上、好ましくは 100 体積 % とする。 20

【 0 1 1 7 】

次に、微結晶酸化物半導体膜について説明する。

【 0 1 1 8 】

微結晶酸化物半導体膜は、 T E M による観察像では、明確に結晶部を確認することができない場合がある。微結晶酸化物半導体膜に含まれる結晶部は、 1 nm 以上 100 nm 以下、または 1 nm 以上 10 nm 以下の大きさであることが多い。特に、 1 nm 以上 10 nm 以下、または 1 nm 以上 3 nm 以下の微結晶であるナノ結晶 ( n c : n a n o c r y s t a l ) を有する酸化物半導体膜を、 n c - O S ( n a n o c r y s t a l l i n e O x i d e S e m i c o n d u c t o r ) 膜と呼ぶ。また、 n c - O S 膜は、例えば、 T E M による観察像では、結晶粒界を明確に確認できない場合がある。 30

【 0 1 1 9 】

n c - O S 膜は、微小な領域（例えば、 1 nm 以上 10 nm 以下の領域、特に 1 nm 以上 3 nm 以下の領域）において原子配列に周期性を有する。また、 n c - O S 膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。従って、 n c - O S 膜は、分析方法によっては、非晶質酸化物半導体膜と区別が付かない場合がある。例えば、 n c - O S 膜に対し、結晶部よりも大きいビーム径の X 線を用いる X R D 装置を用いて構造解析を行うと、 o u t - o f - p l a n e 法による解析では、結晶面を示すピークが検出されない。また、 n c - O S 膜に対し、結晶部よりも大きいプローブ径（例えば 50 nm 以上）の電子線を用いる電子線回折（制限視野電子線回折ともいう。）を行うと、ハローパターンのような回折像が観測される。一方、 n c - O S 膜に対し、結晶部の大きさと近いか結晶部より小さいプローブ径（例えば 1 nm 以上 30 nm 以下）の電子線を用いる電子線回折（ナノビーム電子線回折ともいう。）を行うと、スポットが観測される。また、 n c - O S 膜に対しナノビーム電子線回折を行うと、円を描くよう（リング状に）輝度の高い領域が観測される場合がある。また、 n c - O S 膜に対しナノビーム電子線回折を行うと、リング状の領域内に複数のスポットが観測される場合がある。 40

【 0 1 2 0 】

n c - O S 膜は、非晶質酸化物半導体膜よりも規則性の高い酸化物半導体膜である。そのため、 n c - O S 膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低くなる。ただし、 50

n c - O S 膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、n c - O S 膜は、C A A C - O S 膜と比べて欠陥準位密度が高くなる。

【0121】

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、微結晶酸化物半導体膜、C A A C - O S 膜のうち、二種以上を有する積層膜であってもよい。

【0122】

ここでは、まず上述の方法を用いて第1の酸化物半導体層144a及び第2の酸化物半導体層144bを積層して成膜した後、加熱処理を行い、マスクを用いて選択的にエッチングを行う。

【0123】

本実施の形態では、基板温度を室温とし、In : Ga : Zn = 1 : 3 : 2の原子数比のターゲットを用いて、非晶質構造である第1の酸化物半導体層144aを成膜する。非晶質構造である第1の酸化物半導体層144aの膜厚は、10nm以上40nm以下、好ましくは20nm以上30nm以下とする。非晶質構造である第1の酸化物半導体層144aの膜厚を大きくすることで、第2の酸化物半導体層144bへシリコン等が混入することを防止することができる。

10

【0124】

また、結晶構造を有する第2の酸化物半導体層144bの成膜には、基板温度を400とし、In : Ga : Zn = 1 : 1 : 1の原子数比のターゲットを用いる。第2の酸化物半導体層144bは、表面と略垂直な方向にc軸が配向した結晶を含む膜であり、C A A C - O S 膜とすることが好ましい。第2の酸化物半導体層144bの膜厚は、5nm以上10nm以下とする。第2の酸化物半導体層144bの成膜温度は、400以上550以下、好ましくは450以上500以下とする。ただし、既に形成している配線層が耐えられる温度範囲で行うこととする。

20

【0125】

非晶質構造を有する第1の酸化物半導体層144a上に結晶構造を有する第2の酸化物半導体層144bを積層するため、ヘテロ構造と呼ぶことができる。

【0126】

成膜後の加熱処理は、減圧下で窒素、酸素、又は窒素及び酸素雰囲気下で150以上基板の歪み点未満、好ましくは250以上450以下、更に好ましくは300以上450以下とする。加熱処理によって、酸化物半導体層中の過剰な水素（水や水酸基を含む）を除去（脱水化または脱水素化）する。そして、熱処理終了後の加熱温度を維持、またはその加熱温度から徐冷しながら同じ炉に高純度の酸素ガス、又は超乾燥エア（C R D S（キャビティリングダウンレーザー分光法）方式の露点計を用いて測定した場合の水分量が20ppm（露点換算で-55）以下、好ましくは1ppm以下、より好ましくは10ppb以下の空気）を導入する。酸素ガスの作用により、脱水化または脱水素化処理による不純物の排除工程によって同時に減少してしまった酸化物半導体を構成する主成分材料である酸素を供給する。

30

【0127】

第2の酸化物半導体層144bを形成した後、加熱処理を行うことで、第2の酸化物半導体層144bにおいて、水素濃度を $5 \times 10^{-8}$ atoms/cm<sup>3</sup>未満、好ましくは $1 \times 10^{-8}$ atoms/cm<sup>3</sup>以下、より好ましくは $5 \times 10^{-7}$ atoms/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{-6}$ atoms/cm<sup>3</sup>以下とすることができる。

40

【0128】

加熱処理は、ヘリウム、ネオン、アルゴン、キセノン、クリプトン等の希ガス、または窒素を含む不活性ガス雰囲気で行う。または、不活性ガス雰囲気で加熱した後、酸素雰囲気で加熱してもよい。なお、上記不活性雰囲気及び酸素雰囲気に水素、水などが含まれないことが好ましい。処理時間は3分～24時間とする。酸化物半導体層の加熱処理は何度行ってもよく、そのタイミングは問わない。

【0129】

50

なお、酸化物半導体積層144の上側、下側、または上下の両側に酸化物絶縁層が設けられた状態で加熱することによって、酸化物絶縁層から酸化物半導体積層144に酸素を供給し、酸化物半導体積層144の酸素欠陥を低減してもよい。酸化物半導体積層144の酸素欠損を低減することによって、半導体特性を良好にすることができる。

【0130】

続いて、第2の酸化物半導体層144bの上面及び側面並びに第1の酸化物半導体層144aの側面を覆うように第3の酸化物半導体層144cを形成する(図3(A)参照)。第3の酸化物半導体層144cの成膜後にも、酸化物半導体の脱水素化または脱水化のための加熱処理をしてもよい。

【0131】

また、第3の酸化物半導体層144cの成膜には、基板温度を室温とし、In:Ga:Zn = 1:3:2の原子数比のターゲットを用いる。第3の酸化物半導体層144cは、第1の酸化物半導体層144aとほぼ成膜条件が同じであり、膜全体が非晶質構造を有する。第3の酸化物半導体層144cの膜厚は、10nm以上40nm以下、好ましくは20nm以上30nm以下とする。

【0132】

第3の酸化物半導体層144cは非晶質とする。結晶構造を有する第2の酸化物半導体層144b上に非晶質構造を有する第3の酸化物半導体層144cを積層するため、ヘテロ構造と呼ぶことができる。

【0133】

第3の酸化物半導体層144cは、第1の酸化物半導体層144aと同様の条件を用いて成膜することができる。なお、第1の酸化物半導体層144a及び第3の酸化物半導体層144cは同一の組成及び結晶性を有しているため、その界面が明確でない場合がある。そのため、図において、第1の酸化物半導体層144aと第3の酸化物半導体層144cの界面を点線で示した。

【0134】

チャネル形成領域となる第2の酸化物半導体層144bを非晶質である第1の酸化物半導体層144a及び第3の酸化物半導体層144cによって挟む又は囲むことによって、酸化物半導体積層144の内部応力や外部からの応力を緩和し、トランジスタの特性ばらつきが低減され、また、トランジスタの信頼性をさらに高めることができる。

【0135】

また、キャリアパスとなる第2の酸化物半導体層144bに結晶構造を有するCAC-O<sub>5</sub>膜を用い、第1の酸化物半導体層144a及び第3の酸化物半導体層144cを非晶質構造とすることによって、第2の酸化物半導体層144bに良好にチャネルを形成することができる。

【0136】

次に、酸化物半導体積層144上にソース電極層142a、ドレイン電極層142bとなる導電膜を形成する。導電膜としては、ゲート電極層110と同様の材料及び方法を用いて形成することができる。

【0137】

なお、ソース電極層142a及びドレイン電極層142bを形成する際のエッチングにおいて、ソース電極層142a及びドレイン電極層142bに挟まれた酸化物半導体積層144も同時にエッチングされ、膜厚が減少する場合がある。そのため、酸化物半導体積層144のソース電極層142a及びドレイン電極層142bと重畠しない領域は、重畠する領域と比較して膜厚が薄い場合がある。

【0138】

酸化物半導体積層144は、チャネル形成領域となる第2の酸化物半導体層144bが第1の酸化物半導体層144a及び第3の酸化物半導体層144cによって挟まれている。したがって、ソース電極層142a及びドレイン電極層142bのエッチングの際に、酸化物半導体積層144が同時にエッチングされても、チャネル形成領域となる第2の酸化

10

20

30

40

50

物半導体層 144b にその影響が及びにくく、チャネル形成領域がエッチングされて膜厚が減少する可能性が低いため、安定した特性を示すことができる。

【0139】

続いて、ソース電極層 142a 及びドレイン電極層 142b 上にゲート絶縁層 147 となる酸化物絶縁層を形成する。ここでは、ゲート絶縁層 147 を 2 層構造とし、酸化物絶縁層を含むゲート絶縁層 147a と、窒化物絶縁層を含むゲート絶縁層 147b の積層構造とする。

【0140】

ゲート絶縁層 147a に用いる酸化物絶縁層としては絶縁層 140 と同様の材料及び方法を用いることができる。特に、ゲート絶縁層 147a としては酸化物半導体積層 144 に対するプラズマダメージを低減するため、プラズマダメージの少ない成膜条件で成膜することがよい。また、ゲート絶縁層 147a は、酸化物半導体積層 144 と接するため、酸化物半導体積層 144 に酸素を供給できるよう、化学量論的組成よりも多量の酸素を含み、かつ加熱処理によって、酸素が脱離しやすい膜を用いるといよい。

10

【0141】

ゲート絶縁層 147b として用いることができる絶縁膜は、窒化酸化シリコン膜、酸化窒化シリコン膜等の酸素及び窒素が含有されたシリコン膜を用いるとよい。

【0142】

続いて、ゲート絶縁層 147 上にゲート電極層 148 を形成する。ゲート電極層 148 としては、ゲート電極層 110 と同様の材料及び方法を用いて形成することができる。

20

【0143】

ゲート電極層 148 上に絶縁層 150 を形成する。絶縁層 150 は、絶縁層 140 と同様の材料及び方法を用いて形成することができる。絶縁層 150 は、酸化物半導体積層 144 に対し、酸素を供給できるよう、化学量論的組成に対し過剰に酸素を含むようにすることが好ましい。

【0144】

また、絶縁層 150 にイオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法などを用いて酸素を添加してもよい。酸素を添加することによって、絶縁層 150 に酸素を過剰に含ませ、絶縁層 150 から酸化物半導体積層 144 へ酸素を供給することができる。なお、図において、絶縁層 150 に酸素が添加され、絶縁層 150 が酸素濃度のピークを有することを明示するため、絶縁層 150 中に点線で示した。

30

【0145】

絶縁層 150 を形成後、加熱処理を行う。酸化物半導体積層 144 は、酸化物半導体積層 144 の形成後のエッチングやプラズマに曝され、ダメージを受けて形成される酸素欠損を含む。そのため、酸化物半導体積層の成膜後に与えられたダメージを回復させるために加熱処理を行い、酸素を供給することによって酸素欠損を低減させる。該熱処理の温度は、代表的には、200 以上 450 以下とする。当該加熱処理により、窒素を有する酸化絶縁層に含まれる窒素を放出させることができる。なお、当該加熱処理により、窒素を有する酸化物絶縁層から、水、水素等を脱離させることができる。

40

【0146】

例えば、窒素及び酸素の混合雰囲気で、350 、1 時間の加熱処理を行う。酸化物半導体積層 144 に含まれる水素原子及び酸素原子が、加熱処理により、酸化物半導体積層 144 、酸化物半導体積層 144 及び絶縁層（絶縁層 140 及びゲート絶縁層 147 ）の界面から脱離する。酸化物半導体積層 144 において、酸素原子が脱離した位置は酸素欠損となるが、酸化物絶縁層に含まれる化学量論的組成を満たす酸素よりも多くの酸素原子が酸素欠損の位置へ移動し、酸素欠損を補填する。

【0147】

こうして、絶縁層 150 形成後の加熱処理によって、酸化物半導体層から、窒素、水素、または水が脱離することで、膜中の窒素、水素、または水の含有率を約 10 分の一程度ま

50

で低減することができる。

【0148】

絶縁層150上に絶縁層155を形成する。絶縁層155は絶縁層135と同様の、材料及び方法を用いて形成することができる。絶縁層155によって、酸化物半導体積層144に半導体装置上部からの不純物が入り込むことまたは、酸化物半導体積層144及び絶縁層150に含まれる酸素が半導体装置の上部へ脱離することを抑制することができる。

【0149】

以上の工程で、半導体装置を作製することができる(図3(B)参照)。

【0150】

本実施の形態に示す半導体装置は、チャネル形成領域となる第2の酸化物半導体層144bが第1の酸化物半導体層144a及び第3の酸化物半導体層144cに挟まれて形成されているため、チャネル形成領域が酸化物半導体積層144の表面から遠ざけることができ、表面散乱の影響を低減することができる。

10

【0151】

さらに、酸化物半導体積層144を挟んで、化学量論的組成に対して酸素を過剰に含んだ絶縁層が形成されているため、酸化物半導体積層144へ酸素を供給し、酸化物半導体積層144の酸素欠損を補填することで、信頼性の高い半導体装置とできる。

【0152】

加えて、酸素を過剰に含む絶縁層を挟んで、水素、酸素に対するブロッキング性を有する窒化絶縁膜を形成しているため、酸化物半導体積層144へ水素、水分等の不純物が入り込むこと、または酸化物半導体層及び酸素を過剰に含む絶縁層から、酸素が抜けることを抑制することができる。

20

【0153】

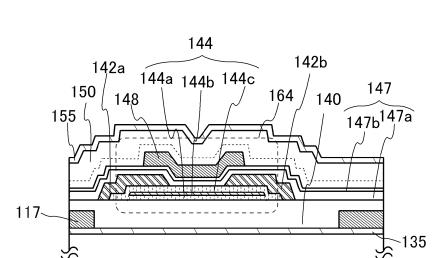

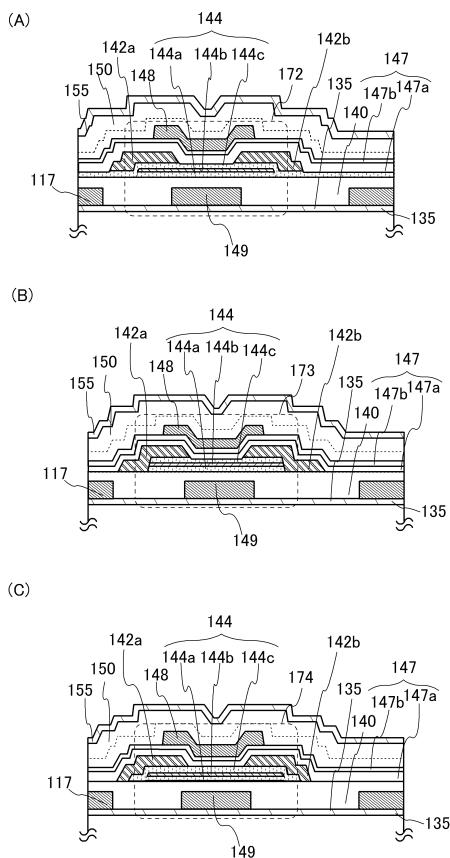

なお、本実施の形態に示す半導体装置が有する第2のトランジスタは上記の構成に限らない。例えば、図4及び図5に、本発明の一態様の半導体装置の別のー態様を示す。なお、図4及び図5では、第2のトランジスタのみについて示し、第1のトランジスタ及び配線層等については省略する。

【0154】

図4(A)に示すトランジスタ163は、図1に示すトランジスタ162と比較して、第3の酸化物半導体層144cが第2の酸化物半導体層144bの側面及び第1の酸化物半導体層144aの側面を覆っていない点が異なる。トランジスタ163は、第1の酸化物半導体層144a、第2の酸化物半導体層144b及び第3の酸化物半導体層144cを大気にふれること無く連続して成膜した後、マスクを用いてエッチングし、島状の酸化物半導体積層144とすることによって形成することができる。このような構成とすることによって、第2の酸化物半導体層144bの表面が大気やエッチング処理に曝されることはなく、安定した特性を与えることができる。

30

【0155】

また、第3の酸化物半導体層144cがエッチングされていることによって、ゲート絶縁層147(ゲート絶縁層147a)と絶縁層140が接し、酸化物半導体積層144を酸化物絶縁層によって囲むことができる。また、酸化物絶縁層同士が接することによって密着性を向上させることができる。

40

【0156】

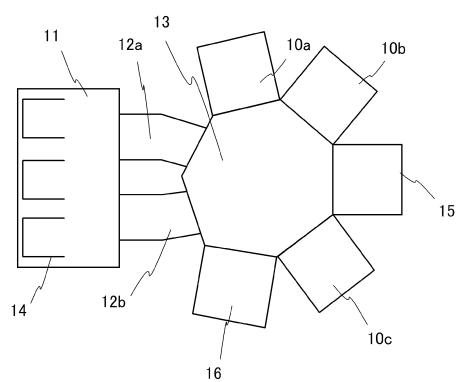

なお、3層の酸化物半導体層は、順次積層する工程を大気に触れることなく連続的に行う場合、図13に上面図を示す製造装置を用いればよい。

【0157】

図13に示す製造装置は、枚葉式マルチチャンバー設備であり、3つのスパッタ装置10a、10b、10cや、被処理基板を収容するカセットポート14を3つ有する基板供給室11や、ロードロック室12a、12bや、搬送室13や、基板加熱室15、16などを有している。なお、基板供給室11及び搬送室13には、被処理基板を搬送するための搬送ロボットがそれぞれ配置されている。スパッタ装置10a、10b、10c、搬送室

50

13、及び基板加熱室15、16は、水素及び水分をほとんど含まない雰囲気（不活性雰囲気、減圧雰囲気、乾燥空気雰囲気など）下に制御することが好ましく、例えば、水分については露点-40以下、好ましくは露点-50以下の乾燥窒素雰囲気とする。図13の製造装置を用いた作製工程の手順の一例は、まず、基板供給室11から被処理基板を搬送し、ロードロック室12aと搬送室13を経て基板加熱室15に移動させ、基板加熱室15で被処理基板に付着している水分を真空ベークなどで除去し、その後、搬送室13を経てスパッタ装置10cに被処理基板を移動させ、スパッタ装置10c内で第1の酸化物半導体層144aを成膜する。そして、大気に触れることなく、搬送室13を経てスパッタ装置10aに被処理基板を移動させ、スパッタ装置10a内で第2の酸化物半導体層144bを成膜する。そして、大気に触れることなく、搬送室13を経てスパッタ装置10bに被処理基板を移動させ、スパッタ装置10b内で第3の酸化物半導体層144cを成膜する。必要であれば、大気に触れることなく、搬送室13を経て基板加熱室16に被処理基板を移動させ、加熱処理を行う。このように、図13の製造装置を用いることによって大気に触れることなく、作製プロセスを進めることができる。また、図13の製造装置のスパッタ装置は、スパッタリングターゲットを変更することで大気に触れることのないプロセスを実現できる。また、図13の製造装置のスパッタ装置は、平行平板型スパッタリング装置、イオンビームスパッタリング装置、または対向ターゲット式スパッタリング装置などを用いればよい。対向ターゲット式スパッタリング装置は、被成膜面がプラスマから遠く、成膜ダメージが小さいため、結晶化度の高いC A A C - O S 膜を形成することができる。10

#### 【0158】

スパッタ装置10a、10b、10cでの酸化物半導体層の成膜において、成膜ガスとして、水素、水、水酸基又は水素化物などの不純物濃度が低い高純度ガスを用いる。

#### 【0159】

また、基板加熱室16は、減圧下、又は窒素、酸素、超乾燥エア（C R D S（キャビティリングダウンレーザー分光法）方式の露点計を用いて測定した場合の水分量が20ppm（露点換算で-55）以下、好ましくは1ppm以下、好ましくは10ppb以下の空気）、若しくは希ガス（アルゴン、ヘリウムなど）の雰囲気下として、加熱処理を行えばよいが、上記窒素、酸素、超乾燥エア、または希ガス等の雰囲気に水、水素などが含まれないことが好ましい。また、加熱処理装置に導入する窒素、酸素、または希ガスの純度を、6N（99.9999%）以上好ましくは7N（99.99999%）以上（即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下）とすることが好ましい。30

#### 【0160】

図4（B）に示すトランジスタ164は、第3の酸化物半導体層144cが第2の酸化物半導体層144bの上面及び側面並びに第1の酸化物半導体層144aの側面を覆う点はトランジスタ162と同様であるが、第3の酸化物半導体層144cがエッチングされ、第3の酸化物半導体層144cの端部がソース電極層142a及びドレイン電極層142bと重畳している点が異なる。このような構造によって、第2の酸化物半導体層144bの側面が第3の酸化物半導体層144cによって覆われ、かつ絶縁層140及びゲート絶縁層147が接する構造とすることができます。40

#### 【0161】

また、第2のトランジスタとして、ゲート電極層を2つ有する構造としてもよい。図5に、ゲート電極層を2つ有するトランジスタを示す。

#### 【0162】

図5（A）に示すトランジスタ172は、図1に示すトランジスタ162に加えて、ゲート電極層149を形成した構造である。ゲート電極層149は、配線層117と同一の導電膜で形成することができる。ゲート電極層148とゲート電極層149とに異なる電位を印加することで、トランジスタ172の閾値電圧を制御し、好ましくは、閾値電圧のマイナスシフトを抑制することができる。また、ゲート電極層148及びゲート電極層149に同電位を印加することで、トランジスタ172のオン電流を増加させることができる50

。

## 【0163】

図5(B)には、同様にトランジスタ163に加えて、ゲート電極層149を設けたトランジスタ173を示し、図5(C)には、トランジスタ164に加えてゲート電極層149を加えたトランジスタ174を示す。

## 【0164】

以上、本実施の形態の半導体装置は他の実施の形態の半導体装置と適宜組み合わせて用いることができる。

## 【0165】

## (実施の形態2)

10

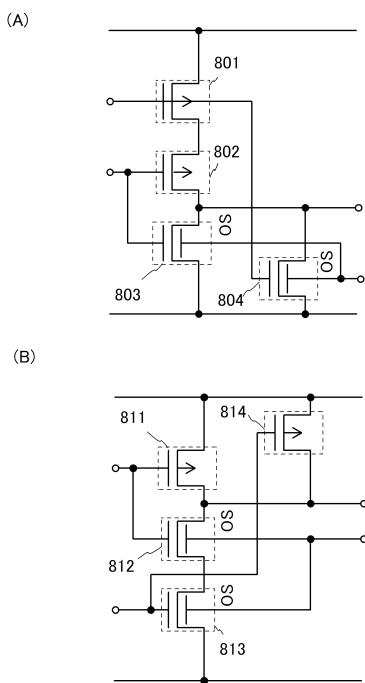

実施の形態1に示す半導体装置の一例として、論理回路であるNOR型回路の回路図の一例を図6(A)に示す。図6(B)はNAND型回路の回路図である。

## 【0166】

図6(A)に示すNOR型回路において、pチャネル型トランジスタであるトランジスタ801、802は、図1に示すトランジスタ160と同様な構造を有する、チャネル形成領域に単結晶シリコン基板を用いたトランジスタとし、nチャネル型トランジスタであるトランジスタ803、804は、図1に示すトランジスタ162、図4に示すトランジスタ163及びトランジスタ164、図5に示すトランジスタ172、トランジスタ173及びトランジスタ174と同様な構造を有するチャネル形成領域に酸化物半導体膜を用いたトランジスタを用いる。

20

## 【0167】

なお、図6(A)に示すNOR型回路において、トランジスタ803、804は、酸化物半導体膜を介して、ゲート電極層と重なる位置にトランジスタの電気的特性を形御する導電層を設けてもよい。該導電層の電位を制御し、例えばGNDとすることでトランジスタ803、804のしきい値電圧をよりプラスとし、さらにノーマリーオフのトランジスタとすることができます。

## 【0168】

また、図6(B)に示すNAND型回路では、pチャネル型トランジスタであるトランジスタ811、814は、図1に示すトランジスタ160と同様な構造を有し、nチャネル型トランジスタであるトランジスタ812、813は、図1に示すトランジスタ162、及び図4で示すトランジスタ163及びトランジスタ164、図5に示すトランジスタ172、トランジスタ173及びトランジスタ174と同様な構造を有するチャネル形成領域に酸化物半導体膜を用いたトランジスタを用いる。

30

## 【0169】

なお、図6(B)に示すNAND型回路において、トランジスタ812、813は、酸化物半導体膜を介して、ゲート電極層と重なる位置にトランジスタの電気的特性を制御する導電層を設けてもよい。該導電層の電位を制御し、例えばGNDとすることでトランジスタ812、813のしきい値電圧をよりプラスとし、さらにノーマリーオフのトランジスタとすることができます。

## 【0170】

40

本実施の形態に示す半導体装置では、チャネル形成領域に酸化物半導体を用いたオフ電流の極めて小さいトランジスタを適用することで、消費電力を十分に低減することができる。

## 【0171】

また、異なる半導体材料を用いた半導体素子を積層することにより、微細化及び高集積化を実現し、かつ安定で高い電気的特性を付与された半導体装置、及び該半導体装置の作製方法を提供することができる。

## 【0172】

また、実施の形態1に示す半導体装置を用いることで、酸化物半導体層に対する不純物元素の入り込みが抑制され、かつ酸化物半導体層の酸素欠損が低減された半導体装置を用い

50

ることによって、信頼性が高く、安定した特性を示すN O R型回路とN A N D型回路を提供することができる。

【0173】

また、本実施の形態では、実施の形態1に示すトランジスタを使用したN O R型回路とN A N D型回路の例を示したが、特に限定されず、実施の形態1に示すトランジスタを使用してA N D型回路やO R回路などを形成することができる。

【0174】

本実施の形態の半導体装置は、他の実施の形態に示す半導体装置と適宜組み合わせて用いることができる。

【0175】

10

(実施の形態3)

本実施の形態では、実施の形態1に示す半導体装置を使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置(記憶装置)の一例を、図面を用いて説明する。

【0176】

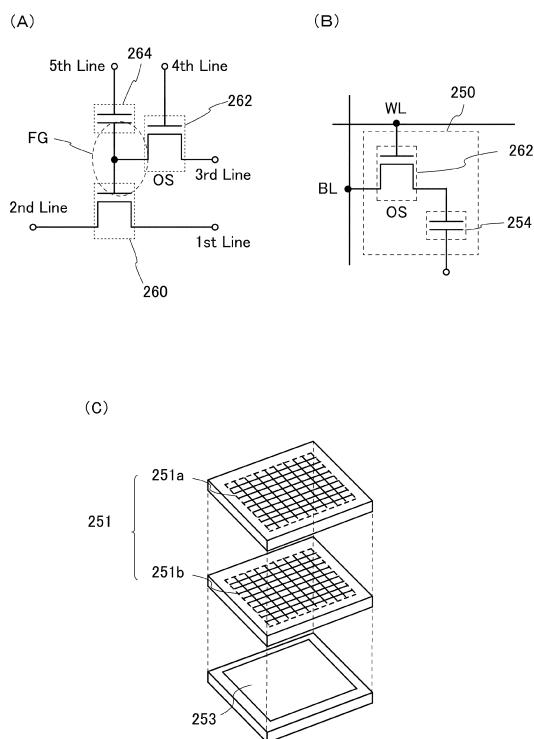

図7(A)は、本実施の形態の半導体装置を示す回路図である。

【0177】

20

図7(A)に示すトランジスタ260は、図1に示すトランジスタ160と同様の構造を適用することができ、高速動作が容易である。また、トランジスタ262には図1に示すトランジスタ162、図4に示すトランジスタ163、トランジスタ164、図5に示すトランジスタ172、トランジスタ173及びトランジスタ174と同様の構造を適用することができ、その特性により長時間の電荷保持を可能とする。

【0178】

なお、上記トランジスタは、いずれもnチャネル型トランジスタであるものとして説明するが、本実施の形態に示す半導体装置に用いるトランジスタとしては、pチャネル型トランジスタを用いることもできる。

【0179】

30

図7(A)において、第1の配線(1st Line)とトランジスタ260のソース電極層とは、電気的に接続され、第2の配線(2nd Line)とトランジスタ260のドレイン電極層とは、電気的に接続されている。また、第3の配線(3rd Line)とトランジスタ262のソース電極層又はドレイン電極層の一方とは、電気的に接続され、第4の配線(4th Line)と、トランジスタ262のゲート電極層とは、電気的に接続されている。そして、トランジスタ260のゲート電極層と、トランジスタ262のソース電極層又はドレイン電極層の他方は、容量素子264の電極の一方と電気的に接続され、第5の配線(5th Line)と、容量素子264の電極の他方は電気的に接続されている。

【0180】

図7(A)に示す半導体装置では、トランジスタ260のゲート電極層の電位が保持可能という特徴を生かすことで、次のように、情報の書き込み、保持、読み出しが可能である。

40

【0181】

情報の書き込みおよび保持について説明する。まず、第4の配線の電位を、トランジスタ262がオン状態となる電位にして、トランジスタ262をオン状態とする。これにより、第3の配線の電位が、トランジスタ260のゲート電極層、および容量素子264に与えられる。すなわち、トランジスタ260のゲート電極層には、所定の電荷が与えられる(書き込み)。ここでは、異なる二つの電位レベルを与える電荷(以下L o w レベル電荷、H i g h レベル電荷という)のいずれかが与えられるものとする。その後、第4の配線の電位を、トランジスタ262がオフ状態となる電位にして、トランジスタ262をオフ状態とすることにより、トランジスタ260のゲート電極層に与えられた電荷が保持される(保持)。

50

## 【0182】

トランジスタ262のオフ電流は極めて小さいため、トランジスタ260のゲート電極層の電荷は長時間にわたって保持される。

## 【0183】

次に情報の読み出しについて説明する。第1の配線に所定の電位（定電位）を与えた状態で、第5の配線に適切な電位（読み出し電位）を与えると、トランジスタ260のゲート電極層に保持された電荷量に応じて、第2の配線は異なる電位をとる。一般に、トランジスタ260をnチャネル型とすると、トランジスタ260のゲート電極層にHighレベル電荷が与えられている場合の見かけのしきい値 $V_{th\_H}$ は、トランジスタ260のゲート電極層にLowレベル電荷が与えられている場合の見かけのしきい値 $V_{th\_L}$ より低くなるためである。ここで、見かけのしきい値電圧とは、トランジスタ260を「オン状態」とするために必要な第5の配線の電位をいうものとする。したがって、第5の配線の電位を $V_{th\_H}$ と $V_{th\_L}$ の間の電位 $V_0$ とすることにより、トランジスタ260のゲート電極層に与えられた電荷を判別できる。例えば、書き込みにおいて、Highレベル電荷が与えられていた場合には、第5の配線の電位が $V_0$  ( $> V_{th\_H}$ ) となれば、トランジスタ260は「オン状態」となる。Lowレベル電荷が与えられていた場合には、第5の配線の電位が $V_0$  ( $< V_{th\_L}$ ) となっても、トランジスタ260は「オフ状態」のままである。このため、第2の配線の電位を見ることで、保持されている情報を読み出すことができる。

## 【0184】

なお、メモリセルをアレイ状に配置して用いる場合、所望のメモリセルの情報のみを読み出せることが必要になる。このように情報を読み出さない場合には、ゲート電極層の状態にかかわらずトランジスタ260が「オフ状態」となるような電位、つまり、 $V_{th\_H}$ より小さい電位を第5の配線に与えればよい。又は、ゲート電極層の状態にかかわらずトランジスタ260が「オン状態」となるような電位、つまり、 $V_{th\_L}$ より大きい電位を第5の配線に与えればよい。

## 【0185】

図7(B)に異なる記憶装置の構造の一形態の例を示す。図7(B)は、半導体装置の回路構成の一例を示し、図7(C)は半導体装置の一例を示す概念図である。まず、図7(B)に示す半導体装置について説明を行い、続けて図7(C)に示す半導体装置について、以下説明を行う。

## 【0186】

図7(B)に示す半導体装置において、ビット線BLとトランジスタ262のソース電極またはドレイン電極の一方とは電気的に接続され、ワード線WLとトランジスタ262のゲート電極層とは電気的に接続され、トランジスタ262のソース電極またはドレイン電極の他方と容量素子254の第1の端子とは電気的に接続されている。

## 【0187】

酸化物半導体を用いたトランジスタ262は、オフ電流が極めて小さいという特徴を有している。このため、トランジスタ262をオフ状態とすることで、容量素子254の第1の端子の電位（あるいは、容量素子254に蓄積された電荷）を極めて長時間にわたって保持することが可能である。

## 【0188】

次に、図7(B)に示す半導体装置（メモリセル250）に、情報の書き込み及び保持を行う場合について説明する。

## 【0189】

まず、ワード線WLの電位を、トランジスタ262がオン状態となる電位として、トランジスタ262をオン状態とする。これにより、ビット線BLの電位が、容量素子254の第1の端子に与えられる（書き込み）。その後、ワード線WLの電位を、トランジスタ262がオフ状態となる電位として、トランジスタ262をオフ状態とすることにより、容量素子254の第1の端子の電位が保持される（保持）。

10

20

30

40

50

## 【0190】

トランジスタ262のオフ電流は極めて小さいから、容量素子254の第1の端子の電位（あるいは容量素子に蓄積された電荷）を長時間にわたって保持することができる。

## 【0191】

次に、情報の読み出しについて説明する。トランジスタ262がオン状態となると、浮遊状態であるビット線BLと容量素子254とが導通し、ビット線BLと容量素子254の間で電荷が再分配される。その結果、ビット線BLの電位が変化する。ビット線BLの電位の変化量は、容量素子254の第1の端子の電位（あるいは容量素子254に蓄積された電荷）によって、異なる値をとる。

## 【0192】

例えば、容量素子254の第1の端子の電位をV、容量素子254の容量をC、ビット線BLが有する容量成分（以下、ビット線容量とも呼ぶ）をCB、電荷が再分配される前のビット線BLの電位をVB0とすると、電荷が再分配された後のビット線BLの電位は、 $(CB * VB0 + C * V) / (CB + C)$ となる。従って、メモリセル250の状態として、容量素子254の第1の端子の電位がV1とV0 ( $V1 > V0$ )の2状態をとるとすると、電位V1を保持している場合のビット線BLの電位 ( $= (CB * VB0 + C * V1) / (CB + C)$ )は、電位V0を保持している場合のビット線BLの電位 ( $= (CB * VB0 + C * V0) / (CB + C)$ )よりも高くなることがわかる。

## 【0193】

そして、ビット線BLの電位を所定の電位と比較することで、情報を読み出すことができる。

## 【0194】

このように、図7(B)に示す半導体装置は、トランジスタ262のオフ電流が極めて小さいという特徴から、容量素子254に蓄積された電荷は長時間にわたって保持することができる。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合であっても、長期にわたって記憶内容を保持することができる。

## 【0195】

次に、図7(C)に示す半導体装置について、説明を行う。

## 【0196】

図7(C)に示す半導体装置は、上部に記憶回路として図7(B)に示したメモリセル250を複数有するメモリセルアレイ251a及びメモリセルアレイ251bを有し、下部に、メモリセルアレイ251（メモリセルアレイ251a及びメモリセルアレイ251b）を動作させるために必要な周辺回路253を有する。なお、周辺回路253は、メモリセルアレイ251と電気的に接続されている。

## 【0197】

図7(C)に示した構成とすることにより、周辺回路253をメモリセルアレイ251（メモリセルアレイ251a及びメモリセルアレイ251b）の直下に設けることができるため半導体装置の小型化を図ることができる。

## 【0198】

周辺回路253に設けられるトランジスタは、トランジスタ262とは異なる半導体材料を用いるのがより好ましい。例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体を用いることが好ましい。他に、有機半導体材料などを用いてもよい。このような半導体材料を用いたトランジスタは、十分な高速動作が可能である。したがって、前記トランジスタにより、高速動作が要求される各種回路（論理回路、駆動回路など）を好適に実現することが可能である。

## 【0199】

なお、図7(C)に示した半導体装置では、2つのメモリセルアレイ251（メモリセル

10

20

30

40

50

アレイ 251a と、メモリセルアレイ 251b ) が積層された構成を例示したが、積層するメモリセルアレイの数はこれに限定されない。3つ以上のメモリセルアレイを積層する構成としても良い。

#### 【0200】

トランジスタ 262 として、酸化物半導体をチャネル形成領域に用いるトランジスタを適用することによって、長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作を必要としない、或いは、リフレッシュ動作の頻度が極めて少ない半導体記憶装置とすることが可能となるため、消費電力を十分に低減することができる。

#### 【0201】

また、本実施の形態に示す半導体装置として実施の形態 1 に示す、酸化物半導体層が積層され、チャネル形成領域となる第 2 の酸化物半導体層が酸化物半導体積層の表面から遠ざけられている半導体装置を適用することで、信頼性が高く、安定した電気特性を示す半導体装置とすることができます。

#### 【0202】

##### (実施の形態 4)

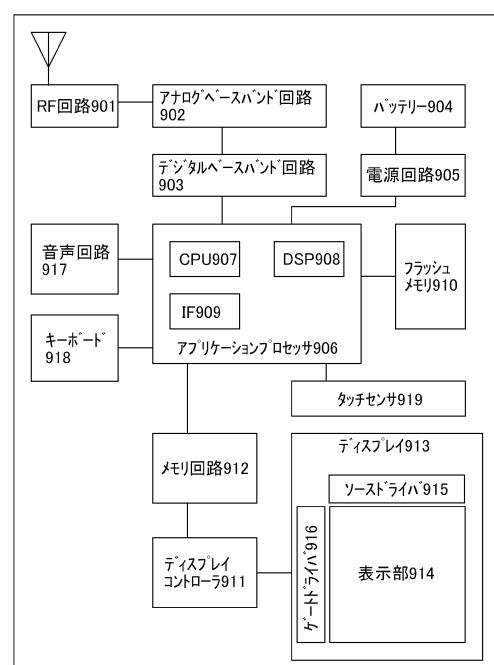

本実施の形態では、先の実施の形態で示した半導体装置を携帯電話、スマートフォン、電子書籍などの電子機器に応用した場合の例を図 8 乃至図 11 を用いて説明する。

#### 【0203】

図 8 に電子機器のブロック図を示す。図 8 に示す電子機器は R F 回路 901、アナログベースバンド回路 902、デジタルベースバンド回路 903、バッテリー 904、電源回路 905、アプリケーションプロセッサ 906、フラッシュメモリ 910、ディスプレイコントローラ 911、メモリ回路 912、ディスプレイ 913、タッチセンサ 919、音声回路 917、キーボード 918 などより構成されている。ディスプレイ 913 は表示部 914、ソースドライバ 915、ゲートドライバ 916 によって構成されている。アプリケーションプロセッサ 906 は C P U 907、D S P 908、インターフェイス ( I F ) 909 を有している。一般にメモリ回路 912 は S R A M または D R A M で構成されており、この部分に先の実施の形態で説明した半導体装置を採用することによって、情報の書き込み及び読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減された信頼性の高い電子機器を提供することができる。

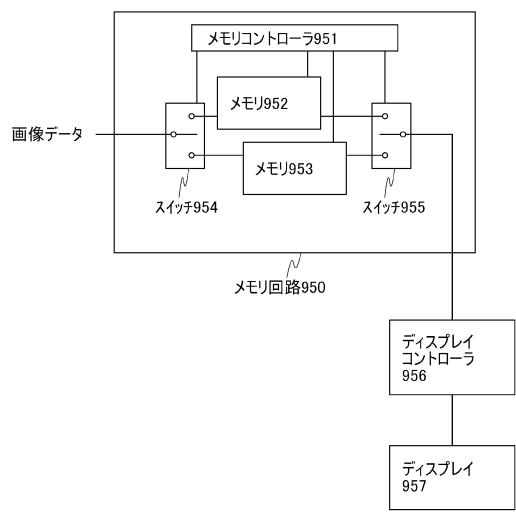

#### 【0204】

図 9 に、ディスプレイのメモリ回路 950 に先の実施の形態で説明した半導体装置を使用した例を示す。図 9 に示すメモリ回路 950 は、メモリ 952、メモリ 953、スイッチ 954、スイッチ 955 及びメモリコントローラ 951 により構成されている。また、メモリ回路は、信号線から入力された画像データ ( 入力画像データ ) 、メモリ 952 及びメモリ 953 に記憶されたデータ ( 記憶画像データ ) を読み出し、及び制御を行うディスプレイコントローラ 956 と、ディスプレイコントローラ 956 からの信号により表示するディスプレイ 957 が接続されている。

#### 【0205】

まず、ある画像データがアプリケーションプロセッサ ( 図示しない ) によって、形成される ( 入力画像データ A ) 。入力画像データ A は、スイッチ 954 を介してメモリ 952 に記憶される。そしてメモリ 952 に記憶された画像データ ( 記憶画像データ A ) は、スイッチ 955 、及びディスプレイコントローラ 956 を介してディスプレイ 957 に送られ、表示される。

#### 【0206】

入力画像データ A に変更が無い場合、記憶画像データ A は、通常 30 ~ 60 H z 程度の周期でメモリ 952 からスイッチ 955 を介して、ディスプレイコントローラ 956 から読み出される。

#### 【0207】

次に、例えばユーザーが画面を書き換える操作をしたとき ( すなわち、入力画像データ A に変更が有る場合 ) 、アプリケーションプロセッサは新たな画像データ ( 入力画像データ )

10

20

30

40

50

B)を形成する。入力画像データBはスイッチ954を介してメモリ953に記憶される。この間も定期的にメモリ952からスイッチ955を介して記憶画像データAは読み出されている。メモリ953に新たな画像データ(記憶画像データB)が記憶し終わると、ディスプレイ957の次のフレームより、記憶画像データBは読み出され、スイッチ955、及びディスプレイコントローラ956を介して、ディスプレイ957に記憶画像データBが送られ、表示がおこなわれる。この読み出しあはさらに次に新たな画像データがメモリ952に記憶されるまで継続される。

【0208】

このようにメモリ952及びメモリ953は交互に画像データの書き込みと、画像データの読み出しを行うことによって、ディスプレイ957の表示をおこなう。なお、メモリ952及びメモリ953はそれぞれ別のメモリには限定されず、1つのメモリを分割して使用してもよい。先の実施の形態で説明した半導体装置をメモリ952及びメモリ953に採用することによって、情報の書き込み及び読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減することができる。また、外部からの水、水分等の侵入の影響を受けにくい信頼性の高い半導体装置とすることができる。

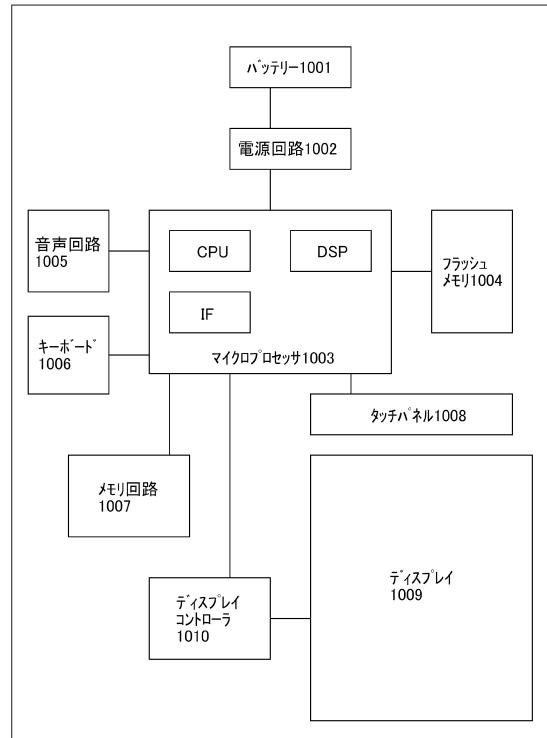

【0209】

図10に電子書籍のブロック図を示す。図10はバッテリー1001、電源回路1002、マイクロプロセッサ1003、フラッシュメモリ1004、音声回路1005、キーボード1006、メモリ回路1007、タッチパネル1008、ディスプレイ1009、ディスプレイコントローラ1010によって構成される。

【0210】

ここでは、図10のメモリ回路1007に先の実施の形態で説明した半導体装置を使用することができる。メモリ回路1007は書籍の内容を一時的に保持する機能を持つ。例えば、ユーザーがハイライト機能を使用する場合、メモリ回路1007は、ユーザーが指定した箇所の情報を記憶し、保持する。なおハイライト機能とは、ユーザーが電子書籍を読んでいるときに、特定の箇所にマーキング、例えば、表示の色を変える、アンダーラインを引く、文字を太くする、文字の書体を変えるなどによってマーキングして周囲との違いを示すことである。メモリ回路1007は短期的な情報の記憶に用い、長期的な情報の保存にはフラッシュメモリ1004に、メモリ回路1007が保持しているデータをコピーしてもよい。このような場合においても、先の実施の形態で説明した半導体装置を採用することによって、情報の書き込み及び読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力を十分に低減することができる。また、外部からの水、水分等の侵入の影響を受けにくい信頼性の高い半導体装置とすることができる。

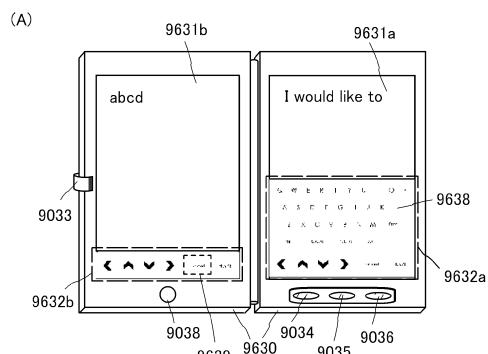

【0211】

図11に電子機器の具体例を示す。図11(A)及び図11(B)は、2つ折り可能なタブレット型端末である。図11(A)は、開いた状態であり、タブレット型端末は、筐体9630、表示部9631a、表示部9631b、表示モード切り替えスイッチ9034、電源スイッチ9035、省電力モード切り替えスイッチ9036、留め具9033、操作スイッチ9038を有する。

【0212】

実施の形態1に示す半導体装置は、表示部9631a、表示部9631bに用いることが可能であり、信頼性の高いタブレット型端末とすることが可能となる。また、先の実施の形態に示す記憶装置を本実施の形態の半導体装置に適用してもよい。

【0213】

表示部9631aは、一部をタッチパネルの領域9632aとすることでき、表示された操作キー9638にふれることでデータ入力をすることができる。なお、表示部9631aにおいては、一例として半分の領域が表示のみの機能を有する構成、もう半分の領域がタッチパネルの機能を有する構成を示しているが、該構成に限定されない。表示部9631aの全面をキーボードボタン表示させてタッチパネルとし、表示部9631bを表示画面として用いることができる。

10

20

30

40

50

## 【0214】

また、表示部 9631b においても表示部 9631a と同様に、表示部 9631b の一部をタッチパネルの領域 9632b とすることができます。また、タッチパネルのキーボード表示切り替えボタン 9639 が表示されている位置に指やスタイルスなどでふれることで表示部 9631b にキーボードボタン表示することができます。

## 【0215】

また、タッチパネルの領域 9632a とタッチパネルの領域 9632b に対して同時にタッチ入力することもできる。

## 【0216】

また、表示モード切り替えスイッチ 9034 は、縦表示または横表示などの表示の向きを切り替え、白黒表示やカラー表示の切り替えなどを選択できる。省電力モード切り替えスイッチ 9036 は、タブレット型端末に内蔵している光センサで検出される使用時の外光の光量に応じて表示の輝度を最適なものとすることができます。タブレット型端末は光センサだけでなく、ジャイロ、加速度センサ等の傾きを検出するセンサなどの他の検出装置を内蔵させてもよい。

10

## 【0217】

また、図 11 (A) では表示部 9631b と表示部 9631a の表示面積が同じ例を示しているが特に限定されず、一方のサイズともう一方のサイズが異なっていてもよく、表示の品質も異なっていてもよい。例えば一方が他方よりも高精細な表示を行える表示パネルとしてもよい。

20

## 【0218】

図 11 (B) は、閉じた状態であり、タブレット型端末は、筐体 9630、太陽電池 9633、充放電制御回路 9634、バッテリー 9635、DCDC コンバータ 9636 を有する。なお、図 11 (B) では充放電制御回路 9634 の一例としてバッテリー 9635、DCDC コンバータ 9636 を有する構成について示している。

## 【0219】

なお、タブレット型端末は 2 つ折り可能なため、未使用時に筐体 9630 を閉じた状態にすることができる。従って、表示部 9631a、表示部 9631b を保護できるため、耐久性に優れ、長期使用の観点からも信頼性の優れたタブレット型端末を提供できる。

30

## 【0220】

また、この他にも図 11 (A) および図 11 (B) に示したタブレット型端末は、様々な情報（静止画、動画、テキスト画像など）を表示する機能、カレンダー、日付または時刻などを表示部に表示する機能、表示部に表示した情報をタッチ入力操作または編集するタッチ入力機能、様々なソフトウェア（プログラム）によって処理を制御する機能、等を有することができる。

## 【0221】

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

## 【符号の説明】

## 【0222】

40

|      |         |

|------|---------|

| 100  | 基板      |

| 102  | 素子分離絶縁層 |

| 104  | 絶縁層     |

| 108  | ゲート絶縁層  |

| 110  | ゲート電極層  |

| 112  | 配線層     |

| 114  | 配線層     |

| 115  | 配線層     |

| 115a | 配線層     |

| 115b | 配線層     |

50

|         |               |    |

|---------|---------------|----|

| 1 1 5 c | 配線層           |    |

| 1 1 6   | 配線層           |    |

| 1 1 7   | 配線層           |    |

| 1 2 0   | 絶縁層           |    |

| 1 3 5   | 絶縁層           |    |

| 1 4 0   | 絶縁層           |    |

| 1 4 2 a | ソース電極層        |    |

| 1 4 2 b | ドレイン電極層       |    |

| 1 4 4   | 酸化物半導体積層      | 10 |

| 1 4 4 a | 酸化物半導体層       |    |

| 1 4 4 b | 酸化物半導体層       |    |

| 1 4 4 c | 酸化物半導体層       |    |

| 1 4 7   | ゲート絶縁層        |    |

| 1 4 7 a | ゲート絶縁層        |    |

| 1 4 7 b | ゲート絶縁層        |    |

| 1 4 8   | ゲート電極層        |    |

| 1 4 9   | ゲート電極層        |    |

| 1 5 0   | 絶縁層           |    |

| 1 5 5   | 絶縁層           |    |

| 1 6 0   | トランジスタ        | 20 |

| 1 6 2   | トランジスタ        |    |

| 1 6 3   | トランジスタ        |    |

| 1 6 4   | トランジスタ        |    |

| 1 7 2   | トランジスタ        |    |

| 1 7 3   | トランジスタ        |    |

| 1 7 4   | トランジスタ        |    |

| 2 5 0   | メモリセル         |    |

| 2 5 1   | メモリセルアレイ      |    |

| 2 5 1 a | メモリセルアレイ      |    |

| 2 5 1 b | メモリセルアレイ      | 30 |

| 2 5 3   | 周辺回路          |    |

| 2 5 4   | 容量素子          |    |

| 2 6 0   | トランジスタ        |    |

| 2 6 2   | トランジスタ        |    |

| 2 6 4   | 容量素子          |    |

| 8 0 1   | トランジスタ        |    |

| 8 0 2   | トランジスタ        |    |

| 8 0 3   | トランジスタ        |    |

| 8 0 4   | トランジスタ        |    |

| 8 1 1   | トランジスタ        | 40 |

| 8 1 2   | トランジスタ        |    |

| 8 1 3   | トランジスタ        |    |

| 8 1 4   | トランジスタ        |    |

| 9 0 1   | R F 回路        |    |

| 9 0 2   | アナログベースバンド回路  |    |

| 9 0 3   | デジタルベースバンド回路  |    |

| 9 0 4   | パッテリー         |    |

| 9 0 5   | 電源回路          |    |

| 9 0 6   | アプリケーションプロセッサ |    |

| 9 0 7   | C P U         | 50 |

|           |               |    |

|-----------|---------------|----|

| 9 0 8     | D S P         |    |

| 9 1 0     | フラッシュメモリ      |    |

| 9 1 1     | ディスプレイコントローラ  |    |

| 9 1 2     | メモリ回路         |    |

| 9 1 3     | ディスプレイ        |    |

| 9 1 4     | 表示部           |    |

| 9 1 5     | ソースドライバ       | 10 |

| 9 1 6     | ゲートドライバ       |    |

| 9 1 7     | 音声回路          |    |

| 9 1 8     | キーボード         |    |

| 9 1 9     | タッチセンサ        |    |

| 9 5 0     | メモリ回路         |    |

| 9 5 1     | メモリコントローラ     |    |

| 9 5 2     | メモリ           |    |

| 9 5 3     | メモリ           |    |

| 9 5 4     | スイッチ          |    |

| 9 5 5     | スイッチ          |    |

| 9 5 6     | ディスプレイコントローラ  |    |

| 9 5 7     | ディスプレイ        |    |

| 1 0 0 1   | バッテリー         | 20 |

| 1 0 0 2   | 電源回路          |    |

| 1 0 0 3   | マイクロプロセッサ     |    |

| 1 0 0 4   | フラッシュメモリ      |    |

| 1 0 0 5   | 音声回路          |    |

| 1 0 0 6   | キーボード         |    |

| 1 0 0 7   | メモリ回路         |    |

| 1 0 0 8   | タッチパネル        |    |

| 1 0 0 9   | ディスプレイ        |    |

| 1 0 1 0   | ディスプレイコントローラ  |    |

| 9 0 3 3   | 留め具           | 30 |

| 9 0 3 4   | スイッチ          |    |

| 9 0 3 5   | 電源スイッチ        |    |

| 9 0 3 6   | スイッチ          |    |

| 9 0 3 8   | 操作スイッチ        |    |

| 9 6 3 0   | 筐体            |    |

| 9 6 3 1 a | 表示部           |    |

| 9 6 3 1 b | 表示部           |    |

| 9 6 3 2 a | 領域            |    |

| 9 6 3 2 b | 領域            |    |

| 9 6 3 3   | 太陽電池          | 40 |

| 9 6 3 4   | 充放電制御回路       |    |

| 9 6 3 5   | バッテリー         |    |

| 9 6 3 6   | D C D C コンバータ |    |

| 9 6 3 8   | 操作キー          |    |

| 9 6 3 9   | ボタン           |    |

【図1】

【図2】

【図3】

(B)

【図4】

(B)

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

## フロントページの続き

| (51)Int.Cl. |       | F I                    |

|-------------|-------|------------------------|

| C 2 3 C     | 14/08 | H 0 1 L 29/78 6 1 8 G  |

|             |       | H 0 1 L 29/78 6 2 7 F  |

|             |       | H 0 1 L 27/108 3 2 1   |

|             |       | H 0 1 L 27/108 6 2 1 Z |

|             |       | H 0 1 L 27/108 6 7 1 Z |

|             |       | H 0 1 L 27/108 6 8 1 A |

|             |       | H 0 1 L 27/108 6 8 1 B |

|             |       | H 0 1 L 27/108 6 8 1 E |

|             |       | H 0 1 L 27/108 6 8 1 F |

|             |       | H 0 1 L 27/10 4 6 1    |

|             |       | C 2 3 C 14/08 K        |

|             |       | H 0 1 L 29/78 6 1 7 N  |

(56)参考文献 特開2012-054547 (JP, A)

特開2011-243745 (JP, A)

特開2012-084851 (JP, A)

特開2012-151461 (JP, A)

特開2012-134475 (JP, A)

特開2011-119720 (JP, A)

特開2011-228695 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L 2 9 / 7 8 6

C 2 3 C 1 4 / 0 8

H 0 1 L 2 1 / 3 3 6

H 0 1 L 2 1 / 8 2 4 2

H 0 1 L 2 7 / 1 0

H 0 1 L 2 7 / 1 0 8