(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6022153号

(P6022153)

(45) 発行日 平成28年11月9日(2016.11.9)

(24) 登録日 平成28年10月14日(2016.10.14)

(51) Int.Cl.

F 1

G 11 C 16/02 (2006.01)

G 11 C 16/06 (2006.01)G 11 C 17/00 6 1 3

G 11 C 17/00 6 1 1 E

G 11 C 17/00 6 3 3 B

G 11 C 17/00 6 3 3 D

請求項の数 6 (全 24 頁)

(21) 出願番号 特願2011-257510 (P2011-257510)

(22) 出願日 平成23年11月25日 (2011.11.25)

(65) 公開番号 特開2012-113810 (P2012-113810A)

(43) 公開日 平成24年6月14日 (2012.6.14)

審査請求日 平成26年9月22日 (2014.9.22)

(31) 優先権主張番号 10-2010-0117950

(32) 優先日 平成22年11月25日 (2010.11.25)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 129

129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic

of Korea

(74) 代理人 100110364

弁理士 実広 信哉

(72) 発明者 崔允熙

大韓民国京畿道華城市石隅洞 (番地なし)

ドンタンイエダンマウルブルジオアパート 105 棟 501 号

最終頁に続く

(54) 【発明の名称】フラッシュメモリ装置及びそれを含むデータ格納装置

## (57) 【特許請求の範囲】

## 【請求項 1】

動作電圧発生器と不揮発性メモリセルのメモリセルアレイとを含む不揮発性メモリ装置を含むメモリシステムで動作電圧を発生する方法において、

前記メモリセルアレイのトリム情報領域にトリム情報を格納する段階と、

前記不揮発性メモリ装置のパワーアップの時、前記トリム情報を用いて、複数のオフセット値を格納するルックアップテーブルを構成する段階と、

前記不揮発性メモリ装置の現在温度を検出する段階と、

前記不揮発性メモリ装置によるアクセス命令に関連するアクセス動作の実行を開始する前記アクセス命令を入力した後、前記現在温度に応答して前記ルックアップテーブルに格納された前記複数のオフセット値の中から第1オフセット値と第2オフセット値を選択することによって補償された動作電圧を発生する段階と、

前記補償された動作電圧を利用して前記アクセス動作を遂行する段階と、を含み、

前記補償された動作電圧を発生する段階は、

前記選択された前記第1オフセット値と前記第2オフセット値を利用して補償オフセット値を発生する段階と、

前記動作電圧発生器を利用して前記補償オフセット値にしたがって前記補償された動作電圧を発生する段階と、を含み、

前記補償オフセット値を発生する段階は、

前記現在温度に応答して前記複数のオフセット値の中から前記第1オフセット値を選択

10

20

する段階と、

前記現在温度と選択されたメモリセルのプログラム状態、あるいは少なくとも前記選択されたメモリセルに対応するワードラインの位置のうち少なくともいずれか一方に応答して前記複数のオフセット値の中から前記第2オフセット値を選択する段階と、

前記第1オフセット値と前記第2オフセット値とに基づいて前記補償オフセット値を発生する段階と、を含むことを特徴とする方法。

#### 【請求項2】

前記第2オフセット値を選択する段階は、

前記現在温度と前記選択されたメモリセルのプログラム状態、あるいは前記現在温度と前記選択されたメモリセルに対応するワードライン位置のうち少なくともいずれか一方に応答して前記複数のオフセット値の中から前記第2オフセット値を選択する、

ことを特徴とする請求項1に記載の方法。

10

#### 【請求項3】

不揮発性メモリ装置において、

前記不揮発性メモリ装置の動作を制御する制御ロジックと、

不揮発性メモリセルのメモリセルアレイと、

前記メモリセルアレイに属する選択されたメモリセルに関連する選択されたワードラインに印加される補償された動作電圧を発生する動作電圧発生器と、を含み、

前記動作電圧発生器は、

現在温度を検出し対応する温度コードの発生する温度コード発生器と、

20

各温度範囲に各々対応する複数の第1オフセット値を格納する第1ルックアップテーブルと、

前記温度コードと選択されたメモリセルのプログラム状態、あるいは少なくとも前記選択されたメモリセルに対応するワードラインの位置のうち少なくともいずれか一方に対応する複数の第2オフセット値を格納する第2ルックアップテーブルと、を含み、

前記制御ロジックは、前記温度コードに応答して前記複数の第1オフセット値の中から1つ、及び前記温度コードと前記選択されたメモリセルのプログラム状態、あるいは少なくとも前記選択されたメモリセルに対応するワードラインの位置のうち少なくともいずれか一方に応答して前記複数の第2オフセット値の中から1つを選択し、

前記動作電圧発生器は、前記複数の第1オフセット値の選択された1つと前記複数の第2オフセット値の選択された1つとに応答して前記補償された動作電圧を発生する不揮発性メモリ装置。

30

#### 【請求項4】

前記制御ロジックは、

前記現在温度と前記選択されたメモリセルのプログラム状態、あるいは前記現在温度と前記選択されたメモリセルに対応するワードライン位置のうち少なくともいずれか一方に応答して前記複数の第2オフセット値の中から1つを選択する、

ことを特徴とする請求項3に記載の不揮発性メモリ装置。

#### 【請求項5】

少なくとも1つの不揮発性メモリ装置と、

40

バッファーメモリを含み、前記少なくとも1つの不揮発性メモリ装置を制御するように構成された制御器と、

前記制御器と外部装置との間で通信を行うインターフェイスと、を含み、

前記少なくとも1つの不揮発性メモリ装置は、

前記少なくとも1つの不揮発性メモリ装置の動作を制御する制御ロジックと、

不揮発性メモリセルのメモリセルアレイと、

前記メモリセルアレイに属する選択されたメモリセルに対応するワードラインに印加される補償された動作電圧を発生する動作電圧発生器と、を含み、

前記動作電圧発生器は、

現在温度を検出し対応する温度コードの発生する温度コード発生器と、

50

各温度範囲に各々対応する複数の第1オフセット値を格納する第1ルックアップテーブルと、

前記温度コードと選択されたメモリセルのプログラム状態、あるいは少なくとも前記選択されたメモリセルに対応するワードラインの位置のうち少なくともいづれか一方に対応する複数の第2オフセット値を格納する第2ルックアップテーブルと、を含み、

前記制御ロジックは、前記温度コードに応答して前記複数の第1オフセット値の中から1つ、及び前記温度コードと前記選択されたメモリセルのプログラム状態、あるいは少なくとも前記選択されたメモリセルに対応するワードラインの位置のうち少なくともいづれか一方に応答して前記複数の第2オフセット値の中から1つを選択し、

前記動作電圧発生器は、前記複数の第1オフセット値の選択された1つと前記複数の第2オフセット値の選択された1つとに応答して前記補償された動作電圧を発生するメモリカード。

#### 【請求項6】

前記制御ロジックは、

前記温度コードと前記選択されたメモリセルのプログラム状態、あるいは前記温度コードと前記選択されたメモリセルに対応するワードライン位置のうち少なくともいづれか一方に応答して前記複数の第2オフセット値の中から1つを選択する、

ことを特徴とする請求項5に記載のメモリカード。

#### 【発明の詳細な説明】

##### 【技術分野】

20

##### 【0001】

本発明は半導体メモリ装置に関し、より具体的にはフラッシュメモリ装置及びそれを含むデータ格納装置に関する。

##### 【背景技術】

##### 【0002】

半導体メモリは、一般的に、衛星から消費者電子技術までの範囲に属するマイクロプロセッサーを基盤にする応用及びコンピューターのようなデジタルロジック設計の最も必須的なマイクロ電子素子である。したがって、高い集積度及び速い速度のための縮小(scaling)を通じて得られるプロセス向上及び技術開発を含む半導体メモリの製造技術の進歩は他のデジタルロジック系列の性能基準を確立するのに役に立つ。

30

##### 【0003】

半導体メモリ装置は大きく揮発性半導体メモリ装置と不揮発性半導体メモリ装置とに分けられる。揮発性半導体メモリ装置において、ロジック情報はスタティックランダムアクセスメモリの場合、双安定フリップフロップのロジック状態を設定することによって、又はダイナミックランダムアクセスメモリの場合、キャパシターの充電を通じて格納される。揮発性半導体メモリ装置の場合、電源が印加される間にデータが格納され、読み出され、電源が遮断される時、データは消失される。

##### 【0004】

MROM、PROM、EPROM、EEPROM等のような不揮発性半導体メモリ装置は電源が遮断されてもデータを格納できる。不揮発性メモリデータ格納状態は使用される製造技術によって永久的に格納できるか、或いは再プログラムできる。不揮発性半導体メモリ装置はコンピューター、航行電子工学、通信、及び消費者電子技術産業のような広い範囲の応用でプログラム及びマイクロコードに格納のために使用される。单一チップで揮発性及び不揮発性メモリ格納モードの組合が速くて再プログラムできる不揮発性メモリを要求するシステムで不揮発性RAM(nvRAM)のような装置でまた使用できる。その上に、応用指向業務のための性能を最適化させるために幾つかの追加的なロジック回路を含む特定メモリ構造が開発してきた。

##### 【0005】

不揮発性半導体メモリ装置において、MROM、PROM及びEPROMはシステム自体的に消去及び書き込みが容易でないので、一般の使用者が記憶内容を新しくするのが容易

40

50

でない。これに反して、EEPROMは電気的に消去及び書き込みが可能であるので、継続的な更新が必要であるシステムプログラミング(system programming)や補助記憶装置としての応用が拡大されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】韓国公開特許第10-2010-0049924号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の目的は、信頼性を向上させることができるフラッシュメモリ装置及びそれを含むデータ格納装置を提供するものである。

【課題を解決するための手段】

【0008】

一実施形態において、本発明は不揮発性メモリセルのメモリセルアレイを含む不揮発性メモリ装置で動作電圧を発生する方法を提供し、前記方法は前記不揮発性メモリ装置の現在温度を含む少なくとも1つのメモリセル条件を検出する段階と、前記メモリセルアレイの選択されたメモリセルに印加される動作電圧を発生する段階と、前記少なくとも1つのメモリセル条件に応答して前記動作電圧を補償する段階と、を含む。

【0009】

他の実施形態において、本発明は動作電圧発生器と不揮発性メモリセルのメモリセルアレイを含む不揮発性メモリ装置とを含むメモリシステムで動作電圧を発生する方法を提供し、前記方法は前記メモリセルアレイのトリム情報領域にトリム情報を格納する段階と、前記不揮発性メモリ装置のパワーアップの時、そして前記トリム情報の使用の時、複数の補償オフセット値を格納する少なくとも1つのルックアップテーブルを構成する段階と、前記不揮発性メモリ装置の現在温度を検出する段階と、前記不揮発性メモリ装置によるアクセス動作の実行を開始するアクセス命令を入力した後、前記現在温度に応答して前記少なくとも1つのルックアップテーブルに格納された複数の補償オフセット値の中で1つのオフセット値を選択することによって補償された動作電圧を発生する段階と、前記補償された動作電圧を利用して前記アクセス動作を遂行する段階と、を含む。

【0010】

他の実施形態において、本発明は前記不揮発性メモリ装置の動作を制御する制御ロジックと、不揮発性メモリセルのメモリセルアレイと、前記メモリセルアレイに属する選択されたメモリセルに印加される補償された動作電圧を発生する動作電圧発生器と、を含み、前記動作電圧発生器は現在温度を検出し対応する温度コードの発生する温度コード発生器と、複数の温度範囲に各々対応する複数の第1オフセット値を格納する第1ルックアップテーブルと、メモリセル条件の変化に各々対応する複数の第2オフセット値を格納する第2ルックアップテーブルと、を含み、前記制御ロジックは、前記温度コードに応答して前記第1オフセット値の中で1つ、及び前記メモリセル条件の決定された変化に応答して前記第2オフセット値の中で1つを選択し、前記動作電圧発生器は、前記第1オフセット値と前記第2オフセット値とに応答して前記補償された動作電圧を発生する不揮発性メモリ装置を提供する。

【0011】

他の実施形態において、本発明は少なくとも1つの不揮発性メモリ装置と、バッファーメモリを含み、前記不揮発性メモリ装置を制御するように構成された制御器と、前記制御器と外部装置間のインターフェイスを提供するインターフェイスと、を含み、前記少なくとも1つの不揮発性メモリ装置は前記少なくとも1つの不揮発性メモリ装置の動作を制御する制御ロジックと、不揮発性メモリセルのメモリセルアレイと、前記メモリセルアレイに属する選択されたメモリセルに印加される補償された動作電圧を発生する動作電圧発生器と、を含み、前記動作電圧発生器は現在温度を検出し対応する温度コードの発生する温

10

20

30

40

50

度コード発生器と、複数の温度範囲に各々対応する複数の第1オフセット値を格納する第1ルックアップテーブルと、メモリセル条件の変化に各々対応する複数の第2オフセット値を格納する第2ルックアップテーブルと、を含み、前記制御ロジックは、前記温度コードに応答して前記第1オフセット値の中で1つ、及び前記メモリセル条件の決定された変化に応答して前記第2オフセット値の中で1つを選択し、前記動作電圧発生器は、前記第1オフセット値と前記第2オフセット値とに応答して前記補償された動作電圧を発生するメモリカードを提供する。

#### 【0012】

他の実施形態において、本発明は複数の不揮発性メモリ装置を含む格納媒体と、複数のチャンネルを通じて前記格納媒体と連結され、前記格納媒体を制御するように構成された制御器と、を含み、前記複数の不揮発性メモリ装置の中で少なくとも1つは前記不揮発性メモリ装置の動作を制御する制御ロジックと、不揮発性メモリセルのメモリセルアレイと、前記メモリセルアレイに属する選択されたメモリセルに印加される補償された動作電圧を発生する動作電圧発生器と、を含み、前記動作電圧発生器は現在温度を検出し対応する温度コードの発生する温度コード発生器と、複数の温度範囲に各々対応する複数の第1オフセット値を格納する第1ルックアップテーブルと、メモリセル条件の変化に各々対応する複数の第2オフセット値を格納する第2ルックアップテーブルと、を含み、前記制御ロジックは、前記温度コードに応答して前記第1オフセット値の中で1つ、及び前記メモリセル条件の決定された変化に応答して前記第2オフセット値の中で1つを選択し、前記動作電圧発生器は、前記第1オフセット値と前記第2オフセット値とに応答して前記補償された動作電圧を発生する半導体ドライブを提供する。

10

#### 【発明の効果】

#### 【0013】

本発明の例示的な実施形態によれば、温度変化の時、多様な条件（例えば、プログラム状態、ワードライン位置、ページ情報、温度領域、等）にしたがってメモリセルに印加される電圧を補償することによって、メモリセルの閾値電圧を正確に判別できる。

#### 【図面の簡単な説明】

#### 【0014】

【図1】本発明の例示的な実施形態による電圧補償方式を概略的に説明するための図面である。

30

【図2A】メモリセルの閾値電圧の変化を発生させる多様な条件を説明するための図面である。

【図2B】メモリセルの閾値電圧の変化を発生させる多様な条件を説明するための図面である。

【図2C】メモリセルの閾値電圧の変化を発生させる多様な条件を説明するための図面である。

【図2D】メモリセルの閾値電圧の変化を発生させる多様な条件を説明するための図面である。

【図3】本発明の例示的な実施形態による不揮発性メモリ装置の動作を概略的に説明するためのフローチャートである。

40

【図4】図1で説明された電圧補償方式が適用される本発明の例示的な実施形態によるフラッシュメモリ装置を概略的に示すブロック図である。

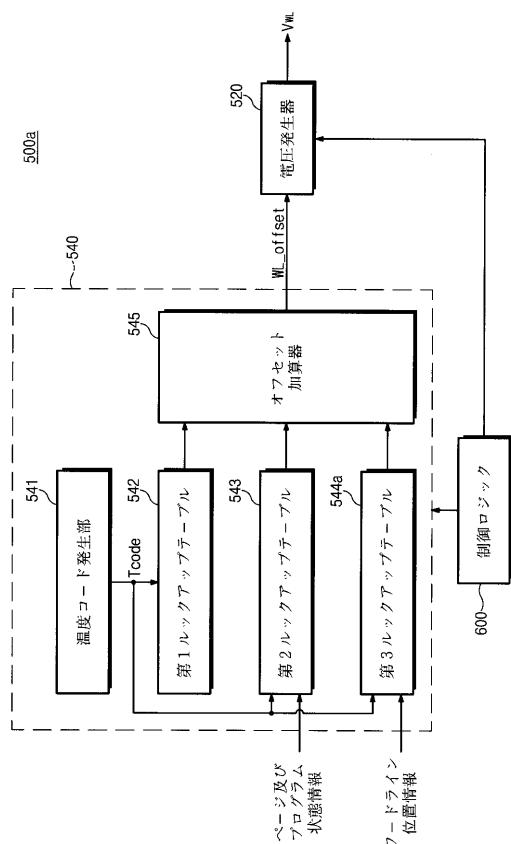

【図5A】図4に示された本発明の例示的な実施形態によるワードライン電圧発生回路を概略的に示すブロック図である。

【図5B】図4に示された本発明の他の例示的な実施形態によるワードライン電圧発生回路を概略的に示すブロック図である。

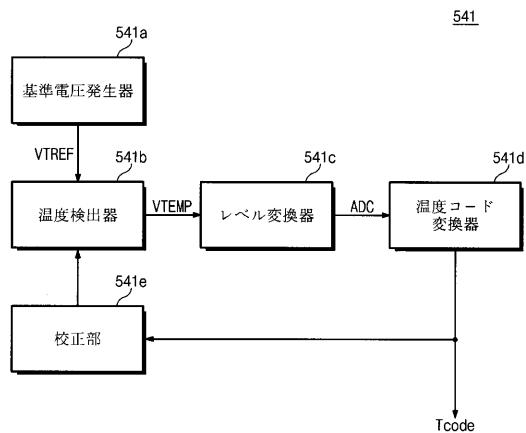

【図6】図5に示された温度コード発生部を概略的に示すブロック図である。

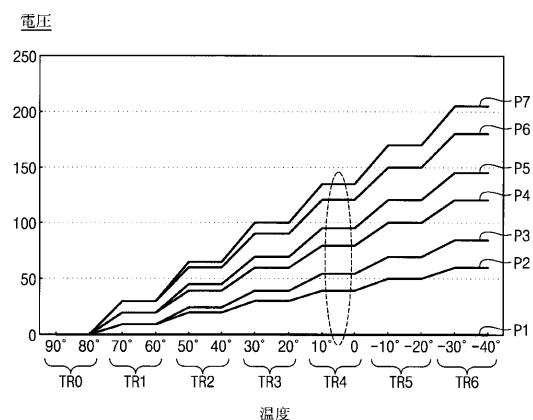

【図7A】図5で説明された第2ルックアップテーブルに含まれるオフセット値を説明するための図面である。

【図7B】図5で説明された第2ルックアップテーブルに含まれるオフセット値を説明す

50

るための図面である。

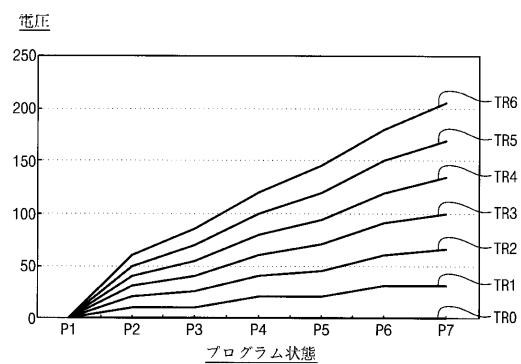

【図 8】本発明の例示的な実施形態によるフラッシュメモリ装置に適用された電圧補償方法を説明するための図面である。

【図 9】本発明の例示的な実施形態による不揮発性メモリ装置を含むデータ格納装置を概略的に示すブロック図である。

【図 10】本発明の例示的な実施形態による図 9 に示された制御器を概略的に示すプロック図である。

【図 11】本発明の例示的な実施形態による不揮発性メモリ装置を利用する半導体ドライブを概略的に示すブロック図である。

【図 12】図 11 に示された半導体ドライブを利用するストレージを概略的に示すプロック図である。10

【図 13】図 11 に示された半導体ドライブを利用するストレージサーバーを概略的に示すプロック図である。

【図 14】本発明の例示的な実施形態によるデータ格納装置が適用されるシステムを概略的に示す図面である。

【図 15】本発明の例示的な実施形態によるデータ格納装置が適用されるシステムを概略的に示す図面である。

【図 16】本発明の例示的な実施形態によるデータ格納装置が適用されるシステムを概略的に示す図面である。20

【図 17】本発明の例示的な実施形態による不揮発性メモリ装置が適用される他のシステムを概略的に示す図面である。

【図 18】本発明の例示的な実施形態による不揮発性メモリ装置が適用される他のシステムを概略的に示す図面である。

【図 19】本発明の例示的な実施形態による不揮発性メモリ装置が適用される他のシステムを概略的に示す図面である。

【図 20】本発明の例示的な実施形態による不揮発性メモリ装置が適用される他のシステムを概略的に示す図面である。

【図 21】本発明の例示的な実施形態による不揮発性メモリ装置が適用される他のシステムを概略的に示す図面である。30

#### 【発明を実施するための形態】

##### 【0015】

本発明の長所及び特徴、及びそれを達成する方法は添付される図面と共に詳細に後述されている実施形態を通じて説明される。しかし、本発明はここで説明される実施形態に限定されることなく他の形態に具体化できる。本実施形態は、単に本発明が属する技術分野で通常の知識を有する者に本発明の技術的思想を容易に実施できるように詳細に説明するために提供される。

##### 【0016】

図面において、本発明の実施形態は図示された特定形態に制限されることではなく説明を明確するために誇張されている。また明細書全体に掛けて同一な参照番号に表示された部分は同一な構成要素を示す。40

##### 【0017】

本明細書で‘及び／又は’という表現は前後に並べた構成要素の中で少なくとも1つを含む意味に使用される。また、‘連結される／結合される’という表現は他の構成要素と直接的に連結されたか、或いは他の構成要素を通じて間接的に連結されることを含む意味に使用される。本明細書で单数形は文句で特別に言及しない限り複数形も含む。また、明細書で使用される‘含む’又は‘包含する’で言及された構成要素、段階、動作及び素子は1つ以上の他の構成要素、段階、動作、素子及び装置の存在又は追加を意味する。

##### 【0018】

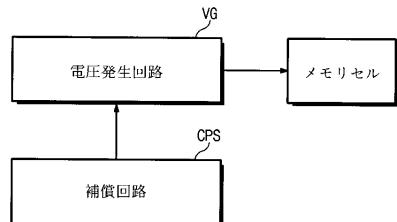

図1は本発明の例示的な実施形態による電圧補償方式を概略的に説明するための図面である。50

## 【0019】

図1を参照すれば、本発明の例示的な実施形態による電圧補償方式は半導体メモリ装置に適用される。具体的には、本発明の例示的な実施形態による電圧補償方式は不揮発性メモリ装置に適用される。不揮発性メモリ装置はデータ情報を格納するためのメモリセル（又は、不揮発性メモリセル）を含む。データ情報は単一ビットデータ又はマルチビットデータである。メモリセルの各々は格納されるデータ状態（又は、プログラム状態）にしたがって可変できる閾値電圧又は可変できる抵抗を有するセルトランジスターで構成される。メモリセルは複数の行（例えば、複数のワードライン）と複数の列（又は、ビットライン）とに配列される。メモリセルは2次元構造（two-dimensional structure）を有するように又は3次元構造（three-dimensional structure）を有するように配列される。10

## 【0020】

本発明の例示的な実施形態による不揮発性メモリ装置は電圧発生回路VGと補償回路CPSとをさらに含む。電圧発生回路VGはメモリセルへ供給される複数の電圧（例えば、ワードライン電圧、ウェル電圧、等）を発生するように構成される。補償回路CPSは、温度変化の時、多様な条件（又は、基準）にしたがって変化されるように電圧発生回路VGから出力される電圧を補償する。例えば、メモリセルの閾値電圧／抵抗は温度変化にしたがって変化される。仮にメモリセルに供給される電圧（例えば、ワードライン電圧）が温度変化に関わらず固定されれば、温度変化の時、メモリセルの閾値電圧を正確に判別することが難しい。20

## 【0021】

本発明の例示的な実施形態による補償回路CPSは、温度変化に比例して自動的に変化されるように電圧発生回路VGから出力される電圧を補償する。その上に、本発明の例示的な実施形態による補償回路CPSは、選択されたメモリセルのプログラム状態、選択されたワードラインの物理的な位置、現在温度が属する温度領域、選択されたメモリセルのページ情報、等のような多様な条件（又は、基準）にしたがって変化されるように電圧発生回路VGから出力される電圧を補償する。このような条件／基準は電圧発生回路VGから出力された電圧を補償するために全て又は部分的に利用され得る。選択されたメモリセルのプログラム状態、選択されたワードラインの物理的な位置、選択されたメモリセルのページ情報、等のような多様な条件（又は、基準）は選択されたメモリセルによって変化される。温度変化によって生じる閾値電圧／抵抗の移動は、メモリセルの閾値電圧を正確に判別するためにメモリセルに印加される電圧の移動を必要とする。メモリセルに印加される電圧の移動は、基本的に、温度変化に比例して遂行される。また、本発明の場合、温度変化によって生じる閾値電圧／抵抗の移動は上述した条件を考慮して追加的に遂行される。このような理由で、温度変化の時、先に言及された条件にしたがってメモリセルに印加される電圧を補償することによってメモリセルの閾値電圧を正確に判別できる。30

## 【0022】

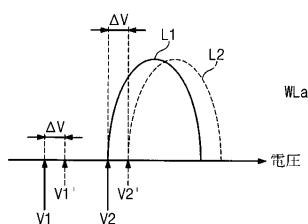

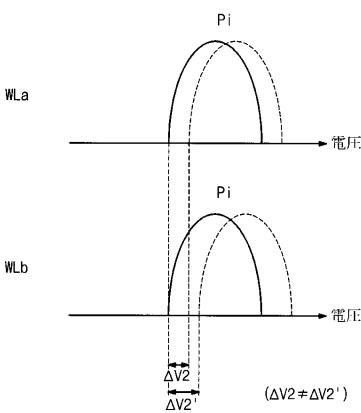

図2A乃至図2Dはメモリセルの閾値電圧の変化を発生させる多様な条件を説明するための図面である。

## 【0023】

先ず、図2Aを参照すれば、任意のワードラインWL<sub>a</sub>に連結されたメモリセルはプログラム状態Piを有するメモリセルを含む。プログラム状態Piを有するメモリセルは、デフォルト温度の下で実線L1で表示された閾値電圧分布に属する閾値電圧を有する。このような場合、閾値電圧分布L1に属するメモリセルの閾値電圧は、正常読出し動作の時、読出し電圧V1を通じて、そして検証読出し動作の時、検証読出し電圧V2を通じて判別される。電圧V1、V2は図1の電圧発生回路VGから出力される。閾値電圧分布L1は、温度変化によって点線で表示された閾値電圧分布L2に移動され得る。本発明の例示的な実施形態による補償回路CPSは、電圧V1、V2が温度変化にしたがって変化されるように電圧発生回路VGを制御する。電圧補償は、例えば、温度変化に比例して遂行される。4050

## 【0024】

温度（検出された温度又は周辺温度）がデフォルト温度を基準に変化される時、図2Bに示したように、任意のワードラインW L aに連結されたメモリセルの閾値電圧はプログラム状態（例えば、P i、P j）にしたがって互に異なるようになります。したがって、本発明の例示的な実施形態による補償回路C P Sは、選択されたメモリセルに印加される電圧が温度変化の時、プログラム状態にしたがって異なるようになります。（又は、異なるようになります。）電圧発生回路V Gを制御する。即ち、温度（検出された温度又は周辺温度）がデフォルト温度を基準に変化される時、本発明の例示的な実施形態による補償回路C P Sは、選択されたメモリセルに印加される電圧が選択されたメモリセルのプログラム状態にしたがって可変的に変化されるよう電圧発生回路V Gを制御する。

10

## 【0025】

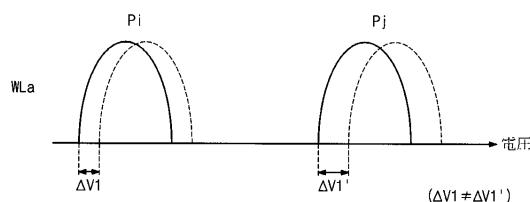

温度（検出された温度又は周辺温度）がデフォルト温度を基準に変化される時、図2Cに示したように、メモリセルの閾値電圧の移動はワードラインの物理的な位置にしたがって一定でない。したがって、本発明の例示的な実施形態による補償回路C P Sは、選択されたメモリセルに印加される電圧が温度変化の時、ワードラインW L a、W L bの物理的な位置にしたがって可変的に変化されるよう電圧発生回路V Gを制御する。即ち、温度（検出された温度又は周辺温度）がデフォルト温度を基準に変化される時、本発明の例示的な実施形態による補償回路C P Sは、選択されたメモリセルに印加される電圧が選択されたメモリセルに連結されたワードラインの物理的な位置にしたがって変化されるよう、電圧発生回路V Gを制御する。

20

## 【0026】

温度（検出された温度又は周辺温度）がデフォルト温度（又は、デフォルト温度領域T R 0）を基準に変化される時、図2Dに示したように、メモリセルの閾値電圧の移動は現在温度が属する温度領域T Rにしたがって互に異なる。したがって、本発明の例示的な実施形態による補償回路C P Sは、選択されたメモリセルに印加される電圧が現在温度が属する温度領域にしたがって可変的に変化されるよう、電圧発生回路V Gを制御する。即ち、温度がデフォルト温度領域を基準に変化される時、本発明の例示的な実施形態による補償回路C P Sは、選択されたメモリセルに印加される電圧が現在温度が属する温度領域T Rにしたがって変化されるよう、電圧発生回路V Gを制御する。

30

## 【0027】

以上の説明から分かるように、本発明の例示的な実施形態による補償回路C P Sは、温度変化の時、プログラム状態、ワードラインの物理的な位置、温度領域、ページ情報、等のような多様な条件を考慮して電圧発生回路V Gから出力される電圧を補償する。本発明の例示的な実施形態による補償回路C P Sは、上述した条件全て又は一部にしたがって変化されるよう電圧発生回路V Gから出力される電圧を補償する。

## 【0028】

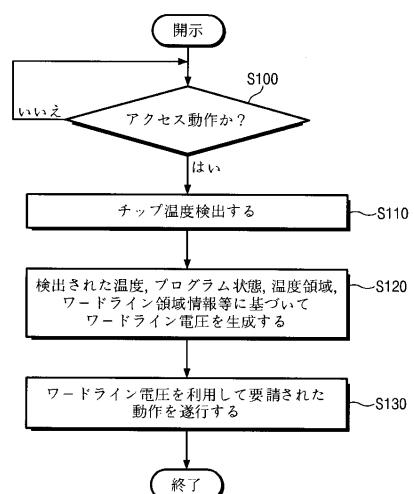

図3は本発明の例示的な実施形態による不揮発性メモリ装置の動作を概略的に説明するためのフローチャートである。以下、本発明の例示的な実施形態による不揮発性メモリ装置の動作が参照図面に基づいて詳細に説明される。

40

## 【0029】

S 1 0 0段階で、不揮発性メモリ装置は外部（例えば、メモリ制御器又はホスト）からアクセスが要請されたか否かを判別する。仮にそうでないと、S 1 0 0段階は反復的に遂行される。外部（例えば、メモリ制御器又はホスト）からアクセスが要請された場合、S 1 1 0段階で、補償回路C P Sは現在温度を検出する。現在温度の検出はアクセス要請以前に遂行される。即ち、現在温度の検出は不揮発性メモリ装置が待機状態にある間に遂行される。S 1 2 0段階で、電圧発生回路V Gはメモリセルへ印加されるワードライン電圧を生成する。特に、メモリセルへ印加されるワードライン電圧は、検出された温度、選択されたメモリセルのプログラム状態、検出された温度が属する温度領域、ページ情報、及び選択されたメモリセルと連結されたワードラインの物理的な位置に基づいて生成される

50

。S130段階で、不揮発性メモリ装置はそのように生成されたワードライン電圧を利用して要請された動作を遂行する。

#### 【0030】

例示的な実施形態において、現在の温度がデフォルト温度を基準に変化されない場合、S120段階で生成されるワードライン電圧はデフォルト温度を基準に設定されたレベルを有する。

#### 【0031】

現在の温度がデフォルト温度を基準に変化される時、検出された温度、選択されたメモリセルのプログラム状態、検出された温度が属する温度領域、ページ情報、及び選択されたメモリセルと連結されたワードラインの物理的な位置に基づいてメモリセルに印加される電圧（例えば、ワードライン電圧）を補償することによって、メモリセルの閾値電圧をより正確に判別できる。10

#### 【0032】

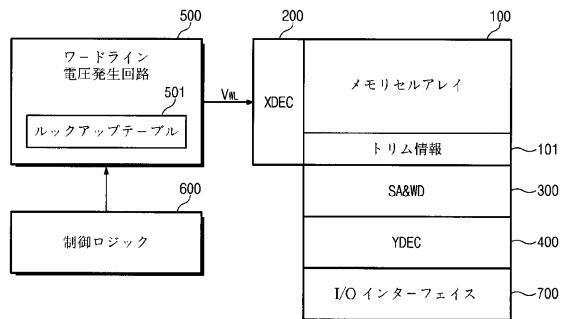

図4は図1で説明された電圧補償方式が適用される本発明の例示的な実施形態によるフラッシュメモリ装置を概略的に示すブロック図である。本発明の例示的な実施形態による不揮発性メモリ装置はフラッシュメモリ装置である。しかし、本発明が他のメモリ装置（例えば、MRAM、PRAM、FRAM（登録商標）、等）に適用され得ることはこの分野の通常的な知識を習得した者に明確である。

#### 【0033】

図4を参照すれば、本発明の例示的な実施形態によるフラッシュメモリ装置はメモリセルアレイ100を含む。メモリセルアレイ100はMビットデータ情報（Mは1又はそれより大きい定数）を格納するメモリセルを含む。メモリセルは、例えば、複数の行（複数のワードライン）と複数の列（複数のビットライン）とに配列される。メモリセルは、データ状態（又は、プログラム状態）にしたがって可変できる抵抗又は可変できる閾値電圧を有するように構成される。メモリセルアレイ100はトリム情報を格納するトリム情報領域101を含む。トリム情報は、例えば、リペアアドレス情報、入出力構造情報、電圧調整情報、等を含む。ここで、電圧調整情報は先に説明された条件（例えば、温度変化、温度領域、プログラム状態、ページ情報、ワードライン位置、等）にしたがってワードライン電圧を調整／補償するための情報である。電圧調整情報は、ルックアップテーブルを構成するようにパワーアップの時、フラッシュメモリ装置のレジスター又は外部（例えば、メモリ制御器又はホスト）へ伝達される。2030

#### 【0034】

本発明の例示的な実施形態によるフラッシュメモリ装置は、行選択回路200、感知増幅器及び記入ドライバ回路300、列選択回路400、ワードライン電圧発生回路500、制御ロジック600、及び入出力インターフェイス700をさらに含む。

#### 【0035】

行選択回路200はメモリセルアレイ100の行を選択し、駆動するように構成される。行選択回路200の選択及び駆動動作は制御ロジック600の制御の下で遂行される。感知増幅器及び記入ドライバ回路300は、読み出し動作の時、メモリセルアレイ100からデータを読み出すように、そしてプログラム動作の時、メモリセルアレイ100にデータを書き込むように構成される。感知増幅器及び記入ドライバ回路300は広く公知されたページバッファー回路とも称される。列選択回路400は、感知増幅器及び記入ドライバ回路300によって読み出されたデータをあらかじめ設定された単位（例えば、バイト単位、ワード単位、等）で選択するように構成される。列選択回路400によって選択されたデータは入出力インターフェイス700を通じて外部へ伝送される。感知増幅器及び記入ドライバ回路300、列選択回路400、及び入出力インターフェイス700は、制御ロジック600の制御に応答して動作する。40

#### 【0036】

続いて、図4を参照すれば、ワードライン電圧発生回路500は、メモリセルアレイ100の選択されたメモリセル（又は、選択された行／ワードライン）へ供給される電圧（50

即ち、ワードライン電圧  $V_{WL}$  ) を生成するように構成される。しかし、ワードライン電圧発生回路 500 が単なるワードライン電圧の生成に制限されることはよく理解できる。例えば、ワードライン電圧発生回路 500 はウェル電圧、消去電圧、等を生成するよう構成され得る。ワードライン電圧発生回路 500 はルックアップテーブルを格納するためのレジスター 501 を含む。レジスター 501 に格納されるルックアップテーブルは、多様な条件（例えば、温度変化、選択されたメモリセルのプログラム状態、ページ情報、温度領域、ワードライン位置、等）にしたがってワードライン電圧  $V_{WL}$  を補償 / 調整するのに使用される。レジスター 501 に格納されたルックアップテーブルの値はパワーアップの時、制御ロジック 600 の制御の下でメモリセルアレイ 100 から読み出されたトリム情報の中で電圧調整情報に設定される。本発明の例示的な実施形態において、電圧調整情報がレジスター 501 にロードされる時、制御ロジック 600 を通じて電圧調整情報が変更できる。ワードライン電圧発生回路 500 は、多様な条件（例えば、温度変化、選択されたメモリセルのプログラム状態、ページ情報、温度領域、ワードライン位置、等）を反映するルックアップテーブルの値に基づいてワードライン電圧  $V_{WL}$  を生成する。

10

#### 【0037】

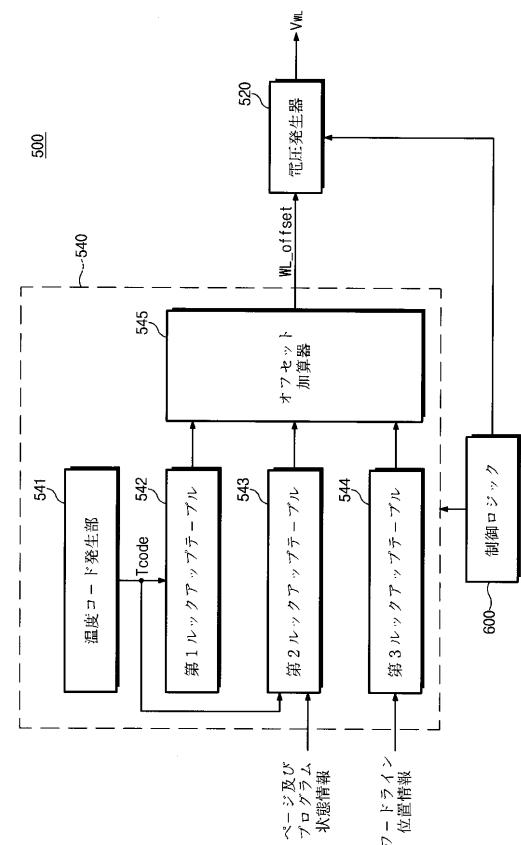

図 5 A は図 4 に示された本発明の例示的な実施形態によるワードライン電圧発生回路を概略的に示すブロック図である。

#### 【0038】

図 5 A を参照すれば、ワードライン電圧発生回路 500 は電圧発生器 520 と補償回路 540 とを含む。電圧発生器 520 は制御ロジック 600 の制御の下で補償回路 540 からのワードラインオフセット値  $WL\_offset$  にしたがってワードライン電圧  $V_{WL}$  を発生するように構成される。補償回路 540 は温度変化にしたがってワードライン電圧  $V_{WL}$  を調整 / 補償するように電圧発生器 520 を制御する。電圧発生器 520 によって生成されるワードライン電圧  $V_{WL}$  は、読み出し電圧、プログラム電圧、検証読み出し電圧等を含む。補償回路 540 は、現在温度を示す温度コード  $Tcode$  を発生する温度コード発生部 541、多様な条件にしたがって決定されたオフセット値を含む第 1 乃至第 3 ルックアップテーブル 542、543、544、及び第 1 乃至第 3 ルックアップテーブル 542、543、544 から出力されるオフセット値を加算するオフセット加算器 545 を含む。ワードライン電圧  $V_{WL}$  は、オフセット加算器 545 から出力されるワードラインオフセット値  $WL\_offset$  によって補償され得る。

20

30

#### 【0039】

第 1 ルックアップテーブル 542 は、フラッシュメモリ装置の許容できる温度範囲に属する温度領域に各々対応するオフセット値を含む。オフセット値はデフォルト温度（例えば、許容できる温度範囲の最も高い温度）を基準に設定される。しかし、第 1 ルックアップテーブル 542 のオフセット値は、デフォルト温度で許容できる温度範囲の最も低い温度又は中間温度を基準に設定され得る。第 1 ルックアップテーブル 542 のオフセット値の中で 1 つは、温度コード発生部 541 によって生成された温度コード  $Tcode$  にしたがって選択される。温度コード  $Tcode$  はフラッシュメモリ装置の現在温度を示す。

#### 【0040】

第 2 ルックアップテーブル 543 は、プログラム状態情報、ページ情報、及び温度領域情報にしたがって決定されたオフセット値を含む。先に言及されたように、温度変化によるメモリセルの閾値電圧移動は、プログラム状態にしたがって、そして温度領域にしたがって差異がある。プログラム状態及び温度領域によるオフセット値は、また、任意のワードラインに属するページに対して即ち、ページに区別される。フラッシュメモリ装置の許容できる温度範囲は複数の温度領域に区分され得る。温度領域各々にはプログラム状態に各々対応するオフセット値が含まれる。任意の温度領域に属するオフセット値はプログラム状態にしたがって異なるように設定される。これは、図 2 B で説明されたように、プログラム状態にしたがって閾値電圧の移動が異なるためである。また、任意のプログラム状態に対するオフセット値は温度領域にしたがって異なるように設定される。これは、図 2 D で説明されたように、温度領域にしたがって閾値電圧の移動が異なるためである。任

40

50

意の温度領域に属する、そしてプログラム状態に各々対応するオフセット値の差は制御ロジック 600 の制御にしたがって可変され得る。同様に、任意のプログラム状態に属する、そして温度領域各々に対応するオフセット値の差は制御ロジック 600 の制御にしたがって可変され得る。

#### 【0041】

第 3 ルックアップテーブル 544 は、選択されたワードラインの位置にしたがって決定されたオフセット値を含む。先に言及されたように、温度変化によるメモリセルの閾値電圧移動は選択されたワードラインの位置にしたがって差異がある。例えば、第 3 ルックアップテーブル 544 はメモリブロックに属するワードライン各々に対応するオフセット値を含む。他の例として、第 3 ルックアップテーブル 544 は、各々がワードラインで構成されたワードライングループに各々対応するオフセット値を含む。10

#### 【0042】

例示的な実施形態において、第 1 乃至第 3 ルックアップテーブル 542、543、544 は、図 4 で説明されたレジスター 501 に格納され、第 1 乃至第 3 ルックアップテーブル 542、543、544 のオフセット値は、図 4 で説明されたトリム情報を格納する領域 101 からロードされる。第 1 乃至第 3 ルックアップテーブル 542、543、544 のオフセット値は、例えば、バイナリコードで構成される。

#### 【0043】

オフセット加算器 545 は、第 1 乃至第 3 ルックアップテーブル 542、543、544 から出力されるオフセット値を加算してワードラインオフセット値  $WL\_offset$  を出力する。ワードラインオフセット値  $WL\_offset$  は、温度変化にしたがってワードライン電圧  $V_{WL}$  を増加させるか、或いは減少させるのに使用される。ワードラインオフセット値  $WL\_offset$  は、電圧発生器 520 に提供され、温度変化によって生じるメモリセルの閾値電圧移動を補償するように電圧発生器 520 によって生成される電圧（即ち、ワードライン電圧）を調整／補償するのに使用される。ここで、オフセット加算器 545 は選択的に使用され得る。又は、オフセット加算器 545 は使用しないこともあり得る。この場合、第 1 乃至第 3 ルックアップテーブル 542、543、544 のオフセット値は、電圧発生器 520 に直接提供され、電圧発生器 520 は、第 1 乃至第 3 ルックアップテーブル 542、543、544 のオフセット値にしたがってワードライン電圧  $V_{WL}$  を順次的に又は同時に補償できる。20 ワードライン電圧の補償は、例えば、ワードラインオフセット値又は第 1 乃至第 3 ルックアップテーブル 542、543、544 のオフセット値にしたがって、電圧発生器 520 に含まれる、電圧分配用抵抗列の抵抗値を可変させることによって遂行される。図面には示していないが、電圧発生器 520 は高電圧を発生するポンプ、高電圧を要求される電圧を調整するレギュレータ、等を含み、抵抗列はレギュレータに包含される。又は、電圧発生器 520 はレギュレータを含む。このような場合、電圧発生器 520 は、ポンプから高電圧を受信し、ワードラインオフセット値  $WL\_offset$  及び動作モードにしたがって入力された高電圧を調整してワードライン電圧  $V_{WL}$  を出力する。30

#### 【0044】

図 5B は図 4 に示された本発明の他の例示的な実施形態によるワードライン電圧発生回路を概略的に示すブロック図である。40

#### 【0045】

図 5B において、図 5A に示されたことと同一な機能を遂行する構成要素は同一な参照番号で表記される。図 5B に示されたワードライン電圧発生回路 500a は下の差異点を除外すれば、図 5A に示されたことと実質的に同一であり、したがってそれに対する説明は省略される。補償回路 540a に含まれた第 3 ルックアップテーブル 544a は、ワードライン位置情報と温度コード  $T\_code$  とに応答して動作する。第 3 ルックアップテーブル 544a は選択されたワードラインの位置にしたがって決定されたオフセット値を含む。先に言及されたように、温度変化によるメモリセルの閾値電圧移動は選択されたワードラインの位置にしたがって差異がある。例えば、第 3 ルックアップテーブル 544a は50

メモリブロックに属するワードライン各々に対応するオフセット値を含み、オフセット値は温度領域にしたがって区分される。このような場合、温度コード T c o d e によって指定される現在温度領域に対応するオフセット値の中で 1 つが、選択されたワードラインの位置にしたがって選択される。他の例として、第 3 ルックアップテーブル 5 4 4 a は各々がワードラインで構成されたワードライングループに各々対応するオフセット値を含み、オフセット値は温度領域にしたがって区分される。このような場合、温度コード T c o d e によって指定される現在温度領域に対応するオフセット値の中で 1 つが、選択されたワードラインを含むワードライングループによって選択される。

#### 【 0 0 4 6 】

図 6 は図 5 に示された温度コード発生部を概略的に示すプロック図である。

10

#### 【 0 0 4 7 】

図 6 を参照すれば、温度コード発生部 5 4 1 は、温度変化に拘わらず基準電圧 V T R E F を安定的に / 一定に発生する基準電圧発生器 5 4 1 a と、基準電圧 V T R E F に応答して現在温度に対応する温度電圧 V T E M P を発生する温度検出器 5 4 1 b と、アナログ形態の温度電圧 V T E M P をデジタルコード A D C に変換するレベル変換器 5 4 1 c と、デジタルコード A D C を温度コード T c o d e に変換する温度コード変換器 5 4 1 d を含む。ここで、温度コード変換器 5 4 1 d はデジタルコード A D C を構成するビットの数を減らすために使用され、デジタルコード A D C と比較して、温度コード T c o d e を構成するビットの数が少ない。温度コード発生部 5 4 1 は、温度コード T c o d e がデフォルト温度（例えば、許容できる温度範囲の最も高い温度、最も低い温度、又は中間温度）に対応する値に設定されたのか否かを判別し、判別結果にしたがって温度検出器 5 4 1 b を制御する校正部 5 4 1 e をさらに含む。校正部 5 4 1 e の制御にしたがって温度検出器 5 4 1 b の出力電圧 V T E M P が可変される。温度検出器 5 4 1 b の出力電圧 V T E M P は、温度コード T c o d e がデフォルト温度（例えば、許容できる温度範囲の最も高い温度、最も低い温度、又は中間温度）に対応する値に設定されるまで可変される。校正部 5 4 1 e は、例えば、テスト動作の時に動作し、正常動作の時に非活性化される。これは制御ロジック 6 0 0 によって制御される。現在温度に対応する温度コードの生成する温度コード発生部 5 4 1 の構成がここに開示されたことに制限されないことはよく理解できる。

20

#### 【 0 0 4 8 】

図 7 A 及び図 7 B は図 5 で説明された第 2 ルックアップテーブルに含まれるオフセット値を説明するための図面である。説明の前に、フラッシュメモリ装置が 9 0 ~ - 4 0 の温度範囲で動作すると仮定する。また、デフォルト温度が許容できる温度範囲の最も高い温度（9 0 ）であると仮定する。このような仮定によれば、温度がデフォルト温度より低くなることにしてメモリセルの閾値電圧は増加する。したがって、メモリセルに印加されるワードライン電圧もやはり温度変化にしたがって増加されるように補償される。これに反して、デフォルト温度が許容できる温度範囲の最も低い温度（ - 4 0 ）である場合、温度がデフォルト温度より高くなることにしてメモリセルの閾値電圧は減少し、その結果メモリセルに印加されるワードライン電圧もやはり温度変化にしたがって減少されるように補償される。

30

#### 【 0 0 4 9 】

温度変化の時、各プログラム状態のオフセット値の変化を説明するための図 7 A を参照すれば、温度領域（例えば、T R 0 ~ T R 6 ）の各々で、プログラム状態 P 1 ~ P 7 に各々対応するオフセット値が決定される。任意の温度領域に属するオフセット値（例えば、図面で点線円で表示される）は、プログラム状態 P 1 ~ P 7 にしたがって互に異なるように設定される。これは、図 2 B で説明されたように、メモリセルの閾値電圧がプログラム状態にしたがって異なるように変化されるためである。図 7 A で分かるように、各プログラム状態のオフセット値は温度変化にしたがって一定の大きさ程度（又は、一定の勾配を有して）増加 / 減少される。特に、本発明の例示的な実施形態によれば、プログラム状態のオフセット値の増加 / 減少勾配は互に異なるように設定される。ここで、増加 / 減少勾配は温度領域に各々対応する任意のプログラム状態のオフセット値の差を意味する。各温

40

50

度領域に属するプログラム状態 P 1 ~ P 7 のオフセット値の増加 / 減少勾配は一定に又は互に異なるように設定され得る。例えば、図 7 B に示したように、任意の温度領域（例えば、T R 6 ）に属するプログラム状態 P 1 ~ P 7 のオフセット値の増加 / 減少勾配は互に異なるように設定される。これは残り温度領域にも同様に適用される。オフセット値の増加 / 減少勾配が互に異なるように設定されることとはプログラム状態、ワードラインの物理的な位置、温度領域、等のような条件にしたがって最適に補償されたワードライン電圧を利用して温度変化による移動された閾値電圧が正確に判別されることを意味する。

#### 【 0 0 5 0 】

例示的な実施形態において、オフセット値の増加 / 減少勾配は、電圧調整情報がメモリセルアレイ 1 0 0 でレジスター 5 0 1 にロードされる時、制御ロジック 6 0 0 を通じて変更できる。又は、オフセット値の多様な増加 / 減少勾配を反映する複数の電圧調整情報セットがメモリセルアレイ 1 0 0 に格納され、パワーアップの時、複数の電圧調整情報セットの中で 1 つが制御ロジック 6 0 0 によって選択され、選択された電圧調整情報セットがレジスター 5 0 1 にロードされ得る。電圧調整情報セットの選択又は電圧調整情報の変更は外部（例えば、メモリ制御器又はホスト）の制御にしたがって遂行される。10

#### 【 0 0 5 1 】

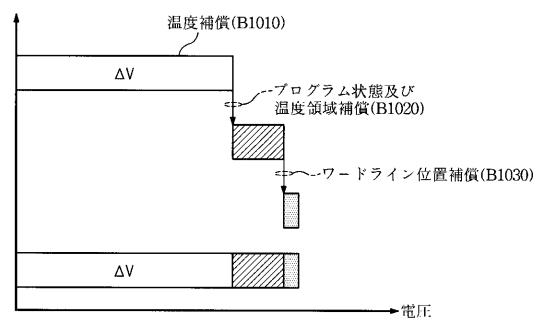

図 8 は本発明の例示的な実施形態によるフラッシュメモリ装置に適用された電圧補償方法を説明するための図面である。

#### 【 0 0 5 2 】

説明の前に、フラッシュメモリ装置が 9 0 ~ - 4 0 の温度範囲で動作すると仮定する。また、デフォルト温度が、許容できる温度範囲の最も高い温度（9 0 ）であると仮定する。温度範囲が複数の温度領域（例えば、T R 0 ~ T R 6 ）で構成されると仮定する。デフォルト温度が含まれた温度領域をデフォルト温度領域 T R 0 であると称する。このような仮定によれば、温度がデフォルト温度より低くなることにしたがってメモリセルの閾値電圧は増加する。したがって、メモリセルに印加されるワードライン電圧もやはり温度変化にしたがって増加されるように補償される。しかし、デフォルト温度の設定によって減少されるようにワードライン電圧が補償されることもあり得る。20

#### 【 0 0 5 3 】

本発明の例示的な実施形態による電圧補償方法は、基本的に、温度変化に比例してワードライン電圧を補償することを含む（B 1 0 1 0）。例えば、補償回路 5 4 0 によって検出された温度（又は、現在温度）がデフォルト温度領域とは異なる温度領域に属すると判別される時、ワードライン電圧は一定の大きさ（V）程度補償される。一定の大きさ（30V）は温度変化の大きさに比例する。温度変化に比例してワードライン電圧を補償することは、温度コード T c o d e にしたがって第 1 ルックアップテーブル 5 4 2 で出力されるオフセット値によって遂行される。追加的に、本発明の例示的な実施形態による電圧補償方法は温度領域及びプログラム状態に基づいてワードライン電圧を補償することを含む（B 1 0 2 0）。これは温度コード T c o d e にしたがって第 2 ルックアップテーブル 5 4 3 で出力されるオフセット値によって遂行される。また、本発明の例示的な実施形態による電圧補償方法はワードラインの物理的な位置に基づいてワードライン電圧を補償することを含む（B 1 0 3 0）。これは第 3 ルックアップテーブル 5 4 4 で出力されるオフセット値によって遂行される。40

#### 【 0 0 5 4 】

図 8 から分かるように、ワードライン電圧は温度変化に比例して補償されるのみでなく、プログラム状態、温度領域、ページ情報、及びワードライン位置を考慮して追加的に補償される。これはプログラム状態、ワードラインの物理的な位置、温度領域、ページ情報等のような条件にしたがって最適に補償されたワードライン電圧を利用して温度変化によって移動された閾値電圧が正確に判別されることを意味する。

#### 【 0 0 5 5 】

例示的な実施形態において、ワードライン電圧の補償段階（B 1 0 1 0、B 1 0 2 0、B 1 0 3 0）は順次的に遂行されるか、或いは同時に遂行される。ワードラインの物理的50

な位置にしたがってワードライン電圧を補償すること（B1030）は選択的に遂行される。ワードラインの物理的な位置はフラッシュメモリ装置のアレイ構造、即ち、2次元アレイ構造又は3次元アレイ構造を含む。

#### 【0056】

所定の実施形態において、デフォルト温度の設定にしたがって減少されるようにワードライン電圧が補償されることもあり得る。例えば、デフォルト温度が許容できる温度範囲の最も低い温度（-40）であると仮定すれば、ワードライン電圧が図8で説明されたワードラインオフセット値程度減少される。又は、デフォルト温度の設定にしたがって減少されるか、或いは増加されるようにワードライン電圧が補償されることもあり得る。例えば、デフォルト温度が許容できる温度範囲の中間温度（25）であると仮定すれば、ワードライン電圧は、現在温度がデフォルト温度より低ければ、増加されるように、そして現在温度がデフォルト温度より高ければ、減少するように調整される。10

#### 【0057】

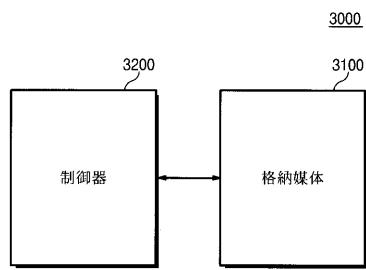

図9は本発明の例示的な実施形態による不揮発性メモリ装置を含むデータ格納装置を概略的に示すブロック図である。

#### 【0058】

図9を参照すれば、データ格納装置3000は格納媒体3100と制御器3200とを含む。格納媒体3100はテキスト、グラフィック、ソフトウェアコード等のような多様なデータ形態を有するデータ情報を格納するのに使用される。格納媒体3100は図1又は図4で説明された不揮発性メモリ装置で構成され、先に説明された電圧補償方式にしたがってワードライン電圧を補償するように構成される。制御器3200は外部要請に応答して格納媒体3100を制御するように構成される。20

#### 【0059】

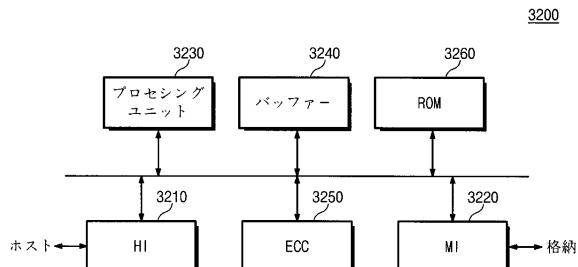

図10は本発明の例示的な実施形態による図9に示された制御器を概略的に示すブロック図である。図10を参照すれば、本発明の例示的な実施形態による制御器3200は、第1インターフェイス3210、第2インターフェイス3220、処理ユニット3230、バッファー3240、ECCユニット3250、及びROM3260を含む。

#### 【0060】

第1インターフェイス3210は外部（又は、ホスト）とインターフェイスするように構成される。第2インターフェイス3220は図10に示された格納媒体3100とインターフェイスするように構成される。処理ユニット3230は制御器3200の全般的な動作を制御するように構成される。例えば、CPU3230は、ROM3260に格納されたフラッシュ変換階層（Flash Translation Layer：FTL）のようなファームウェアを運用するように構成される。バッファー3240は、第1インターフェイス3210を通じて外部へ伝達されるデータを一時的に格納するのに使用される。バッファー3240は第2インターフェイス3220を通じて格納媒体3100から伝達されるデータを一時的に格納するのに使用される。ECCユニット3250は、格納媒体3100に格納されるデータを符号化するように、そして格納媒体3100から読み出されたデータを復号化するように構成される。30

#### 【0061】

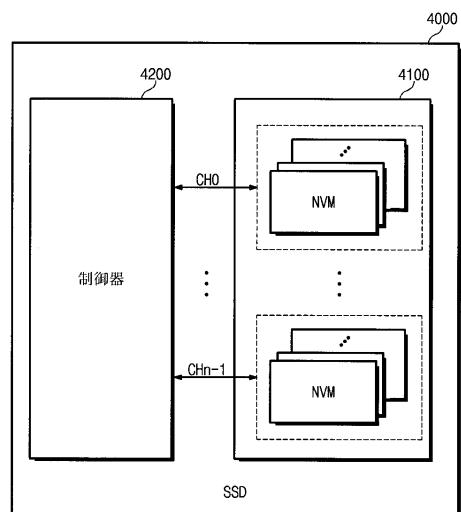

図11は本発明の例示的な実施形態による不揮発性メモリ装置を利用する半導体ドライブを概略的に示すブロック図である。

#### 【0062】

図11を参照すれば、半導体ドライブ4000（SSD）は格納媒体4100と制御器4200とを含む。格納媒体4100は複数のチャンネルを通じて制御器4200と連結される。各チャンネルには複数の不揮発性メモリが共通に連結される。各不揮発性メモリは図1又は図4で説明されたメモリで構成される。制御器4200は格納媒体4100を制御するように構成される。

#### 【0063】

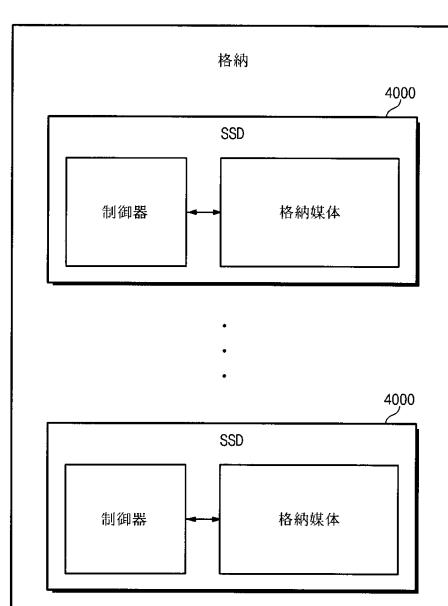

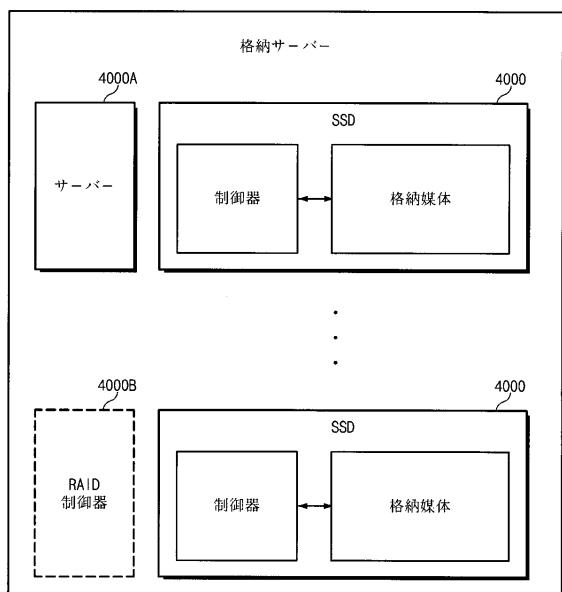

図12は図11に示された半導体ドライブを利用するストレージを概略的に示すブロッ40

50

ク図であり、図13は図11に示された半導体ドライブを利用するストレージサーバーを概略的に示すブロック図である。

#### 【0064】

本発明の例示的な実施形態による半導体ドライブ4000はストレージを構成するのに使用され得る。図12に示したように、ストレージは図11で説明されたことと実質的に同様に構成される複数の半導体ドライブを含む。本発明の例示的な実施形態による半導体ドライブ4000はストレージサーバーを構成するのに使用され得る。図13に示したように、ストレージサーバーは図11で説明されたことと実質的に同様に構成される複数の半導体ドライブ4000とサーバー4000Aとを含む。また、この分野で広く公知されたRAID制御器4000Bがストレージサーバーとして提供され得ることはよく理解できる。10

#### 【0065】

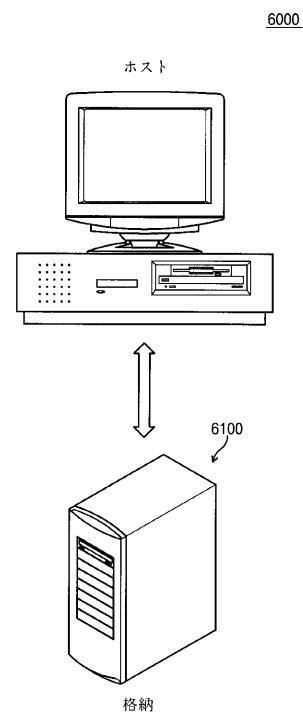

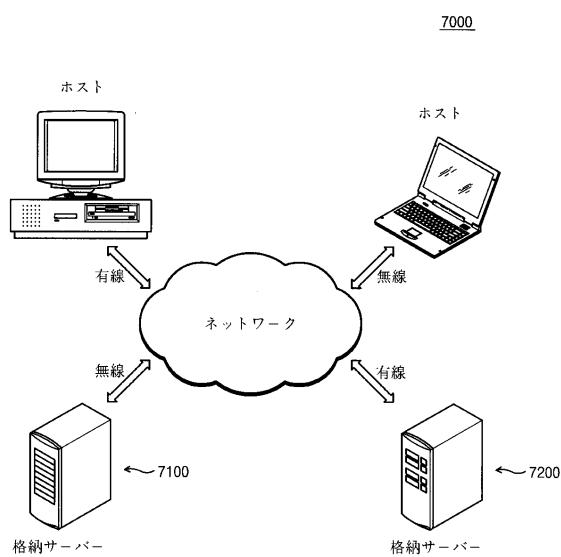

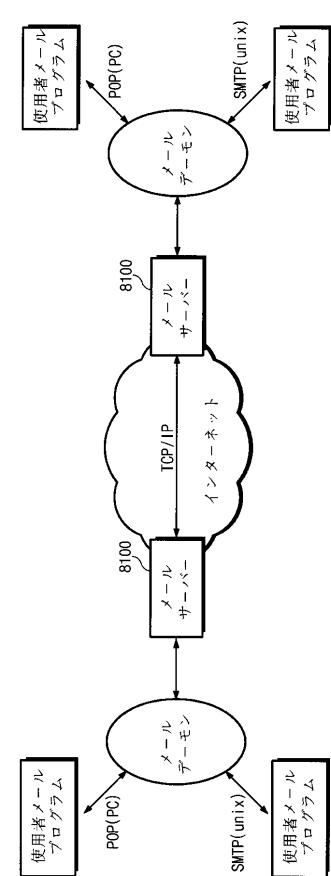

図14乃至図16は本発明の例示的な実施形態によるデータ格納装置が適用されるシステムを概略的に示す図面である。

#### 【0066】

本発明の例示的な実施形態によるデータ格納装置を含む半導体ドライブがストレージに適用される場合、図14に示したように、システム6000は有線及び/又は無線にホストと通信するストレージ6100を含む。本発明の例示的な実施形態によるデータ格納装置を含む半導体ドライブがストレージサーバーに適用される場合、図15に示したように、システム7000は有線及び/又は無線にホストと通信するストレージサーバー7100、7200を含む。また、図16に示したように、本発明の例示的な実施形態によるデータ格納装置を含む半導体ドライブはメールサーバー8100にも適用され得る。20

#### 【0067】

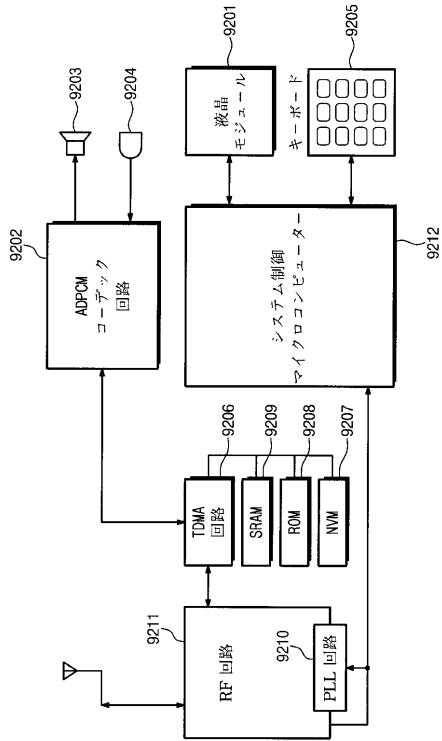

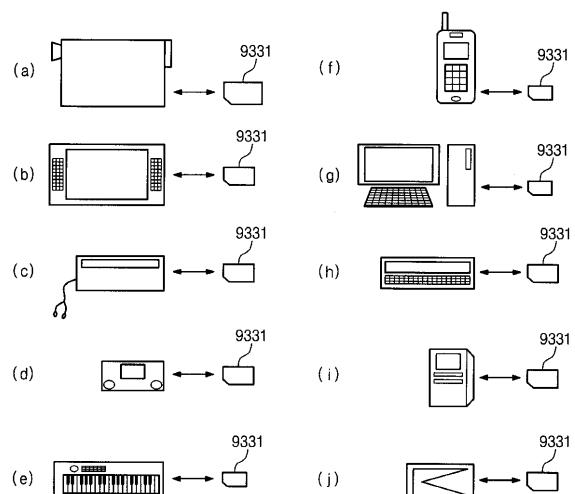

図17乃至図21は本発明の例示的な実施形態による不揮発性メモリ装置が適用される他のシステムを概略的に示す図面である。

#### 【0068】

図17は本発明の実施形態による不揮発性メモリ装置が使用される携帯電話システム(cellular phone system)を概略的に示すブロック図である。

#### 【0069】

図17を参照すれば、携帯電話システムは、音を圧縮するか、或いは圧縮された音を復元する(compression or decompression)ADPCMコードック回路9202、スピーカー(speaker)9203、マイクロフォン(microphone)9204、デジタルデータを時分割マルチプレクシングするTDM A回路9206、無線信号のキャリヤー周波数(carrier frequency)をセッティングするPLL回路9210、無線信号を送信又は受信するためのRF回路9211等を包含できる。30

#### 【0070】

また、携帯電話システムは様々な種類のメモリ装置を包含でき、例えば、携帯電話システムは不揮発性メモリ装置9207、ROM9208、SRAM9209を包含できる。携帯電話システムの不揮発性メモリ装置9207で、例えば、本発明の例示的な実施形態による不揮発性メモリ装置が使用され得る。ROM9208はプログラムを格納でき、SRAM9209はシステムコントロールマイクロコンピューター9212のための作業領域として役割を果たすか、或いはデータを一時的に格納する。ここで、システムコントロールマイクロコンピューター9212はプロセッサーとして、不揮発性メモリ装置9207の書き込み動作及び読み出し動作を制御することができる。40

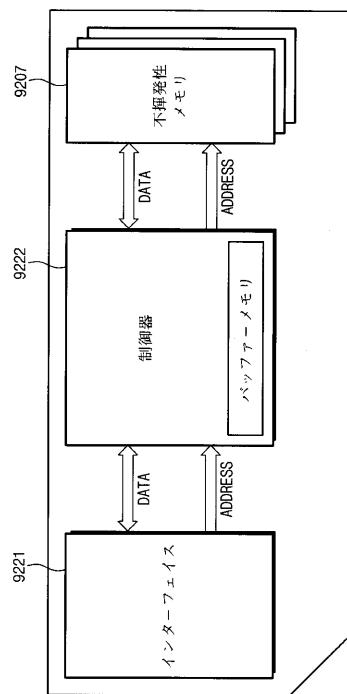

#### 【0071】

図18は本発明の実施形態による不揮発性メモリ装置が使用されるメモリカード(memory card)の例示的な図面である。メモリカードは、例えば、MMCカード、SDカード、マルチユーズ(multiuse)カード、マイクロSDカード、メモリスティック、コンパクトSDカード、IDカード、PCMCIAカード、SSDカード、チ50

チップカード (chip card)、スマートカード (smart card)、USBカード等であり得る。

【0072】

図18を参照すれば、メモリカードは外部とのインターフェイスを遂行するインターフェイス部9221、バッファーメモリを有し、メモリカードの動作を制御するコントローラ9222、本発明の実施形態による不揮発性メモリ装置9207を少なくとも1つ包含できる。コントローラ9222はプロセッサーとして、不揮発性メモリ装置9207の書き込み動作及び読み出し動作を制御することができる。具体的に、コントローラ9222はデータバスDATAとアドレスバスADDRESSを通じて不揮発性メモリ装置9207、インターフェイス部9221とカップリングされている。

10

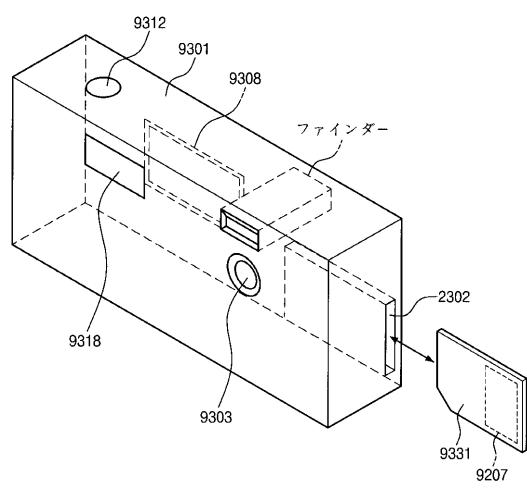

【0073】

図19は本発明の実施形態による不揮発性メモリ装置が使用されるデジタルスチールカメラ (digital still camera) の例示的な図面である。

【0074】

図19を参照すれば、デジタルスチールカメラはボディー9301、スロット9302、レンズ9303、ディスプレイ部9308、シャッターボタン9312、ストロボ (strobe) 9318等を含む。特に、スロット9308にはメモリカード9331が挿入され、メモリカード9331は本発明の実施形態による不揮発性メモリ装置9207を少なくとも1つ包含できる。

【0075】

20

メモリカード9331が接触形 (contact type) である場合、メモリカード9331がスロット9308に挿入される時、メモリカード9331と回路基板の上の特定電気回路が電気的に接触するようになる。メモリカード9331が非接触形 (non-contact type) である場合、無線信号を通じてメモリカード9331がアクセスされる。

【0076】

図20は図19のメモリカードが使用される多様なシステムを説明する例示的な図面である。

【0077】

図20を参照すれば、メモリカード2331は (a) ビデオカメラ、(b) テレビジョン、(c) オーディオ装置、(d) ゲーム装置、(e) 電子音楽装置、(f) 携帯電話、(g) コンピューター、(h) PDA (Personal Digital Assistant)、(i) ボイスレコーダー (voice recorder)、(j) PCカード等に使用され得る。

30

【0078】

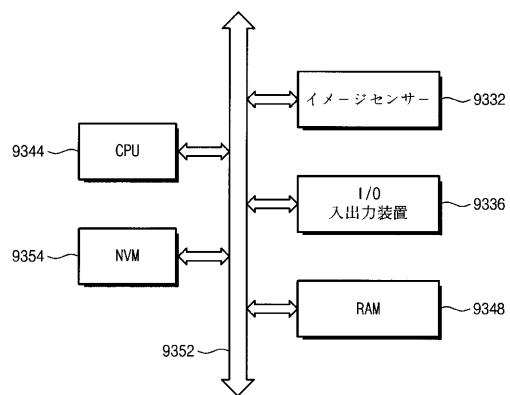

図21は本発明の実施形態による不揮発性メモリ装置が使用されるイメージセンサー (image sensor) システムの例示的な図面である。

【0079】

図21を参照すれば、イメージセンサーシステムは、イメージセンサー9332、出入力装置9336、RAM9348、CPU9344、本発明の実施形態による不揮発性メモリ装置9354等を包含できる。各構成要素、即ち、イメージセンサー9332、出入力装置9336、RAM9348、CPU9344、不揮発性メモリ装置9354はバス9352を通じて互に通信する。イメージセンサー9332はフォトゲート、フォトダイオード等のようなフォトセンシング (photo sensing) 素子を包含できる。各々の構成要素はプロセッサーと共に1つのチップで構成され、プロセッサーと各々別個のチップで構成されることもあり得る。

40

【0080】

本発明の範囲又は技術的思想を逸脱しなく本発明の構造が多様に修正や変更され得ることはこの分野に熟練された者に明確である。上述した内容を考慮して見る時、もし本発明の修正及び変更が下の請求項及び同等物の範疇内に属すれば、本発明がこの発明の変更及

50

び修正を含むことと見なす。

【符号の説明】

【0081】

|       |                 |    |

|-------|-----------------|----|

| 100   | メモリセルアレイ        |    |

| 101   | トリム情報           |    |

| 200   | 行選択回路           |    |

| 300   | 感知増幅器及び記入ドライバ回路 |    |

| 400   | 列選択回路           |    |

| 500   | ワードライン電圧発生回路    | 10 |

| 501   | レジスター           |    |

| 520   | 電圧発生器           |    |

| 540   | 補償回路            |    |

| 541   | 温度コード発生部        |    |

| 541 a | 基準電圧発生器         |    |

| 541 b | 温度検出器           |    |

| 541 c | レベル変換器          |    |

| 541 d | 温度コード変換器        |    |

| 541 e | 校正部             |    |

| 542   | 第1ルックアップテーブル    |    |

| 543   | 第2ルックアップテーブル    | 20 |

| 544   | 第3ルックアップテーブル    |    |

| 600   | 制御ロジック          |    |

| 700   | 入出力インターフェイス     |    |

| V G   | 電圧発生回路          |    |

| C P S | 補償回路            |    |

【図1】

【図2 A】

【図2 B】

【図2 D】

【図2 C】

【図3】

【図4】

【図5 A】

【図5 B】

【図6】

【図 7 A】

【図 7 B】

【図 10】

【図 11】

【図 8】

【図 9】

【図 12】

【図13】

【図14】

【図15】

【 図 1 6 】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

(72)発明者 朴 起台

大韓民国京畿道城南市盆唐区盆唐洞(番地なし) セトビヨル - マウルサムブアパート410棟3

04号

(72)発明者 金 甫根

大韓民国京畿道水原市靈通区靈通洞(番地なし) ビヨクジヨクゴル9団地アパート946棟13

08号

審査官 滝谷 亮一

(56)参考文献 米国特許出願公開第2010/0110815(US, A1)

米国特許出願公開第2007/0291567(US, A1)

特表2013-520760(JP, A)

特開平11-297084(JP, A)

特開2009-123292(JP, A)

米国特許出願公開第2007/0291566(US, A1)

特開2006-196078(JP, A)

(58)調査した分野(Int.Cl., DB名)

G11C 16/02

G11C 16/06