(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4027829号

(P4027829)

(45) 発行日 平成19年12月26日(2007.12.26)

(24) 登録日 平成19年10月19日(2007.10.19)

(51) Int.CI.

F 1

**G 11 B 5/09 (2006.01)**

G 11 B 5/09 311 B

請求項の数 10 (全 10 頁)

(21) 出願番号 特願2003-82215 (P2003-82215)

(22) 出願日 平成15年3月25日 (2003.3.25)

(65) 公開番号 特開2003-317204 (P2003-317204A)

(43) 公開日 平成15年11月7日 (2003.11.7)

審査請求日 平成18年3月8日 (2006.3.8)

(31) 優先権主張番号 10/118782

(32) 優先日 平成14年4月9日 (2002.4.9)

(33) 優先権主張国 米国(US)

(73) 特許権者 590000879

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国テキサス州ダラス、ノース

セントラルエクスプレスウェイ 135

OO

(74) 代理人 100059959

弁理士 中村 稔

(74) 代理人 100067013

弁理士 大塚 文昭

(74) 代理人 100082005

弁理士 熊倉 賢男

(74) 代理人 100065189

弁理士 宍戸 嘉一

最終頁に続く

(54) 【発明の名称】書込みドライバ性能増強方法及びそのシステム

## (57) 【特許請求の範囲】

## 【請求項 1】

書込み電流ドライバ回路であって、

第1及び第2上側スイッチと第1及び第2下側スイッチとを有し、第1及び第2入力信号に応答して、第1上側スイッチを第1下側スイッチへ接続する第1ノードと第2上側スイッチを第2下側スイッチに接続する第2ノードとの間に接続された書込みヘッドを通じて反対方向に書込み電流を流す、Hスイッチドライバと、

第1上側スイッチのベースに接続された第1プルアップ抵抗(R4又はR8)、及び、

第2上側スイッチのベースに接続された第2プルアップ抵抗であって、当該プルアップ抵抗が上側スイッチのベースにおいてインピーダンスを削減するものであり、

第1電流パルス発生器と、

第1入力信号に応答して、第1下側スイッチへのスイッチング信号を発生するように動作する第1インバータ回路であって、この第1インバータ回路に関連した供給電流が第1上側スイッチと関連した書込み電流の変化を加速するために第1上側スイッチへ高電流パルスを与えるように第1電流パルス発生器により処理される、第1インバータ回路であって、高電流パルスが、プルアップ抵抗の値の増加を可能とするものである、

を備える書込み電流ドライバ回路。

## 【請求項 2】

第2電流パルス発生器と、

第2入力信号に応答して、第2下側スイッチへのスイッチング信号を発生するように動

10

20

作する第2インバータ回路であって、この第2インバータ回路に関連した供給電流が第2上側スイッチと関連した書き込み電流の変化を加速するために第2上側スイッチへ高電流パルスを与えるように第2電流パルス発生器により処理される、第2インバータ回路とをさらに備える1項に記載の書き込み電流ドライバ回路。

**【請求項3】**

第1及び第2電流パルス発生器の各々が、

それぞれのインバータ回路を適切に動作するためにバイアスされていて電圧パルスを発生するように動作するエミッターフォロワーと、

電圧パルスに応答して、高電流パルスを発生するように動作するパワーMOSFET装置と

を含む2項に記載の書き込み電流ドライバ回路。

10

**【請求項4】**

第1電流パルス発生器が、

第1インバータ回路を適切に動作するためにバイアスされていて電圧パルスを発生するように動作するエミッターフォロワーと、

電圧パルスに応答して、高電流パルスを発生するように動作するパワーMOSFET装置と

を含む1項に記載の書き込み電流ドライバ回路。

**【請求項5】**

書き込み電流ドライバ回路であって、

第1及び第2上側スイッチと第1及び第2下側スイッチとを有し、第1及び第2入力信号に応答して、第1上側スイッチを第1下側スイッチへ接続する第1ノードと第2上側スイッチを第2下側スイッチに接続する第2ノードとの間に接続された書き込みヘッドを通じて反対方向に書き込み電流を流す、Hスイッチドライバと、

第1上側スイッチのベースに接続された第1プルアップ抵抗(R4又はR8)、及び、

第2上側スイッチのベースに接続された第2プルアップ抵抗であって、当該プルアップ抵抗が上側スイッチのベースにおいてインピーダンスを削減するものであり、

20

第1電流パルスを発生する手段と、

第1入力信号に応答して、第1下側スイッチへのスイッチング信号を発生する手段であって、この第1下側スイッチへのスイッチング信号を発生する手段に関連した供給電流が第1上側スイッチと関連した書き込み電流の変化を加速するために第1上側スイッチへ高電流パルスを与えるように第1電流パルスを発生する手段により処理される、第1下側スイッチへのスイッチング信号を発生する手段であって、高電流パルスが、プルアップ抵抗の値の増加を可能とするものである、

30

を備える書き込み電流ドライバ回路。

**【請求項6】**

第2電流パルスを発生する手段と、

第2入力信号に応答して、第2下側スイッチへのスイッチング信号を発生する手段であって、この第2下側スイッチへのスイッチング信号を発生する手段に関連した供給電流が第2上側スイッチと関連した書き込み電流の変化を加速するために第2上側スイッチへ高電流パルスを与えるように第2電流パルスを発生する手段により処理される、第2下側スイッチへのスイッチング信号を発生する手段と

40

をさらに備える5項に記載の書き込み電流ドライバ回路。

**【請求項7】**

第1電流パルスを発生する手段及び第2電流パルスを発生する手段がそれぞれ、

電圧パルスを発生する手段と、

電圧パルスに応答して高電流パルスを発生する手段と

を備える6項に記載の書き込み電流ドライバ回路。

**【請求項8】**

第1電流パルスを発生する手段が、

50

電圧パルスを発生する手段と、

電圧パルスに応答して高電流パルスを発生する手段と

を備える 5 項に記載の書き込み電流ドライバ回路。

【請求項 9】

磁気記録ヘッド H スイッチドライバの上側スイッチと関連した書き込み電流の変化を加速する方法であって、

H スイッチと、上側スイッチのベースにおけるインピーダンスを削減させる第 1 プルアップ抵抗 (R 4 又は R 8) 及び第 2 プルアップ抵抗と、第 1 及び第 2 電流パルス発生器と、第 1 及び第 2 インバータとを有する書き込み電流ドライバを準備するステップと、

第 1 入力信号に応答して、H スイッチと関連した第 1 下側スイッチへ第 1 インバータを介してスイッチング信号を発生するステップと、

H スイッチと関連した第 1 上側スイッチと関連した書き込み電流の変化を加速するために第 1 上側スイッチへ高電流パルスを与えるように第 1 電流パルス発生器を介して第 1 インバータと関連した供給電流を処理するステップであって、高電流パルスがプルアップ抵抗の値の増加を可能とするものである、

を含んだ方法。

【請求項 10】

第 2 入力信号に応答して、H スイッチと関連した第 2 下側スイッチへ第 2 インバータを介してスイッチング信号を発生するステップと、

H スイッチと関連した第 2 上側スイッチと関連した書き込み電流の変化を加速するために第 2 上側スイッチへ高電流パルスを与えるように第 2 電流パルス発生器を介して第 2 インバータと関連した供給電流を処理するステップと

をさらに含んだ 9 項に記載の方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、一般に、書き込みドライバに関し、より詳細には、誘導記録ヘッド書き込みドライバの性能を増強するための技術に関する。

【0002】

【従来の技術】

H スイッチ・ドライバが記録ディスクにデータを書き込む誘導記録ヘッドに書き込み電流を供給するために使用される。H スイッチは一般に各々が H の 1 つの脚を形成する 4 つのトランジスタスイッチを含む。そして書き込みヘッドコイルは、H の中心スパンを横断するターミナルに接続される。H スイッチの対向する脚の 2 つのトランジスタ・スイッチを動作することにより、電流がコイル中を第 1 方向へ流される。同様に、残りの 2 つのトランジスタ・スイッチを動作することにより、電流がコイル中を反対方向へ流される。

【0003】

【発明が解決しようとする課題】

誘導書き込みヘッド用の書き込みドライバは、高速スイッチングを達成するために上側 H スイッチにおいてが強固なプルアップが必要である。一般に、所望のプルアップを達成するためには、低い値の抵抗をプレドライバに使用する。これは相当の電力を消費する。プライス、ジェーアールに 2001 年 2 月 6 日に付与された米国特許第 6,184,727 号「増強されたスイッチング制御回路を有する書き込みドライバ回路」は、高速スイッチングを達成するために制御信号を使用することを記載しているが、高速スイッチングを達成するために必要な最適な制御信号タイミングを提供していない。

【0004】

以上の観点から、誘導記録ヘッド内で高速の電流の変化を達成できる態様で上側 H スイッチ・ドライバへ最適なタイミングの制御信号を与える技術を提供することが好ましく且つ望ましい。もし、この技術が他の時には最小の電力消費を発生しながら変化中に電流ブーストを与えることができるならばまた好ましく且つ望ましい。

10

20

30

40

50

**【0005】****【課題を解決するための手段】**

本発明は、誘導記録ヘッド書き込みドライバの性能を増強するためのシステム及びその方法に関する。

**【0006】**

本発明の1つの観点において、システム及び方法は誘導記録ヘッド内に高速変化する電流を達成するために上側Hスイッチ・ドライバに最適にタイミングを取った制御信号を与える。

**【0007】**

本発明の別の観点において、システム及び方法は他の時には最小の電力消費を発生しながら誘導記録ヘッド内の電流変化中に誘導記録ヘッド電流ブーストを与える。

10

**【0008】**

本発明の1つの実施の形態は、第1及び第2上側スイッチと第1及び第2下側スイッチを有するHスイッチ・ドライバを含む書き込み電流ドライバ回路に関し、Hスイッチ・ドライバは、第1及び第2入力信号に応答して、第1上側スイッチを第1下側スイッチに接続する第1ノードと第2上側スイッチを第2下側スイッチに接続する第2ノードとの間に接続された書き込みヘッドを通じて書き込み電流を反対方向へ流すように動作する。書き込み電流ドライバ回路はさらに、第1電流パルス発生器と第1入力信号に応答して第1下側スイッチへスイッチング信号を発生するように動作する第1インバータ回路とを含み、第1インバータ回路に関連する供給電流は、第1上側スイッチに関連する書き込み電流の変化を加速するために第1上側スイッチへ高電流パルスを与えるように第1電流パルス発生器により処理される。

20

**【0009】**

本発明の別の実施の形態は、第1及び第2上側スイッチと第1及び第2下側スイッチを有するHスイッチ・ドライバを含む書き込み電流ドライバ回路に関し、Hスイッチ・ドライバは、第1及び第2入力信号に応答して、第1上側スイッチを第1下側スイッチに接続する第1ノードと第2上側スイッチを第2下側スイッチに接続する第2ノードとの間に接続された書き込みヘッドを通じて書き込み電流を反対方向へ流すように動作する。書き込み電流ドライバ回路はさらに、第1電流パルス発生手段と第1入力信号に応答して第1下側スイッチへスイッチング信号を発生する手段とを含み、スイッチング信号を発生する手段に関連する供給電流は、第1上側スイッチに関連する書き込み電流の変化を加速するために第1上側スイッチへ高電流パルスを与えるように第1電流パルス発生手段により処理される。

30

**【0010】**

本発明のさらに別の実施の形態は、磁気記録ヘッドHスイッチ・ドライバの上側スイッチと関連した書き込み電流の変化を加速する方法に関し、Hスイッチ、第1及び第2電流パルス発生器、及び第1及び第2インバータを有する書き込み電流ドライバを準備するステップと、第1入力信号に応答して第1インバータを介してHスイッチと関連した第1下側スイッチへスイッチング信号を発生するステップと、第1上側スイッチと関連した書き込み電流の変化を加速するためにHスイッチと関連した第1上側スイッチへ高電流パルスを与えるように第1電流パルス発生器を介して第1インバータと関連した供給電流を処理するステップとを含む。

40

**【0011】**

本発明の他の観点、特徴、及び利点は、添付図面と共に以下の本発明の詳細な説明を参照することにより容易に理解できるであろう。

**【0012】**

添付図は、特定の実施の形態について説明しているが、本発明の別の実施の形態も説明されるように考慮される。全ての場合、この開示は本発明の代表として説明された実施の形態であり、限定するものではない。当業者により本発明の原理の精神と範囲の中に入る数々の他の修正と実施の形態が想定できる。

**【0013】**

50

### 【発明の実施の形態】

前述のように、Hスイッチ・ドライバは記録ディスクにデータ書込むための誘導記録ヘッドへ書込み電流を供給するために磁気ディスク・ドライブ中に使用される。Hスイッチは一般に、各々がHスイッチの1つの脚を形成する4つのトランジスタ・スイッチを含む。そして、書込みヘッドコイルはHスイッチの中心スパンを横断するターミナルに接続される。Hスイッチの対向する脚のトランジスタスイッチの2つを動作させることにより、電流がコイルを通じて第1方向へ流される。同様にして、残りの2つのトランジスタスイッチを動作することにより、電流がコイルを通じて反対方向へ流される。

### 【0014】

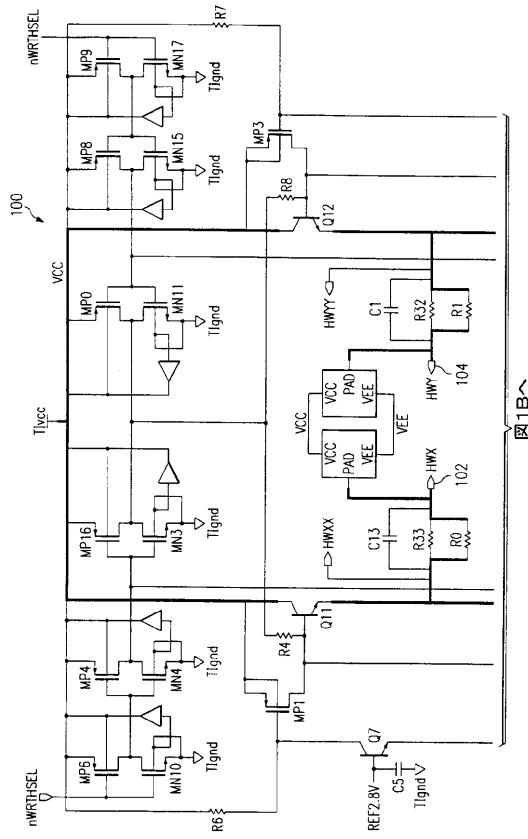

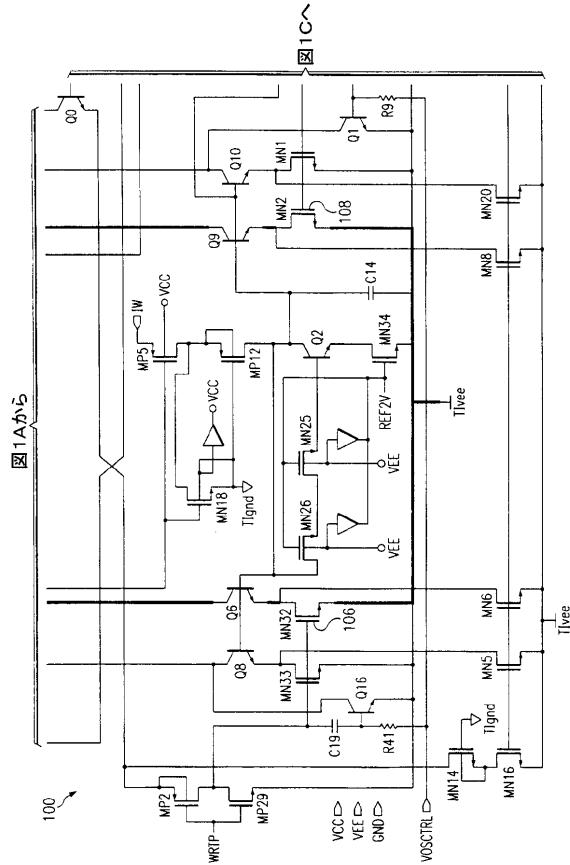

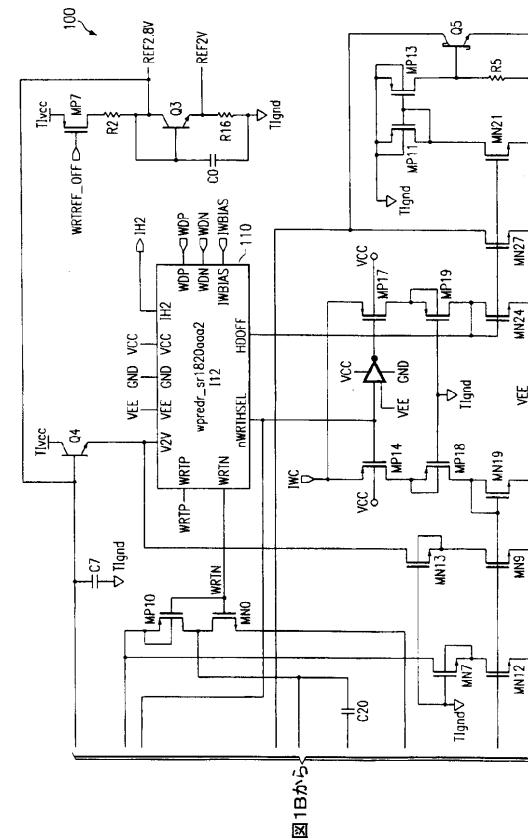

図1A乃至図1Cを参照すると、本発明の1つの実施の形態による誘導記録ヘッド用の書込みドライバ回路100の概略図が示されている。書込みドライバ回路100は、上側HスイッチNPNトランジスタQ11とQ12及び下側HスイッチNPNトランジスタQ6とQ9を有するHスイッチ・ドライバを含んでいる。

10

### 【0015】

書込み電流が、対向するHスイッチNPNトランジスタQ11とQ9が導通する時、ピンHWX102とHWY104の誘導書込みヘッドを通って流れ、そして対向する対のHスイッチNPNトランジスタQ12とQ6が導通する時に、スイッチする。スイッチング変化は高速で発生しなければならず、HスイッチNPNトランジスタは前述したように大変強固に駆動されなければならない。Hスイッチの動作に関する説明は、記録ヘッド書込みドライブ技術の当業者は既に知識を有するから、簡潔さのために好適な実施の形態ではこれ以上は説明しない。

20

### 【0016】

典型的に、トランジスタQ11とQ12のベースにそれぞれ接続されたプルアップ抵抗R4とR8は、低インピーダンスと高電流駆動をHスイッチNPNトランジスタQ11とQ12のベースのそれぞれに与えるためにかなり低い値の抵抗である。しかし、当業者に容易に理解されるようにこれらの特性は低電力消費の達成には貢献しない。前述した‘727特許は、変化中に電流パルスを与えることにより、抵抗R4と抵抗R8の値を1オーダーの大きさまで増大することができ、そしてこれらに流れる電流を減少することができる方法を記述している。しかし、‘727特許に記述された方法は、適切にタイミングが合ったパルスを与えるためには到達が遅すぎるHスイッチの対向する側の電圧スイッチングを利用する。

30

### 【0017】

図1A乃至図1Cを続いて参照すると、トランジスタQ6とQ9のそれぞれのエミッタ内のNMOS装置106、108を駆動するために使用されるインバータINV1とINV2と関連した供給電流が、変化中に適切にタイミングが合わされた電流パルスを与えるために使用される。インバータINV1とINV2は、NMOS装置106、108の十分な駆動を達成するためにコントローラから来る書込みデータ信号をバッファアすることが必要である。普通、4乃至6つのインバータのストリングが使用され、各々はHスイッチに最終的に到達する前に漸進的により強くなる。本実施の形態では、インバータ・ストリング内の最後のインバータのみがヘッド・セル内にある。本発明者は、変化中を除いてインバータの供給電流はゼロであるため、インバータINV1とINV2に関連した供給電流を使用して変化中に適切にタイミングが合った電流パルスを達成できることを認識した。例えば、インバータINV2に関連した供給電流パルスは、インバータINV2の適正な動作のためバイアスされたエミッタ・フォロワーQ7を通過して抵抗R6へ流れ、ここで電圧パルスが発生されてPMOSFETMP1のゲートに加えられる。そして、トランジスタMP1は、抵抗R4への低電流を単に使用することより達成できるよりも高速にトランジスタQ11をプルアップをするために、書込み電流変化中にHスイッチNPNトランジスタQ11のベースへ高電流パルスを与える。INV1又はINV2などのCMOSインバータからの供給電流パルスは大変短い期間であって、入力がスイッチングする間だけである。従って、PMOSプルアップ・トランジスタMP1へのパルスも大変短い期間

40

50

であるが、所望の機能を達成するには十分である。インバータIN V 2と関連した供給電流パルスは、下側HスイッチN P Nトランジスタヘドライブより先立ち、そして上側スイッチをパルスするために適切にタイミングが合わされる。同様にして、インバータIN V 1と関連した供給電流パルスは下側HスイッチN P Nトランジスタヘドライブより先立ち、そして上側HスイッチN P NトランジスタQ 1 2のベースへ高電流パルスを与るために適切にタイミングが合わせられる。書き込みドライバ回路100の1つの実施の形態は、-3Vの負の供給電源を使用し、そして、必要なロジックを与るために、+2Vが正供給接続へ供給されなければならない。従って、上述したエミッタ・フォロワー(Q7とQ12)は内部で生成される+2.8Vへ結合されるそれぞれのベース・ノードを有する。

## 【0018】

10

当業者には容易に理解されるように、インバータIN V 1とIN V 2は、必要なプルアップ信号を発生するために関連する供給電流パルスが構成される限り、限定的ではなく、NAND、NOR等を含むどんな既知のロジック機能を使用して実現できる。従って、本発明は実施の形態に限定されるものではない。さらに、パワーFET MP1とMP3は、書き込みドライバ回路100のいくつかの実現であるPNPトランジスタと置換えることができる。

## 【0019】

本発明と特に関係しないが、図1Aに示されたロジック装置は単にヘッド選択のために使用されている。従って、本発明の詳細な実施の形態に関連した抵抗R4とR8は、正の供給電源に接続されていて、ヘッドが選択された時に正の供給電源にプルアップされる。それ以外は、図1Aのインバータは抵抗R4と抵抗R8を接地して、従って、Hスイッチを使用不可にする。当業者には理解されるように、プレアンプは複数(いくつかの応用では8つまで)のヘッドを駆動でき、このような応用では8つの書き込みドライバ回路100が存在するが、通常の動作中には一時に1つのみがオンとなる。ブロック110は、書き込みデータパルス成形器であり、関連したインバータ・ストリングの最初のいくつかのインバータも含む。書き込みドライバ回路100の底を横断して示されるいくつかの10μAシンクは単に、それらのそれぞれのトランジスタが完全に遮断することを防止して、加速装置として動作する。このように、これらの装置は本発明には関係しない。

## 【0020】

20

要約すると、下側Hスイッチへスイッチング信号を加えるインバータ・ストリング内のインバータからの供給電流が、上側Hスイッチへプルアップ信号を与えるPMOS装置を駆動するために使用される。書き込み電流の変化時において、誘導負荷(記録ヘッド)内の電流の高速な変化を発生するために、書き込みドライバ内の回路は非常に高速に反応しなければならない。現代の方法は一般に書き込みヘッドの適切な性能を達成するために50%又はそれ以上の書き込み電流オーバーシュートを必要とする。そのため、ヘッドドライバ回路でHスイッチをプルアップする大きな必要性が存在する。しかし、これとは逆に、低電力消費が維持されなければならない。本発明は、他の時に電力消費を最小にしながら、書き込み電流変化中にはプルアップ電流をブーストすることにより、書き込みドライバ性能を増強する解決を与える。

## 【0021】

30

以上の記載に関連して、以下の各項を開示する。

## 【0022】

1. 書込み電流ドライバ回路であって、

第1及び第2上側スイッチと第1及び第2下側スイッチとを有し、第1及び第2入力信号に応答して、第1上側スイッチを第1下側スイッチへ接続する第1ノードと第2上側スイッチを第2下側スイッチに接続する第2ノードとの間に接続された書き込みヘッドを通じて反対方向に書き込み電流を流す、Hスイッチドライバと、

第1電流パルス発生器と、

第1入力信号に応答して、第1下側スイッチへのスイッチング信号を発生するように動作する第1インバタ回路であって、この第1インバタ回路に関連した供給電流が第1上

40

50

側スイッチと関連した書き込み電流の変化を加速するために第1上側スイッチへ高電流パルスを与えるように第1電流パルス発生器により処理される、第1インバータ回路とを備える書き込み電流ドライバ回路。

**【0023】**

2. 第2電流パルス発生器と、

第2入力信号に応答して、第2下側スイッチへのスイッチング信号を発生するように動作する第2インバータ回路であって、この第2インバータ回路に関連した供給電流が第2上側スイッチと関連した書き込み電流の変化を加速するために第2上側スイッチへ高電流パルスを与えるように第2電流パルス発生器により処理される、第2インバータ回路とをさらに備える1項に記載の書き込み電流ドライバ回路。 10

**【0024】**

3. 第1及び第2電流パルス発生器の各々が、

それぞれのインバータ回路を適切に動作するためにバイアスされていて電圧パルスを発生するように動作するエミッターフォロワーと、

電圧パルスに応答して、高電流パルスを発生するように動作するパワーMOSFET装置と

を含む2項に記載の書き込み電流ドライバ回路。

**【0025】**

4. 第1電流パルス発生器が、

第1インバータ回路を適切に動作するためにバイアスされていて電圧パルスを発生するように動作するエミッターフォロワーと、

電圧パルスに応答して、高電流パルスを発生するように動作するパワーMOSFET装置と

を含む1項に記載の書き込み電流ドライバ回路。 20

**【0026】**

5. 書込み電流ドライバ回路であって、

第1及び第2上側スイッチと第1及び第2下側スイッチとを有し、第1及び第2入力信号に応答して、第1上側スイッチを第1下側スイッチへ接続する第1ノードと第2上側スイッチを第2下側スイッチに接続する第2ノードとの間に接続された書き込みヘッドを通じて反対方向に書き込み電流を流す、Hスイッチドライバと、 30

第1電流パルスを発生する手段と、

第1入力信号に応答して、第1下側スイッチへのスイッチング信号を発生する手段であって、この第1下側スイッチへのスイッチング信号を発生する手段に関連した供給電流が第1上側スイッチと関連した書き込み電流の変化を加速するために第1上側スイッチへ高電流パルスを与えるように第1電流パルスを発生する手段により処理される、第1下側スイッチへのスイッチング信号を発生する手段と

を備える書き込み電流ドライバ回路。

**【0027】**

6. 第2電流パルスを発生する手段と、

第2入力信号に応答して、第2下側スイッチへのスイッチング信号を発生する手段であって、この第2下側スイッチへのスイッチング信号を発生する手段に関連した供給電流が第2上側スイッチと関連した書き込み電流の変化を加速するために第2上側スイッチへ高電流パルスを与えるように第2電流パルスを発生する手段により処理される、第2下側スイッチへのスイッチング信号を発生する手段と

をさらに備える5項に記載の書き込み電流ドライバ回路。 40

**【0028】**

7. 第1電流パルスを発生する手段及び第2電流パルスを発生する手段がそれぞれ、

電圧パルスを発生する手段と、

電圧パルスに応答して高電流パルスを発生する手段と

を備える6項に記載の書き込み電流ドライバ回路。 50

**【0029】**

8. 第1電流パルスを発生する手段が、

電圧パルスを発生する手段と、

電圧パルスに応答して高電流パルスを発生する手段と

を備える5項に記載の書き込み電流ドライバ回路。

**【0030】**

9. 磁気記録ヘッドHスイッチドライバの上側スイッチと関連した書き込み電流の変化を加速する方法であって、

Hスイッチと、第1及び第2電流パルス発生器と、第1及び第2インバータとを有する書き込み電流ドライバを準備するステップと、

第1入力信号に応答して、Hスイッチと関連した第1下側スイッチへ第1インバータを介してスイッチング信号を発生するステップと、

Hスイッチと関連した第1上側スイッチと関連した書き込み電流の変化を加速するために第1上側スイッチへ高電流パルスを与えるように第1電流パルス発生器を介して第1インバータと関連した供給電流を処理するステップと

を含んだ方法。

10

**【0031】**

10. 第2入力信号に応答して、Hスイッチと関連した第2下側スイッチへ第2インバータを介してスイッチング信号を発生するステップと、

Hスイッチと関連した第2上側スイッチと関連した書き込み電流の変化を加速するために第2上側スイッチへ高電流パルスを与えるように第2電流パルス発生器を介して第2インバータと関連した供給電流を処理するステップと

をさらに含んだ9項に記載の方法。

20

**【0032】****【発明の効果】**

以上の説明から、本発明は誘導記録ヘッド書き込みドライバの技術において顕著な利益を提供することが理解できる。さらに、ディスクドライブ技術の当業者に新しい原理を応用して必要に応じてこのような特別なコンポーネントを使用するのに必要な情報を提供するために、本発明が十分に詳細に説明された。以上の説明から、本発明は従来技術と比較して構成と作用において顕著に異なることが理解される。本発明の特定の実施の形態がここに詳細に説明されたが、特許請求の範囲の記載により定義される本発明の範囲と精神から逸脱することなく、さまざまな変形、修正、置換が可能であることが理解できる。

30

**【図面の簡単な説明】**

【図1A】本発明の1つの実施の形態による誘導記録ヘッドの書き込みドライバ回路を示す概略図。

【図1B】本発明の1つの実施の形態による誘導記録ヘッドの書き込みドライバ回路を示す概略図。

【図1C】本発明の1つの実施の形態による誘導記録ヘッドの書き込みドライバ回路を示す概略図。

**【符号の説明】**

40

|       |                  |

|-------|------------------|

| 100   | 書き込みドライバ回路       |

| 102   | ピン               |

| 104   | ピン               |

| Q6    | 下側HスイッチNPNトランジスタ |

| Q7    | エミッタフォロワ         |

| Q9    | 下側HスイッチNPNトランジスタ |

| Q11   | 上側HスイッチNPNトランジスタ |

| Q12   | 上側HスイッチNPNトランジスタ |

| M P 1 | PMOSFET          |

| M P 3 | PMOSFET          |

50

【図 1 A】

【図 1 B】

【図 1 C】

---

フロントページの続き

(74)代理人 100074228

弁理士 今城 俊夫

(74)代理人 100084009

弁理士 小川 信夫

(74)代理人 100082821

弁理士 村社 厚夫

(74)代理人 100086771

弁理士 西島 孝喜

(74)代理人 100084663

弁理士 箱田 篤

(72)発明者 ジョン ジェイ プライス

アメリカ合衆国 ミネソタ州 55439 エディーナ グリーソン ロード 6500

審査官 中村 豊

(56)参考文献 特開2000-268309(JP,A)

特開平06-301907(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11B 5/09