(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-149720

(P2015-149720A)

(43) 公開日 平成27年8月20日(2015.8.20)

| (51) Int.Cl.                  | F 1         | テーマコード (参考) |

|-------------------------------|-------------|-------------|

| <b>HO3K 17/687 (2006.01)</b>  | HO3K 17/687 | G 5FO38     |

| <b>HO1L 21/8234 (2006.01)</b> | HO1L 27/06  | 1O2A 5FO48  |

| <b>HO1L 27/06 (2006.01)</b>   | HO1L 27/08  | 1O2H 5JO55  |

| <b>HO1L 27/088 (2006.01)</b>  | HO1L 27/04  | M           |

| <b>HO1L 21/822 (2006.01)</b>  | HO3K 17/04  | E           |

審査請求 未請求 請求項の数 20 O L 外国語出願 (全 14 頁) 最終頁に続く

|              |                            |          |                                                                                                                                                                                                                   |

|--------------|----------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2015-19167 (P2015-19167) | (71) 出願人 | 599034594<br>トライクイント・セミコンダクター・イン<br>コーポレイテッド<br>TriQuint Semiconductor, Inc.<br>アメリカ合衆国オレゴン州97124・ヒ<br>ルスボロ・ノースイーストブルックウッド<br>パークウェイ 2300<br>2300 NE Brookwood P<br>arkway, Hillsboro, Or<br>egon 94124, U. S. A. |

| (22) 出願日     | 平成27年2月3日(2015.2.3)        |          |                                                                                                                                                                                                                   |

| (31) 優先権主張番号 | 14/172,727                 |          |                                                                                                                                                                                                                   |

| (32) 優先日     | 平成26年2月4日(2014.2.4)        |          |                                                                                                                                                                                                                   |

| (33) 優先権主張国  | 米国(US)                     | (74) 代理人 | 100105924<br>弁理士 森下 賢樹                                                                                                                                                                                            |

最終頁に続く

(54) 【発明の名称】電界効果トランジスタスイッチ回路

(57) 【要約】 (修正有)

【課題】超高速、かつ、超低損失で高い分離性のスイッチを提供する。

【解決手段】nチャネルトランジスタを含む第1スイッチと、第1スイッチに接続される第2スイッチとを備え、第2スイッチは、第1ソース、第1ドレイン、第1ゲート、第1ボディコンタクトを有するpチャネルスイッチトランジスタと、第2ソース、第2ドレイン、第2ゲート、第2ボディコンタクトを有する放電用pチャネルトランジスタとを有する。第1ゲートと第2ドレインが接続され、第1ボディコンタクトが第2ソースに接続され、第1ドレインと第1ソース間に接続される第1抵抗、第2抵抗との接続点に第2ゲートを接続する。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

n チャネルトランジスタを含む第 1 スイッチと、

前記第 1 スイッチに接続される第 2 スイッチと、を備え、

前記第 2 スイッチは、

第 1 ソースコンタクトと、第 1 ドレインコンタクトと、第 1 ゲートコンタクトと、第 1 ボディコンタクトとを含む第 1 p チャネルトランジスタと、

前記第 1 p チャネルトランジスタに接続され、第 2 ソースコンタクトと、第 2 ドレインコンタクトと、第 2 ゲートコンタクトと、第 2 ボディコンタクトとを含み、前記第 1 ゲートコンタクトが前記第 2 ドレインコンタクトに接続され、前記第 1 ボディコンタクトが前記第 2 ソースコンタクトに接続される第 2 p チャネルトランジスタと、

前記第 2 ゲートコンタクトに双方が接続される第 1 抵抗および第 2 抵抗と、

を含むことを特徴とするスイッチ回路。

**【請求項 2】**

前記第 1 抵抗または前記第 2 抵抗は、高密度抵抗であることを特徴とする請求項 1 に記載のスイッチ回路。

**【請求項 3】**

前記第 1 p チャネルトランジスタは、1 ミリメートル (mm) の厚さを有することを特徴とする請求項 1 に記載のスイッチ回路。

**【請求項 4】**

前記第 2 p チャネルトランジスタは、3 マイクロメートル (μm) の厚さを有する請求項 1 に記載のスイッチ回路。

**【請求項 5】**

前記第 1 ソースコンタクトは、少なくとも第 3 p チャネルトランジスタおよび第 4 p チャネルトランジスタを含む第 3 スイッチに接続されることを特徴とする請求項 1 に記載のスイッチ回路。

**【請求項 6】**

前記第 1 p チャネルトランジスタまたは前記第 2 p チャネルトランジスタは、p チャネル金属酸化物半導体電界効果トランジスタ (MOSFET) であることを特徴とする請求項 1 に記載のスイッチ回路。

**【請求項 7】**

前記第 1 ゲートコンタクトは、直流電圧入力源に接続される請求項 1 に記載のスイッチ回路。

**【請求項 8】**

前記第 1 スイッチは、前記第 1 p チャネルトランジスタが前記第 1 スイッチに直接接続され、かつ、前記第 1 p チャネルトランジスタが前記第 1 スイッチと当該スイッチ回路のグランドコンタクトの間となるように、前記第 2 スイッチに接続されることを特徴とする請求項 1 に記載のスイッチ回路。

**【請求項 9】**

第 1 p チャネル電界効果トランジスタ (FET) のゲートコンタクトを第 2 p チャネル FET のドレインコンタクトに接続するステップと、

前記第 1 p チャネル FET のボディコンタクトを前記第 2 p チャネル FET のソースコンタクトに接続するステップと、

前記第 2 p チャネル FET のゲートコンタクトを第 1 抵抗および第 2 抵抗に接続するステップと、

前記第 1 p チャネル FET が電気的に n チャネル FET とグランドの間に位置するよう、前記第 1 p チャネル FET のドレインコンタクトおよび前記第 1 抵抗を前記 n チャネル FET に接続するステップと、を備えることを特徴とする方法。

**【請求項 10】**

前記第 1 抵抗または前記第 2 抵抗は、高密度抵抗であることを特徴とする請求項 9 に記

10

20

30

40

50

載の方法。

【請求項 1 1】

前記第 1 p チャネル F E T は、 1 ミリメートル ( m m ) の厚さを有することを特徴とする請求項 9 に記載の方法。

【請求項 1 2】

前記第 2 p チャネル F E T は、 3 マイクロメートル (  $\mu$  m ) の厚さを有することを特徴とする請求項 9 に記載の方法。

【請求項 1 3】

前記第 1 p チャネル F E T 、前記第 2 p チャネル F E T 、前記第 1 抵抗および前記第 2 抵抗は、第 1 スイッチであり、

前記第 1 p チャネル F E T のソースコンタクトは、第 3 p チャネル F E T を含む第 2 スイッチに接続されることを特徴とする請求項 9 に記載の方法。

【請求項 1 4】

前記第 1 p チャネル F E T または前記第 2 p チャネル F E T は、 p チャネル金属酸化物半導体 F E T ( M O S F E T ) であることを特徴とする請求項 9 に記載の方法。

【請求項 1 5】

信号入力と、

電気的に前記信号入力と信号出力の間に位置し、 n チャネル電界効果トランジスタ ( F E T ) を含む第 1 スイッチと、

電気的に前記信号入力とグランドの間に位置し、電気的に前記第 1 スイッチと前記グランドの間に接続される第 2 スイッチと、を備え、

前記第 2 スイッチは、

第 1 p チャネル F E T と、

前記第 1 p チャネル F E T に接続されるとともに、前記第 1 p チャネル F E T のゲートコンタクトに接続されるドレインコンタクトと、前記第 1 p チャネル F E T のボディコンタクトに接続されるソースコンタクトとを含む第 2 p チャネル F E T と、

前記第 2 p チャネル F E T のゲートコンタクトに双方が接続される第 1 抵抗および第 2 抵抗と、

を含むことを特徴とするシステム。

【請求項 1 6】

前記第 1 抵抗または前記第 2 抵抗は、高密度抵抗であることを特徴とする請求項 1 5 に記載のシステム。

【請求項 1 7】

前記第 1 p チャネル F E T は、 1 ミリメートル ( m m ) の厚さを有することを特徴とする請求項 1 5 に記載のシステム。

【請求項 1 8】

前記第 2 p チャネル F E T は、 3 マイクロメートル (  $\mu$  m ) の厚さを有することを特徴とする請求項 1 5 に記載のシステム。

【請求項 1 9】

第 3 p チャネル F E T および第 4 p チャネル F E T を含む第 3 スイッチをさらに備え、前記第 1 p チャネル F E T のソースコンタクトは、前記第 3 p チャネル F E T のドレインコンタクトに接続されることを特徴とする請求項 1 5 に記載のシステム。

【請求項 2 0】

前記第 1 p チャネル F E T または前記第 2 p チャネル F E T は、 p チャネル金属酸化物半導体 F E T ( M O S F E T ) であることを特徴とする請求項 1 5 に記載のシステム。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本開示の実施の形態は、広く回路の分野に関し、特にスイッチ回路に関する。

【背景技術】

10

20

30

40

50

## 【0002】

電界効果トランジスタ（FET）は、低電力の無線周波数（RF；radio frequency）スイッチデバイスとして用いられ、特に、価格、性能および電力消費量が重要な要素であるモバイル用途に用いられる。しかしながら、より大きな信号を扱うときにFETは足かせとなりうる。特に、スイッチとして機能するFETにおける大信号動作は、FETのボディの準中性領域に蓄積される電荷に影響される。電荷の蓄積は、ホットキャリアの蓄積、過剰なゲート誘導ドレインリーク（GIDL；gate-induced drain leakage）、負のトランスクンダクタンス、ゲート制御の喪失、ヒステリシスなどにつながりうる。これらの問題は、一般にフローティングボディ効果（FBE；floating body effect）と称されうる。

10

## 【0003】

いくつかの用途の中で、ある用途では超高速、かつ、超低損失で高い分離性のスイッチが求められる。いくつかの場合、低損失なスイッチは、要求される低損失および分離を実現し、また、大信号の要件を満たすために用いられる負電圧発生器（NVG；negative voltage generator）を必要としうる。しかしながら、NVGを用いると、より遅いスイッチにつながりうるとともに、回路面積の観点から大幅な付帯的コストにつながりうる。さらに、NVGを用いると、回路が能動的に信号を伝送していない状態である休止モードにおいて、漏れ電流が生じる結果となりうる。いくつかの場合、上述の問題に対処するために阻止コンデンサがスイッチに用いられるが、阻止コンデンサを用いると、回路面積の増大につながるとともに、回路性能の低下にもつながりうる。

20

## 【図面の簡単な説明】

## 【0004】

実施の形態は、例示を目的とし、添付の図面の記載に限定されないことを目的として例示される。添付の図面において同種の要素には同種の符号が付される。

## 【0005】

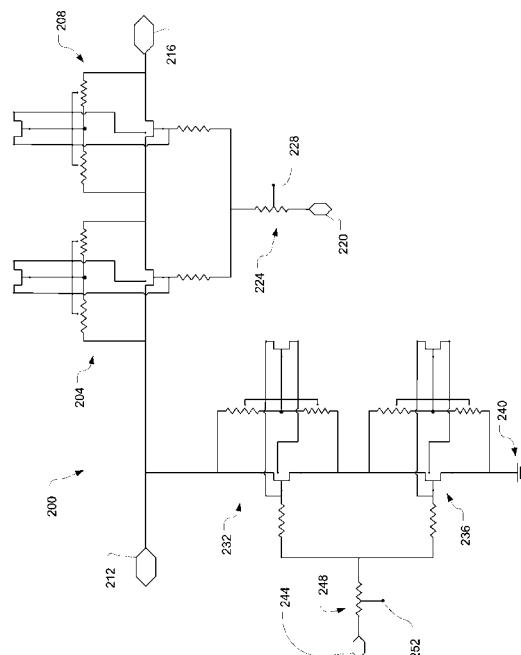

【図1】様々な実施の形態に係る電界効果トランジスタ（FET）スイッチを示す図である。

## 【0006】

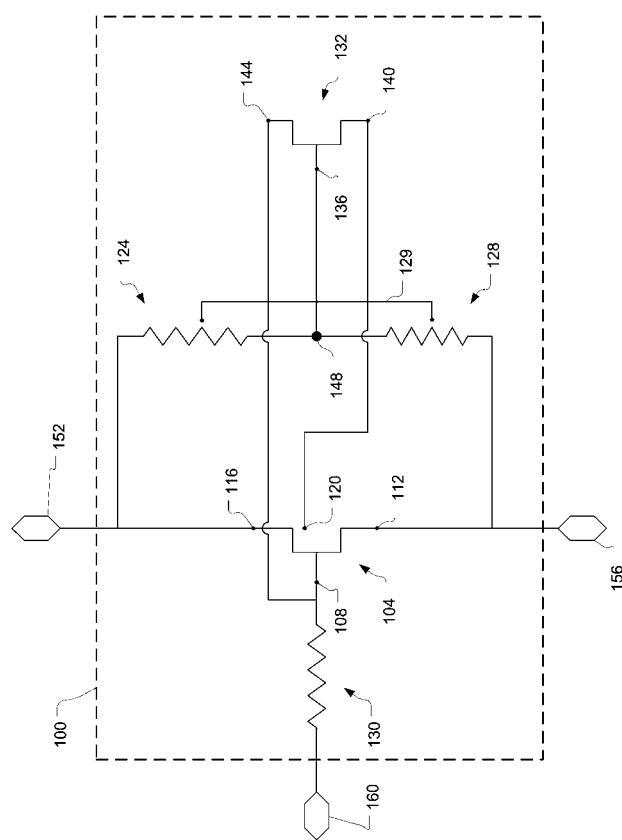

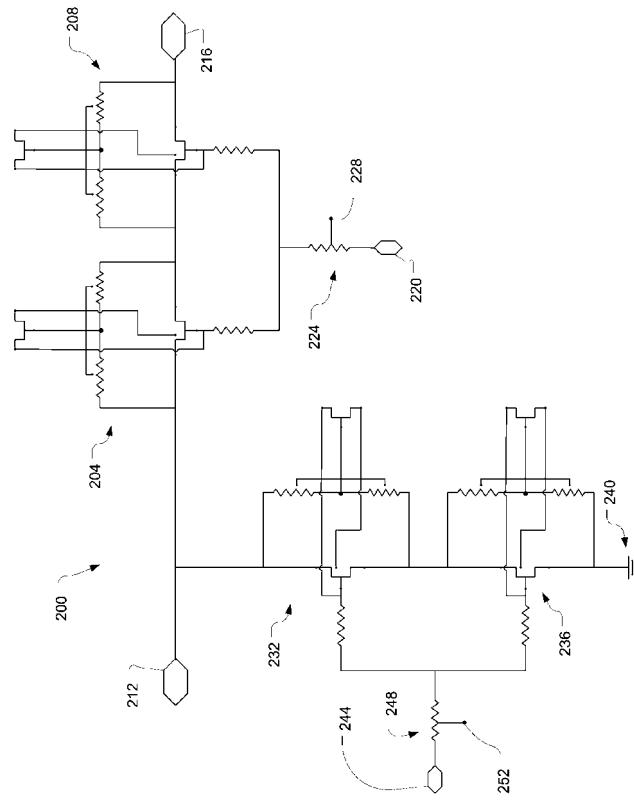

【図2】様々な実施の形態に係る複数のスイッチが組み込まれたスイッチ回路を示す図である。

30

## 【0007】

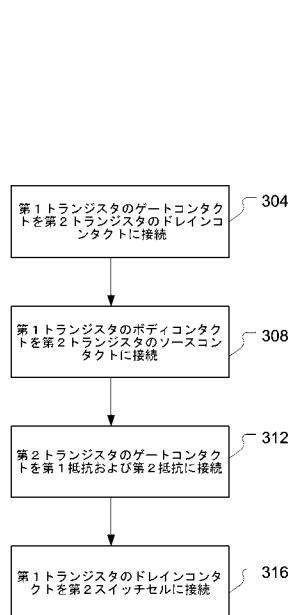

【図3】様々な実施の形態に係るスイッチ回路の製造プロセスの例を示す図である。

## 【0008】

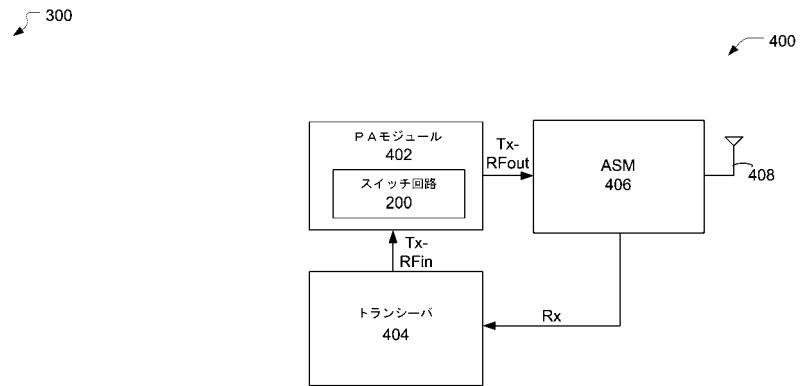

【図4】様々な実施の形態に係る無線通信デバイスの例を示すブロック図である。

## 【発明を実施するための形態】

## 【0009】

実施の形態は、スイッチ回路を含む。いくつかの実施の形態において、スイッチ回路は、nチャネルスイッチトランジスタを含む第1スイッチを信号経路上に含んでもよい。nチャネルスイッチトランジスタは、nチャネル電界効果トランジスタ（FET）であってもよい。スイッチ回路は、第1スイッチへの分岐路上に第2スイッチをさらに含んでもよい。第2スイッチは、スイッチトランジスタと、スイッチトランジスタのボディに放電経路を与えるための放電トランジスタと、を含んでもよい。スイッチトランジスタおよび放電トランジスタは、pチャネルトランジスタであってもよく、より具体的には、pチャネルFETであってもよい。nチャネルトランジスタとpチャネルトランジスタの双方は、スイッチに正の電圧を与えるように構成される電圧源に接続されてもよい。電圧源が正の電圧を与えるとき、nチャネルスイッチトランジスタを含むスイッチは、スイッチを通じて無線周波数（RF）信号が伝わることをスイッチが許容するようにしてオンとなってもよい。同時に、pチャネルトランジスタを含むスイッチは、正の電圧に起因してオフとなってもよい。その後、正の電圧が解除されるか、もしくは、負の電圧が印加されてもよく、また、nチャネルトランジスタを含むスイッチがオフになる一方で、pチャネルトラン

40

50

ジスタを含むスイッチがオンになってもよい。他の実施の形態は、本明細書および請求項に記載されうる。

【0010】

例示される実施の形態に係る様々な態様は、当業者にとって一般的に採用される用語を用いて他の当業者に本発明の本質を伝えるために示される。しかしながら、以下に示されるいくつかの要素のみを用いて代替的な実施の形態を実施しうることは、当業者にとって明らかであろう。説明のために、特定の装置または構成は、例示される実施の形態の詳細な理解を与えるために示される。しかし、当業者にとって、代替的な実施の形態を具体的な細部を省いて実施しうることは明らかであろう。他の例では、例示される実施の形態を不明確としないために、周知な特徴は除外され、もしくは単純化される。

10

【0011】

さらに、様々な動作は、複数の個別の動作として本開示の理解を最も助ける形で順に示される。しかしながら、記載の順序は、これらの動作が必ずしも順序依存であることを示すものであるとして解釈されるべきはない。特に、これらの動作は、説明される順序で実行される必要はない。

【0012】

「一つの実施の形態において」の語は、繰り返し用いられる。この語は、ほとんどの場合において、同じ実施の形態を参照するものではないが、同じ実施の形態を参照するかもしれない。「備える」、「有する」および「含む」の語は、文脈において別に規定されない限り、同義語である。

20

【0013】

種々の実施の形態の結合に用いうる用語に対し、文脈上の明確性を与えるため、「A / B」および「A および / または B」の語は、(A)、(B)または(A および B)を意味することとする。また、「A、B および / または C」の語は、(A)、(B)、(C)、(A および B)、(A および C)、(B および C)または(A、B および C)を意味する。

【0014】

「～と接続される」の語は、ここでは、派生的に用いられる。「接続される」は、以下に示す以上の意味で用いられる。「接続される」は、二以上の要素が物理的または電気的に直接接触することを意味しうる。しかしながら、「接続される」は、二以上の要素が互いに間接的に接触しつつ互いに協働または相互作用することも意味し、また、一つ以上の他の要素が、上述の意味で互いに接続された要素間において結合または接続されることを意味しうる。

30

【0015】

図1は、様々な実施の形態に係るスイッチ100を示す。スイッチ100は、埋め込み酸化膜(BOX; buried oxide)層とも称されうる絶縁層上に設けられるシリコン層を有するシリコン・オン・インシュレータ(SOI)デバイスであってもよい。いくつかの実施の形態において、絶縁層の下に追加のシリコン層が設けられてもよい。

【0016】

様々な実施の形態において、上部シリコン層は、約50～90nmの厚さであってもよくなり、二酸化シリコンまたはサファイアでありうる絶縁層は、約100～200nmの厚さであってもよい。いくつかの実施の形態において、スイッチ100は、ドープチャネル下が部分的に可動電荷キャリアの枯渇されたシリコンとなる部分空乏型SOI(PDSOI、P-D; partially-depleted)であってもよい。部分的に枯渇された領域は、準中性領域(quasi-neutral region)とも称されうる。

40

【0017】

スイッチ100は、スイッチトランジスタ104を含んでもよい。いくつかの実施の形態において、スイッチトランジスタ104は、電界効果トランジスタ(FET)であってもよい。いくつかの実施の形態において、スイッチトランジスタ104は、上述の準中性領域において電荷を蓄積する特性を有してもよい。本明細書に記載される実施の形態は、

50

この蓄積される電荷の放電を提供するとともに、フローティングボディ効果( F B E )問題に対処するために考案された他の技術に関連して識別された上述の問題の少なくとも一部を軽減する。

【0018】

スイッチトランジスタ104は、ゲートコンタクト108と、ソースコンタクト112と、ドレインコンタクト116と、ボディコンタクト120とを含んでもよい。スイッチ100は、互いに直列に接続されるとともに、さらに図示されるようにソースコンタクト112とドレインコンタクト116の間に接続される抵抗124及び128をさらに含んでもよい。抵抗124及び128は、いくつかの実施の形態において、同じ大きさであってもよい。いくつかの実施の形態において、抵抗124及び128は、高密度抵抗であってもよい。いくつかの実施の形態において、抵抗124及び128は、制御線129によって接続されてもよい。スイッチ100は、ゲートコンタクト108に接続される抵抗130をさらに含んでもよい。

10

【0019】

スイッチ100は、放電トランジスタ132をさらに含んでもよい。いくつかの実施の形態において、放電トランジスタ132は、FETであってもよい。放電トランジスタ132は、スイッチトランジスタ104の準中性領域に蓄積される電荷を放電するための放電経路を生成するように機能してもよい。放電トランジスタ132は、ゲートコンタクト136と、ソースコンタクト140と、ドレインコンタクト144を含んでもよい。ゲートコンタクト136は、抵抗124及び128の間に位置するノード148に接続されてもよく、ソースコンタクト140は、ボディコンタクト120に接続されてもよく、ドレインコンタクト144は、ゲートコンタクト108に接続されてもよい。

20

【0020】

抵抗124及び128は、ノード148において、したがって、ゲートコンタクト136において、仮想グランド(例えば、固定された電位)を提供してもよい。ボディコンタクト120、ドレインコンタクト116およびソースコンタクト112をノード148の固定電位に結合するための放電トランジスタ132を用いることで、ゲートコンタクト108とボディコンタクト120の間の電位差の除去を促進させ、その結果、準中性領域からの電荷の放電を促進させてもよい。

30

【0021】

いくつかの実施の形態において、ドレインコンタクト116は、直接もしくは間接的に無線周波数( RF )信号入力端子152に接続されてもよい。スイッチ100は、RF信号入力端子152を通じてRF信号を受信してもよい。ソースコンタクト112は、直接もしくは間接的にRF信号出力端子156に接続されてもよい。RF信号は、スイッチ100によってRF信号出力端子156から出力されてもよい。ゲートコンタクト108および/またはドレインコンタクト144は、直接もしくは間接的に電圧源160に接続されてもよい。電圧源160は、後述されるように、スイッチトランジスタ104および放電トランジスタ132をオンまたはオフにするための制御電圧を供給してもよい。

【0022】

実施の形態において、スイッチ100は以下のように動作してもよい。なお、下記の記載では、スイッチトランジスタ104および放電トランジスタ132の双方がnチャネルFETであると仮定している。しかしながら、後述されるように、いくつかの実施の形態において、スイッチトランジスタ104および放電トランジスタ132の双方がpチャネルFETであってもよく、この場合には動作が逆となってもよい。

40

【0023】

最初に、スイッチ100は、スイッチトランジスタ104をオンにすることによりオンにされ、例えばRF信号入力端子152から受信する無線周波数( RF )信号などの信号をドレインコンタクト116からソースコンタクト112へ通過させてもよい。いくつかの実施の形態において、スイッチトランジスタ104は、例えば2.5Vの正の直流電圧をスイッチトランジスタ132のゲートコンタクト108に印加することによりオンにさ

50

れてもよく、例えば、電圧源 160 からの正の直流電圧が印加されてもよい。放電トランジスタ 132 のドレインコンタクト 144 もまた正の直流電圧を参照するであろう。放電トランジスタ 132 のゲートコンタクト 136 は、仮想グランドにおける 0V を参照してもよい。これにより、放電トランジスタ 132 におけるゲート - ソース間電圧  $V_{gs}$  が -2.5V となってもよい。これにより放電トランジスタ 132 はオフとなり、放電トランジスタ 132 が事実上スイッチ回路から取り除かれてよい。

#### 【0024】

いくつかの実施の形態において、ゲートコンタクト 108 とスイッチトランジスタ 104 のボディコンタクト 120 の間の放電経路を提供するために、スイッチ 100 はオフにされてもよい。いくつかの実施の形態において、スイッチ 100 は、スイッチトランジスタ 104 をオフにすることによりオフにされ、例えば RF 信号入力端子 152 から受信する無線周波数 (RF) 信号などの信号がドレインコンタクト 116 からソースコンタクト 112 へ通過するのを妨げてもよい。いくつかの実施の形態において、スイッチトランジスタ 104 は、スイッチトランジスタ 104 のゲートコンタクト 108 に直流電圧を印加しないか、負の直流電圧 (例えば、0V または -2.5V) を印加することにより、オフにされてもよい。放電トランジスタ 132 のドレインコンタクト 144 もまた負の直流電圧を参照してもよい。これにより、放電トランジスタ 132 において例えば 2.5V の正の  $V_{gs}$  となってもよい。これにより、放電トランジスタ 132 がオンとなって、スイッチトランジスタ 104 のゲートコンタクト 108 とスイッチトランジスタ 104 のボディコンタクト 120 を結合することによる放電経路を形成してもよい。これは、閾値電圧 ( $V_{th}$ ) の低下が生じないであろう電圧許容値 (voltage headroom) を与えなければならぬことなしに実現されてもよい。

10

20

30

#### 【0025】

スイッチ 100 の動作が主にスイッチトランジスタ 104 として n チャネル FET (「NMOS スイッチ」または「NMOS トランジスタ」ともいう) を用いる観点で説明がなされるが、スイッチトランジスタ 104 および放電トランジスタ 132 として p チャネル FET などの p チャネルトランジスタ (「PMOS スイッチ」または「PMOS トランジスタ」ともいう) を用いる実施の形態が用いられてもよい。スイッチトランジスタ 104 および放電トランジスタ 132 が p チャネルトランジスタである実施の形態において、正電圧の印加により p チャネルトランジスタをオフにする一方で、負電圧の印加または電圧を印加しないことにより n チャネルトランジスタをオンにしてもよい。

#### 【0026】

上述のようなスイッチ 100 を用いて放電経路を与えることは、ダイオード接続 FET スイッチ回路に伴う電圧閾値許容量 (voltage threshold headroom) に関連した同様の不利益を招かないかもしれない。ダイオード接続 FET スイッチ回路に対して、スイッチ 100 は、相互変調歪み (IMD) について 3dB の向上、第 3 次高調波について 2.5dB の向上、第 2 次高調波について 1.5dB の向上を伴うというシミュレーション例が示されている。

#### 【0027】

上述のようなスイッチ 100 を用いて放電経路を与えることは、抵抗性ボディコンタクト (BC) スイッチ回路に伴う挿入損失に関連した同様の不利益をも招かないかもしれない。抵抗性 BC スイッチ回路に対して、スイッチ 100 は、挿入損失について 40m dB 以上の向上、第 2 次高調波について 3.5dB の向上、第 3 次高調波について 0.5dB の向上を伴うというシミュレーション例が示されている。

40

#### 【0028】

スイッチ 100 は、ゲート接地増幅器であってもよいし、相補型金属酸化膜半導体 (CMOS) スイッチ、パワー増幅器、低雑音増幅器 (LNA; low-noise amplifier)、バッファ、デュブレクサなどを含むがこれらに限定されない多くの用途に組み込まれてもよい。

#### 【0029】

50

いくつかの実施の形態において、複数のスイッチ 100 は、一つの回路設計に組み込まれてもよい。図 2 は、それぞれが上述のスイッチ 100 と同様であってよい—以上のスイッチを包含するスイッチ回路 200 の例を示す。具体的には、スイッチ回路 200 は、スイッチ 204 および 208 を含んでもよい。スイッチ 204 および 208 は、主に RF 信号入力端子 152 および RF 信号出力端子 156 のそれぞれと同様の RF 信号入力 212 および RF 信号出力 216 の間の位置において、これらに接続されてもよい。スイッチ 204 および 208 は、それぞれ上述のスイッチ 100 と同様であってもよく、スイッチ 204 および 208 のスイッチトランジスタおよび放電トランジスタの双方は、上述のように n チャネルトランジスタ、より具体的には n チャネル FET であってもよい。図 2 に示されるように、スイッチ 204 および 208 は、スイッチ 204 のスイッチトランジスタのソースコンタクトがスイッチ 208 のスイッチトランジスタのドレインコンタクトに接続されるようにして、互いに直列に接続されてもよい。

10

#### 【0030】

いくつかの実施の形態において、スイッチ 204 および 208 は、例えば 2.5V の正電圧を与えるように構成される電圧源 220 に接続されてもよい。いくつかの実施の形態において、抵抗 224 は、主に電圧源 220 とスイッチ 204 および 208 の間に位置してもよい。いくつかの実施の形態において、抵抗 224 は制御線 228 を含んでもよい。いくつかの実施の形態において、電圧源 220 は上述の電圧源 160 と同様であってもよい。

20

#### 【0031】

スイッチ回路 200 は、追加のスイッチ 232 および 236 を含んでもよい。スイッチ 232 および 236 は、主に RF 信号入力 212 とグランド 240 の間に位置してもよい。具体的には、スイッチ回路 200 の分岐路上にあると言わってもよい。いくつかの実施の形態において、スイッチ 232 および 236 は、例えば 2.5V の正電圧を与えるように構成される電圧源 244 に接続されてもよい。いくつかの実施の形態において、電圧源 244 および電圧源 220 は同一の電圧源であってもよいし、または、互いに接続された別の電圧源であってもよい。いくつかの実施の形態において、抵抗 248 は、主に電圧源 244 とスイッチ 232 および 236 の間に位置してもよい。いくつかの実施の形態において、抵抗 248 は制御線 252 を含んでもよい。

30

#### 【0032】

スイッチ 232 および 236 は、上述のスイッチ 100 とそれぞれ同様であってもよく、スイッチ 232 および 236 のスイッチトランジスタおよび放電トランジスタの双方は、上述のように p チャネルトランジスタ、より具体的には p チャネル FET であってもよい。図 2 に示されるように、スイッチ 232 および 236 は、スイッチ 232 のスイッチトランジスタのソースコンタクトがスイッチ 236 のスイッチトランジスタのドレインコンタクトに接続されるようにして、互いに直列に接続されてもよい。

30

#### 【0033】

スイッチ回路 200 は、n チャネルトランジスタを有する二つのスイッチ 204 および 208 と、p チャネルトランジスタを有する二つのスイッチ 232 および 236 とを有するように説明されるが、他の実施の形態においては、スイッチ回路はより多く、もしくは、より少ないスイッチを有してもよい。いくつかの実施の形態において、スイッチ 204 およびスイッチ 208 が p チャネルトランジスタを有し、スイッチ 232 および 236 が n チャネルトランジスタを有し、電圧源 220 および 224 が負電圧を与えるように構成されてもよい。

40

#### 【0034】

動作時に、スイッチ回路 200 は以下のように動作してもよい。RF 信号が RF 信号入力 212 に供給されてもよい。電圧源 220 および 244 において正の電圧が供給されてもよい。上述のように、スイッチ 204 および 208 は、n チャネル FET を含んでもよい。スイッチ 204 および 208 が電圧源 220 から正電圧を受けるとき、スイッチ 204 およびスイッチ 208 のそれぞれの放電トランジスタはオフになってもよい。さらに、

50

スイッチ回路 200 を通って RF 信号入力 212 から RF 信号出力 216 へと RF 信号を伝えることができるよう、スイッチトランジスタはオンになってもよい。

#### 【0035】

同様に、スイッチ 232 およびスイッチ 236 は、電圧源 244 から正電圧を受けてもよい。上述のように、スイッチ 232 および 236 は p チャネル FET を含んでもよい。したがって、電圧源 244 から受ける正電圧は、スイッチ 232 および 236 のスイッチトランジスタをオフにしてもよい。スイッチ 232 および 236 のスイッチトランジスタがオフになるとき、RF 信号入力 212 からグランド 240 へと信号が伝わることができなくなってもよい。したがって、正電圧の印加によってスイッチ回路 200 の分岐部が実際に閉鎖される一方で、正電圧によってスイッチ回路 200 の信号部が開放されてもよい。

10

#### 【0036】

その一方で、電圧源 244 および 220 から電圧を印加しないか、グランド電圧を印加することにより、上述の態様とは逆の態様でスイッチ回路 200 を動作させてよい。具体的には、電圧源 220 からグランド電圧を印加することにより、信号がグランド 240 に流れることができるように、スイッチ 204 および 208 の放電トランジスタをオンにしてもよい。例えば、RF 信号入力 212 からの雑音がグランド 240 に短絡されてもよい。同時に、スイッチ 204 および 208 のスイッチトランジスタをオフにすることで、RF 信号入力 212 からの雑音が RF 信号出力 216 に伝わらないようにしてもよい。

#### 【0037】

上述のスイッチ回路 200 は、いくつかの優位性を享受しうる。具体的に、スイッチ回路 200 は、増強された挿入損失や、増大した分離性および全体的特性を有する一方で、比較的コンパクトな面積内に依然として存在しうる。例えば、いくつかの実施の形態において、スイッチのスイッチトランジスタは、約 1 mm の厚さを有してもよい。スイッチの放電トランジスタは、約 1 μm の厚さを有してもよい。さらに、スイッチ回路 200 のスイッチング速度は、非常に高速であると考えられうる。さらに、スイッチ回路 200 は、電圧源 220 および 244 のような正電圧源のみを用いて実装されてもよく、いくつかの実施の形態において、これらは一つの正電圧源に統合されてもよい。したがって、スイッチ回路 200 は、阻止コンデンサや負電圧発生器を必要としなくてもよい。

20

#### 【0038】

図 3 は、スイッチ回路 200 などのスイッチ回路の製造工程の例を示す。最初に、ステップ 304 において、第 1 トランジスタのゲートコンタクトが第 2 トランジスタのドレインコンタクトに接続されてもよい。具体的には、スイッチ 232 などのスイッチに含まれるスイッチ 100 のスイッチトランジスタ 104 といったスイッチトランジスタのゲートコンタクトが、スイッチ 232 に含まれる放電トランジスタ 132 といった放電トランジスタのドレインコンタクトに接続されてもよい。

30

#### 【0039】

次に、ステップ 308 において、第 1 トランジスタのボディコンタクトが第 2 トランジスタのソースコンタクトに接続されてもよい。具体的には、スイッチ 232 に含まれるスイッチ 100 のスイッチトランジスタ 104 のボディコンタクトが、スイッチ 232 に含まれる放電トランジスタ 132 のソースコンタクトに接続されてもよい。

40

#### 【0040】

次に、ステップ 312 において、第 2 トランジスタのゲートコンタクトが第 1 抵抗および第 2 抵抗に接続されてもよい。具体的には、スイッチ 232 に含まれる放電トランジスタ 132 のゲートコンタクトが、抵抗 124 および 128 といった抵抗に接続され、ゲートコンタクト 136 が仮想グランドを参照するようにしてもよい。

#### 【0041】

最後に、第 1 トランジスタのドレインコンタクトが第 2 スイッチに接続されてもよい。例えば、スイッチ 232 に含まれるスイッチ 100 のスイッチトランジスタ 104 のドレインコンタクトが、スイッチ 204 といった別のスイッチに接続されてもよい。具体的に

50

は、スイッチ232に含まれるスイッチトランジスタ104のドレインコンタクトが、スイッチ204に含まれるスイッチングトランジスタのドレインコンタクトに接続されてもよい。上述のように、スイッチ232の放電トランジスタおよびスイッチトランジスタはpチャネルFETであってもよく、一方でスイッチ204のスイッチトランジスタはnチャネルFETであってもよい。

#### 【0042】

スイッチ回路200は、様々なシステムに組み込まれてもよい。図4は、システム400の例を示すブロック図である。図示されるように、システム400は、いくつかの実施の形態において無線周波数(RF)パワー増幅器(PA; power amplifier)モジュールであってもよいPAモジュール402を含む。システム400は、図示されるようにPAモジュール402に接続されるトランシーバ404を含んでもよい。PAモジュール402は、増幅、スイッチング、ミキシングなどの任意の種類の動作を実行するスイッチ回路200を含んでもよい。様々な実施の形態において、スイッチ回路200は、追加的/代替的に、例えばアップコンバートを提供するためにトランシーバ404に含まれてもよいし、または、様々なスイッチング機能を提供するためにアンテナスイッチモジュール(ASM)406に含まれてもよい。

10

#### 【0043】

PAモジュール402は、トランシーバ404からのRF入力信号RF<sub>in</sub>を受信してもよい。PAモジュール402は、RF入力信号RF<sub>in</sub>を増幅してRF出力信号RF<sub>out</sub>を提供してもよい。RF入力信号RF<sub>in</sub>およびRF出力信号RF<sub>out</sub>の双方は、図4においてそれぞれTx-RF<sub>in</sub>およびTx-RF<sub>out</sub>と称される送信チェーンの一部であってもよい。

20

#### 【0044】

増幅されたRF出力信号RF<sub>out</sub>は、アンテナ構造408を通じて、RF出力信号RF<sub>out</sub>の無線(OTA; over-the-air)伝送を実現させるASM406に提供されてもよい。ASM406は、アンテナ構造408を通じてRF信号を受信してもよく、受信したRF信号Rxを受信チェーンに沿ってトランシーバ404につないでもよい。

30

#### 【0045】

様々な実施の形態において、アンテナ構造408は、例えば、ダイポールアンテナ、モノポールアンテナ、パッチアンテナ、ループアンテナ、マイクロストリップアンテナまたはRF信号の無線(OTA)送信/受信に適した、いかなる種類のアンテナを含む、一以上の指向性および/または無指向性アンテナを含んでもよい。

#### 【0046】

システム400は、パワー増幅を含む任意のシステムであってもよい。様々な実施の形態において、RF信号をスイッチするためにシステム400にスイッチ回路200を含むことは、システム400がRFの高いパワーおよび周波数においてパワー増幅するために用いられるときに特に有用でありうる。例えば、システム400にスイッチ回路200を含めることは、約32dBm以上のパワーおよび約1800MHz以上の周波数を有するグローバル・システム・フォー・モバイル・コミュニケーション(GSM(登録商標))の信号や、約34dBm以上のパワーを有する例えば800MHzから915MHzの低帯域GSMの信号の伝送に特に有益である。

40

#### 【0047】

システム400は、地上もしくは衛星通信、レーダシステム、様々な産業および医療用途において利用可能な任意の一以上のものに適してもよい。より具体的には、いくつかの実施の形態において、システム400は、レーダデバイス、衛星通信デバイス、モバイルコンピューティングデバイス(例えば、電話、タブレット、ラップトップなど)、基地局、放送ラジオ、または、テレビ増幅器システムの中から選択される一つであってもよい。

#### 【0048】

本開示は、上述の実施の形態の観点から示されたが、本開示の範囲を逸脱しない限りにおいて、同様の目的を実現すると考えられるさまざまな代替的および/または等価な実施

50

の形態により、上述した特定の実施の形態が置換されてもよいことは、当業者によって理解されるであろう。当業者であれば、本開示によって示された内容が、様々な実施の形態として実施されてもよいことは、すぐに理解されるであろう。本記載は、制限的であるとみなされるのではなく、例示的であるとみなされることを意図する。

【図1】

【図2】

【図3】

【図4】

## フロントページの続き

(51) Int.Cl. F I テーマコード(参考)

H 01 L 27/04 (2006.01)

H 03 K 17/04 (2006.01)

(72)発明者 ノーラ、ジョージ

アメリカ合衆国オレゴン州 9 7 1 2 4 ・ ヒルズボロ・ノースイーストブルックウッドパークウェイ

2 3 0 0

F ターム(参考) 5F038 AR00 BE07 CD02 DF11 DF17 EZ06 EZ20

5F048 AA01 AB10 AC01 AC03 AC10 BA16 BE09 BF15 BF16 BF18

5J055 AX04 AX56 BX17 CX03 DX12 EY01 EY03 EY21 FX12 FX35

GX01 GX02

【外国語明細書】

2015149720000001.pdf