## (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2003/0002303 A1

Riggio et al.

Jan. 2, 2003 (43) Pub. Date:

(54)POWER FACTOR CONTROLLER

Inventors: Christopher Allen Riggio, Longmont, CO (US); Garth Blair Woodland,

Littleton, CO (US)

Correspondence Address: Patent Law Office of Rick Martin, P.C. 416 Coffman Street Longmont, CO 80501 (US)

Appl. No.: 10/099,736 (21)

Mar. 15, 2002 (22)Filed:

### Related U.S. Application Data

Continuation of application No. 09/923,027, filed on Aug. 6, 2001, which is a division of application No. 09/410,849, filed on Oct. 1, 1999, now Pat. No. 6,272,025.

#### **Publication Classification**

#### ABSTRACT (57)

A drive with a high impedance input, low impedance output is created. When a switching or driving action requiring the sourcing and sinking of current from a common node in a wide frequency range is desired, the invention allows the creation of a simple, efficient, two switch drive system that functions across a wide range of conditions. The circuit uses a discrete N-Channel FET paired with discrete PNP transistors. A high impedance input node is formed by connecting the FET gate to the transistor base. The differential threshold voltage that exists between the FET gate and the transistor base prevents the two devices from generating conflicting currents at the output node formed by the common source emitter. The circuit further lends itself to output waveform variations as may be required for various drive strategies by manipulating the input signal processing to custom modify the resulting output voltage and current.

FIG. 2

FIG. 5

FIG. 12A

## NORMAL MAGNETIZATION CURVES, KOOL MU

FIG. 15

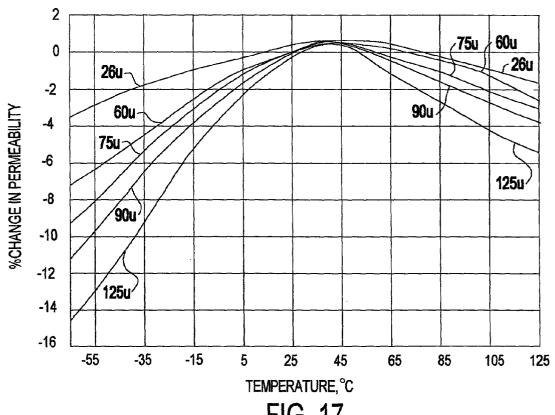

## PERMEABILITY VERSUS TEMPERATURE CURVES, KOOL Mu

FIG. 17

FIG. 30A

FIG. 40A

FIG. 40C

FIG. 41

### POWER FACTOR CONTROLLER

### CROSS REFERENCE APPLICATIONS

[0001] This application is a continuation of application No. 09/923,027 filed Aug. 6, 2001 which is a divisional of application No. 09/410,849 filed Oct. 1, 1999 and issued as U.S. Pat. No 6,272,025 on Aug. 7, 2001.

#### FIELD OF INVENTION

[0002] The present invention relates to converters, power supplies, more particularly, to single, or multi stage, AC/DC or DC/DC isolated and non-isolated push-pull converters including but not limited to, forward, flyback, buck, boost, push pull, and resonant mode converters, and power supplies, having individual or distributed NSME with high speed FET switching and efficient flyback management and or having input PFC (power factor correction) and input protection from lightning transients. The invention also allows the magnetic element(s) be distributed to accommodate packaging restrictions, multiple secondary windings, or operation at very high winding voltages.

# BACKGROUND OF THE INVENTION

[0003] There are several basic topologies commonly used to implement switching converters.

[0004] A DC-DC converter is a device that converts a DC voltage at one level to a DC voltage at another level. The converter typically includes a magnetic element having primary and secondary windings wound around it to form a transformer. By opening and closing the primary circuit at appropriate intervals control over the energy transfer between the windings occurs. The magnetic element provides an alternating voltage and current whose amplitude can be adjusted by changing the number and ratio of turns in each set of the windings. The magnetic element provides galvanic isolation between the input and the output of the converter.

[0005] One of the topologies is the push-pull converter. The output signal is the output of an IC network that switches the transistors alternately "on" and "off". High frequency square waves on the transistor output drive the magnetic element into AC (alternating current) bias. The isolated secondary outputs a wave that is rectified to produce DC (direct current). The push-pull converters generally have more components as compared to other topologies. The push-pull approach makes efficient use of the magnetic element by producing AC bias, but suffers from high parts count, thermal derating, oversized magnetics, and elaborate core reset schemes. The destructive fly-back voltages occurring across the switches are controlled through the use of dissipative snubber networks positioned across the primary switches. Another of the topologies is the forward converter. When the primary of the forward converter is energized, energy is immediately transferred to the secondary winding. In addition to the aforementioned issues the forward converter suffers from inefficient (dc bias) use of the magnetic element. The prior art power supplies use high permeability gapped ferrite magnetic elements. These are well known in the art and are widely used. The magnetics of the prior art power supplies are generally designed for twice the required power rating and require complex methods to reset and cool the magnetic elements resulting in increased costs and limited operating temperatures. This is because high permeability magnetic elements saturate during operation producing heat in the core, which increases permeability and lowers the saturation threshold. This produces runaway heating, current spikes and/or large leakage currents in the air gap, reduced efficiency, and ultimately less power at higher temperatures and/or high load. The overall effects are, lower efficiency, lower power density, and forced air/heatsink dependant supplies that require over-rated ferrite magnetic elements for a given output over time, temperature, and loading.

#### Improvements

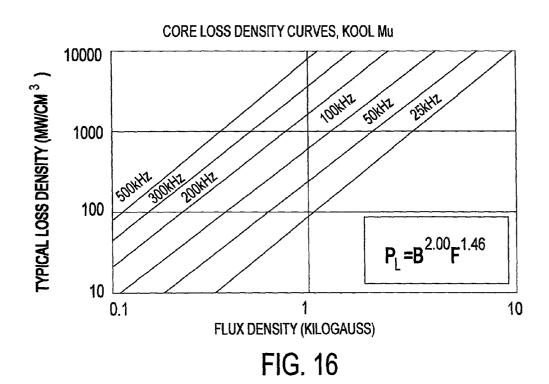

[0006] The combined improvements of the invention translate to higher system efficiencies, higher power densities, lower operating temperatures, and, improved thermal tolerance thereby reducing or eliminating the need for forced air cooling per unit output. The non-saturating magnetic properties are relatively insensitive to temperature (see FIG. 17), thus allowing the converter to operate over a greater temperature range. In practice, the operating temperature for the NSME is limited to 200C by wire/core insulation; the non-saturating magnetic material remains operable to near its Curie temperature of 500C.

[0007] What are needed are converters having circuit strategies that make advantageous use of individual and distributed NSME.

[0008] What are needed are converters having buffer circuits that provide fast, low impedance critically damped switching of the main FET's.

[0009] What are needed are converters that incorporate efficient multiple "stress-less" flyback management techniques to rectify and critically damp excessive node voltages across converter switches.

[0010] What are needed are converters having flux feedback frequency modulation.

[0011] What are needed are converters that correct AC power factor.

[0012] What is needed are converters that meet or exceed class B conducted EMI requirements.

[0013] What are needed are converters tolerant of lightning and harsh thermal environments. The present invention addresses these and more.

## SUMMARY OF THE INVENTION

[0014] The main aspect of the present invention is to implement converters having circuit strategies that make advantageous use of individual and distributed NSME for the achievement of the key performance enhancements disclosed herein.

[0015] Another aspect of the present invention is to provide unique resonant tank circuit converter strategies with individual and distributed NSME that make use of higher primary circuit voltage excursions in the production of high frequency/high density magnetic flux.

[0016] Another aspect of the present invention is a high energy density single stage frequency controlled resonant tank converter topology enabled by the use of individual and distributed NSME. Another aspect of the present invention

is to provide a converter design that utilizes a FET drive technique consisting of an ultra fast, low RDS on N-channel FET for charging the main FET gate and an ultra fast P-channel transistor for discharging the main FET gate.

[0017] Another aspect of the present invention is to provide converters that incorporate efficient multiple "stressless" flyback management techniques to rectify and critically damp excessive node voltages across converter switches.

[0018] Another aspect of the present invention is to provide a converter having core (flux) synchronized zero crossing frequency modulation.

[0019] Another aspect of the present invention is to present a high power factor to the AC line.

[0020] Another aspect of the present invention is to provide protection from high voltage (input line) transients.

[0021] Another aspect of the present invention is to combine distributed magnetics advantageously with the other converter aspects.

[0022] Another aspect of the present invention is active ripple rejection provided by several high-gain high-speed isolated control and feedback systems.

[0023] Other aspects of this invention will appear from the following description and appended claims, reference being made to the accompanying drawings forming a part of this specification wherein like reference characters designate corresponding parts in the several views.

## BRIEF DESCRIPTION OF THE DRAWINGS

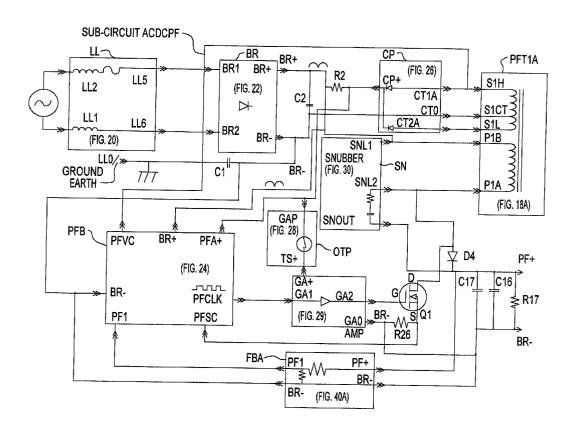

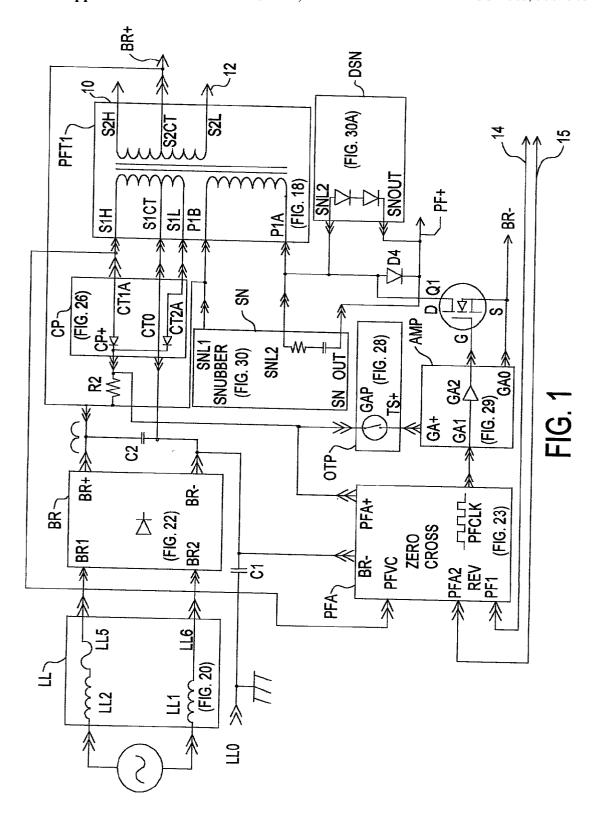

[0024] FIGS. 1 and 1A is a schematic diagram of a two-stage power factor corrected AC to DC isolated output converter embodiment of the invention.

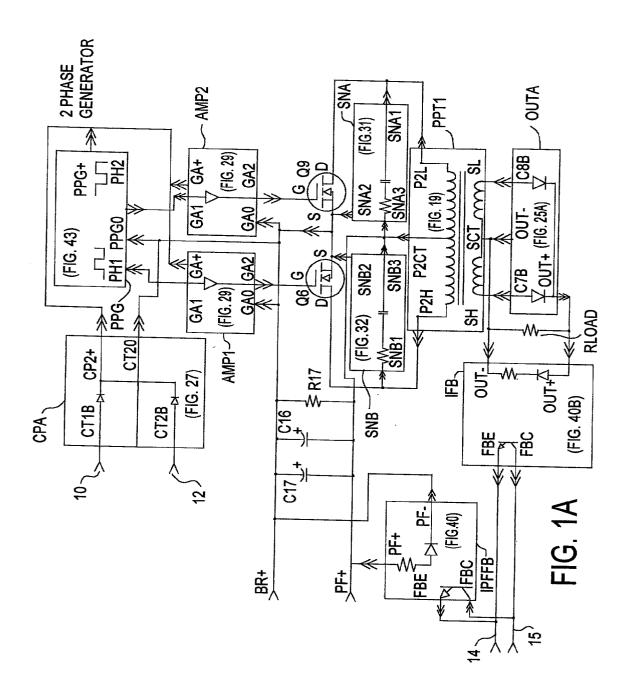

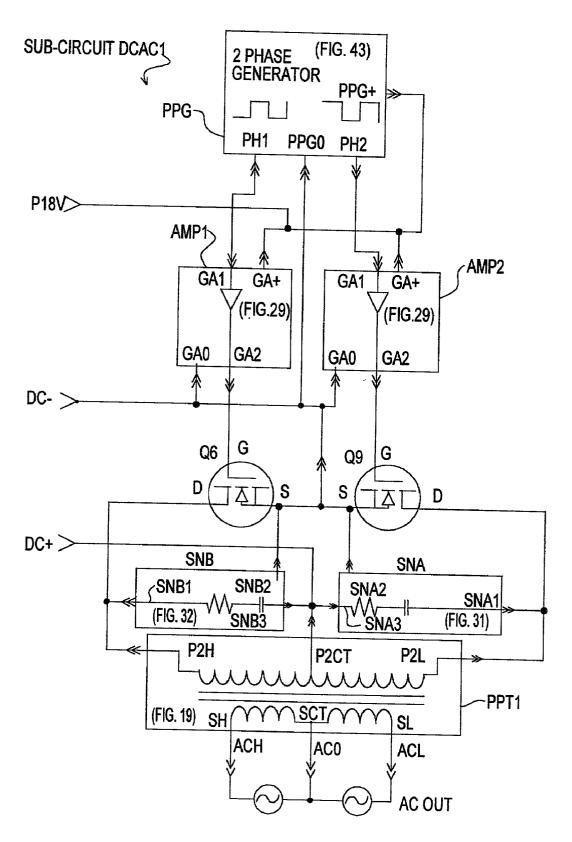

[0025] FIG. 2 is a schematic diagram of a single stage DC to AC converter embodiment with isolated output sub-circuit DCAC1.

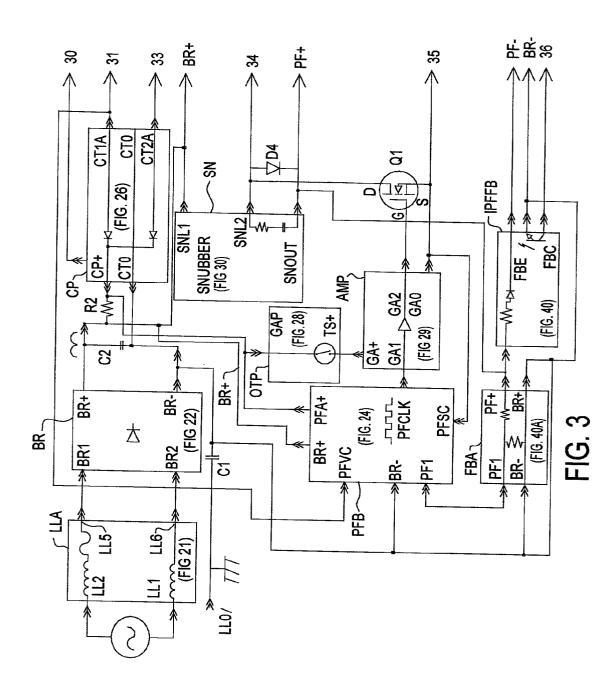

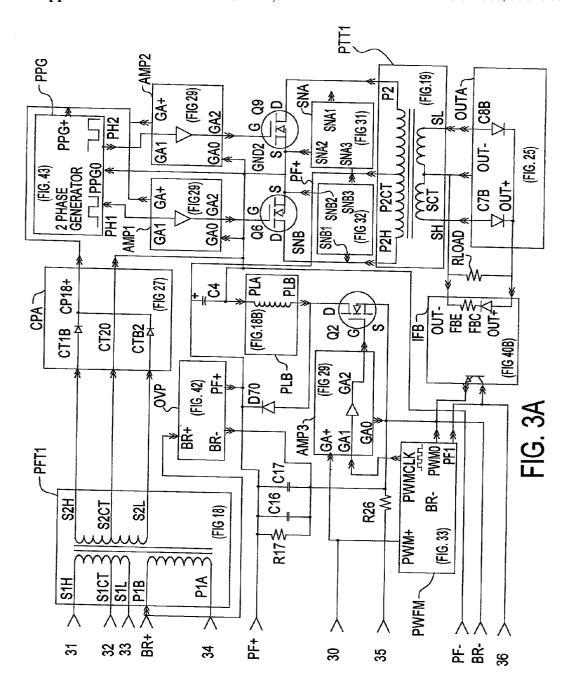

[0026] FIGS. 3 and 3A is a schematic diagram of a three stage AC to DC isolated output converter embodiment of the invention.

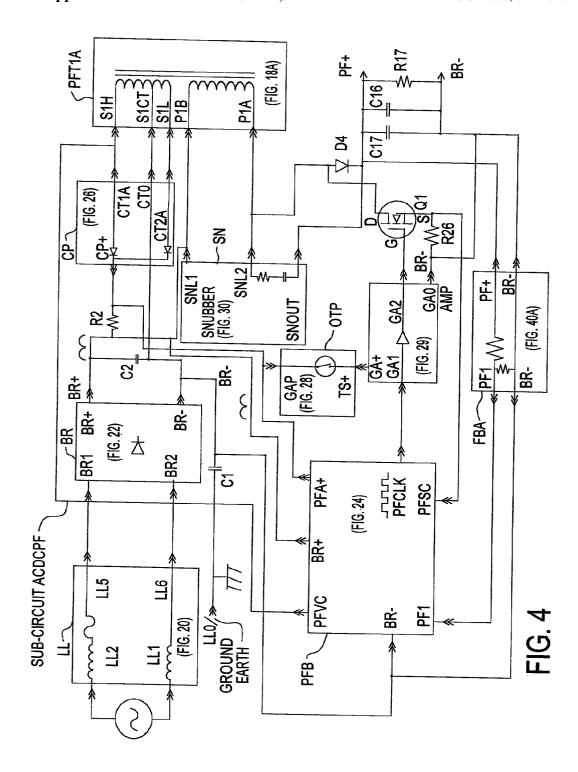

[0027] FIG. 4 is a schematic diagram of a power factor corrected single stage AC to DC converter sub-circuit ACD-FPF.

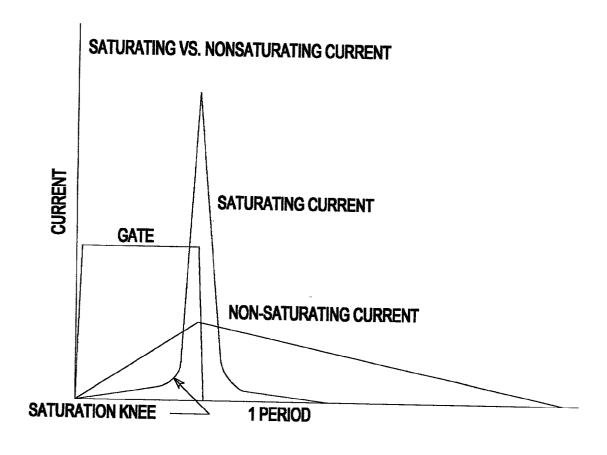

[0028] FIG. 5 is a graph comparing typical winding currents in saturating and non-saturating magnetics of equal inductance.

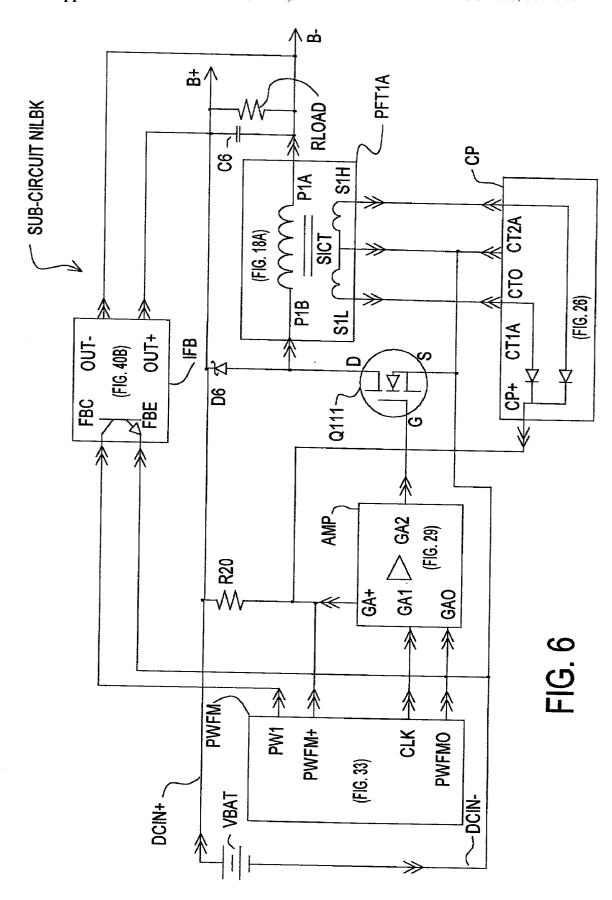

[0029] FIG. 6 is a schematic for a non-isolated low side switch buck converter sub-circuit NILBK.

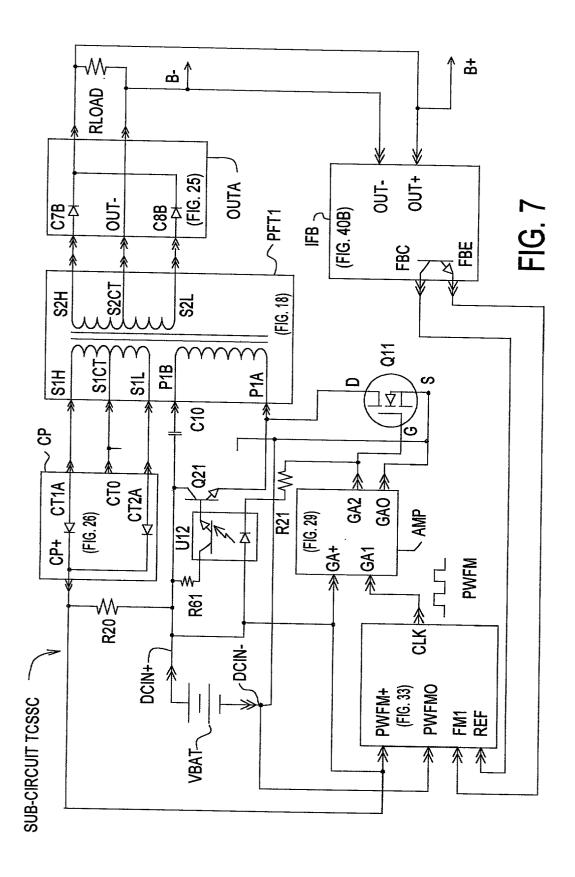

[0030] FIG. 7 is the preferred embodiment schematic for a tank coupled single stage converter sub-circuit TCSSC.

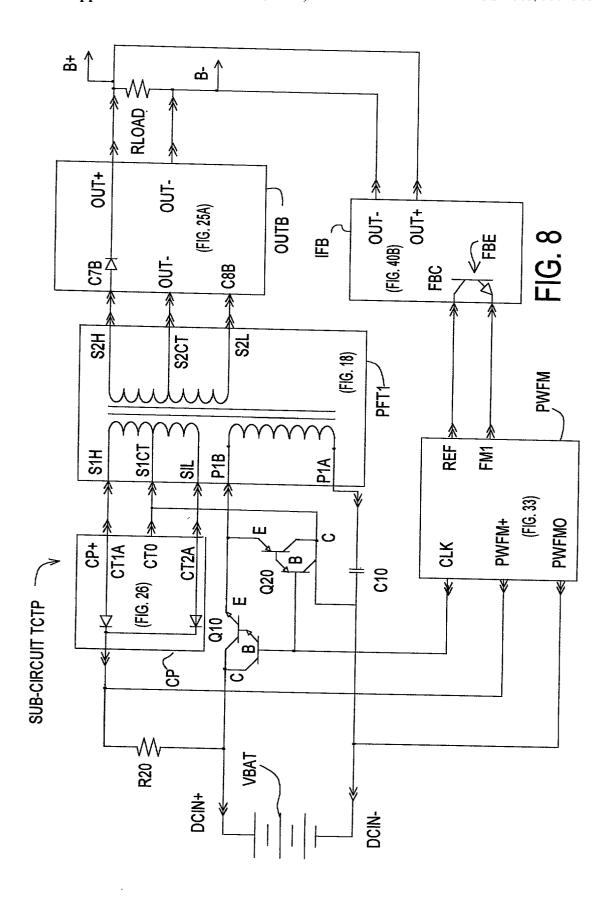

[0031] FIG. 8 is a schematic for a tank coupled totem pole converter sub-circuit TCTP.

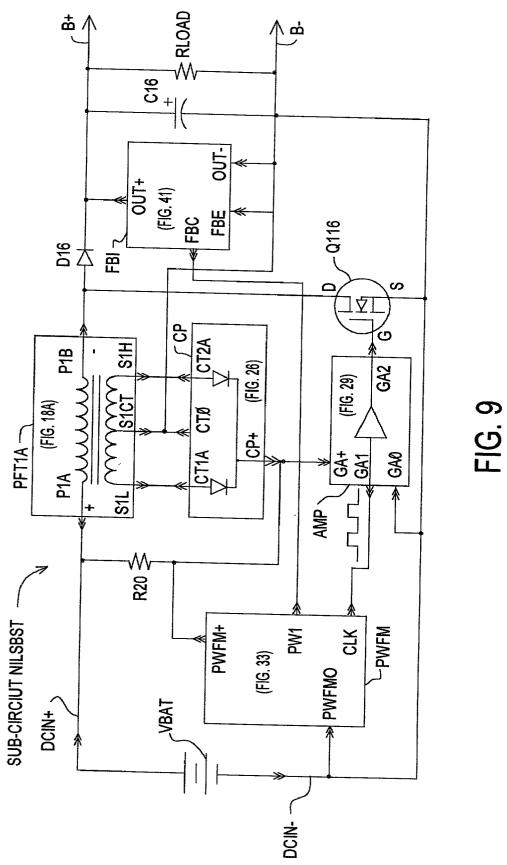

[0032] FIG. 9 is a block diagram for a single stage non-isolated DC to DC boost converter NILSBST.

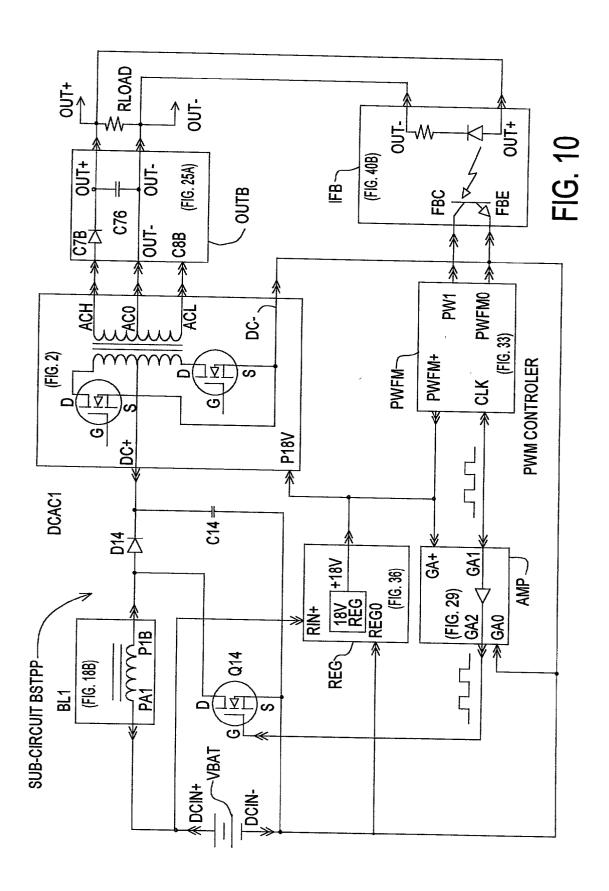

[0033] FIG. 10 is a schematic for a two stage isolated DC to DC boost controlled push-pull converter BSTPP.

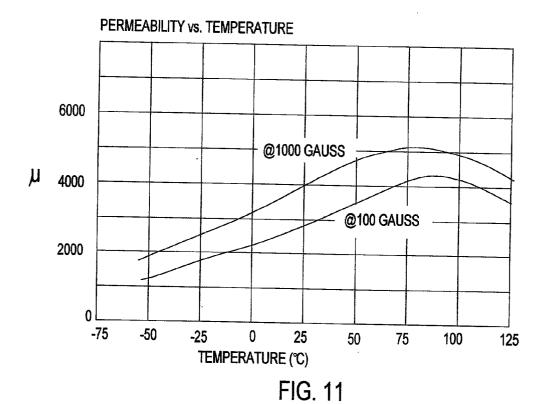

[0034] FIG. 11 is a graph of permeability as a function of temperature for typical prior art magnetic element material.

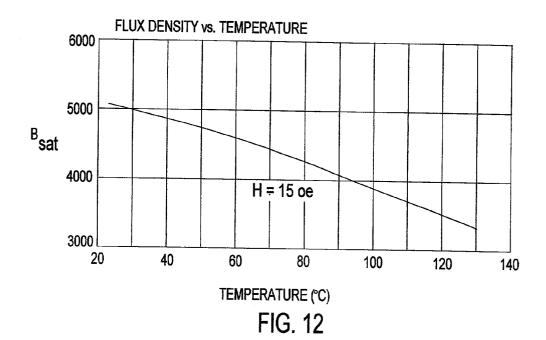

[0035] FIG. 12 is a graph of flux density as a function of temperature for typical prior art magnetic element material.

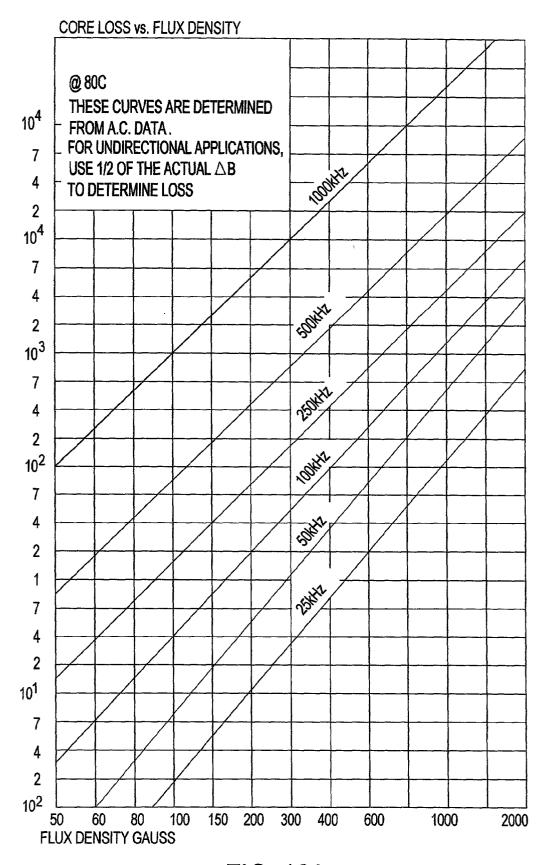

[0036] FIG. 12A is a graph of magnetic element losses for various flux densities and operating frequencies typical of prior art magnetic element material.

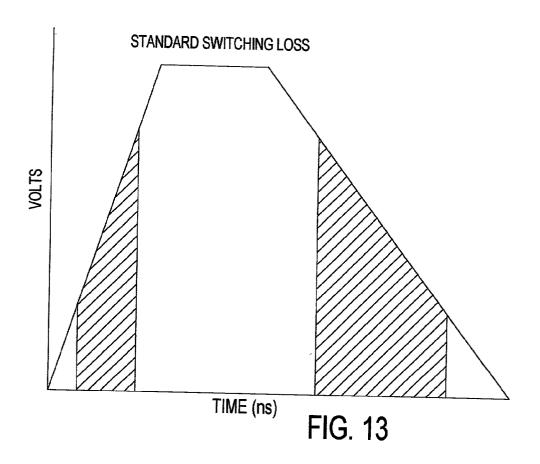

[0037] FIG. 13 is a graph showing standard switching losses.

[0038] FIG. 14 is a graph showing lower switching losses of the invention.

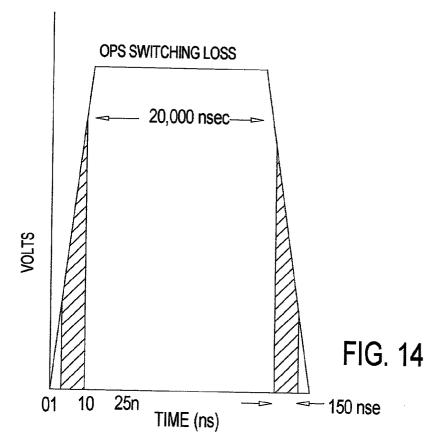

[0039] FIG. 15 is a graph showing the magnetizing curve (BH) for the NSME material.

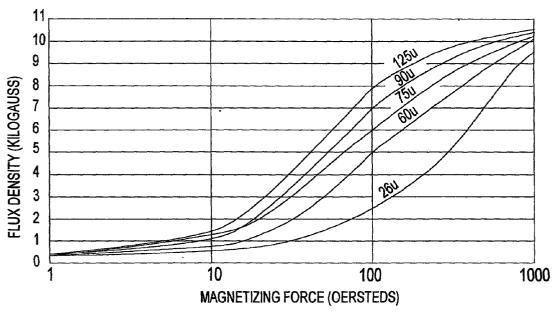

[0040] FIG. 16 is a graph of magnetic element losses for various flux densities and operating frequencies of the NSME material.

[0041] FIG. 17 is a graph of permeability as a function of temperature for the NSME.

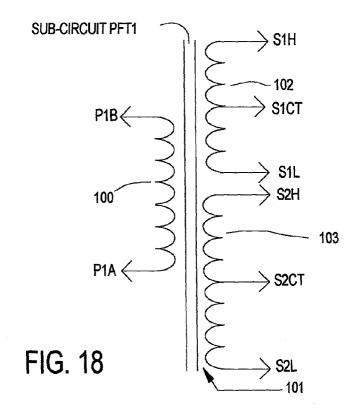

[0042] FIG. 18 is a schematic representation of the boost NSME sub-circuit PFT1.

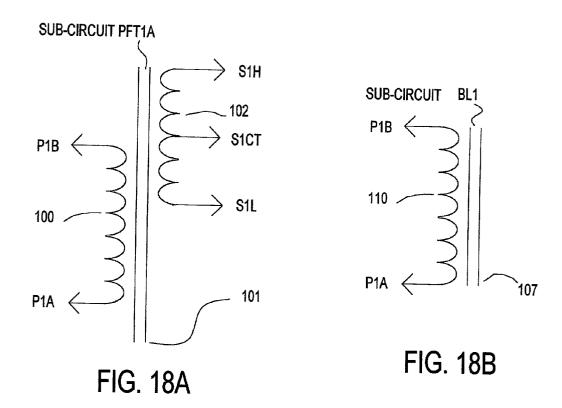

[0043] FIG. 18A is a schematic representation of the NSME sub-circuit PFT1A.

[0044] FIG. 18B is a schematic representation of the non-saturating two terminal NSME sub-circuit BL1.

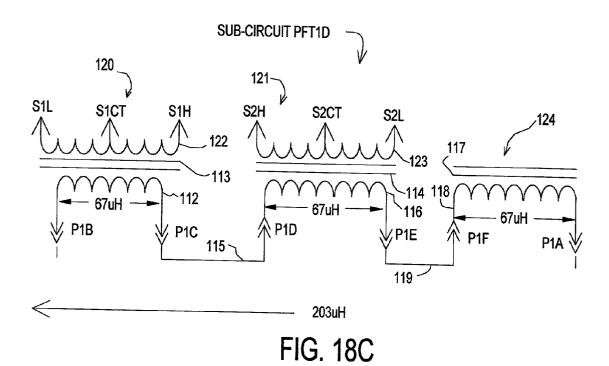

[0045] FIG. 18C is a schematic diagram of the NSME implemented as distributed magnetic assembly PFT1D.

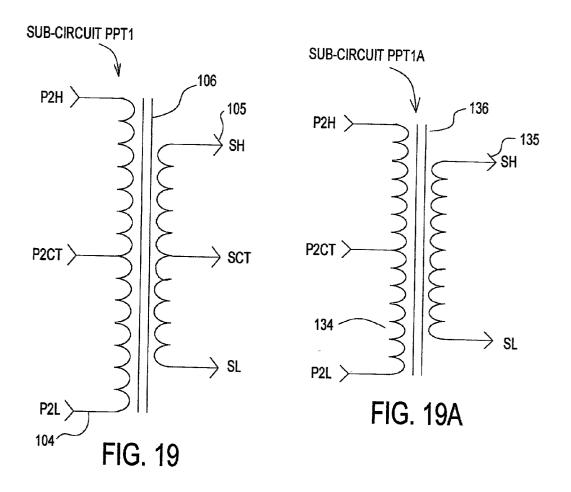

[0046] FIG. 19 is a schematic representation of the push-pull NSME sub-circuit PPT1.

[0047] FIG. 19A is a schematic representation of the alternate push-pull NSME sub-circuit PPT1A.

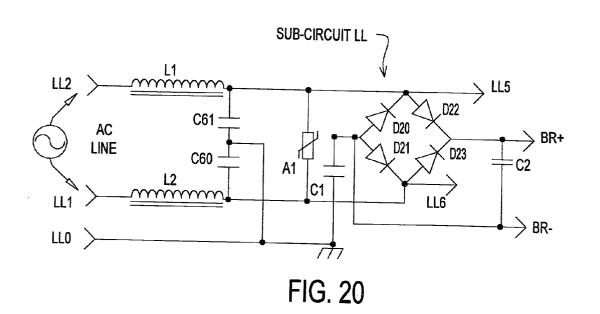

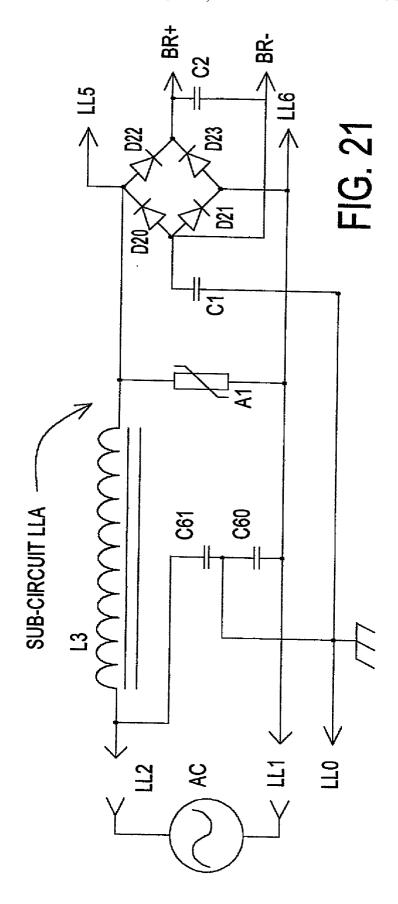

[0048] FIG. 20 is a schematic diagram of the NSME input transient protection and line filter sub-circuit LL.

[0049] FIG. 21 is a schematic diagram of the alternate NSME input transient protection and line filter sub-circuit LLA.

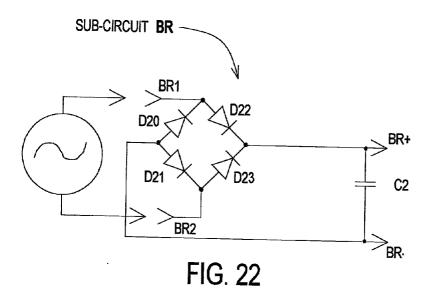

[0050] FIG. 22 is a schematic diagram of the AC line rectifier sub-circuit BR.

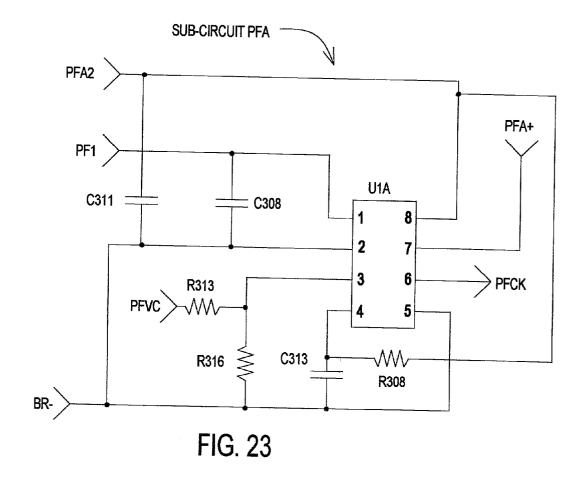

[0051] FIG. 23 is a schematic diagram of the power factor controller sub-circuit PFA.

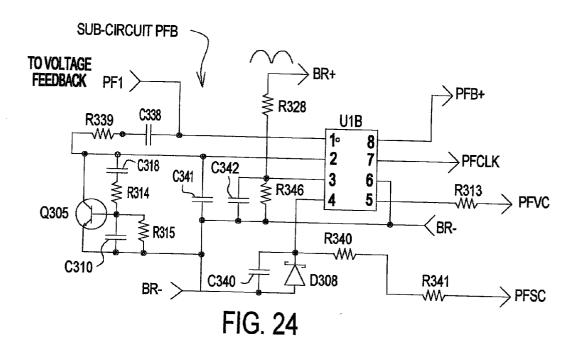

[0052] FIG. 24 is a schematic diagram of the alternate power factor correcting boost control element sub-circuit PFB.

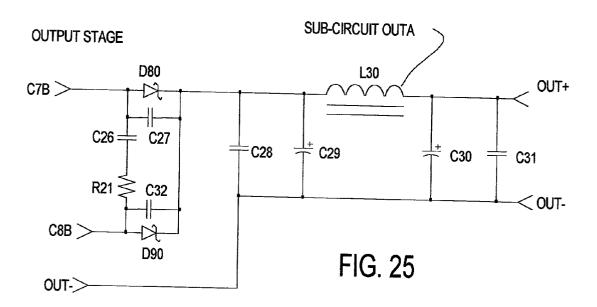

[0053] FIG. 25 is a schematic diagram of the output rectifier and filter sub-circuit OUTA.

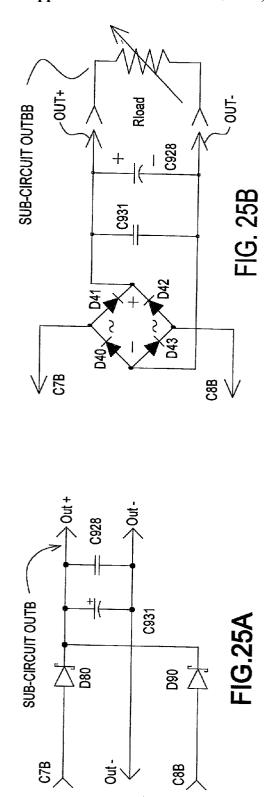

[0054] FIG. 25A is a schematic diagram of an alternate rectifier sub-circuit OUTB.

[0055] FIG. 25B is a schematic diagram of an alternate final output rectifier and filter sub-circuit OUTBB.

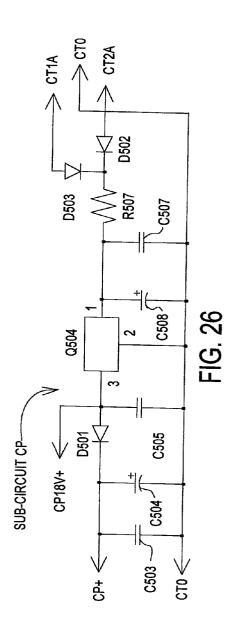

[0056] FIG. 26 is a schematic diagram of the floating 18 Volt DC control power sub-circuit CP.

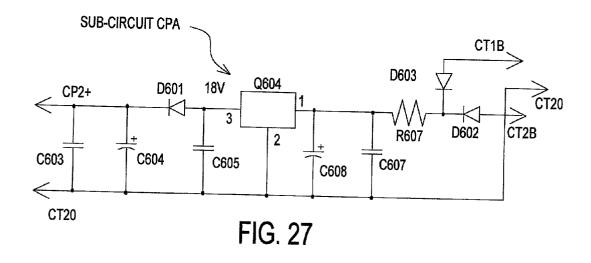

[0057] FIG. 27 is a schematic diagram of the alternate floating 18\_Volt DC push-pull control power sub-circuit CPA.

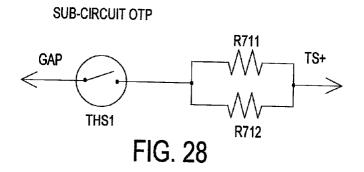

[0058] FIG. 28 is a schematic diagram of the over temperature protection sub-circuit OTP.

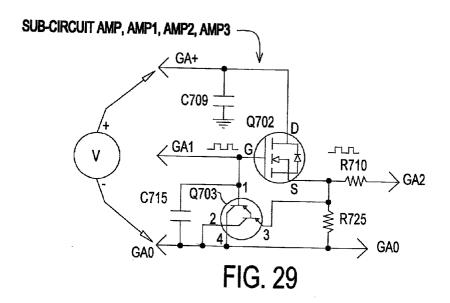

[0059] FIG. 29 is a schematic diagram of the high-speed low impedance buffer sub-circuit AMP, AMP1, AMP2 and AMP3.

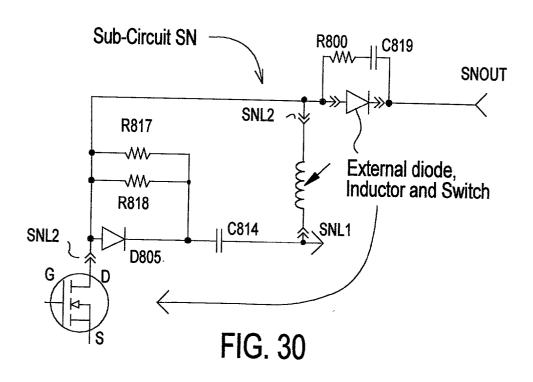

[0060] FIG. 30 is a schematic diagram of the main switch snubber sub-circuit SN.

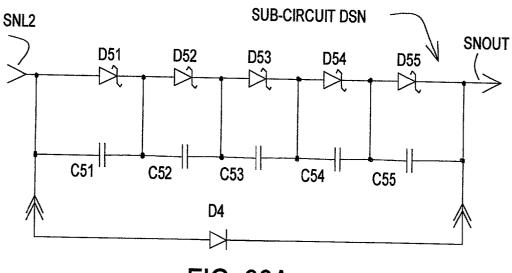

[0061] FIG. 30A is a schematic diagram of the main switch rectifying diode snubber sub-circuit DSN.

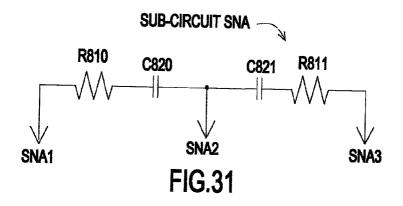

[0062] FIG. 31 is a schematic diagram of the alternate snubber sub-circuit SNA.

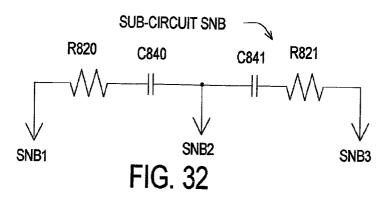

[0063] FIG. 32 is a schematic diagram of the mirror snubber sub-circuit SNB.

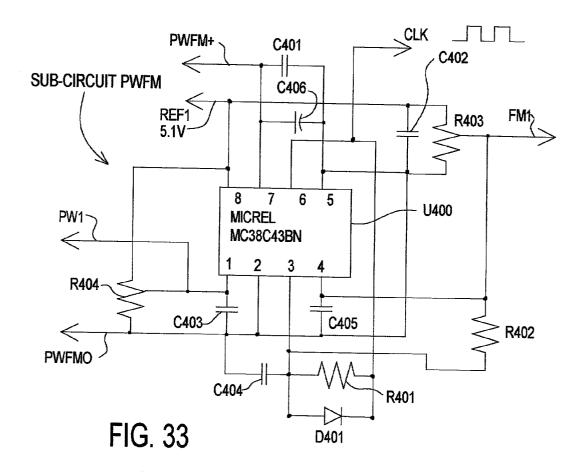

[0064] FIG. 33 is a schematic diagram of the pulse-width/ Frequency modulator sub-circuit PWFM.

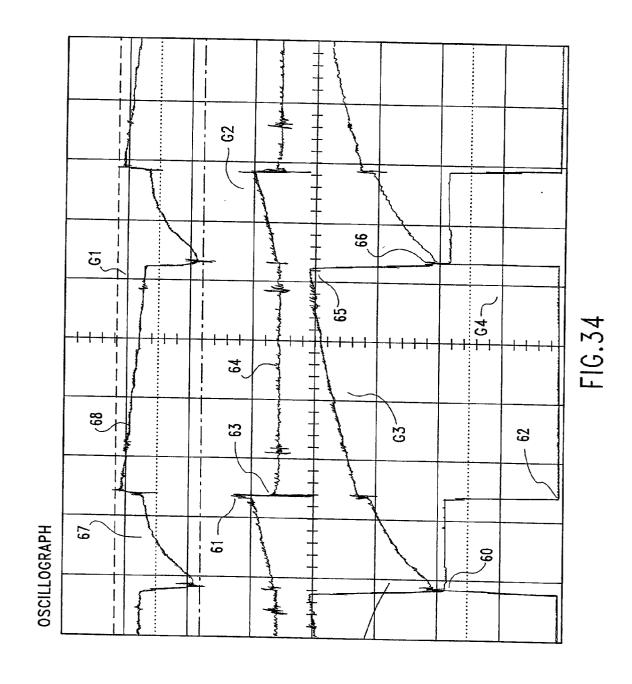

[0065] FIG. 34 is an oscillograph of node voltages measured during operation of sub-circuit PWFM (FIG. 33).

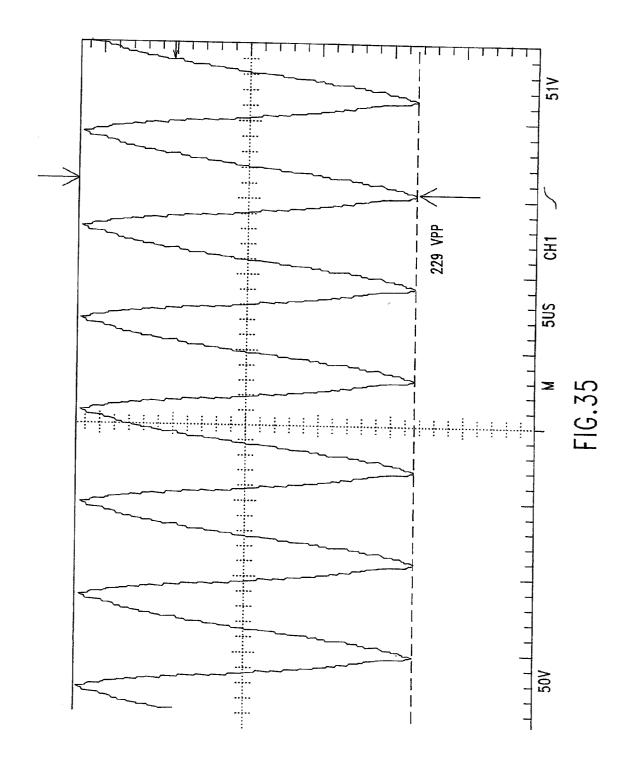

[0066] FIG. 35 is an oscillograph of the primary tank voltage measured during operation of sub-circuit TCTP (FIG. 8).

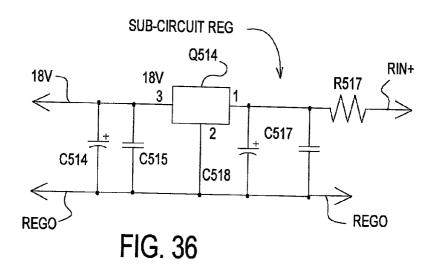

[0067] FIG. 36 is a schematic diagram of the non-isolated 18-Volt DC control power sub-circuit REG.

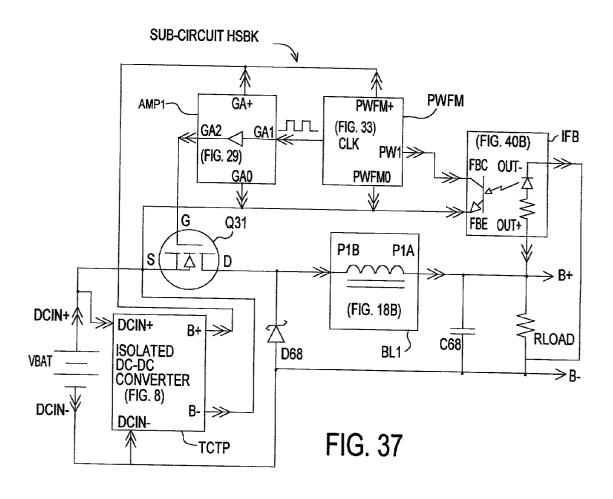

[0068] FIG. 37 is a schematic for a non-isolated high-side switch buck converter sub-circuit HSBK.

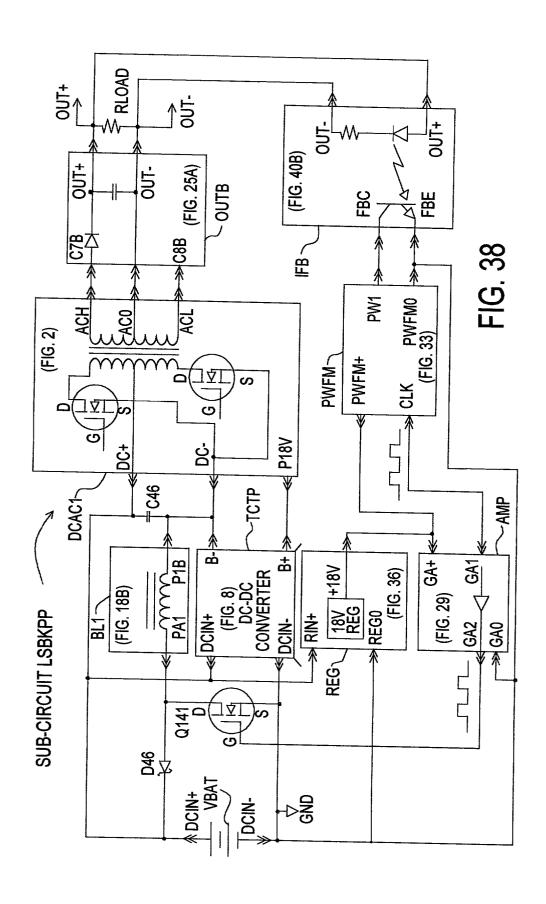

[0069] FIG. 38 is a schematic for the low-side buck regulated two-stage converter embodiment with isolated push-pull output sub-circuit LSBKPP.

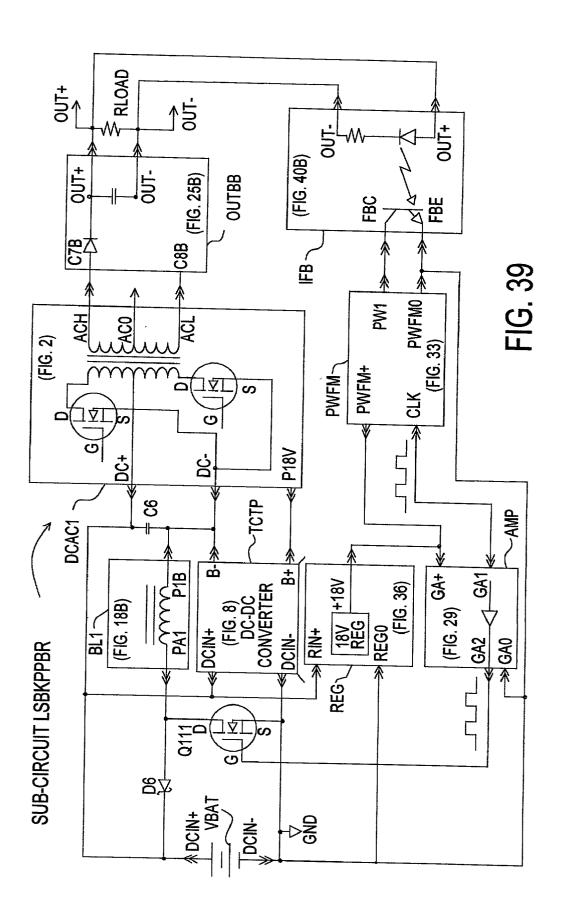

[0070] FIG. 39 is a schematic for an alternate isolated two-stage low-side switch buck converter sub-circuit LSBKPPBR.

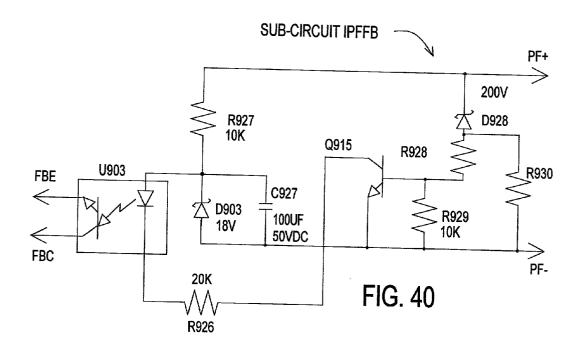

[0071] FIG. 40 is a schematic diagram of the over voltage feed back sub-circuit IPFFB.

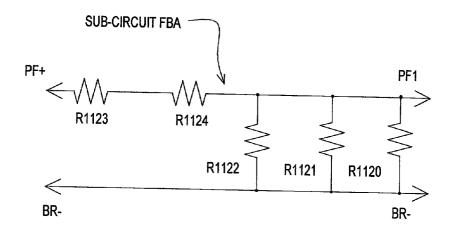

[0072] FIG. 40A is a schematic diagram of the non-isolated boost output voltage feedback sub-circuit FBA.

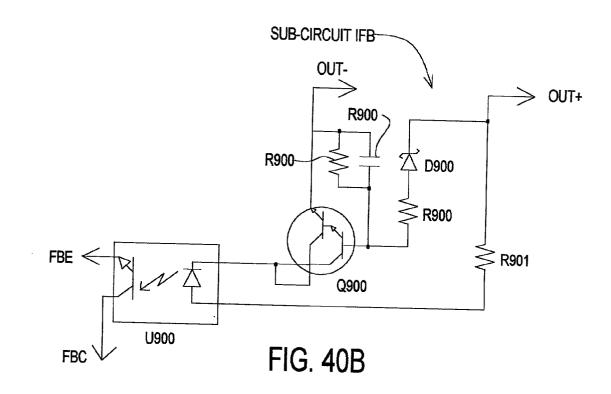

[0073] FIG. 40B is a schematic diagram of the isolated output voltage feedback sub-circuit IFB.

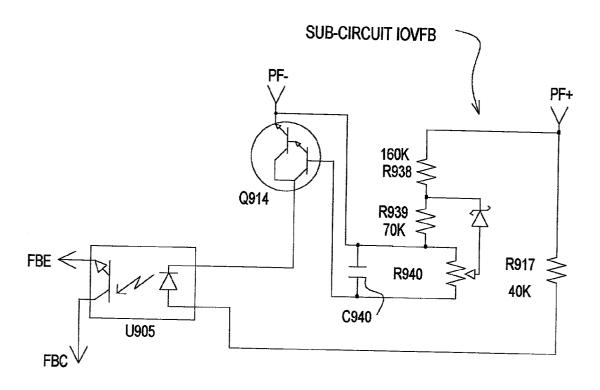

[0074] FIG. 40C is a schematic diagram of the alternate isolated over voltage feedback sub-circuit IOVFB.

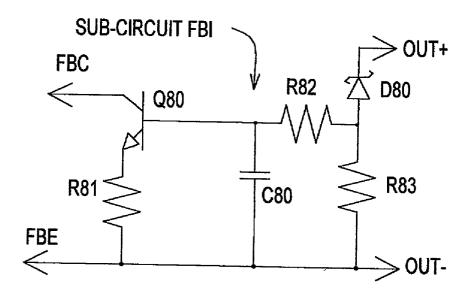

[0075] FIG. 41 is a schematic diagram of the non-isolated output voltage feedback sub-circuit FBI.

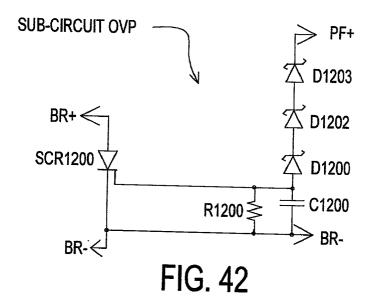

[0076] FIG. 42 is a schematic diagram of an over voltage protection sub-circuit OVP.

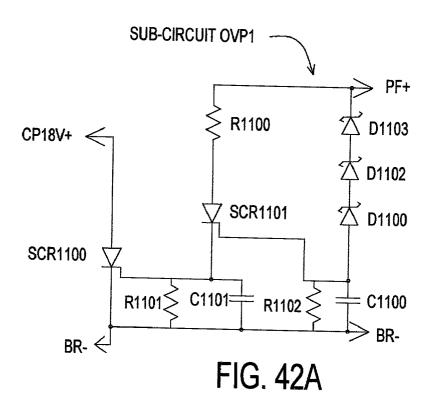

[0077] FIG. 42A is a schematic diagram of the isolated over voltage feedback sub-circuit OVP1.

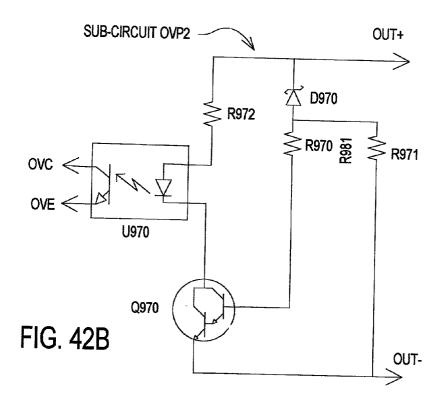

[0078] FIG. 42B is a schematic diagram of the over voltage protection sub-circuit OVP2.

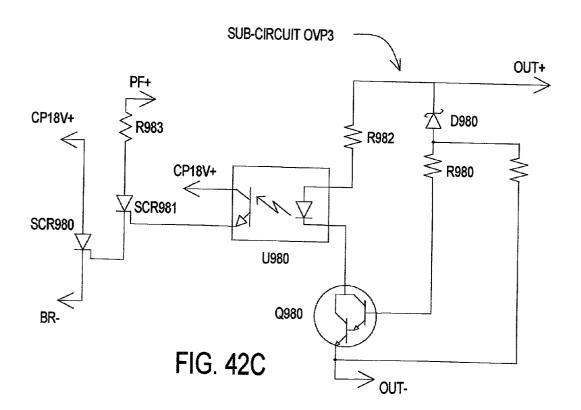

[0079] FIG. 42C is a schematic diagram of the isolated over voltage feedback sub-circuit OVP3.

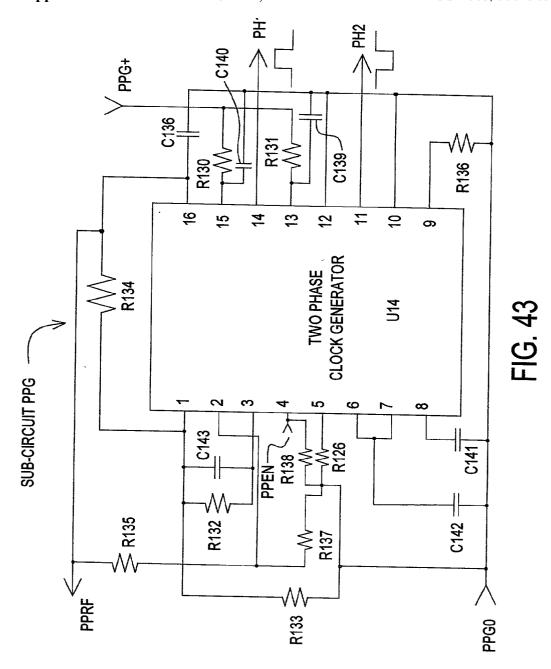

[0080] FIG. 43 is a schematic diagram of the Push-pull oscillator sub-circuit PPG.

[0081] Before explaining the disclosed embodiments of the present invention in detail, it is to be understood that:

[0082] The invention is not limited in its application to the details of the particular arrangements shown or described, since the invention is capable of other embodiments.

[0083] The expression "distributed magnetic(s)" refers to the configuration of multiple magnetic elements that share a single series coupled primary winding to induce isolated output currents from multiple series or parallel secondary windings.

[0084] Also, the terminology used herein is for the purpose of description not limitation.

# DESCRIPTION OF THE PREFERRED EMBODIMENT

[0085] In this and other descriptions contained herein, the following symbols shall have the meanings attributed to them: "+" shall indicate a series connection, such as resistor A in series with resistor B shown as "A+B". "||" Shall indicate a parallel connection, such as resistor A in parallel with resistor B shown as "A||B".

[0086] Referring first to FIG. 7, a schematic diagram of the preferred embodiment of the invention.

[0087] FIG. 7 is a schematic of the preferred embodiment of a tank coupled single stage converter sub-circuit TCSSC. Sub-circuit TCSSC consists of resistor R20 and RLOAD, capacitor C10, transistors Q21 and Q11, sub-circuit CP (FIG. 26), sub-circuit PFT1 (FIG. 18), sub-circuit OUTA (FIG. 25), sub-circuit AMP (FIG. 29), sub-circuit IFB (FIG. 40B) and sub-circuit PWFM (FIG. 33).

| FIG. 7  | Table             |

|---------|-------------------|

| Element | Value/part number |

| R20     | 1 k ohms          |

| R61     | 2 k ohms          |

| Q21     | TST541            |

| U12     | 4N29              |

| Q11     | IRFP460           |

| C10     | 1.8 uf            |

[0088] TCSSC can be configured to operate as an AC-DC converter, a DC-DC converter, a DC-AC converter, and an AC-AC converter. Sub-circuit TCSSC consists of resistor R20 and RLOAD, capacitor C10, switches Q11 and Q21, opto-isolator U12, sub-circuit PFT1 (FIG. 18), sub-circuit OUTA (FIG. 25), sub-circuit CP (FIG. 26), sub-circuit AMP (FIG. 29), sub-circuit IFB (FIG. 40B) and sub-circuit PWFM (FIG. 33). External power source VBAT connects to pins DCIN+ and DCIN-. Source power may also be derived from rectified AC line voltage such as FIG. 20 or FIG. 21 to form a single stage power factor corrected AC to DC converter with isolated output. From DCIN+resistor R20 connects to sub-circuit CP pin CP+, sub-circuit AMP pin GA+, U12 LED anode and to sub-circuit PWFM pin PWFM+. Resistor R20 provides startup power to the converter until the control supply regulator sub-circuit CP reaches the desired 18-volt output. VBAT negative is the ground return node connects to sub-circuit PWFM pin PWFM0, Q11 source, sub-circuit AMP pin GA0, sub-circuit CP pin CT0, pin DCIN- and sub-circuit PFT1 pin S1CT. Magnetic element winding node S1H of sub-circuit PFT1 is connected to CP pin CT1A. Magnetic element winding node

4

S1L of sub-circuit PFT1 is connected to CP pin CT2A. Sub-circuit PWFM is designed as a constant 50% duty-cycle variable frequency generator. Sub-circuit PWFM Clock output pin CLK is connected to input of buffer sub-circuit AMP pin GA1. The output of buffer sub-circuit AMP pin GA2 is connected to the gate of Q11 and R21. Resistor R21 is connected to the cathode of U12 LED. The emitter of Q21 and drain of Q11 is connected to sub-circuit PFT1 pin P1A. Pin P1B of sub-circuit PFT1 is connected through tank capacitor C10 to node DCIN+, Q21 collector and through resistor R61 to U12 phototransistor collector. The emitter of U12 phototransistor is connected to the base of Q21. With PWFM pin CLK high transistor Q11 conducts charging capacitor C10 through NSME PFT1 from VBAT storing energy in PFT1. Sub-circuit PWFM switches CLK low, Q11 turns "off". With CLK low LED of U12 is turned "on" injecting base current into Q21. With transistor Q21 "on" the tank circuit is completed, allowing capacitor C10 to discharge into NSME PFT1 winding 100 (FIG. 18). Now the energy not transferred into the load is released from NSME PFT1 into the now forward biased NPN switch Q21 back into capacitor C10. Thus any energy not used by the secondary load remains in the tank coupled primary circuit (winding 100). When the switching occurs at the resonant frequency, high voltages oscillate between C10 and winding 100 creating high flux density AC excursions in PFT1. C10 and PFT1 exchange variable AC currents whose magnitude is controlled by frequency modulation scheme IFB and PWFM. The large primary voltage generates large, high frequency biases in the NSME PFT1 thereby producing high flux density AC excursions to be harvested by secondary windings 102 and 103 (FIG. 18) to support a load or rectifier sub-circuit OUTA. Magnetic element winding node S2H of sub-circuit PFT1 is connected to OUTA pin C7B. Magnetic element winding node S2L of sub-circuit PFT1 is connected to OUTA C8B. Magnetic element winding node S2CT of sub-circuit PFT1 is connected to OUTA pin OUT-. Node OUT- is connected to RLOAD, pin B- and to sub-circuit IFB pin OUT-. Rectified power is delivered to pin OUT+ of OUTA and is connected to RLOAD, pin B+ and to subcircuit IFB pin OUT+. Sub-circuit IFB provides the isolated feedback signal to the sub-circuit PWFM. Frequency control pin FM1 of sub-circuit PWFM is connected to sub-circuit IFB pin FBE. Internal reference pin REF of sub-circuit PWFM is connected to sub-circuit IFB pin FBC. PWFM is designed to operate at the resonate frequency of the tank (2\*pi\*(square root (C10 \* inductance of 100 (FIG. 18)). When sub-circuit IFB senses the converter output is at the target voltage, current from PWFM pin REF is injected into FM1. Injecting current into FM1 commands the PWFM to a lower clock frequency pin CLK. Driving the tank out of resonance reduces the amount of energy added to the tank thus reducing the converter output voltage. In the event the feedback signal from IFB commands the PWFM off or OHz, i.e.: at no load, all primary activity stops. The input current from VBAT may be steady state or variable DC. When TCSSC is operated from rectified AC (sub-circuit LL FIG. 20), high input (line) power factor and input transient protection is achieved. The primary and secondary currents of PFT1 are sinusoidal and free of edge transitions making the converter very quiet. In addition the switches Q11 and Q21 are never exposed to the large circulating voltage induced in the tank (See FIG. 35). This allows the use of lower voltage switches in the design thereby reducing losses and increasing the MTBF. Sub-circuit TCSSC takes advantage of the desirable properties of the NSME in this converter topology. TCSSC is well suited for implementation with distributed NSME PFT1D (FIG. 18C). This combination exemplifies how distributed magnetics enable advantageous high voltage converter design variations that support form factor flexibility and multiple parallel secondary outputs from series coupled voltage divided primary windings across multiple NSME. This magnetic strategy is useful in addressing wire/core insulation, form factor and packaging limitations, circuit complexity and manufacturability. These converter strategies are very useful for obtaining isolated high current density output from a high voltage low current series coupled primary. Adjusting the secondary turn's ratio allows TCSSC to generate very large AC or DC output voltages as well as low-voltage high current outputs.

# Additional Embodiments

[0089] FIGS. 1 and 1A is a schematic diagram of a two stage power factor corrected AC to DC converter. The invention is comprised of line protection filter sub-circuit LL (FIG. 20) and full-wave rectifier sub-circuit BR (FIG. 22). A power factor corrected regulated boost stage with subcircuits PFA2 (FIG. 23), snubber sub-circuit SN (FIG. 30), magnetic element sub-circuit PFT1 (FIG. 18), sub-circuit CP (FIG. 26), buffer sub-circuit AMP (FIG. 29), over temperature sub-circuit OTP (FIG. 28), over voltage feedback sub-circuit IPFFB (FIG. 40) and voltage feedback sub-circuit IFB (FIG. 40B). Start up resistor R2, filter capacitor C1, PFC capacitor C2, flyback diode D4, switch transistor Q1, hold up capacitors C17 and C16, and resistor R17. An efficient push-pull isolation stage with sub-circuits CPA (FIG. 27), PPG (FIG. 43), AMP1 (FIG. 29), AMP2 (FIG. 29), snubber sub-circuits SNB (FIG. 32) and SNA (FIG. 31), resistor Rload, transistors Q6 and Q9, magnetic element PPT1 (FIG. 19), and OUTA (FIG. 25).

| FIG. 1<br>Element | Table<br>Value/part number |

|-------------------|----------------------------|

| C1                | 0.01 uf                    |

| C2                | 1.8 uf                     |

| R2                | 100 k ohms                 |

| D4                | 8A,600V                    |

| Q1                | IRFP 460                   |

| C17               | 100 uf                     |

| C16               | 100 uf                     |

| R17               | 375 k ohms                 |

| Q6                | FS 14SM-18A                |

| Q9                | FS 14SM-18A                |

[0090] In the two-stage converter the primary side voltage to the second push-pull output stage is modulated by the power factor corrected input (boost) stage. Each stage can comprise of individual and distributed NSME. A graph of B-H hysteresis for the non-saturating magnetics is set forth in FIG. 15. Although the following description is in terms of particular converter topologies, i.e., flyback controlled primary and constant duty cycle push pull secondary, number of outputs, the style, and arrangement of the several topologies are offered by way of example, not limitation. In addition non-saturating magnetics BL1, PFT1, and PPT1 may be implemented as distributed NSME. As an example PFT1 is shown as a distributed magnetic PFT1A (FIG.

18C). Distributed magnetics enable advantageous high voltage converter design variations that support form factor flexibility and multiple parallel secondary outputs from series coupled voltage divided primary windings across multiple NSME. The negative of the hold-up capacitor(s) [C17][C16] is connected to bridge positive. This allows the rectified line voltage to be excluded from the boost voltage in the hold-up capacitor(s). This, in turn, allows direct regulation of the push-pull stage from the boost (PFC) stage. This eliminates the typical PWM control of the oversized thermally derated transformer and many sub-circuit components from the known art. AC line is connected to sub-circuit LL (FIG. 20) between pins LL1 and LL2. AC/earth ground is connected to node LLO. The filtered and voltage limited AC line appears on node/pin LL5 of sub-circuit LL and connected to node BR1 of bridge rectifier sub-circuit BR (FIG. 22). The neutral/AC return leg of the filtered and voltage limited AC appears on pin LL6 of sub-circuit LL is connected to input pin BR2 of BR. The line voltage is full-wave rectified and is converted to a positive haversine appearing on node BR+ of sub-circuit BR (FIG. 22). Start up resistor R2 connects BR+ to sub-circuit CP pin CP+. Node CP+ connects to pins PFA+ of control element subcircuit PFA (FIG. 23) and over temperature switch subcircuit OTP (FIG. 28) pin GAP. Resistor R2 provides start up power to the control element until the rectifier/regulator CP is at full output. Node S1H from PFT1 is connected to node PFVC of sub-circuit PFA. The zero crossings of the core are sensed when the voltage at S1H is at zero. The core zero crossings are used to reset the PFC and start a new cycle. The positive node of the DC side of bridge BR+ is connected through capacitor C2 to BR-. C2 is selected for various line and load conditions to de-couple switching current from the line improving power factor while reducing line harmonics and EMI. Primary of NSME sub-circuit PFT1 (FIG. 18) pins P1B and S2CT connects to pin SNL1 of snubber sub-circuit SN (FIG. 30), to sub-circuit BR pin BR+ and connects to pin BR+ (FIG. 1A). The return line for the rectified AC power BR- is connected to the following pins: BR- of sub-circuit BR, PFA pin BR-, sub-circuit AMP pin GAO, output switch Q1 source, capacitor C2, sub-circuit CP pin CT0 sub-circuit PFT1 pin S1CT and CT20 through EMI filter capacitor C1 to earth ground node LLO. Pin BR+ from FIG. 1 is connected to FIG. 1A sub-circuits CPA pin SN pin SNL1, sub-circuit PFT1 pin P1B, and sub-circuit PFT1 pin S2CT. Pin BR+ continues to FIG. 1A connecting to sub-circuit CPA pin CT20, PPG (FIG. 43) pin PPG0, sub-circuit AMP1 pin GA0, sub-circuit AMP2 pin GA0, sub-circuit IPFFB pin PF-, Capacitor [C16||C17|| resistor R17], transistor Q6 source, transistor Q9 source, sub-circuit SNA pin SNA2 and sub-circuit SNB pin SNB2. The drain of output switch Q1 is connected to diode D4 anode, subcircuit SNB pin SNL2, and sub-circuit PFT1 pin P1A and sub-circuit SN pin SNL2. Snubber network SN reduces the high voltage stress to Q1 until flyback diode D4 begins conduction. Line coupled, power factor corrected boost regulated output voltage of the AC to DC converter stage (FIG. 1) appears on node PF+. Addition efficiency may be realized by connecting sub-circuit DSN (FIG. 30A) in parallel with D4. The regulated boost output PF+ connects to the following: sub-circuit SN pin SNOUT, sub-circuit DSN pin SNOUT and diode D4 cathode. Node PF+ also connects on FIG. 1A to capacitors [C16||C17||R17], subcircuit IPFFB (FIG. 40) pin PF+, sub-circuit PPT1 (FIG. 19) pin P2CT, snubber sub-circuit SNA (FIG. 31) pin SNA3, and snubber SNB (FIG. 32) pin SNB3. Magnetic element winding pin S1H of sub-circuit PFT1 is connected to CP pin CT1A and pin PFVC of sub-circuit PFA. Magnetic element winding node S1L of sub-circuit PFT1 is connected to CP pin CT2A. Magnetic element winding node S2H of sub-circuit PFT1 is connected to pin 10FIG. 1A then to CPA pin CT1B. Magnetic element winding node S2L of subcircuit PFT1 is connected to pin 12FIG. 1A then to CPA pin CT2B. Sub-circuit PFA using the AC line phase, load voltage, and magnetic element feedback, generates a command pulse PFCLK. Pin PFCLK of sub-circuit PFA (FIG. 23) is connected to the input of buffer amplifier pin GA1 of sub-circuit AMP1 (FIG. 29). Buffered high-speed gate drive output pin GA2 of sub-circuit AMP is connected to gate of switch FET Q1. The buffering provided by AMP shortens switch Q1 ON and OFF times greatly reducing switch losses (see FIGS. 13 & 14). The source of Q1 with pin GA0 is connected to return node BR-. Power to sub-circuit AMP is connected to pin GA+ from sub-circuit OTP pin TS+. Thermal switch THS1 is connected to Q1. In the event the case of Q1 reaches approximately 105C THS1 opens removing power to sub-circuit AMP, safely shutting down the first (input) stage. Normal operation resumes after the switch temperature drops 20-30 deg. C. closing THS1. Drain of output switch Q1 is connected to primary winding pin P1A of non-saturating magnetic sub-circuit PFT1 (FIG. 18) and to pin SNL2 of snubber sub-circuit SN (FIG. 30). Reference voltage from PFC sub-circuit PFA pin PFA2 is connected to feedback networks sub-circuit IPFFB pin FBC and to subcircuit IFB pin FBC. Control current feedback networks is summed at node PF1 of sub-circuit PFA. Pin PF1 is connected to feed back networks sub-circuit IPFFB pin FBE and to sub-circuit IFB pin FBE. Constant frequency/duty-cycle non-overlapping two-phase generator sub-circuit PPG (FIG. **431**A) generates the drive for the push-pull output stage. Phase one output pin PH1 is connected to sub-circuit AMP1 pin GA1, second phase output pin PH2 is connected to sub-circuit AMP2 pin GA1. Output of amplifier buffer sub-circuit AMP1 pin GAP2 connects to gate of push-pull output switch Q6. Output of amplifier buffer sub-circuit AMP2 pin GAP2 connects to gate of push-pull output switch Q9. The buffering currents from AMP1 and AMP2 provide fast, low impedance critically damped switching to Q6 and Q9 greatly reducing ON-OFF transition time and switching losses. Regulated 18-volt power from sub-circuit CPA (FIG. 1A) pin CP2+ is connected to amplifier buffer sub-circuit AMP1 pin GA+, amplifier buffer sub-circuit AMP2 pin GA+ and sub-circuit PPG pin PPG+. Drain of transistor Q6 is connected to snubber network sub-circuit SNB pin SNB1and to non-saturating center tapped primary magnetic element sub-circuit PPT1 pin P2H. Drain of transistor Q9 is connected to snubber network sub-circuit SNA (FIG. 31) pin SNA1 and sub-circuit PPT1 pin P2L. Source of transistor Q6 is connected to snubber network sub-circuit SNB pin SNB2, transistor Q9 source, sub-circuit SNA pin SNA2 and to return node BR+. Isolated output of NSME sub-circuit PPT1 pin SH connects to Pin C7B of rectifier sub-circuit OUTA (FIG. 25A), pin SL connects to sub-circuit OUTA C8B. Center tap of PPT1 pin SCT is the output return or negative node OUT- it connects to sub-circuit OUTA pin OUT- and sub-circuit IFB (FIG. 40B) pin OUT- and RLOAD. Converter positive output from sub-circuit OUTA pin OUT+ is connected to RLOAD and sub-circuit IFB pin

OUT+. FIG. 1 elements LL1, BR, PFA, AMP, Q1, IPFFB, IFB and PFT1 (input stage) perform power factor corrected AC to DC conversion. The regulated high voltage output of this converter supplies the efficient fixed frequency/dutycycle push-pull stage comprising PPG, AMP1, AMP2, Q6, Q9, PPT1 and OUTA (FIG. 1A). Magnetic element subcircuit PPT1 provides galvanic isolation and minimal voltage overshoot and ripple in the secondary thus minimizing filtering requirements of the rectifier sub-circuit OUTA. Five volt reference output from sub-circuit PFA pin PFA2 connects to pin 15 then to FIG. 1A sub-circuit IPFFB pin FBC and to sub-circuit IFB pin FBC. Pulse width control input from sub-circuit PFA pin PF1 connects to pin 14 then to FIG. 1A sub-circuit IPFFB pin FBE and to sub-circuit IFB pin FBE. Sub-circuit IFB provides high-speed feedback to the AC DC converter, the speed of the boost stage provides precise output voltage regulation and active ripple rejection. In the event of sudden line or load changes, sub-circuit IPFFB corrects the internal boost to maintain regulation at the isolated output. Remote load sensing and other feedback schemes known in the art may be implemented with subcircuit IPFFB. This configuration provides power factor corrected input transient protection, rapid line-load response, excellent regulation, isolated output and quiet efficient operation at high temperatures.

[0091] FIG. 2 is a schematic diagram of an embodiment of a DC to AC converter. The invention DCAC1 is an efficient push-pull converter. Comprised of sub-circuits PPG (FIG. 43), AMP1 (FIG. 29), AMP2 (FIG. 29), SNB (FIG. 32), SNA (FIG. 31), PPT1 (FIG. 19) and OUTA (FIG. 25), switches Q6 and Q9.

| FIG. 2  | Table             |

|---------|-------------------|

| Element | Value/part number |

| Q6      | FS 14SM-18A       |

| Q9      | FS 14SM-18A       |

[0092] Converter ACDC1 accepts variable DC voltage and efficiently converts it to a variable AC voltage output at a fixed frequency. Variable frequency operation may be achieved by simple changes to PPG. In this embodiment fixed frequency operation is required. The magnetic element comprises non-saturating magnetics. A graph of B-H hysteresis for the non-saturating magnetics is set forth in **FIG.** 15. Variable DC voltage is applied to pin DC+. The pin DC+ connects to the following, sub-circuit PPT1 (FIG. 19) pin P2CT, snubber sub-circuit SNA (FIG. 31) pin SNA3, and snubber SNB (FIG. 32) pin SNB3. Constant frequency non-overlapping two-phase generator sub-circuit PPG (FIG. 43) generates the drive for the push-pull output switches. Phase one output pin PH1 is connected to sub-circuit AMP1 pin GA1, the second phase output pin PH2 is connected to sub-circuit AMP2 pin GA1. Output of amplifier buffer sub-circuit AMP1 pin GAP2 connects to gate of push-pull output switch Q6. Output of amplifier buffer sub-circuit AMP2 pin GAP2 connects to gate of push-pull output switch Q9. The buffering provided by AMP1 and AMP2 shortens switch Q1 ON and OFF times greatly reducing switching losses (See FIGS. 13 and 14). External regulated 18-volt power from pin P18V connected to amplifier buffer subcircuit AMP1 pin GA+, amplifier buffer sub-circuit AMP2 pin GA+ and sub-circuit PPG pin PPG+. Drain of transistor Q6 is connected to snubber network sub-circuit SNB pin SNB1 and to non-saturating center tapped primary magnetic element sub-circuit PPT1 pin P2H. Drain of transistor Q9 is connected to snubber network sub-circuit SNA (FIG. 31) pin SNA1 and sub-circuit PPT1 pin P2L. Source of transistor Q6 is connected to snubber network sub-circuit SNB pin SNB2, transistor Q9 source, sub-circuit SNA pin SNA2, sub-circuit AMP1 pin GA0, sub-circuit AMP2 pin GA0, sub-circuit PPG pin PPGO, and to return pin DC-. AC output of NSME sub-circuit PPT1 pin SH connects to Pin ACH, pin SL connects to pin ACL. Center tap of PPT1 pin SCT is connected to pin ACO. Magnetic element sub-circuit PPT1 provides galvanic isolation and minimal voltage overshoot in the secondary thus minimizing filtering requirements if a rectifier assembly is attached. Sub-circuit DCAC1 may be used as a stand-alone converter or as a fast quiet efficient stage in a multi stage converter system. Sub-circuit DCAC1 achieves isolated output, quiet operation, efficient conversion, and operation at high and low temperatures.

[0093] FIGS. 3 and 3A is a three-stage version of the present invention. The arrangement is comprised of an AC-DC or DC-DC boost converter stage, DC-DC forward converter stage, and a push-pull stage. This system reduces losses by combining low current buck regulation, buffered switching, rectified snubbering, and NSME in each stage. A power factor corrected boost stage is used to assure that any load connected to the converter looks like a resistive load to the AC line, eliminating undesirable harmonic and displacement currents in the AC power line. NSME having a lower permeability compared to the prior art are used to minimize magnetizing losses, improve coupling efficiency, minimize magnetic element heating, eliminate saturated core current spikes/gap leakage, reduce parts count, reduce thermal deterioration, and increase MTBF (mean time before failure). The invention also uses an emitter follower circuit with a high speed switching FET to slew the main FET gate rapidly. The use of non-saturating magnetics allows operation at higher voltages, which proportionally lowers current further reducing switch, magnetic element, and conductor losses due to I<sup>2</sup>R heating. High voltage FET switches have the added benefit of lower gate capacitance, which translates to faster switching. At turn on, the n-channel gate drive FET quickly charges the main FET gate. At turn off, a PNP Darlington transistor switch quickly discharges the main FET gate. The flyback effect in the PFC stage is managed by use of rectifying RC networks positioned across the output diode with an additional capacitor coupled diode across the switched magnetic element to decouple and further dampen the inductive flyback.

[0094] FIG. 3 and FIG. 3A is a schematic diagram of a three stage AC to DC converter. FIGS. 3 and 3A is a three-stage version of the present invention. The arrangement is comprised of an AC-DC or DC-DC boost converter stage, DC-DC forward converter stage, and a push-pull stage. This system reduces losses by combining low current buck regulation, buffered switching, rectified snubbering, and NSME in each stage. A power factor corrected boost stage is used to assure that any load connected to the converter looks like a resistive load to the AC line, eliminating undesirable harmonic and displacement currents in the AC power line. NSME having a lower permeability compared to the prior art are used to minimize magnetizing losses, improve coupling efficiency, minimize magnetic ele-

ment heating, eliminate saturated core current spikes/gap leakage, reduce parts count, reduce thermal deterioration, and increase MTBF (mean time before failure). The invention also uses an emitter follower circuit with a high speed switching FET to slew the main FET gate rapidly. The use of non-saturating magnetics allows operation at higher voltages, which proportionally lowers current further reducing switch, magnetic element, and conductor losses due to I<sup>2</sup>R heating. High voltage FET switches have the added benefit of lower gate capacitance, which translates to faster switching. At turn on, the n-channel gate drive FET quickly charges the main FET gate. At turn off, a PNP Darlington transistor switch quickly discharges the main FET gate. The flyback effect in the PFC stage is managed by use of rectifying RC networks positioned across the output diode with an additional capacitor coupled diode across the switched magnetic element to decouple and further dampen the inductive flyback. The invention is comprised of a power factor corrected regulating boost stage with line protection filter sub-circuit LL1 (FIG. 21) and full-wave rectifier sub-circuit BR (FIG. 22) and capacitors C1 and C2. Subcircuits PFB (FIG. 24), resistor R2, rectifier CP (FIG. 26), magnetic element PFT1 (FIG. 18), over temperature protection OTP (FIG. 28) snubber SN (FIG. 30) gate buffer AMP (FIG. 29), switch transistors Q1, flyback diode D4, holdup capacitors C17 and C16, bleed resistor R17, and voltage feedback sub-circuit FBA (FIG. 40A). An efficient second pre-regulating buck stage with sub-circuits PWFM (FIG. 33), current sense resistor R26, rectifier CPA (FIG. 27), magnetic element BL1 (FIG. 18B), over voltage protection OVP (FIG. 42), IPFFB (FIG. 40) gate buffer AMP3 (FIG. 29), switch transistor Q2, flyback diode D70, storage capacitor C4, and voltage feedback sub-circuit IFB (FIG. 40B).

[0095] An efficient third push-pull isolation stage with sub-circuits CPA (FIG. 27), two-phase generator PPG (FIG. 43), gate buffers AMP1 (FIG. 29) and AMP2 (FIG. 29), switch transistors Q6, and Q9, snubbers SNA (FIG. 31) and SNB (FIG. 32), magnetic element PPT1 (FIG. 19) and rectifier OUTA (FIG. 25).

| FIG. 33A<br>Element | Table<br>Value/part number |

|---------------------|----------------------------|

| C1                  | .01 uf                     |

| C2                  | 1.8 uf                     |

| R2                  | 100 k ohms                 |

| D4                  | STA1206 DI                 |

| R17                 | 375 k ohms                 |

| Q1                  | IRFP460                    |

| C16                 | 100 uf                     |

| C17                 | 100 uf                     |

| R26                 | .05 ohms                   |

| D70                 | STA1206 DI                 |

| Q2                  | IRFP460                    |

| C4                  | 10 uf                      |

| Q6                  | FS14Sm-18A                 |

| <b>Q</b> 9          | FS14Sm-18A                 |

[0096] AC line is connected to sub-circuit LLA (FIG. 21) between pins LL1 and LL2. AC/earth ground is connected to node LL0. The filtered and voltage limited AC line appears on node/pin LL5 of sub-circuit LLA and connected to node BR1 of bridge rectifier sub-circuit BR. The neutral/AC return leg of the filtered and voltage limited AC appears on

pin LL6 of sub-circuit LL is connected to input pin BR2 of BR. The line voltage is full-wave rectified and is converted to a positive haversine appearing on node BR+ of sub-circuit BR. Start up resistor R2 connects BR+ to sub-circuit CP pin CP+. Node CP+ connects to pins PFA+ of control element sub-circuit PFB and over temperature switch sub-circuit OTP pin GAP. Resistor R2 provides start up power to the control element until the regulator CP is at full output. Node S1H from PFT1 is connected to pin 31 (FIG. 3) then to pin CT1A of sub-circuit CP and pin PFVC of sub-circuit PFB. The zero crossing of the core bias are sensed when the voltage at S1H is at zero relative to BR-. The core zero crossings are used to reset the PFC and start a new cycle. The positive node of the DC side of bridge BR+ is connected through capacitor C2 to BR-. Capacitor C2 is selected for various line and load conditions to de-couple switching current from the line improving power factor. Sub-circuit BR pin BR+ connects to pin SNL1 of snubber sub-circuit SN, sub-circuit PFB pin BR+ and pin BR+ (FIG. 3A) then to primary of NSME sub-circuit PFT1 pin P1B and to sub-circuit OVP pin BR+. The return line for the rectified AC power is connected to the following pins; BR- of sub-circuit BR, sub-circuit PFT1 pin S1CT, PFC sub-circuit PFB pin BR-, sub-circuit FBA pin BR-, capacitor C2, sub-circuit CP pin CT0, sub-circuit IPFFB pin FBE, and through EMI filter capacitor C1 to earth ground node LL0. Node BR- continues to FIG. 3A connecting to R26, capacitors [C16||C17||R17], sub-circuit OVP pin BR-, sub-circuit PWFM pin PWFM0, sub-circuit AMP3 pin GA0, switch Q2 source. Floating ground node PF- is connected to magnetic element sub-circuit PFT1 pin S2CT, rectifier sub-circuit CPA pin CT20, generator sub-circuit PPG (FIG. 43) pin PPG0, sub-circuit AMP1 pin GA0, sub-circuit AMP2 pin GAO, capacitor C4, magnetic element BL1 pin, transistor Q6 source, transistor Q9 source, sub-circuit SNA pin SNA2 sub-circuit SNB pin SNB2, pin PF-FIG. 3 then to subcircuit IPFFB pin PF-. Drain of output switch Q1 is connected to diode D4 anode, sub-circuit SN pin SNL2, then to pin 34 of FIG. 3A then to sub-circuit PFT1 pin P1A. Snubber SN reduces the high voltage stress to Q1 until flyback diode D4 begins conduction. Additional rectification efficiency and protection is achieved by adding sub-circuit DSN (FIG. 30A) across flyback diode D4. Feedback corrected boost output voltage of the power factor corrected AC to DC converter stage appears across nodes PF+ and PF+. The regulated 385-volt boost output node PF+ connects to the following; sub-circuit SN pin SNOUT, diode D4 cathode, sub-circuit IPFFB (FIG. 40) pin PF+, sub-circuit FBA pin PF+, then to pin PF+ of FIG. 3A, capacitors [C16||C17||R17], magnetic element sub-circuit PTT1 (FIG. 19) pin P2CT, snubber sub-circuit SNA (FIG. 31) pin SNA3, and snubber SNB (FIG. 32) pin SNB3, sub-circuit OVP pin PF+, capacitor C4 and diode D70 cathode. Magnetic element winding node S1H of sub-circuit PFT1 is connected to pin 31FIG. 3 then to sub-circuit CP pin CT1A and pin PFVC of sub-circuit PFB. Magnetic element winding node S1L of sub-circuit PFT1 is connected to pin 33FIG. 3 then to sub-circuit CP pin CT2A. Magnetic element winding node S2H of sub-circuit PFT1 is connected to CPA pin CT1B. Magnetic element winding node S2L of subcircuit PFT1 is connected to CP pin CT2B. Sub-circuit PFB using feedback from the phase of the AC line, Q1 switch current, magnetic bias first stage and output voltage feedback generates a command pulse on pin PFCLK. Pin

PFCLK of sub-circuit PFB (FIG. 24) is connected to the input of buffer AMP amplifier pin GA1 of sub-circuit AMP1. Buffered high-speed low impedance gate drive output pin GA2 of sub-circuit AMP is connected to gate of switch FET Q1. The buffering provided by AMP shortens switch Q1 "ON" and "OFF" times greatly reducing switch losses (See FIGS. 13 and 14). The source of Q1 is connected to sub-circuit AMP pin GAO, pin 35 of FIG. 3A then to current sense resistor R26 connected to return node BR-. The voltage developed across R26 is fed back to PFB pin PFSC. This signal is used to protect the switch by reducing the pulse width in response to a low line or high load induced over current fault. The return line of sub-circuit FBA pin BR- is connected to node BR- and to pin BR- of sub-circuit PFB. This feedback is non-isolated; network values are selected for the first stage to develop a 385-Volt output at PF+. Sub-circuit feedback network FBA (FIG. 40A) pin PF1 is connected to sub-circuit PFB pin PF1. Controller PFB modulates PFCLK signal to maintain a substantially constant 385-voltage at PF+ independent of line and load conditions. In the event of a component failure in sub-circuit FBA the PBF may command the converter to very high voltages. Sub-circuit OVP monitors the first stage boost in the event it exceeds 405-volts OVP will clamp the output of sub-circuit BR causing fuse F1 in sub-circuit LLA to open. An alternate over voltage network OVP1 (FIG. 42A) may replace OVP clamping the 18-volt control power stopping the boost action of the converter without opening the fuse. Sampled converter output at node from sub-circuit FBA pin PF1 is connected to sub-circuit PFB pin PF1. The haversine on BR+ is used with an internal multiplier by PFB to generate variable width control pulses on pin PFCLK. The high frequency modulation of switch Q1 makes the load/ converter appear resistive to the AC line. Over temperature protection sub-circuit OTP pin TS+ is connected to subcircuit AMP pin GA+. Thermal switch THS1 is connected to Q1. In the event Q1 reaches approximately 105C THS1 opens removing power to sub-circuit AMP, safely shutting down the first stage. Normal operation resumes after the temperature decreases 20-30C closing THS1. The second stage is configured as a buck stage. It accepts the 385-Volt output of the first stage. By employing a second floating reference node PF- energy storage element capacitor C4 the voltage to the final push-pull stage may be regulated with minimal loss. Power from sub-circuit CP pin CP18V+ is connected to pin 30 of FIG. 3A then to sub-circuit PWFM (FIG. 33) pin PWM+ and AMP3 pin GA+. Feedback current from sub-circuit IPFFB pin FBC is connected to pin 36FIG. 3A then to sub-circuit IFB pin FBC and sub-circuit PWFM pin PF1. Sub-circuit IPFFB only shunts current from this node if the output of the second stage is greater than 200-volts. When the converter reaches its designed output voltage, IFB shunts current from PWFM pin PF1 signaling PWFM to reduce the pulse width on pin PWMCLK. Subcircuit AMP3 input pin is connected to sub-circuit PWFM pin PWMCLK. Output of AMP3 buffer pin GA2 is connected to gate of switch Q2. Drain of Q2 is connected to anode of D70 and non-saturating magnetic sub-circuit BL1 pin P2B (FIG. 18B). Turning on switch Q2 charges C4 also storing energy in magnetic element BL1. Releasing switch Q2 allows energy stored in magnetic element BL1 to charge C4 through flyback diode D70. Larger pulse widths charge C4 to larger voltages thus efficiently blocking part of the first stage voltage to the final push-pull stage. This action provides regulated voltage to the final converter stage. The third and final push-pull (transformer) converter stage provides the galvanic isolation, filtering and typically converts the internal high voltage bus to a lower regulated output voltage. The efficient push-pull stage produces alternating magnetizing currents in the NSME for maximum load over core mass. Constant frequency non-overlapping two-phase generator sub-circuit PPG (FIG. 43) generates the drive for the push-pull output stage. Phase one output pin PH1 is connected to sub-circuit AMP1 pin GA1, output pin PH2 is connected to sub-circuit AMP2 pin GA1. Output of amplifier buffer sub-circuit AMP1 pin GAP2 connects to gate of push-pull output switch Q6. Output of amplifier buffer sub-circuit AMP2 pin GAP2 connects to gate of push-pull output switch Q9. The buffering provided by AMP1 and AMP2 shortens switch Q1 ON and OFF times greatly reducing switching losses. (See FIGS. 13 and 14) Regulated 18-volt power from sub-circuit CPA pin CP18+ is connected to amplifier buffer sub-circuit AMP1 pin GA+, amplifier buffer sub-circuit AMP2 pin GA+ and sub-circuit PPG pin PPG+. Drain of transistor Q6 is connected to snubber network sub-circuit SNB pin SNB1 and to non-saturating center tapped primary magnetic element sub-circuit PPT1 pin P2H. Drain of transistor Q9 is connected to snubber network sub-circuit SNA (FIG. 31) pin SNA1 and subcircuit PPT1 pin P2L. Return node PF- connects source of transistor Q6 to snubber network sub-circuit SNB pin SNB3, transistor Q9 source, sub-circuit SNA pin SNA3 and to return node GND2. Output of NSME sub-circuit PPT1 pin SH connects to pin C7B of rectifier sub-circuit OUTA (FIG. 25), pin SL connects to C8B. Center tap of PPT1 pin SCT is the output return or negative node OUT- it connects to sub-circuit pin OUT- and sub-circuit IFB pin OUT- and RLOAD. Supply positive output from sub-circuit OUTA pin OUT+ is connected to RLOAD and sub-circuit IFB pin OUT+. Elements LL1, BR, PFA, AMP, Q1, IPFFB, IFB and PFT1 provide power factor corrected AC to DC conversion and DC output regulation. The regulated high voltage output of this converter is used to power the efficient fixed frequency push-pull stages PPG, AMP1, AMP2, Q6, Q9, PPT1 and OUTA. Magnetic element sub-circuit PPT1 provides galvanic isolation and minimal voltage overshoot in the secondary thus minimizing filtering requirements of the rectifier sub-circuit OUTA. Sub-circuit IFB provides highspeed feedback to the AC DC converter, the speed of the boost stage provides precise output voltage regulation and active ripple rejection. In the event of a sudden line or load changes sub-circuit IPFFB compensates the internal boost. This system reduces losses by focusing output control in the middle (low current) stage of the converter and by using non-saturating magnetics, buffered switching, and rectifying snubbers throughout each stage. The combined improvements translate to higher system efficiencies, higher power densities, lower operating temperatures, and, improved thermal tolerance thereby reducing or eliminating the need for forced air-cooling per unit output. The non-saturating magnetic properties are relatively insensitive to temperature (see FIG. 17), thus allowing the converter to operate over a greater temperature range. In practice, the operating temperature for the Kool Mu NSME is limited to 200C by wire/core insulation; the non-saturating magnetic material remains operable to near its Curie temperature of 500C. This configuration provides power factor corrected input transient protection, rapid line-load and ripple compensation,

excellent output regulation, output isolation and quiet efficient operation at high temperatures.

[0097] FIG. 4 is a schematic diagram sub-circuit ACD-

[0098] FIG. 4 is a schematic diagram of a power factor corrected single stage AC to DC converter sub-circuit ACD-CPF. The invention is comprised of line protection filter sub-circuit LL (FIG. 20) and full-wave rectifier sub-circuit BR (FIG. 22). A power factor corrected regulated boost stage with sub-circuits PFB (FIG. 24), snubber sub-circuit SN (FIG. 30), magnetic element sub-circuit PFT1A (FIG. 18A), sub-circuit CP (FIG. 26), buffer sub-circuit AMP (FIG. 29), over temperature sub-circuit OTP (FIG. 28), and voltage feedback sub-circuit FBA (FIG. 40A). Start up resistor R2, filter capacitor C1, PFC capacitor C2, flyback diode D4, switch transistor Q1, hold up capacitors C17 and C16, and resistor R17.

| FIG. 4                                                 | Table                                                                           |

|--------------------------------------------------------|---------------------------------------------------------------------------------|

| Element                                                | Value/part number                                                               |

| C1<br>C2<br>R2<br>R26<br>Q1<br>D4<br>C17<br>C16<br>R17 | .01 uf 1.8 uf 100 k ohms 0.05 ohms IRFP 460 STA1206 DI 100 uf 100 uf 375 k ohms |

[0099] AC line is connected to sub-circuit LL (FIG. 20) between pins LL1 and LL2. AC/earth ground is connected to node LL0. The filtered and voltage limited AC line appears on node/pin LL5 of sub-circuit LL1 and connected to node BR1 of bridge rectifier sub-circuit BR (FIG. 22). The neutral/AC return leg of the filtered and voltage limited AC appears on pin LL6 of sub-circuit LL is connected to input pin BR2 of BR. The line voltage is full-wave rectified and is converted to a positive haversine appearing on node BR+ of sub-circuit BR (FIG. 22). Start up resistor R2 connects BR+ to sub-circuit CP pin CP+. Node CP+ connects to pins PFA+ of power factor controller sub-circuit PFA (FIG. 24) and over temperature switch sub-circuit OTP (FIG. 28) pin GAP. Resistor R2 provides start up power to the control element until the rectifier and regulator CP is at full output. Node S1H from PFT1A is connected to node PFVC subcircuit PFB. The zero crossing of the core bias are sensed when the voltage at S1H is at zero. The core zero crossings are used to reset the PFC and start a new cycle. The positive node of the DC side of bridge BR+ is connected through capacitor C2 to BR-. C2 is selected for various line and load conditions to de-couple switching current from the line improving power factor. Primary of NSME sub-circuit PFT1A (FIG. 18A) pin P1B connects to pin SNL1 of snubber sub-circuit SN (FIG. 30), sub-circuit PFB pin BR+ and connects to node BR+. The return line for the rectified AC power BR- is connected to the following pins; BR- of sub-circuit BR, sub-circuit PFB pin BR-, sub-circuit AMP pin GAO, sense resistor R26, capacitor [C16||C17 ||resistor R17], capacitor C2, sub-circuit CP pin CT0, sub-circuit PFT1A pin S1CT and through EMI filter capacitor C1 to earth ground node LLO. Drain of output switch Q1 is connected to diode D4 anode, sub-circuit PFT1A pin P1A and snubber sub-circuit SN pin SNL2. Additional rectification efficiency and protection is achieved by adding subcircuit DSN (FIG. 30A) in parallel flyback diode D4. Sub-circuit provides reduces the high voltage stress to Q1 until flyback diode D4 begins conduction. Line coupled, power factor corrected boost regulated output voltage of the AC to DC converter stage (FIG. 1) appears on node PF+. The regulated boost output PF+ connects to the following; sub-circuit SN pin SNOUT, diode D4 cathode, capacitor [C16||C17||R17], and snubber DSN (FIG. 30A) pin SNOUT. Magnetic element winding node S1H of sub-circuit PFT1A is connected to CP pin CT1A and pin PFVC of sub-circuit PFB. Magnetic element winding node S1L of sub-circuit PFT1A is connected to CP pin CT2A. Sub-circuit PFB using the phase of the AC line, and load voltage generates a command pulse PFCLK. Pin PFCLK of sub-circuit PFB (FIG. 24) is connected to the input of buffer amplifier pin GA1 of sub-circuit AMP1 (FIG. 29). Buffered high-speed gate drive output pin GA2 of sub-circuit AMP is connected to gate of switch FET Q1. The buffering provided by AMP shortens switch Q1 ON and OFF times greatly reducing switch losses. The source of Q1 is connected to current sense resistor R26, pin PFSC of sub-circuit PFB, connected then to return node BR-. The voltage developed across R26 is feedback to PFB pin PFSC. This signal is used to protect the switch in the event of an over current fault. Thermal switch THS1 is connected to Q1. In the event Q1 reaches approximately 105C THS1 opens removing power to sub-circuit AMP, safely shutting down the first stage. Normal operation resumes after the switch temperature drops 20-30 C. closing THS1. Sub-circuit feedback network FBA (FIG. 40A) pin PF1 is connected to sub-circuit PFB pin PF1. Converter output at node PF+ (the junction of C17||C16 and D4) is connected to sub-circuit FBA pin PF+. The return line of sub-circuit FBA pin BR- is connected to pin BR- of sub-circuit PFB. This feed back is non-isolated; network values are selected for a substantially constant 385-Volt output at PF+ relative to BR-. The high-voltage haversine from the rectifier section BR pin BR+ is connected to sub-circuit PFB pin BR+. The haversine is used with an internal multiplier by PFB to make the converter ACDCPF appear resistive to the AC line. Sub-circuits LL1, BR, PFB, AMP, Q1, OTP, FBA, IFB and PFT1A perform power factor corrected AC to DC conversion. The regulated high voltage output of this converter may be used use to power one or more external converters connected to the PF+ and BRnodes. The NSME sub-circuit PPT1A provides efficient boost action at high power levels in a very small form factor. Sub-circuit FBA provides high-speed feedback to the converter the speed of the boost stage provides precise output voltage regulation and active ripple rejection. This configuration provides power factor corrected input transient protection, rapid line-load response, excellent regulation, and quiet efficient operation at high temperatures.

[0100] FIG. 5 is a graph comparing typical currents in saturating and non-saturating magnetic elements. As the inductance does not radically change at high temperatures and currents in the NSME, the large current spikes due to the rapid reduction of inductance common in saturating magnetics is not seen. As a result, destructive current levels, excessive gap leakage, magnetizing losses, and magnetic element heating are avoided in NSME.

[0101] FIG. 6 is a schematic for non-isolated low side switch buck converter sub-circuit NILBK. Sub-circuit NILBK consists of resistor R20, diode D6, capacitor C6, FET transistor Q111, sub-circuit CP (FIG. 26), sub-circuit PFT1A (FIG. 18A), sub-circuit IFB (FIG. 40B), sub-circuit AMP (FIG. 29) and sub-circuit PWFM (FIG. 33).

| FIG. 6  | Table             |

|---------|-------------------|

| Element | Value/part number |

| R20     | 100 k ohms        |

| R20     | STA1206 DI        |

| Q111    | IRFP460           |

| C6      | 10 uf             |

[0102] External power source VBAT connects to pins DCIN+ and DCIN-. From DCIN+ through resistor R20 connects to sub-circuit CP pin CP+, sub-circuit AMP pin GA+ and to sub-circuit PWFM pin PWFM+. Resistor R20 provides startup power to the converter before regulator sub-circuit CP reaches it full 18-volt output. VBAT negative is connected to pin DCIN- connects to sub-circuit PWFM pin PWFM0, sub-circuit AMP pin GA0, Q111 source, subcircuit IFB pin FBE, sub-circuit CP pin CT0, and sub-circuit PFT1 pin S1CT. Magnetic element winding node S1H of sub-circuit PFT1A is connected to CP pin CT1A. Magnetic element winding node S1CT of sub-circuit PFT1 is connected to CP pin CT0. Magnetic element winding node S1H of sub-circuit PFT1A is connected to CP pin CT2A. The regulated 18 volts from sub-circuit CP+ is connected to R20, sub-circuit AMP pin GA+ and to sub-circuit PWFM pin PWFM+. Sub-circuit PWFM is designed for variable pulse width operation. PWFM is configured for maximum pulse width 90-95% with no feedback current from sub-circuit IFB pin FBC. Increasing the feedback current reduces the pulse-width and output voltage from converter NILBK. Sub-circuit PWFM clock/PWM output pin CLK is connected to the input pin GA1 of buffer sub-circuit AMP. The output of sub-circuit AMP pin GA2 is connected to the gate of Q111. Input node DCIN+ connects to the cathode of flyback diode D6, sub-circuit IFB pin OUT+, resistor RLOAD, capacitor C6 and pin B+. The drain of Q111 is connected to sub-circuit PFT1 pin P1B and the anode of D6. Pin P1A of sub-circuit PFT1A is connected to capacitor C6, RLOAD, sub-circuit IFB pin OUT- and to node B-. With sub-circuit PWFM pin CLK high buffer AMP output pin GA2 charges the gate of transistor switch Q111. Switch Q111 conducts charging capacitor C10 through NSME PFT1A from source VBAT and storing energy in PFT1A. Feedback output pin FBC from sub-circuit IFB is connected to sub-circuit PWFM pulse-width adjustment pin PW1. Sub-circuit IFB removes current from PW1 commanding PWFM to reduce the pulse-width or on time of signal CLK. After sub-circuit PWFM reaches the commanded pulsewidth PWFM switches output pin CLK low turning "off" Q111 stopping the current into PFT1A. The energy not transferred into regulator sub-circuit CP load is released from NSME PFT1A into the now forward biased diode D6 charging capacitor C6. By modulating the "on" time of switch Q111 the converter buck voltage is regulated. Regulated voltage is developed across Nodes B- and B+. Subcircuit IFB provides the isolated feedback voltage to the sub-circuit PWFM. When sub-circuit IFB senses the converter output (nodes B+ and B-) is at the designed voltage, current from REF is removed from PM1. Sinking current from PM1 commands the PWFM to a shorter pulse-width thus reducing the converter output voltage. In the event the feedback signal from IFB commands the PWFM to minimum output. Gate drive to switch Q111 is removed stopping all buck activity capacitor C6 discharges through RLOAD. Input current from VBAT is sinusoidal making the converter very quiet. In addition the switch Q111 is not exposed to large flyback voltage. Placing less stress on the switches thereby increasing the MTBF. Sub-circuit NILBK takes advantage of the desirable properties of the NSME in this converter topology. Adjusting the NSME 100 (FIG. 18A) primary inductance and component values in sub-circuit IFB determines the output buck voltage.

[0103] FIG. 8 is a schematic for a tank coupled single stage converter sub-circuit TCTP. Sub-circuit TCTP consists of resistor R20 and RLOAD, capacitor C10, Darlington transistors Q10 and Q20, sub-circuit CP (FIG. 26), sub-circuit PFT1 (FIG. 18), sub-circuit OUTB (FIG. 25A), sub-circuit IFB (FIG. 40B) and sub-circuit PWFM (FIG. 33).

| FIG. 8<br>Element        | Table<br>Value/part number              |  |

|--------------------------|-----------------------------------------|--|

| R20<br>Q10<br>Q20<br>C10 | 5 k ohms<br>TST541<br>IRFP460<br>1.8 uf |  |

[0104] External power source VBAT connects to pins DCIN+ and DCIN-. From DCIN+ connects to Q10 collector then through resistor R20 connects to sub-circuit CP pin CP+ and to sub-circuit PWFM pin PWFM+. Resistor R20 provides startup power to the converter before regulator sub-circuit CP reaches it full 18-volt output. VBAT negative is connected to pin DCIN- ground/return node GND. Node GND connects to sub-circuit PWFM0 pin PWFM0, Q20 collector, C10, sub-circuit CP pin CT0 and sub-circuit PFT1 pin S1CT. Magnetic element winding node S1H of subcircuit PFT1 is connected to CP CT1A. Magnetic element winding node S1L of sub-circuit PFT1 is connected to CP CT2A. Magnetic element winding node S1CT of sub-circuit PFT1 is connected to CP pin CT0. Magnetic element winding node S2H of sub-circuit PFT1 is connected to CP pin CT2A. The regulated 18 volts from sub-circuit CP+ is connected to R20 and to sub-circuit PWFM pin PWFM+. Sub-circuit PWFM is designed for a constant 50% duty cycle variable frequency generator. Sub-circuit PWFM clock output pin CLK is connected to the base of Q10 and Q20. The emitters of Q10 and Q20 are connected to subcircuit PFT1 pin P1B. This forms an emitter follower configuration. Pin P1A of sub-circuit PFT1 is connected through tank capacitor C10 to node GND. With PWFM CLK pin high forward biased transistor Q10 supplies current to the tank from BAT1 charging capacitor C10 through NSME PFT1 and transferring energy into PFT1. Sub-circuit PWFM switches CLK low turning "off" Q10 stopping the current into PFT1. Energy not transferred into the load is released from NSME PFT1 into the now forward biased PNP transistor Q20 back into capacitor C10. Thus any energy not used by the secondary loads is transferred back to the primary tank to be used next cycle. When the switching occurs at the resonant frequency large circulating currents develop in the tank. Also C10 is charged and discharged to very large voltages. Oscillograph in FIG. 35 is the actual voltage developed across capacitor C10 with VBAT equal to 18 volts. A very large 229-Volts peak to peak was developed across the nodes P1A and P1A of NSME PFT1. The large primary voltage generates large biases in the NSME PFT1 to be flux harvested by the windings 102 and 103 (FIG. 18) and transferred to a load or rectifier sub-circuit OUTB. Magnetic element winding node S2L of sub-circuit PFT1 is connected to OUTB C8b. Magnetic element winding node S2H of sub-circuit PFT1 is connected to C8B of sub-circuit OUTB node OUT-. Node OUT- is connected to RLOAD, pin Band to sub-circuit IFB pin OUT-. Rectified power is delivered to pin OUT+ of OUTB and is connected to RLOAD, pin B+ and to sub-circuit IFB pin OUT+. Sub-circuit IFB provides the isolated feedback signal to the sub-circuit PWFM. Frequency control pin FM1 of sub-circuit PWFM is connected to sub-circuit IFB pin FBE. Internal reference pin REF of sub-circuit PWFM is connected to sub-circuit IFB pin FBC. PWFM is designed to operate at the resonate frequency of the tank. When sub-circuit IFB senses the converter output is at the designed voltage, current from REF is injected into FM1. Injecting current into FM1 commands PWFM to a lower frequency. Operating below resonance reduces the amount of energy added to the primary tank thus reducing the converter output voltage. In the event the feedback signal from IFB commands the PWFM to 0Hz all primary activity stops. Input current from VBAT is sinusoidal making the converter very quiet. In addition the switches Q10 and Q20 are never exposed to the large circulating voltage (FIG. 35). Placing less stress on the switches thereby increasing the MTBF. Sub-circuit TCTP takes advantage of the desirable properties of the NSME in this converter topology. Adjusting secondary turns allows TCTP to generate very large AC or DC output voltages as well as low-voltage high current outputs.

[0105] FIG. 9 is a schematic for non-isolated low side switch boost converter sub-circuit NILSBST. Sub-circuit NILSBST consists of resistor R20 and RLOAD, diode D6, capacitor C6, FET transistor Q111, sub-circuit CP (FIG. 26), sub-circuit PFT1A (FIG. 18A), sub-circuit FBI (FIG. 41), sub-circuit AMP (FIG. 29) and sub-circuit PWFM (FIG. 33).

| FIG. 9  | Table             |

|---------|-------------------|

| Element | Value/part number |

| R20     | 100 k ohms        |

| Q111    | IRFP460           |

| D6      | STA1206 DI        |

| C6      | 200 uf            |

[0106] External power source VBAT connects to pins DCIN+ and DCIN- From DCIN+Resistor R20 connects to sub-circuit CP pin CP+, sub-circuit AMP pin GA+ and to sub-circuit PWFM pin PWFM+. Resistor R20 provides startup power to the converter before regulator sub-circuit CP reaches it full 18-volt output. VBAT negative is connected to pin DCIN- and ground return node GND. Node GND connects to sub-circuit PWFM pin PWFM0, sub-circuit AMP pin GA0, Q111 source, sub-circuit FBA pin

BR-, sub-circuit FBA pin FBA, sub-circuit CP pin CT0, capacitor C6, resistor RLOAD, transistor Q111 source, and sub-circuit PFT1 pin S1CT. Magnetic element winding node S1H of sub-circuit PFT1A is connected to CP pin CT1A Magnetic element winding node S1CT of sub-circuit PFT1 is connected to CP pin CT0. Magnetic element winding node S2H of sub-circuit PFT1 A is connected to CP pin CT2A. The regulated 18 volts from sub-circuit CP+ is connected to R20, sub-circuit AMP pin GA+ and to subcircuit PWFM pin PWFM+. Sub-circuit PWFM is designed for variable pulse width operation. PWFM is configured for maximum pulse width 90-95% (maximum boost voltage) with no feedback current from sub-circuit FBI. Increasing the feedback current reduces the pulse-width reducing the boost voltage and reducing the output from converter NILSBST. Sub-circuit PWFM clock/PWM output pin CLK is connected to the input pin GA1 of buffer sub-circuit AMP. The output of sub-circuit AMP pin GA2 is connected to the gate of Q111. Input node DCIN+ connects to the NSME PFT1A pin P1A. The drain of Q11 is connected to subcircuit PFT1A pin P1B and the anode of D6. Cathode of diode D6 is connected to sub-circuit FBA pin PF+, resistor RLOAD, C6 and pin BK+. With sub-circuit PWFM pin CLK high buffer AMP output pin GA2 charges the gate of transistor switch Q111. Switch Q111 conducts reverse biasing diode D6 capacitor C10 stops charging through NSME PFT1A from source VBAT. During the time Q111 is conducting, energy is stored in NSME sub-circuit PFT1A. Feedback output pin FBC from sub-circuit FBI is connected to sub-circuit PWFM pulse-width adjustment pin PW1 Subcircuit FBI removes current from PW1 commanding PWFM to reduce the pulse-width or on time of signal CLK. After sub-circuit PWFM reaches the commanded pulse-width PFFM switches CLK low turning "off" Q111 stopping the current into PFT1A. The energy not transferred into regulator sub-circuit CP load is released from NSME PFT1 A into the now forward biased diode D6 charging capacitor C6. By modulating the "on" time of switch Q111 the converter boost voltage is regulated. Regulated voltage is developed across Nodes B- and B+. Sub-circuit IFB provides the feedback current to the sub-circuit PWFM. When sub-circuit IFB senses the converter output (nodes B+ and B-) is at or greater than the designed voltage, current is removed from PM1. Sinking current from PM1 commands the PWFM to a shorter pulse-width thus reducing the converter output voltage. In the event the feedback signal from IFB commands the PWFM to minimum output. Gate drive to switch Q111 is removed stopping all boost activity capacitor C6 charges to VBAT. Input current from VBAT is sinusoidal making the converter very quiet. In addition the switch Q111 is not exposed to large flyback voltage. Placing less stress on the switches thereby increasing the MTBF. Sub-circuit NILBK takes advantage of the desirable properties of the NSME in this converter topology. Adjusting the NSME 100 (FIG. 18A) primary inductance and component values in sub-circuit IFB determines the output boost volt-

[0107] FIG. 10 is a schematic for a two stage isolated DC to DC boost controlled push-pull converter BSTPP. Subcircuit BSTPP consists of diode D14, capacitor C14, FET transistor Q1 4, sub-circuit REG (FIG. 36), sub-circuit BL1 (FIG. 18B), sub-circuit IFB (FIG. 40B), sub-circuit AMP (FIG. 29), sub-circuit DCAC1 and sub-circuit PWFM (FIG. 33). External power source VBAT connects to pins DCIN+ and DCIN-.

| FIG. 10<br>Element | Table<br>Value/part number     |  |

|--------------------|--------------------------------|--|

| Q31<br>D14<br>C14  | IRFP460<br>STA1206 DI<br>10 uf |  |

[0108] From pin DCIN+ connects to sub-circuit REG pin RIN+ and sub-circuit BL1 pin P1A. Voltage regulator subcircuit output pin +18V connects to sub-circuit AMP pin GA+ and to sub-circuit PWFM pin PWFM+. Sub-circuit REG provides regulated low voltage power to the controller and to the main switch buffers. VBAT negative is connected to pin DCIN- and ground return node GND. Node GND connects to sub-circuit PWFM pin PWFM0, sub-circuit AMP pin GA0, Q14 source, capacitor C14, sub-circuit IFB pin FBE, sub-circuit REG pin REGO, sub-circuit DCAC1 pin DC-. Sub-circuit PWFM (FIG. 33) is designed for variable pulse width operation. The nominal frequency is between 20-600 Khz PWFM is configured for maximum pulse width 90% (maximum boost voltage) with no feedback current from sub-circuit FBI. Increasing the feedback current reduces the pulse-width reducing the boost voltage and reducing the output from converter BSTPP. Sub-circuit PWFM clock/PWM output pin CLK is connected to the input pin GA1 of buffer sub-circuit AMP (FIG. 29). The output of switch speed up buffer sub-circuit AMP pin GA2 is connected to the gate of Q14. Input node DCIN+ connects to the NSME BL1 pin P1A. The drain of Q14 is connected to sub-circuit BL1 pin P1B and the anode of D14. Cathode of flyback diode D14 is connected to sub-circuit DCAC1 pin DC+ and C14. With sub-circuit PWFM pin CLK high buffer AMP output pin GA2 charges the gate of transistor switch Q14. Switch Q14 conducts reverse biasing diode D14 capacitor C14 stops charging through NSME BL1 from source VBAT. During the time Q14 is conducting, energy is stored in NSME sub-circuit BL1. Feedback output pin FBC from sub-circuit IFB is connected to sub-circuit PWFM pulse-width adjustment pin PW1 Sub-circuit IFB removes current from PW1 commanding PWFM to reduce the pulsewidth or "on" time of signal CLK. After sub-circuit PWFM reaches the commanded pulse-width PFFM switches CLK low turning "off" Q14 stopping the current into BL1. The energy is released from NSME BL1 into the now forward biased flyback diode D14 charging capacitor C14. By modulating the "on" time of switch Q14 the converter boost voltage is regulated. Regulated voltage is developed across C14 Nodes DC+ and GND is provided to the isolated constant frequency push-pull DC to AC converter subcircuit DCAC1 (FIG. 2). Sub-circuit DCAC1 provides efficient conversion of the regulated boost voltage to a higher or lower voltage set by the magnetic element-winding ratio. The center tap of the push-pull output magnetic is connected to, sub-circuit OUTB pin OUT-, RLOAD, subcircuit IFB pin OUT- and the pin OUT- forming the return line for the load and feedback network. Output of sub-circuit DCAC1 pin ACH is connected to sub-circuit OUTB pin C7b. Output of sub-circuit DCAC1 pin ACL is connected to sub-circuit OUTB pin C8b. Sub-circuit OUTB provides rectification of the AC power generated by sub-circuit DCAC1. Since the non-saturating magnetic converter has low output ripple, minimal filtering is required by OUTB.

This further reduces cost and improves efficiency as losses to filter components are minimized. Sub-circuit IFB provides the isolated feedback current to the sub-circuit PWFM. When sub-circuit IFB senses the converter output (nodes OUT+ and OUT-) is greater than the designed/desired voltage, current is removed from node PM1 Sinking current from PM1 commands the PWFM to a shorter pulse-width thus reducing the converter output voltage. In the event the feedback signal from IFB commands the PWFM to minimum output. Gate drive to switch Q14 is removed stopping all boost activity capacitor C14 charges to VBAT. As the non-saturating does not saturate the destructive noisy current "spikes" common to prior art are absent. Input current from VBAT to charge C14 is sinusoidal making the converter very quiet. In addition the switch Q14 is not exposed a potentially destructive current spike. Placing less stress on the switches thereby increasing the MTBF. Sub-circuit BSTPP takes advantage of the desirable properties of the NSME. Adjusting the NSME BL1 (FIG. 18B) sets the amount of boost voltage available to the final push-pull isolation stage. Greater efficiencies are achieved at higher voltages. The final output voltage is set by the feedback set point and the turns ratio of the push-pull element PPT1 (FIG. 19). FIG. 11 is a graph of permeability as a function of temperature for typical prior art magnetic element material. The high permeability material in FIG. 11 exhibits large changes in permeability of almost 100% over a 100C range as compared to the less than 5% change for the material in FIG. 17. The increase in permeability at high temperatures of the prior art material increases the flux density resulting in core saturation for a constant power level. (See FIG. 12) Thus the prior art core must be derated at least 100% to operate over extended temperatures. The instant invention takes advantage of the desirable properties of the NSME. Eliminating the need to derate the magnetic element. As the magnetic element performs better at high temperatures, currently limited by melting wire insulation.