(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2019-12753

(P2019-12753A)

(43) 公開日 平成31年1月24日(2019.1.24)

| (51) Int.Cl.         | F I              |        |       | テーマコード (参考) |         |

|----------------------|------------------|--------|-------|-------------|---------|

| <b>HO 1 L 21/822</b> | <b>(2006.01)</b> | HO 1 L | 27/04 | H           | 5 F 038 |

| <b>HO 1 L 27/04</b>  | <b>(2006.01)</b> | HO 1 L | 27/06 | 3 1 1 A     | 5 F 048 |

| <b>HO 1 L 27/06</b>  | <b>(2006.01)</b> | HO 1 L | 27/06 | 3 1 1 B     |         |

審査請求 未請求 請求項の数 10 O.L. (全 25 頁)

|           |                              |          |                  |

|-----------|------------------------------|----------|------------------|

| (21) 出願番号 | 特願2017-127992 (P2017-127992) | (71) 出願人 | 000003078        |

| (22) 出願日  | 平成29年6月29日 (2017. 6. 29)     |          | 株式会社東芝           |

|           |                              |          | 東京都港区芝浦一丁目1番1号   |

|           |                              | (71) 出願人 | 317011920        |

|           |                              |          | 東芝デバイス＆ストレージ株式会社 |

|           |                              |          | 東京都港区芝浦一丁目1番1号   |

|           |                              | (74) 代理人 | 100108855        |

|           |                              |          | 弁理士 蔵田 昌俊        |

|           |                              | (74) 代理人 | 100103034        |

|           |                              |          | 弁理士 野河 信久        |

|           |                              | (74) 代理人 | 100075672        |

|           |                              |          | 弁理士 峰 隆司         |

|           |                              | (74) 代理人 | 100153051        |

|           |                              |          | 弁理士 河野 直樹        |

最終頁に続く

(54) 【発明の名称】 電源保護回路

(57) 【要約】

### 【課題】電源保護回路に流れるリーク電流を低減させる

1

【解決手段】一実施形態の電源保護回路は第1電圧が供給される第1パッド、第1電圧と異なる第2電圧が供給される第2パッド、第1及び第2トランジスタ、並びにスイッチ回路を備える。第1トランジスタは第1パッドに電気的に接続された第1端と、第1ノードに電気的に接続された第2端及びバックゲートと、第2ノードに電気的に接続されたゲートと、を含む。第2トランジスタは第1ノードに電気的に接続された第1端と、第2パッドに電気的に接続された第2端及びバックゲートと、を含む。スイッチ回路は第2トランジスタのゲートに第1論理信号が入力される場合、第2ノードを第1パッドと電気的に接続し、第2トランジスタのゲートに第1論理信号と互いに反転した論理レベルを有する第2論理信号が入力される場合、第2ノードを第1パッドから電気的に切断して前記第1ノードと電気的に接続する。

### 【選択図】図 2

## 【特許請求の範囲】

## 【請求項 1】

第1電圧が供給される第1パッドと、

前記第1電圧と異なる第2電圧が供給される第2パッドと、

前記第1パッドに電気的に接続された第1端と、第1ノードに電気的に接続された第2端及びバックゲートと、第2ノードに電気的に接続されたゲートと、を含む第1トランジスタと、

前記第1ノードに電気的に接続された第1端と、前記第2パッドに電気的に接続された第2端及びバックゲートと、を含む第2トランジスタと、

前記第2トランジスタのゲートに第1論理信号が入力される場合、前記第2ノードを前記第1パッドと電気的に接続し、前記第2トランジスタのゲートに前記第1論理信号と互いに反転した論理レベルを有する第2論理信号が入力される場合、前記第2ノードを前記第1パッドから電気的に切断して前記第1ノードと電気的に接続するスイッチ回路と、

を備える、電源保護回路。

## 【請求項 2】

前記スイッチ回路は、前記第1パッドに電気的に接続された第1端と、前記第2ノードに電気的に接続された第2端と、を含み、前記第1トランジスタ及び前記第2トランジスタと互いに異なる極性を有する第3トランジスタを含む、請求項1記載の電源保護回路。

## 【請求項 3】

前記第3トランジスタのゲートには、前記第2トランジスタのゲートに入力される論理信号と互いに反転した論理信号が入力される、請求項2記載の電源保護回路。

## 【請求項 4】

前記スイッチ回路は、前記第1ノードに電気的に接続された第1端と、前記第2ノードに電気的に接続された第2端と、を含む第1抵抗を更に含む、請求項3記載の電源保護回路。

## 【請求項 5】

前記スイッチ回路は、前記第1ノードに電気的に接続された第1端と、前記第2ノードに電気的に接続された第2端と、前記第3トランジスタのゲートに電気的に接続されたゲートと、を含む第4トランジスタを更に含む、請求項3記載の電源保護回路。

## 【請求項 6】

前記第4トランジスタは、前記第3トランジスタと互いに異なる極性を有する、請求項5記載の電源保護回路。

## 【請求項 7】

前記第1パッドと前記第2パッドとの間に電気的に接続され、第3ノードにトリガ信号を出力するトリガ回路と、

前記トリガ信号の電圧値が或る閾値を超えたか否かに応じて、前記第2トランジスタのゲート及び前記第3トランジスタのゲートへ入力される論理信号の論理レベルを切り替える信号制御回路と、

を更に備える、請求項2記載の電源保護回路。

## 【請求項 8】

前記トリガ回路は、

前記第1パッドに電気的に接続された第1端と、前記第3ノードに電気的に接続された第2端と、を含む第2抵抗と、

前記第3ノードに電気的に接続された第1端と、前記第2パッドに電気的に接続された第2端と、を含むキャパシタと、

を含む、請求項7記載の電源保護回路。

## 【請求項 9】

前記トリガ回路は、

前記第1パッドに電気的に接続された第1端と、前記第3ノードに電気的に接続された第2端と、を含む第2抵抗と、

10

20

30

40

50

前記第3ノードに電気的に接続された第1端と、前記第2パッドに電気的に接続された第2端及びゲートと、を含む第5トランジスタと、

を含む、請求項7記載の電源保護回路。

【請求項10】

前記トリガ回路は、

前記第1パッドに電気的に接続された第1端と、前記第3ノードに電気的に接続された第2端と、を含む第2抵抗と、

前記第3ノードに電気的に接続された第1端と、前記第2パッドに電気的に接続された第2端と、を含むダイオードと、

を含む、請求項7記載の電源保護回路。

10

【発明の詳細な説明】

【技術分野】

【0001】

実施形態は、電源保護回路に関する。

【背景技術】

【0002】

半導体装置の電源をサージから保護する電源保護回路が知られている。

【先行技術文献】

【特許文献】

【0003】

20

【特許文献1】特開2014-75435号公報

【特許文献2】特開2015-103689号公報

【特許文献3】特表2016-35958号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

電源保護回路に流れるリーク電流を低減させる。

【課題を解決するための手段】

【0005】

実施形態の電源保護回路は、第1パッドと、第2パッドと、第1トランジスタと、第2トランジスタと、スイッチ回路と、を備える。上記第1パッドは、第1電圧が供給される。上記第2パッドは、上記第1電圧と異なる第2電圧が供給される。上記第1トランジスタは、上記第1パッドに電気的に接続された第1端と、第1ノードに電気的に接続された第2端及びバックゲートと、第2ノードに電気的に接続されたゲートと、を含む。上記第2トランジスタは、上記第1ノードに電気的に接続された第1端と、上記第2パッドに電気的に接続された第2端及びバックゲートと、を含む。上記スイッチ回路は、上記第2トランジスタのゲートに第1論理信号が入力される場合、上記第2ノードを上記第1パッドと電気的に接続し、上記第2トランジスタのゲートに上記第1論理信号と互いに反転した論理レベルを有する第2論理信号が入力される場合、上記第2ノードを上記第1パッドから電気的に切断して上記第1ノードと電気的に接続する。

30

【図面の簡単な説明】

【0006】

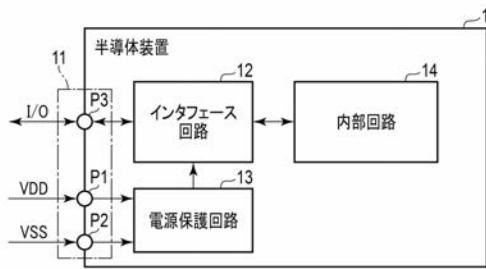

【図1】第1実施形態に係る半導体装置の構成を説明するためのブロック図。

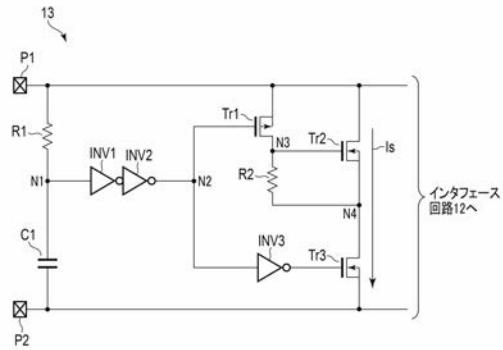

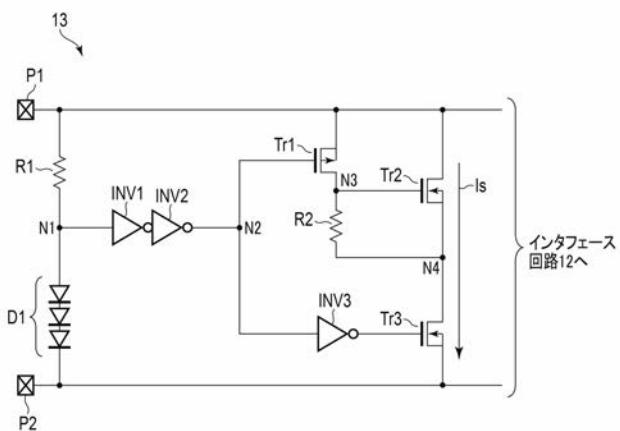

【図2】第1実施形態に係る半導体装置の電源保護回路の構成を説明するための回路図。

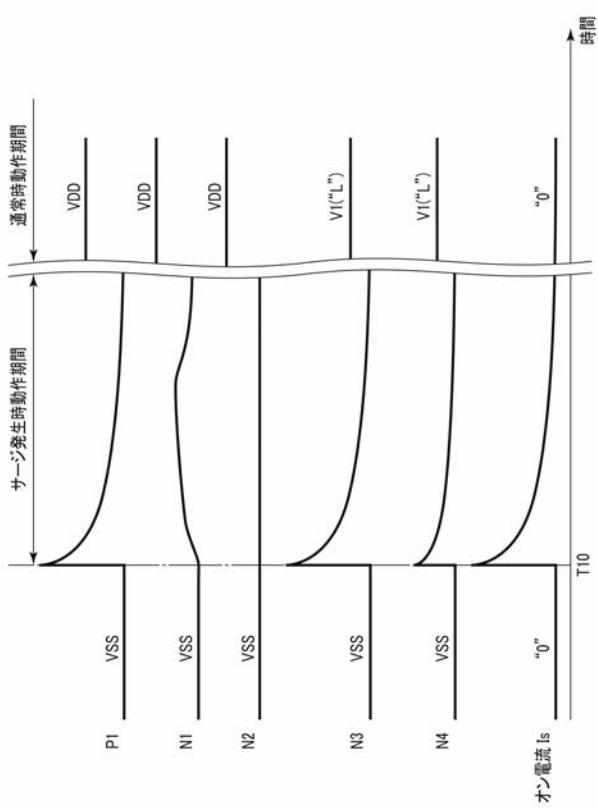

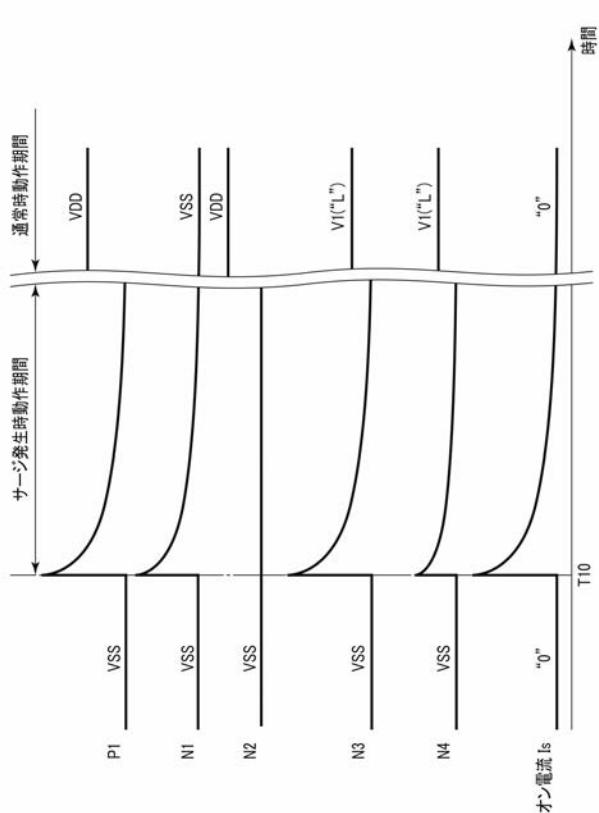

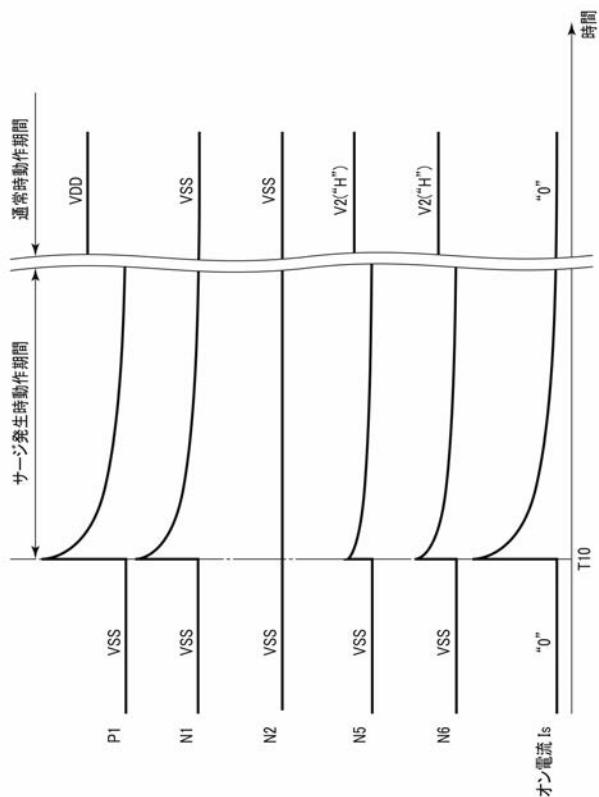

【図3】第1実施形態に係る半導体装置の電源保護回路の動作を説明するためのタイミングチャート。

40

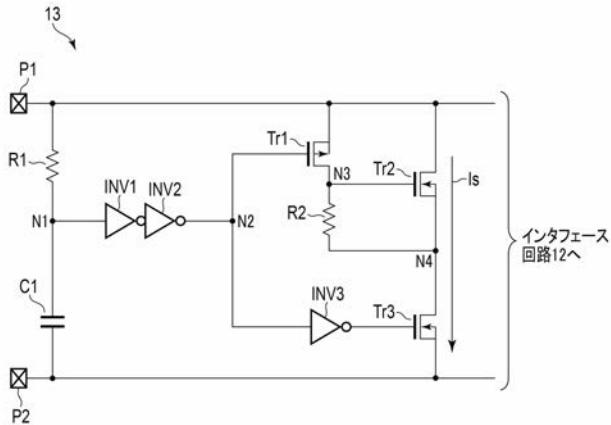

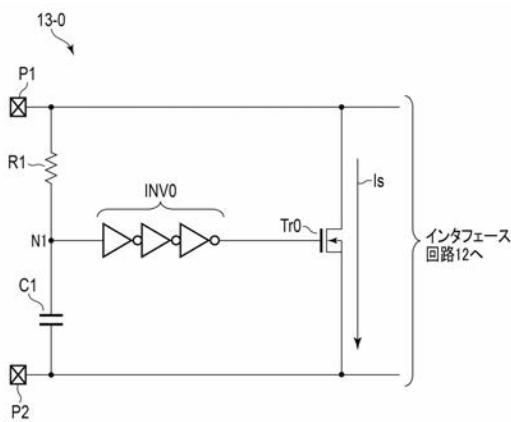

【図4】比較例に係る半導体装置の電源保護回路の構成を説明するための回路図。

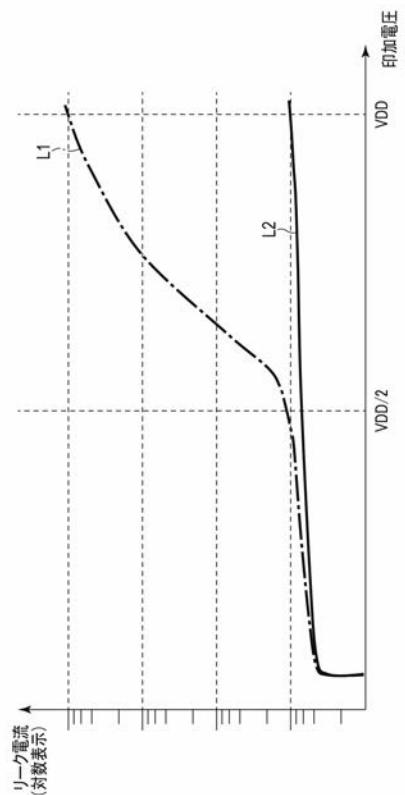

【図5】第1実施形態に係る効果を説明するためのダイアグラム。

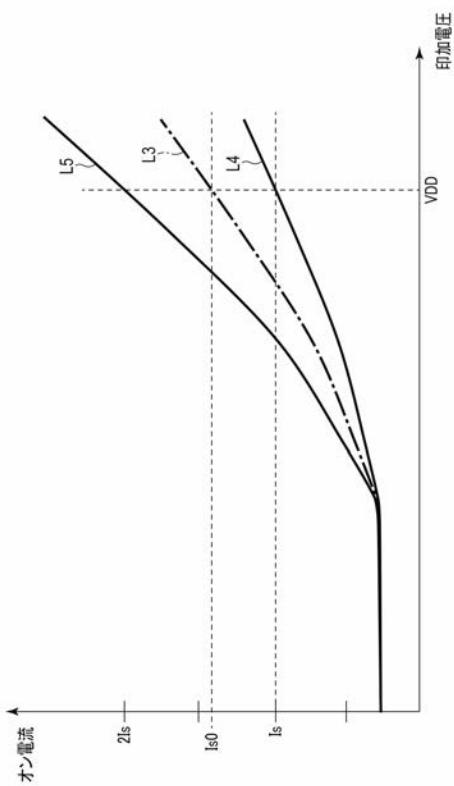

【図6】第1実施形態に係る効果を説明するためのダイアグラム。

【図7】第1実施形態の第1変形例に係る半導体装置の電源保護回路の構成を説明するた

50

めの回路図。

【図 8】第 1 実施形態の第 2 変形例に係る半導体装置の電源保護回路の構成を説明するための回路図。

【図 9】第 1 実施形態の第 2 変形例に係る半導体装置の電源保護回路の構成を説明するための回路図。

【図 10】第 1 実施形態の第 2 変形例に係る半導体装置の電源保護回路の構成を説明するための回路図。

【図 11】第 1 実施形態の第 3 変形例に係る半導体装置の電源保護回路の構成を説明するための回路図。

【図 12】第 1 実施形態の第 3 変形例に係る半導体装置の電源保護回路の動作を説明するためのタイミングチャート。 10

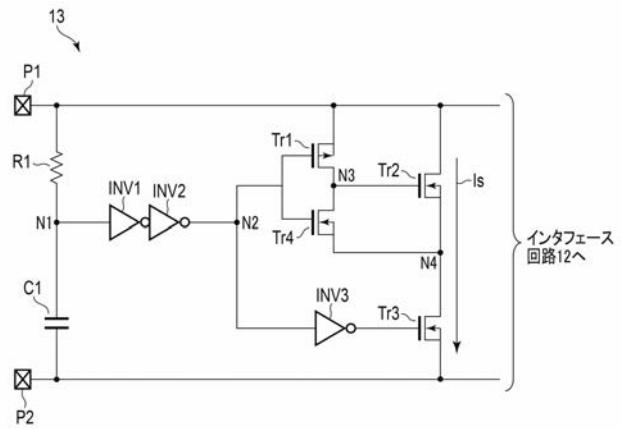

【図 13】第 2 実施形態に係る半導体装置の電源保護回路の構成を説明するための回路図。

【図 14】第 2 実施形態に係る半導体装置の電源保護回路の動作を説明するためのタイミングチャート。

【図 15】第 2 実施形態の第 1 変形例に係る半導体装置の電源保護回路の構成を説明するための回路図。

【図 16】第 2 実施形態の第 2 変形例に係る半導体装置の電源保護回路の構成を説明するための回路図。

【図 17】第 2 実施形態の第 2 変形例に係る半導体装置の電源保護回路の構成を説明するための回路図。 20

【図 18】第 2 実施形態の第 2 変形例に係る半導体装置の電源保護回路の構成を説明するための回路図。

【図 19】第 2 実施形態の第 3 変形例に係る半導体装置の電源保護回路の構成を説明するための回路図。

【図 20】第 2 実施形態の第 3 変形例に係る半導体装置の電源保護回路の動作を説明するためのタイミングチャート。

【発明を実施するための形態】

【0007】

以下、図面を参照して実施形態について説明する。なお、以下の説明において、同一の機能及び構成を有する構成要素については、共通する参照符号を付す。 30

【0008】

1. 第 1 実施形態

第 1 実施形態に係る電源保護回路について説明する。

【0009】

1.1 構成について

まず、第 1 実施形態に係る電源保護回路を含む半導体装置の構成について説明する。

【0010】

1.1.1 半導体装置の構成について

図 1 は、第 1 実施形態に係る半導体装置の構成の一例を示すブロック図である。半導体装置 1 は、例えば、図示しない外部機器からの入力信号に対して所定の処理を実行し、出力信号を出力する半導体チップを含む。 40

【0011】

半導体装置 1 は、例えば、外部機器と信号 I/O を通信する。信号 I/O は、半導体装置 1 と外部機器との間で送受信されるデータの実体であり、入力信号及び出力信号を含む。

【0012】

また、半導体装置 1 には、種々の電圧が供給される。半導体装置 1 に供給される電圧は、例えば、電圧 VDD 及び VSS を含む。電圧 VDD は、半導体装置 1 を駆動するために用いられる基準電圧であり、例えば、1.8V である。電圧 VSS は、接地電圧で

あり、電圧 V D D より小さい。電圧 V S S は、例えば、0 V である。

【0013】

半導体装置 1 は、パッド群 1 1、インターフェース回路 1 2、電源保護回路 1 3、及び内部回路 1 4 を備えている。

【0014】

パッド群 1 1 は、電圧供給用のパッド P 1 及び P 2 を含む。パッド P 1 及び P 2 はそれぞれ、電圧 V D D 及び V S S を電源保護回路 1 3 と共有する。なお、図 1 の例では、パッド P 1 及び P 2 の各々は、1 個の機能ブロックとして示されているが、これに限らず、複数個設けられてもよい。パッド P 1 及び P 2 の各々が 1 つのチップ内に複数個設けられている場合、当該複数のパッド P 1 及び P 2 は、チップ内の複数の場所に分散してレイアウトされていてもよい。

10

【0015】

また、パッド群 1 1 は、例えば、信号送受信用のパッド P 3 を含む。パッド P 3 は、外部機器から受信した入力信号をインターフェース回路 1 2 に転送する。また、パッド P 3 は、インターフェース回路 1 2 から受信した信号を出力信号として半導体装置 1 0 の外部に出力する。

【0016】

インターフェース回路 1 2 は、パッド P 3 から入力信号を信号 I / O として受けると、当該入力信号を内部回路 1 4 に送信する。また、インターフェース回路 1 2 は、内部回路 1 4 から出力信号を受けると、パッド P 3 を介して当該出力信号を外部に出力する。

20

【0017】

電源保護回路 1 3 は、電圧 V D D をインターフェース回路 1 2 と共有する。電源保護回路 1 3 は、例えば、電圧 V D D 及び V S S に基づき、電圧 V D D にサージが発生した場合、当該サージによる影響を低減させた電圧 V D D をインターフェース回路 1 2 と共有する機能を有する。電源保護回路 1 3 の詳細については後述する。なお、電源保護回路 1 3 は、例えば、パッド P 1 及び P 2 の各々が複数個設けられている場合、当該複数のパッド P 1 及び P 2 のチップ内におけるレイアウトに対応付けられて複数個設けられる。

【0018】

内部回路 1 4 は、半導体装置 1 の具体的な処理を行う機能構成を有する回路である。内部回路 1 4 は、インターフェース回路 1 2 から信号を受けると、所定の処理を実行し、当該所定の処理の結果として出力信号を生成する。

30

【0019】

1.1.2 電源保護回路の構成について

次に、第 1 実施形態に係る半導体装置の電源保護回路の構成について、図 2 を用いて説明する。

【0020】

図 2 に示すように、電源保護回路 1 3 は、トランジスタ Tr 1、Tr 2、及び Tr 3、抵抗 R 1 及び R 2、キャパシタ C 1、並びにインバータ INV 1、INV 2、及び INV 3 を含む。トランジスタ Tr 1 は、例えば、p チャネルの極性を有する MOS (Metal Oxide Semiconductor) トランジスタである。トランジスタ Tr 2、及び Tr 3 は、例えば、n チャネルの極性を有する MOS トランジスタである。トランジスタ Tr 1 ~ Tr 3、抵抗 R 1 及び R 2、キャパシタ C 1、並びにインバータ INV 1 ~ INV 3 は、RCT (Resistance Capacitor Triggered) MOS 回路として機能し得る。

40

【0021】

上述の通り、電源保護回路 1 3 には、パッド P 1 及び P 2 を介してそれぞれ電圧 V D D 及び V S S が供給される。

【0022】

抵抗 R 1 は、第 1 端がパッド P 1 に接続され、第 2 端がノード N 1 に接続される。キャパシタ C 1 は、第 1 端がノード N 1 に接続され、第 2 端がパッド P 2 に接続される。抵抗 R 1 及びキャパシタ C 1 は、各々の抵抗値及び容量に基づいて決定される時定数に基づい

50

て動作するRCタイマとして機能する。具体的には、ノードN1の電圧は、パッドP1の電圧変動に対して、当該時定数に基づく時間的な遅れを伴って追従する。

【0023】

インバータINV1及びINV2は、ノードN1及びN2の間ににおいて直列に接続される。具体的には、インバータINV1は、入力端がノードN1に接続され、出力端がインバータINV2の入力端に接続される。インバータINV2は、出力端がノードN2に接続される。

【0024】

インバータINV3は、入力端がノードN2に接続され、出力端がトランジスタTr3のゲートに接続される。

10

【0025】

インバータINV1～INV3は、例えば、パッドP1及びP2の電位差に応じた値の信号を出力するよう構成されてもよい。

【0026】

トランジスタTr1は、第1端及びバックゲートがパッドP1に接続され、第2端がノードN3に接続され、ゲートがノードN2に接続される。すなわち、トランジスタTr1の第1端及び第2端はそれぞれ、ソース及びドレインとして機能する。なお、バックゲートは、「ボディ」とも言う。

【0027】

抵抗R2は、第1端がノードN3に接続され、第2端がノードN4に接続される。

20

【0028】

トランジスタTr2は、第1端がパッドP1に接続され、第2端及びバックゲートがノードN4に接続され、ゲートがノードN3に接続される。トランジスタTr3は、第1端がノードN4に接続され、第2端及びバックゲートがパッドP2に接続され、ゲートがインバータINV3の出力端に接続される。すなわち、トランジスタTr2の第1端及びトランジスタTr3の第1端はドレインとして機能し、トランジスタTr2の第2端及びトランジスタTr3の第2端はソースとして機能する。

【0029】

トランジスタTr2及びTr3は、パッドP1の電圧が急峻に立ち上った際にオン状態となって第1端から第2端に向けてオン電流Isを流し、当該パッドP1の電圧の急激な変化に対するインターフェース回路12への影響を緩和させる機能を有する。なお、トランジスタTr2及びTr3は、互いに同程度の大きさのゲートサイズを有することが好ましい。ゲートサイズとは、例えば、ゲート長Lに対するゲート幅Wの割合(W/L)である。トランジスタTr2及びTr3のゲートサイズは、他のトランジスタTr1のゲートサイズより大きい。

30

【0030】

なお、トランジスタTr1～Tr3は、例えば、電圧VDDと、電圧VSSとの間の或る電圧(便宜的に、電圧VTと言う。)において、オン状態又はオフ状態に切り替わることが好ましい。より好ましくは、電圧VTは、電圧VDDと、電圧VDD/2との間に設定されることが好ましい。トランジスタTr1は、電圧VTより低い電圧がゲートに印加されると、オン状態となり、電圧VTより高い電圧がゲートに印加されると、オフ状態となる。また、トランジスタTr2及びTr3は、電圧VTより低い電圧がゲートに印加されると、オフ状態となり、電圧VTより高い電圧がゲートに印加されると、オン状態となる。このように、pチャネルの極性を有するトランジスタと、nチャネルの極性を有するトランジスタは、一方がオン状態の場合は他方がオフ状態となり、一方がオフ状態の場合は他方がオン状態となることが好ましい。

40

【0031】

以下の説明では、トランジスタTr1～Tr3のゲートに印加される電圧について、電圧VTよりも低い電圧の論理レベルを“L”レベルと言い、電圧VTよりも高い電圧を“H”レベルと言う。

50

## 【0032】

なお、インバータIN V1～IN V3は、トランジスタTr1～Tr3と同様、入力端に入力される電圧が電圧VTより小さいか大きいかに応じて、出力端から出力される信号の論理レベルが切り替わるよう構成されてもよい。より具体的には、インバータIN V1～IN V3は、“L”レベルが入力端に入力されると、出力端から“H”レベルを出力し、“H”レベルが入力端に入力されると、出力端から“L”レベルを出力してもよい。このように構成することにより、インバータIN V1～IN V3は、例えば、ノードN1の電圧値が電圧VTを超えたか否かに応じてトランジスタTr2及びTr3へのゲートへ入力される信号の論理レベルを切り替える信号制御回路として機能する。

## 【0033】

10

## 1.2 電源保護回路の動作について

次に、第1実施形態に係る半導体装置の電源保護回路の動作について説明する。

## 【0034】

図3は、第1実施形態に係る電源保護回路の動作を説明するためのタイミングチャートである。図3は、一例として、サージが発生した際と、定常的に電源が供給されている際における、電源保護回路13の動作を模式的に示している。図3では、サージの一例として、HBM(Human Body Model)に基づくサージが発生した場合が示される。なお、以下の説明では、サージが発生した際ににおける電源保護回路13の動作を示す期間を「サージ発生時動作期間」、定常的に電源が供給されている際ににおける電源保護回路13の動作を示す期間を「通常時動作期間」としてそれぞれ示している。

20

## 【0035】

図3に示すように、時刻T10に至るまで、半導体装置10には電圧VDDが供給されていない。このため、パッドP1及びP2は、例えば電圧VSSとなる。これに伴い、ノードN1、N2、N3、及びN4は、いずれも電圧VSS(“L”レベル)となる。これに伴い、トランジスタTr2及びTr3はオフ状態となり、オン電流Isは流れない。

## 【0036】

30

時刻T10において、サージが発生することにより、パッドP1の電圧は急峻に立ち上がり、徐々に電圧VSSに近づいていく。ノードN1は、サージに応じてキャパシタC1の電荷が充電されるため電圧が緩やかに上昇するものの、パッドP1の電圧の減少に伴って再度減少する。このため、ノードN1はサージ発生時動作期間にわたって“L”レベルのままである。

## 【0037】

これに伴い、インバータIN V1は“H”レベルを出力する。インバータIN V1から出力された“H”レベルは、インバータIN V2に入力される。これにより、インバータIN V2はノードN2に“L”レベルを出力する。このため、インバータIN V2から出力された“L”レベルがトランジスタTr1のゲート及びインバータIN V3の入力端に入力される。

## 【0038】

40

インバータIN V3は、“L”レベルが入力されたことによって“H”レベルを出力する。インバータIN V3から出力された“H”レベルは、トランジスタTr3のゲートに入力され、トランジスタTr3をオン状態にする。

## 【0039】

また、トランジスタTr1は、“L”レベルが入力されたことによってオン状態となり、ノードN3の電圧は、パッドP1と電気的に接続されることにより、パッドP1と同様に推移し、“H”レベルとなる。このため、トランジスタTr2は、オン状態となる。

## 【0040】

50

このように、抵抗R1及びキャパシタC1は、サージの発生をトリガとしてトランジスタTr2及びTr3をオン状態とするトリガ回路として機能する。サージ発生時動作期間にわたってトランジスタTr2及びTr3がいずれもオン状態となることにより、トランジスタTr2及びTr3を電流経路として、パッドP1からパッドP2に向けてオン電流

$I_s$  が流れる。

【0041】

以上のように動作することにより、電源保護回路13は、サージ発生動作期間においてオン電流 $I_s$ を流した後、停止する。

【0042】

一方、通常時動作期間において、ノードN1は、キャパシタC1が十分に充電されたことに伴い、電圧VDDに達する。すなわち、ノードN1は、“H”レベルとなる。

【0043】

ノードN1が“H”レベルとなると、インバータINV1は“L”レベルを出力する。インバータINV1から出力された“L”レベルは、インバータINV2に入力される。これにより、インバータINV2はノードN2に“H”レベルを出力する。このため、インバータINV2から出力された“H”レベルがトランジスタTr1のゲート及びインバータINV3の入力端に入力される。

【0044】

インバータINV3は、“H”レベルが入力されたことによって“L”レベルを出力する。インバータINV3から出力された“L”レベルは、トランジスタTr3のゲートに入力され、トランジスタTr3をオフ状態にする。

【0045】

また、トランジスタTr1は、“H”レベルが入力されたことによってオフ状態となる。これにより、ノードN3は、パッドP1から電気的に切断されるが、抵抗R2を介してノードN4と接続されたままである。このとき、ノードN3及びN4の電圧は、電圧V1となる。電圧V1は、電圧VDD及びVSSの間の大きさであり、例えば、電圧VTより小さい（“L”レベルである）。電圧V1は、トランジスタTr2及びTr3のゲートサイズが同等の場合、例えば、VDD/2程度となる。このため、トランジスタTr2は、オフ状態となる。

【0046】

以上のように動作することにより、電源保護回路13は、通常時動作期間において、トランジスタTr2及びTr3がいずれもオフ状態となることにより、オン電流 $I_s$ を流さない。また、ノードN3及びN4の電圧は、電圧V1に維持される。

【0047】

1.3 本実施形態に係る効果

第1実施形態によれば、電源保護回路に流れるリーク電流を低減させることが出来る。本効果につき、以下説明する。

【0048】

静電気放電（ESD：Electrostatic Discharge）によるサージが発生した際、当該サージが内部回路に印加されることを防止するため、RCTMOS回路を電源保護回路に用いる手法が提案されている。

【0049】

RCTMOS回路は、サージが発生した際に電源及びグラウンド間を強制的にショートさせる必要があるため、大型のゲートサイズを有するトランジスタが用いられる。このため、当該トランジスタに発生するリーク電流は、そのゲートサイズに応じて大きくなり得る。リーク電流を引き起こす要因のうちの支配的なものとしては、例えば、ゲートリーク、及びGIDL（Gate Induced Drain Leakage）がある。ゲートリークは、主に、トランジスタのゲート及びドレイン間の電位差に応じて発生する。GIDLは、主に、トランジスタのバックゲート及びドレイン間の電位差、並びにゲート及びドレイン間の電位差に応じて発生する。これらのリーク電流は、ドレイン及びソース間の電位差に応じて指数関数的に増加することが知られている。

【0050】

第1実施形態によれば、トランジスタTr1は、第1端がパッドP1に接続され、第2端がノードN3に接続され、ゲートがノードN2に接続される。ノードN2は、ノードN

10

20

30

40

50

1が“L”レベルの際、“L”レベルとなり、“H”レベルの際、“H”レベルとなる。つまり、トランジスタTr1は、ノードN1が“L”レベルの際、ゲートに“L”レベルが入力されることにより、オン状態となる。これにより、サージ発生時動作期間において、パッドP1にノードN3を電気的に接続する。このため、トランジスタTr2のゲートに“H”レベルが入力され、トランジスタTr2をオン状態にすることができます。一方、ノードN1が“H”レベルの際、トランジスタTr1のゲートには“H”レベルが入力されることにより、オフ状態となる。これにより、通常時動作期間において、ノードN3は、パッドP1から電気的に切断される。このため、トランジスタTr2のゲートに“L”レベルが入力され、トランジスタTr2をオフ状態にすることができます。

## 【0051】

10

また、抵抗R2は、ノードN3とノードN4とを電気的に接続する。これにより、通常時動作期間において、ノードN3の電圧がノードN4の電圧に維持される。ノードN4は、トランジスタTr2及びTr3の中間ノードであるため、電圧VDD及び電圧VSSの中間電位である電圧V1となる。このため、トランジスタTr2のゲート及びバックゲートを、電圧V1にすることができます。

## 【0052】

また、インバータINV3は、ノードN2に接続された入力端と、トランジスタTr3のゲートに接続された出力端と、を含む。これにより、インバータINV3は、ノードN1が“L”レベルの際、“H”レベルを出力し、ノードN1が“H”レベルの際、“L”レベルを出力する。このため、サージ発生時動作期間において、トランジスタTr3をオン状態にすることができます、通常時動作期間において、トランジスタTr3をオフ状態にすることができます。

20

## 【0053】

上述の効果について、比較例を用いて具体的に説明する。

## 【0054】

図4は、比較例に係る電源保護回路の構成を説明するための回路図である。図4に示すように、比較例に係る電源保護回路13-0は、抵抗R1と、キャパシタC1と、直列に接続された複数のインバータINV0と、トランジスタTr0と、を含む。電源保護回路13-0は、第1実施形態に係る電源保護回路13から、トランジスタTr1及びTr2、並びに抵抗R2を除いた構成に相当する。より具体的には、トランジスタTr0は、パッドP1に接続された第1端と、パッドP2に接続された第2端と、複数のインバータINVの出力端に接続されたゲートと、を含む。

30

## 【0055】

上記の比較例に係る電源保護回路13-0の特性と、第1実施形態に係る電源保護回路13の特性との比較の様子について、図5及び図6を用いて以下に示す。

## 【0056】

図5及び図6は、第1実施形態の効果を説明するためのダイアグラムである。図5及び図6では、第1実施形態に係る電源保護回路13の特性と、比較例に係る電源保護回路13-0の特性とが、比較して示される。

40

## 【0057】

まず、図5に示される効果について説明する。図5では、パッドP1へ電圧VDDが定常に印加されている際（通常時動作期間）におけるリーク電流の大きさが対数表示される。つまり、図5では、電源保護回路にパッドP1及びパッドP2をショートするためのオン電流Isが流れていらない状態におけるリーク電流の大きさが示される。具体的には、図5では、電源保護回路13-0のリーク電流が曲線L1で示され、電源保護回路13のリーク電流が曲線L2で示される。

## 【0058】

図5に示すように、電源保護回路13におけるリーク電流は、電源保護回路13-0におけるリーク電流に対して低く抑えることができる。具体的には、パッドP1に供給される電圧が電圧VDDの場合、電源保護回路13は、電源保護回路13-0に対して、リー

50

ク電流の大きさを約1/1000に低減させることができる。また、電圧VDDが供給される場合の電源保護回路13のリーク電流の大きさは、電圧VDD/2が供給される場合の電源保護回路13-0におけるリーク電流の大きさと同等に抑えることができる。

#### 【0059】

これは、通常時動作期間において、トランジスタTr0のバックゲート及びドレイン間の電位差、並びにゲート及びドレイン間の電位差が電圧VDDであるのに対し、トランジスタTr2及びTr3のバックゲート及びドレイン間の電位差、並びにゲート及びドレイン間の電位差が電圧VDD/2程度に低減されるためである。

#### 【0060】

より具体的には、トランジスタTr2のゲートは、ノードN3に接続されることにより、トランジスタTr2のドレインに対する電位差が電圧VDD/2程度となる。トランジスタTr3のゲートは、INV3から“L”レベルが出力されることにより、ノードN4に対する電位差が電圧VDD/2より小さくなる。これにより、トランジスタTr2及びTr3のゲートとドレインとの間の電位差が低減され、ひいては、ゲートリークに起因するリーク電流が低減される。

#### 【0061】

また、トランジスタTr2のバックゲートは、ノードN4に接続されることにより、トランジスタTr2のドレインに対する電位差が電圧VDD/2程度となる。トランジスタTr3のバックゲートは、パッドP2に接続されることにより、ノードN4に対する電位差が電圧VDD/2程度となる。これにより、トランジスタTr2及びTr3のバックゲートとドレインとの間の電位差が低減され、ひいては、GIDLに起因するリーク電流が低減される。

#### 【0062】

なお、第1実施形態に係る電源保護回路13では、トランジスタTr2及びTr3のゲートサイズが同じとなるよう設計される。これにより、電圧V1は、電圧VDD/2と等しくなる。このため、トランジスタTr2及びTr3のバックゲート及びドレイン間の電位差、並びにゲート及びドレイン間の電位差が電圧VDD/2となり、リーク電流を最小化することができる。

#### 【0063】

次に、図6に示される効果について説明する。図6では、サージ発生時の動作が想定され、パッドP1へ供給される電圧VDDに対応するオン電流Isの大きさが示される。具体的には、図6では、電源保護回路13-0のオン電流が曲線L3で示され、電源保護回路13のリーク電流が曲線L4及びL5で示される。曲線L4では、トランジスタTr2及びTr3に、トランジスタTr0と同等の大きさのゲートサイズを適用した場合が示される。曲線L5では、トランジスタTr2及びTr3に、トランジスタTr0の2倍の大きさのゲートサイズを適用した場合が示される。

#### 【0064】

図6に示すように、ゲートサイズが同じ場合、電源保護回路13に流れるオン電流Isは、電源保護回路13-0に流れるオン電流Is0に対して、少なくなる。これは、トランジスタTr2及びTr3がパッドP1及びP2の間で直列に接続されるため、電源保護回路13におけるトランジスタのゲートサイズが実質的に小さくなるためである。このため、ゲートサイズが同じ場合、電源保護回路13のESD保護特性は、電源保護回路13-0に対して低下する。

#### 【0065】

しかしながら、一般的に、オン電流とゲートサイズとの相関は、線形性を有する。このため、曲線L5に示されるように、電源保護回路13のゲートサイズを例えば2倍程度の大きさにすることによって、オン電流Is0と同等又はそれ以上のオン電流2Isを流すことができる。

#### 【0066】

なお、ゲートサイズを大きくすることによって、当該ゲートサイズの増分に対して線形

10

20

30

40

50

にリーク電流も大きくなると考えられる。しかしながら、図5において示されたように、電源保護回路13は、電源保護回路13-0に対して指數関数的に（約1/1000倍程度に低減）改善されるため、ゲートサイズを大きくすることによるESD保護特性の低下の影響（約2倍程度の増加）を十分にカバーすることができる。したがって、ESD保護特性を損なうことなく、リーク電流を低減させることができる。

【0067】

1.4 第1実施形態の変形例

なお、第1実施形態に係る半導体装置は、上述の例に限らず、種々の変形が適用可能である。

【0068】

1.4.1 第1変形例

例えば、電源保護回路13は、抵抗R2に代えて、トランジスタを備えていてもよい。

【0069】

図7は、第1実施形態の第1変形例に係る電源保護回路の構成を示す回路図である。図7に示すように、トランジスタTr4は、ノードN3に接続された第1端と、ノードN4に接続された第2端と、ノードN2に接続されたゲートと、を含む。トランジスタTr4は、例えば、nチャネルの極性を有する。

【0070】

トランジスタTr4は、ノードN2に“L”レベルが供給される場合、すなわち、サージ発生時動作期間において、オフ状態となる。これにより、ノードN3をノードN4から電気的に切断し、トランジスタTr2に供給される電圧をより安定化させることができる。また、トランジスタTr4は、ノードN2に“H”レベルが供給される場合、すなわち、通常時動作期間において、オン状態となる。これにより、トランジスタTr2にオン電流Isが流れない際にはノードN3をノードN4に電気的に接続することができる。このため、トランジスタTr2のゲートの電位をパッドP1及びP2の中間電位V1に維持することができ、ひいては、リーク電流を低減させることができる。

【0071】

1.4.2 第2変形例

また、電源保護回路13は、トリガ回路としてRC時定数によるタイマ機能を有するものの限らず、タイマ機能を有さないその他のトリガ回路を備えていてもよい。図8、図9、及び図10は、第1実施形態の第2変形例に係る電源保護回路の構成を示す回路図である。

【0072】

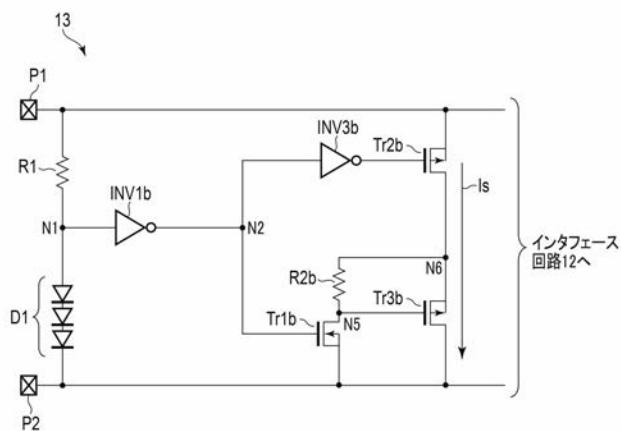

図8では、キャパシタC1に代えて、直列に接続された複数のダイオードD1が用いられる例が示される。図8に示すように、複数のダイオードD1は、ノードN1に接続された入力端（アノード）と、パッドP2に接続された出力端（カソード）と、を含む。複数のダイオードD1は、例えば、オン電流Isを流して内部回路14をESDから保護する必要がある程度にパッドP1の電圧が上昇した場合、オン状態となるように設定される。

【0073】

このように構成することにより、ノードN1の電圧は、複数のダイオードD1がオン状態となると、抵抗R1に生じる電圧降下によって低下し、“L”レベルとなる。これにより、トランジスタTr2及びTr3をオン状態にさせ、オン電流Isを流すことができる。また、パッドP1の電圧が通常の動作範囲に戻ると、複数のダイオードD1はオフ状態となる。このため、抵抗R1に生じる電圧降下はほぼなくなり、ノードN1の電圧は、“H”レベルとなる。これにより、オン電流Isを停止させることができる。

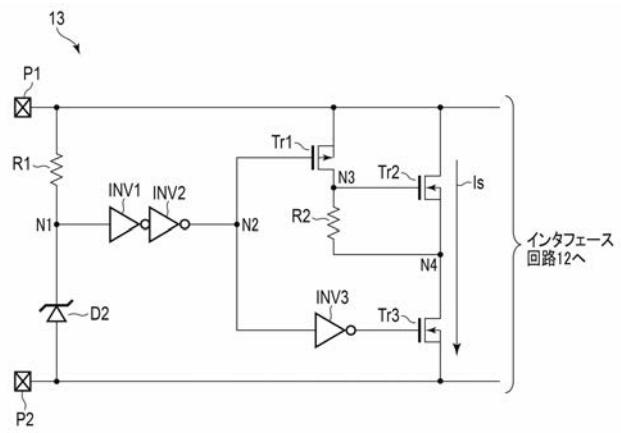

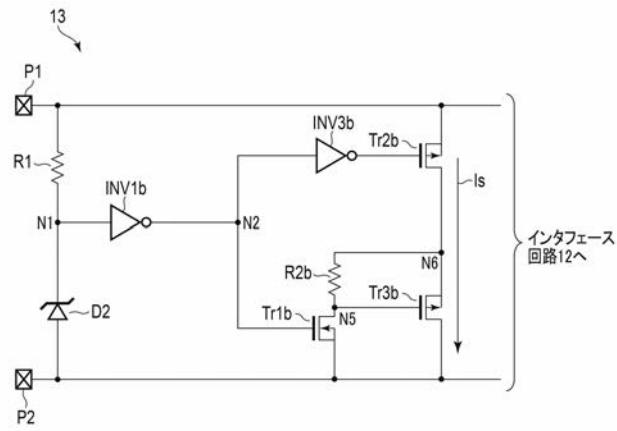

【0074】

図9では、キャパシタC1に代えて、ツェナダイオードD2が用いられる例が示される。図9に示すように、ツェナダイオードD2は、ノードN1に接続された入力端（カソード）と、パッドP2に接続された出力端（アノード）と、を含む。ツェナダイオードD2は、例えば、オン電流Isを流して内部回路14をESDから保護する必要がある程度に

パッド P 1 の電圧が上昇した場合、降伏状態となるように設定される。

【0075】

このように構成することにより、ノード N 1 の電圧は、ツエナダイオード D 2 が降伏状態となると、抵抗 R 1 に生じる電圧降下によって低下し、“L”レベルとなる。これにより、トランジスタ Tr 2 及び Tr 3 をオン状態にさせ、オン電流 I s を流すことができる。また、パッド P 1 の電圧が通常の動作範囲に戻ると、ツエナダイオード D 2 は降伏状態から回復する。このため、抵抗 R 1 に生じる電圧降下はほぼなくなり、ノード N 1 の電圧は、“H”レベルとなる。これにより、オン電流 I s を停止させることができる。

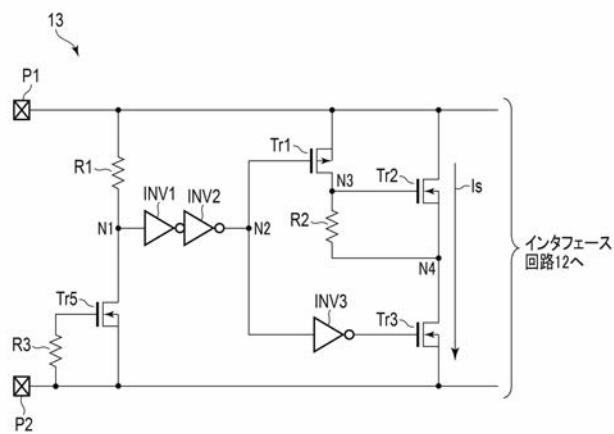

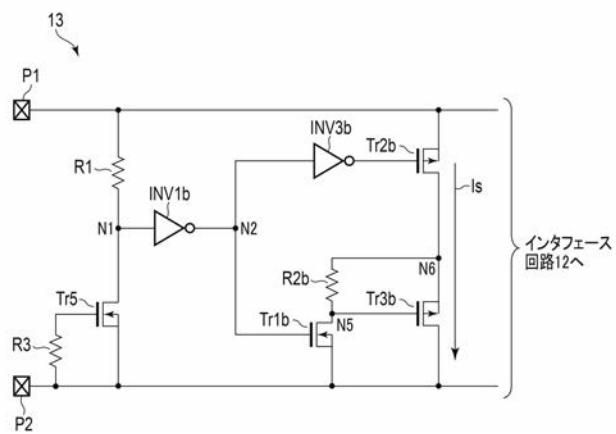

【0076】

図 10 では、キャパシタ C 1 に代えて、トランジスタ Tr 5 及び抵抗 R 3 が用いられる例が示される。図 10 に示すように、トランジスタ Tr 5 は、ノード N 1 に接続された第 1 端と、パッド P 2 に接続された第 2 端と、を含む。抵抗 R 3 は、トランジスタ Tr 5 のゲートに接続された第 1 端と、パッド P 2 に接続された第 2 端と、を含む。トランジスタ Tr 5 は、図 9 におけるツエナダイオード D 2 と同様、例えば、オン電流 I s を流して内部回路 14 を ESD から保護する必要がある程度にパッド P 1 の電圧が上昇した場合、降伏状態となるように設定される。

【0077】

このように構成することにより、ノード N 1 の電圧は、トランジスタ Tr 5 が降伏状態となると、抵抗 R 1 に生じる電圧降下によって低下し、“L”レベルとなる。これにより、トランジスタ Tr 2 及び Tr 3 をオン状態にさせ、オン電流 I s を流すことができる。また、パッド P 1 の電圧が通常の動作範囲に戻ると、トランジスタ Tr 5 は降伏状態から回復する。このため、抵抗 R 1 に生じる電圧降下はほぼなくなり、ノード N 1 の電圧は、“H”レベルとなる。これにより、オン電流 I s を停止させることができる。

【0078】

1.4.3 第 3 变形例

また、例えば、電源保護回路 13 は、パッド P 1 及び P 2 に対して、RC タイマを逆方向となるように設けてもよい。

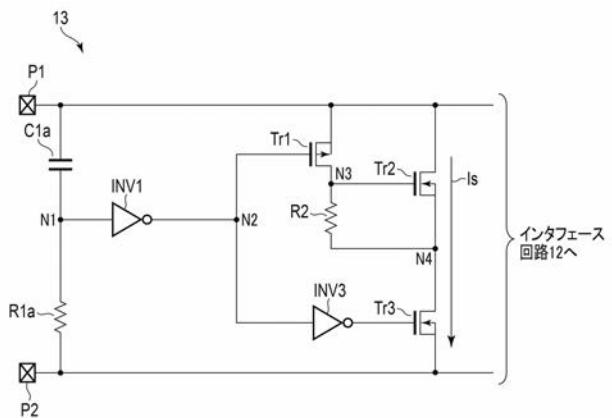

【0079】

図 11 は、第 1 実施形態の第 3 变形例に係る電源保護回路の構成を示す回路図である。図 11 では、抵抗 R 1 及びキャパシタ C 1 に代えて、キャパシタ C 1 a 及び抵抗 R 1 a が用いられる例が示される。

【0080】

図 11 に示すように、キャパシタ C 1 a は、パッド P 1 に接続された第 1 端と、ノード N 1 に接続された第 2 端と、を含む。抵抗 R 1 a は、ノード N 1 に接続された第 1 端と、パッド P 2 に接続された第 2 端と、を含む。抵抗 R 1 及びキャパシタ C 1 は、各々の抵抗値及び容量に基づいて決定される時定数に基づいて動作する RC タイマとして機能する。

【0081】

また、図 11 では、インバータ INV 2 が除かれる。すなわち、インバータ INV 1 の出力端は、ノード N 2 に接続される。

【0082】

図 12 は、第 1 実施形態の第 3 变形例に係る電源保護回路の動作を示すタイミングチャートである。図 12 は、第 1 実施形態に係る図 3 に対応する。

【0083】

図 12 に示すように、時刻 T 10 において、サージが発生する。これにより、パッド P 1 の電圧は急峻に立ち上がった後、徐々に電圧 VSS に近づいていく。ノード N 1 は、パッド P 1 の電圧上昇に追従する。このため、ノード N 1 は、サージ発生時動作期間にわたって“H”レベルのままとなる。これに伴い、インバータ INV 1 は“L”レベルを出力する。このため、インバータ INV 1 から出力された“L”レベルがノード N 2 を介してトランジスタ Tr 1 のゲート及びインバータ INV 3 の入力端に入力される。

【0084】

10

20

30

40

50

これにより、トランジスタ Tr 2 及び Tr 3 がいずれもオン状態となることにより、トランジスタ Tr 2 及び Tr 3 を電流経路として、パッド P 1 からパッド P 2 に向けてオン電流 I s が流れる。なお、トランジスタ Tr 1 ~ 3、及びインバータ INV 3 の以降の動作は、図 3 と同様であるため、説明を省略する。

【0085】

以上のように動作することにより、電源保護回路 1 3 は、サージ発生時動作期間においてオン電流 I s を流した後、停止する。

【0086】

一方、通常時動作期間において、ノード N 1 の電圧は、電圧 VSS となる。すなわち、ノード N 1 は、通常時動作期間において、“L”レベルとなる。これにより、インバータ INV 1 は“H”レベルを出力する。このため、インバータ INV 1 から出力された“H”レベルがトランジスタ Tr 1 のゲート及びインバータ INV 3 の入力端に入力される。

10

【0087】

これにより、トランジスタ Tr 2 及び Tr 3 がいずれもオフ状態となり、オン電流 I s は流れない。なお、トランジスタ Tr 1 ~ 3、及びインバータ INV 3 の以降の動作は、図 3 と同様であるため、説明を省略する。

【0088】

以上のように動作することにより、電源保護回路 1 3 では、通常時動作期間においてはオン電流 I s が流れない。また、ノード N 3 及び N 4 の電圧は、電圧 V 1 に維持される。

20

【0089】

このように、RC タイマを逆方向に取付けた場合においても、トランジスタ Tr 2 及び Tr 3 に対して第 1 実施形態と同様の信号を入力することができる。したがって、第 1 実施形態と同様の効果を奏することができる。

30

【0090】

なお、本変形例は、第 2 変形例に対しても同様に適用可能である。すなわち、トリガ回路として RC 時定数によるタイマ機能を有するものに限らず、タイマ機能を有さない他のトリガ回路についても、逆方向に取付けることが可能である。具体的には、本変形例の図 1 1 において、キャパシタ C 1 a に代えて、複数のダイオード、ツェナダイオード、及びトランジスタを備える構成であってもよい。この場合についても、本変形例と同様の効果を奏することができる。

30

【0091】

## 2. 第 2 実施形態

次に、第 2 実施形態に係る半導体装置について説明する。第 1 実施形態に係る半導体装置は、n チャネルの極性を有するトランジスタを介してオン電流 I s を流す構成であった。一方、第 2 実施形態に係る半導体装置は、p チャネルの極性を有するトランジスタを介してオン電流 I s を流す構成である点において、第 1 実施形態と異なる。以下では、第 1 実施形態と同様の構成要素には同一の符号を付してその説明を省略し、第 1 実施形態と異なる部分についてのみ説明する。

40

【0092】

### 2.1 電源保護回路の構成について

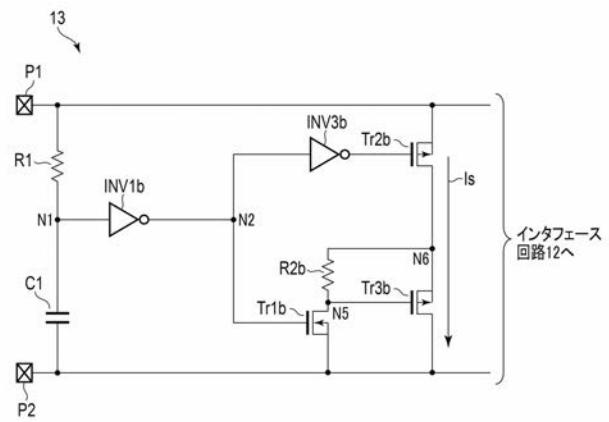

第 2 実施形態に係る半導体装置の電源保護回路の構成例について、図 1 3 を用いて説明する。図 1 3 は、第 1 実施形態における図 2 に対応する。

【0093】

図 1 3 に示すように、電源保護回路 1 3 は、トランジスタ Tr 1 b、Tr 2 b、及び Tr 3 b、抵抗 R 1 及び R 2 b、キャパシタ C 1、並びにインバータ INV 1 b 及び INV 3 b を含む。トランジスタ Tr 1 b は、例えば、n チャネルの極性を有する。トランジスタ Tr 2 b、及び Tr 3 b は、例えば、p チャネルの極性を有する。抵抗 R 1 及びキャパシタ C 1 の構成については、第 1 実施形態の図 2 と同様の構成であるため、説明を省略する。

50

【0094】

インバータ IN V 1 b は、ノード N 1 に接続される入力端と、ノード N 2 に接続される出力端と、を含む。インバータ IN V 3 b は、入力端がノード N 2 に接続され、出力端がトランジスタ Tr 2 b のゲートに接続される。インバータ IN V 1 b 及び IN V 3 b は、例えば、パッド P 1 及び P 2 の電位差に応じた値の信号を出力するよう構成されてもよい。

【0095】

トランジスタ Tr 1 b は、第 1 端及びバックゲートがパッド P 2 に接続され、第 2 端がノード N 5 に接続され、ゲートがノード N 2 に接続される。すなわち、トランジスタ Tr 1 b の第 1 端及び第 2 端はそれぞれ、ソース及びドレインとして機能する。

【0096】

抵抗 R 2 b は、第 1 端がノード N 5 に接続され、第 2 端がノード N 6 に接続される。

10

【0097】

トランジスタ Tr 2 b は、第 1 端及びバックゲートがパッド P 1 に接続され、第 2 端がノード N 6 に接続され、ゲートがインバータ IN V 3 b の出力端に接続される。トランジスタ Tr 3 b は、第 1 端及びバックゲートがノード N 6 に接続され、第 2 端がパッド P 2 に接続され、ゲートがノード N 5 に接続される。すなわち、トランジスタ Tr 2 b の第 1 端及びトランジスタ Tr 3 b の第 1 端はソースとして機能し、トランジスタ Tr 2 b の第 2 端及びトランジスタ Tr 3 b の第 2 端はドレインとして機能する。トランジスタ Tr 2 b 及び Tr 3 b は、互いに同程度の大きさのゲートサイズを有することが好ましい。

20

【0098】

なお、トランジスタ Tr 1 b ~ Tr 3 b は、例えば、電圧 V DD と、電圧 V SS との間の或る電圧（便宜的に、電圧 V T b と言う。）において、オン状態又はオフ状態に切り替わることが好ましい。より好ましくは、電圧 V T b は、電圧 V DD / 2 と、電圧 V SS との間に設定されることが好ましい。トランジスタ Tr 1 b は、電圧 V T b より高い電圧がゲートに印加されると、オン状態となり、電圧 V T b より低い電圧がゲートに印加されると、オフ状態となる。また、トランジスタ Tr 2 b 及び Tr 3 b は、電圧 V T b より高い電圧がゲートに印加されると、オフ状態となり、電圧 V T b より低い電圧がゲートに印加されると、オン状態となる。このように、p チャネルの極性を有するトランジスタと、n チャネルの極性を有するトランジスタは、一方がオン状態の場合は他方がオフ状態となり、一方がオフ状態の場合は他方がオン状態となることが好ましい。

30

【0099】

以下の説明では、トランジスタ Tr 1 b ~ Tr 3 b のゲートに印加される電圧について、電圧 V T b よりも低い電圧の論理レベルを“L”レベルと言い、電圧 V T よりも高い電圧を“H”レベルと言う。

【0100】

なお、インバータ IN V 1 b 及び IN V 3 b は、トランジスタ Tr 1 b ~ Tr 3 b と同様、電圧 V T b において、入力端に入力される信号に基づいて出力端から出力される信号が切り替わってもよい。より具体的には、インバータ IN V 1 b 及び IN V 3 b は、“L”レベルが入力端に入力されると、出力端から“H”レベルを出力し、“H”レベルが入力端に入力されると、出力端から“L”レベルを出力してもよい。

40

【0101】

## 2.2 電源保護回路の動作について

次に、第 2 実施形態に係る半導体装置の電源保護回路の動作について説明する。

【0102】

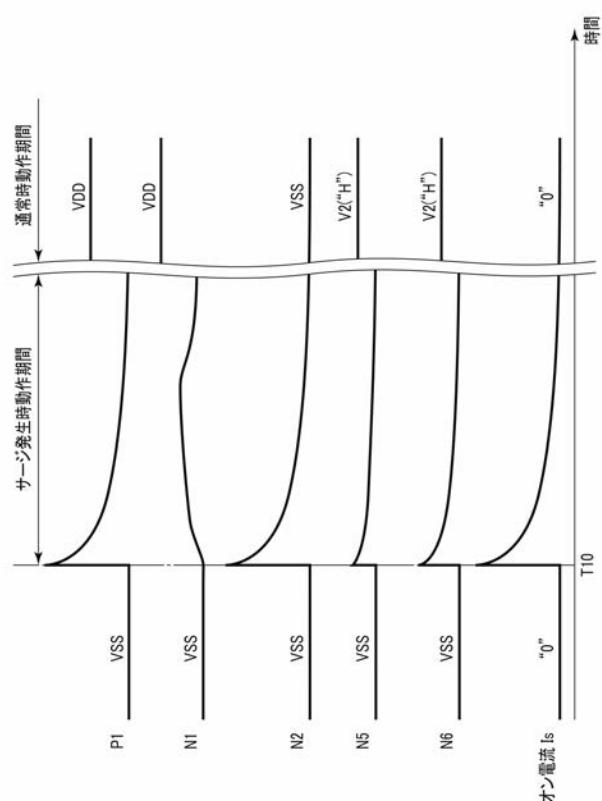

図 14 は、第 2 実施形態に係る電源保護回路の動作を説明するためのタイミングチャートである。図 14 は、一例として、サージが発生した際と、定常的に電源が供給されている際ににおける、電源保護回路 13 の動作を模式的に示している。

【0103】

図 14 に示すように、時刻 T 10 に至るまでの動作は、第 1 実施形態と同様であるため、その説明を省略する。

50

## 【0104】

時刻 T 1 0 において、サージが発生することにより、パッド P 1 の電圧は急峻に立ち上がった後、徐々に電圧 VSS に近づいていく。ノード N 1 は、サージに応じてキャパシタ C 1 の電荷が充電されるため電圧が緩やかに上昇するものの、パッド P 1 の電圧の減少に伴って再度減少する。このため、ノード N 1 はサージ発生時動作期間にわたって “L” レベルのままである。

## 【0105】

これに伴い、インバータ INV 1 b はノード N 2 に “H” レベルを出力する。このため、インバータ INV 1 b から出力された “H” レベルがトランジスタ Tr 1 b のゲート及びインバータ INV 3 b の入力端に入力される。

10

## 【0106】

インバータ INV 3 b は、“H” レベルが入力されたことによって “L” レベルを出力する。インバータ INV 3 b から出力された “L” レベルは、トランジスタ Tr 2 b のゲートに入力され、トランジスタ Tr 2 b をオン状態にする。

## 【0107】

また、トランジスタ Tr 1 b は、“H” レベルが入力されたことによってオン状態となる。ノード N 5 の電圧は、ノード N 6 及びパッド P 2 と電気的に接続されることにより、ノード N 6 の動きに追従する。しかしながら、ノード N 5 の電圧は、電圧 VSS 及び電圧 VDD の間の大きさであり、トランジスタ Tr 3 b をオン状態にする大きさの電圧である。すなわち、ノード N 5 は、“L” レベルとなる。

20

## 【0108】

このように、サージ発生時動作期間にわたってトランジスタ Tr 2 b 及び Tr 3 b がいずれもオン状態となることにより、トランジスタ Tr 2 b 及び Tr 3 b を電流経路として、パッド P 1 からパッド P 2 に向けてオン電流 Is が流れる。

## 【0109】

一方、通常時動作期間において、ノード N 1 は、キャパシタ C 1 が十分に充電されたことに伴い、電圧 VDD に達する。すなわち、ノード N 1 は、“H” レベルとなる。

## 【0110】

ノード N 1 が “H” レベルとなると、インバータ INV 1 b は “L” レベルを出力する。このため、インバータ INV 1 b から出力された “L” レベルがトランジスタ Tr 1 b のゲート及びインバータ INV 3 b の入力端に入力される。

30

## 【0111】

インバータ INV 3 b は、“L” レベルが入力されたことによって “H” レベルを出力する。インバータ INV 3 b から出力された “H” レベルは、トランジスタ Tr 2 b のゲートに入力され、トランジスタ Tr 2 b をオフ状態にする。

## 【0112】

トランジスタ Tr 1 b は、“L” レベルが入力されたことによってオフ状態となり、ノード N 5 は、パッド P 2 から電気的に切断されるが、抵抗 R 2 b を介してノード N 6 と接続されたままである。このとき、ノード N 5 及び N 6 の電圧は、電圧 V2 となる。電圧 V2 は、電圧 VDD 及び VSS の間の大きさであり、例えば、電圧 VTb より大きい (“H” レベルである)。電圧 V2 は、トランジスタ Tr 2 b 及び Tr 3 b のゲートサイズが同等の場合、例えば、VDD / 2 程度となる。このため、トランジスタ Tr 3 b は、オフ状態となる。

40

## 【0113】

以上のように動作することにより、電源保護回路 13 では、通常時動作期間において、トランジスタ Tr 2 b 及び Tr 3 b がいずれもオフ状態となることにより、オン電流 Is が流れない。また、ノード N 5 及び N 6 の電圧は、電圧 V2 に維持される。

## 【0114】

## 2.3 本実施形態に係る効果

第 2 実施形態によれば、トランジスタ Tr 1 b は、第 1 端がパッド P 2 に接続され、第

50

2端がノードN5に接続され、ゲートがノードN2に接続される。ノードN2は、ノードN1が“L”レベルの際、“H”レベルとなり、“H”レベルの際、“L”レベルとなる。つまり、トランジスタTr1bは、ノードN1が“L”レベルの際、ゲートに“H”レベルが入力されることにより、オン状態となる。これにより、サージ発生時動作期間において、パッドP2にノードN5を電気的に接続する。このため、トランジスタTr3bのゲートに“L”レベルが入力され、トランジスタTr3bをオン状態にすることができる。一方、ノードN1が“H”レベルの際、トランジスタTr1bのゲートには“L”レベルが入力されることにより、オフ状態となる。これにより、通常時動作期間において、ノードN5は、パッドP2から電気的に切断される。このため、トランジスタTr3bのゲートに“H”レベルが入力され、トランジスタTr3bをオフ状態にすることができる。

10

## 【0115】

また、抵抗R2bは、ノードN5とノードN6とを電気的に接続する。これにより、通常時動作期間において、ノードN5の電圧がノードN6の電圧に維持される。ノードN6は、トランジスタTr2b及びTr3bの中間ノードであるため、電圧VDD及び電圧VSSの中間電位である電圧V2となる。このため、トランジスタTr3bのゲート及びバックゲートを、電圧V2にすることができる。

## 【0116】

また、インバータINV3bは、ノードN2に接続された入力端と、トランジスタTr2bのゲートに接続された出力端と、を含む。これにより、インバータINV3bは、ノードN1が“L”レベルの際、“L”レベルを出力し、ノードN1が“H”レベルの際、“H”レベルを出力する。このため、サージ発生時動作期間において、トランジスタTr2bをオン状態にすることができる、通常時動作期間において、トランジスタTr2bをオフ状態にすることができる。

20

## 【0117】

したがって、オン電流Isを流すトランジスタの極性をpチャネルにした場合においても、トランジスタTr2b及びTr3bを第1実施形態と同様に動作させることができる。したがって、第1実施形態と同様の効果を奏すことができる。

## 【0118】

## 2.4 第2実施形態の変形例

なお、第2実施形態に係る半導体装置は、上述の例に限らず、種々の変形が適用可能である。

30

## 【0119】

## 2.4.1 第1変形例

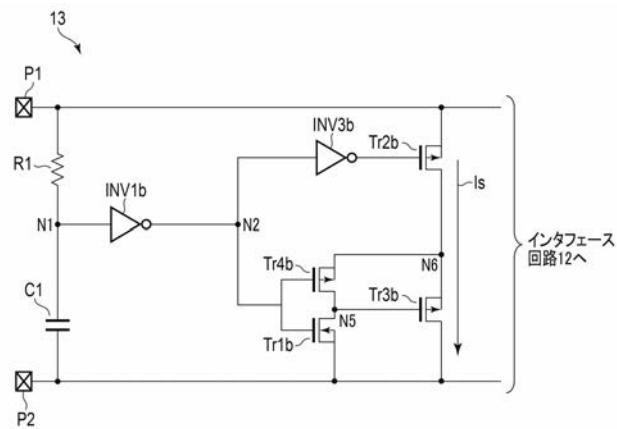

例えば、電源保護回路13は、抵抗R2bに代えて、トランジスタを備えていてよい。

## 【0120】

図15は、第2実施形態の第1変形例に係る電源保護回路の構成を示す回路図である。図15に示すように、トランジスタTr4bは、ノードN5に接続された第1端と、ノードN6に接続された第2端と、ノードN2に接続されたゲートと、を含む。トランジスタTr4bは、例えば、pチャネルの極性を有する。

40

## 【0121】

トランジスタTr4bは、ノードN2に“H”レベルが供給される場合、すなわち、サージ発生時動作期間において、オフ状態となる。これにより、ノードN5をノードN6から電気的に切断し、トランジスタTr3bに供給される電圧をより安定化させることができる。また、トランジスタTr4bは、ノードN2に“L”レベルが供給される場合、すなわち、通常時動作期間において、オン状態となる。これにより、トランジスタTr3bにオン電流Isが流れない際にはノードN5をノードN6に電気的に接続することができる。このため、トランジスタTr3bのゲートの電位をパッドP1及びP2の中間電位V2に維持することができ、ひいては、リーク電流を低減させることができる。

## 【0122】

50

## 2.4.2 第2変形例

また、電源保護回路13は、トリガ回路としてRC時定数によるタイマ機能を有するものに限らず、タイマ機能を有さないその他のトリガ回路を備えていてもよい。図16、図17、及び図18は、第2実施形態の第2変形例に係る電源保護回路の構成を示す回路図である。

## 【0123】

図16では、キャパシタC1に代えて、直列に接続された複数のダイオードD1が用いられる例が示される。図16に示すように、複数のダイオードD1は、ノードN1に接続された入力端(アノード)と、パッドP2に接続された出力端(カソード)と、を含む。複数のダイオードD1は、例えば、オン電流Isを流して内部回路14をESDから保護する必要がある程度にパッドP1の電圧が上昇した場合、オン状態となるように設定される。

10

## 【0124】

このように構成することにより、ノードN1の電圧は、複数のダイオードD1がオン状態となると、抵抗R1に生じる電圧降下によって低下し、“L”レベルとなる。これにより、トランジスタTr2b及びTr3bをオン状態にさせ、オン電流Isを流すことができる。また、パッドP1の電圧が通常の動作範囲に戻ると、複数のダイオードD1はオフ状態となる。このため、抵抗R1に生じる電圧降下はほぼなくなり、ノードN1の電圧は、“H”レベルとなる。これにより、オン電流Isを停止させることができる。

20

## 【0125】

図17では、キャパシタC1に代えて、ツェナダイオードD2が用いられる例が示される。図17に示すように、ツェナダイオードD2は、ノードN1に接続された入力端(カソード)と、パッドP2に接続された出力端(アノード)と、を含む。ツェナダイオードD2は、例えば、オン電流Isを流して内部回路14をESDから保護する必要がある程度にパッドP1の電圧が上昇した場合、降伏状態となるように設定される。

20

## 【0126】

このように構成することにより、ノードN1の電圧は、ツェナダイオードD2が降伏状態となると、抵抗R1に生じる電圧降下によって低下し、“L”レベルとなる。これにより、トランジスタTr2b及びTr3bをオン状態にさせ、オン電流Isを流すことができる。また、パッドP1の電圧が通常の動作範囲に戻ると、ツェナダイオードD2は降伏状態から回復する。このため、抵抗R1に生じる電圧降下はほぼなくなり、ノードN1の電圧は、“H”レベルとなる。これにより、オン電流Isを停止させることができる。

30

## 【0127】

図18では、キャパシタC1に代えて、トランジスタTr5及び抵抗R3が用いられる例が示される。図18に示すように、トランジスタTr5は、ノードN1に接続された第1端と、パッドP2に接続された第2端と、を含む。抵抗R3は、トランジスタTr5のゲートに接続された第1端と、パッドP2に接続された第2端と、を含む。トランジスタTr5は、図17におけるツェナダイオードD2と同様、例えば、オン電流Isを流して内部回路14をESDから保護する必要がある程度にパッドP1の電圧が上昇した場合、降伏状態となるように設定される。

40

## 【0128】

このように構成することにより、ノードN1の電圧は、トランジスタTr5が降伏状態となると、抵抗R1に生じる電圧降下によって低下し、“L”レベルとなる。これにより、トランジスタTr2b及びTr3bをオン状態にさせ、オン電流Isを流すことができる。また、パッドP1の電圧が通常の動作範囲に戻ると、トランジスタTr5は降伏状態から回復する。このため、抵抗R1に生じる電圧降下はほぼなくなり、ノードN1の電圧は、“H”レベルとなる。これにより、オン電流Isを停止させることができる。

## 【0129】

## 2.4.3 第3変形例

また、例えば、電源保護回路13は、パッドP1及びP2に対して、RCタイマを逆方

50

向となるように設けてよい。

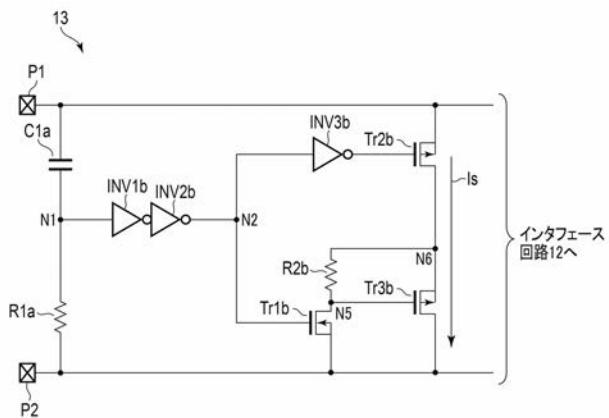

【0130】

図19は、第2実施形態の第3変形例に係る電源保護回路の構成を示す回路図である。図19では、抵抗R1及びキャパシタC1に代えて、キャパシタC1a及び抵抗R1aが用いられる例が示される。

【0131】

図19に示すように、キャパシタC1aは、パッドP1に接続された第1端と、ノードN1に接続された第2端と、を含む。抵抗R1aは、ノードN1に接続された第1端と、パッドP2に接続された第2端と、を含む。抵抗R1及びキャパシタC1は、各々の抵抗値及び容量に基づいて決定される時定数に基づいて動作するRCタイマとして機能する。具体的には、ノードN1の電圧は、パッドP2の電圧に対して、当該時定数に基づく時間的な遅れを伴って追従する。

10

【0132】

また、第2実施形態に係る第3変形例では、電源保護回路13は、インバータINV2bを更に含む。インバータINV2bの入力端及び出力端はそれぞれ、インバータINV1bの出力端、及びノードN2に接続される。

【0133】

図20は、第2実施形態の第3変形例に係る電源保護回路の動作を示すタイミングチャートである。

20

【0134】

図20に示すように、時刻T10において、サージが発生する。これにより、パッドP1の電圧は急峻に立ち上がった後、徐々に電圧VSSに近づいてく。ノードN1は、パッドP1の電圧上昇に追従する。このため、ノードN1は、サージ発生時動作期間にわたって“H”レベルのまとなる。これに伴い、インバータINV1bは“L”レベルを出力し、インバータINV2bは“H”レベルを出力する。インバータINV2bから出力された“H”レベルがトランジスタTr1bのゲート及びインバータINV3bの入力端に入力される。

20

【0135】

これにより、トランジスタTr2b及びTr3bがいずれもオン状態となることにより、トランジスタTr2b及びTr3bを電流経路として、パッドP1からパッドP2に向けてオン電流Isが流れる。なお、トランジスタTr1b～3b、及びインバータINV3bの以降の動作は、第2実施形態に係る図14と同様であるため、説明を省略する。

30

【0136】

以上のように動作することにより、電源保護回路13は、サージ発生時動作期間においてオン電流Isを流した後、停止する。

【0137】

通常時動作期間において、ノードN1の電圧は、電圧VSSとなる。すなわち、ノードN1は、通常時動作期間において、“L”レベルとなる。これにより、インバータINV1bは“H”レベルを出力し、インバータINV2bは“L”レベルを出力する。このため、インバータINV2bから出力された“L”レベルがトランジスタTr1bのゲート及びインバータINV3bの入力端に入力される。

40

【0138】

これにより、トランジスタTr2b及びTr3bがいずれもオフ状態となり、オン電流Isは流れない。なお、トランジスタTr1b～3b、及びインバータINV3bの以降の動作は、第2実施形態に係る図14と同様であるため、説明を省略する。

【0139】

以上のように動作することにより、電源保護回路13では、通常時動作期間においてはオン電流Isは流れない。また、ノードN5及びN6の電圧は、電圧V2に維持される。

【0140】

このように、RCタイマを逆方向に取付けた場合においても、トランジスタTr2b及

50

びTr3bに対して第2実施形態と同様の信号を入力することができる。したがって、第2実施形態と同様の効果を奏することができる。

#### 【0141】

なお、本変形例は、第2変形例に対しても同様に適用可能である。すなわち、トリガ回路としてRC時定数によるタイマ機能を有するものに限らず、タイマ機能を有さないその他のトリガ回路についても、逆方向に取付けることが可能である。具体的には、本変形例の図19において、キャパシタC1aに代えて、複数のダイオード、ツエナダイオード、及びトランジスタを備える構成であってもよい。この場合についても、本変形例と同様の効果を奏することができる。

#### 【0142】

##### 5. その他

その他、各実施形態及び各変形例において、以下の事項が適用されることが可能である。

#### 【0143】

例えば、第1実施形態に係るトランジスタTr3、及び第2実施形態の第3変形例に係るトランジスタTr2bには、3段のインバータが直列接続される例について説明したが、これに限られない。例えば、第1実施形態に係るトランジスタTr3、及び第2実施形態の第3変形例に係るトランジスタTr2bには、任意の奇数段のインバータが直列接続可能である。

#### 【0144】

また、第1実施形態の第3変形例に係るトランジスタTr3、及び第2実施形態に係るトランジスタTr2bには、2段のインバータが直列接続される例について説明したが、これに限られない。例えば、第1実施形態の第3変形例に係るトランジスタTr3、及び第2実施形態に係るトランジスタTr2bには、任意の偶数段のインバータが直列接続可能である。

#### 【0145】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

#### 【符号の説明】

#### 【0146】

1...半導体装置、11...パッド群、12...インターフェース回路、13...電源保護回路、14...内部回路。

【図 1】

【図 3】

【図 2】

【図 4】

【図 5】

【 図 6 】

【 図 7 】

〔 叁 8 〕

【 図 9 】

【図 1 0】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図 1 7】

【図 1 8】

【図 1 9】

【図 2 0】

---

フロントページの続き

(74)代理人 100189913

弁理士 鵜飼 健

(72)発明者 渡邊 健太郎

東京都港区芝浦一丁目 1 番 1 号 株式会社東芝内

F ターム(参考) 5F038 BE09 BH02 BH03 BH04 BH05 BH07 BH13 DF01 EZ20

5F048 AA02 AB04 AB06 AB07 AC03 AC10 BD10 BE09 CC01 CC05

CC06 CC09 CC13 CC15 CC16 CC19