(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3616468号

(P3616468)

(45) 発行日 平成17年2月2日(2005.2.2)

(24) 登録日 平成16年11月12日(2004.11.12)

(51) Int.C1.<sup>7</sup>

F 1

G 06 F 13/42

G 06 F 13/42 3 4 O A

H 03 K 19/0175

H 04 L 7/00 G

H 04 L 7/00

H 03 K 19/00 1 O 1 N

請求項の数 3 (全 18 頁)

(21) 出願番号

特願平8-307246

(22) 出願日

平成8年11月1日(1996.11.1)

(65) 公開番号

特開平9-167134

(43) 公開日

平成9年6月24日(1997.6.24)

審査請求日

平成13年10月2日(2001.10.2)

(31) 優先権主張番号

552657

(32) 優先日

平成7年11月3日(1995.11.3)

(33) 優先権主張国

米国(US)

前置審査

(73) 特許権者 390009597

モトローラ・インコーポレイテッド

MOTOROLA INCORPORATEDアメリカ合衆国イリノイ州シャンバーグ、

イースト・アルゴンクイン・ロード130

3

(74) 代理人 100083574

弁理士 池内 義明

(72) 発明者 ミッセル・シー・アレキサンダー

アメリカ合衆国テキサス州オースチン、ナンバー244、バートン・ヒルズ・ドライブ1200

審査官 石井 茂和

最終頁に続く

(54) 【発明の名称】データ同期システム

## (57) 【特許請求の範囲】

## 【請求項 1】

第1デバイスおよび第2デバイスと用いられるデータ同期システム(12)であり、前記第1デバイスは第1周波数で発振する第1クロック信号に基づいて動作し、前記第2デバイスは第2周波数で発振する第2クロック信号に基づいて動作し、前記第1周波数は前記第2周波数よりも大きい、ところのデータ同期システムであって：

前記第1デバイスの出力を受ける入力を有する転送ラッチ(40)であり、前記転送ラッチは、TXFR C1信号に応答して前記入力にてデータ・ビットを捕捉し、TXFR C2信号に応答してデータ・ビットを送り出す、ところの転送ラッチ(40)；

前記転送ラッチの出力を受ける入力と、前記第2デバイスに結合された出力を有するバス・ラッチ(46)であり、前記バス・ラッチは、BUS C1信号に応答して前記入力にてデータ・ビットを捕捉し、BUS C2信号に応答してデータ・ビットを送り出す、ところのバス・ラッチ(46)；

前記第2デバイスの出力に結合された入力と、前記第1デバイスに結合された出力を有する受信ラッチ(48)であって、前記受信ラッチは、RCV C1信号に応答して前記入力にてデータ・ビットを捕捉し、RCV C2信号に応答してデータ・ビットを送り出す、受信ラッチ(48)；

第1デバイスの出力に結合された入力と、第1デバイスに結合された出力を有するコア・ラッチ(38)であり、前記コア・ラッチは、CORE C1信号に応答して前記入力においてデータ・ビットを捕捉し、CORE C2信号に応答して前記データ・ビットを

10

20

送り出す、ところのコア・ラッチ(38)；および

前記CORE C1, CORE C2, TXFR C1, TXFR C2, BUS C1, BUS C2, RCV C1およびRCV C2信号を生成するクロック発生回路(80, 82, 84, 86, 94, 96)であって、前記BUS C1, BUS C2, RCV C1およびRCV C2信号は前記第2周波数で発振しつつ前記TXFR C1, TXFR C2, CORE C1およびCORE C2は前記第1周波数で発振し、そして前記第1クロック信号の第1の所定のエッジおよび前記第2クロック信号の第2の所定のエッジの一一致に応じて、前記クロック発生回路は、(1)前記TXFR C2信号のアサートを削除し、かつ(2)前記第1クロック信号の半サイクルで前記RCV C2のアサートを遅延させる、クロック発生回路(80, 82, 84, 86, 94, 96)；

によって構成されることを特徴とするデータ同期システム。

10

### 【請求項2】

第1周波数で発振する第1クロック信号に基づいて動作するデータ・プロセッサ(10)であって、前記データ・プロセッサは、第2周波数で発振する第2クロック信号に基づいて動作するバス(データ・バス、アドレス・バス)に結合され、前記第1周波数は前記第2周波数よりも大きい、ところのデータ・プロセッサであって；

前記第1周波数で動作するコア回路(14, 16)であり、前記バスから受けた命令を実行し、かつ結果を前記バスに書き込む、コア回路(14, 16)；ならびに

前記コア回路および前記バスを結合するバス・インターフェース回路(12)であり、複数のビット経路から成る前記バス・インターフェース回路；

20

から構成されたデータ・プロセッサであって：

前記複数のビット経路のそれぞれが：

前記コア回路の出力を受ける入力を有する転送ラッチ(40)であって、前記転送ラッチは、TXFR C1信号に応答して前記入力にてデータ・ビットを捕捉し、TXFR C2信号に応答してデータ・ビットを送り出す、転送ラッチ(40)と；

前記転送ラッチの出力を受ける入力と、前記バスに結合された出力とを有するバス・ラッチ(46)であって、前記バス・ラッチは、BUS C1信号に応答して前記入力にてデータ・ビットを捕捉し、BUS C2信号に応答してデータ・ビットを送り出す、バス・ラッチ(46)と；

前記バスに結合された入力と、前記コア回路に結合された出力とを有する受信ラッチ(48)であって、前記受信ラッチは、RCV C1信号に応答して前記入力にてデータ・ビットを捕捉し、RCV C2信号に応答してデータ・ビットを送り出す、受信ラッチ(48)と；

30

前記コア回路の出力に結合された入力と、前記コア回路に結合された出力とを有するコア・ラッチ(38)であり、前記コア・ラッチは、CORE C1信号に応答して前記入力においてデータ・ビットを捕捉し、CORE C2信号に応答して前記データ・ビットを送り出す、ところのコア・ラッチ(38)；および

前記CORE C1, CORE C2, TXFR C1, TXFR C2, BUS C1, BUS C2, RCV C1およびRCV C2信号を生成するクロック発生回路(80, 82, 84, 86, 94, 96)であって、前記BUS C1, BUS C2, RCV C1およびRCV C2信号は前記第2周波数で発振しつつ前記TXFR C1, TXFR C2, CORE C1およびCORE C2は前記第1周波数で発振し、そして前記第1クロック信号の第1の所定のエッジおよび前記第2クロック信号の第2の所定のエッジの一一致に応じて、前記クロック発生回路は、(1)前記TXFR C2信号のアサートを削除し、かつ(2)前記第1クロック信号の半サイクルで前記RCV C2のアサートを遅延させる、クロック発生回路(80, 82, 84, 86, 94, 96)；

40

から成るバス・インターフェース回路(12)；

によって構成されることを特徴とするデータ・プロセッサ。

### 【請求項3】

第1周波数で発振する第1クロック信号に基づいて動作するデータ・プロセッサ(10)

50

であって、前記データ・プロセッサは、第2周波数で発振する第2クロック信号に基づいて動作するバス(データ・バス, アドレス・バス)に結合され、前記第1周波数は前記第2周波数よりも大きい、ところのデータ・プロセッサであって；

第1入力と、前記第2クロック信号に結合された第2入力を備えた位相検出器(72, 76, 78)であり、前記第2クロック信号と、前記第1入力にて受けた入力との間の位相差に応答して制御信号を生成する位相検出器；

前記位相検出器に結合されたクロック発生回路(94, 96)であり、第3クロック信号を発生し、前記第3クロック信号の位相および周波数は前記制御信号に応答する、クロック発生回路(94, 96)；

前記クロック発生回路に結合されたバス・リジエネレータ(80)であり、B U S C 1 10

信号およびB U S C 2 信号を発生し、前記B U S C 1 信号および前記B U S C 2 信号は、前記第2周波数で発振し、前記B U S C 1 信号は前記位相検出器の第1入力に結合される、バス・リジエネレータ(80)；

前記クロック発生回路に結合された受信リジエネレータ(82)であり、R C V C 1 信号およびR C V C 2 信号を発生し、前記R C V C 1 信号および前記R C V C 2 信号は前記第2周波数で発振し、前記受信リジエネレータは、前記第1クロック信号の第1の所定のエッジと前記第2クロック信号の第2の所定のエッジとが一致したときに、前記第1クロック信号の半サイクルでR C V C 2 のアサートを遅延させる、受信リジエネレータ(82)；

前記クロック発生回路に結合された転送リジエネレータ(84)であり、T X F R C 1 20

信号およびT X F R C 2 信号を発生し、前記T X F R C 1 信号および前記T X F R C 2 信号は前記第1周波数で発振し、一致時にT X F R C 2 のアサートを削除する、転送リジエネレータ(84)；および

前記クロック発生回路に結合されたコア・リジエネレータ(86)であり、C O R E C 1 信号およびC O R E C 2 信号を発生し、前記C O R E C 1 信号および前記C O R E C 2 信号は、前記第1周波数で発振する、コア・リジエネレータ(86)；

によって構成されることを特徴とするデータ・プロセッサ。

#### 【発明の詳細な説明】

##### 【0001】

##### 【産業上の利用分野】

本発明は、一般に、データ処理システムに関し、さらに詳しくは、データ処理システムで用いられるデータ同期方法に関する。

##### 【0002】

##### 【従来の技術】

多くのデータ処理システムは、異なるクロック周波数で動作するサブシステムと設計される。この方法は、精選したサブシステムのスピードを残りのサブシステムに比べて増加することにより全体的な処理スループットを向上させることができる。一般に、これらの高速サブシステムの性能は、システムの性能全体にとって重要であるか、あるいは向上させるのが比較的安価のいずれかである。この設計方法の一例として、関連バスのクロック周波数の数倍のクロック周波数で動作する単一のV L S I (v e r y l a r g e s c a l e i n t e g r a t e d ) データ・プロセッサを有するデータ処理システムがある。この場合、データ処理システム内の全てではないにしろほとんどの他のサブシステムは、低いバス・クロック・スピードで動作する。一般に、2つのクロック周波数の比率は、2つの整数の比率、例えば、2 : 1, 3 : 1, 4 : 1などで表すことができる。これらの比率の範囲は、システム間通信を同期させるため2つのクロック信号がある程度の周波数位相整合を有するという実際的な条件を反映する。位相整合が頻繁になればなるほど、高速データ・プロセッサと低速バスとの間でデータを転送する回数が増える。

##### 【0003】

##### 【発明が解決しようとする課題】

関連バスとは異なるクロック周波数で動作するデータ・プロセッサを有するデータ処理シ 50

システムは、データ・プロセッサとバスとの間のデータ転送を同期しなければならない。例えば、2:1プロセッサ・バス・システムでは、データ・プロセッサが1プロセッサ・クロック・サイクルでしか信号をアサートしなければ、データ・プロセッサはバス信号の適正位相中に出力信号をアサートしない場合がある。逆に、バスは、2プロセッサ・クロック・サイクルで、データ・プロセッサの入力信号をアサートする場合がある。これら両方の場合では、データ転送は不安定になる。第1の場合では、データはデータ・プロセッサからバスに全く転送されないことがある。第2の場合では、バスは同じデータをデータ・プロセッサに2回転送する。

#### 【0004】

既知の同期方法には制限がある。一般に、データ転送方法は、非同期あるいは同期として表すことができる。これら各方法には、異なる同期問題がある。

10

#### 【0005】

非同期の場合、最少信号ホールド時間以外には、2つの通信するサブシステム間にタイミング条件はない。一つの既知の解決方法では、低速出力信号を、一連のシーケンシャル・ラッチ素子を介して高速入力デバイスによってサンプリングする。高速入力デバイスのクロッキング信号は、各ラッチ素子をクロックする。各連続したラッチ素子は、準安定状態(`meta stable state`)が低速デバイスから高速デバイスに渡される可能性を低減する。残念ながら、各追加ラッチは、サブシステムからサブシステムへの伝搬時間を、追加高速クロック・サイクル分だけ増加させる。

#### 【0006】

同期の場合、2つの通信するサブシステム間にタイミング条件がある。特に、受信側デバイスのクロック信号の特定の位相中に信号をアサートしなければならない。第2の既知の解決方法では、単一のラッチ素子マルチプレクサ回路が異なるクロック周波数で動作する2つのサブシステムを連結する。ラッチ素子は、各高速クロック・サイクルと同時にマルチプレクサの出力をサンプリングする。マルチプレクサは、以前ラッチした値または入力信号のいずれかを出力する。マルチプレクサの出力は、受信側サブシステムのタイミング条件に従って各入力信号を渡すように、制御信号によって選択される。一般に、受信側サブシステムのクロック信号は、高速クロック信号のN-1クロック・パルスを「飲み込む(`swallow`)」ことによって生成され、ここでプロセッサ対バス・クロック周波数の比率は、N:1である。この方法は、2つのクロック周波数の比率が整数の場合のみ堅牢である。それ以外の場合には、Nが1.5, 2.5などのとき、この方法は1つおきのバス・クロックで半サイクル転送を許可する。さらに、特定の解決は、一つのプロセッサ対バス・クロック比でのみ一般に有効となる。

20

#### 【0007】

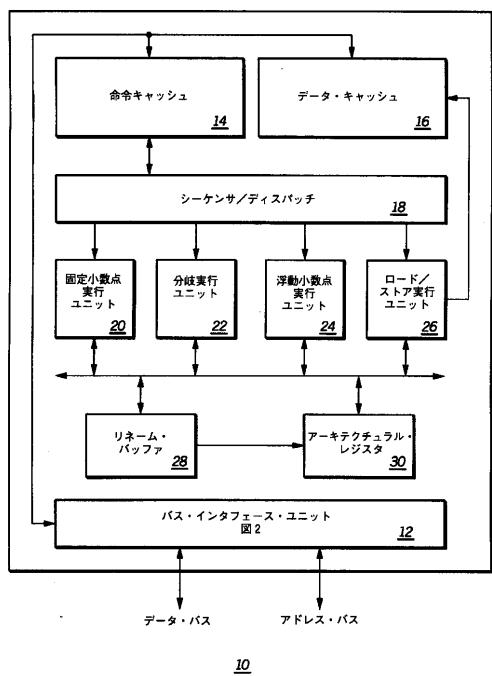

##### 【実施例】

図1は、本発明により構成されたデータ・プロセッサ10のプロック図を示す。図示のように、データ・プロセッサ10は、バス・インターフェース・ユニット12(以下では簡単にBIU12という)を有する。BIU12は、データ・プロセッサ10と、データ・プロセッサ10を他のデータ処理要素(図示せず)に接続するアドレス・バスおよび制御バスとの間のデータの流れを制御する。データ・プロセッサ10およびBIU12は、関連バスのクロック・スピードよりも高いクロック・スピードで動作する。従来技術の説明のところで説明したように、このクロッキング方式は、データ・プロセッサ10を内蔵するデータ処理システムの性能を改善する。また、本開示の発明によれば、BIU12は、バス・クロック・レートの数倍のプロセッサ・クロック・レートによって生じる同期問題に対する汎用的な解決方法を提供する。この解決方法により、单一データ・プロセッサ・モデルをさまざまなバス周波数で利用できるようになる。さらに、本開示の発明は、非同期および同期データ転送システムに従来つきまとった問題である、データ・プロセッサと関連バスとの間のデータの流れに不必要的遅延を発生することや、また不安定な半サイクル・データ経路を許可することがない。

30

#### 【0008】

40

50

図1において、B I U 1 2は、命令キャッシュ14と、データ・キャッシュ16とに接続される。命令キャッシュ14は、命令ストリームをシーケンサ/ディスパッч・ユニット18に供給する。シーケンサ/ディスパッч・ユニット18は、個々の命令を適切な実行ユニット・ブロックに送出する。データ・プロセッサ10は、固定小数点実行ユニット20、分岐実行ユニット22、浮動小数点実行ユニット24およびロード/ストア実行ユニット26を有する。これらの実行ユニット・ブロックは、リネーム・バッファ(rename buffer)28とアーキテクチャル・レジスタ・ファイル(register file)30とに接続される。

#### 【0009】

本開示の同期方法およびそのためのシステムのないデータ・プロセッサの動作は、当技術分野で周知である。一般に、シーケンサ/ディスパッч・ユニット18は、個々の命令を各実行ユニット20、22、24、26に発行する。各実行ユニットは、特定クラスの命令のうち1つまたはそれ以上の命令を実行する。各実行ユニットの特定クラスの命令は、実行ユニットの名称によって表される。例えば、分岐実行ユニット22は、分岐命令を実行する。実行ユニット・ブロック20、22、24、26は、その演算結果をリネーム・バッファ28内の指定されたエントリに返す。リネーム・バッファ28は、本発明には関係ない既知のプロトコルに従ってアーキテクチャル・レジスタ・ファイル30内の値を更新する。リネーム・バッファ28およびアーキテクチャル・レジスタ・ファイル30は、オペランドを実行ユニット・ブロック20~26に与える。

#### 【0010】

データ同期方法およびそのためのシステムを有するデータ・プロセッサ10の動作について、図2ないし図13を参照して以下で説明する。概して、データ・プロセッサ10と、アドレスおよびデータ・バスとは、1:1のデータ・プロセッサ・クロック周波数とバス・クロック周波数の比率では、同期方法やシステムなしにデータ通信を可能にする通信プロトコルに従う。例えば、特定の期間でバス・クロックの特定の位相中にいすれかのバス上でアサートされた信号は、データ・プロセッサおよびバスが同一周波数で動作する場合には、次の特定のエッジ遷移の発生時にデータ・プロセッサ10によって正しくラッチされる。さらに、データ・プロセッサ10およびアドレスおよびデータ・バスは、「ハンドシェイク」通信プロトコルに従う。ハンドシェイク通信プロトコルとは、プロトコル参加側の任意のクロック・サイクルを任意の種類のデータ・プロトコル動作のために利用できるプロトコルのことである。プロトコル参加側間の制御信号のセット上でアサートされた論理信号のセットは、各クロック・サイクル中にどの動作が行われるのかを決定する。特定のプロトコルは、本開示の発明の一部ではない。データ・プロセッサ10ができるだけ高いクロック周波数で動作させることができると有利である。ただし、アドレスおよびデータ・バスを同じ高いクロック周波数で動作させることは経済的でなく、不可能でさえある。本開示のデータ同期システムは、このようなシステムに内蔵できる。

#### 【0011】

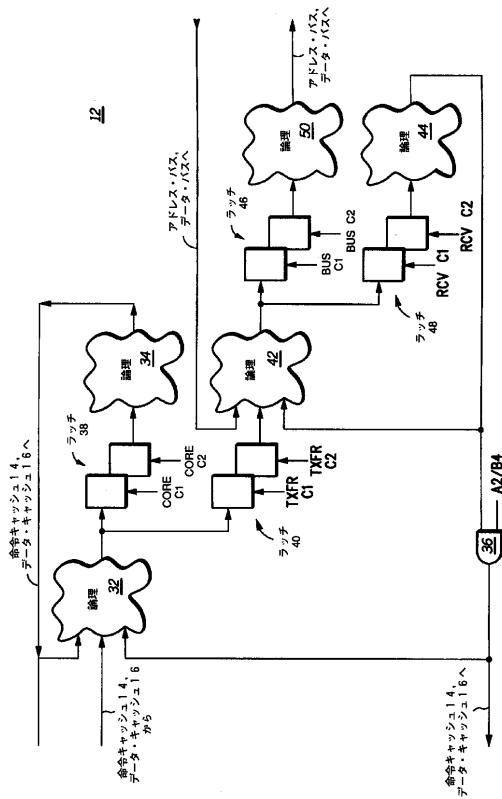

図2は、図1に示すB I U 1 2の一部のブロック図を示す。図2は、B I U 1 2内の単一のビット経路を示すことに理解されたい。当業者であれば、B I U 1 2には図示以外の多くの他の個別のビット経路があることが理解される。さらに、図2は、B I U 1 2の各機能ではなく、本開示の発明をさらにわかりやすく説明するため汎用論理ブロックを示す。これらの機能は、インプリメントに依存し、本開示の発明の一部ではない。当業者であれば、各ビット経路には、それに関連して、固有論理機能および固有論理ブロックがあることが理解されよう。また、全てのビット経路が図2の全ての部分を含むわけではないが、各ビット経路の一般的な形状は同じである。また、個別のビット経路の多くは汎用論理ブロック内で相互接続されることが当業者に理解される。

#### 【0012】

一般に、B I U 1 2は、4つの時間領域、すなわち、コア・レート領域('CORE')、転送レート領域('TXFR')、バス・レート領域('BUS')および受信レート領域('RCV')に従って、データ・プロセッサ10とアドレスおよびデータ・バスと

10

20

30

40

50

の間でデータを処理する。CMOS (complementary metal oxide semiconductor) 構成では、マスタ・スレーブ・ラッチは、中間結果を論理ステージ間でホールドするために、入力／出力バッファとして用いられる。CMOS マスタ・スレーブ・ラッチのマスタ部分は、一般に C1 パルスと呼ばれる信号によって制御される。C1 パルスをアサートすることにより、マスタ部分はラッチへのデータ入力を捕捉する。CMOS マスタ・スレーブ・ラッチのスレーブ部分は、一般に C2 パルスと呼ばれる信号によって制御される。C2 パルスをアサートすることにより、スレーブ部分は、以前の C1 パルス中に捕捉されたデータ入力をラッチの出力に送り出す。本開示の発明に従って、各 4 つのクロック領域について個別の C1 および C2 制御信号が存在する。

10

#### 【0013】

コア・レート領域は、データ・プロセッサ 10 の通常クロック領域である。コア・レート領域は、グローバル分散クロック (「GCLK」: globally distributed clock) の各サイクルに一回クロックする。GCLK の低位相は濾波され、制御信号 CORE\_C1 を生成する。GCLK の高位相は濾波されて、制御信号 CORE\_C2 を生成する。データ・プロセッサ 10 の大部分は、コア・レート領域に従って動作する。BIU12 は、コア・レート領域で動作してデータ・プロセッサ 10 の残りの部分から情報を受け、この情報を処理し、データ・プロセッサ 10 の残りの部分に返送する回路を内蔵する。

#### 【0014】

転送レート領域は、コア・レートがバス・クロック・サイクルの開始前に半サイクルしかクロックしない場合の除いて、コア・レートの各サイクルで一回クロックする。これらの場合には、バス・レート・クロックの立ち上がりエッジは、コア・レート・クロックの立ち下がりエッジと一致する。ここで、TXFR\_C1 および TXFR\_C2 の両方は濾波される。BIU12 は、転送レート領域で動作してデータ・プロセッサ 10 の残りの部分から情報を受け、この情報を処理し、バス・レート領域で動作する BIU12 の部分に送出する回路を内蔵する。転送レート領域は、非整数コア：バス・クロック比で発生する「半サイクル」経路中に、データがバスに転送されるのを防ぐ。本開示の発明の別の実施例では、半サイクルの場合に CORE\_C2 の次の発生まで TXFR\_C2 を単純に遅延させることも可能である。この別の実施例では、バス・レート・クロックの立ち上がりエッジの直後に発生する TXFR\_C1 パルスは削除しなければならない。

20

#### 【0015】

バス・レート領域は、アドレスおよびデータ・バスの通常クロック領域である。上記のように、バス・レート領域は、性能上の理由から、コア・レート領域の整数倍遅く、あるいは整数プラス 1 / 2 倍遅くクロックする。バス・レート領域の周波数は、一般に、データ・プロセッサ 10 の位同期ループ (「PLL」) に入力されるシステム・クロック (「SYSCLK」) によって表される。GCLK の特定の低位相は濾波され、制御信号 BUS\_C1 を生成する。GCLK の特定の高位相は濾波され、制御信号 BUS\_C2 を生成する。このように濾波された特定の位相については、図 7 および図 8 を参照して以下で説明する。BIU12 は、バス・レート領域で動作してアドレスおよびデータ・バスから情報を受け、この情報を処理し、アドレスおよびデータ・バスに返送する回路を内蔵する。

30

#### 【0016】

受信レート領域は、コア・レートがバス・クロック・サイクルの開始前に半サイクルしかクロックしない場合を除いて、バス・レート領域の各サイクルで一回クロックする。これらの場合には、RCV\_C2 は、CORE\_C2 パルスと整合できるまで遅延される。BIU12 は、受信レート領域で動作してアドレスおよびデータ・バスからできるだけすぐにデータをサンプリングする回路を内蔵する。ただし、BIU12 は、完全なコア・クロック・サイクルが開始するまで、データをデータ・プロセッサ 10 のコアに送り出さない。

40

#### 【0017】

50

さらに図2において、論理ブロック32は、論理ブロック34の出力から、命令キャッシュ14および／またはデータ・キャッシュ16から、それにANDゲート36の出力から、シングル入力ビットを受ける。論理ブロック32の出力は、マスタ・スレーブ・ラッチ(以下では「ラッチ」という)38の入力と、ラッチ40の入力とに結合される。ラッチ38のマスタ部分は、制御信号COREC1によってクロックされる。ラッチ38のスレーブ部分は、制御信号COREC2によってクロックされる。ラッチ38のスレーブ部分の出力は、論理ブロック34に結合される。ラッチ38については、図3を参照して以下で説明する。ラッチ40のマスタ部分は、制御信号TXFC1によってクロックされる。ラッチ40のスレーブ部分は、制御信号TXFC2によってクロックされる。ラッチ38のスレーブ部分の出力は、論理ブロック34に結合される。

10

#### 【0018】

論理ブロック42は、ラッチ40のスレーブ部分の出力から、アドレス・バスおよび／またはデータ・バスから、それに論理ブロック44の出力から、シングル入力ビットを受ける。論理ブロック42の出力は、ラッチ46の入力と、ラッチ48の入力とに結合される。ラッチ46のマスタ部分は、制御信号BUS\_C1によってクロックされる。ラッチ46のスレーブ部分は、制御信号BUS\_C2によってクロックされる。ラッチ46のスレーブ部分の出力は、論理ブロック50に結合される。論理ブロック50は、シングル・ビットをアドレスおよびデータ・バスに出力する。ラッチ48のマスタ部分は、制御信号RCV\_C1によってクロックされる。ラッチ48のスレーブ部分は、制御信号RCV\_C2によってクロックされる。ラッチ48のスレーブ部分の出力は、論理ブロック44に結合される。また、論理ブロック44の出力は、ANDゲート36の第1入力に結合される。ANDゲート36の第2入力は、制御信号A2/B4を受ける。制御信号A2/B4は、論理ブロック44の出力の第1部分を除く全てをマスクする。この第1部分は、ラッチ48がその出力を論理ブロック44に送り出した後に発生する最初のCORE\_C1およびCORE\_C2パルスと一致する。制御信号A2/B4の生成については、図7を参照して以下で説明する。

20

#### 【0019】

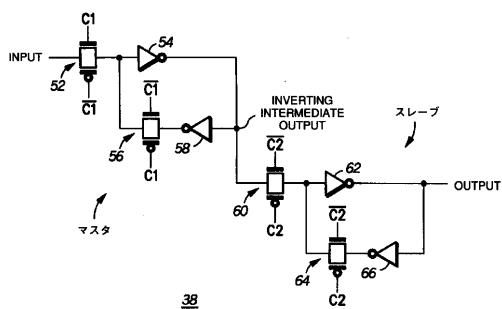

図3は、図2および他の図面に示すマスタ・スレーブ・ラッチ38の回路図を示す。当業者であれば、ラッチ38は、異なるクロック入力を除いて、図2に示す他のラッチと同一であることが理解される。従って、図2では、本発明を理解する上で図面の有用性を汎用化するため、制御信号は「C1」および「C2」と略されている。

30

#### 【0020】

ラッチ38のマスタ部分は、パス・ゲート(pass gate)52の第1端子に結合されたデータ入力を受ける。パス・ゲート52の第2端子は、インバータ54の入力と、パス・ゲート56の第1端子とに接続される。インバータ54の出力は、インバータ58の入力に結合される。インバータ58の出力は、パス・ゲート56の第2端子に接続される。パス・ゲート52のn型デバイスおよびp型デバイスの制御電極は、制御信号C1と、「反転C1」と記された制御信号C1の論理補数とをそれぞれ受ける。パス・ゲート56のp型デバイスおよびn型デバイスの制御電極は、C1および反転C1をそれぞれ受ける。インバータ54の出力は、「INVERTING INTERMEDIATE OUTPUT」と記された中間出力を生成する。この中間出力は、入力の論理補数であり、一つのC1パルス後に出力される。通常コア・レートまたはバス・レート領域では、中間出力は半クロック・サイクル後に通過する。

40

#### 【0021】

ラッチ38のスレーブ部分は、パス・ゲート60の第1端子に結合された中間出力を受ける。パス・ゲート60の第2端子は、インバータ62の入力と、パス・ゲート64の第1端子とに接続される。インバータ62の出力は、インバータ66の入力に結合される。インバータ66の出力は、パス・ゲート64の第2端子に接続される。パス・ゲート60のn型デバイスおよびp型デバイスの制御電極は、制御信号C2と、「反転C2」と記された制御信号C2の論理補数とをそれぞれ受ける。パス・ゲート64のp型デバイスおよび

50

n型デバイスの制御電極は、C2および反転C2をそれぞれ受ける。インバータ62の出力は、「OUTPUT」と記された最終出力を生成する。中間出力は、中間出力の補数であり、一つのC2パルス後に出力される。通常コア・レートまたはバス・レート領域では、入力は、完全なクロック・サイクル後にラッチ38のマスタ部分およびスレーブ部分を通過する。

#### 【0022】

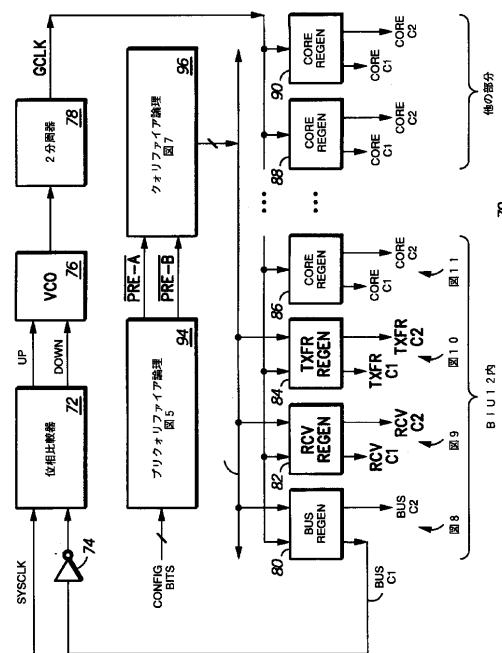

図4は、図2に示すBIU12に入力される制御信号を生成すべく動作可能な位相同期ループ（「PLL」）70を示す。位相比較器72は、インバータ74の出力と、バス・レート領域クロックSYSCLKとを受ける。上記のように、SYSCLKは、同期のためにデータ・プロセッサ10に入力されるアドレスおよびデータ・バス・クロック信号である。位相比較器72は、SYSCLKの各立ち上がりエッジにおいてインバータ74によって出力されるクロック信号の位相を比較する。SYSCLKの位相がインバータ74の出力よりも進む場合、位相比較器72は制御信号UPをアサートする。SYSCLKの位相がインバータ74の出力より遅れる場合、位相比較器72は制御信号DOWNをアサートする。

#### 【0023】

電圧制御発振器（「VCO」）76は、制御信号UPおよびDOWNを受けて、クロック信号GCLKの周波数の2倍の周期クロッキング信号を生成する。上記のように、GCLKは、データ・プロセッサ10全体で分散されるクロッキング信号である。一般に、VCO76は、UPおよびDOWNのアサートによってそれぞれ充電および放電されるノード（図示せず）を内蔵する。このノードの電圧は、出力クロック信号の周波数を制御するために用いられる。一実施例では、この電圧は、リング発振器への一つまたはそれ以上の電源の印加を制御するために用いられる。VCO76の出力は、2分周回路（divide-by-two circuit）78に結合される。2分周回路78は、VCOによって出力されたクロック信号の周波数を2分の1にする。この分周により、GCLKの均等なデューティ・サイクルが保証される（低位相および高位相は長さが等しい）。

#### 【0024】

上記のように、クロック信号GCLKは、データ・プロセッサ全体で分散される。データ・プロセッサ10内のクロック・スキュー（clock skew）を最小限に抑えることを目的として、多数のクロック・リジェネレータ（clock regenerator）用いられ、図2に示す各クラッチからのGCLKをバッファする。一実施例では、約300個のクロック・リジェネレータが各ラッチからのGCLKをバッファする。ただし、全てのラッチが同一時間領域でクロックされるわけではない。本発明の4つの異なる時間領域については、図2を参照して上で説明した。

#### 【0025】

BIU12内には、4種類のクロック・リジェネレータが存在する。各種類の数は、BIU12に複雑性と、アドレスおよびデータ・バスの幅とに依存する。図示のため、各種類のリジェネレータの一つの例を図示する。バス・リジェネレータ（「BUS REGEN」と記される）80は、GCLKからと、QUALIFIER SIGNALSのグループのうちの少なくとも一つから、クロックパルスBUS C1およびBUS C2を生成する。QUALIFIER SIGNALSのグループについて、図7を参照して以下で説明する。一つのバス・リジェネレータ80のBUS C1出力は、インバータ74の入力に結合される。インバータ74の出力は、各クロック領域をSYSCLKと同期させるために位相比較器72によって用いられる。バス・リジェネレータ80については、図8を参照して以下でさらに説明する。受信リジェネレータ（「RCV REGEN」と記される）82は、GCLKからと、QUALIFIER SIGNALSのグループのうち少なくとも一つから、クロック・パルスRCV C1およびRCV C2を生成する。受信リジェネレータ82については、図9を参照して以下でさらに説明する。転送リジェネレータ（「TXFR REGEN」と記される）84は、GCLKからと、QUALIFIER SIGNALSのグループの少なくとも一つから、クロック・パルスTXF

10

20

30

40

50

R C 1 および T X F R C 2 を生成する。転送リジエネレータ 8 4 については、図 10 を参照して以下でさらに説明する。コア・リジエネレータ（「CORE REGEN」と記される）8 6 は、G C L K からクロック・パルス CORE C 1 および CORE C 2 を生成する。コア・リジエネレータ 8 6 については、図 11 を参照して以下でさらに説明する。

#### 【0026】

データ・プロセッサ 10 内のほとんどのクロック・リジエネレータは、非 B I U 回路についてはクロック・パルス CORE C 1 および CORE C 2 を生成する。図 4 は、これらのコア・リジエネレータ（「CORE REGEN」と記される）8 8, 9 0 のうち 2 つを示す。

プリクオリファイア論理ブロック（prequalifier logic block）9 4 は、CORE C 1 および CORE C 2 クロック信号と、入力信号 CONFIG BITS を受けて、制御信号反転 PRE - A および反転 PRE - B を生成する。（エンジニアリング分野では、上線（反転）を用いてアクティブ・ロー信号を表すのが慣習である。）CONFIG BITS により、データ・プロセッサ 10 のユーザは、G C L K の周波数と S Y S C L K の周波数の比率を設定できる。これらは、いくつかの専用入力／出力ピンを介してデータ・プロセッサ 10 に直接入力してもよく、あるいは命令の実行によってユーザにアクセス可能なレジスタに格納してもよい。プリクオリファイア論理ブロック 9 4 はについては、図 5 を参照して以下で説明する。制御信号反転 PRE - A および反転 PRE - B は、クオリファイア論理ブロック 9 6 に結合される。クオリファイア論理ブロック 9 6 は、バス・リジエネレータ 8 0, 受信リジエネレータ 8 2 および転送リジエネレータ 8 4 によって用いられる Q U A L I F I E R S I G N A L S のグループを生成する。

#### 【0027】

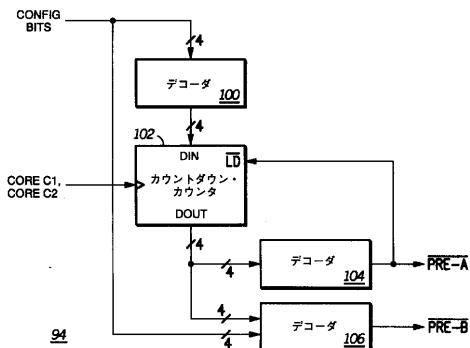

図 5 は、図 4 に示すプリクオリファイア論理ブロック 9 4 のブロック図を示す。第 1 デコーダ・ブロック 100 は、4 つの CONFIG BITS をバイナリ数値に復号する。上記のように、CONFIG BITS は、コアとバス・クロック周波数の比率を指定する。CONFIG BITS が 1 : 1, 2 : 1, 3 : 1, . . . , N : 1 などの整数バス・モードを指定するように設定されると、デコーダ・ブロック 100 はバイナリ形式で数値 N - 1 を出力する。CONFIG BITS が 1.5 : 1, 2.5 : 1, 3.5 : 1, . . . , N + 0.5 : 1 など整数プラス 1 / 2 バス・モードを指定するように設定されると、デコーダ・ブロック 100 はバイナリ形式で数値 2N を出力する。

#### 【0028】

デコーダ・ブロック 100 の復号された出力は、カウントダウン・カウンタ 102 のデータ入力（「DIN」）に結合される。カウントダウン・カウンタ 102 は、そのロード入力（反転 LD）がアサートされたときに復号出力をロードする。カウントダウン・カウンタ 102 は、コアまたは G C L K サイクル毎に 1 数値のレートで、入力数値からゼロまでカウントダウンする。カウントダウン・カウンタ 102 のカレント・カウント値は、D O U T を介して第 2 デコーダ・ブロック 104 と、第 3 デコーダ・ブロック 106 とに絶えず出力される。また、CONFIG BITS は、デコーダ・ブロック 106 に入力される。デコーダ・ブロック 104, 106 は、信号反転 PRE - A および反転 PRE - B をそれぞれ生成する。信号反転 PRE - A は、カウントダウン・カウンタ 102 のロード入力に結合される。

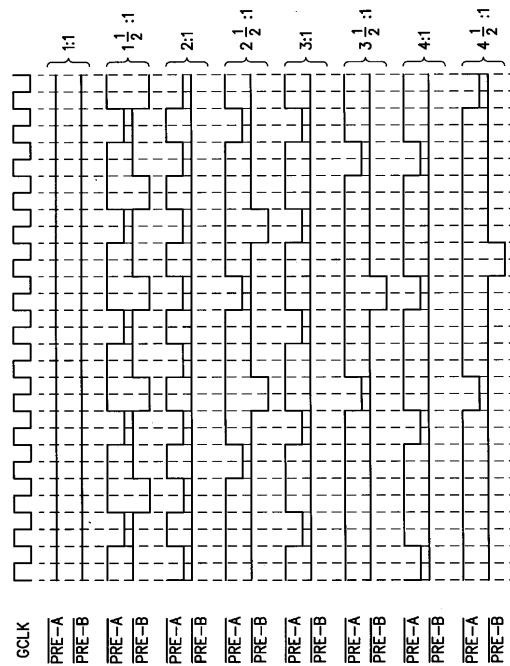

#### 【0029】

図 6 は、図 5 に示すプリクオリファイア論理ブロック 9 4 の動作を示すタイミング図を示す。デコーダ・ブロック 104 は、D O U T がゼロに等しいとき、低論理状態に対応する電圧を反転 PRE - A として出力する。デコーダ・ブロック 104 は、D O U T がゼロ以外の数値に等しいとき、高論理状態に対応する電圧を反転 PRE - A として出力する。反転 PRE - A の低アサートにより、カウントダウン・カウンタ 102 はデコーダ・ブロック 100 によって出力された数値にリセットされ、再びカウントダウンを開始する。その

10

20

30

40

50

ため、反転 P R E - A は、整数バス・モードでは、G C L K の N 倍の周期を有するよう みえ、また整数プラス 1 / 2 バス・モードでは、G C L K の 2 N + 1 倍の周期を有するよ うにみえる。1 : 1 バス・モードの場合、反転 P R E - A は低論理状態のままである。C O N F I G B I T S が整数バス・モードを指定すると、デコーダ・ブロック 1 0 6 は高論理状態に対応する定電圧を反転 P R E - B として出力する。C O N F I G B I T S が整数プラス 1 / 2 バス・モードを指定すると、デコーダ・ブロック 1 0 6 は、反転 P R E - B として可変電圧レベルを出力する。後者の場合、デコーダ・ブロック 1 0 6 は、デコーダ・ブロック 1 0 4 が低論理状態を反転 P R E - A として出力した後、低論理状態に対応する出力を反転 P R E - B の N サイクルとして出力し、ここでコア：バス比は N + 0 . 5 : 1 として定義される。デコーダ・ブロック 1 0 6 は、他の全ての場合で高論理状態に 10 対応する電圧を出力する。

### 【 0 0 3 0 】

本開示の発明の一実施例では、信号反転 P R E - A を特定のサイクル数だけ遅延せずに、カウントダウン・カウンタ 1 0 2 によって出力された数値を復号するほうが有利である。この方式では、より簡単な汎用的な解決方法が得られる。この実施例では、( 1 ) C O N F I G B I T S が 1 . 5 : 1 を指定し、かつカウントダウン・カウンタ 1 0 2 によって出力される数値が 2 に等しいとき、あるいは( 2 ) C O N F I G B I T S が 2 . 5 : 1 を指定し、かつカウントダウン・カウンタ 1 0 2 によって出力される数値が 3 に等しいとき、あるいは( 3 ) C O N F I G B I T S が 3 . 5 : 1 を指定し、かつカウントダウン・カウンタ 1 0 2 によって出力される数値が 4 に等しいとき、あるいは( 4 ) C O N F I G B I T S が 4 . 5 : 1 を指定し、かつカウントダウン・カウンタ 1 0 2 によって出力される数値が 5 に等しいとき、デコード・ブロック 1 0 6 は低論理状態に対応する電圧を反転 P R E - B として出力する。一般に、デコーダ・ブロック 1 0 6 は、C O N F I G B I T S が N + 0 . 5 : 1 を指定し、かつカウントダウン・カウンタ 1 0 2 によって出力される数値が N + 1 に等しいとき、低論理状態に対応する電圧を反転 P R E - B として出力する。 20

### 【 0 0 3 1 】

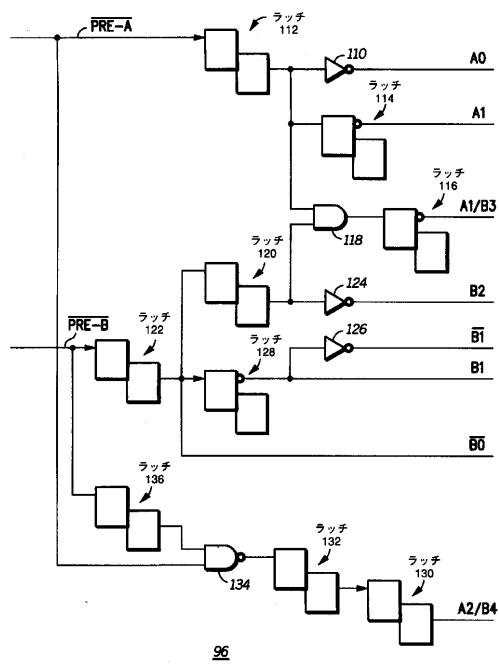

図 7 は、図 4 に示すクオリファイア論理ブロック 9 6 のブロック図を示す。クオリファイア論理ブロック 9 6 は、バス・リジェネレータ 8 0 , 受信リジェネレータ 8 2 および転送リジェネレータ 8 4 によって用いられる Q U A L I F I E R S I G N A L S のグループを生成する。インバータ 1 1 0 の出力は、クオリファイア信号 A 0 を生成する。インバータ 1 1 0 の入力は、ラッチ 1 1 2 のデータ出力に結合される。ラッチ 1 1 2 の入力は、反転 P R E - A を受ける。ラッチ 1 1 4 の反転中間出力は、クオリファイア信号 A 1 を生成する。ラッチ 1 1 4 の入力は、ラッチ 1 1 2 の出力に結合される。ラッチ 1 1 6 の反転中間出力は、クオリファイア信号 A 1 / B 3 を生成する。ラッチ 1 1 6 の入力は、A N D ゲート 1 1 8 の出力に結合される。A N D ゲート 1 1 8 の第 1 入力は、ラッチ 1 1 2 の出力に結合される。A N D ゲート 1 1 8 の第 2 入力は、ラッチ 1 2 0 の出力に結合される。ラッチ 1 2 0 の入力は、ラッチ 1 2 2 の出力に結合される。ラッチ 1 2 2 の入力は、反転 P R E - B を受ける。インバータ 1 2 4 の出力は、クオリファイア信号 B 2 を生成する。インバータ 1 2 4 の入力は、ラッチ 1 2 0 の出力に結合される。インバータ 1 2 6 の出力は、クオリファイア信号反転 B 2 を生成する。インバータ 1 2 6 の入力は、ラッチ 1 2 8 の反転中間出力に結合される。ラッチ 1 2 8 の入力は、ラッチ 1 2 2 の出力に結合される。また、ラッチ 1 2 8 の反転中間出力は、クオリファイア信号 B 1 を生成する。ラッチ 1 2 2 の出力は、クオリファイア信号反転 B 0 を生成する。ラッチ 1 3 0 の出力は、クオリファイア信号 A 2 / B 4 を生成する。ラッチ 1 3 0 の入力は、ラッチ 1 3 2 の出力に結合される。ラッチ 1 3 2 の入力は、N A N D ゲート 1 3 4 の出力に結合される。N A N D ゲート 1 3 4 の第 1 入力は、ラッチ 1 3 6 の出力に結合される。ラッチ 1 3 6 の入力は、反転 P R E - B を受ける。N A N D ゲート 1 3 4 の第 2 入力は、反転 P R E - A を受ける。 30

### 【 0 0 3 2 】

図 8 ないし図 1 1 は、図 4 に示すバス・リジェネレータ 8 0 , 受信リジェネレータ 8 2 , 50

転送リジェネレータ 84 およびコア・リジェネレータ 86 の回路図をそれぞれ示す。当業者であれば、図 8 ないし図 11 に示す回路は、各入力を除いて同一であることが理解される。

### 【0033】

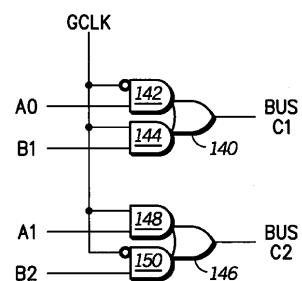

図 8において、OR ゲート 140 の出力は、信号 BUS\_C1 を生成する。OR ゲート 140 の第1入力は、AND ゲート 142 の出力に結合される。OR ゲート 140 の第2入力は、AND ゲート 144 の出力に結合される。AND ゲート 142 の第1および第2入力は、GCLK の論理補数および A0 をそれぞれ受ける。AND ゲート 144 の第1および第2入力は、GCLK および B1 をそれぞれ受ける。OR ゲート 146 の出力は、信号 BUS\_C2 を生成する。OR ゲート 146 の第1入力は、AND ゲート 148 の出力に結合される。OR ゲート 146 の第2入力は、AND ゲート 150 の出力に結合される。AND ゲート 148 の第1および第2入力は、GCLK および A1 をそれぞれ受ける。AND ゲート 150 の第1および第2入力は、GCLK の論理補数および B2 をそれぞれ受ける。

10

### 【0034】

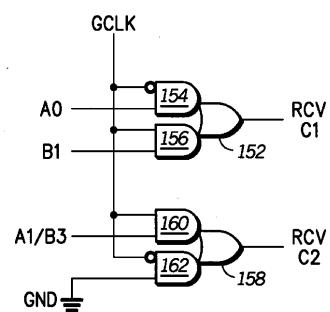

図 9において、OR ゲート 152 の出力は、信号 RCV\_C1 を生成する。OR ゲート 152 の第1入力は、AND ゲート 154 の出力に結合される。OR ゲート 152 の第2入力は、AND ゲート 156 の出力に結合される。AND ゲート 154 の第1および第2入力は、GCLK の論理補数および A0 をそれぞれ受ける。AND ゲート 156 の第1および第2入力は、GCLK および B1 をそれぞれ受ける。OR ゲート 158 の出力は、信号 RCV\_C2 を生成する。OR ゲート 158 の第1入力は、AND ゲート 160 の出力に結合される。OR ゲート 158 の第2入力は、AND ゲート 162 の出力に結合される。AND ゲート 160 の第1および第2入力は、GCLK および A1 / B3 をそれぞれ受ける。AND ゲート 162 の第1および第2入力は、GCLK の論理補数と、低論理状態（「GND」と記される）に対応する電圧レベルとをそれぞれ受ける。

20

### 【0035】

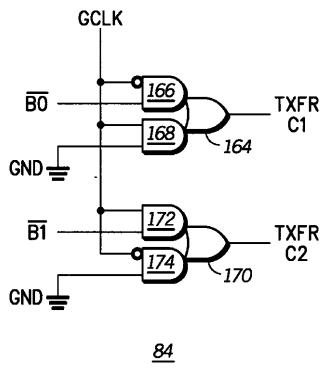

図 10において、OR ゲート 164 の出力は、信号 TXFR\_C1 を生成する。OR ゲート 164 の第1入力は、AND ゲート 166 の出力に結合される。OR ゲート 164 の第2入力は、AND ゲート 168 の出力に結合される。AND ゲート 166 の第1および第2入力は、GCLK の論理補数および反転 B0 をそれぞれ受ける。AND ゲート 168 の第1および第2入力は、GCLK と、低論理状態に対応する電圧レベルとをそれぞれ受ける。OR ゲート 170 の出力は、信号 TXFR\_C2 を生成する。OR ゲート 170 の第1入力は、AND ゲート 172 の出力に結合される。OR ゲート 170 の第2入力は、AND ゲート 174 の出力に結合される。AND ゲート 172 の第1および第2入力は、GCLK および反転 B1 をそれぞれ受ける。AND ゲート 174 の第1および第2入力は、GCLK の論理補数と、低論理状態に対応する電圧レベルとをそれぞれ受ける。

30

### 【0036】

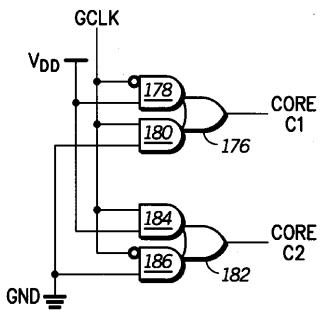

図 11において、OR ゲート 176 の出力は、信号 CORE\_C1 を生成する。OR ゲート 176 の第1入力は、AND ゲート 178 の出力に結合される。OR ゲート 176 の第2入力は、AND ゲート 180 の出力に結合される。AND ゲート 178 の第1および第2入力は、GCLK の論理補数と、高論理状態（「VDD」と記される）に対応する電圧レベルとをそれぞれ受ける。AND ゲート 180 の第1および第2入力は、GCLK と、高論理状態に対応する電圧レベルとをそれぞれ受ける。OR ゲート 182 の出力は、信号 CORE\_C2 を生成する。OR ゲート 182 の第1入力は、AND ゲート 184 の出力に結合される。OR ゲート 182 の第2入力は、AND ゲート 186 の出力に結合される。AND ゲート 184 の第1および第2入力は、GCLK と、高論理状態に対応する電圧レベルとをそれぞれ受ける。AND ゲート 186 の第1および第2入力は、GCLK の論理補数と、高論理状態に対応する電圧レベルとをそれぞれ受ける。コア・リジェネレータ 86 は、データ・プロセッサ 10 におけるクロッキング・スキュームを最小限に抑えるため、バス・リジェネレータ 80 , 受信リジェネレータ 82 および転送リジェネレータ 84 と

40

50

同じ数の論理ゲートを内蔵する。

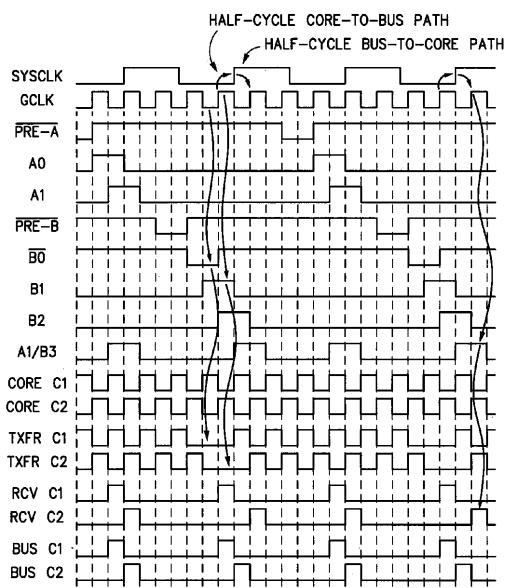

**【0037】**

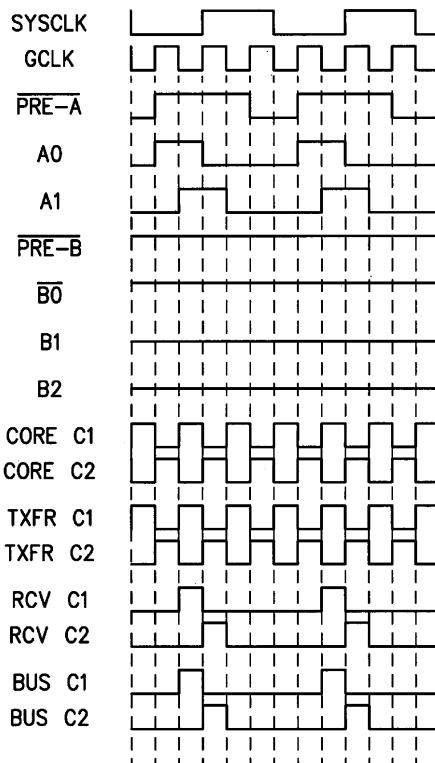

図12は、3:1モードにおける本開示の発明の動作を示すタイミング図を示す。ここで、反転P R E - A , A 0 およびA 1 は、3つのG C L Kサイクルの周期を有する。反転P R E - B , 反転B 0 , B 1 およびB 2 は、全て静的(s t a t i c)である。本開示の発明を明確に説明するため、図12は、特定のC 1 およびC 2 パルスを発生のみを示す。

**【0038】**

上記のように、B I U 1 2 は、コア・レート領域で動作するデータ・プロセッサ10の大半と、バス・レート領域で動作するアドレスおよびデータ・バスとの間でインターフェースとして機能する。ラッチ38および論理ブロック32, 34(図3に図示)は、コア・レート領域においてデータ・プロセッサ10から受けたデータを処理する。C O R E C 1 およびC O R E C 2 は、G C L Kの2位相から生成される。同様に、ラッチ46および論理ブロック42, 50は、バス・レート領域においてアドレスおよびデータ・バスから受けたデータを処理する。B U S C 1 およびB U S C 2 は、A 0 およびA 1 によってそれぞれゲートされたG C L Kの2位相から生成される。図示のように、B U S C 1 およびB U S C 2 は、S Y S C L K立ち上がりエッジにまたがるG C L K長のパルスである。

**【0039】**

しかし、データ・プロセッサ10が有用な仕事を実行するためには、コア・レート領域とバス・レート領域との間でデータを転送できなければならない。ラッチ40は、コア・レート領域からバス・レート領域へのデータ経路を提供する。ラッチ40は、T X F R C 1 およびT X F R C 2 によってクロックされる。同様に、ラッチ48は、バス・レート領域からコア・レート領域へのデータ経路を提供する。ラッチ48は、R C V C 1 およびR C V C 2 によってクロックされる。上記のように、データは、半サイクル経路の発生中に、コア・レート領域とバス・レート領域との間で転送してはならない。転送レート領域および受信レート領域は、他の転送を許可しつつ、これらの転送を阻止する。この整数のコア対バス比では、コア・レート領域とバス・レート領域との間では半サイクル経路はない。従って、T X F R C 1 およびT X F R C 2 は、C O R E C 1 およびC O R E C 2 とそれぞれ同一であり、またR C V C 1 およびR C V C 2 は、B U S C 1 およびB U S C 2 とそれぞれ同一である。

**【0040】**

図13は、3.5:1モードにおける本開示の発明の動作を示すタイミング図を示す。この整数プラス1/2のコア対バス比では、コア・レート領域とバス・レート領域との間で周期的な半サイクル経路が存在する。図示のように、G C L Kの立ち下がりエッジは、一つおきのS Y S C L KサイクルでS Y S C L Kの立ち上がりエッジと整合する。通常、G C L Kの立ち上がりエッジは、S Y S C L Kの立ち上がりエッジとのみ整合する。(例えば、図12を参照。)半サイクル経路では、G C L Kの高位相(C O R E C 2)中にコア・レート領域デバイスによって送り出された信号は、バス・レート領域で動作するデバイスによって、半クロック・サイクルだけ遅れてサンプリングされる。同様に、B U S C 2 中にバス・レート領域デバイスによって送り出された信号は、コア・レート領域で動作するデバイスによって、半クロック・サイクルだけ遅れてサンプリングされる。

**【0041】**

信号伝搬のために許容された半クロック・サイクルでのみ、ラッチからラッチにデータが送り出された場合、データ・プロセッサ10にエラーが生じることがある。一般に、データ・プロセッサ10内の全ての回路は、特定の最少サイクル時間あるいはそれ以上で適正動作するように設計される。介在する論理を介して伝搬するために信号にフル・サイクルが与えられないと、信号は不安定になる可能性がある。このような状況で信号が不安定になるかどうかは、次のラッチに達する前に通過する論理の複雑性に依存する。介在する論理が単純ならば、信号は半サイクルのみで確実に伝搬できる。しかし、介在する論理が複雑ならば、信号は伝搬するために半サイクル以上を必要とすることがある。この場合、信

10

20

30

40

50

号は、動作すべき半クロック・サイクルしか与えられないと、誤った値を報告する。

**【0042】**

コア・レート領域からバス・レート領域へのデータ転送の場合、転送リジェネレータ84(図4に図示)は、半サイクル経路の前に発生する各TXFR C2パルスを飲み込む。TXFR C2をこのように修正することにより、バス・レート領域回路がデータをラッチするのが速すぎるかもしれないと、ラッチ40はデータをラッチ46, 48に送り出さない。図示の実施例では、転送リジェネレータ8は半サイクル経路前に発生する各TXFR C1パルスも飲み込む。従って、論理ブロック32によって出力されるデータは、SYCLKの開始までラッチ40によって捕捉されない。

**【0043】**

バス・レート領域からコア・レート領域へのデータ転送の場合、受信リジェネレータ82(図4に図示)は、半サイクル経路中に発生する各RCV C2パルスを遅延させる。RCV C2をこのように修正することにより、ラッチ38, 40がデータをラッチするのが速すぎるかもしれないと、ラッチ48はデータをラッチ38, 40に送り出さない。RCV C1は、BUS C1と同一であり、そのためラッチ48はバス・レート領域においてバス情報を捕捉できる。

**【0044】**

本発明について特定の実施例とともに説明してきたが、更なる修正や改善は当業者に想起される。例えば、本開示の発明は、データ・プロセッサの一部として説明した。しかし、本開示の発明は、アドレス・バスまたはデータ・バスあるいはスタンドアロン・デバイスとしても構築できる。従って、特許請求の範囲は、2つのデバイス間で動作するデータ同期システムについて記載する。故に、本発明は、特許請求の範囲に定義される発明の精神および範囲から逸脱しない一切のこのような修正を網羅するものとする。

**【図面の簡単な説明】**

**【図1】**本発明により構成されたデータ・プロセッサのブロック図である。

**【図2】**図1に示すバス・インターフェース・ユニットの一部のブロック図である。

**【図3】**図2および他の図面に示すマスター・スレーブ・ラッチの回路図である。

**【図4】**図2に示すバス・インターフェース・ユニットに入力される制御信号を生成すべく動作可能な位相同期ループを示す図である。

**【図5】**図4に示すプリクオリファイア論理ブロックのブロック図である。

**【図6】**図5に示すプリクオリファイアの動作を示すタイミング図である。

**【図7】**図4に示すクオリファイア論理ブロックのブロック図である。

**【図8】**図4に示すバス・リジェネレータを示す回路図である。

**【図9】**図4に示す受信リジェネレータを示す回路図である。

**【図10】**図4に示す転送リジェネレータを示す回路図である。

**【図11】**図4に示すコア・リジェネレータを示す回路図である。

**【図12】**3:1モードにおける本発明の動作を示すタイミング図である。

**【図13】**3.5:1モードにおける本発明の動作を示すタイミング図である。

**【符号の説明】**

10 データ・プロセッサ

12 バス・インターフェース・ユニット(BIU)

14 命令キャッシュ

16 データ・キャッシュ

18 シーケンサ/ディスパッチャ・ユニット

20 固定小数点実行ユニット

22 分岐実行ユニット

24 浮動小数点実行ユニット

26 ロード/ストア実行ユニット

28 リネーム・バッファ

30 アーキテクチュラル・レジスタ・ファイル

10

20

30

40

50

|                               |                        |    |

|-------------------------------|------------------------|----|

| 3 2                           | 論理ブロック                 |    |

| 3 4                           | 論理ブロック                 |    |

| 3 6                           | A N D ゲート              |    |

| 3 8                           | ラッチ                    |    |

| 4 0                           | ラッチ                    |    |

| 4 2                           | 論理ブロック                 |    |

| 4 4                           | 論理ブロック                 |    |

| 4 6                           | ラッチ                    |    |

| 4 8                           | ラッチ                    |    |

| 5 0                           | 論理ブロック                 | 10 |

| 5 2                           | バス・ゲート                 |    |

| 5 4                           | インバータ                  |    |

| 5 6                           | バス・ゲート                 |    |

| 5 8                           | インバータ                  |    |

| 6 0                           | バス・ゲート                 |    |

| 6 2                           | インバータ                  |    |

| 6 4                           | バス・ゲート                 |    |

| 6 6                           | インバータ                  |    |

| 7 0                           | 位相同期ループ(PLL)           |    |

| 7 2                           | 位相比較器                  | 20 |

| 7 4                           | インバータ                  |    |

| 7 6                           | 電圧制御発振器(VCO)           |    |

| 7 8                           | 2分周回路                  |    |

| 8 0                           | バス・リジエネレータ(BUS REGEN)  |    |

| 8 2                           | 受信リジエネレータ(RCV REGEN)   |    |

| 8 4                           | 転送リジエネレータ(TXFR REGEN)  |    |

| 8 6                           | コア・リジエネレータ(CORE REGEN) |    |

| 8 8 , 9 0                     | コア・リジエネレータ(CORE REGEN) |    |

| 9 4                           | プリクオリファイア論理ブロック        |    |

| 9 6                           | クオリファイア論理ブロック          | 30 |

| 1 0 0                         | 第1デコーダ・ブロック            |    |

| 1 0 2                         | カウントダウン・カウンタ           |    |

| 1 0 4                         | 第2デコーダ・ブロック            |    |

| 1 0 6                         | 第3デコーダ・ブロック            |    |

| 1 1 0                         | インバータ                  |    |

| 1 1 2 , 1 1 4 , 1 1 6         | ラッチ                    |    |

| 1 1 8                         | ANDゲート                 |    |

| 1 2 0 , 1 2 2                 | ラッチ                    |    |

| 1 2 4 , 1 2 6                 | インバータ                  |    |

| 1 2 8 , 1 3 0 , 1 3 2 , 1 3 6 | ラッチ                    | 40 |

| 1 3 4                         | NANDゲート                |    |

| 1 4 0 , 1 4 6                 | ORゲート                  |    |

| 1 4 2 , 1 4 4 , 1 4 8 , 1 5 0 | ANDゲート                 |    |

| 1 5 2 , 1 5 8                 | ORゲート                  |    |

| 1 5 4 , 1 5 6 . 1 6 0 , 1 6 2 | ANDゲート                 |    |

| 1 6 4 , 1 7 0                 | ORゲート                  |    |

| 1 6 6 , 1 6 8 , 1 7 2 , 1 7 4 | ANDゲート                 |    |

| 1 7 6 , 1 8 2                 | ORゲート                  |    |

| 1 7 8 , 1 8 0 , 1 8 4 , 1 8 6 | ANDゲート                 |    |

【図1】

10

【図2】

36

【図3】

138

【図4】

70

【図5】

【 図 6 】

【図7】

【 図 8 】

〔 図 9 〕

82

【図10】

84

【図11】

86

【図12】

【図13】

---

フロントページの続き

(56)参考文献 特開平03-154514(JP,A)

特開平07-084668(JP,A)

特開平07-253947(JP,A)

特開昭56-105524(JP,A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

G06F 13/42 340

H03K 19/0175

H04L 7/00

WPI(DIALOG)