(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4559036号

(P4559036)

(45) 発行日 平成22年10月6日(2010.10.6)

(24) 登録日 平成22年7月30日(2010.7.30)

|               |           |

|---------------|-----------|

| (51) Int.Cl.  | F 1       |

| HO 1 L 27/146 | (2006.01) |

| HO 1 L 29/786 | (2006.01) |

| HO 1 L 27/14  | (2006.01) |

| HO 4 N 5/32   | (2006.01) |

| HO 4 N 5/335  | (2006.01) |

| HO 1 L        | 27/14     |

| HO 1 L        | 29/78     |

| HO 1 L        | 27/14     |

| HO 4 N        | 5/32      |

| HO 4 N        | 5/335     |

請求項の数 6 (全 11 頁)

|              |                           |

|--------------|---------------------------|

| (21) 出願番号    | 特願2003-98711(P2003-98711) |

| (22) 出願日     | 平成15年4月2日(2003.4.2)       |

| (65) 公開番号    | 特開2004-6781(P2004-6781A)  |

| (43) 公開日     | 平成16年1月8日(2004.1.8)       |

| 審査請求日        | 平成18年3月29日(2006.3.29)     |

| (31) 優先権主張番号 | 10/115,829                |

| (32) 優先日     | 平成14年4月3日(2002.4.3)       |

| (33) 優先権主張国  | 米国(US)                    |

|           |                                                                                                  |

|-----------|--------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390041542<br>ゼネラル・エレクトリック・カンパニー<br>GENERAL ELECTRIC COMPANY<br>アメリカ合衆国、ニューヨーク州、スケネクタディ、リバーロード、1番 |

| (74) 代理人  | 100137545<br>弁理士 荒川 聰志                                                                           |

| (74) 代理人  | 100105588<br>弁理士 小倉 博                                                                            |

| (74) 代理人  | 100106541<br>弁理士 伊藤 信和                                                                           |

最終頁に続く

(54) 【発明の名称】撮影アレイ及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板(20)と、前記基板(20)の上に配置されたフォトセンサアレイ(22)と、前記フォトセンサアレイ(22)の上面に配置され、放射線を吸収して光学光子を発生するX線シンチレータとを備え、

前記フォトセンサアレイ(22)は前記X線シンチレータから光の供給を受け、供給された光に対応する電気信号を発生し、

前記フォトセンサアレイ(22)は、

ソース電極(50)と、ドレイン電極(52)と、ゲート電極(62)と、TFT誘電体層(64)と、TFT半導体層(66)と、前記ソース電極(50)又は前記ドレイン電極(52)と、前記TFT半導体層(66)との間に配置されたn型不純物添加のa-Si層(58)とを具備するトップゲート薄膜トランジスタ(TFT)(28)と、

第1の電極(54)と、前記ゲート電極と同一平面にある第2の電極(72)と、コンデンサ誘電体(70)とを具備し、前記コンデンサ誘電体は前記TFT誘電体層と同一平面にあるコンデンサ誘電体層(74)と、前記TFT半導体層と同一平面にあるコンデンサ半導体層(76)と、前記n型不純物添加のa-Si層と同一平面にあるコンデンサa-Si層とを具備するコンデンサ(68)と、

前記コンデンサ(68)に電気的に結合されたフォトダイオード(78)と、

を具備し、

前記ソース電極(50)及び前記ドレイン電極(52)が、第1の金属層(56)から形

10

20

成され、

前記 T F T 半導体層 ( 6 6 ) が、前記 n 型不純物添加の a - S i 層 ( 5 8 ) 、前記ソース電極 ( 5 0 ) 及び前記ドレイン電極 ( 5 2 ) の上に形成された半導体材料層 ( 9 0 ) から形成され、

前記 T F T 誘電体層 ( 6 4 ) が、前記半導体材料層 ( 9 0 ) の上に形成された誘電体層 ( 9 2 ) から形成され、

前記ゲート電極 ( 6 2 ) が、前記誘電体層 ( 9 2 ) の上に形成された第 2 の金属層 ( 9 4 ) から形成され、

前記 T F T 半導体層 ( 6 6 ) 、前記 T F T 誘電体層 ( 6 4 ) 及び前記ゲート電極 ( 6 2 ) は、前記半導体材料層 ( 9 0 ) 、前記誘電体層 ( 9 2 ) 及び前記第 2 の金属層 ( 9 4 ) が

10

、前記第 1 の金属層 ( 5 6 ) に至るまでエッチングされることによりパターン形成され、

前記ゲート電極 ( 6 2 ) が前記 X 線シンチレータから前記 n 型不純物添加の a - S i 層 ( 5 8 ) へ入射する入射光を有効に阻止する放射線検出器 ( 1 8 ) 。

【請求項 2】

前記第 2 の電極 ( 7 2 ) が前記 X 線シンチレータから前記コンデンサ a - S i 層へ入射する入射光を有効に阻止する請求項 1 記載の放射線検出器 ( 1 8 ) 。

【請求項 3】

前記薄膜トランジスタ ( T F T ) ( 2 8 ) は、前記ソース電極 ( 5 0 ) に電気的に結合されたソースビア ( 8 4 ) と、前記フォトダイオード ( 7 8 ) に電気的に結合された共通ビア ( 8 2 ) とを更に具備する請求項 2 記載の放射線検出器 ( 1 8 ) 。

20

【請求項 4】

前記ドレイン電極 ( 5 2 ) とデータ線 ( 3 0 ) は一体に形成され、前記ゲート電極 ( 6 2 ) と走査線 ( 3 2 ) は一体に形成され、前記共通ビア ( 8 2 ) と共通線 ( 4 0 ) は一体に形成されている請求項 3 記載の放射線検出器 ( 1 8 ) 。

【請求項 5】

前記ソース電極 ( 5 0 ) 、前記ドレイン電極 ( 5 2 ) 及び前記コンデンサの第 1 の電極 ( 5 4 ) はクロム材料から形成され、前記コンデンサ誘電体層 ( 7 4 ) 及び前記 T F T 誘電体層 ( 6 4 ) は窒化珪素から形成され、前記コンデンサ半導体層 ( 7 6 ) 及び前記 T F T 半導体層 ( 6 6 ) は真性アモルファスシリコンから形成され、前記コンデンサ a - S i 層 ( 5 8 ) 及び前記 n 型不純物添加の a - S i 層は n 型不純物添加アモルファスシリコンから形成されている請求項 1 記載の放射線検出器 ( 1 8 ) 。

30

【請求項 6】

前記コンデンサ a - S i 層 ( 5 8 ) 及び前記 n 型不純物添加の a - S i 層は、それぞれ、約 4 0 0 オングストローム ( ) の厚さであり、前記コンデンサ半導体層 ( 7 6 ) 及び前記 T F T 半導体層 ( 6 6 ) は、それぞれ、約 5 0 0 オングストローム ( ) の厚さであり、前記 T F T 誘電体層 ( 6 4 ) 及び前記コンデンサ誘電体層 ( 7 4 ) は、それぞれ、約 2 5 0 0 オングストローム ( ) の厚さである請求項 1 記載の放射線検出器 ( 1 8 ) 。

【発明の詳細な説明】

【 0 0 0 1 】

【発明の属する技術分野】

40

本発明は一般に撮影アレイに関し、特に撮影アレイの画素構造に関する。

【 0 0 0 2 】

【発明の背景】

撮影アレイは、通常、シンチレーション媒体に結合されたフォトセンサアレイを含む。シンチレータで吸収された放射線は光学光子を発生し、それらの光子がフォトダイオードなどのフォトセンサに入射する。光子はフォトセンサで吸収され、入射光子束に対応する電気信号が発生される。フォトセンサの製造においては、a - S i : H の光電特性が好都合であり且つフォトセンサなどのデバイスを製造するのが相対的に容易であるという理由により、一般に水素化アモルファスシリコン ( a - S i : H ) が使用されている。具体的には、フォトダイオードなどの感光素子を薄膜トランジスタ ( T F T ) などの必要な制御素

50

子又はスイッチング素子と関連させて相対的に大きなアレイとして形成することができる。放射線検出器及びディスプレイアレイは、通常、大きな基板の上に製造され、基板上には TFT、アドレス線、コンデンサ、及びフォトセンサなどのデバイスのような多数の構成要素が導電性材料、半導体材料及び絶縁材料の蒸着及びパターン形成によって形成される。

#### 【0003】

そのような TFT アレイを製造するための少なくとも 1 つの周知の方法は、通常、ボトムゲート TFT と、データアドレス線及び走査アドレス線とを製造することを含む。周知のいくつかのボトムゲート TFT においては、ボトムゲート金属がチャネル領域を遮蔽している。すなわち、ボトムゲート金属はバックライトからの光を阻止する光阻止素子として作用する。光子は TFT に望ましくない漏れを発生させる可能性があるため、光阻止層を設けることが望ましい。例えば、デジタル X 線パネルでは、光はデバイスの上面に蒸着されたシンチレータから発生され、従って、TFT 領域は光子に直接さらされる。従って、TFT チャネル領域を望ましくない光から遮蔽するために、追加のフォトリソグラフィレベルを必要とする追加の光阻止層が必要である。

10

#### 【特許文献 1】

米国特許第 6 4 6 2 8 0 2 号

#### 【0004】

#### 【発明の概要】

1 つの面においては、放射線検出器が提供される。放射線検出器は、ソース電極と、ドレイン電極と、ゲート電極と、TFT 誘電体層と、TFT 半導体層と、TFT 真性アモルファスシリコン (a-Si) 層とを含むトップゲート薄膜トランジスタ (TFT) を含む。放射線検出器は、第 1 の電極と、ゲート電極とほぼ共面である第 2 の電極と、コンデンサ誘電体とを含むコンデンサを更に含み、コンデンサ誘電体は、TFT 誘電体層とほぼ共面であるコンデンサ誘電体層と、TFT 半導体層とほぼ共面であるコンデンサ半導体層と、TFT a - Si 層とほぼ共面であるコンデンサ a - Si 層とを含む。

20

#### 【0005】

別の面においては、放射線検出器を製造する方法が提供される。方法は、ソース電極と、ドレイン電極と、ゲート電極と、TFT 誘電体層と、TFT 半導体層と、a - Si 層とを含むトップゲート薄膜トランジスタ (TFT) を形成することと、第 1 の電極と、ゲート電極とほぼ共面である第 2 の電極と、コンデンサ誘電体とを含み、コンデンサ誘電体は TFT 誘電体層とほぼ共面であるコンデンサ誘電体層と、TFT 半導体層とほぼ共面であるコンデンサ半導体層と、TFT a - Si 層とほぼ共面であるコンデンサ a - Si 層とを具備するようなコンデンサを形成することとを含む。

30

#### 【0006】

更に別の面においては、放射線源と、放射線検出器とを含む撮影システムが提供される。放射線検出器は、ソース電極と、ドレイン電極と、ゲート電極と、TFT 誘電体層と、TFT 半導体層と、TFT 真性アモルファスシリコン (a-Si) 層とを含むトップゲート薄膜トランジスタ (TFT) を含む。放射線検出器は、第 1 の電極と、ゲート電極とほぼ共面である第 2 の電極と、コンデンサ誘電体とを含むコンデンサを更に含み、コンデンサ誘電体は、TFT 誘電体層とほぼ共面であるコンデンサ誘電体層と、TFT 半導体層とほぼ共面であるコンデンサ半導体層と、TFT a - Si 層とほぼ共面であるコンデンサ a - Si 層とを含む。

40

#### 【0007】

更に別の面においては、放射線検出器を製造する方法が提供される。方法は、コンデンサの第 2 の電極とゲート電極を 1 回の処理工程で形成することと、コンデンサ誘電体と TFT 誘電体層を 1 回の処理工程で形成することと、コンデンサ半導体層と TFT 半導体層を 1 回の処理工程で形成することとを含む。

#### 【0008】

#### 【発明の実施の形態】

50

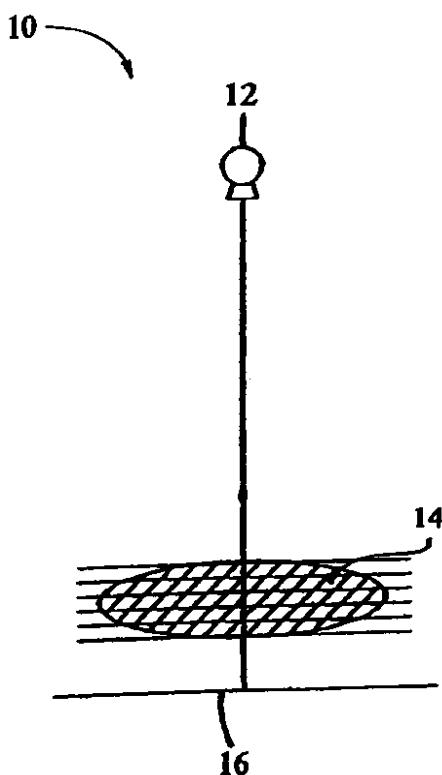

図1は、撮影システム10の概略図である。一実施例では、撮影システム10は、以下に説明する放射線検出器が組み込まれた、ウィスコンシン州ミルウォーキーのGeneral Electric CorporationのGE Medical Systemsビジネスから市販されているSennovision 2000D（商標）などの医療用撮影システムであるが、それには限定されない。撮影システム10は、円錐形ビームを投射する放射線源12を含む。一実施例においては、放射線源12はX線源12であり、円錐形ビームはX線ビームである。X線ビームは物体14、すなわち、患者などの撮影されるべき物体を通過する。X線ビームは物体14により減衰された後に、放射線検出器16に入射する。

【0009】

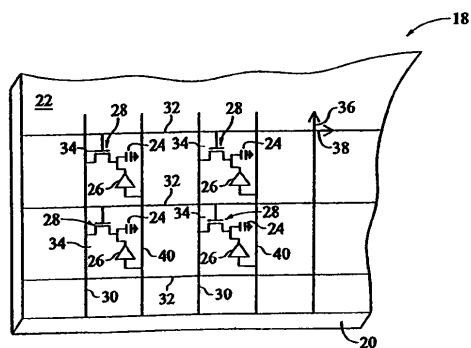

図2は、撮影システム10（図1に示す）と共に使用できる放射線検出器18を示す。放射線検出器18は基板20を含み、基板20の上に画素アレイ22（フォトセンサアレイと呼ばれることがある）が配置されている。フォトセンサアレイ22はコンデンサ24、フォトダイオード26及びTFTなどのスイッチングデバイス28のような複数の電子素子を含む。TFT28は画素アレイ22の上に配置され、対応する1つのコンデンサ24と1つのフォトダイオード26を対応するデータ線30に選択的に結合する。フォトセンサアレイ22は、複数の個別の画素34をアドレス指定するための複数の走査線32を更に含む。データ線30は画素アレイ22の第1の軸36に沿って方向を定められており、走査線32は画素アレイ22の第2の軸38に沿って方向を定められている。画素アレイ22の第1の軸36と第2の軸38は互いにほぼ垂直に配置されている。

【0010】

図2では、図面をわかりやすくするために、フォトセンサアレイ22に沿って延出するデータ線30、走査線32及び共通線40は数本ずつしか示されていない。データ線30、走査線32及び共通線40は、フォトセンサアレイ22の個々の画素34を1本のデータ線30、1本の走査線32及び1本の共通線40によりアドレス指定可能であるように、行と列を成して配列されている。一実施例では、データ線30、走査線32及び共通線40はモリブデン、クロム及び/又はアルミニウムなどの導電性材料を含む。コンデンサ24はフォトダイオード26に電気的に接触し、TFT28を介してデータ線30に電気的に結合されている。フォトダイオード26は、入射する光子に応答して、検出された入射光に対応する電気信号を発生するアレイ22の活性部分を含む。X線エネルギーは、フォトダイオード26の表面付近に配置されたヨウ化セシウムなどの蛍光物質の層（図示せず）を通過することにより、可視光エネルギーに変換される。コンデンサ24はフォトダイオード26で発生された電荷を蓄積し、走査線32がアドレス指定されたときに、蓄積されたこの電荷をTFT28を介して放電する。

【0011】

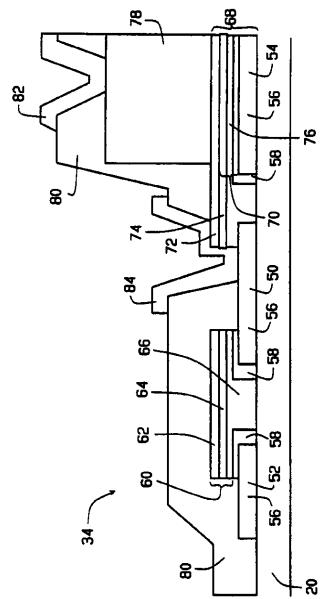

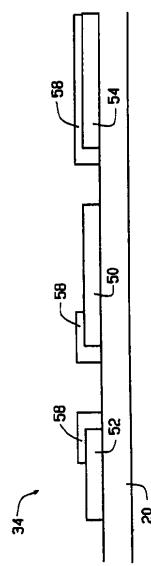

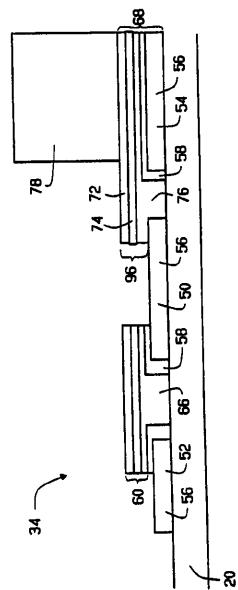

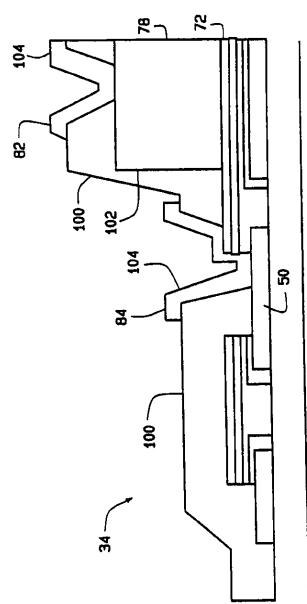

図3は、基板20の上に形成された画素34の一部の横断面図である。一実施例では、ここで説明する全ての半導体層及び誘電体層はプラズマ化学気相成長（PECVD）により蒸着される。画素34は、基板20の表面全体に延在する第1の金属層56から形成されるソース電極50、ドレイン電極52及び第1のコンデンサ電極54を含む。第1の金属層56は、ドレイン電極52とデータ線30（図2に示す）が一体に形成され、且つソース電極50、ドレイン電極52及び第1のコンデンサ電極54がほぼ等しい厚さになるよう形成される。ソース電極50とドレイン電極52の上及びその間と、第1のコンデンサ電極54の上及びそれに隣接する領域にn型不純物添加真性a-Si層58が形成される。ここで使用する用語「形成される」は、パターン形成、マスキング、蒸着及びエッチングを含む画素34の各素子を製造するための工程を含むが、それらには限定されない。

【0012】

a-Si層58の上及びその間と、基板20の上にTFTスタック60が形成される。ここで使用する用語「TFTスタック」は、真性アモルファシリコンなどのTFT半導体材料層66の表面上に延在するTFT誘電体層64の表面に沿って延在するTFTゲート電極62を表す。一実施例では、ゲート電極62は走査線32（図2に示す）と一体に形成される。蓄積コンデンサ68は第1の蓄積コンデンサ電極54と、コンデンサ誘電体7

10

20

30

40

50

0と、コンデンサ誘電体層74の表面に沿って延在する第2の蓄積コンデンサ電極72とを含む。一実施例においては、コンデンサ誘電体70は、n型不純物添加真性a-Si層58の表面に沿って延在する、真性アモルファスシリコンなどのコンデンサ半導体材料層76の表面に沿って延在するコンデンサ誘電体層74を含み、a-Si層58は第1のコンデンサ電極54の表面に沿って延在すると共に、第1のコンデンサ電極54に隣接して延在している。別の実施例では、コンデンサ誘電体70は、真性アモルファスシリコンなどの半導体材料層76の表面に沿って延在するコンデンサ誘電体層74を含む。

【0013】

第2のコンデンサ電極72の上にダイオードスタック78が形成される。一実施例では、ダイオードスタック78はPINダイオード(図示せず)を含む。PINダイオードは、n+型材料の層の上に蒸着された真性a-Siの層の上に蒸着されるp+型材料の層を含む。ダイオードスタック78と、ゲート電極62、ソース電極50、ドレイン電極52、第2のコンデンサ電極72及び基板20の露出部分の上にパッシベーション層80が形成される。共通ビア82がダイオードスタック78に電気的に接続され且つソースビア84がソース電極50及び第2のコンデンサ電極72に電気的に接続されるように、共通ビア82とソースビア84は形成される。

【0014】

図4及び図5は、それぞれ、初期製造段階と、それに続く第1の製造段階における図3に示す画素34の一部の横断面図である。半導体層及び誘電体層はプラズマエンハンスト化学気相成長(PECVD)により蒸着される。

【0015】

一実施例では、第1の金属層56は基板20の上に1回のメタライゼーション工程により蒸着される。メタライゼーション中、金属材料はスパッタリングにより蒸着されるか、又は金属材料の薄い層を蒸着することにより蒸着される。あるいは、スパッタリング又は蒸着以外の方法により金属材料が蒸着される。第1の金属層56はアルミニウム、クロム及び/又はモリブデンを含むが、それらには限定されない。第1の金属層56は、ソース電極50、ドレイン電極52及び第1のコンデンサ電極54を露出させるためにパターン形成され且つエッチングされる。パターン形成工程はフォトレジストを蒸着させ、所望のパターンに従ってフォトレジストを露出させ、フォトレジストを処理してその複数の部分を除去し、所望の寸法に対応する選択されたパターンを有するマスクを残すことを含むが、それらには限定されない。

【0016】

一実施例では、ソース電極50、ドレイン電極52及び第1のコンデンサ電極54の上にn型不純物添加a-Si層58が蒸着される。ほぼ真性のa-Si半導体材料層66(図3に示す)を蒸着させる前に、n型不純物添加a-Si層58をパターン形成し且つエッチングする。n型不純物添加a-Si層58は半導体材料層66への所望の電子注入を促進すると共に、望ましくないホール注入を抑制する。一実施例では、a-Si層58の厚さは約100オングストローム( )から約3000である。別の実施例においては、a-Si層58は約400の厚さである。更に別の実施例では、a-Si層58は約200から約600の厚さである。

【0017】

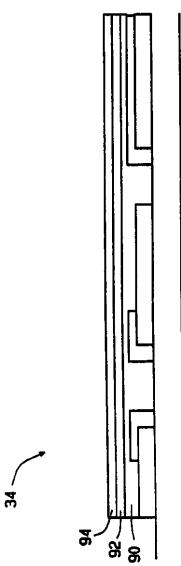

図6及び図7は、それぞれ、第2の製造段階と、続く第3の製造段階の間の図3に示す画素34の一部の横断面図である。a-Si層58の上に半導体材料層90が蒸着される。半導体材料層90はこの時点ではエッチングされない。一実施例では、半導体材料層90の厚さは約100から約3000である。別の実施例においては、半導体材料層90は約500の厚さである。さらに別の実施例では、半導体材料層90は約300から約700の厚さである。半導体材料層90は真性アモルファスシリコンを含むが、それに限定されない。

【0018】

半導体材料層90の上に誘電体層92が蒸着される。誘電体層92はこの時点ではエッチ

10

20

30

40

50

ングされない。一実施例では、誘電体層 92 の厚さは約 1000 から約 4000 である。別の実施例においては、誘電体層 92 は約 2500 の厚さである。さらに別の実施例では、誘電体層 92 は約 1500 から約 3500 の厚さである。誘電体層 92 は SiN を含むが、それに限定されない。

【0019】

誘電体層 92 の上に第 2 の金属層 94 が蒸着される。一実施例では、第 2 の金属層 94 の厚さは約 500 から約 5000 である。別の実施例においては、第 2 の金属層 94 は約 2500 の厚さである。さらに別の実施例では、第 2 の金属層 94 は約 1500 から約 3500 の厚さである。第 2 の金属層 94 はモリブデン、アルミニウム及び/又はクロムを含むが、それらには限定されない。

10

【0020】

第 2 のコンデンサ電極 72 の上に、パターン形成工程を行なうことなくダイオードスタック 78 が蒸着される。一実施例では、ダイオードスタック 78 は p+ 型層と、ほぼ真性の層と、n+ 型 a-Si 層とを含む。別の実施例においては、第 4 の透明導電性トップコンタクト層（図示せず）がダイオードスタック 78 の一部となっている。一実施例では、ダイオードトップコンタクトは酸化インジウムスズ（ITO）などの透明導体を含むが、それに限定されない。ダイオードスタック 78 はパターン形成され且つエッチングされる。ダイオードトップコンタクトをまずウェットエッチングするか、あるいはダイオードトップコンタクトをドライエッチングし、その後に、ダイオードスタック 78 をドライエッチングするときに、同じマスクを使用しても良い。あるいは、ダイオードスタック 78 より小さいダイオードトップコンタクトを規定するために 2 つの別個のマスキング工程を使用することも可能であり、その後にダイオードスタック 78 をパターン形成し、エッチングする。

20

【0021】

半導体材料層 90、誘電体層 92 及び第 2 の金属層 94 は、TFT スタック 60 及び蓄積コンデンサ 68 の一部 96 を形成するためにパターン形成され、エッチングされる。エッチング工程は、第 1 の金属層 56 が接触されたときに停止する。一実施例では、TFT スタック 60 は、第 2 のコンデンサ電極 72 とほぼ共面であり（すなわち、同一平面上にある）且つ同じメタライゼーションから同じ処理工程で形成される TFT ゲート電極 62 と、コンデンサ誘電体層 74 とほぼ共面であり且つ同じ蒸着層から同じ処理工程で形成される TFT 誘電体層 64 と、半導体材料層 76 とほぼ共面であり且つ同じ半導体材料から同じ処理工程で形成される TFT 半導体材料層 66 とを含む。一実施例では、ゲート電極 62 は活性 TFT 領域から光を阻止することを容易にする。

30

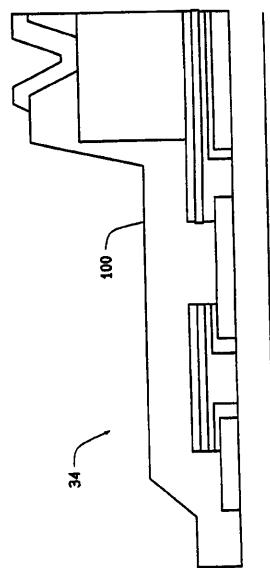

【0022】

図 8 及び図 9 は、それぞれ、第 4 の製造段階と、続く第 5 の製造段階の間の図 3 に示す画素 34 の一部の横断面図である。製造中、画素 34 の全面にパッシベーション層 100 が蒸着される。パッシベーション層 100 は、ダイオードスタック 78、第 2 のコンデンサ電極 72 及びソース電極 50 を露出させるためにエッチングされる。一実施例では、パッシベーション層 100 の厚さは約 0.5 ミクロン (μ) から約 1.5 μ である。別の実施例においては、パッシベーション層 100 は約 1.0 μ の厚さである。更に別の実施例では、パッシベーション層 100 は約 0.8 μ から約 1.2 μ の厚さである。パッシベーション層 100 は窒化珪素及び酸化珪素を含むが、それらには限定されない。パッシベーション層 100 は、これ以降の処理における機械的損傷及び化学的損傷から複数のダイオード側壁 102 を保護することを容易にする。パッシベーション層 100 はエッチングされ、画素 34 の上に第 3 の金属層 104 が蒸着されて、共通ビア 82 及びソーススピア 84 を形成する。共通ビア 82 及びソーススピア 84 は、パッシベーション層 100 の下方に位置する素子に対して電気的接触を成立させることができるようにパッシベーション層 100 の一部を貫通する孔を設けるために 1 回のエッチング工程で形成される（すなわち、共通ビア 82 及びソーススピア 84 は全ての側面で共通するパッシベーション層 100 の残りの部分により包囲されている）。最後に、アレイ 18（図 2 に示す）の 1 つの縁部で走査線 32

40

50

(図2に示す)、共通線40(図2に示す)及びデータ線30(図2に示す)に対するコンタクトパッドを露出させるために、画素34の上にバリア誘電体層(図示せず)が蒸着され、パターン形成され、エッチングされる。バリア誘電体層は窒化珪素を含んでいて良いが、それには限定されない。

【0023】

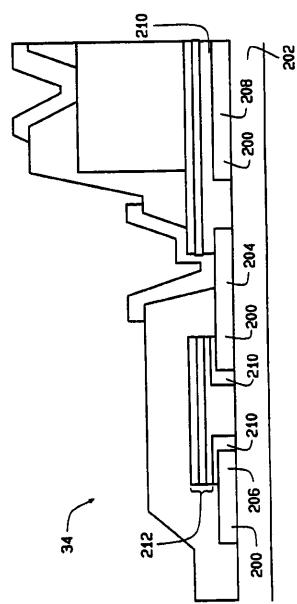

図10は、放射線検出器の画素34の一部の別の実施例の横断面図である。半導体層及び誘電体層はプラズマエンハンスト化学気相成長(PEDCVD)により蒸着される。一実施例では、基板202の上に1回のマスキング工程により酸化インジウムスズ(ITO)層200が蒸着される。一実施例では、オームコンタクトを形成するためにn+型a-Siの薄い層が使用される。オームコンタクトは、コンタクトの特性自体により確定されるのではなく、半導体を通過する電荷搬送により確定される速度で電荷担体を半導体に供給することを容易にし、従って、電流はコンタクトの導電率ではなく、半導体の導電率により制限されることになる。ソース電極204、ドレイン電極206及び第1のコンデンサ電極208を露出させるために、ITO層200はパターン形成され、エッチングされる。ソース電極204及びドレイン電極206は、a-Si層を蒸着する前にフォスフィンプラズマなどのシリコンドーパント(図示せず)によって選択的に処理される。ただし、シリコンドーパントはフォスフィンプラズマには限定されない。シリコンドーパントはソース電極204及びドレイン電極206と反応して、ソース電極204及びドレイン電極206の表面にリン物質210を選択的に取り込み、それにより、TFT28(図2に示す)の電気的活動を変化させると共に、ソース電極204とドレイン電極206との間のオームコンタクトを改善する。

【0024】

一実施例では、画素34をここで説明した処理工程により製造でき、活性TFT領域の上面からの入射光を有效地に阻止することができる。この種の用途においては、主な光の供給源はアレイ22の上面にあるX線シンチレータである。更に、画素34は次のような改善点を含む。TFT構造は十分にパッシベートされたバックチャネルを有するために、性能の改善を容易に実現できる。画素34は、典型的なa-SiPINダイオードの自己キャパシタンスの蓄積容量の約3倍までの蓄積容量を有するコンデンサ68を更に含む。走査線とデータ線の交差箇所にある誘電体は、ダイオード側壁102をパッシベートすると共に、交差キャパシタンス及び交差電荷トラッピングを減少させる目的でも使用される厚い誘電体である。ダイオードパッシベーション誘電体はパッシベーション機能を示すために厚く且つ最適化することができ、更にレベル間誘電体としても機能できる。FETサンドイッチ構造(真性Si、ゲート誘電体、ゲート金属)及びダイオードPIN層を、間にパターン形成工程または洗浄工程を挟まずに、順次蒸着することが可能である。厚いダイオードパッシベーション層はダイオード側壁102における共通電極バスステップを柔軟にする。ダイオードアイランドのためのボトムコンタクト金属エッチストップは走査線及びデータ線に対してアレイ縁部に至る抵抗の低い経路を規定するために必要とされないため、Crなどの薄い金属であって良い。クロムなどの薄い金属を使用することで、従来の縮小マスク処理で使用されていたCr/Mo/Crゲート金属などのより厚く、より複雑なメタライゼーションは不要になる。データ線30及び共通ビア82を形成する第3の金属層104はTFTのソース-ドレイン間隙を形成しないために厚くて良く、それにより、データ線30の抵抗を容易に低減することができる。最後に、画素34の配線を画素34の最上面に形成できるので、修理及び再加工が簡単になる。

【0025】

本発明を様々な特定の実施例によって説明したが、特許請求の範囲の趣旨の範囲内で変形を伴って本発明を実施できることは当業者には了承されるであろう。

【図面の簡単な説明】

【図1】 撮影システムの概略図。

【図2】 フォトセンサアレイにおける典型的な画素の概略図。

【図3】 放射線検出器の1つの画素の一部の横断面図。

10

20

30

40

50

【図4】 初期製造段階の間の図3に示す画素の一部の横断面図。

【図5】 続く第1の製造段階の間の図3に示す画素の一部の横断面図。

【図6】 続く第2の製造段階の間の図3に示す画素の一部の横断面図。

【図7】 続く第3の製造段階の間の図3に示す画素の一部の横断面図。

【図8】 続く第4の製造段階の間の図3に示す画素の一部の横断面図。

【図9】 続く第5の製造段階の間の図3に示す画素の一部の横断面図。

【図10】 放射線検出器の一部の別の実施例の横断面図。

## 【符号の説明】

18...放射線検出器、20...基板、28...薄膜トランジスタ(TFT)、30...データ線、32...走査線、40...共通線、50...ソース電極、52...ドレイン電極、54...第1のコンデンサ電極、58...真性a-Si層、60...TFTスタック、62...TFTゲート電極、64...TFT誘電体層、68...蓄積コンデンサ、70...コンデンサ誘電体、72...第2の蓄積コンデンサ電極、74...コンデンサ誘電体層、76...コンデンサ半導体材料層、78...ダイオードスタック、80...パッシベーション層、82...共通ビア、84...ソースビア

10

( 1 )

〔 図 2 〕

【 図 3 】

〔 四 4 〕

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 チー・アン・リー

アメリカ合衆国、ニューヨーク州、ニスカユナ、フォックス・ヒル・ドライブ、2186番

(72)発明者 ジョージ・エドワード・ポッシン

アメリカ合衆国、ニューヨーク州、ニスカユナ、アルゴンキン・ロード、2361番

審査官 柴山 将隆

(56)参考文献 特開2000-241557(JP,A)

特開平10-163463(JP,A)

特開2002-033331(JP,A)

特開平07-221279(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/146

H01L 27/14

H01L 29/786

H04N 5/32

H04N 5/335