### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2014/107301 A1

(43) International Publication Date 10 July 2014 (10.07.2014)

(21) International Application Number:

PCT/US2013/075672

(22) International Filing Date:

17 December 2013 (17.12.2013)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

13/722,189 20 December 2012 (20.12.2012)

US

- (71) Applicant: INVENSAS CORPORATION [US/US]; 3025 Orchard Parkway, San Jose, CA 95134 (US).

- (72) Inventors: HABA, Belgacem; 19487 Miller Court, Saratoga, CA 95070 (US). MOHAMMED, Ilyas; 2377 Bohannon Drive, Santa Clara, CA 95050 (US). CASKEY, Terrence; 3025 Orchard Parkway, San Jose, CA 95134 (US). CO, Reynaldo; 3025 Orchard Parkway, San Jose, CA 95134 (US). CHAU, Ellis; 3025 Orchard Parkway, San Jose, CA 95134 (US).

- (74) Agents: ZONERAICH, Davy et al.; Lerner, David, Littenberg, Krumholz & Mentlik, LLP, 600 South Avenue West, Westfield, New Jersey 07090 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM,

AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

### **Declarations under Rule 4.17:**

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

#### Published:

with international search report (Art. 21(3))

(54) Title: STRUCTURE FOR MICROELECTRONIC PACKAGING WITH ENCAPSULATED BOND ELEMENTS

(57) Abstract: A structure (10) may include bond elements (24) having bases joined to conductive elements (18) at a first portion of a first surface and end surfaces remote from the substrate (12). A dielectric encapsulation element (40) may overlie and extend from the first portion and fill spaces between the bond elements (24) to separate the bond elements (24) from one another. The encapsulation element (40) has a third surface facing away from the first surface. Unencapsulated portions of the bond elements (24) are defined by at least portions of the end surfaces uncovered by the encapsulation element at the third surface. The encapsulation element (40) at least partially defines a second portion (210) of the first surface that is other than the first portion and has an area sized to accommodate an entire area of a microelectronic element (602). Some conductive elements (18) are at the second portion and configured for connection with such microelectronic element (602).

# STRUCTURE FOR MICROELECTRONIC PACKAGING WITH ENCAPSULATED BOND ELEMENTS

CROSS-REFERENCE TO RELATED APPLICATIONS.

[0001] The present application is a continuation of U.S. Application No. 13/722,189, filed on December 20, 2012, the disclosure of which is hereby incorporated herein by reference.

FIELD OF THE INVENTION

[0002] The present invention relates to structures for microelectronic packaging.

BACKGROUND OF THE INVENTION

Microelectronic elements such as semiconductor chips commonly are provided with elements which protect the microelectronic element and facilitate its connection to other elements of a larger circuit. For example, semiconductor chip typically is provided as a small, flat element having oppositely facing front and rear surfaces and contacts at the front surface. The contacts are electrically connected to the numerous electronic circuit elements formed integrally within the chip. Such a chip most commonly is provided in a package having a miniature circuit referred to as a substrate. The chip is typically mounted to the substrate with the front or rear surface overlying a surface of the substrate, and the substrate typically has terminals at a surface of the substrate. The terminals are electrically connected to the contacts of the chip. package typically also includes some form of covering overlying the chip on the side of the chip opposite from the substrate. The covering serves to protect the chip and, in some cases, the connections between the chip and the conductive elements of the substrate. Such a packaged chip may be mounted to a circuit panel, such as a circuit board,

by connecting the terminals of the substrate to conductive elements such as contact pads on the larger circuit panel.

[0004] In certain packages, the chip is mounted with its front or back surface overlying an upper surface of the substrate, whereas terminals are provided on the oppositely facing lower surface. A mass of a dielectric material overlies the chip and, most typically, the electrical connections between the chip and the conductive elements of the substrate. The dielectric mass may be formed by molding a flowable dielectric composition around the chip so that the dielectric composition covers the chip and all or part of the top surface of the substrate. Such a package is commonly referred to as an "overmolded" package, and the mass of dielectric material is referred to as the "overmold." Overmolded packages are economical to manufacture and thus are widely used.

In some applications, it is desirable to stack 100051 chip packages on top of one another, so that plural chips may be provided in the same space on the surface of the larger circuit panel. Also, it is desirable to have a large number of input/output interconnections to the chips. overmolded packages incorporate stacking contacts at the top surface of the substrate outside of the area covered by the chip and, typically, outside of the area covered by the overmold. Such packages may be stacked one atop the other with interconnecting elements such as solder balls, elongated posts, wire bonds or other conductive connections extending between the stacking contacts of the lower package and the terminals of the next higher package in the stack. In such an arrangement, all of the packages in the stack are electrically connected to the terminals on the package at the bottom of the stack. In addition, because the substrate of the higher package in the stack sits above the dielectric

overmold in the next lower package, there is an appreciable gap in the vertical direction between the terminals of the higher package and the stacking contacts of the lower package. The interconnecting elements must bridge this gap.

[0006] Despite the considerable effort devoted in the art to development of stackable packages and other packages having top-surface mounting pads, further improvement would be desirable.

## SUMMARY OF THE INVENTION

In accordance with one embodiment, a structure may include a substrate having first and second oppositely facing surfaces and a plurality of electrically conductive elements at the first surface. In addition, the structure may include bond elements having bases joined to respective ones of the conductive elements at a first portion of the first surface and end surfaces remote from the substrate and the bases, where each of the bond elements extend from the base to the end surface thereof. Further the structure may include a dielectric encapsulation element overlying and extending from the first portion of the first surface of the substrate and filling spaces between the bond elements such that the bond elements are separated from one another by the encapsulation element, the encapsulation element having a third surface facing away from the first surface of the substrate and having an edge surface extending from the third surface towards the first surface, where unencapsulated portions of the bond elements are defined by at least portions of the end surfaces of the bond elements that are uncovered by the encapsulation element at the third surface, the encapsulation element at least partially defines a second portion of the first surface, the second portion being other than the first portion of the first surface and having an area sized to accommodate an entire area of a microelectronic element, and

at least some of the conductive elements at the first surface are at the second portion and configured for connection with such microelectronic element.

In accordance with another embodiment, a method of making a structure may include forming a dielectric encapsulation element on a substrate, the substrate having first and second oppositely facing surfaces and a plurality of electrically conductive elements at the first surface, where bond elements are joined at bases thereof to respective ones of the conductive elements at a first portion of the first surface and end surfaces of the bond elements are remote from the substrate and the bases, each of the bond elements extending from the base to the end surface thereof, dielectric encapsulation element is formed where the overlying and extending from the first portion of the first surface of the substrate and filling spaces between the bond elements such that the bond elements are separated from one another by the encapsulation element, the encapsulation element having a third surface facing away from the first surface of the substrate and having an edge surface extending from the third surface towards the first surface, where unencapsulated portions of the bond elements are defined by at least portions of the end surfaces of the bond elements that are uncovered by the encapsulation element at the third surface, where the encapsulation element at least partially defines a second portion of the first surface, the second portion being other than the first portion of the first surface and having an area sized to accommodate an entire area of a microelectronic element, and at least some of the conductive elements at the first surface are at the second portion and configured for connection with such microelectronic element.

In accordance with another embodiment, a structure 100091 may include an active die having first and second oppositely facing surfaces and a plurality of electrically conductive elements at the first surface. In addition, the structure may include bond elements having bases joined to respective ones of the conductive elements at a first portion of the first surface and end surfaces remote from the die and the bases, each of the bond elements extending from the base to the end surface thereof. Further, the structure may include a dielectric encapsulation element overlying and extending from the first portion of the first surface of the die and filling spaces between the bond elements such that the bond elements are separated from one another by the encapsulation element, the encapsulation element having a third surface facing away from the first surface of the die and having an edge surface extending from the third surface towards the first surface, wherein unencapsulated portions of the bond elements are defined by at least portions of the end surfaces of the bond elements that are uncovered by the encapsulation element at the third surface. The encapsulation element may at least partially define a second portion of the first surface, the second portion being other than the first portion of the first surface and having an area sized to accommodate an entire area of a microelectronic element, and at least some of the conductive elements at the first surface are at the second portion and configured for connection with such microelectronic element.

[0010] In accordance with another embodiment, a method of making a structure may include forming a dielectric encapsulation element on an active die provided at wafer level. The die may have first and second oppositely facing surfaces and a plurality of electrically conductive elements at the first surface, where bond elements may be joined at

bases thereof to respective ones of the conductive elements at a first portion of the first surface and end surfaces of the bond elements are remote from the substrate and the bases, each of the bond elements extending from the base to the end surface thereof, where the dielectric encapsulation element is formed overlying and extending from the first portion of the first surface of the die and filling spaces between the bond elements such that the bond elements are separated from one another by the encapsulation element, the encapsulation element having a third surface facing away from the first surface of the die and having an edge surface extending from the third surface towards the first surface, where unencapsulated portions of the bond elements are defined by at least portions of the end surfaces of the bond elements that are uncovered by the encapsulation element at the third surface, and where the encapsulation element at least partially defines a second portion of the first surface, the second portion being other than the first portion of the first surface and having an area sized to accommodate an entire area of a microelectronic element, and at least some of the conductive elements at the first surface are at the second portion and configured for connection with such microelectronic element.

## BRIEF DESCRIPTION OF THE DRAWINGS

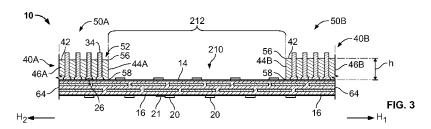

[0011] FIG. 1 is a diagrammatic sectional view depicting a substrate used in a method of manufacturing a structure, according to an embodiment of the disclosure.

[0012] FIG. 2 is a diagrammatic sectional view depicting the substrate and associated elements at a later stage of manufacturing operations, according to an embodiment of the disclosure.

[0013] FIG. 3 is a diagrammatic sectional view depicting a structure made using the substrate and the associated

elements of FIGs. 1-2, according to an embodiment of the disclosure.

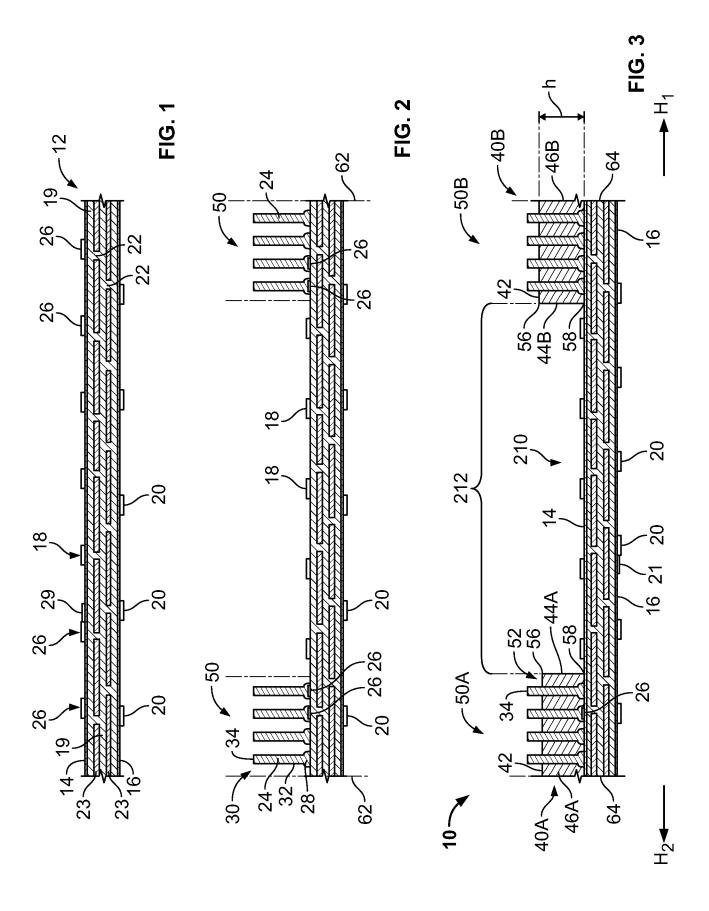

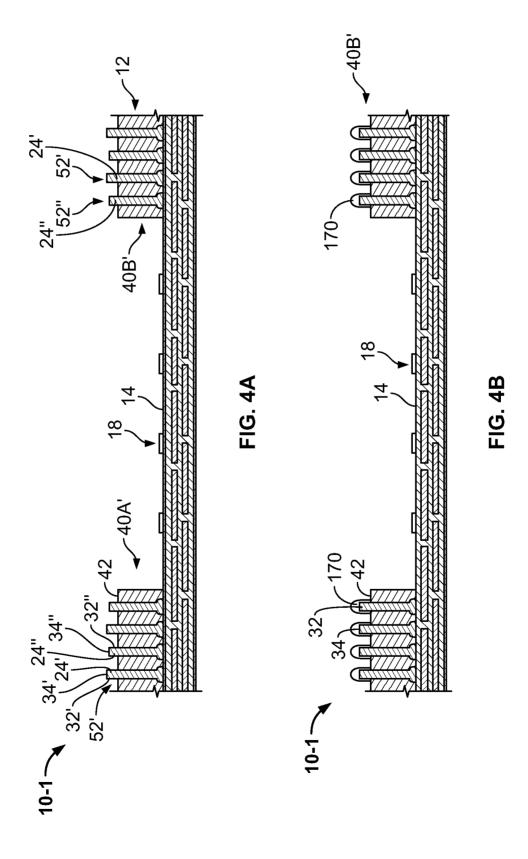

- [0014] FIG. 4A is a diagrammatic sectional view of an exemplary structure, according to an embodiment of the disclosure.

- [0015] FIG. 4B is a diagrammatic sectional view of the structure of FIG. 4A at a later stage of manufacturing operations.

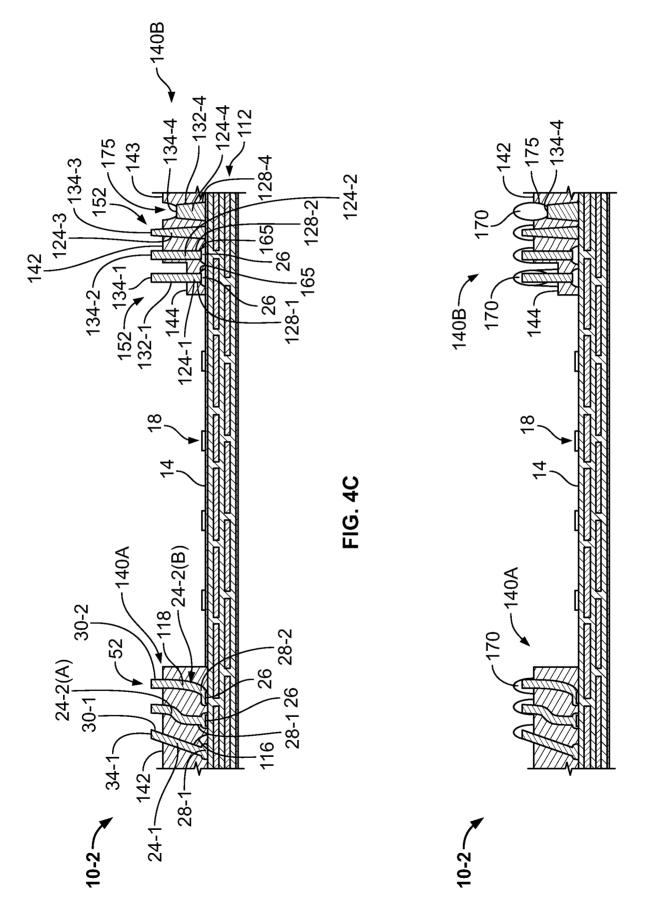

- [0016] FIG. 4C is a diagrammatic sectional view of another exemplary structure, according to an embodiment of the disclosure.

- [0017] FIG. 4D is a diagrammatic sectional view of the structure of FIG. 4C at a later stage of manufacturing operations.

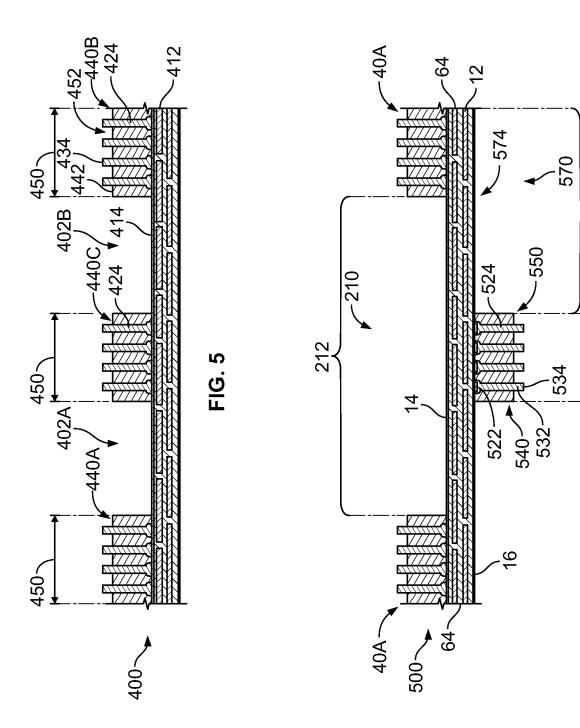

- [0018] FIG. 5 is a diagrammatic sectional view of another exemplary structure, according to an embodiment of the disclosure.

- [0019] FIG. 6 is a diagrammatic sectional view of another exemplary structure, according to an embodiment of the disclosure.

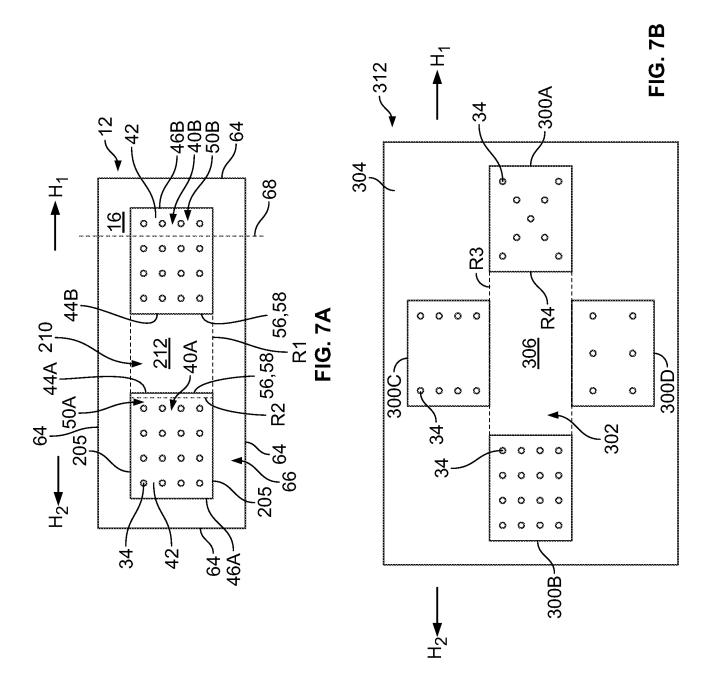

- [0020] FIG. 7A is a diagrammatic top plan view depicting the structure of FIG. 3.

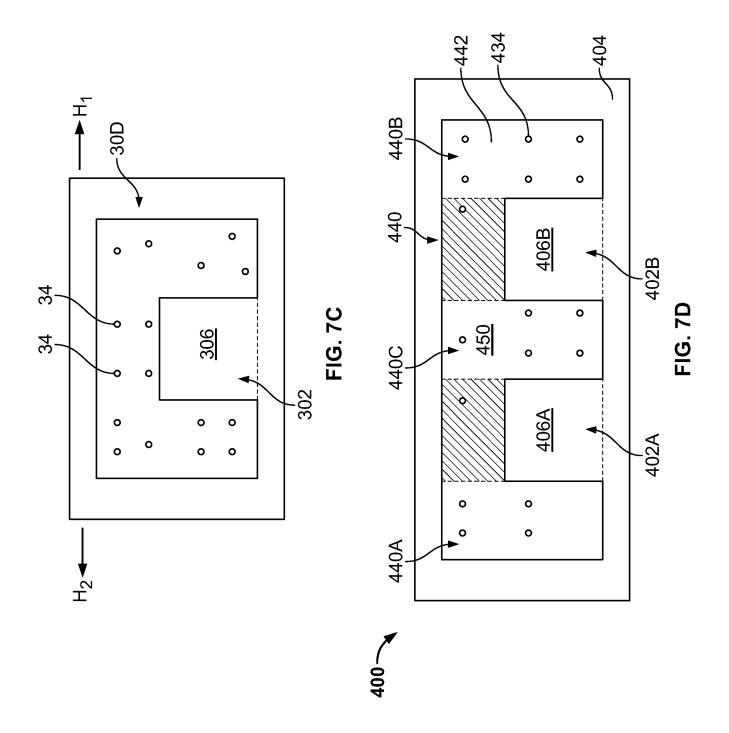

- [0021] FIGs. 7B-7C are diagrammatic top plan views depicting exemplary structures, in accordance with the disclosure.

- [0022] FIG. 7D is a diagrammatic top plan view depicting the structure of FIG. 5.

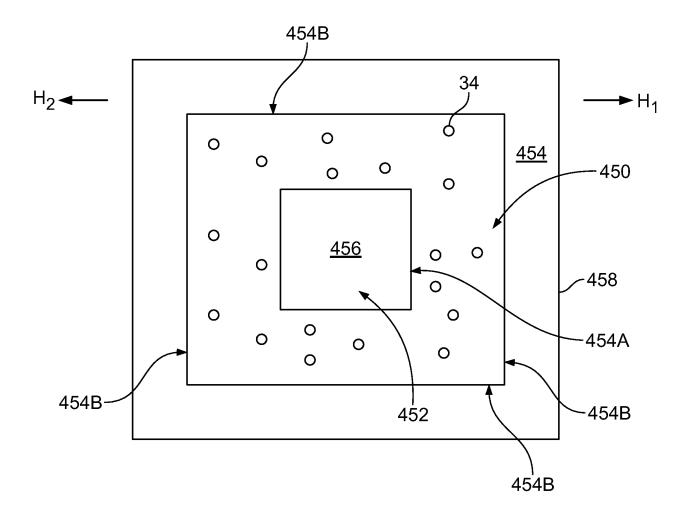

- [0023] FIG. 7E is a diagrammatic top plan view depicting an exemplary structure, in accordance with the disclosure.

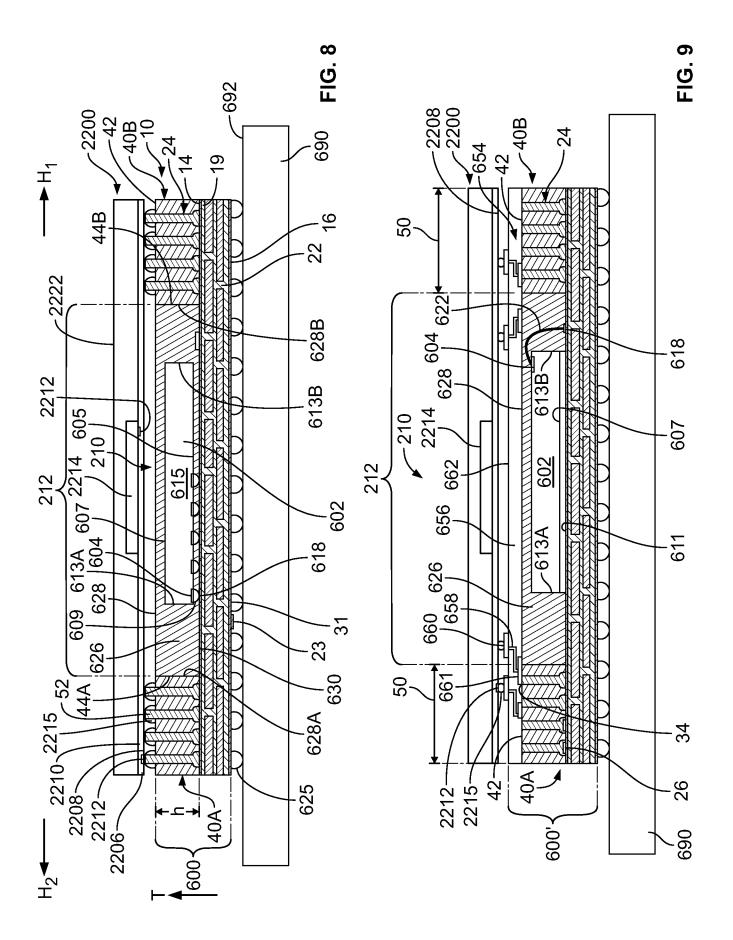

- [0024] FIG. 8 is a diagrammatic sectional view of an exemplary package assembly including the structure of FIG. 3, in accordance with the disclosure.

[0025] FIG. 9 is a diagrammatic sectional view of another exemplary package assembly including the structure of FIG. 3, in accordance with the disclosure.

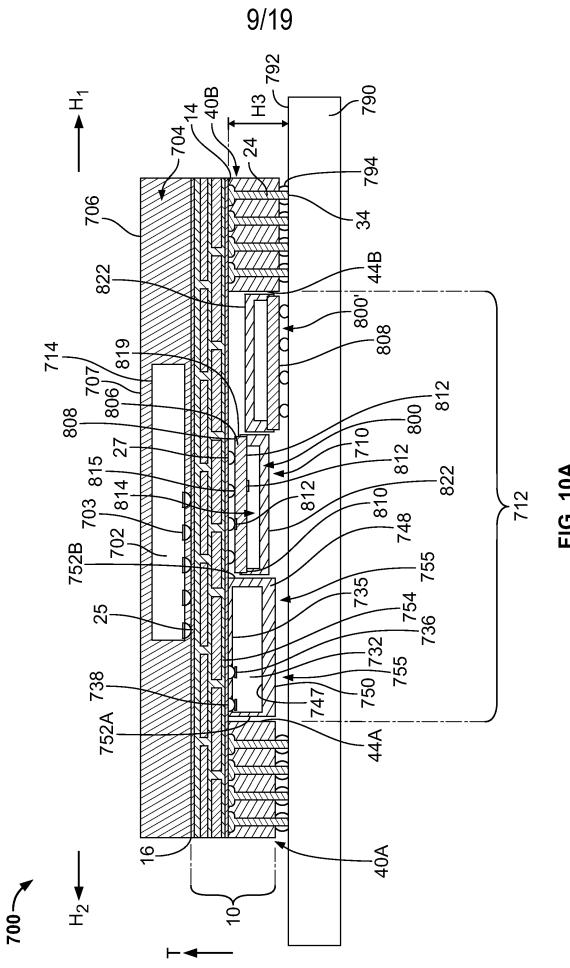

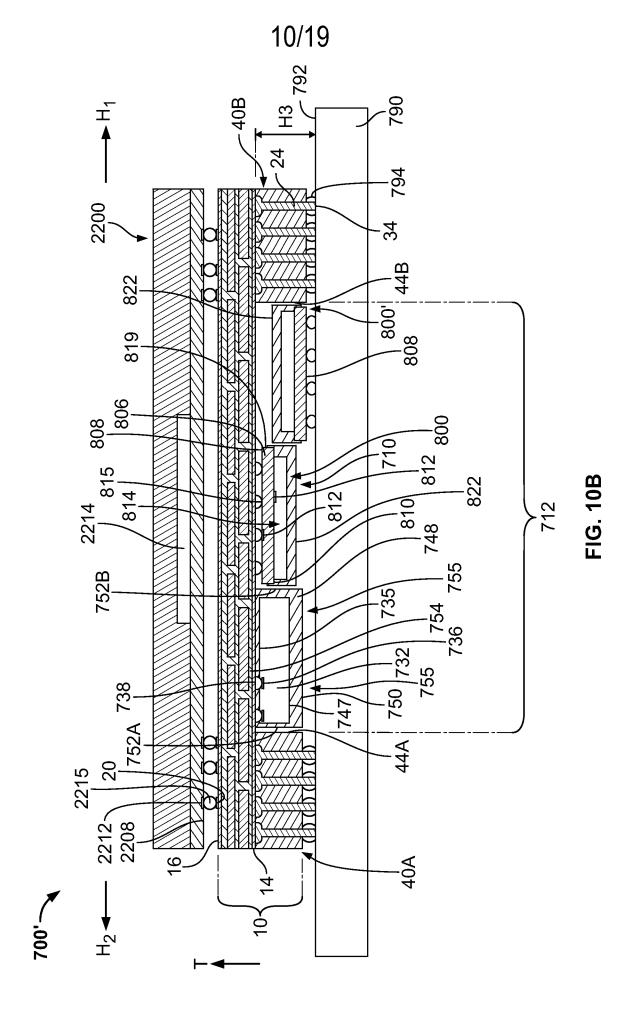

[0026] FIG. 10A is a diagrammatic sectional view of another exemplary package assembly including the structure of FIG. 3, in accordance with the disclosure.

[0027] FIG. 10B is a diagrammatic sectional view of another exemplary package assembly including the structure of FIG. 3, in accordance with the disclosure.

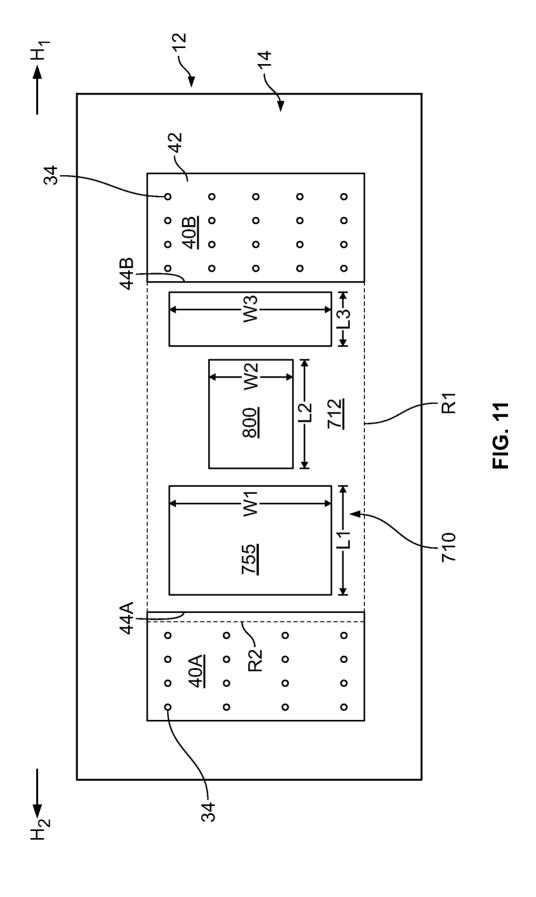

[0028] FIG. 11 is a bottom plan view of the package assembly of FIG. 10A.

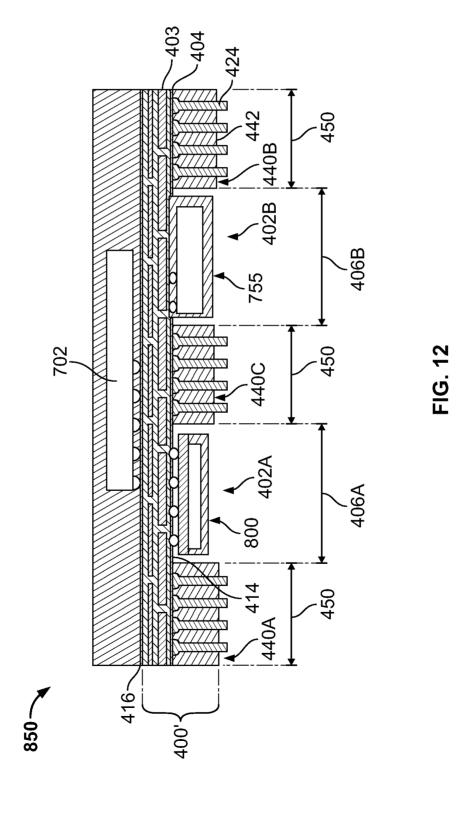

[0029] FIG. 12 is a diagrammatic sectional view of an exemplary package assembly including the structure of FIG. 5, in accordance with the disclosure.

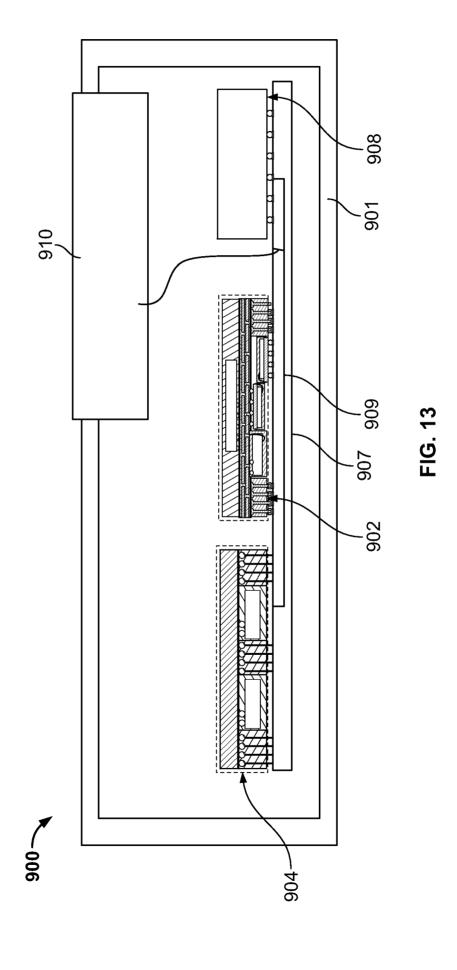

[0030] FIG. 13 is a diagrammatic view depicting a system according with the disclosure.

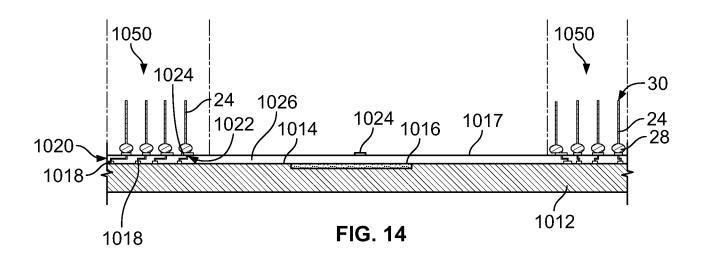

[0031] FIG. 14 is a diagrammatic sectional view depicting an active die and associated elements at a stage of manufacturing a structure, according to an embodiment of the disclosure.

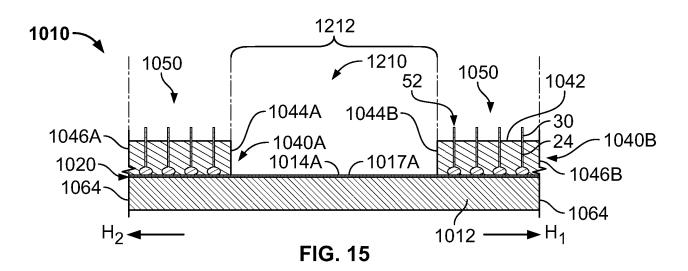

[0032] FIG. 15 is a diagrammatic sectional view depicting the structure made using the die and the associated elements of FIG. 14, according to an embodiment of the disclosure.

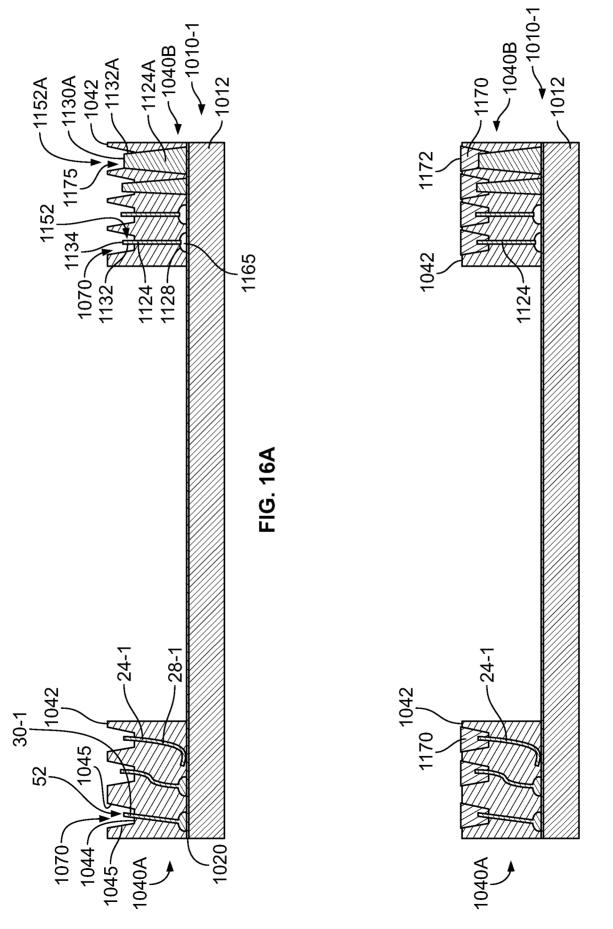

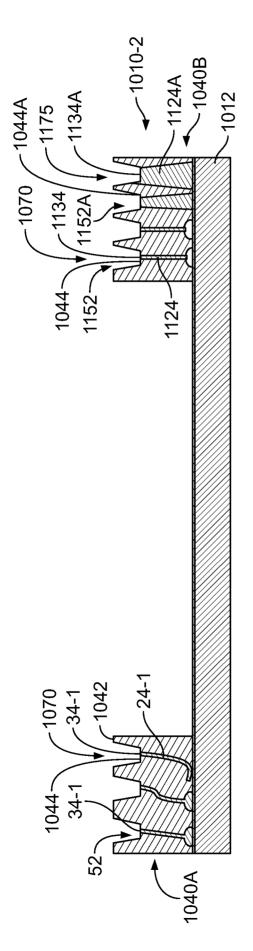

[0033] FIG. 16A is a diagrammatic sectional view of an exemplary structure including an active die, according to an embodiment of the disclosure.

[0034] FIG. 16B is a diagrammatic sectional view of the structure of FIG. 16A at a later stage of manufacturing operations.

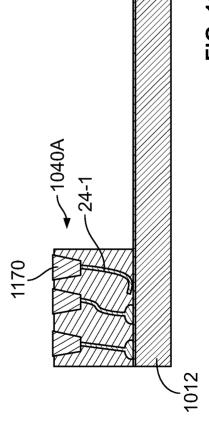

[0035] FIG. 16C is a diagrammatic sectional view of another exemplary structure including an active die, according to an embodiment of the disclosure.

[0036] FIG. 16D is a diagrammatic sectional view of the structure of FIG. 16C at a later stage of manufacturing operations.

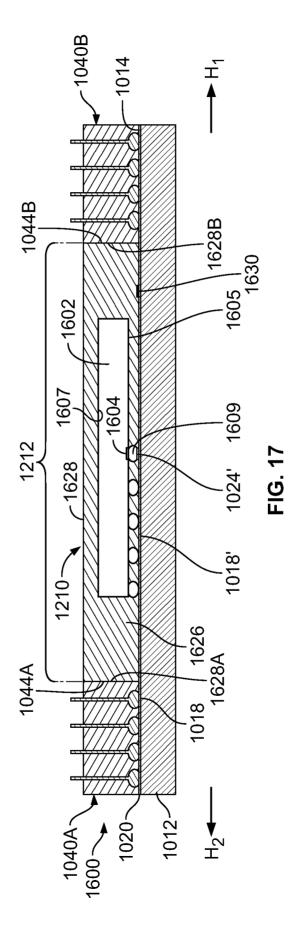

[0037] FIG. 17 is a diagrammatic sectional view of an exemplary package assembly including the structure of FIG. 15, in accordance with the disclosure.

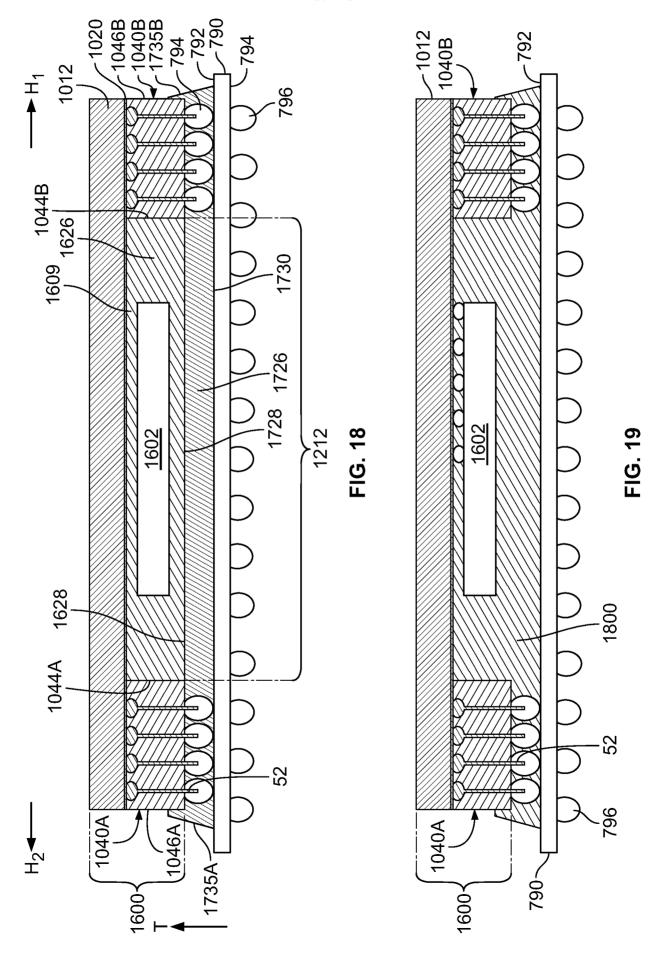

[0038] FIG. 18 is a diagrammatic sectional view of an exemplary package assembly including the structure of FIG. 15, in accordance with the disclosure.

[0039] FIG. 19 is a diagrammatic sectional view of an exemplary package assembly including the structure of FIG. 15, in accordance with the disclosure.

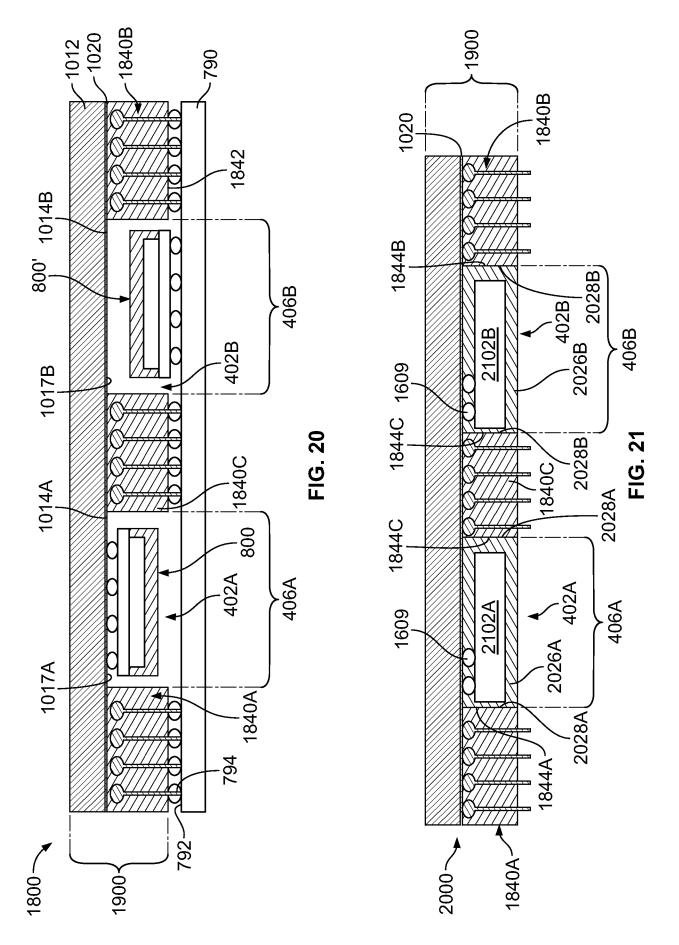

[0040] FIG. 20 is a diagrammatic sectional view of an exemplary package assembly including a structure, in accordance with the disclosure.

[0041] FIG. 21 is a diagrammatic sectional view of an exemplary package assembly including a structure, in accordance with the disclosure.

## DETAILED DESCRIPTION

A structure 10 (see FIG. 3) according to one embodiment of the disclosure may include a substrate 12 (see FIG. 1) having a first surface 14 and a second surface 16. The substrate 12 typically is in the form of a dielectric element, which is substantially flat. The dielectric element may be sheet-like and thin. In particular embodiments, the dielectric element may include one or more layers 23 of organic dielectric material or composite dielectric such as, without limitation: materials, polyimide, polytetrafluoroethylene ("PTFE"), epoxy, epoxy-glass, FR-4, BT resin, thermoplastic, or thermoset plastic materials. The first surface 14 and second surface 16 are preferably substantially parallel to each other and are spaced apart at a distance perpendicular to the surfaces 14 and 16 defining

the thickness of the substrate 12. The thickness of substrate 12 is preferably within a range of generally acceptable thicknesses for the present application. In an embodiment, the distance between the first surface 14 and the second surface 16 is between about 25 and 500  $\mu m$ . For purposes of this discussion, the first surface 14 may be described as being positioned opposite or remote from the second surface 16. Such a description, as well as any other description of the relative position of elements used herein that refers to a vertical or horizontal position of such elements is made for illustrative purposes only to correspond with the position of the elements within the Figures, and is not limiting.

Electrically conductive elements 18, which may [0043] include contacts or pads, traces or terminals, are at the first surface 14 of the substrate 12. As used in this disclosure, a statement that an electrically conductive element is "at" a surface of a substrate indicates that, when the substrate is not assembled with any other element, the electrically conductive element is available for contact with a theoretical point moving in a direction perpendicular to the surface of the substrate toward the surface of the substrate from outside the substrate. Thus, a terminal or other conductive element which is at a surface of a substrate may project from such surface; may be flush with such surface; or may be recessed relative to such surface in a hole or depression in the substrate. In addition, as used in this disclosure a statement that an electrically conductive circuit panel, element is "at" a surface of a microelectronic element such as a semiconductor chip or a like element, indicates that, when the panel or the element is not assembled with any other element, the electrically conductive element is available for contact with a

theoretical point moving in a direction perpendicular to the surface of the panel or element toward the surface of the panel or element from outside the panel or element. Further, as used in this disclosure, a statement that a trace extends "along" a surface means that the trace extends in proximity to the surface and substantially parallel to the surface.

[0044] Traces 29 included as the conductive elements 18 may be formed as flat, thin, elongated strips of conductive material at the surface 14. In some embodiments, the traces may be formed integrally with and extend from terminals 27 included as the conductive elements 18 having a similar composition. In addition, contact pads 26 included as the conductive elements 16 on the surface 14 may be interconnected by traces 29 on the surface 14.

[0045] The terminals, pads or traces serving as the conductive elements 18 may be fabricated by numerous known methods, such as by plating the terminals, pads and traces onto the surface 14 of the substrate. In one embodiment, the traces may be embedded in the surfaces of the substrate, with the surfaces of the traces lying substantially flush with the surfaces of the substrate. In one embodiment, the conductive elements 18 may be formed from a solid metal material such as copper, copper, gold, nickel, or other materials that are acceptable for such an application, including various alloys including one or more of copper, gold, nickel or combinations thereof.

[0046] At least some of conductive elements 18 may be interconnected with second conductive elements 20, which may include conductive pads, traces or terminals similarly as described with respect to the conductive elements 18, at the second surface 16 of the substrate 12. Such an interconnection may be completed using vias 22 formed in the substrate 12 that may be lined or filled with conductive

metal that may be of the same material as the conductive elements 18 and 20. The vias 22 in the substrate 12 desirably are fully closed by traces at the surfaces 14 or 16 of the substrate 12 or traces 19 within the substrate 12. The substrate 12 may include a plurality of dielectric material layers 23 with a layer of traces 19 disposed between adjacent ones of the layers 23. Contact pads 25 and terminals 31 included as the conductive elements 18 may be further interconnected by traces 33 on the surface 16 also serving as the conductive elements 18.

Referring to FIG. 2, the structure 10 may further include a plurality of bond elements 24 joined with at least some of the conductive elements 18, such as on pads 26 thereof, at a portion 50 of the surface 14. The portion 50 may include one or more areas of the surface 14, such as portions 50A and 50B as shown in FIG. 7A. The bond elements 24 are joined at a base 28 thereof to the pads 26 and may extend to a free end 30 remote from the respective bases 28 and from the substrate 12. The ends 30 of the bond elements 24 are characterized as being free in that they are not electrically connected or otherwise joined to microelectronic element electrically connected to the conductive elements 18 at the surface 14 or any other conductive features within a microelectronic assembly including the structure 10 that are, in turn, connected to such microelectronic element. In other words, the free ends 30 are available for electronic connection, either directly or indirectly as through a solder ball or other features discussed herein, to a conductive feature external to a microelectronic assembly including the structure 10. fact that the ends 30 may be held in a predetermined position by, for example, an encapsulant material, such as forming a dielectric encapsulation element 40 as discussed below in the

text accompanying the description of FIGs. 3 and 4A-4D, or otherwise joined or electrically connected to another conductive feature, does not mean that they are not "free" as described herein, so long as any such feature is not electrically connected to a microelectronic element joined with the conductive elements at the surfaces, such as the surfaces 14 or 16, to which the bases thereof are joined. Conversely, base 28 is not free as it is either directly or indirectly electrically connected to a microelectronic element connected at the surfaces 14 or 16, as described herein.

[0048] As shown in FIG. 2, the base 28 may be substantially rounded in shape, extending outward from an edge surface 32 of the bond element 24, which may be a wire bond, defined between the base 28 and the end 30. particular size and shape of the base 30 may vary according to the type of material used to form the wire bond 24, the desired strength of the connection between the wire bond 24 and the conductive element 18, or the particular process used to form the wire bond 24. Exemplary methods for making the wire bonds 24 are described in U.S. Pat. No. 7,391,121 to Otremba and in U.S. Pat. App. Pub. No. 2005/0095835, the disclosures of which are both incorporated herein by reference in their entireties. In an alternative embodiment, some of the wire bonds 24 may be joined to conductive elements 20 at the second surface 16 of substrate 12, through the conductive elements 19 and conductive material in the vias 22 within the substrate 12.

[0049] The bond elements 24 may be made from a conductive material such as copper, gold, nickel, solder, aluminum or the like. Additionally, the bond elements 24 may be made from combinations of materials, such as from a core of a conductive material, such as copper or aluminum, for example,

with a coating applied over the core. The coating may be of a second conductive material, such as aluminum, nickel or the like. Alternatively, the coating may be of an insulating material, such as an insulating jacket. In an embodiment, the wire used to form bond elements 24 may have a thickness, i.e., in a dimension transverse to the wire's length, of between about 15  $\mu$ m and 150  $\mu$ m.

In other embodiments, including those in which wedge bonding is used, wire bonds 24 may have a thickness of up to about 500  $\mu m$ . In general, a wire bond is formed on a conductive element, such as conductive element 26 that is a pad or the like, using specialized equipment that is known in the art. A leading end of a wire segment is heated and pressed against the receiving surface to which the wire segment bonds, typically forming a ball or ball-like base 28 joined to the surface of the pad 26. The desired length of the wire segment to form the wire bond is drawn out of the bonding tool, which may then cut the wire bond at the desired length. Wedge bonding, which may be used to form wire bonds of aluminum, for example, is a process in which the heated portion of the wire is dragged across the receiving surface to form a wedge that lies generally parallel to the surface. The wedge-bonded wire bond may then be bent upward, if necessary, and extended to the desired length or position before cutting. In a particular embodiment, the wire used to form a wire bond may be cylindrical in cross-section. Otherwise, the wire fed from the tool to form a wire bond or wedge-bonded wire bond may have a polygonal cross-section such as rectangular or trapezoidal, for example.

[0051] The free end 30 of the wire bond 24 has an end surface 34. The end surface 34 may form at least a part of a contact in an array formed by respective end surfaces 34 of a plurality of wire bonds 24.

[0052] Referring to FIG. 3, the structure 10 may further include encapsulation elements 40A and 40B formed from a dielectric material. In the embodiment of FIG. 3, the encapsulation elements 40 may be formed over the portion 50 of the first surface 14 of the substrate 12, and define a top surface 42 remote and facing away from the substrate 12. The material of the element 40 fills spaces between the bond elements 24, such that the bond elements 24 are separated from one another by the material of the encapsulation elements 40. Unencapsulated portions 52 of the bond elements 24 are defined by at least a portion of the end 30 of the bond elements 24, desirably by the end surface 34 thereof, and are uncovered by the encapsulation elements 40, for example, at the surface 42.

[0053] In a particular embodiment, the substrates of numerous structures are provided as a continuous or semi-continuous element such as a strip, tape or sheet, although in FIGs. 1-2 there are no visible borders between the individual substrates. After the encapsulation elements 40 are formed on the substrates, the structures 10 are then severed along lines of separation 62 (see FIG. 2 which does not show visible borders between the individual substrates) to yield the individual structure 10 having the configuration illustrated in FIG. 3, and where the substrate 12 of the structure 10 extends between opposing edges 64. FIGs. 1-2 depict only a portion of a substrate sheet suitable for making a plurality of structures that may accommodate a microelectronic element over a defined portion of the substrate thereof, as described in detail below.

[0054] Referring to FIG. 3, the encapsulation elements 40A and 40B may define first edge surfaces 44A and 44B, respectively, extending downwardly from a top border 56 adjacent the top surface 42 to a bottom border 58 adjacent

the substrate 12 and disposed inside the edges 64 of the substrate 12. Further referring to FIG. 7A, bottom border 58 is disposed within a horizontal area 66 bounded by the edges 64 of the substrate. In one embodiment, the first edge surfaces 44A and 44B extend orthogonally from the surface 42 of the elements 40A, 40B, respectively, and the surface 14, and the surfaces 42 and 14 extend parallel to each other, such that the borders 56, 58 are aligned in a thickness direction of the structure 10.

[0055] In another embodiment, one or both of the first edge surfaces 44A and 44B may slope away from the top surface 42 in a horizontal direction toward the other element 40A or 40B opposite thereto, at an incline of less than 90 degrees with respect to the top surface 42, so that the bottom border 58 of the first edge surface 44 is further from the top surface 42 than the top border 56 in the horizontal direction toward the opposite element 40, similarly as described in U.S. Application No. 13/674,280 filed November 12, 2012, incorporated by reference herein.

[0056] In one embodiment, referring to FIG. 7A, the first edge surfaces 44 may be shaped such that any straight line extending along the first edge surface 44 at a constant vertical distance from the substrate 12 is disposed at a constant location in a first horizontal direction  $H_1$ . For example, an imaginary line 68 (FIG. 7A) extending at a constant vertical distance from the substrate would also lie at a constant horizontal location. In some embodiments, the first edge surfaces 44 may be substantially planar.

[0057] The elements 40A and 40B further may include second edge surfaces 46A and 46B, respectively, extending downwardly from the top surface 42 toward the substrate. The surfaces 46A, 46B, similar to the surfaces 44, may extend orthogonally from the surfaces 42 and 14, or alternatively

may slope away from the surface 42 in horizontal directions  $\mathrm{H}_2$  and  $\mathrm{H}_1$ , respectively. Similar to the edge surfaces 44, the edge surfaces 46 may be shaped such that any straight line extending along the surfaces 46 at a constant vertical distance from the substrate 12 is disposed at a constant location in the horizontal directions  $\mathrm{H}_2$  and  $\mathrm{H}_1$ , respectively, similarly as described above for the edge surfaces 44.

[0058] The encapsulation elements 40 may have a thickness (h) of at least about 150 micrometers extending away from the surface 14 in a direction orthogonal to the horizontal directions  $H_2$  and  $H_1$ . The encapsulation elements 40 may also cover some conductive elements 18 within the region 50, including pads 26 thereof, that are not otherwise covered by bond elements 24.

The encapsulation elements 40 may at [0059] least partially, and desirably substantially, encapsulate the wire bonds 24 joined with the conductive elements 26 within the region 50, including the bases 28 and at least a portion of the edge surfaces 32 of the bond elements. A portion of the wire bonds 24 may remain uncovered by the encapsulation element, which may also be referred to as unencapsulated, thereby making the wire bond 24 available for electrical connection to a feature or element located outside of encapsulation element 40. In an embodiment, end surfaces 34 wire bonds 24 remain uncovered by the encapsulation element 40 at the surface 42 of the encapsulation element 42. Other embodiments are possible in which a portion of edge surface 32 is uncovered by encapsulation element 40 in addition to or as an alternative to having end surface 34 remain uncovered by encapsulation layer 40. In other words, encapsulation element 40 may cover all portions of components overlying the portion 50 of the first surface 14, with the exception of a portion of the wire bonds 24, such as at least

the end surfaces 34, and optionally portions of the edge surfaces 32 or combinations of the two. In the embodiments shown in the drawings, the surface 42 of the encapsulation layer 40 may be spaced apart from first surface 14 of substrate 12 at a distance great enough to cover all but a portion of the bond element 24 at the end 30. Referring to FIG. 3, embodiments of the structure 10 may have end surfaces 30 of the wire bonds 24 other than flush with the surface 42, such as wire bonds 24 having ends that project from the surface 42 and terminate at end surfaces 34 that are at a same distance from the surface 42.

[0060] Alternatively, an embodiment of the disclosure may include a structure 10-1 as shown in FIG. 4A, which includes components similar to those of the structure 10 described above. Referring to FIG. 4A, the structure 10-1 may include encapsulation elements 40A' and 40B' each having a top surface 42 that is substantially planar and parallel to planar surface 14 of the substrate 12. The elements 40A' and 40B' may encapsulate wire bonds 24' and 24'' having end surfaces 34' and 34'', respectively, at different distances from the surface 42, and define unencapsulated portions 52' and 52'' including the end surfaces 34' and 34'' and portions of edges surfaces 32' and 32'', respectively. In some embodiments, the end surface 34 of the bond element 24 may be planar and an edge surface 32 thereof may be planar and extend perpendicular to the end surface 34.

[0061] The configuration of the bond elements 24 having the unencapsulated portions 52, such as shown in FIGs. 3 and 4A, may provide for a connection, such as by a solder ball 170 or the like as shown in FIG. 4B, to another conductive element by allowing the solder to wick along edge surfaces 32 and join thereto in addition to joining to end surfaces 34.

The solder ball 170 also may extend onto uncovered portions of the surface 42 from the edge surfaces 32.

[0062] Other configurations for bond elements 24 encapsulated by encapsulation elements 40 of a structure according to the disclosure also are possible. For example, FIG. 4C shows an embodiment of a structure 10-2 having a wire bond 24-1 encapsulated by an encapsulation element 140A with an end 30-1 thereof that is not positioned directly above base 28-1 thereof. That is, considering the first surface 14 of the substrate 12 as extending in two lateral directions, so as to substantially define a plane (see FIG. 7A), an end 30-1 of a wire bond 24-1 extending through the encapsulation element 140A may be displaced in at least one of these lateral directions from a corresponding lateral position of base 28-1. As shown in FIG. 4C, the wire bond 24-1 may be substantially straight along the longitudinal axis thereof, as in the embodiment of FIGs. 3 and 4A, with the longitudinal axis being angled at an angle 116 with respect to the first surface 14 of the substrate 12. Although the cross-sectional view of FIG. 4C only shows the angle 116 through a first plane perpendicular to the first surface 14, the wire bond 24-1 may also be angled with respect to the first surface 14 in another plane perpendicular to both that first plane and to the first surface 14. Such an angle may be substantially equal to or different than angle 116. That is displacement of end 30-1 relative to base 28-1 may be in two lateral directions and may be by the same or a different distance in each of those directions.

[0063] In an embodiment, various ones of wire bonds 24-1 and 24-2 encapsulated by the element 140A may be displaced in different directions and by different amounts along the first surface 14 and within the encapsulation element 140A. Such an arrangement allows the structure 10-2 to have an array

that is configured differently at the level of the surface 142 of the element 140A compared to at the level of substrate For example, an array may cover a smaller or larger overall area or have a smaller or larger pitch at the surface 142 level compared to that at the first surface 14 of the substrate 12. Further, some wire bonds 24-1 may have ends 30-1 positioned above the substrate 12 to accommodate a stacked arrangement of packaged microelectronic elements of different sizes. In another example, the wire bonds 24-1 may be configured such that the end 30-1 of one wire bond 24-1 is positioned substantially above the base 28-1 of another wire bond 24-1, and the end 30-1 of the another wire bond 24-1 is positioned elsewhere. Such an arrangement may be referred to as changing the relative position of a contact end surface 34 within an array of contacts, compared to the position of a corresponding contact array on another surface, such as the surface 14. Within such an array, the relative positions of the contact end surfaces may be changed or varied, as desired, depending on application of a microelectronic assembly formed from the structure 10-2 or requirements.

[0064] In a further example as shown in FIG. 4C, wire bonds 24-1 encapsulated by the element 140A may be arranged such that the bases 28-1 are arranged in a first pattern having a pitch thereof. The wire bonds 24-1 may be configured such that the unencapsulated portions 52 thereof, which include end surfaces 30-1, may be disposed in a pattern at positions at the surface 142 of the encapsulation element 140A which have a minimum pitch that is greater than a minimum pitch between the respective adjacent bases 28-1 of the wire bonds 24-1 attached to conductive pads 26 within the region 50. Accordingly, the minimum pitch between adjacent wire bonds at the surface 142 may be greater than the

corresponding minimum pitch between the conductive pads 26 of the substrate to which the wire bonds are attached. To achieve this, the wire bonds may be angled or curved as shown, for example, in FIG. 4C, such that the ends 30 are displaced in one or more lateral directions from the bases 28, as discussed above. In one embodiment, the conductive elements 26 and the ends 30 may be arranged in respective rows or columns and the lateral displacement of end surfaces 34 in one row may be greater than in another row. To achieve this, the wire bonds 24 can, for example be at different angles 116 with respect to the surface 14 of the substrate 12.

[0065] FIG. 4C shows a further embodiment in which wire bonds 24-2 have ends 30-2 in displaced lateral positions with respect to the bases 24-2 thereof. In the embodiment of FIG. 4C, the wire bonds 24-2 achieve this lateral displacement by including a curved portion 118 therein. The curved portion 118 may be formed in an additional step during a wire bond formation process and may occur, for example, while the wire portion is being drawn out to the desired length. This step may be carried out using available wire-bonding equipment, which may include the use of a single machine.

[0066] The curved portions 118 may take on a variety of shapes, as needed, to achieve the desired position of the end 30-2 of the wire bond 24-2. For example, as shown in FIG. 4C, the curved portions 118 may be formed as S-curves of various shapes, such as included in wire bond 24-2(A), or of a smoother form as in wire bond 24-2(B). Additionally, the curved portion 118 may be positioned closer to base 28-2 than to end 30-2 or vice-versa. The curved portion 118 may also be in the form of a spiral or loop, or may be compound including curves in multiple directions or of different shapes or characters.

[0067] In one embodiment, the structure 10-2 may include encapsulation elements 140 each having a different type of bond elements 24 encapsulated therein. Referring to FIG. 4C, the element 140A may include wire bonds or wires as the bond elements 24, and encapsulation element 140B may include substantially vertical conductive features, such as micropillars or posts, as the bond elements 124.

It is to be understood that, as shown FIG. 4C, a structure may include any combination of bond elements having leading various shapes to various relative lateral displacements between bases and ends thereof. Some of the bond elements 24 are substantially straight with ends 30 positioned above their respective bases 28 as shown in FIG. 3 and FIG. 4A, while other bond elements 24 include a curved portion 118 leading to a somewhat slight relative lateral displacement between end 30 and base 28. Further, some bond elements 24 include curved portions 118 having a sweeping shape that result in ends 30 that are laterally displaced from the relative bases 28 at a greater distance than that of ends 28.

[0069] In such embodiments of the bond elements 24, wire bonds thereof may be configured to be uncovered by the encapsulation element at an end 30 and along at least a portion of the edge surface thereof extending away from the end surface 34. As shown in FIGs. 3 and 4A, 4C, free ends of the bond elements are uncovered, however, a portion of edge surface 32 may additionally or alternatively be uncovered by the encapsulation element. Such a configuration may be used for grounding of a microelectronic assembly including the structure by electrical connection to an appropriate feature or for mechanical or electrical connection to other features disposed laterally to the microelectronic assembly.

[0070] Additionally, referring to FIG. 4C, encapsulation element 140B may encapsulate bond elements 124 that are in the form of posts or micro-pillars connected at bases 128 thereof with conductive elements 26 at the surface The element 140B may be configured to include an area that has been etched away, molded, or otherwise formed to define a recessed surface 144 that is positioned closer to substrate 12 than the surface 142. One or more micro-pillars 124-1 may be uncovered within an area along the recessed surface 144. In the exemplary embodiment shown in FIG. 4C, end surface 134-1 and a portion of edge surface 132-1 of the micro-pillar 124-1 may be uncovered by encapsulation element 140B to form an unencapsulation portion 152 of the bond element 124-1.

[0071] In one embodiment, base 128-1 of a post 124-1 may be joined by a stud bump 165 with the conductive element 26 on the surface 14. The stud bump may consist essentially of one or more of copper, nickel, silver, platinum and gold ends 38 and provide a way of forming conductive interconnects when the post 124-1 is made from a non-wettable metal.

[0072] Similar to the bond elements 24, referring to FIG. 4D, such a configuration of the bond element 124 may provide a connection, such as by a solder ball 170 or the like, to another conductive element by allowing the solder to wick along edge surface 132-1 and join thereto in addition to joining to end surface 134-1, and where the solder may extend along the surface 144 from the edge surface 132-1. Other configurations by which a portion of the bond element 124 may be uncovered by encapsulation element 140B along recessed surface 144 are possible, including ones in which the end surfaces are substantially flush with recessed surface 144.

[0073] Referring again to FIG. 4C, the structure 10-2 may include a bond element 124-2 in the form of a micro-pillar

having a base 128-2 joined by the stud bump 165 to a conductive element 26, and an end surface 134-2 and an edge surface 132-2 extending from the end surface 134-2 defining an unencapsulated portion 152 of the wirebond 124-2 at the surface 142. In another embodiment, the structure 10-2 may include a bond element 124-3 in the form of a micro-pillar formed integrally with the conductive element 26 at the surface 14 and extending from the surface 14 to an end surface 134-3. The bond element 124-3 includes the end surface 134-3 and an edge surface 132-3 extending therefrom as an unencapsulated portion 152 at the surface 142.

In a further embodiment, the element 140B may be configured to include an area that has been etched away, molded, or otherwise formed to define a cavity 175 extending from the surface 142 to the surface 14 of the substrate. cavity 175 may have any suitable shape to permit electrical connection at an end surface 134-4 of a bond element 124-4 that may be formed in the cavity 175, such as by deposition of electrically conductive material therein, where the bond element 124-4 has an end surface 134-4 as the unencapsulated portion 152. In one embodiment, the bond element 124-4 may be formed in a trapezoidally shaped cavity 175, with tapered side walls. The bond element 124-4 may have an end surface 134-4 wider in cross-section than a cross-section of a portion between the base 128-4 and end surface 134-4, where the base 128-4 and end surface 134-4 are parallel and edge surfaces 132-4 extend tapered toward each other from the base 128-4 to the end surface 134-4.

[0075] Referring FIG. 4D, solder 170 may be deposited in the cavity 175 to extend from the end surface 134-4 to above the surface 142 and along portions of the surface 142 extending away from the cavity 175.

[0076] It is to be understand that, in accordance with the disclosure, a structure may include other configurations by which a portion of a bond element is uncovered by an encapsulation element, such at an end surface and optionally along an edge surface thereof, which are similar to those discussed herein with respect to the variations of the configuration of the surface of the encapsulation element remote and facing away from the surface of the substrate.

[0077] Referring again to FIG. 3, for example, the encapsulation elements 40 serve to protect conductive elements 18 within the region 50, including the bond elements 24 connected with the pads 26 within the region 50. This allows for a more robust structure that is less likely to be damaged by testing thereof or during transportation or assembly to other microelectronic structures. Encapsulation element 40 may be formed from a dielectric material with insulating properties such as that described in U.S. Patent App. Pub. No. 2010/0232129, which is incorporated by reference herein in its entirety.

[0078] Referring to FIGs. 3 and 7A, an exemplary pattern for an array of contacts formed by end surfaces 34 of the bond elements 24 of the structure 10 is shown. Such an array may be formed in an area array configuration, variations of which could be implemented using the structures described herein. Such an array may be used to electrically and mechanically connect a microelectronic assembly including the structure 10 to another microelectronic structure, such as to a printed circuit board ("PCB"), or to other packaged microelectronic elements. In such a stacked arrangement, wire bonds 24 and conductive elements 18 and 20 may carry multiple electronic signals therethrough, each having a different signal potential to allow for different signals to be processed by different microelectronic elements in a

single stack. Solder masses may be used to interconnect the microelectronic assemblies in such a stack, such as by electronically and mechanically attaching end surfaces 34 to conductive elements of an external component.

Referring to FIGs. 3 and 7A, the surfaces 14 and of the substrate 14 of the structure 10 extend in horizontal directions  $H_1$  and  $H_2$  and the edges 64 of the structure 90 extend between the upper and lower surfaces. encapsulation elements 40A and 40B mav define microelectronic element receiving region 210 of predetermined size and predetermined shape to accommodate a microelectronic semiconductor element, such as а chip alone, microelectronic assembly or a microelectronic package containing at least one chip, disposed laterally from the elements 40A and 40B and connected to the substrate 12 at a portion of the surface 14 that a bottom portion 212 of the region 210 overlies. For example, referring to FIG. 7A, the bottom portion 212 may have a linear dimension R1 extending in the horizontal direction  ${\rm H}_{\rm 1}$  from the bottom border 58 of the element 40A to the bottom border 58 of the element 40B, and a linear dimension R2 extending in a horizontal direction orthogonal to the direction  $H_1$  between opposing ends 205 of the elements 40 extending in a direction parallel to the horizontal direction  $H_1$ . The region 210 includes a space that extends, at the bottom portion 212, upwardly from exposed portions of the surface 14 and conductive elements 18 at the surface face 14, to a predetermined vertical distance from the surface 14 of the substrate, which may be a height above, the same or below the height of the surface 42 of one or both of the elements 40 as measured vertically from the surface The region 210, thus, includes a space defined between the surfaces 44A, 44B of the encapsulation elements 40A, 40B, respectively. The region 210 is of a predetermined size and

shape that is based on size, shape and positioning of the encapsulation elements 40 on the surface 14 of the substrate, and provides that a portion of a microelectronic element by itself, or within a package or assembly, to be connected to a portion of the substrate that the portion 212 overlies may be disposed in the region 210 without the element, package or assembly contacting the surfaces 42A and 42B.

[0080] A process according to a further embodiment of the invention for manufacture of the structure 10 may use a pre-formed dielectric mass, such as a substrate consisting essentially of dielectric material, and use a mold element (not shown) to form a dielectric mass of the encapsulation element 40 that encapsulates the bond elements 24. In this process, the bond elements connected with pads 26 at the surface 14 of substrate 12 may be present at the time of molding. In one embodiment, the dielectric mass forming the element 40 may be molded over the bond elements 24, which are connected to traces 18 on the surface 14 of the substrate 12.

[0081] In addition, a pre-formed dielectric mass serving as the encapsulation element encapsulating the bond elements to define unencapsulated portions, and having a top surface 42 and edge surfaces 44 and 46, as described above and shown in FIG. 3, may be attached to the portion 50 of the surface 14 of the substrate 12, laterally spaced from another similar encapsulation element, using an adhesive, such as curable adhesive or epoxy.

[0082] In a further step of manufacture of the structure 10 before the encapsulation elements are formed on the substrate 12, traces and pads as the conductive elements 18 may be patterned onto the surface 14. For example, the entire surface 14 may be plated, masked and selectively etched to form the traces. Alternatively, the surface 14 may be covered with a mask material, and then selectively exposed

to laser radiation to cut grooves through the mask. A seed layer may be applied over the mask and into the grooves, whereupon the mask is removed so as to lift off the seed layer everywhere except at the grooves. The surface is then exposed to a plating bath, so that metal is deposited only at the grooves where the seed is present. Any other technique for forming metallic features on a dielectric body may be used.

[0083] In other embodiments, flowable dielectric material used to form the encapsulation element 40 may serve as an adhesive which bonds the encapsulation element to the substrate 12.

Referring to FIGs. 7B, 7C and 7E, alternative arrangements of encapsulation elements on a substrate, which encapsulate bond elements connected with the substrate, may be used to obtain a microelectronic element receiving region, in accordance with embodiments of the disclosure. example, one or more encapsulation elements 300 may be formed on an upper surface 304 of a substrate 312, such as similar to the substrate 12, to have a size, shape and arrangement on the upper surface 304, such as relative to one another, to define a microelectronic element receiving region 302 of size and shape that may accommodate a microelectronic element, package or assembly, similarly as described above for the Referring to FIG. 7B, four encapsulation region 210. elements 300 may be arranged to define the region 302 overlying the upper surface 304 of the substrate 312 and having a bottom portion 306 having horizontally extending dimensions R3 and R4, where R4 is aligned in a thickness direction of the structure with the upper and lower borders of the elements 300A and 300B at the facing edge surfaces thereof, respectively, and R3 is aligned in the thickness direction of the structure with the upper and lower borders

of elements 300C and 300D at the facing edge surfaces thereof, respectively. Referring to FIG. 7C, encapsulation element 300 may be a single element that defines a region 302 having a rectangularly-shaped bottom portion 306, three sides of which are defined by the single element. Referring to FIG. 7E, a single encapsulation element 450 may be arranged overlying upper surface 454 of substrate 456 to define a microelectronic element receiving region 452 having a bottom portion 456 overlying a portion 454A of the surface 454. The element 450 overlies a portion 454B of the surface 454, and the portion 454B completely encloses the portion 454A. The element 450, as such, completely encloses the receiving region 452, at least at a portion of the region 452 that extends vertically away from the portion 454A.

Referring to FIGs. 5 and 7D, in one embodiment a [0085] structure 400, having components similar to those of the structure 10, may include a single encapsulation element 440, or multiple encapsulation sub-elements 440A, 440B and 440C, that encapsulate bond elements 424 to provide, at surfaces 442 of sub-elements 440 facing away from the substrate, unencapsulated portions 452 defined by at least end surfaces 434 of the bond elements 424. For example, referring to FIG. 7D, a single element 440 may define a plurality of microelectronic receiving regions 402A, 402B overlying upper surface 414 of the substrate and having bottom portions 406A, 406B, respectively. Alternatively, the sub-elements 440A, 440B and 440C (indicated in FIG. 7D by portions of the element 440 that do not have cross-hatching) may be arranged in parallel and spaced from each other, similarly as the elements 40A and 40B in FIG. 3 and 4A, to define the regions 402A and 402B.

Referring to FIG. 6, in one embodiment a structure 198001 500, having a construction similar to the structure 10, may include the encapsulation elements 40A, 40B on the surface 14 of the substrate 12 to define the region 210. In addition, an encapsulation element 540 may overlie a portion 560 of the surface 16 and encapsulate bond elements 524 joined to pads 560, within the portion while providing unencapsulated portions 550 defined by end surfaces 534 and portions of edge surfaces 532. In one embodiment, the encapsulation element 540 may at least partially overlie a portion of the surface 14 that the portion 212 overlies. In some embodiments, the encapsulation element 540 may overlie the surface 16 to define at least one microelectronic element receiving region 570 having a bottom portion 572 overlying a portion 574 of the surface 16 extending from the portion 560 to an opposing edge 64 of the substrate 12.

Referring to FIGs. 14 and 15, [0087] in another embodiment of the present disclosure a structure 1010 may include an active die 1012, such as a field programmable gate array, which is provided at the wafer level. The die 1012 may have an active surface 1014 including electrical circuitry 1016 and bond pads 1018. The die 1012 is typically silicon of thickness 730 micrometers, and the electrical circuitry 1016 may be provided by any suitable conventional technique. Alternatively, the die 1012 may be any other suitable material, such as, for example, gallium arsenide and may be of any suitable thickness. A redistribution layer 1020 of dielectric material may extend along the surface 1014. Traces 1022 may be electrically connected to contact pads 1024 at surface 1017 of the layer 1020, the surface 1017 being remote from the surface 1014, and extend through substrate 1026 of the redistribution layer 1020 to the pads 1018 at the surface 1014. Similar to the structure 10 as

shown in FIG. 2, bond elements 24 may be joined at bases thereof with at least some of the pads 1024, which are joined through traces 1022 with pads 1018 at a portion 1050 of the surface 1014. In another embodiment where the redistribution layer 1020 is omitted from the structure, the bases 28 of the bond elements 24 may be joined by solder elements (not shown) with the pads 1018 at the portion 1050.

Referring to FIG. 15, the structure 1010 may further include encapsulation elements 1040A and 1040B, having features similar to the encapsulation elements 40 in the assembly 10 as described above, formed from a dielectric material over the portion 1050 of the surface 1014 of the substrate 12, and defining a top surface 1042 remote and facing away from the die 1012. The material of the element fills spaces between the bond elements unencapsulated portions 52 are defined by at least a portion of the ends 30 of the bond elements 24. In addition, the encapsulation elements 1040A and 1040B may define first edge surfaces 1044A and 1044B, respectively, extending downwardly adjacent the top surface 1042 to the surface 1017 of the redistribution layer 1020, or to the surface 1014 if the layer 1020 is omitted, where the surfaces 1044 are disposed inside peripheral edges 1064 of the die 1012. The elements and 1040B further may include second surfaces 1046A and 1046B, respectively, extending downwardly from the top surface 1042 to the surface 1017 of the layer 1020 or the surface 1014 of the die 1012, similarly as described above for the surfaces 46 of the elements 40 extending to the substrate 12. The encapsulation elements 1040 may be configured similarly as the encapsulation elements 40' and 140, as shown in FIGs. 4A and 4B, to encapsulate bond elements 24 and uncover unencapsulated portions 52 thereof.

[0089] In some embodiment, the dies of numerous structures are provided as a continuous or semi-continuous element such as a strip, tape or sheet. After the encapsulation elements 1040 are formed on the dies, the structures 1010 are then severed along lines of separation to yield the individual structure 1010 having the configuration illustrated in FIG. 15, and where the die 1012 of the structure 1010 extends between opposing edges 1064.

Alternatively, an embodiment of the disclosure may include a structure 1010-1, as shown in FIG. 16A, which includes components similar to those of the structure 1010 described above. Referring to FIG. 16A, the structure 1010-1 may include wire bonds 24-1, some of which may include curved or substantially straight portions similar to those shown in FIG. 4C, encapsulated by an encapsulation element 1040A with respective ends 30-1 thereof that are not positioned directly above bases 28-1 thereof, such that the structure 1010-1 may have an array that is configured differently at a level of the element 1040A, which is remote from the die 1012 compared to at the level of the die 1012 or the redistribution layer 1020. The element 1040A may be configured to include an area that has been etched away, molded, or otherwise formed to define a cavity 1070 extending from a surface 1042 of the element 1040A, which is remote from the die 1012, to a recessed surface 1044 that is positioned closer to the die 1012 than the surface 1042. The bond elements 24-1 may be uncovered in the cavity 1070 within an area along the recessed surface 1044. The cavity 1070 may have any suitable shape to permit electrical connection of the unencapsulated portion 52 at end 30-1 of a bond element 24-1 that is disposed in the cavity 1070. In one embodiment, the unencapsulated portion 52 of the bond element 24-1 may overlie the surface 1044, and be between tapered side walls

1045 of the encapsulation element 1040A extending from the surface 1042 to the surface 1044 that define the cavity 1070.

Additionally, the encapsulation element 1040B may encapsulate bond elements 1124 configured similar to the bond elements 124 as shown in FIG. 4C, and connected at bases 1128 thereof with pads at the surface 1017 of the redistribution layer 1020 or at the surface 1014 of the die 1012. exemplary embodiment shown in FIG. 16A, a bond element 1124 may be uncovered by encapsulation element 1040B to form an unencapsulation portion 1152 defined by an end surface 1134 and a portion of edge surface 1132 of the bond element within a cavity 1070 of the encapsulation element 1040B. embodiment, base 1128 of a post 1124 may be joined by a stud bump 1165 with a pad at the surface 1017 or 1014. Further, a cavity 1075, having a configuration similar to the cavity 175 as shown in FIG. 4C, may be formed in the encapsulation element 1040B and extend from the surface 1042 to the surface 1017, or the surface 1014 if the layer 1020 is omitted. A bond element 1124A, similar to the bond elements 124-2, 124-3 or 124-4, may extend from an end surface 1130A disposed within the cavity 1175, through the cavity 1175 to a base thereof joined with a pad of the die 1012 or layer 1020, where an unencapsulated portion 1152A of the bond element 1124A is defined by the end surface 1130A and an edge surface 1132A extending from the end surface 1130A.

[0092] Referring to FIG. 16B, the bond elements 1124 may provide a connection, such as by a solder element 1170 or the like, to another conductive element by allowing to fill the cavities 1070 or the portions of the cavities 1175 not occupied by the bond elements 1124, so as to encapsulate the unencapsulated portions 52 and 1152 of the bond elements 24-1 and 1124, respectively. In some embodiments, the material forming the solder elements 1170 may be formed on portions of

the surface 1042 extending from the cavities 1070 and 1175. In another embodiment, a surface 1172 of the solder element 1170, remote from the die 1012, may be in a same plane as planar surface 1042 of the encapsulation element 1040.

In another embodiment, a structure 1010-2 (see FIG. 16C) may have components and a configuration similar to the structure 1010-1, except for the following differences. bond elements 24-1 may encapsulated be encapsulation element 1040A such that only the end surfaces 34-1 of the elements 24-1 define the unencapsulated portions 52 thereof, and the end surfaces 34-1 are flush with the surfaces 1044. In addition, the bond elements 1124 having the unencapsulated portions 1152 may be encapsulated by the encapsulation element 1040B such that only the end surfaces 1134 of the elements 1124 define the unencapsulated portions 1152, and the end surfaces 1134 are flush with the surfaces 1044. Further, the bond elements 1124A may be encapsulated by the encapsulation element 1040B such that only the end surfaces 1134A thereof define the unencapsulated portions 1152A, and the end surfaces 1134A are flush with the surfaces 1044. Referring to FIG. 16D, and similarly as described with reference to FIG. 16C, solder elements 1170 may fill the cavities 1070 or the portions of the cavities 1175 not occupied by the bond elements 1124, so as to encapsulate the unencapsulated portions 52 and 1152 of the bond elements 24-1and 1124, respectively.

[0094] In some embodiments, the encapsulation elements overlying the substrate 112, such as in the structures 10 as described above (see FIGs. 3 and 4A-4D), may be configured to encapsulate bond elements and uncover unencapsulated portions 52 similarly as the encapsulation elements overlying the die 1012 in the embodiments of the structures 1010 as shown in FIGs. 16A-16D.

Referring to FIGs. 15 and 7E, similarly as 100951 described above for the structure 10, the encapsulation elements 1040A and 1040B may define a microelectronic element receiving region 1210 of predetermined size and predetermined shape to accommodate a microelectronic element, such as a semiconductor chip alone, a microelectronic assembly or a microelectronic package containing at least disposed laterally from the elements 1040A and 1040B and electrically connected with pads of the die 1012 at a portion of the surface 1014 that a bottom portion 1212 of the region 1210 overlies. For example, referring to FIG. 7E, the encapsulation elements 1040A and 1040B may be in the form of a single, integral encapsulation element 1040, having a configuration similar to the element 450, that overlies an area of the die 1012 that completely encloses an area 1014A or 1017A of the surfaces 1014 or 1017, so to define the region 1210. The region 1201 may have a configuration similar to the region 452 and include a portion 1212, similar to the bottom portion 456, adjacent the die 1012. The region 1210 is of a predetermined size and shape that is based on size, shape and positioning of the encapsulation elements 1040 over the surface 1014 of the die 1012, and provides that a portion of a microelectronic element by itself, or within a package or assembly, to be connected to a portion of the die that the portion 1212 overlies may be disposed in the region 1210 without the element, package or assembly contacting the surfaces 1042A and 1042B.

[0096] Referring to FIG. 8, a package assembly 600 may include a structure of the present disclosure connected to a microelectronic element, package or assembly at the microelectronic element region of the structure. The package assembly 600, for example, may include the structure 10 as described above, connected to a microelectronic element 602.

microelectronic element or chip 602 may include oppositely facing surfaces 605, 607, and be positioned in a "face-down" orientation relative to the substrate 12 in the region 212, with the surface 605 facing the surface 14 of the substrate 12. Contacts 604 at the surface 605 may be bonded by solder elements 609 to conductive elements 618 at the The bottom portion 212 of the region surface 14. overlies the conductive elements 618. The contacts 604 may be electrically connected with terminals 31 from which traces 33 extend on the surface 16 of the substrate 12, and the bond elements 24 within the elements 40A and 40B, through electrical circuitry, such the traces 19 within or conductive vias 22 extending through, the substrate 12. assembly 600 may be joined to an external component 690, such as a printed circuit board, by electrically connecting solder elements 625, such as solder balls, formed at the terminals 31 to contacts (not shown) on a facing surface 692 of the component 690 arranged in a pattern corresponding to that of the terminals 31 of the structure 10.

In one embodiment, the region 210 may be adapted such that, when the microelectronic element 602 is bonded to the substrate 12, opposing edge surfaces 613A and 613B of the microelectronic element 602 that face the edge surfaces 44A and 44B, respectively, are spaced a distance of at least about 200 microns from the edge surfaces 44A, 44B. In some embodiment, the distance of the spacing may permit that dielectric material, for example, underfill, may be provided between the facing surfaces 613A and 44A and the facing surfaces 613B and 44B. In another embodiment, the distance of the spacing may permit molding of dielectric material over the top surface 607 of the microelectronic element 602, which extends between the surfaces 613A and 613B, and the surfaces 613A and 613B.

A dielectric mass or overmold 626 is formed over 186001 the bottom portion 212 of the region 210, such as using any of the techniques described to form the dielectric masses of the encapsulation elements over the substrate 12 discussed above. The dielectric mass 626 has a top surface 628 remote from the surface 14 that extends over the microelectronic element 602 and away from the element 602 over the surface 14 in the horizontal directions  $H_1$  and  $H_2$  toward the edge surfaces 44A and 44B of the encapsulation elements 40A and 40B, respectively. In one embodiment, the top surface 628 extends to the edge surfaces 44A and 44B, and edges surfaces 628A and 628B extend downwardly thereform to the substrate 12 facing, and in some embodiments along and contacting at least portions of, portions of the edge surfaces 44A and 44B, respectively. As such, the dielectric mass 626 may be made from a first dielectric material, and the encapsulation elements 40 may be made from a second dielectric material that is different from the first dielectric material. some embodiments, the dielectric mass 626 may be provided such that the top surface 628 thereof extends over a portion of the surface 42 of an encapsulation element 40. dielectric mass 626 further includes a bottom surface 630 extending from the edges surfaces 628A and 628B in horizontal directions  $H_1$  and  $H_2$  away from the encapsulation elements 40A and 40B and along exposed portions of the surface 14 and traces 618 on the surface 14.

[0099] In one embodiment, a thickness (h) of the encapsulation elements 40, in a thickness direction T of the assembly 600 orthogonal to  $H_1$  and  $H_2$ , extends upwardly away from the surface 14, and is the same as, greater than, or less than a thickness of the microelectronic element 602 in the direction T. In another embodiment, the thickness (h) of at least one of the elements 40 is less than or equal to the

thickness in the direction T of the dielectric mass 626 with the microelectronic element 602 encapsulated therein.

[0100] The assembly 600 may be joined with microelectronic package 2200 that overlies the surface 14 of the substrate 12. The package 2200 may include a substrate 2206 having a first surface 2208 remote from a second surface 2210, where the first surface 2208 faces the surface 42 of the encapsulation elements 40 and the surface 628 of the mass 626. Conductive elements 2212 may extend along the surfaces 2208 and 2210. In addition, a microelectronic element 2214 is positioned in a "face down" orientation facing the surface 2210, and contacts (not shown) of the microelectronic element 2214 are bonded to the conductive elements 2212 on the surface 2210 by solder elements (not shown). Further, the conductive elements 2212 on the surface 2208 may be arranged a pattern corresponding to the pattern of unencapsulated portions 52 of the bond elements 24, and solder elements 2215 may electrically connect such elements 2212 with the unencapsulated portions 52. A dielectric mass 2220 may be formed over the microelectronic element 2214 and uncovered portions of the surface 2210 to encapsulate the element 2202 and the surface 2210 of the substrate 2206, such as using any of the techniques described to form a dielectric mass. A surface 2222 of the mass 2220, remote from the substrate 2206, overlies the microelectronic element 2214 and portions of the surface 2210 adjacent the element 2214. As such, the bond elements 24 may electrically interconnect conductive elements of the package 2200 with conductive elements of the assembly 600 and conductive elements of the external component 690.

[0101] In another embodiment, referring to FIG. 9, a package assembly 600' may have a similar construction as the assembly 600 shown in FIG. 8, except that end surfaces 34 of

the bond elements 24 are flush with the surface 42, the chip 602 is joined by wire leads 622 to traces 618 on the substrate and the assembly 600' further includes a redistribution layer 654. For example, the surface 607 of the chip 602 may be attached by an adhesive layer 611 with a portion of the layer 14 that the portion 212 overlies, and the wire leads 622 may extend from the contacts 604, over the surface 607 and an edge surface 613 of the chip 602, to the traces 618. Further, the layer 654 may be formed of dielectric material and extend along a portion of the surface 42 of at least one of the encapsulation elements 40, or a portion of the surface 628 of the mass 626. embodiment, the redistribution layer 654 may overlie only the portion 50 of the structure 10. In an embodiment, the portion 212 may overlie a portion of the redistribution layer 654. Traces 658 may be electrically connected to inner contact pads 661 which are electrically connected to the end surfaces 34 of bond elements 24 and extend through substrate 656 of the redistribution layer 654 to contact pads 660 at surface 662 of the substrate 656. Another microelectronic assembly may then be connected to the contact pads 660 by solder masses or the like. redistribution layer 654, in effect, serves as what is known as a fan-out layer that may allow the assembly 600' to connect to an array of a different configuration than the conductive element 26 array within the portion 50 would otherwise permit.

[0102] In a further embodiment, the assembly 600' may be joined with a microelectronic package, such as the package 2200 as described above (see FIG. 8), that overlies the redistribution layer 654. The surface 2208 of the package 2202 may face the surface 662 of the layer 654, and the conductive elements 2212 of the package 220 at the surface

2208 may be arranged in a pattern corresponding to the pattern of the contact pads 660 at the surface 662 of the layer 654. Solder elements 2215 may electrically connect such elements 2212 with the contact pads 660. As such, the conductive elements of the package 2200 may be electrically connected, through conductive elements of the redistribution layer and the bond elements 24, with conductive elements of the assembly 600' and conductive elements of the external component 690.

[0103] It is to be understood that, in accordance with the disclosure, a microelectronic element or a microelectronic package may be mounted "face-up" or "face-down" and coupled to a surface, such as a surface (e.g., 14, 16) of a substrate of a structure according to the disclosure or a surface (e.g., 692) of an external component joined with a package assembly including such structure, by wire bond, ball bond or other known connection technique.

In another embodiment, referring to FIG. 10A, a package assembly 700 may include a structure, according to the disclosure, joined with a plurality of microelectronic elements, where some of the microelectronic elements may be part of microelectronic packages. Referring to FIG. 10A, the assembly 700 may include the structure 10 as described above, and a microelectronic element 702 with its contacts 703 facing the surface 16 and electrically connected to pads 25 the conductive elements 20 at the surface 16. dielectric mass 704 is formed over the microelectronic element 702 and the surface 16, and has a surface 706 overlying the element 702 and the surface 16. The mass 704 covers the microelectronic element 702 and the surface 16, similarly as described above for the dielectric mass 626 formed over the element 602 and the surface 14 as in FIG. 8.

[0105] In addition, the package assembly 700 may include a microelectronic element 732 connected with conductive elements at the surface 14. The microelectronic element 732, similar to the microelectronic element 602, may be positioned in a "face-down" orientation relative to the surface 14 of the substrate 12 in the region 710, with the surface 735 facing the surface 14 of the substrate 12. Contacts 736 at surface 735 may be bonded by solder elements to conductive elements 738 at the surface 14. The bottom portion 712 of the region 710 overlies the conductive elements 738. The contacts 736 may be electrically connected with other conductive components or elements electrically connected with the contacts 736 through electrical interconnections within the substrate 12, and also the bond elements 24 encapsulated within the elements 40A and 40B.

In addition, a mass of dielectric material 748 may [0106] be formed over the portion 712 of the region 710, similarly as discussed above for the overmold 628. The dielectric mass 748 has a surface 750 remote from the surface 14 that extends over the microelectronic element 732 and away from the element 732 over the surface 14 in the horizontal directions and  $H_2$  toward the edge surfaces 44A and 44B of the encapsulation elements 40A and 40B, respectively. embodiment, the surface 750 may be spaced from the edge surfaces 44A and 44B, and the mass 748 includes edge surfaces 752A and 752B extending downwardly therefrom to the substrate 12 facing and spaced from the edge surfaces 44A and 44B, respectively. In another embodiment, one of the surfaces 752, such as the edge surface 752A, may at least partially contact a portion of the edge surface 44A. dielectric mass 748 may be made from a first dielectric material, and the encapsulation elements 40 may be made from a second dielectric material that is different from the first

dielectric material. The dielectric mass 748 further includes a bottom surface 754 extending along exposed portions of the surface 14 and traces 738 at the surface 14 in horizontal directions  $\rm H_1$  and  $\rm H_2$  and spaced from the elements 40A and 40B.