(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6097574号

(P6097574)

(45) 発行日 平成29年3月15日(2017.3.15)

(24) 登録日 平成29年2月24日(2017.2.24)

(51) Int.Cl.

HO4N 5/378 (2011.01)

F 1

HO4N 5/335 780

請求項の数 17 (全 19 頁)

(21) 出願番号 特願2013-12437 (P2013-12437)

(22) 出願日 平成25年1月25日 (2013.1.25)

(65) 公開番号 特開2014-146849 (P2014-146849A)

(43) 公開日 平成26年8月14日 (2014.8.14)

審査請求日 平成28年1月21日 (2016.1.21)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】撮像装置、その駆動方法、及び撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換部を各々が備える複数の画素が複数の行及び複数の列を形成するように配され、前記光電変換部で発生した電荷に基づく信号を第1の信号として出力する画素アレイと、

前記第1の信号に対して、第1の電位から第2の電位まで変化する第1の参照信号を用いて第1のアナログデジタル変換を行う第1のA/Dコンバータと、

前記第1の信号に対して、前記第1の電位とは異なる第3の電位から前記第2の電位とは異なる第4の電位まで変化する第2の参照信号を用いて第2のアナログデジタル変換を行う第2のA/Dコンバータと、

前記第1のA/Dコンバータにおける前記第1のアナログデジタル変換により得られた第1のデジタル信号、および、前記第2のA/Dコンバータにおける前記第2のアナログデジタル変換により得られた第2のデジタル信号のうちの一方を出力する第1の出力部と、

前記第1の出力部の出力が前記第1のデジタル信号および前記第2のデジタル信号のいずれであるかを示す情報を出力する第2の出力部と、を備える、

ことを特徴とする撮像装置。

## 【請求項 2】

前記第2のA/Dコンバータは、前記第2のアナログデジタル変換を、前記第1のA/Dコンバータによる前記第1のアナログデジタル変換と並列に行う

ことを特徴とする請求項1に記載の撮像装置。

**【請求項 3】**

前記第1の参照信号および前記第2の参照信号はともにランプ信号であり、

前記第2の参照信号は、前記第1の参照信号と同じ傾きを有し、前記第1の参照信号に

対してオフセット成分を有する、

ことを特徴とする請求項2に記載の撮像装置。

**【請求項 4】**

信号出力部および容量をさらに備え、

前記信号出力部は、前記容量の充電を行った後に前記ランプ信号を出力することによつ

て、当該ランプ信号を前記第1の参照信号として出力し、前記充電によって生じた前記容

量の電圧を前記第1の参照信号に対する前記オフセット成分とする前記第2の参照信号と

して出力する、

ことを特徴とする請求項3に記載の撮像装置。

**【請求項 5】**

前記第1の参照信号および前記第2の参照信号はともにランプ信号であり、

前記画素アレイからの信号のダイナミックレンジは、互いに異なるレンジ幅である第1

の範囲および第2の範囲を有しており、

前記第1の参照信号は、前記第1の範囲および前記第2の範囲の一方に含まれる信号の

アナログデジタル変換に用いられ、

前記第2の参照信号は、前記第1の範囲および前記第2の範囲の他方に含まれる信号の

アナログデジタル変換に用いられ、

前記第1の参照信号と前記第2の参照信号との傾きの比は、前記第1の範囲と前記第2

の範囲とのレンジ幅の比にしたがう、

ことを特徴とする請求項1乃至4のいずれか1項に記載の撮像装置。

**【請求項 6】**

前記第1のA Dコンバータは、カウントアップおよびカウントダウンの少なくとも一方

を行って、前記画素アレイからの前記信号と前記第1の参照信号との大小関係が逆転する

までの時間を計測するカウンタを含み、

前記第2のA Dコンバータは、カウントアップおよびカウントダウンの少なくとも一方

を行って、前記画素アレイからの前記信号と前記第2の参照信号との大小関係が逆転する

までの時間を計測するカウンタを含む、

ことを特徴とする請求項1乃至5のいずれか1項に記載の撮像装置。

**【請求項 7】**

光電変換部を各々が備える複数の画素が複数の行及び複数の列を形成するように配され

、前記光電変換部で発生した電荷に基づく信号を第1の信号として出力する画素アレイと

前記第1の信号とは極性が異なる一定の信号を出力する第1のユニットと、

前記第1のユニットまたは前記画素アレイに接続され、前記画素アレイからの前記第1

の信号の積分を行った後に前記第1のユニットからの信号の積分を行う第2のユニットと

、前記第2のユニットからの出力信号と第1の参照信号との比較を行うことによって第1

のアナログデジタル変換を行う第1のA Dコンバータと、

前記第1のA Dコンバータによる前記第1のアナログデジタル変換と並列に、前記第2

のユニットからの前記出力信号と、前記第1の参照信号とは異なる第2の参照信号との比

較を行うことによって第2のアナログデジタル変換を行う第2のA Dコンバータと、

前記第1のA Dコンバータにおける前記第1のアナログデジタル変換により得られた第

1のデジタル信号、および前記第2のA Dコンバータにおける前記第2のアナログデジタ

ル変換により得られた第2のデジタル信号のうちの一方を出力する第1の出力部と、

前記第1の出力部の出力が前記第1のデジタル信号および前記第2のデジタル信号のい

ずれであるかを示す情報を出力する第2の出力部と、を備え、

前記第1の参照信号は、前記第2のユニットからの出力信号のダイナミックレンジにお

10

20

30

40

50

ける第1の範囲および第2の範囲のうちの一方に含まれる信号との比較に用いられ、前記第2の参照信号は、前記第1の範囲および前記第2の範囲のうちの他方に含まれる信号との比較に用いられる、

ことを特徴とする撮像装置。

【請求項8】

前記第1のA/Dコンバータは、第1のレジスタ、前記第1のレジスタの値を第1の参照信号に基づいて第1のアナログ信号に変換する第1のD/Aコンバータ、および前記画素アレイからの前記信号と前記第1のアナログ信号とを比較する第1のコンパレータを含み、

前記第2のA/Dコンバータは、第2のレジスタ、前記第2のレジスタの値を第2の参照信号に基づいて第2のアナログ信号に変換する第2のD/Aコンバータ、および前記画素アレイからの前記信号と前記第2のアナログ信号とを比較する第2のコンパレータを含み、

前記第1のアナログ信号は、前記画素アレイからの信号のダイナミックレンジにおける第1の範囲および第2の範囲のうちの一方に含まれる信号との比較に用いられ、前記第2のアナログ信号は、前記第1の範囲および前記第2の範囲のうちの他方に含まれる信号との比較に用いられる、

ことを特徴とする請求項1に記載の撮像装置。

【請求項9】

前記第1の出力部からの前記第1のデジタル信号および前記第2のデジタル信号の一方と、前記第2の出力部からの前記情報とを、当該情報を1ビットのヘッダとして含むデジタル信号で出力する、

ことを特徴とする請求項1乃至8のいずれか1項に記載の撮像装置。

【請求項10】

前記第1のA/Dコンバータは、前記複数の画素の前記複数の列のそれぞれに対応してそれぞれ配されており、前記第2のA/Dコンバータは、前記複数の列のそれぞれに対応してそれぞれ配されている、

ことを特徴とする請求項1乃至9のいずれか1項に記載の撮像装置。

【請求項11】

スイッチ部をさらに備えており、

前記撮像装置は、前記画素アレイの前記複数の列のそれから信号を読み出す第1モードと、当該複数の列のうちの第1群のそれから信号を読み出す第2モードとを動作モードとして含み、

前記スイッチ部により、前記第1モードにおいては、前記第1のA/Dコンバータが前記第1群のうちの1列に対応し、前記第2のA/Dコンバータが前記第1群とは異なる第2群のうちの1列に対応し、前記第2モードにおいては、前記第1のA/Dコンバータおよび前記第2のA/Dコンバータが前記第1群のうちの1列に対応する、

ことを特徴とする請求項1乃至9のいずれか1項に記載の撮像装置。

【請求項12】

前記第1の出力部は、前記第1のA/Dコンバータの出力に基づいて、前記第1のデジタル信号および前記第2のデジタル信号のうちの一方を選択するセレクタを含む、

ことを特徴とする請求項1乃至11のいずれか1項に記載の撮像装置。

【請求項13】

前記第1の出力部は、前記第1のA/Dコンバータからの前記出力を保持するラッチをさらに含む、

ことを特徴とする請求項12に記載の撮像装置。

【請求項14】

複数の画素を有する画素アレイと、

前記画素アレイからの信号であって第1の範囲に含まれる値を有する信号に対して第1のアナログデジタル変換を行う第1のA/Dコンバータと、

前記第1のA/Dコンバータによる前記第1のアナログデジタル変換と並列に、前記画素アレイからの信号であって前記第1の範囲とは異なる第2の範囲に含まれる値を有する信

10

20

30

40

50

号に対して第2のアナログデジタル変換を行う第2のA Dコンバータと、

前記第1のA Dコンバータにおける前記第1のアナログデジタル変換により得られた第1のデジタル信号、および、前記第2のA Dコンバータにおける前記第2のアナログデジタル変換により得られた第2のデジタル信号のうちの一方を出力する第1の出力部と、

前記第1の出力部の出力が前記第1のデジタル信号および前記第2のデジタル信号のいずれであるかを示す情報を出力する第2の出力部と、を備える、

ことを特徴とする撮像装置。

【請求項15】

請求項1乃至14のいずれか1項に記載の撮像装置と、

前記撮像装置から出力される信号を処理する処理部と、

を備えることを特徴とする撮像システム。

10

【請求項16】

光電変換部を各々が備える複数の画素が複数の行及び複数の列を形成するように配され、前記光電変換部で発生した電荷に基づく信号を第1の信号として出力する画素アレイを備える撮像装置の駆動方法であって、

前記第1の信号に対して、第1の電位から第2の電位まで変化する第1の参照信号を用いて第1のアナログデジタル変換を行う第1の変換工程と、

前記第1の信号に対して、前記第1の電位とは異なる第3の電位から前記第2の電位とは異なる第4の電位まで変化する第2の参照信号を用いて第2のアナログデジタル変換を行う第2の変換工程と、

20

前記第1の変換工程により得られた第1のデジタル信号および前記第2の変換工程により得られた第2のデジタル信号のうちの一方を出力する第1の出力工程と、

前記第1の出力工程での出力が前記第1のデジタル信号および前記第2のデジタル信号のいずれであるかを示す情報を出力する第2の出力工程と、を含む、

ことを特徴とする撮像装置の駆動方法。

【請求項17】

複数の画素を有する画素アレイを備える撮像装置の駆動方法であって、

前記画素アレイからの信号であって第1の範囲に含まれる値を有する信号に対して第1のアナログデジタル変換を行う第1の変換工程と、

30

前記第1の変換工程と並列に、前記画素アレイからの信号であって前記第1の範囲とは異なる第2の範囲に含まれる値を有する信号に対して第2のアナログデジタル変換を行う第2の変換工程と、

前記第1の変換工程により得られた第1のデジタル信号および前記第2の変換工程により得られた第2のデジタル信号のうちの一方を出力する第1の出力工程と、

前記第1の出力工程での出力が前記第1のデジタル信号および前記第2のデジタル信号のいずれであるかを示す情報を出力する第2の出力工程と、を含む、

ことを特徴とする撮像装置の駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

40

本発明は、撮像装置、その駆動方法、及び撮像システムに関する。

【背景技術】

【0002】

特許文献1には、2つのA Dコンバータを画素アレイの1列に対応させることにより、画素アレイの各列からの画素信号に対して2つの信号処理を並列に行う撮像装置の構成が開示されている。2つのA Dコンバータのそれぞれはコンパレータおよびカウンタを有する。2つのコンパレータには、変化の範囲が互いに異なるランプ信号が入力され、各コンパレータは当該ランプ信号と画素信号との比較を行う。2つのカウンタのそれぞれは、当該カウンタに対応するコンパレータの比較時間を計測し、その計測結果(カウンタ値)をそれぞれ出力する。

50

**【0003】**

以上のような構成により、1つの画素信号から2つのカウンタ値が得られ、これら2つのカウンタ値をデータ転送した後に加算することによって当該画素信号に対応するデジタル信号が得られる。特許文献1によると、1つの画素信号が2つのA/Dコンバータに入力され、変化の範囲が互いに異なる2つのランプ信号を用いるためコンパレータにおける比較時間が半減され、撮像装置のフレームレートが向上する。

**【先行技術文献】****【特許文献】****【0004】**

【特許文献1】特開2011-35689号公報

10

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

特許文献1のような方式の撮像装置では、例えば、カウント値を16進数で表すと、カウント値0(0000)～F(1111)のうち、カウント値0～7に対応するアナログ信号についての比較および計測は一方のA/Dコンバータが担う。また、カウント値8～Fに対応するアナログ信号についての比較および計測は他方のA/Dコンバータが担う。

**【0006】**

例えば、カウント値3に対応するアナログ信号が入力された場合は、一方のA/Dコンバータからカウント値3が得られ、他方のA/Dコンバータから最大カウント値(値としては0であり、オーバーフローを示す。)が得られ、これらが加算されると考えられる。カウント値Bに対応するアナログ信号が入力された場合は、一方のA/Dコンバータから最大カウント値(値としては8であり、オーバーフローを示す。)が得られ、他方のA/Dコンバータからカウント値3が得られ、これらが加算されると考えられる。

20

**【0007】**

2つのデータのうちの一方はオーバーフローを示す最大カウント値であることから、得られたデータの2つをそのまま出力する必要はなく、特許文献1のデータ処理方法によると、過剰な量のデータが転送されると言える。このことは、特に、外部I/Cに出力するような場合には負荷の大きいバスを駆動することになり、消費電力の増大をもたらしうる。

30

**【0008】**

本発明の目的は、画素信号の信号処理に有利な技術を提供することにある。

**【課題を解決するための手段】****【0009】**

本発明の1つの側面は、撮像装置に係り、前記撮像装置は、光電変換部を各々が備える複数の画素が複数の行及び複数の列を形成するように配され、前記光電変換部で発生した電荷に基づく信号を第1の信号として出力する画素アレイと、前記第1の信号に対して、第1の電位から第2の電位まで変化する第1の参照信号を用いて第1のアナログデジタル変換を行う第1のA/Dコンバータと、前記第1の信号に対して、前記第1の電位とは異なる第3の電位から前記第2の電位とは異なる第4の電位まで変化する第2の参照信号を用いて第2のアナログデジタル変換を行う第2のA/Dコンバータと、前記第1のA/Dコンバータにおける前記第1のアナログデジタル変換により得られた第1のデジタル信号、および、前記第2のA/Dコンバータにおける前記第2のアナログデジタル変換により得られた第2のデジタル信号のうちの一方を出力する第1の出力部と、前記第1の出力部の出力が前記第1のデジタル信号および前記第2のデジタル信号のいずれであるかを示す情報を出力する第2の出力部と、を備える。

40

**【発明の効果】****【0010】**

本発明によれば、画素信号の信号処理に有利である。

**【図面の簡単な説明】****【0011】**

50

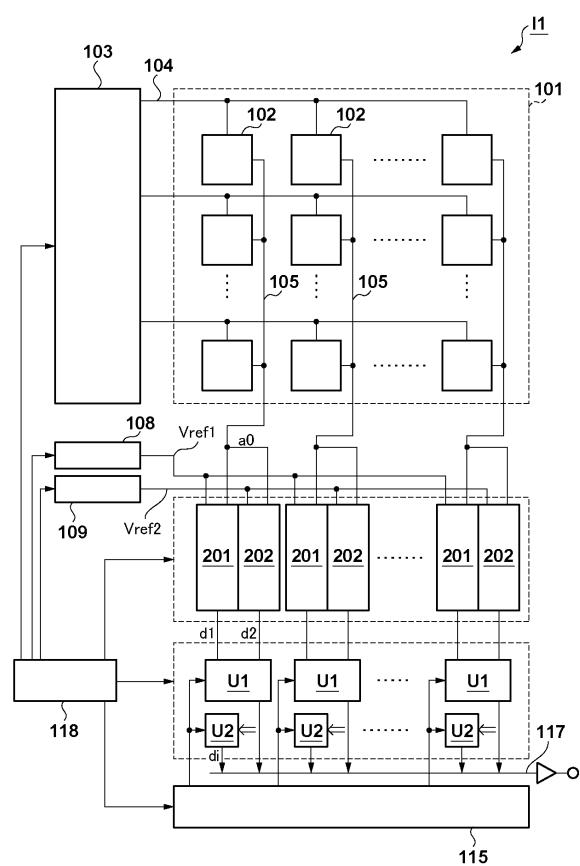

- 【図1】第1実施形態の撮像装置の構成例を説明する図。

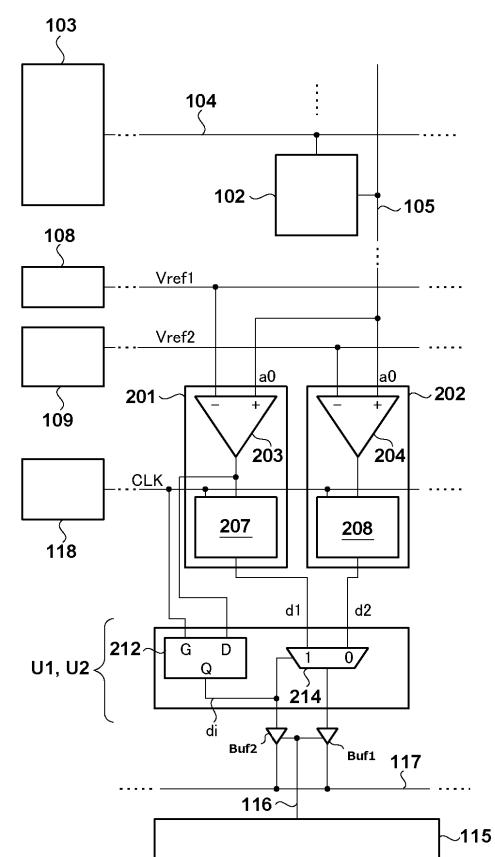

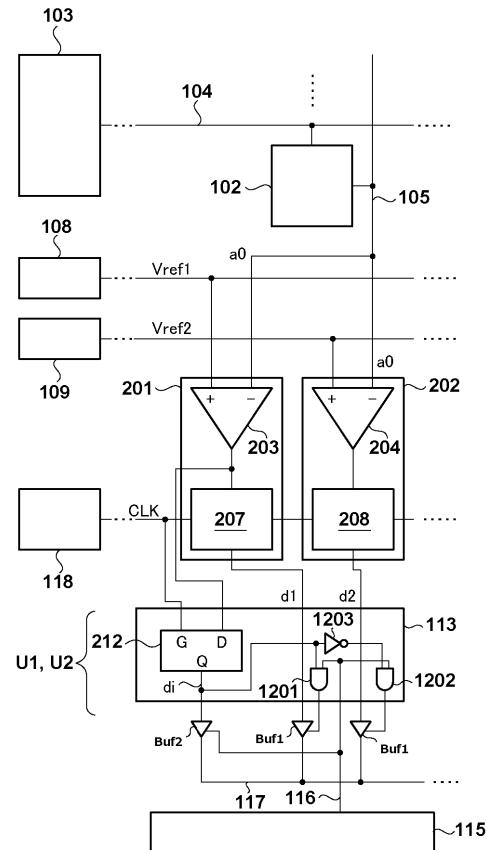

- 【図2】第1実施形態の撮像装置の構成例を説明する図。

- 【図3】第1実施形態の撮像装置におけるセレクタの構成例を説明する図。

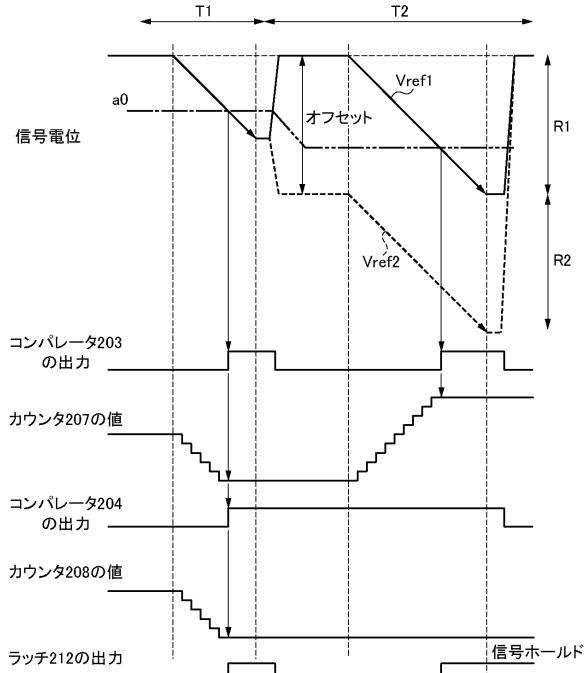

- 【図4】第1実施形態の撮像装置の動作タイミングチャートを説明する図。

- 【図5】第1実施形態の撮像装置の動作タイミングチャートを説明する図。

- 【図6】第1実施形態の撮像装置の他の構成例を説明する図。

- 【図7】第1実施形態の撮像装置の他の動作タイミングチャートを説明する図。

- 【図8】第2実施形態の撮像装置の構成例を説明する図。

- 【図9】第2実施形態の撮像装置の動作タイミングチャートを説明する図。

- 【図10】第2実施形態の撮像装置の動作タイミングチャートを説明する図。 10

- 【図11】第3実施形態の撮像装置の構成例を説明する図。

- 【図12】第3実施形態の撮像装置の動作タイミングチャートを説明する図。

- 【図13】第3実施形態の撮像装置の動作タイミングチャートを説明する図。

- 【図14】第4実施形態の撮像装置の構成例を説明する図。

- 【図15】第4実施形態の撮像装置の他の構成例を説明する図。

- 【図16】第4実施形態の他の構成例における動作タイミングチャートを説明する図。

- 【発明を実施するための形態】

- 【0012】

- (第1実施形態)

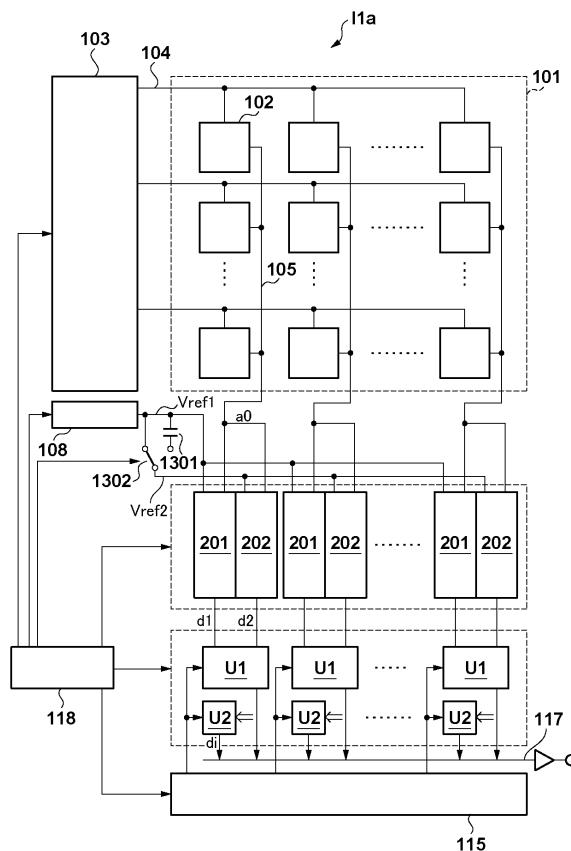

- 図1乃至7を参照しながら、第1実施形態の撮像装置I1を説明する。図1は、撮像装置I1の構成を示している。撮像装置I1は、画素アレイ101、ADコンバータ201(第1のADコンバータ)、ADコンバータ202(第2のADコンバータ)、出力部U1(第1の出力部)、および出力部U2(第2の出力部)を備える。また、撮像装置I1は、タイミングジェネレータ118、垂直走査回路103、水平走査回路115、信号出力部108および信号出力部109を備えうる。 20

- 【0013】

- 画素アレイ101は、複数の画素102が複数の行及び複数の列を形成するように配されて構成されうる。画素102は、公知の構成を採ればよく、例えば、光電変換部(例えば、フォトダイオード)と、入射光により当該光電変換部で発生した電荷の量に相当する信号を読み出すための1または2以上のトランジスタとを含みうる。当該トランジスタには、画素アレイ101の各行に対応して配された信号線104を介して、垂直走査回路103から制御信号が供給され、これにより、列信号線105を介して各画素102から信号(画素信号)が読み出されうる。 30

- 【0014】

- ADコンバータ201、ADコンバータ202、出力部U1および出力部U2は、それぞれ、例えば、画素アレイ101の各列に対応して設けられる。ADコンバータ201は、画素アレイ101からの信号0(アナログ信号)に対してアナログデジタル変換(AD変換)を行う(第1のアナログデジタル変換)。ADコンバータ202は、ADコンバータ201と並列に配されうる。ADコンバータ202は、ADコンバータ201によるAD変換と並列に、画素アレイ101からの信号0に対してAD変換を行う(第2のアナログデジタル変換)。 40

- 【0015】

- 出力部U1は、ADコンバータ201のAD変換により得られたデジタル信号d1(第1の結果)およびADコンバータ202のAD変換により得られたデジタル信号d2(第2の結果)のうちの一方を出力する。また、出力部U2は、出力部U1がデジタル信号d1およびデジタル信号d2のいずれを出力したかを示す情報diを出力する。

- 【0016】

- 水平走査回路115は、出力部U1および出力部U2からの出力(データ)を列ごとに読み出すように制御し、バス117を介して当該データの水平転送を順に行い、不図示の外部回路(例えば、データ処理を行う処理部)に出力する。タイミングジェネレータ11

- 50

8は、クロック信号等を含む基準信号ないし制御信号を上述のモジュールの各々に供給し、これによって各モジュールは各々の構成にしたがう動作を行う。

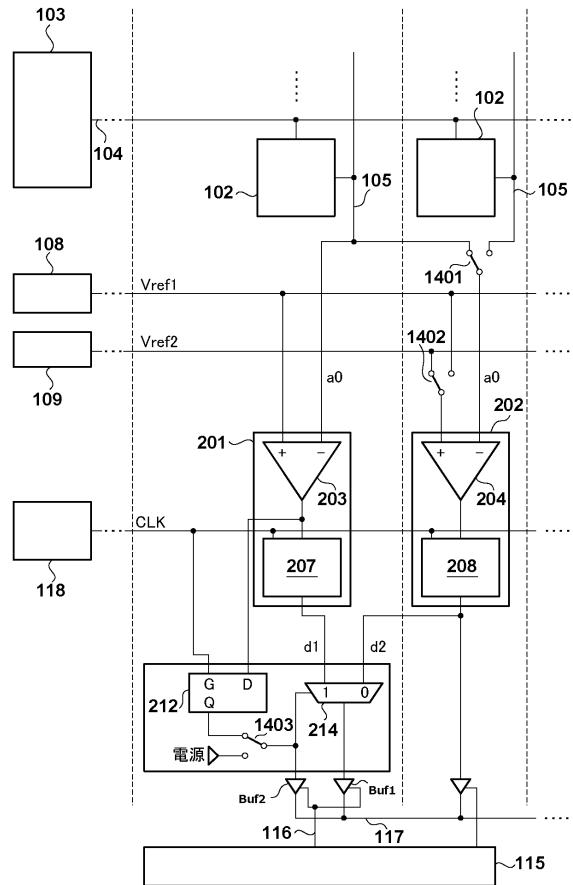

【0017】

図2は、撮像装置I1のうち、ADコンバータ201、ADコンバータ202、出力部U1および出力部U2の部分のより具体的な構成例を、画素アレイ101の1列分について示している。ADコンバータ201は、例えば、コンパレータ203およびカウンタ207を含む。ADコンバータ201は、コンパレータ203およびカウンタ207を用いて画素アレイ101からの信号0と、ランプ信号Vref1(第1の参照信号)との比較を行うことによってAD変換を行う。ランプ信号Vref1は、例えば、信号出力部108からADコンバータ201に供給されうる。カウンタ207は、画素アレイ101からの信号0と、ランプ信号Vref1との大小関係が逆転するまでの時間を、例えば、タイミングジェネレータ118からのクロック信号CLKを用いて計測する。カウンタ207は、カウントアップおよびカウントダウンの少なくとも一方を行う。

【0018】

ADコンバータ202は、ADコンバータ201と同様にして、画素アレイ101からの信号0と、ランプ信号Vref1とは異なるランプ信号Vref2(第2の参照信号)との比較を行う。ランプ信号Vref2は、例えば、信号出力部109からADコンバータ202に供給されうる。ランプ信号Vref1とランプ信号Vref2とは、例えば、互いに同じ傾きを有しており、ランプ信号Vref2は、ランプ信号Vref1に対してオフセット成分を有する。このようにして、画素アレイ101からの信号0について、2つのAD変換が並列に為され、デジタル信号d1およびd2がそれぞれ得られる。

【0019】

出力部U1は、デジタル信号d1およびデジタル信号d2のうちの一方を出力する。出力部U2は、出力部U1がデジタル信号d1およびデジタル信号d2のいずれを出力したかを示す情報diを出力する。出力部U1は、例えばセレクタ214およびバッファBuff1を用いて構成され、出力部U2は、例えばラッチ212およびバッファBuff2を用いて構成されうる。バッファBuff1およびBuff2には、水平走査回路115から信号線116を介して、水平転送を行うための制御信号が入力されうる。ラッチ212は、コンパレータ203からの出力を保持し、セレクタ214は、ラッチ212が保持する情報に基づいて、デジタル信号d1およびデジタル信号d2のうちの一方を選択して出力する。セレクタ214は、例えば、所定の制御信号に基づいて、2つの入力信号のうちの一方を出力するように構成されればよく、図3に示されるように、AND回路やインバータ等の論理回路を用いて構成されうる。また、出力部U1および出力部U2からの信号のそれぞれは、例えば、バッファを介してバス117にそれぞれ出力されうる。

【0020】

以下、図4および図5を参照しながら、撮像装置I1において画素信号を読み出すためのシーケンスを説明する。撮像装置I1によると、1回目の信号読み出しが第1期間T1において為され、2回目の信号読み出しが第2期間T2において為されうる。第1期間T1では、画素102の状態を初期化(リセット)した直後の信号(N成分と称する)が読み出されうる。第2期間T2では、当該初期化から所定の時間が経過した後に画素102からの信号(S成分と称する)が読み出されうる。その後、これら2つの信号の差分についてAD変換が為される。ここで、S成分は、画素102において生じる電荷の量、すなわち画素102への入射光の光量にしたがうため、例えば、入射光の光量が多いときはN成分とS成分との差が大きく、光量が少ないときは当該差が小さくなる。なお、画素信号の読み出し方法は、本実施形態で例示する回路構成に限られず、例えば、相関二重サンプリング(CDS)法にしたがう回路構成を採用してもよい。画素アレイ101とADコンバータ201及び202との間にCDS回路を備える場合には、CDS回路の入力部をリセットしたことによる信号がN成分として第1期間T1に読み出されうる。また、CDS回路を介して出力された画素102からの信号がS成分として第2期間T2に読み出されうる。

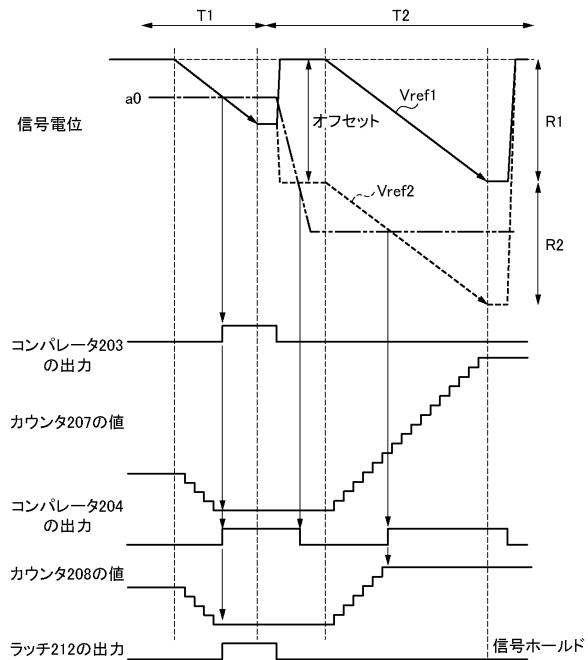

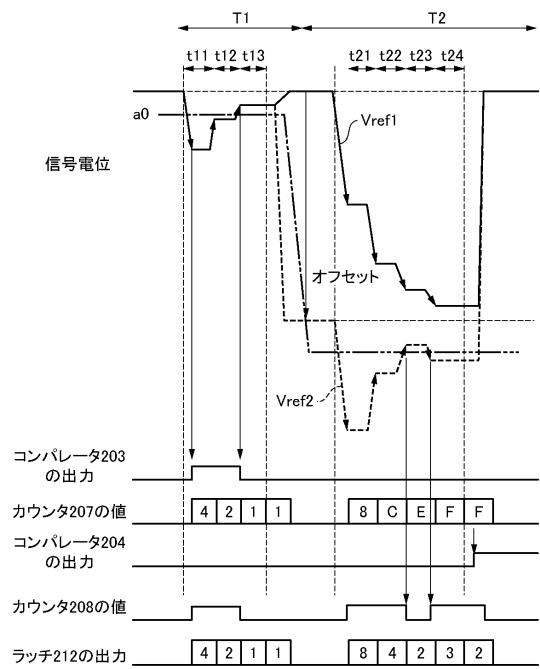

## 【0021】

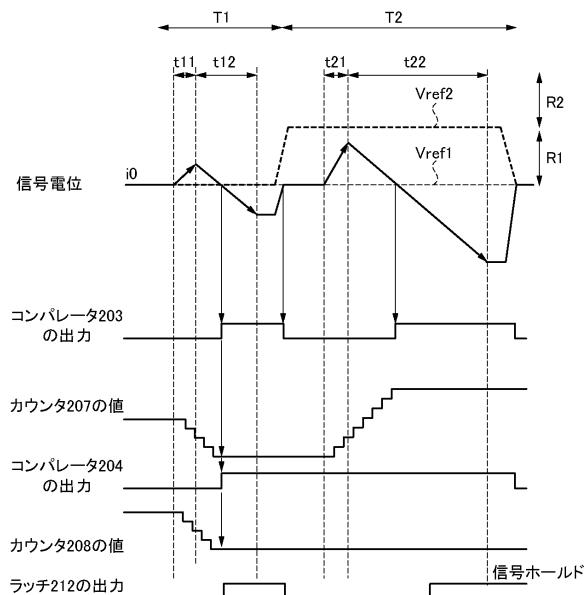

図4は、画素102への入射光の光量が少ない、すなわち輝度レベルが低い場合（低照度時）における撮像装置I1のタイミングチャートを示している。まず、第1期間T1では、N成分の信号についてAD変換を行いういネーブル信号がタイミングジェネレータ118から出力され、1回目の比較が為される。第1期間T1では、ADコンバータ201において、N成分の信号とランプ信号Vref1との比較が為される。当該比較においては、カウンタ207はカウントダウン動作を行う。2つの信号の大小関係が逆転した（例えば、コンパレータ203の出力がLowレベルからHiレベルになった）とき、カウンタ207によるカウントダウンは停止される。ADコンバータ202においては、ADコンバータ201と同様にして、N成分の信号とランプ信号Vref2との比較が為されうる。

10

## 【0022】

次に、第2期間T2では、S成分の信号についてAD変換を行いういネーブル信号がタイミングジェネレータ118から出力され、2回目の比較が為される。第2期間T2では、ADコンバータ201において、S成分の信号とランプ信号Vref1との比較が為される。当該比較においては、カウンタ207はカウントアップ動作を行う。2つの信号の大小関係が逆転したとき、カウンタ207によるカウントアップは停止される。第1期間T1におけるカウントダウンおよび第2期間T2におけるカウントアップの結果により、カウンタ207の初期値からの変化分が、取得すべきデジタル信号として得られうる。

## 【0023】

20

また、第2期間T2では、ADコンバータ202においては、ADコンバータ201と同様にして、S成分の信号とランプ信号Vref2との比較が為されうる。前述のとおり、ランプ信号Vref1とランプ信号Vref2とは、例えは、互いに同じ傾きを有しており、ランプ信号Vref2は、ランプ信号Vref1に対してオフセット成分を有する。輝度レベルが低い本ケースにおいては、ADコンバータ202のコンパレータ204の比較結果は第1期間T1の後から反転したまま（ここでは、コンパレータ204の出力がHiレベルのまま）である。すなわち、ADコンバータ202においては、画素アレイからの信号0は、コンパレータ204による比較が可能な範囲を超えていたため、カウンタ208によるカウントアップを省略してもよい。

## 【0024】

30

よって、輝度レベルが低い本ケースにおいては、ラッチ212は、ADコンバータ201のコンパレータ203からの出力であるHiレベル「1」を保持する。セレクタ214は、これに基づいて、デジタル信号d1を選択して出力する。

## 【0025】

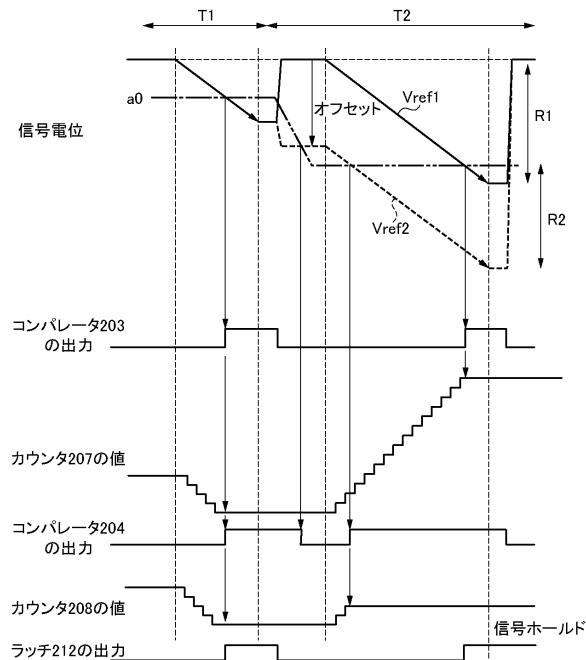

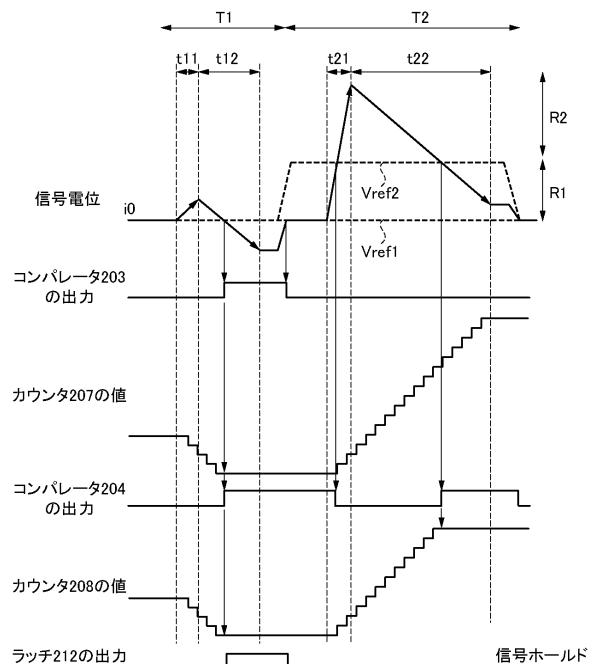

図5は、画素102への入射光の光量が多い、すなわち輝度レベルが高い場合（高照度時）における撮像装置I1のタイミングチャートを、図4と同様にして示している。第1期間T1については、図4と同様であるため説明を省略する。第2期間T2では、輝度レベルが高い本ケースにおいては、S成分が大きいため、ADコンバータ201のコンパレータ203の比較結果は第1期間T1の後から反転しない（ここでは、Lowレベルのまま）。一方で、ADコンバータ202のコンパレータ204の比較結果は第1期間T1の後に反転する（ここでは、LowレベルからHiレベルになる）。よって、輝度レベルが高い本ケースにおいては、ラッチ212はLowレベル「0」を保持し、これに基づいて、セレクタ214はデジタル信号d2を選択して出力する。

40

## 【0026】

撮像装置I1の構成によると、ランプ信号Vref1は、例えは、画素アレイ101からの信号0のダイナミックレンジにおける第1の範囲R1および第2の範囲R2のうちの一方（例えは、範囲R1）に含まれる信号との比較に用いられうる。また、ランプ信号Vref2は、範囲R1および範囲R2のうちの他方（例えは、範囲R2）に含まれる信号との比較に用いられうる。これら2つの参照信号を用いて、画素アレイ101から読み出された1つのアナログ信号（画素信号0）に対して2つのAD変換を並列に行うこと

50

によって、2つのデジタル信号（デジタル信号d1およびデジタル信号d2）が得られる。

【0027】

出力部U1は、2つのデジタル信号のうちの一方を出力し、出力部U2は、出力部U1が2つのデジタル信号のうちのいずれを出力したかを示す情報（情報d1）を出力する。撮像装置I1は、出力部U1および出力部U2から出力（デジタル信号）を、例えば、情報d1を1ビットのヘッダとして含むデジタル信号として外部モジュールに出力すればよい。すなわち、1ビットの情報がヘッダとして付加されたデジタル信号が撮像装置I1の内部において生成される。よって、撮像装置I1の出力先である外部モジュール（例えば、前述の処理部）において取り扱われるデジタル信号のデータ量が低減され、例えば、2つのデジタル信号についての加算処理などのデータ処理が省略されうる。以上、本実施形態によると、撮像装置I1により得られる信号の信号処理が容易になり、例えば、画像処理の高速化や低電力化に有利である。

【0028】

上述の実施形態では、ランプ信号Vref1およびランプ信号Vref2のそれぞれは、信号出力部108および信号出力部109のそれぞれから、それぞれ出力される構成を示したが、本発明は、当該構成に限られるものではない。例えば、撮像装置I1aは、図6に示されるように、容量1301および信号出力部108Xを備え、これらの接続関係をスイッチ1302により切り替えることによって、2つのランプ信号を生成してもよい。具体的には、信号出力部108Xは、容量1301の充電を行った後にランプ波形の信号を出力する。撮像装置I1aは、当該信号をランプ信号Vref1として使用し、また、充電によって生じた容量の電圧をランプ信号Vref1に対するオフセット成分とするランプ信号Vref2として使用することができる。

【0029】

また、上述の実施形態では、互いに同じ傾きを有するランプ信号Vref1とランプ信号Vref2とを用いて2つのA/D変換を行う構成を述べたが、互いに異なる傾きを有するランプ信号Vref1とランプ信号Vref2とを用いて2つのA/D変換を行うこともできる。例えば、範囲R1と範囲R2とが互いに異なるレンジ幅を有し、ランプ信号Vref1とランプ信号Vref2との傾きの比が、範囲R1と範囲R2とのレンジ幅の比にしたがうようにすればよい。また、本発明の趣旨を逸脱しない限り、図7に例示されるように、範囲R1と範囲R2とは重複する範囲を有していてもよい。

【0030】

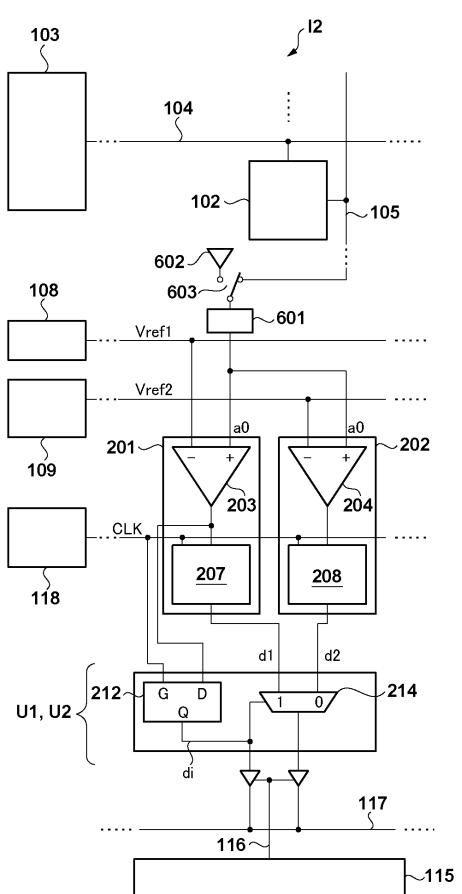

（第2実施形態）

図8乃至10を参照しながら、第2実施形態の撮像装置I2を説明する。本実施形態は、A/D変換を行うための構成が第1実施形態と異なる。撮像装置I2は、図8に例示されるように、定電圧源602（第1のユニット）および積分回路601（第2のユニット）を備えうる。定電圧源602は、例えば、画素アレイ101からの信号0（例えば、正の電圧）とは極性が異なる一定の信号（例えば、負の電圧）を出力すればよい。

【0031】

積分回路601は、スイッチ603を用いて、画素アレイ101（の列信号線105）および定電圧源602のいずれか一方に接続されうる。積分回路601は、画素アレイ101からの信号0の積分を行った後に、定電圧源602からの信号の積分を行う。

【0032】

A/Dコンバータ201は、積分回路601からの出力信号i0と、参照信号Vref1（第1の参照信号）との比較を行うことによってA/D変換を行う（第1のアナログデジタル変換）。また、A/Dコンバータ202は、積分回路601からの出力信号i0と、参照信号Vref1とは異なる参照信号Vref2（第2の参照信号）との比較を行うことによってA/D変換を行う（第2のアナログデジタル変換）。本実施形態では、信号出力部108および109からの参照信号Vref1およびVref2には、ランプ波形の信号ではなく、矩形の波形の信号が用いられる。

10

20

30

40

50

## 【0033】

当該矩形の波形は、参照信号  $V_{ref1}$  と参照信号  $V_{ref2}$  で互いに異なる値を有しており、参照信号  $V_{ref2}$  は、参照信号  $V_{ref1}$  に対してオフセット成分を有する。参照信号  $V_{ref1}$  は、積分回路 601 からの出力信号  $i_0$  のダイナミックレンジにおける範囲 R1 および範囲 R2 のうちの一方（例えば、範囲 R1）に含まれる信号との比較に用いられる。参照信号  $V_{ref2}$  は、範囲 R1 および範囲 R2 のうちの他方（例えば、範囲 R2）に含まれる信号との比較に用いられる。

## 【0034】

以下、第1実施形態と同様にして、図9および図10を参照しながら、撮像装置 I2 における画素アレイ 101 からの信号を読み出すためのシーケンスを説明する。

10

## 【0035】

図9は、輝度レベルが低い場合における撮像装置 I2 のタイミングチャートを示している。第1実施形態と同様に、第1期間 T1 では1回目の比較が為される。本実施形態では、具体的には、第1期間 T1 のうちの期間  $t_{11}$  において、積分回路 601 はスイッチ 603 によって列信号線 105 に接続され、画素アレイ 101 の N 成分の信号が積分回路 601 に入力されて積分回路 601 の出力  $i_0$  が上昇する。その後の期間  $t_{12}$  において、積分回路 601 はスイッチ 603 によって定電圧源 602 に接続され、定電圧源 602 からの信号は画素アレイ 101 の N 成分の信号とは極性が逆であるため、積分回路 601 の出力  $i_0$  が下降する。ADコンバータ 201 において、積分回路 601 の出力  $i_0$  と、参照信号  $V_{ref1}$  との比較が為される。積分回路 601 の出力  $i_0$  と、参照信号  $V_{ref1}$  との大小関係が逆転した（例えば、コンパレータ 203 の出力が Low レベルから Hi レベルになった）とき、カウンタ 207 によるカウントダウンは停止される。ADコンバータ 202 においても ADコンバータ 201 と同様の動作が為される。

20

## 【0036】

第2期間 T2 では2回目の比較が為される。具体的には、第2期間 T2 のうちの期間  $t_{21}$  においては、積分回路 601 は、スイッチ 603 により列信号線 105 に接続され、画素アレイ 101 の S 成分の信号が積分回路 601 に入力され、積分回路 601 の出力  $i_0$  は上昇する。その後の期間  $t_{22}$  においては、積分回路 601 は、スイッチ 603 により定電圧源 602 に接続され、積分回路 601 の出力  $i_0$  は下降する。ADコンバータ 201 においては、積分回路 601 の出力  $i_0$  と、参照信号  $V_{ref1}$  との大小関係が逆転し、コンパレータ 203 の出力が Low レベルから Hi レベルになったとき、カウンタ 207 によるカウントダウンは停止される。

30

## 【0037】

また、第2期間 T2 では、ADコンバータ 202 においては、ADコンバータ 201 と同様にして、積分回路 601 の出力  $i_0$  と、参照信号  $V_{ref2}$  との比較が為される。ここで、前述のとおり、参照信号  $V_{ref2}$  は、参照信号  $V_{ref1}$  に対してオフセット成分を有する。輝度レベルが低い本ケースにおいては、ADコンバータ 202 のコンパレータ 204 の比較結果は第1期間 T1 の後から反転したまま（ここでは、コンパレータ 204 の出力が Hi レベルのまま）であり、カウンタ 208 はカウントアップを行わなくてよい。

40

## 【0038】

よって、輝度レベルが低い本ケースにおいては、第1実施形態と同様にして、ラッチ 212 は Hi レベル「1」を保持し、これに基づいて、セレクタ 214 はデジタル信号  $d_1$  を選択して出力する。

## 【0039】

図10は、輝度レベルが高い場合における撮像装置 I2 のタイミングチャートを示している。第1期間 T1 については、図9と同様であるため説明を省略する。第2期間 T2 では、輝度レベルが高い本ケースにおいては、S 成分が大きいため、ADコンバータ 201 のコンパレータ 203 の比較結果は第1期間 T1 の後から反転しない（ここでは、Low レベルのまま）。一方で、ADコンバータ 202 のコンパレータ 204 の比較結果は第1

50

期間  $T_1$  の後に反転する（ここでは、Low レベルから Hi レベルになる）。よって、輝度レベルが高い本ケースにおいては、ラッチ 212 は Low レベル「0」を保持し、これに基づいて、セレクタ 214 はデジタル信号  $d_2$  を選択して出力する。

#### 【0040】

以上、本実施形態では、AD 变換を行うための構成が第1実施形態と異なる構成について述べたが、本実施形態の構成によつても、第1実施形態と同様の効果が得られる。

#### 【0041】

##### （第3実施形態）

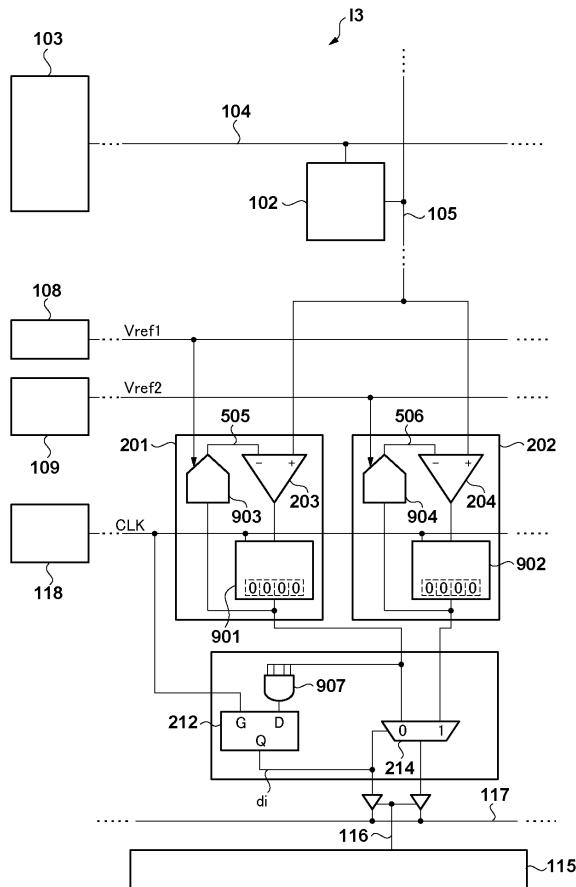

図11乃至13を参照しながら、第3実施形態の撮像装置I3を説明する。本実施形態は、図11に示されるように、AD変換を行うための構成が第1実施形態および第2実施形態と異なる。撮像装置I3においては、ADコンバータ201は、レジスタ901（第1のレジスタ）、DAコンバータ903（第1のDAコンバータ）、およびコンパレータ203（第1のコンパレータ）を含みうる。DAコンバータ903は、参照信号  $V_{ref1}$  を基準電位として、レジスタ901の値をアナログ信号  $a_1$ （第1のアナログ信号）に変換する。コンパレータ203は、画素アレイ101からの信号  $a_0$  と、アナログ信号  $a_1$  との比較を行う。

10

#### 【0042】

ADコンバータ202は、ADコンバータ201と同様にして、レジスタ902（第2のレジスタ）、DAコンバータ904（第2のDAコンバータ）、およびコンパレータ204（第2のコンパレータ）を含みうる。DAコンバータ904は、参照信号  $V_{ref2}$  を基準電位として、レジスタ902の値をアナログ信号  $a_2$ （第2のアナログ信号）に変換する。コンパレータ204は、画素アレイ101からの信号  $a_0$  と、アナログ信号  $a_2$  との比較を行う。

20

#### 【0043】

アナログ信号  $a_2$  は、アナログ信号  $a_1$  に対してオフセット成分を有している。アナログ信号  $a_1$  は、画素アレイ101からの信号  $a_0$  のダイナミックレンジにおける範囲  $R_1$  および範囲  $R_2$  のうちの一方（例えば、範囲  $R_1$ ）に含まれる信号との比較に用いられる。アナログ信号  $a_2$  は、範囲  $R_1$  および範囲  $R_2$  のうちの他方（例えば、範囲  $R_2$ ）に含まれる信号との比較に用いられる。

30

#### 【0044】

以下、第1ないし第2実施形態と同様にして、図12および図13を参照しながら、撮像装置I3における画素アレイ101からの信号  $a_0$  を読み出すためのシーケンスを説明する。

#### 【0045】

図12は、輝度レベルが低い場合における撮像装置I3のタイミングチャートを示している。第1期間  $T_1$  では1回目の比較が為される。具体的には、第1期間  $T_1$  では、ADコンバータ201においては、レジスタ901の値を順に変化させながら、画素アレイ101からの信号  $a_0$  とアナログ信号  $a_1$  との比較が為される。第1期間  $T_1$  のうちの期間  $t_{11}$  では、コンパレータ203は、レジスタ901が「4」（2進数で0100）に設定された状態におけるDAコンバータ903の出力、すなわちアナログ信号  $a_1$  と、信号  $a_0$  とを比較する。その結果、コンパレータ203の出力は Low レベルから Hi レベルになる。

40

#### 【0046】

その後の期間  $t_{12}$  では、レジスタ901が「2」（2進数で0010）に設定され、コンパレータ203はアナログ信号  $a_1$  と信号  $a_0$  とを比較する。アナログ信号  $a_1$  と信号  $a_0$  との大小関係は逆転しないため、コンパレータ203の出力は Hi レベルのままである。さらに、その後の期間  $t_{13}$  では、レジスタ901が「1」（2進数で0001）に設定され、コンパレータ203はアナログ信号  $a_1$  と信号  $a_0$  とを比較する。アナログ信号  $a_1$  と信号  $a_0$  との大小関係は逆転し、コンパレータ203の出力は Hi レベルから Low レベルになる。このようにして、レジスタ901の値「1」（2進数で0001）

50

が1回目の比較の結果として得られ、例えば、レジスタ(不図示)に保持されうる。ADコンバータ202においてもADコンバータ201と同様の動作が為されうる。

#### 【0047】

第2期間T2では2回目の比較が為される。第2期間T2のうちの期間t21では、レジスタ901が「8」(2進数で1000)に設定され、コンパレータ203は、アナログ信号a1と信号a0とを比較する。その結果、コンパレータ203の出力はLowレベルからHiレベルになる。その後の期間t22では、レジスタ901が「4」(2進数で0100)に設定され、コンパレータ203の出力はHiレベルからLowレベルになる。次に、期間t23では、レジスタ901が「6」(2進数で0110)に設定され、コンパレータ203の出力はLowレベルからHiレベルになる。さらに、期間t24では、レジスタ901が「5」(2進数で0101)に設定され、コンパレータ203の出力はHiレベルのままである。レジスタ901の4ビットの値のそれぞれは、4入力AND回路907の各入力端子にそれぞれ入力される。輝度レベルが低い本ケースにおいては、レジスタ901の値は「0101」であるので、ラッチ212には「0」が入力される。

#### 【0048】

なお、第2期間T2では、ADコンバータ202においては、ADコンバータ201と同様にして、アナログ信号a2と信号a0との比較が為されうる。ここで、前述のとおり、アナログ信号a2は、アナログ信号a1に対してオフセット成分を有する。輝度レベルが低い本ケースにおいては、コンパレータ204の出力もHiレベルである。

#### 【0049】

このようにして、レジスタ901の値「5」(2進数で0101)が2回目の比較の結果として得られる。輝度レベルが低い本ケースにおいては、ラッチ212は、4入力AND回路907からの出力である「0」を保持する。よって、これに基づいて、セレクタ214は、ADコンバータ201における1回目の比較と2回目の比較との差分を、取得すべきデジタル信号d1を選択して出力する。

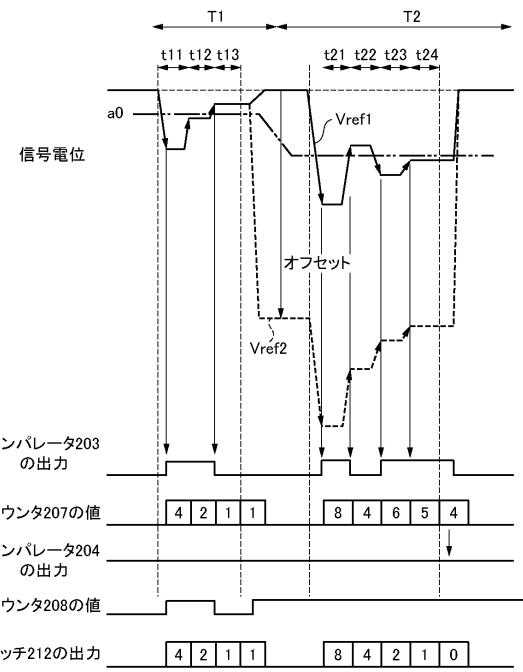

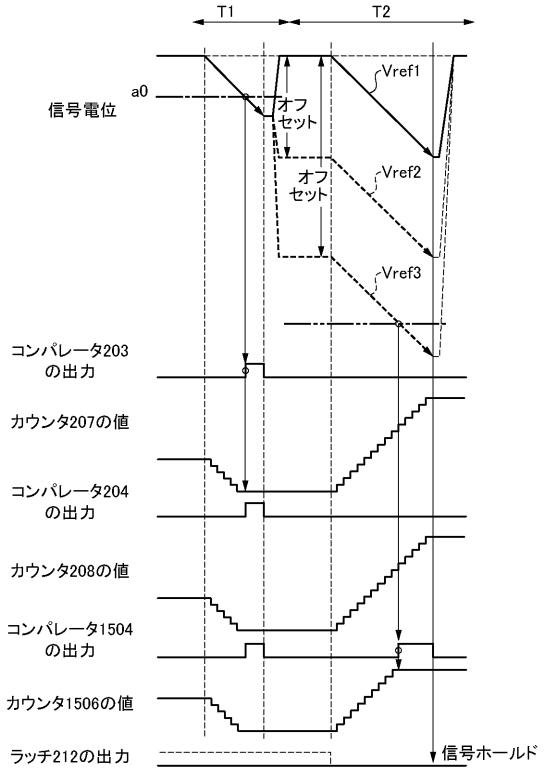

#### 【0050】

図13は、輝度レベルが高い場合における撮像装置I3のタイミングチャートを示している。第1期間T1については、図12と同様であるため説明を省略する。一方、第2期間T2では、輝度レベルが高い本ケースにおいては、アナログ信号a1と信号a0との比較が前述と同様の手順で為されるが、S成分が大きいため、コンパレータ203の比較結果は第1期間T1の後から反転しない(Lowレベルのまま)。その結果、レジスタ901の値は、「F」(2進数で1111)まで変化する。輝度レベルが高い本ケースにおいては、レジスタ901の値は「1111」であるので、ラッチ212には「1」が入力される。

#### 【0051】

一方で、ADコンバータ202のコンパレータ204の比較結果は第1期間T1の後に反転し、アナログ信号a2と信号a0との比較が、前述と同様の手順で為される。ここでは、レジスタ902の値「3」(2進数で0011)が2回目の比較の結果として得られる。輝度レベルが高い本ケースにおいては、ラッチ212は、4入力AND回路907からの出力である「1」を保持する。よって、これに基づいて、セレクタ214は、ADコンバータ202における1回目の比較と2回目の比較との差分を、取得すべきデジタル信号d2を選択して出力する。

#### 【0052】

以上、本実施形態では、AD変換を行うための構成が第1ないし第2実施形態と異なる構成について述べたが、本実施形態の構成によっても、第1ないし第2実施形態と同様の効果が得られる。

#### 【0053】

##### (第4実施形態)

図14乃至16を参照しながら、第4実施形態の撮像装置I4を説明する。以上の第1ないし第3実施形態では、画素アレイ101における複数の列のそれぞれに2つのADコ

10

20

30

40

50

ンバータ(ADコンバータ201および202)が設けられた構成を述べたが、本実施形態では、動作モードに応じて構成を変更する。

【0054】

撮像装置I4は、画素アレイ101の各列に対応して1つのADコンバータが配される。例えば、図14に示されるように、ADコンバータ201は第L1列目(L1は奇数の整数)に対応して配されており、ADコンバータ202は第L2列目(L2は偶数の整数)に対応して配されている。換言すると、第L1列は、第1群(奇数の列)のうちの1列であり、第L2列は、第2群(偶数の列)のうちの1列である。

【0055】

撮像装置I4は、動作モードとして、例えば第1モードおよび第2モードを含みうる。第1モードでは、画素アレイ101の複数の列のそれぞれから信号が読み出され、いわゆる全読み出しが為される。第2モードでは、画素アレイ101の複数の列のうち、例えば、第1群(ここでは、奇数の列)の各画素から信号が読み出され、いわゆる間引き読み出しが為される。撮像装置I4は、例えば、スイッチ部1401および1402を備え、動作モードに応じて、ADコンバータ201およびADコンバータ202の接続関係を切り替える。

10

【0056】

例えば、第1モードでは、スイッチ部1401および1402は、ADコンバータ201が第L1列目からの信号についてAD変換を行い、ADコンバータ202が第L2列目からの信号についてAD変換を行うように、ADコンバータ201および202の接続関係を切り替える。一方、第2モードでは、スイッチ部1401および1402は、ADコンバータ201およびADコンバータ202のそれぞれが第L1列目からの信号についてAD変換を並列に行うように当該接続関係を切り替える。

20

【0057】

以上、本実施形態によると、撮像装置I4は、第1モードにおいては、各列に設けられたADコンバータが各列の画素信号の読み出しにそれぞれ対応するように動作させる。一方、撮像装置I4は、第2モードにおいては、画素信号の読み出しを省略する各列に設けられたADコンバータを、画素信号の読み出しを行う各列に設けられたADコンバータと並列に動作させる。よって、撮像装置I4は、第2モードにおいて第1ないし第3実施形態と同様の効果を達成する。また、ここでは、第2モードにおいては、画素信号が、奇数の列の各画素から読み出される構成を述べたが、偶数の列の各画素から読み出される構成にしてもよい。

30

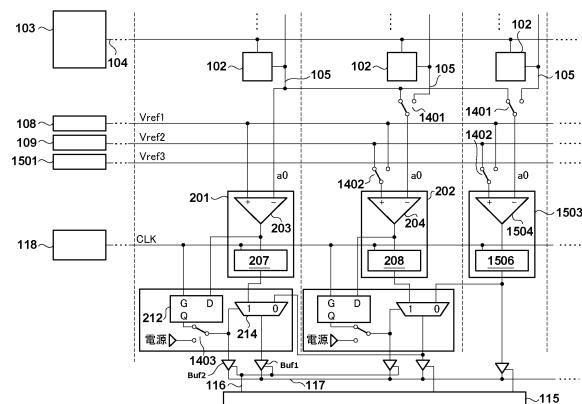

【0058】

また、第2モードによる間引き読み出しへは、画素アレイ101から3列ごと間隔で信号を読み出すように構成してもよく、例えば、図15に例示される撮像装置I4aのように構成してもよい。撮像装置I4aによると、第2モードにおいては、3の倍数の列の各画素から画素信号が読み出される。ここでは、画素アレイ101のうちの3列(第L1列目、第L2列目および第L3列目)を例示して述べる。ここで、mを整数として、ADコンバータ201は第L1列目( $L1 = 3m - 2$ )に対応して配されている。ADコンバータ202は第L2列目( $L2 = 3m - 1$ )に対応して配されている。ADコンバータ203は第L3列目( $L3 = 3m$ )に対応して配されている。

40

【0059】

例えば、第1モードでは、スイッチ部1401および1402は、3つのADコンバータのそれぞれが、画素アレイ101の3列からの信号のそれぞれについて、それぞれAD変換を行うように、3つのADコンバータの接続関係を切り替える。より具体的には、スイッチ部1401および1402は、ADコンバータ201が第L1列目からの信号についてAD変換を行う。ADコンバータ202が第L2列目からの信号についてAD変換を行う。また、ADコンバータ203が第L3列目からの信号についてAD変換を行うよう。

【0060】

50

一方、第2モードでは、スイッチ部1401および1402は、A/Dコンバータ201ないし203のそれぞれが第L1列目からの信号についてA/D変換を並列に行うように当該接続関係を切り替える。図16は、輝度レベルが高い場合における撮像装置I4aのタイミングチャートを前述の各実施形態と同様にして例示している。

【0061】

以上の4つの実施形態を述べたが、本発明はこれらに限られるものではなく、目的、状態、用途及び機能その他の仕様に応じて、適宜、変更が可能であり、他の実施形態によっても為されうる。

【0062】

(撮像システム)

10

以上の実施形態は、カメラ等に代表される撮像システムに含まれる撮像装置について述べた。撮像システムの概念には、撮影を主目的とする装置のみならず、撮影機能を補助的に備える装置（例えば、パーソナルコンピュータ、携帯端末）も含まれる。撮像システムは、上記の実施形態として例示された本発明に係る撮像装置と、この撮像装置から出力される信号を処理する処理部とを含みうる。この処理部は、例えば、A/D変換器、および、このA/D変換器から出力されるデジタルデータを処理するプロセッサを含みうる。

【図1】

【図2】

【図3】

【図4】

【図5】

【 図 6 】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(72)発明者 森田 一路

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 園田 一博

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 鈴木 肇

(56)参考文献 特開2011-041091(JP, A)

特開2011-035689(JP, A)

特開2011-120087(JP, A)

特開2011-166733(JP, A)

特開2010-252140(JP, A)

国際公開第2013/084809(WO, A1)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H01L 21/339

H01L 27/14 - 27/148

H01L 29/762