(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4500610号

(P4500610)

(45) 発行日 平成22年7月14日(2010.7.14)

(24) 登録日 平成22年4月23日(2010.4.23)

|                      |              |

|----------------------|--------------|

| (51) Int.Cl.         | F 1          |

| HO4N 5/225 (2006.01) | HO4N 5/225 F |

| HO4N 5/76 (2006.01)  | HO4N 5/225 B |

| HO4N 5/80 (2006.01)  | HO4N 5/76 Z  |

| HO4N 5/907 (2006.01) | HO4N 5/80    |

|                      | HO4N 5/907   |

請求項の数 14 (全 23 頁)

(21) 出願番号 特願2004-200766 (P2004-200766)

(22) 出願日 平成16年7月7日 (2004.7.7)

(65) 公開番号 特開2006-25124 (P2006-25124A)

(43) 公開日 平成18年1月26日 (2006.1.26)

審査請求日 平成19年7月2日 (2007.7.2)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100125254

弁理士 別役 重尚

(72) 発明者 高木 心

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

(72) 発明者 蓮覚寺 秀行

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 仲間 晃

最終頁に続く

(54) 【発明の名称】 映像信号処理装置、メモリ制御方法、及びプログラム

## (57) 【特許請求の範囲】

## 【請求項 1】

被写体像に対応した画像信号を出力する撮像素子を含む映像信号処理装置であって、前記撮像素子から出力された画像信号に対して信号処理を施す信号処理部と、前記信号処理部から出力される画像信号を記憶する VRAM ( Video Random Access Memory ) 部であって、それぞれが 1 フレームの画像信号を記憶する 3 つ以上の記憶領域からなる VRAM 部と、

前記 VRAM 部の各記憶領域に関して、画像信号の書き込みが完了した記憶領域、及び画像信号の書き込みが完了した順番を示す管理情報を保持する VRAM 管理情報記憶部と、

前記 VRAM 管理情報記憶部の保持する管理情報に基づき、前記 VRAM 部から前記 3 つ以上の記憶領域にそれぞれ記憶される画像信号を書き込みが完了した順に第 1 の読み出し速度で読み出して、当該読み出された画像信号に対して圧縮処理を施す画像圧縮部と、

前記 VRAM 管理情報記憶部の保持する管理情報に基づき、前記 VRAM 部から前記 3 つ以上の記憶領域のうち最後に書き込みが完了した記憶領域に記憶される画像信号を第 2 の読み出し速度で読み出して、当該読み出された画像信号に対して画像表示処理を施す画像表示処理部と、

前記画像表示処理部から出力された画像信号に基づき画像表示を行う画像表示部と、前記画像圧縮部による画像信号の読み出しが完了していない記憶領域、及び前記画像表示処理部による画像信号の読み出しを行っている記憶領域を検出し、当該検出の結果に基

づいて前記信号処理部から出力される画像信号の書き込まれる記憶領域を前記3つ以上の記憶領域の中から選択することによって、前記VRAM部の各記憶領域における書き込みアドレス及び読み出しアドレスの一方が他方を追い越すことのないよう制御するメモリ制御部と、

を有することを特徴とする映像信号処理装置。

#### 【請求項2】

前記メモリ制御部は、前記信号処理部から出力される画像信号を前記VRAM部の1つの記憶領域へ書き込み完了したあと、前記検出の結果に基づいて、前記3つ以上の記憶領域のうち前記画像圧縮部による画像信号の読み出しが完了していない記憶領域、及び前記画像表示処理部による画像信号の読み出しを行っている記憶領域以外の記憶領域を次に画像信号を書き込むべき記憶領域として選択することを特徴とする請求項1記載の映像信号処理装置。

10

#### 【請求項3】

前記メモリ制御部は、前記信号処理部から出力される画像信号を前記VRAM部の1つの記憶領域へ書き込み完了したあと、前記検出の結果によると前記VRAM部に前記画像圧縮部による画像信号の読み出しが完了していない記憶領域、及び前記画像表示処理部による画像信号の読み出しを行っている記憶領域以外の記憶領域が存在しない場合に、前記VRAM部に新たに記憶領域を確保し、該確保された記憶領域を次に書き込むべき記憶領域とすることを特徴とする請求項1または請求項2記載の映像信号処理装置。

20

#### 【請求項4】

前記VRAM部での書き込み速度に比べて前記第1の読み出し速度が遅い場合に、前記画像圧縮部での圧縮速度を上げるようにする制御部を、更に有することを特徴とする請求項1記載の映像信号処理装置。

#### 【請求項5】

前記画像圧縮部が前記VRAM部の1つの画像領域から画像信号の読み出しを完了した際に、更にまだ圧縮処理の行われていない記憶領域がある場合に、前記画像圧縮部での圧縮速度を上げるようにする制御部を、更に有することを特徴とする請求項1記載の映像信号処理装置。

#### 【請求項6】

前記VRAM部の各記憶領域には一連の番号が付され、

30

前記メモリ制御部は、前記信号処理部から出力される画像信号を前記VRAM部の1つの記憶領域へ書き込み完了したあと、該書き込み完了した記憶領域の番号が前記一連の番号の終端の番号である場合は、前記一連の番号の先頭の番号を付された記憶領域を、次に書き込むべき記憶領域とし、一方、前記書き込み完了した記憶領域の番号が前記一連の番号の終端の番号ではない場合は、該書き込み完了した記憶領域の番号をインクリメントして得られた番号をもつ記憶領域を、次に書き込むべき記憶領域とすることを特徴とする請求項1に記載の映像信号処理装置。

#### 【請求項7】

前記VRAM部における前記画像圧縮部による画像信号の読み出しが完了していない記憶領域、及び前記画像表示処理部による画像信号の読み出しを行っている記憶領域以外の記憶領域の数が所定数よりも少ない場合に、前記画像圧縮部での圧縮速度を上げるようにする制御部を、更に有することを特徴とする請求項1記載の映像信号処理装置。

40

#### 【請求項8】

前記制御部は、前記画像圧縮部での圧縮速度を上げた結果、前記VRAM部における前記画像圧縮部による画像信号の読み出しが完了していない記憶領域、及び前記画像表示処理部による画像信号の読み出しを行っている記憶領域以外の記憶領域の数が所定数以上となつた場合に、前記画像圧縮部での圧縮速度を遅くして元に戻すようにすることを特徴とする請求項7記載の映像信号処理装置。

#### 【請求項9】

前記制御部は、前記画像圧縮部での圧縮率を変更する、または前記画像圧縮部へ供給す

50

るクロック信号の周波数を高くすることによって、前記圧縮速度を上げるようにすることを特徴とする請求項4、5または請求項7記載の映像信号処理装置。

#### 【請求項10】

被写体像に対応した画像信号を出力する撮像素子と、当該撮像素子から出力された画像信号に対して信号処理を施す信号処理部と、当該信号処理部から出力される画像信号を記憶するVRAM(Video Random Access Memory)部であって、それが1フレームの画像信号を記憶する3つ以上の記憶領域からなるVRAM部と、当該VRAM管理情報記憶部の保持する管理情報に基づき、前記VRAM部から前記3つ以上の記憶領域にそれぞれ記憶される画像信号を書き込みが完了した順に第1の読み出し速度で読み出して、当該読み出された画像信号に対して圧縮処理を施す画像圧縮部と、当該VRAM管理情報記憶部の保持する管理情報に基づき、前記VRAM部から前記3つ以上の記憶領域のうち最後に書き込みが完了した記憶領域に記憶される画像信号を第2の読み出し速度で読み出して、当該読み出された画像信号に対して画像表示処理を施す画像表示処理部とを備えた映像信号処理装置に適用されるメモリ制御方法であって、

10

前記VRAM部の各記憶領域に関して、画像信号の書き込みが完了した記憶領域、及び画像信号の書き込みが完了した順番を示す管理情報を記憶装置に保持する保持ステップと、

前記画像圧縮部による画像信号の読み出しが完了していない記憶領域、及び前記画像表示処理部による画像信号の読み出しを行っている記憶領域を検出し、当該検出の結果に基づいて前記信号処理部から出力される画像信号の書き込まれる記憶領域を前記3つ以上の記憶領域の中から選択することによって、前記VRAM部の各記憶領域における書き込みアドレス及び読み出しあдресの一方が他方を追い越すことのないよう制御するメモリ制御ステップと、

20

を有することを特徴とするメモリ制御方法。

#### 【請求項11】

前記メモリ制御ステップでは、前記信号処理部から出力される画像信号を前記VRAM部の1つの記憶領域へ書き込み完了したあと、前記検出の結果に基づいて、前記3つ以上の記憶領域のうち前記画像圧縮部による画像信号の読み出しが完了していない記憶領域、及び前記画像表示処理部による画像信号の読み出しを行っている記憶領域以外の記憶領域を次に画像信号を書き込むべき記憶領域として選択することを特徴とする請求項10記載のメモリ制御方法。

30

#### 【請求項12】

前記メモリ制御ステップでは、前記信号処理部から出力される画像信号を前記VRAM部の1つの記憶領域へ書き込み完了したあと、前記検出の結果によると前記VRAM部に前記画像圧縮部による画像信号の読み出しが完了していない記憶領域、及び前記画像表示処理部による画像信号の読み出しを行っている記憶領域以外の記憶領域が存在しない場合に、前記VRAM部に新たに記憶領域を確保し、該確保された記憶領域を次に書き込むべき記憶領域とすることを特徴とする請求項10または請求項11記載のメモリ制御方法。

#### 【請求項13】

前記VRAM部での書き込み速度に比べて前記第1の読み出し速度が遅い場合に、前記画像圧縮部での圧縮速度を上げるようにする制御ステップを、更に有することを特徴とする請求項10記載のメモリ制御方法。

40

#### 【請求項14】

被写体像に対応した画像信号を出力する撮像素子と、当該撮像素子から出力された画像信号に対して信号処理を施す信号処理部と、当該信号処理部から出力される画像信号を記憶するVRAM(Video Random Access Memory)部であって、それが1フレームの画像信号を記憶する3つ以上の記憶領域からなるVRAM部と、当該VRAM管理情報記憶部の保持する管理情報に基づき、前記VRAM部から前記3つ以上の記憶領域にそれぞれ記憶される画像信号を書き込みが完了した順に第1の読み出し速度で読み出して、当該読み出された画像信号に対して圧縮処理を施す画像圧縮部と、当

50

該 V R A M 管理情報記憶部の保持する管理情報に基づき、前記 V R A M 部から前記 3 つ以上の記憶領域のうち最後に書き込みが完了した記憶領域に記憶される画像信号を第 2 の読み出し速度で読み出して、当該読み出された画像信号に対して画像表示処理を施す画像表示処理部とを備えた映像信号処理装置に適用されるメモリ制御方法を、コンピュータに実行させるためのプログラムにおいて、

前記 V R A M 部の各記憶領域に関して、画像信号の書き込みが完了した記憶領域、及び画像信号の書き込みが完了した順番を示す管理情報を記憶装置に保持する保持ステップと、

前記画像圧縮部による画像信号の読み出しが完了していない記憶領域、及び前記画像表示処理部による画像信号の読み出しを行っている記憶領域を検出し、当該検出の結果に基づいて前記信号処理部から出力される画像信号の書き込まれる記憶領域を前記 3 つ以上の記憶領域の中から選択することによって、前記 V R A M 部の各記憶領域における書き込みアドレス及び読み出しあдресの一方が他方を追い越すことのないよう制御するメモリ制御ステップと、

をコンピュータに実行させることを特徴とするプログラム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、映像信号処理装置、メモリ制御方法、及びプログラムに関し、特に、被写体像に対応した画像信号を出力する撮像素子を含む映像信号処理装置、該映像信号処理装置に適用されるメモリ制御方法、及び該メモリ制御方法をコンピュータに実行させるためのプログラムに関する。

【0002】

本発明は、例えば動画撮影を行うことができ、動画撮影時の電子ビューファインダの表示レートと記録画像レートとが異なるような映像信号処理装置に適用される。

【背景技術】

【0003】

従来、画像情報を記憶するメモリである V R A M ( Video Random Access Memory ) から画像表示部への読み出しレートが V R A M への書き込みレートよりも速い映像信号処理装置において、2つの V R A M を用いて各 V R A M を切り替えて使用することで、「胴切り」が発生しない装置が提案されている（特許文献 1 参照）。「胴切り」とは、V R A M へ書き込み中に読み出しが追い越す、もしくは、V R A M から読み出し中に書き込みが追い越すことにより、画面の上部と下部で撮影された時刻が異なる画像が読み出される現象をいう。

【0004】

また、V R A M への書き込みレートが V R A M から画像表示部への読み出しレートより速い場合、及び V R A M から画像表示部への読み出しレートが V R A M への書き込みレートよりも速い場合のいずれにおいても、V R A M からの読み出しと該 V R A M への書き込みの制御方法を切り替えることで、書き込みが読み出しを追い越したり、読み出しが書き込みを追い越したりしない装置が提案されている（特許文献 2 参照）。

【0005】

また、画像表示と並行して画像を圧縮し動画記録を行う場合に、画像の情報量に応じて符号化パラメータを変更することで、圧縮後の画像データサイズを適正に制御しながらリアルタイムで記憶媒体に記憶する装置が提案されている（特許文献 3 参照）。

【特許文献 1】特開平 6 - 67632 号公報

【特許文献 2】特開 2003 - 324644 号公報

【特許文献 3】特開 2000 - 197003 号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献 1 や特許文献 2 に記載の装置においては、動画撮影を行いながら

10

20

30

40

50

ら、動画表示において「胴切り」を発生させないことについては考慮されていなかった。

**【0007】**

また、特許文献3に記載の装置においては、リアルタイムで記憶媒体に動画記録を行うため、シーン変化などで画像の変化スピードや精細度が急激に変化して、画像の情報量が急激に変化したときに、所定のフレームレートを圧縮回路が達成できなくなって動画記録でフレーム落ちするという問題点があった。

**【0008】**

本発明はこのような問題点に鑑みてなされたものであって、「胴切り」の発生やフレーム欠落を防止した映像信号処理装置、メモリ制御方法、及びプログラムを提供することを目的とする。

10

**【課題を解決するための手段】**

**【0009】**

上記目的を達成するために、本発明の映像信号処理装置は、被写体像に対応した画像信号を出力する撮像素子を含む映像信号処理装置であって、前記撮像素子から出力された画像信号に対して信号処理を施す信号処理部と、前記信号処理部から出力される画像信号を記憶するVRAM(Video Random Access Memory)部であつて、それぞれが1フレームの画像信号を記憶する3つ以上の記憶領域からなるVRAM部と、前記VRAM部の各記憶領域に関して、画像信号の書き込みが完了した記憶領域、及び画像信号の書き込みが完了した順番を示す管理情報を保持するVRAM管理情報記憶部と、前記VRAM管理情報記憶部の保持する管理情報に基づき、前記VRAM部から前記3つ以上の記憶領域にそれぞれ記憶される画像信号を書き込みが完了した順に第1の読み出し速度で読み出して、当該読み出された画像信号に対して圧縮処理を施す画像圧縮部と、前記VRAM管理情報記憶部の保持する管理情報に基づき、前記VRAM部から前記3つ以上の記憶領域のうち最後に書き込みが完了した記憶領域に記憶される画像信号を第2の読み出し速度で読み出して、当該読み出された画像信号に対して画像表示処理を施す画像表示部と、前記画像表示部から出力された画像信号に基づき画像表示を行う画像表示部と、前記画像圧縮部による画像信号の読み出しが完了していない記憶領域、及び前記画像表示処理部による画像信号の読み出しを行っている記憶領域を検出し、当該検出の結果に基づいて前記信号処理部から出力される画像信号の書き込まれる記憶領域を前記3つ以上の記憶領域の中から選択することによって、前記VRAM部の各記憶領域における書き込みアドレス及び読み出しアドレスの一方が他方を追い越すことのないよう制御するメモリ制御部と、有することを特徴とする。

20

**【0010】**

上記目的を達成するために、本発明のメモリ制御方法は、被写体像に対応した画像信号を出力する撮像素子と、当該撮像素子から出力された画像信号に対して信号処理を施す信号処理部と、当該信号処理部から出力される画像信号を記憶するVRAM(Video Random Access Memory)部であつて、それぞれが1フレームの画像信号を記憶する3つ以上の記憶領域からなるVRAM部と、当該VRAM管理情報記憶部の保持する管理情報に基づき、前記VRAM部から前記3つ以上の記憶領域にそれぞれ記憶される画像信号を書き込みが完了した順に第1の読み出し速度で読み出して、当該読み出された画像信号に対して圧縮処理を施す画像圧縮部と、当該VRAM管理情報記憶部の保持する管理情報に基づき、前記VRAM部から前記3つ以上の記憶領域のうち最後に書き込みが完了した記憶領域に記憶される画像信号を第2の読み出し速度で読み出して、当該読み出された画像信号に対して画像表示処理を施す画像表示部とを備えた映像信号処理装置に適用されるメモリ制御方法であって、前記VRAM部の各記憶領域に関して、画像信号の書き込みが完了した記憶領域、及び画像信号の書き込みが完了した順番を示す管理情報を記憶装置に保持する保持ステップと、前記画像圧縮部による画像信号の読み出しが完了していない記憶領域、及び前記画像表示処理部による画像信号の読み出しを行っている記憶領域を検出し、当該検出の結果に基づいて前記信号処理部から出力される画像信号の書き込まれる記憶領域を前記3つ以上の記憶領域の中から選択することによって、前記

30

40

50

V R A M部の各記憶領域における書き込みアドレス及び読み出しアドレスの一方が他方を追い越すことのないよう制御するメモリ制御ステップと、を有することを特徴とする。

#### 【0011】

上記目的を達成するために、本発明のプログラムは、被写体像に対応した画像信号を出力する撮像素子と、当該撮像素子から出力された画像信号に対して信号処理を施す信号処理部と、当該信号処理部から出力される画像信号を記憶するV R A M ( V i d e o R a n d o m A c c e s s M e m o r y ) 部であって、それぞれが1フレームの画像信号を記憶する3つ以上の記憶領域からなるV R A M部と、当該V R A M管理情報記憶部の保持する管理情報に基づき、前記V R A M部から前記3つ以上の記憶領域にそれぞれ記憶される画像信号を書き込みが完了した順に第1の読み出し速度で読み出して、当該読み出された画像信号に対して圧縮処理を施す画像圧縮部と、当該V R A M管理情報記憶部の保持する管理情報に基づき、前記V R A M部から前記3つ以上の記憶領域のうち最後に書き込みが完了した記憶領域に記憶される画像信号を第2の読み出し速度で読み出して、当該読み出された画像信号に対して画像表示処理を施す画像表示処理部とを備えた映像信号処理装置に適用されるメモリ制御方法を、コンピュータに実行させるためのプログラムにおいて、前記V R A M部の各記憶領域に関して、画像信号の書き込みが完了した記憶領域、及び画像信号の書き込みが完了した順番を示す管理情報を記憶装置に保持する保持ステップと、前記画像圧縮部による画像信号の読み出しが完了していない記憶領域、及び前記画像表示処理部による画像信号の読み出しを行っている記憶領域を検出し、当該検出の結果に基づいて前記信号処理部から出力される画像信号の書き込まれる記憶領域を前記3つ以上の記憶領域の中から選択することによって、前記V R A M部の各記憶領域における書き込みアドレス及び読み出しアドレスの一方が他方を追い越すことのないよう制御するメモリ制御ステップと、をコンピュータに実行させることを特徴とする。

10

#### 【発明の効果】

#### 【0012】

本発明によれば、V R A M部の各V R A M領域における記憶状態を検出し、該記憶状態を示す管理情報を記憶装置に保持し、該記憶装置に保持された管理情報に基づき、前記V R A M部の各V R A M領域における読み書きを制御する。

#### 【0013】

これにより、「胴切り」の発生やフレーム欠落を防止することができる。

30

#### 【0014】

すなわち、撮像のレート及び表示のレートに比べ圧縮回路の圧縮速度が一定でない場合でも、画像表示装置で胴切りを発生させることなく、また信号処理部から出力された画像信号をフレーム欠落させることなく、かつ圧縮画像に胴切りを発生させることなく、圧縮回路で圧縮することができる。

#### 【0015】

また、予め用意したV R A M領域の数が足りなくなった場合でもV R A Mを動的に増やすことで、ビットレートを下げることなく画像信号を圧縮回路で圧縮することができ、また圧縮のビットレートを制御することで、必要となるV R A M領域の数を抑えて圧縮画像を記憶することができる。

40

#### 【0016】

さらに、画像信号をあるV R A M領域へ書き込み完了したあと、次に書き込むべきV R A M領域を選ぶ際、一連のV R A M番号の順番に従うとともに、それらをサイクリックに辿ることによって、V R A M領域の選択制御を容易にすることができます。

#### 【発明を実施するための最良の形態】

#### 【0017】

以下、本発明を実施するための最良の形態について、図面を参照して説明する。

#### 【0018】

##### 〔第1の実施の形態〕

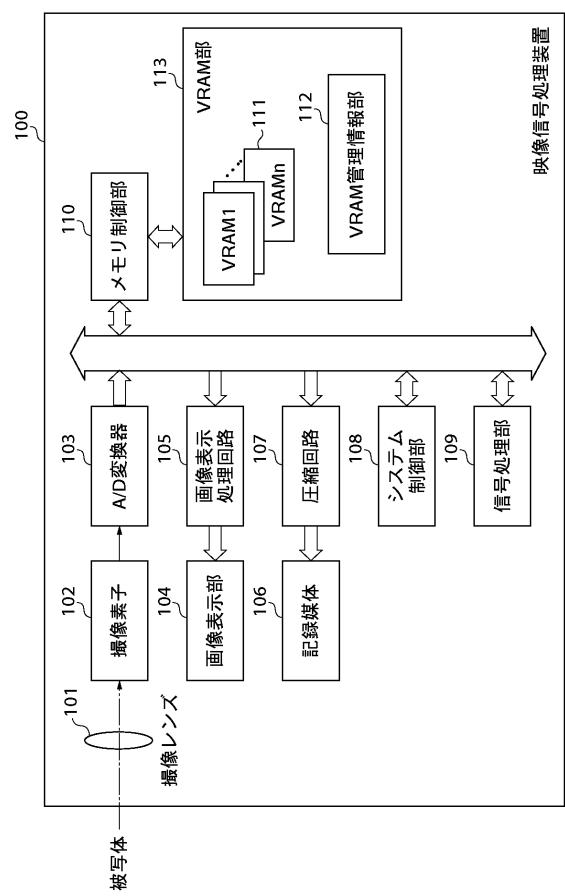

図1は、本発明の第1の実施の形態に係る映像信号処理装置の構成を示すブロック図で

50

ある。

**【0019】**

図1において映像信号処理装置100は、撮像レンズ101、撮像素子102、A/D変換器103、画像表示部104、画像表示処理回路105、記憶媒体106、圧縮回路107、システム制御部108、信号処理部109、メモリ制御部110、メモリ部113から構成される。メモリ部113は、VRAM部111、VRAM管理情報部112を含む。

**【0020】**

撮像レンズ101は被写体像を取り込む。撮像素子102は、撮像レンズ101を介して入射される被写体像を光学信号から電気信号に変換して出力する。A/D変換器103は、撮像素子102から得られたアナログ電気信号をデジタル電気信号に変換して出力する。信号処理部109は、A/D変換器103の出力信号に対して各種信号処理を加えてから、輝度信号と色差信号とで構成される画像信号へと変換する。

**【0021】**

メモリ部113におけるVRAM部111は、複数のVRAM領域から成り、画像信号を保持するDRAMによって構成される。VRAM部111は、画像信号を記録できるVRAM領域が不足した場合にはその数を増やすことができる。これらのVRAM領域は番号(1~n)を付けて管理され、以降この番号のことをVRAM番号と呼ぶ。

**【0022】**

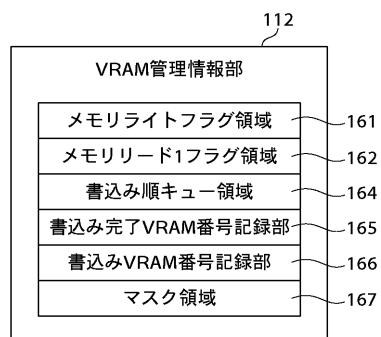

図2は、メモリ部113におけるVRAM管理情報部112の内部メモリ構成を示す図である。

**【0023】**

すなわち、VRAM管理情報部112は、メモリライトフラグ領域161と、メモリリード1フラグ領域162と、書き込み順キュー領域164と、書き込み完了VRAM番号記録部165と、書き込みVRAM番号記録部166と、マスク領域167とから構成される。

**【0024】**

メモリライトフラグ領域161とメモリリード1フラグ領域162にはともに、VRAM領域に対応したフラグが格納される。例えばVRAM部111が8個のVRAMから成るならば、メモリライトフラグ領域161とメモリリード1フラグ領域162にはともに8つのフラグが格納され、それぞれのフラグがVRAM番号1から8に対応する。メモリライトフラグ領域161に格納されるフラグは、画像信号の対応VRAM領域への書き込みが完了したときに立てられ(1に設定)、対応VRAM領域から圧縮回路107への画像信号の読み出しが完了したときにクリアされる(0に設定)フラグである。メモリライトフラグ領域161にフラグが立っている状態は、対応するVRAM領域への画像信号の書き込みは完了したが、まだ圧縮回路107において圧縮されていないことを示し、メモリライトフラグ領域161にフラグが立っていない状態は、対応のVRAM領域へ現在書き込み可能であることを示している。

**【0025】**

メモリリード1フラグ領域162に格納されるフラグは、対応のVRAM領域から画像表示処理回路105への画像信号の読み出し開始時に立てられ、読み出し完了時にクリアされる。メモリリード1フラグ領域162にフラグが立っている状態は、対応のVRAMから画像表示処理回路105への画像信号の読み出しが行われていることを示し、メモリリード1フラグ領域162にフラグが立っていない状態は、対応のVRAM領域から画像表示処理回路105への画像信号の読み出しが行われていないことを示している。

**【0026】**

書き込み順キュー領域164には、VRAM部111の複数のVRAM領域への書き込み順が記憶される。書き込み完了VRAM番号記録部165は、最後に書き込みの完了したVRAM番号を記録する。書き込みVRAM番号記録部166は、現在書き込み中のVRAM番号を記録する。マスク領域167は、映像信号処理装置100が画像表示部104での画像の表示と、圧縮回路107を通して記憶媒体106への圧縮画像の保存との両方を行う場

10

20

30

40

50

合と、画像表示部 104 での画像の表示のみを行う場合との 2 つの状態に対応するために用いられる。すなわち、マスク領域 167 には、メモリライトフラグ領域 161 やメモリード 1 フラグ領域 162 と同様に、VRAM 領域に対応したフラグが格納され、画像表示部 104 での画像の表示と、圧縮回路 107 を通して記憶媒体 106 への圧縮画像の保存との両方が行われる場合には、すべての VRAM 領域に対応したフラグが 1 にセットされ、画像の表示のみが行われる場合には、すべての VRAM 領域に対応したフラグが 0 にクリアされる。

#### 【0027】

図 1 に戻って、メモリ制御部 110 は、VRAM 部 111 と VRAM 管理情報部 112 とにおける読み出しと書き込みとを制御する。画像表示部 104 は、液晶パネルに代表される画像表示装置である。画像表示処理回路 105 は、画像処理された画像信号を画像表示部 104 における信号方式に変換し画像表示部 104 に出力する。圧縮回路 107 は、画像信号の圧縮を行う回路である。圧縮すべき画像信号は、メモリ制御部 110 経由で VRAM 部 111 より読み出して取得する。圧縮回路 107 によって圧縮された画像信号は記憶媒体 106 に記憶される。システム制御部 108 は、CPU, ROM, RAM を備え、この映像信号処理装置 100 全体を制御する。

#### 【0028】

なお、これ以降においては、W、R1、R2 を次のように定義して説明に用いる。

#### 【0029】

W は、信号処理部 109 から出力された画像信号の VRAM 部 111 への書き込みとし、R1 は、VRAM 部 111 から画像表示処理回路 105 への画像信号の読み出しとし、R2 は、VRAM 部 111 から圧縮回路 107 への画像信号の読み出しとする。

#### 【0030】

なおまた本実施の形態においては、W と R1 の処理レートは固定値であり、かつ、R2 の処理レートは、変動するが平均すると W よりは速い値であるとする。

#### 【0031】

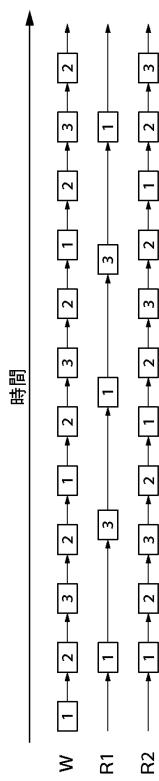

図 3 は、R2 の処理レートが固定されていると仮定した場合に、W、R1、R2 が処理対象とする VRAM が時間軸に沿って遷移していく様子を示した図である。ただし、ここでは VRAM 部 111 が 3 つの VRAM 領域から成るものとし、図中のブロックが VRAM 領域を示し、ブロック内の数字が VRAM 番号である。

#### 【0032】

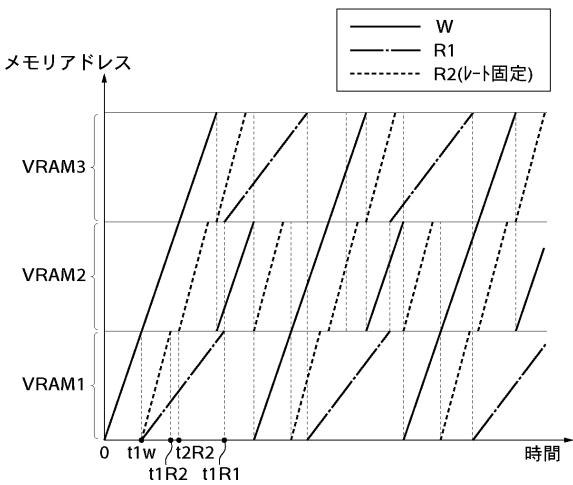

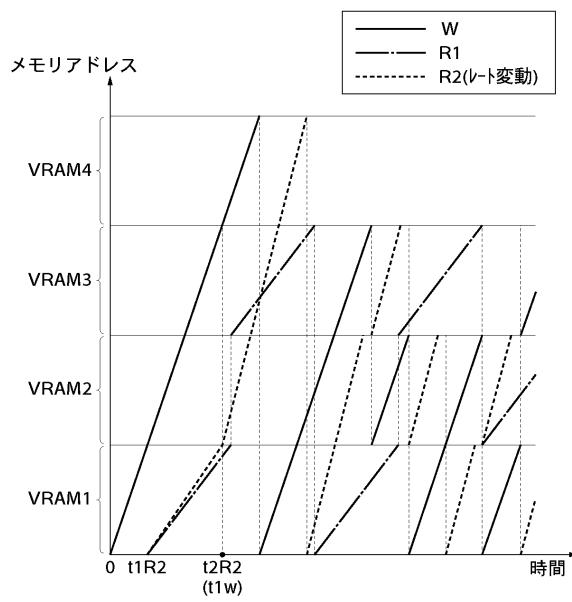

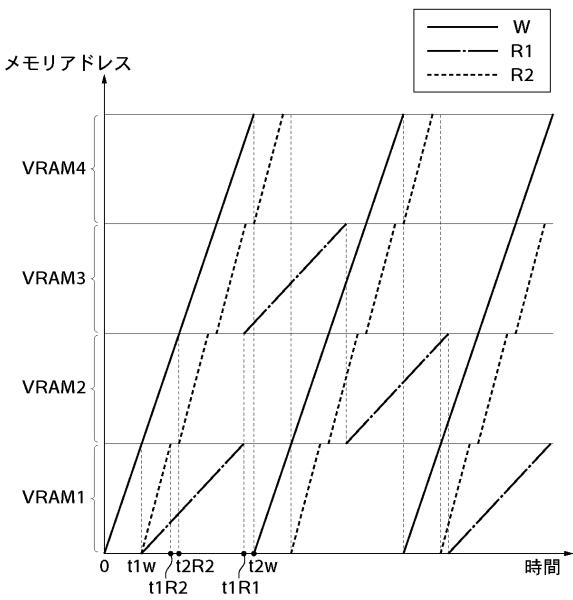

図 4 は、図 3 に示す 3 つの VRAM 領域における W、R1、R2 の処理状況を示すグラフである。横軸は時間、縦軸は各 VRAM 領域のメモリアドレスである。

#### 【0033】

図 5 は、R2 の処理レートが変動した場合における W、R1、R2 の処理状況を示すグラフである。横軸は時間、縦軸は各 VRAM 領域のメモリアドレスである。なお、図 5 に示す例では、VRAM 部 111 が最初は 3 つの VRAM 領域で構成されているが、その後に新たに VRAM 番号 4 の VRAM 領域が追加される場合を示す。

#### 【0034】

なお、図 3 ~ 図 5 は書き込みと読み出しのフレームレートをそれぞれ、W は 80 f p s、R1 は 30 f p s、R2 は 100 f p s とした場合の一例を図示したものである。

#### 【0035】

本実施の形態では、図 6 ~ 図 9 を参照して後述する VRAM 書込読出処理により、図 4 及び図 5 に示すように、W(書き込み)を表す実線と、R1、R2(読み出し)を表す 2 つの破線とが交差しないように制御される。これにより、VRAM 領域へ画像信号を書き込み中に更新途中の画像信号が読み出されることや、VRAM 領域から画像信号を読み出し中に画像信号が更新されてしまうことがなくなるので、「胴切り」が発生しない。「胴切り」とは、前述したように、VRAM 領域へ画像信号を書き込み中に読み出しが追い越す、もしくは、VRAM 領域から画像信号を読み出し中に書き込みが追い越すことにより、画面の上部と下部で撮影された時刻が異なる画像が読み出される現象をいう。

10

20

30

40

50

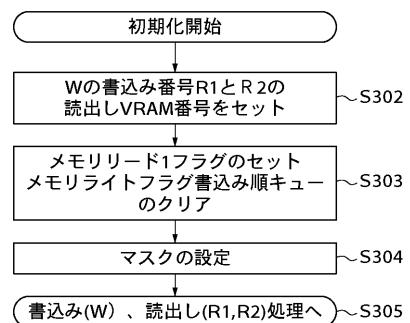

**【0036】**

図6は、映像信号処理装置100で実行されるVRAM書込読出処理のうちの初期化処理の手順を示すフローチャートである。なお、このVRAM書込読出処理は、システム制御部108において、ROMに格納された制御プログラムをCPUが実行することによって行われる処理である。以下、このフローチャートに沿って説明する。

**【0037】**

システム制御部108が、VRAM管理情報部112の書込みVRAM番号記録部166に記録するVRAM番号(Wの書込み対象VRAMの番号)と、R1及びR2の読み出し対象VRAM領域のVRAM番号とを1に設定する(S302)。

**【0038】**

つぎに、メモリリード1フラグ領域162にVRAM番号1に対応するフラグを立て、メモリライトフラグ領域161と書き込み順キュー領域164とをクリアする(S303)。

**【0039】**

また、映像信号処理装置100が、画像表示部104での画像の表示と、圧縮回路107を通して記憶媒体106への圧縮画像の保存との両方を行う場合は、マスク領域167におけるすべてのVRAM領域に対応するフラグに1をセットし、一方、画像表示部104での画像の表示のみを行う場合は、マスク領域167におけるすべてのVRAM領域に対応するフラグに0をセットする(S304)。

**【0040】**

続けて、W、R1、R2それぞれでの書込読出処理を開始する(S305)。

**【0041】**

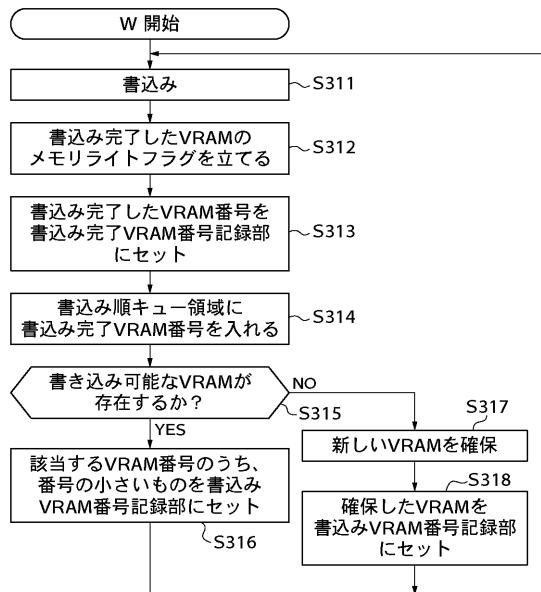

図7は、映像信号処理装置100で実行されるVRAM書込読出処理のうちのW(信号処理部109から出力された画像信号のVRAM部111への書込み)処理の手順を示すフローチャートである。

**【0042】**

VRAM管理情報部112の書込みVRAM番号記録部166に記録されているVRAM番号に対応するVRAM領域に画像信号を書込む(S311)。この書込みが完了した時点でメモリライトフラグ領域161に、書込み完了したVRAM領域に対応するフラグを立てる(S312)とともに、書込み完了VRAM番号記録部165に、書き込みが完了したVRAM領域のVRAM番号を記録し(S313)、さらに、書き込み順キュー領域164の最後尾にこのVRAM番号を記録する(S314)。

**【0043】**

次に、VRAM部111に、書込み可能なVRAM領域が存在するか否かを判別する(S315)。すなわち、対応するVRAM領域どうしにおいて、メモリライトフラグ領域161に記録されたフラグとマスク領域167に記録されたフラグとの論理積を取ったものと、メモリリード1フラグ領域162に記録されたフラグの論理和をとり、それがゼロになるVRAM領域が存在するか否かを判別する。ゼロになるVRAM領域が存在するならばステップS316へ進み、ゼロになるVRAM領域が存在しなければステップS317へ進む。

**【0044】**

ステップS316では、書込み可能なVRAM領域が複数あった場合、その中から1つのVRAM領域を選択する。例えば、該当する複数のVRAM領域のうちでVRAM番号が最も小さいVRAMを選択する。そしてステップS311へ戻る。

**【0045】**

ステップS317では、書込み可能なVRAM領域が存在しないので、VRAM部111に新しいVRAM領域を確保し、次のステップS318で、そのVRAM領域を次に書き込みを行うべきVRAM領域として、そのVRAM番号を書き込みVRAM番号記録部166に記録する。

**【0046】**

10

20

30

40

50

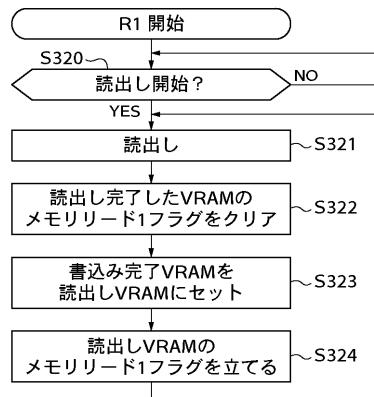

図8は、映像信号処理装置100で実行されるVRAM書き込み読み出し処理のうちのR1（VRAM部111から画像表示処理回路105への画像信号の読み出し）処理の手順を示すフローチャートである。

#### 【0047】

まず、書き込み完了VRAM番号記録部165にVRAM番号が記録されるまで読み出しを開始せずに待機する（S320）。書き込み完了VRAM番号記録部165にVRAM番号が記録されたらステップS321へ進んで、その記録されたVRAM番号のVRAM領域から画像表示処理回路105へ画像信号の読み出しを始める。

#### 【0048】

画像信号の読み出しが完了したら、次に、メモリリード1フラグ領域162において、読み出しを完了したVRAM領域に対応するフラグをクリアする（S322）。

#### 【0049】

次に、書き込み完了VRAM番号記録部165に記録されているVRAM番号のVRAM領域を、次に読み出しを行うべきVRAM領域に設定し（S323）、メモリリード1フラグ領域162において、その設定されたVRAM領域に対応するフラグを立てる（S324）。その後、ステップS321へ戻り、再度読み出しを始める。

#### 【0050】

なお、R1がWより遅い場合はステップS323において、書き込みVRAM番号記録部166に記録されているVRAM番号のVRAM領域を、次に読み出しを行うべきVRAM領域に設定してもよい。またR1がWより速い場合においても、R1が書き込みVRAM番号記録部166に記録されているVRAM番号のVRAM領域から読み出しを開始してもWに追いつかないならば、書き込みVRAM番号記録部166に記録されたVRAM番号のVRAM領域を、次に読み出しを行うべきVRAM領域に設定してもよい。

#### 【0051】

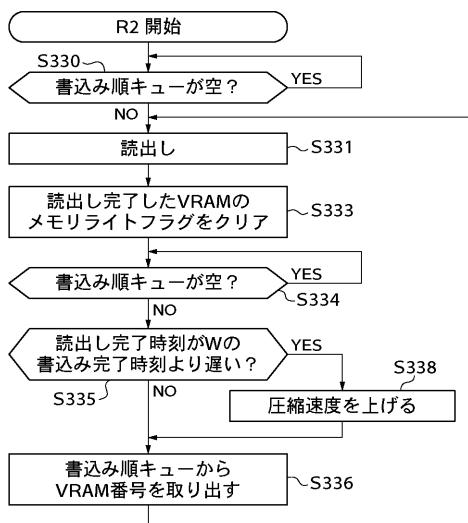

図9は、映像信号処理装置100で実行されるVRAM書き込み読み出し処理のうちのR2（VRAM部111から圧縮回路107への画像信号の読み出し）処理の手順を示すフローチャートである。

#### 【0052】

書き込み順キュー領域164に、書き込み完了したVRAM領域の番号が記録されるまで待ち（S330）、VRAM番号が記録されるとステップS331へ進んで、書き込み順キュー領域164の先頭位置に記載されるVRAM番号のVRAM領域より画像信号の読み出しを始める。この読み出しが完了したら、メモリライトフラグ領域161において、読み出しを完了したVRAM領域に対応するフラグをクリアする（S333）。

#### 【0053】

次に、書き込み順キュー領域164の記載が空であるか否かを調べ（S334）、空ならば読み出す画像信号が存在しないので、読み出しを始めずに、書き込み順キュー領域164にVRAM番号が記録されるまでポーリングしながら待機する（S334でYES）。

#### 【0054】

書き込み順キュー領域164が空でないときは、ステップS335へ進んで、ステップS331で行った読み出しの完了時刻（画像信号の圧縮処理に時間がかかると遅くなる）が、1フレーム先のWの書き込み完了時刻より遅いか否かを判別する。遅い場合はR2の読み出し完了時において圧縮処理すべき記憶領域が更に1つ残っている状態なので、圧縮処理を急ぐためにステップS338へ進む。また、遅くない場合はステップS336へ進む。

#### 【0055】

ステップS338では、圧縮回路107での量子化テーブルの値を変更（圧縮率を変更）して圧縮率を上げたり、圧縮回路107へ供給されるクロック信号の周波数を上げたりして、圧縮速度を速くする。

#### 【0056】

ステップS336では、書き込み順キュー領域164の先頭位置に記載されたVRAM番号を取り出して、このVRAM番号のVRAM領域を、R2の次の読み出しVRAM領域に

10

20

30

40

50

設定する。そしてステップ S 3 3 1 へ戻る。

**【0057】**

次に、図 4 および図 5 に示す W , R 1 及び R 2 の処理状況の一例を参照して、上記の V RAM 書込読出処理を具体的に説明する。

**【0058】**

まず、R 2 の圧縮速度が変化しない場合における W , R 1 及び R 2 の処理状況の一例を示す図 4 を参照して、時間軸に沿って説明する。

**【0059】**

初期化処理として、書込み V RAM 番号記録部 166 に V RAM 番号 1 を記録し、かつ、R 1 及び R 2 の読み出し処理対象の V RAM 領域の V RAM 番号を 1 にする (S 3 0 2) 10 。さらにメモリリード 1 フラグ領域 162 において V RAM 番号 1 の V RAM 領域に対応するフラグを立て (フラグに 1 をセット) 、メモリライトフラグ領域 161 において全部の V RAM 領域に対応するフラグをクリア (フラグに 0 をセット) し、書込み順キュー領域 164 の V RAM 番号の記載をクリアする (S 3 0 3) 。また図 4 に示す例では、映像信号処理装置 100 が画像表示部 104 での画像の表示と、圧縮回路 107 を通して記憶媒体 106 への圧縮画像の保存との両方を行うので、マスク領域 167 におけるすべての V RAM 領域に対応するフラグに 1 をセットする (S 3 0 4) 。

**【0060】**

図 4 に示す時刻 0 で、W は V RAM 番号 1 の V RAM 領域へ画像信号の書き込みを開始する (S 3 1 1) 20 。

**【0061】**

時刻 t 1 w で、W は V RAM 番号 1 の V RAM 領域への書き込みを完了し、この時点で書込み完了 V RAM 番号記録部 165 に V RAM 番号 1 が記録される (S 3 1 3) とともに、書込み順キュー領域 164 に V RAM 番号 1 が記録される (S 3 1 4) 。このとき、V RAM 領域ごとに、メモリライトフラグ領域 161 に記載のフラグとマスク領域 167 に記載のフラグとの論理積を取ったものと、メモリリード 1 フラグ領域 162 との論理和を取ると (S 3 1 5) 、V RAM 番号 2 と V RAM 番号 3 とに対応するフラグがゼロになっているので、それらのうち番号の小さい V RAM 番号 2 の V RAM 領域を、W の書き込み対象として選択し、V RAM 番号 2 を書き込み V RAM 番号記録部 166 に更新記録する (S 3 1 6) 30 。

**【0062】**

時刻 t 1 w で、ステップ S 3 1 3 で書き込み完了 V RAM 番号記録部 165 に V RAM 番号 1 が記録されたので、R 1 は、V RAM 番号 1 の V RAM 領域からの読み出しを開始する (S 3 2 1) 。また、ステップ S 3 1 3 で書き込み順キュー領域 164 に V RAM 番号 1 が記録されたので、R 2 は、書き込み順キュー領域 164 に記録された V RAM 番号 1 の V RAM 領域から読み出しを開始する (S 3 3 0 及び S 3 3 1) 。なお、この読み出し開始に伴い、書き込み順キュー領域 164 の記載内容はクリアされる。

**【0063】**

時刻 t 1 R 2 で、R 2 は、V RAM 番号 1 の V RAM 領域からの読み出しを完了する。このとき、書き込み順キュー領域 164 は空なので、R 2 は時刻 t 2 R 2 まで待機する。 40

**【0064】**

時刻 t 1 R 1 で、R 1 は、V RAM 番号 1 の V RAM 領域からの読み出しを完了するので、メモリリード 1 フラグ領域 162 において V RAM 番号 1 に対応するフラグをクリアする (S 3 2 2) 。この時点で、書き込み完了 V RAM 番号記録部 165 には V RAM 番号 3 が記録されているが、この V RAM 番号 3 を、R 1 が次に読み出し処理すべき V RAM 領域の番号に設定して (S 3 2 3) 、さらにメモリリード 1 フラグ領域 162 において V RAM 番号 3 に対応するフラグを立て (S 3 2 4) 、読み出しを続ける。

**【0065】**

以降、図 6 ~ 図 9 に示す各フローチャートに従って V RAM 書込読出処理を進めていくと、図 4 に示すような動作になる。 50

**【0066】**

次に、R2の圧縮速度が変化する場合におけるW, R1及びR2の処理状況の一例を示す図5を参照して、時間軸に沿って説明する。

**【0067】**

図5に示す時刻t1R2では、R2は、VRAM番号1のVRAM領域から読み出しを始めるが(S331)、このフレームの圧縮に時間がかかり、時刻t2R2になってようやく完了したとする。

**【0068】**

時刻t1wで、WはVRAM番号3のVRAM領域への書き込みが完了するので、VRAM領域ごとに、メモリライトフラグ領域161に記載のフラグとマスク領域167に記載のフラグとの論理積と、メモリリード1フラグ領域162に記載のフラグの論理和とを取ると、VRAM番号1、2、3に対応するフラグが共に1であるので、新たにVRAM番号4を確保し(S317)、書き込みVRAM番号記録部166にVRAM番号4を記録する(S318)。

10

**【0069】**

以降、図6～図9に示す各フローチャートに従ってVRAM書き込み処理を進めていくと、図5に示すような動作になる。

**【0070】**

上記説明では、映像信号処理装置100が、画像表示部104での画像の表示と、圧縮回路107を通して記憶媒体106への圧縮画像の保存とを並列して行うことを前提としているが、画像表示部104で画像の表示だけを行うときは、図6のステップS304において、マスク領域167に記載の全部のVRAM領域に対応するフラグをすべて0にセットしてから、図7～図9に示す各フローチャートに沿って処理を行うようにすればよい。また、画像表示部104での画像の表示と、圧縮回路107を通して記憶媒体106への圧縮画像の保存とを並列して行っていた状態から、画像表示部104での画像の表示だけを行う状態に遷移するには、メモリライトフラグ領域161に記載の全部のVRAM領域に対応するフラグをすべてクリアした後で、図6に示す初期化処理から処理を始めるようすればよい。

20

**【0071】**

また、上記説明では、VRAM部111内のVRAM領域の数が可変であることを前提にしていたが、VRAM領域の数が固定の場合は、圧縮処理に時間がかかった場合に相当するので、図9のステップS335及びステップS338に従い、圧縮速度を上げて圧縮処理にかかる時間を低減させるようにすれば、書き込み順キュー領域164が、圧縮処理待ちの画像信号に対応するVRAM番号で一杯になることを防ぐことができる。

30

**【0072】****[第2の実施の形態]**

次に、本発明の第2の実施の形態を説明する。

**【0073】**

第2の実施の形態の構成は、基本的に第1の実施の形態の構成と同じであるので、第2の実施の形態の説明においては、第1の実施の形態の構成と同一部分には同一の参照符号を付して、第1の実施の形態の説明を流用し、異なる部分だけを説明する。

40

**【0074】**

第2の実施の形態では、図1に示す第1の実施の形態におけるメモリ部113、VRAM部111及びVRAM管理情報部112に代わって、メモリ部113a、VRAM部111a及びVRAM管理情報部112aを設ける。VRAM部111aは、予め定められた数のVRAM領域を備え、その数は増減することはない。

**【0075】**

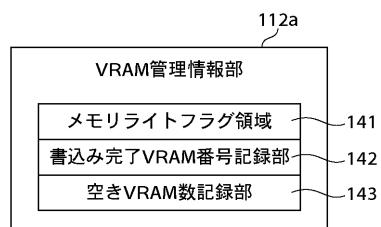

図10は、第2の実施の形態におけるVRAM管理情報部112aの内部メモリ構成を示す図である。

**【0076】**

50

すなわち、V R A M管理情報部 1 1 2 aは、メモリライトフラグ領域 1 4 1と、書き込み完了V R A M番号記録部 1 4 2と、空きV R A M数記録部 1 4 3とから構成される。

#### 【0077】

メモリライトフラグ領域 1 4 1には、第1の実施の形態におけるメモリライトフラグ領域 1 6 1と同様に、V R A M部 1 1 1 aの複数のV R A M領域にそれぞれ対応した複数のフラグが格納され、それらのフラグは、画像信号の対応V R A M領域への書き込みが完了したときに立てられ(1に設定)、対応V R A M領域から圧縮回路 1 0 7への画像信号の読み出しが完了したときにクリアされる(0に設定)。

#### 【0078】

書き込み完了V R A M番号記録部 1 4 2には、最後に書き込みの完了したV R A M領域の番号が記録される。 10

#### 【0079】

空きV R A M数記録部 1 4 3は、現在の空きV R A M領域の数を記録しており、1つのV R A M領域への書き込みが完了するごとにデクリメントされ、また1つのV R A M領域から圧縮回路 1 0 7への読み出しが完了するごとにインクリメントされる。

#### 【0080】

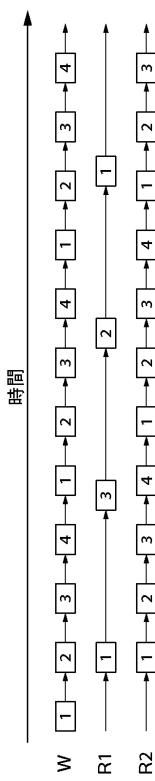

図 1 1 は、第2の実施の形態において、W、R 1、R 2が処理対象とするV R A M領域が時間軸に沿って遷移していく様子を示した図である。ただし、ここではV R A M部 1 1 1 aが4個のV R A M領域から成るものとし、図中のブロックがV R A M領域を示し、ブロック内の数字がV R A M番号である。 20

#### 【0081】

図 1 2 は、図 1 1 に示す4個のV R A M領域におけるW、R 1、R 2の処理状況を示すグラフである。横軸は時間、縦軸は各V R A M領域のメモリアドレスである。

#### 【0082】

なお、図 1 1 及び図 1 2 における書き込みと読み出しのフレームレートは、Wを80 f p s、R 1を30 f p s、R 2を100 f p sとする。

#### 【0083】

第2の実施の形態では、図 1 3 ~ 図 1 6 を参照して後述するV R A M書き込み読出処理により、図 1 2 に示すように、W(書き込み)を表す実線と、R 1、R 2(読み出し)を表す2つの破線とが交差しないように制御される。これにより、V R A M領域へ画像信号を書き込み中に更新途中の画像信号が読み出されることや、V R A M領域から画像信号を読み出し中に画像信号が更新されてしまうことがなくなるので、前述の「胴切り」が発生しない。 30

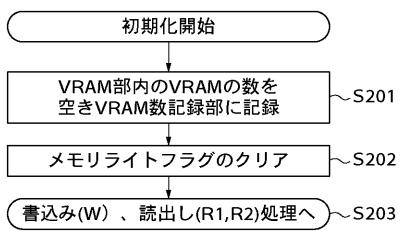

#### 【0084】

図 1 3 は、第2の実施の形態における映像信号処理装置 1 0 0 で実行されるV R A M書き込み読出処理のうちの初期化処理の手順を示すフローチャートである。

#### 【0085】

先ず、システム制御部 1 0 8 がV R A M部 1 1 1 a内のV R A M領域の数を空きV R A M数記録部 1 4 3に記録する(S 2 0 1)。また、メモリライトフラグ領域 1 4 1において、V R A M部 1 1 1 aの4つのV R A M領域に対応する4つのフラグをクリア(0に設定)する(S 2 0 2)。 40

#### 【0086】

続けて、W、R 1、R 2それぞれでの書き込み読出処理を開始する(S 2 0 3)。

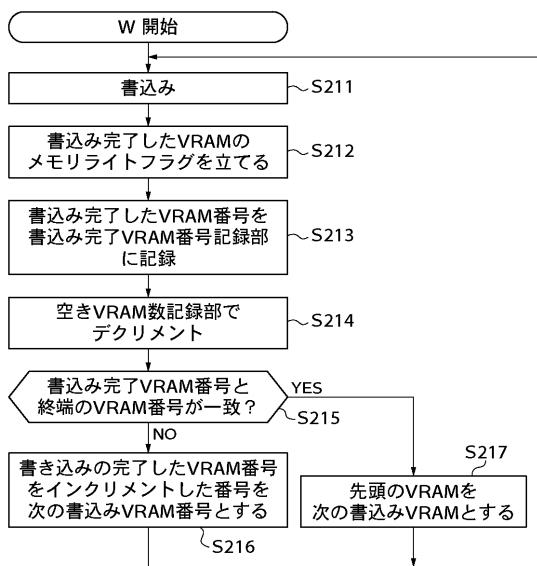

#### 【0087】

図 1 4 は、第2の実施の形態における映像信号処理装置 1 0 0 で実行されるV R A M書き込み読出処理のうちのW(信号処理部 1 0 9 から出力された画像信号のV R A M部 1 1 1 aへの書き込み)処理の手順を示すフローチャートである。

#### 【0088】

設定されたV R A M領域(この処理の始めて行う場合は、V R A M番号 1 に対応するV R A M領域)に画像信号を書き込む(S 2 1 1)。この書き込みが完了した時点で、メモリライトフラグ領域 1 4 1において、書き込みが完了したV R A M領域に対応するフラグを立 50

てる（1にセット）とともに（S212）、書き込みが完了したVRAM領域のVRAM番号を書き込み完了VRAM番号記録部142に記録する（S213）。この書き込みによつて空きVRAM領域の数が一つ減るので、空きVRAM数記録部143でデクリメントを行う（S214）。

#### 【0089】

書き込み完了VRAM番号記録部142に記録されたVRAM番号が、終端のVRAM番号（4）と一致するか否かを判別し（S215）、一致するならばステップS217へ進み、一致しないならばステップS216へ進む。

#### 【0090】

ステップS217では、先頭の番号（1）のVRAM領域を、次に書き込み処理を行うべきVRAM領域に設定し、ステップS211へ戻る。 10

#### 【0091】

ステップS216では、書き込みの完了したVRAM領域の番号をインクリメントした番号をもつVRAM領域を、次に書き込み処理を行うべきVRAM領域に設定し、ステップS211へ戻る。

#### 【0092】

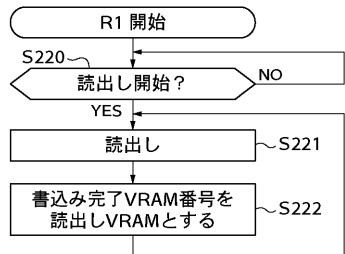

図15は、第2の実施の形態における映像信号処理装置100で実行されるVRAM書き込み出処理のうちのR1（VRAM部111aから画像表示処理回路105への画像信号の読み出し）処理の手順を示すフローチャートである。

#### 【0093】

まず、書き込み完了VRAM番号記録部142にVRAM番号が記録されるまで読み出しを開始せずに待機する（S220）。書き込み完了VRAM番号記録部142にVRAM番号が記録されたら、先頭のVRAM番号をもつVRAM領域より画像信号を読み出す（S221）。この読み出しを完了したら、書き込み完了VRAM番号記録部142に記録されているVRAM番号をもつVRAM領域を、次の読み出し処理対象にする（S222）。 20

#### 【0094】

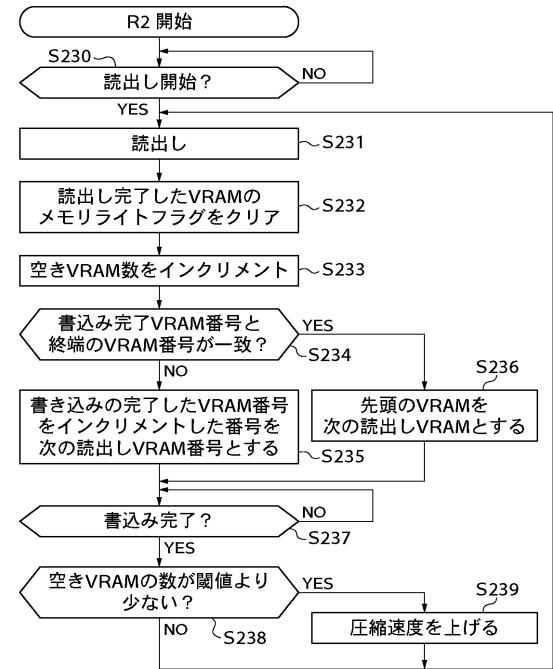

図16は、第2の実施の形態における映像信号処理装置100で実行されるVRAM書き込み出処理のうちのR2（VRAM部111aから圧縮回路107への画像信号の読み出し）処理の手順を示すフローチャートである。

#### 【0095】

Wの書き込みVRAM領域とR2の読み出しVRAM領域とが一致しなくなるまで待ってから（S230）、ステップS231へ進み、書き込み完了VRAM番号記録部142に記録されているVRAM番号のVRAM領域から画像信号を読み出して圧縮する。読み出しが完了したら、メモリライトフラグ領域141において、読み出しを完了したVRAM領域の番号に対応するフラグをクリアする（S232）とともに、空きVRAM数記憶部143に記載のVRAM領域の数をインクリメントする（S233）。 30

#### 【0096】

次に、書き込み完了VRAM番号記録部142に記載されたVRAM番号と終端のVRAM番号（4）とが一致するか否かを判別する（S234）。一致する場合はステップS236へ進み、一致しない場合はステップS235へ進む。 40

#### 【0097】

ステップS236では、先頭の番号（1）のVRAM領域を、次に読み出し処理を行うべきVRAM領域に設定し、ステップS237へ進む。

#### 【0098】

ステップS235では、書き込みの完了したVRAM領域の番号をインクリメントした番号をもつVRAM領域を、次に読み出し処理を行うべきVRAM領域に設定し、ステップS237へ進む。

#### 【0099】

ステップS237では、ステップS235またはステップS236で設定された次に書き込み処理を行うべきVRAM領域に対してWによる書き込みが完了するまで待機する。こ 50

の書き込みが完了すると、ステップ S 238 へ進む。

**【0100】**

ステップ S 238 では、空き V R A M 数記録部 143 に記載されていつ空き V R A M 領域数が所定の閾値より少ないか否かを判別し、少ないならばステップ S 239 へ進み、少なくないならばステップ S 239 をスキップしてステップ S 231 へ戻る。

**【0101】**

ステップ S 239 では、圧縮回路 107 での量子化テーブルの値を変更（圧縮率を変更）して圧縮率を上げたり、圧縮回路 107 へ供給されるクロック信号の周波数を上げたりして、圧縮速度を速くし、これによって、圧縮回路 107 への読み出しが行われていない V R A M 領域の数を減らして、空き V R A M 領域の数を多く確保するようにする。なお、圧縮速度を上げた結果、再度のステップ S 238 の実行時に、空き V R A M 領域数が所定の閾値以上になっていた場合には、量子化テーブルの値と圧縮回路 107 に供給するクロックスピードとを元に戻して圧縮速度を遅くするようとする。10

**【0102】**

次に、図 12 に示す W, R1 及び R2 の処理状況の一例を参照して、上記の V R A M 書込読み出し処理を、時間軸に沿って具体的に説明する。

**【0103】**

先ず初期化処理として、空き V R A M 領域数記録部 143 に、V R A M 部 111a 内の V R A M 領域の数である 4 を記録する（S 201）。また、メモリライトフラグ領域 141 をクリアする（S 202）。20

**【0104】**

図 12 に示す時刻 0 において、W は V R A M 番号 1 への書き込みを始める。

**【0105】**

時刻 t 1w で、W は、V R A M 番号 1 の V R A M 領域への書き込みを完了するので、メモリライトフラグ領域 141 において、V R A M 番号 1 に対応するフラグを立てる（S 212）。また、書き込み完了 V R A M 番号記録部 142 に V R A M 番号 1 を記録し（S 213）、空き V R A M 数記録部 143 に記録されている空き V R A M 領域数を 4 から 3 に減らす（S 214）。

**【0106】**

ここで、書き込み完了 V R A M 番号記録部 142 に記録されている V R A M 番号 1 と終端の V R A M 領域の V R A M 番号 4 とは一致しないので（S 215 で NO）、V R A M 番号 1 をインクレメントして得られた V R A M 番号 2 を、次に書き込みが行われるべき V R A M 領域の V R A M 番号にする（S 216）。30

**【0107】**

時刻 t 1w で書き込み完了番号記録部 142 に V R A M 番号 1 が記録されたので、R1 は、この V R A M 番号 1 をもつ V R A M 領域から読み出しを始める（S 220 と S 221）。

**【0108】**

さらに時刻 t 1w の時点でメモリライトフラグ領域 141 において V R A M 番号 1 に対応するフラグが立ったので（S 230）、R2 も、V R A M 番号 1 の V R A M 領域から読み出しを始める（S 231）。40

**【0109】**

時刻 t 1R2 で、R2 は V R A M 番号 1 の V R A M 領域からの読み出しを完了するので、メモリライトフラグ領域 141 において V R A M 番号 1 に対応するフラグをクリアし（S 232）、空き V R A M 領域数記録部 143 に記録されている空き V R A M 領域数を 3 から 4 に増やす（S 233）。このとき、書き込み完了 V R A M 番号記録部 142 に記録されている V R A M 番号 1 と終端の V R A M 領域の V R A M 番号 4 とは一致しないので（S 234 で NO）、V R A M 番号 1 をインクレメントして得られた V R A M 番号 2 を、次に書き込みを行うべき V R A M 領域の番号にする（S 235）。

**【0110】**

ところで、時刻 t 1R2 の時点ではメモリライトフラグ領域 141 において V R A M 番50

号2に対応するフラグがまだ立っていないので、時刻t2R2でWによるVRAM番号2のVRAM領域への書き込みが完了して、メモリライトフラグ領域141においてVRAM番号2に対応するフラグが立てられるまで待機する(S237)。

#### 【0111】

時刻t1R1では、R1が、VRAM番号1のVRAM領域からの読み出しを完了する。この時点での書き込み完了VRAM番号記録部142にはVRAM番号3が記録されているので、VRAM番号3のVRAM領域を、次に読み出し処理を行うべきVRAM領域にする(S222)。

#### 【0112】

時刻t2wでは、Wが、VRAM番号4のVRAM領域への書き込みを完了するので、メモリライトフラグ領域141においてVRAM番号4に対応するフラグを立て(S212)、書き込み完了VRAM番号記録部142にVRAM番号4を記録し(S213)、空きVRAM領域数記録部143に記録した空きVRAM領域数を4から3に減らす(S214)。

#### 【0113】

このとき、書き込み完了VRAM番号記録部142に記録されているVRAM番号4と終端のVRAM領域のVRAM番号4とが一致するので(S215でYES)、先頭のVRAM番号1のVRAM領域を、次に書き込みを行うべきVRAM領域の番号に設定して(S217)、書き込みを続ける。

#### 【0114】

以降、図13～図16に示す各フローチャートに従ってVRAM書き込み出処理を進めていくと、図12に示すような動作になる。

#### 【0115】

##### 〔他の実施の形態〕

なお、本発明の目的は、前述した各実施の形態の機能を実現するソフトウェアのプログラムコードを記録した記憶媒体を、システムまたは装置に供給し、そのシステムまたは装置のコンピュータ(またはCPU、MPU等)が記憶媒体に格納されたプログラムコードを読み出して実行することによっても達成される。

#### 【0116】

この場合、記憶媒体から読み出されたプログラムコード自体が本発明の新規な機能を実現することになり、そのプログラムコードを記憶した記憶媒体およびプログラムは本発明を構成することになる。

#### 【0117】

また、プログラムコードを供給するための記憶媒体としては、例えば、フレキシブルディスク、ハードディスク、光ディスク、光磁気ディスク、CD-ROM、CD-R、CD-RW、DVD-ROM、DVD-RAM、DVD-RW、DVD+RW、磁気テープ、不揮発性のメモリカード、ROM等を用いることができる。或いは、上記プログラムは、インターネット、商用ネットワーク、若しくはローカルエリアネットワーク等に接続される他のコンピュータやデータベース等からダウンロードすることにより供給される。

#### 【0118】

また、コンピュータが読み出したプログラムコードを実行することにより、前述した各実施の形態の機能が実現されるだけでなく、そのプログラムコードの指示に基づき、コンピュータ上で稼動しているOS(オペレーティングシステム)等が実際の処理の一部または全部を行い、その処理によって前述した各実施の形態の機能が実現される場合も含まれる。

#### 【0119】

更に、記憶媒体から読み出されたプログラムコードが、コンピュータに挿入された機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに書き込まれた後、そのプログラムコードの指示に基づき、その機能拡張ボードや機能拡張ユニットに備わるCPU等が実際の処理の一部または全部を行い、その処理によって前述した各実施の

10

20

30

40

50

形態の機能が実現される場合も含まれる。

【図面の簡単な説明】

【0120】

【図1】本発明の第1の実施の形態に係る映像信号処理装置の構成を示すブロック図である。

【図2】メモリ部におけるVRAM管理情報部の内部メモリ構成を示す図である。

【図3】R2の処理レートが固定されていると仮定した場合に、W、R1、R2が処理対象とするVRAM領域が時間軸に沿って遷移していく様子を示した図である。

【図4】図3に示す3個のVRAM領域におけるW、R1、R2の処理状況を示すグラフである。

【図5】R2の処理レートが変動した場合におけるW、R1、R2の処理状況を示すグラフである。

【図6】映像信号処理装置で実行されるVRAM書き読み出しがうちの初期化処理の手順を示すフローチャートである。

【図7】映像信号処理装置で実行されるVRAM書き読み出しがうちのW(信号処理部から出力された画像信号のVRAM部への書き込み)処理の手順を示すフローチャートである。

【図8】映像信号処理装置で実行されるVRAM書き読み出しがうちのR1(VRAM部から画像表示処理回路への画像信号の読み出し)処理の手順を示すフローチャートである。

【図9】映像信号処理装置で実行されるVRAM書き読み出しがうちのR2(VRAM部から圧縮回路への画像信号の読み出し)処理の手順を示すフローチャートである。

【図10】第2の実施の形態におけるVRAM管理情報部の内部メモリ構成を示す図である。

【図11】第2の実施の形態において、W、R1、R2が処理対象とするVRAM領域が時間軸に沿って遷移していく様子を示した図である。

【図12】図11に示す4個のVRAM領域におけるW、R1、R2の処理状況を示すグラフである。

【図13】第2の実施の形態における映像信号処理装置で実行されるVRAM書き読み出しがうちの初期化処理の手順を示すフローチャートである。

【図14】第2の実施の形態における映像信号処理装置で実行されるVRAM書き読み出しがうちのW処理の手順を示すフローチャートである。

【図15】第2の実施の形態における映像信号処理装置で実行されるVRAM書き読み出しがうちのR1処理の手順を示すフローチャートである。

【図16】第2の実施の形態における映像信号処理装置で実行されるVRAM書き読み出しがうちのR2処理の手順を示すフローチャートである。

【符号の説明】

【0121】

100 映像信号処理装置

101 撮像レンズ

102 撮像素子

103 A/D変換器

104 画像表示部

105 画像表示処理回路

106 記憶媒体

107 圧縮回路

108 システム制御部(メモリ制御手段)

109 信号処理部

110 メモリ制御部(メモリ制御手段、制御手段)

111 VRAM部

10

20

30

40

50

- 1 1 2 VRAM管理情報部

1 1 3 メモリ部

1 6 1 メモリライトフラグ領域

1 6 2 メモリリード1フラグ領域

1 6 4 書込み順キュー領域

1 6 5 書込み完了VRAM番号記録部

1 6 6 書込みVRAM番号記録部

1 6 7 マスク領域

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図1-1】

【図1-2】

【図1-3】

【図1-4】

【図15】

【図16】

---

フロントページの続き

(56)参考文献 特開2003-324644(JP,A)

特開平06-067632(JP,A)

特開2000-197003(JP,A)

特開2000-125255(JP,A)

特開平08-288860(JP,A)

特開2004-187018(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5 / 225

H04N 5 / 76 - 5 / 907