(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

28 July 2005 (28.07.2005)

PCT

(10) International Publication Number

WO 2005/069362 A1

(51) International Patent Classification<sup>7</sup>: H01L 21/336, (21) International Application Number: PCT/US2004/035407

(22) International Filing Date: 26 October 2004 (26.10.2004)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data: 10/747,680 30 December 2003 (30.12.2003) US

(71) Applicant (for all designated States except US): ADVANCED MICRO DEVICES, INC. [US/US]; One AMD Place, Mail Stop 68, P.O. Box 3453, Sunnyvale, CA 94088-3453 (US).

(72) Inventors; and

(75) Inventors/Applicants (for US only): ZHONG, Huicai [CN/US]; 509 Popula Blvd., Wappingers Falls, NY 12590 (US). DAKSHINA-MURTHY, Srikanteswara [IN/US]; 258 Town View Drive, Wappingers Falls, NY 12590 (US).

(74) Agent: DRAKE, Paul, S.; One AMD Place, Mail Stop 68, P.O. Box 3453, Sunnyvale, CA 94088-3453 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

— with international search report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: A METHOD FOR FORMING RECTANGULAR-SHAPE SPACERS FOR SEMICONDUCTOR DEVICES

WO 2005/069362 A1

(57) Abstract: A semiconductor device and method of making the same forms a spacer (46) by depositing a spacer layer (34) over a substrate (30) and a gate electrode (32) and forms a protective layer (42) on the spacer layer (34). The protective layer (42) is dry etched to leave a thin film sidewall on the spacer layer (34). The spacer layer (34) is then etched, with the protective layer (42) protecting the outer sidewalls of the spacer layer (34). This etching creates spacers (46) on the gate that have substantially vertical sidewalls (52) that extend parallel to the gate electrode sidewalls (38). The I-shape of the spacers (46) prevent punch-through during the source/drain ion implantation process, providing an improved source/drain implant dose profile.

A METHOD FOR FORMING RECTANGULAR-SHAPED

SPACERS FOR SEMICONDUCTOR DEVICES

## FIELD OF THE INVENTION

The present invention relates to the field of semiconductor processing, and more particularly, to the

5 formation of spacers and source/drain formation in semiconductor devices.

## BACKGROUND OF THE INVENTION

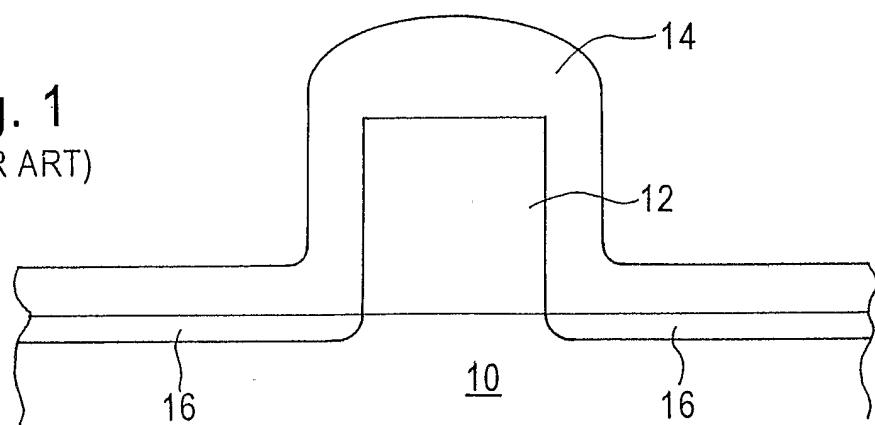

In the formation of semiconductor devices, it is desirable to create spacers on the sidewalls of a gate to serve as masks during source/drain implantation. An exemplary spacer formation process and implantation process is depicted in Figs. 1-3 described below.

10 In Fig. 1, a substrate 10 has a gate 12 formed thereon. The gate 12 may be a polysilicon gate, for example. Source/drain extension regions 16 are formed, by ion implantation, for example, employing the gate 12 as an implantation mask. A spacer layer 14 is deposited by any suitable method, such as chemical vapor deposition. The spacer layer may be made of any suitable material, such as silicon nitride, silicon oxide, low-k dielectric materials, etc.

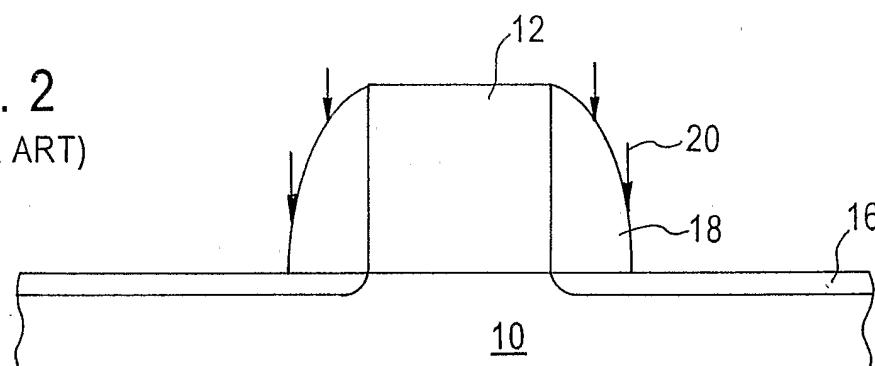

15 An isotropic etching is performed, the results of which are depicted in Fig. 2. The isotropic etching creates "D"-shaped spacers 18 that extend from the sidewalls of gate 12. The spacers 18 form a mask, along with the gate 12, for performing a source/drain implantation process. It is desirable to space the deep source/drain regions from the gate 12 in order to reduce short channel effects. An ion implantation process, as indicated by arrows 20, is employed to create the deep source/drain implants. However, as will be recognized

20 by the configuration of the D-shaped spacers 18 in Fig. 2, the outer regions of the D-shaped spacers 18 have a relatively thin profile at the outer edges. This allows some "punch-through" of the ions during the deep source/drain implantation process, which is a relatively high-energy process.

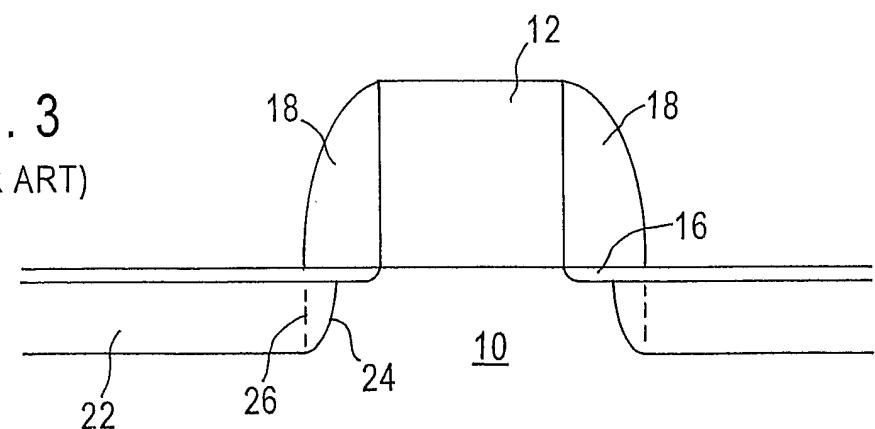

The consequences of the punch-through due to the thin profile of the spacers 18 is depicted in Fig. 3. An impressive control of the location of the deep source/drain implants creates the formation of source/drain

25 regions 22 that extend underneath the spacers 18 to the area indicated by 24. This is further than the desirable region indicated by 26 in Fig. 3. Hence, the channel has been undesirably shortened due to the punch-through of the D-shaped spacers 18 during the source/drain implantation process.

Another disadvantage of the D-shaped spacers 18 is the worsening of conformity for further film deposition, necessary in such processes as the formation of a double spacer or the forming of an interconnect

30 layer dielectric. The sloping nature of the outer shape of the spacers reduces conformity in subsequent film depositions.

## SUMMARY OF THE INVENTION

There is a need for a method of forming a spacer and a semiconductor device that provides for increased control of the source/drain implantation process, as well as improving conformity for further film

35 deposition.

These and other needs are met by embodiments of the present invention which provide a method of forming a spacer comprising the steps of depositing a spacer layer over a substrate and a gate electrode having

a top surface and vertically extending sidewalls, and forming a protective layer on the spacer layer. The protective layer is etched to remove the protective layer from the spacer layer over the top surface of the gate electrode and maintain the protective layer on the spacer layer parallel to the sidewalls of the gate electrode. The spacer layer is etched to remove the spacer layer from the substrate and over the top surface of the gate 5 electrode to form spacers on the gate electrode with each spacer having two substantially vertical sidewalls extending parallel to the gate electrode sidewalls.

By providing a protective layer on the spacer layer, the sidewall of the spacer is protected during the etching process, so that a substantially rectangular (I-shaped) spacer is formed. The spacer according to the present invention therefore does not have a thinner outer edge that makes the implantation profile difficult to 10 control. Also, the relatively vertical outer wall of the spacer increases conformity for further film deposition, such as double spacer processes or interconnect layer dielectrics.

The earlier stated needs are also met by other embodiments of the present invention which provide a method of forming a semiconductor device comprising the steps of forming a gate electrode having vertically extending sidewalls on a substrate, and forming first sidewall spacers on the gate electrode. Each first 15 sidewall spacer has a pair of vertically extending planar sidewalls that are substantially parallel to the gate electrode sidewalls. A source/drain implantation process is performed with the gate electrode and the first sidewall spacers masking the substrate.

The earlier stated needs are also met by other embodiments of the present invention which provide a semiconductor device comprising a substrate, a gate on the substrate with the gate having vertical sidewalls, 20 and sidewall spacers. The sidewall spacers are on the gate sidewalls, and have a rectangular cross-section and extend vertically to greater than half the height of the gate. Ion implanted source/drain regions are provided that are defined by the sidewall spacers.

The foregoing and other features, aspects and advantages of the present invention will become more apparent from the following detailed description of the present invention when taken in conjunction with the 25 accompanying drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Fig. 1 is a schematic, cross-sectional view of a semiconductor device during one phase of manufacture in accordance with prior art methodology.

Fig. 2 depicts the structure of Fig. 1 following isotropic etching to form spacers in accordance with 30 prior art methodologies.

Fig. 3 shows the structure of Fig. 2 after a source/drain implantation process has been performed.

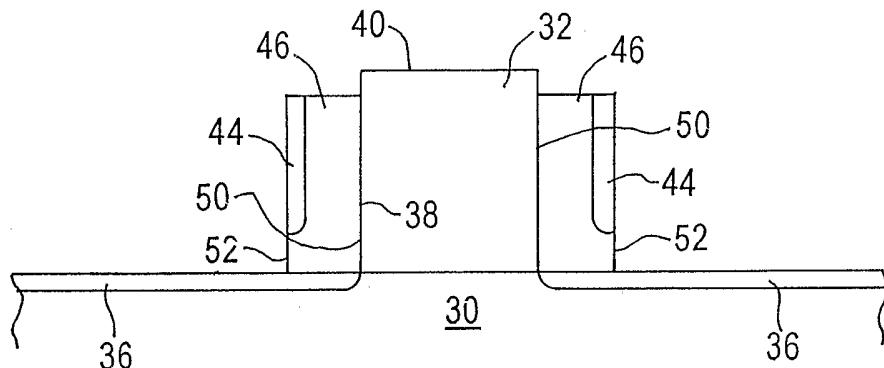

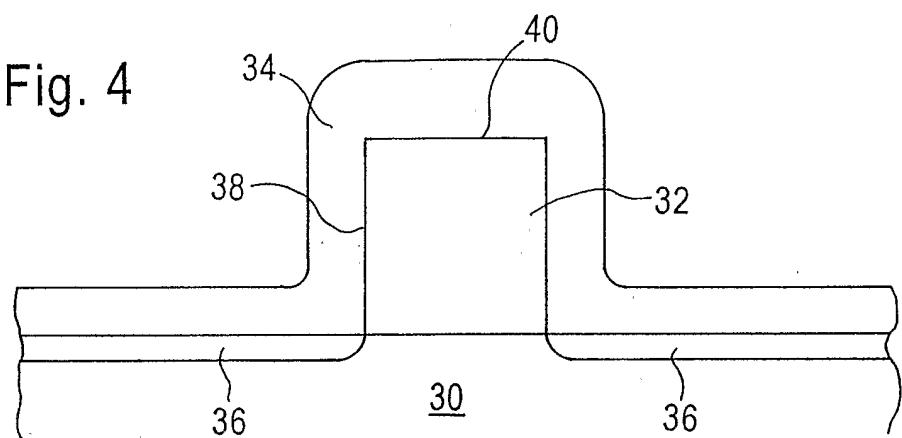

Fig. 4 is a schematic, cross-sectional view of a semiconductor device during one phase of manufacture in accordance with embodiments of the present invention, following the deposition of a spacer 35 layer.

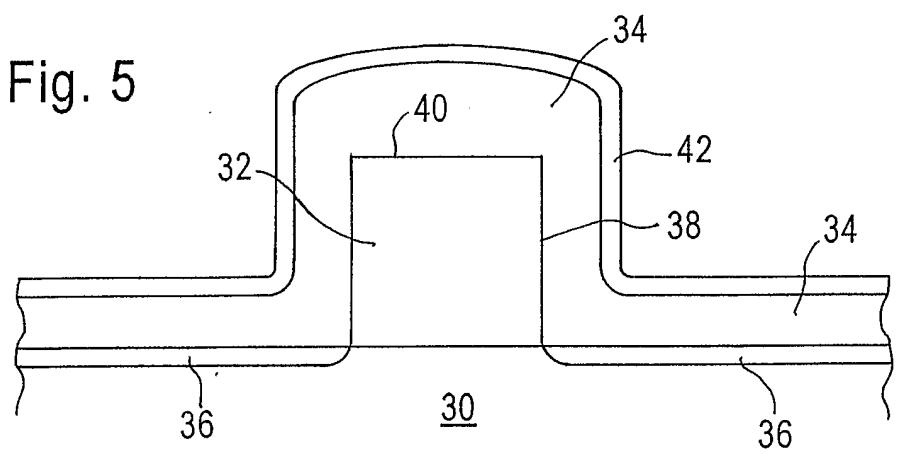

Fig. 5 shows the structure of Fig. 4 after the deposition of a protective layer on the spacer layer, in accordance with embodiments of the present invention.

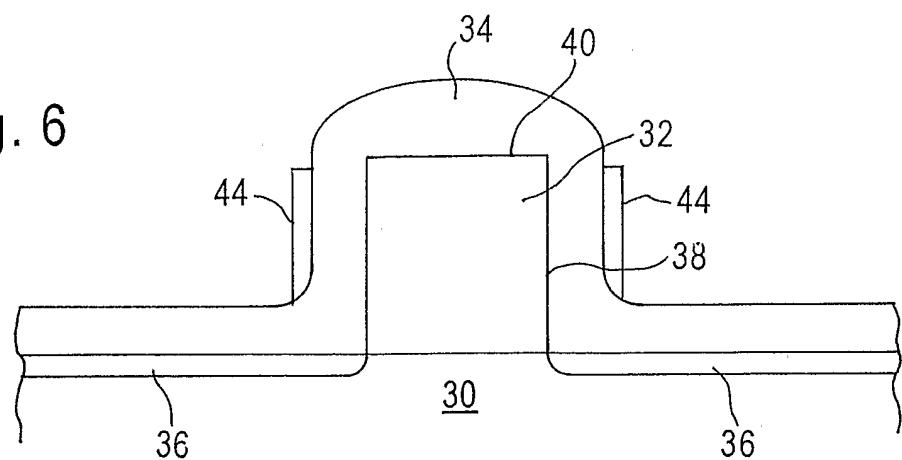

Fig. 6 depicts the structure of Fig. 5 following the etching of the protective layer in accordance with 40 embodiments of the present invention.

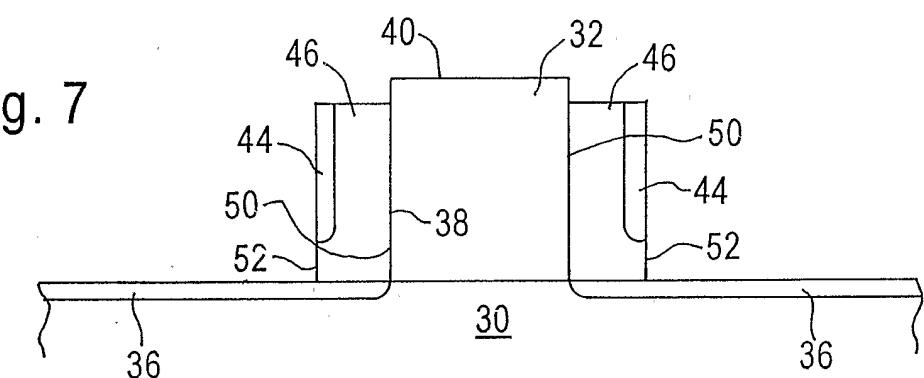

Fig. 7 shows the structure of Fig. 6 following the etching of the spacer layer in accordance with embodiments of the present invention.

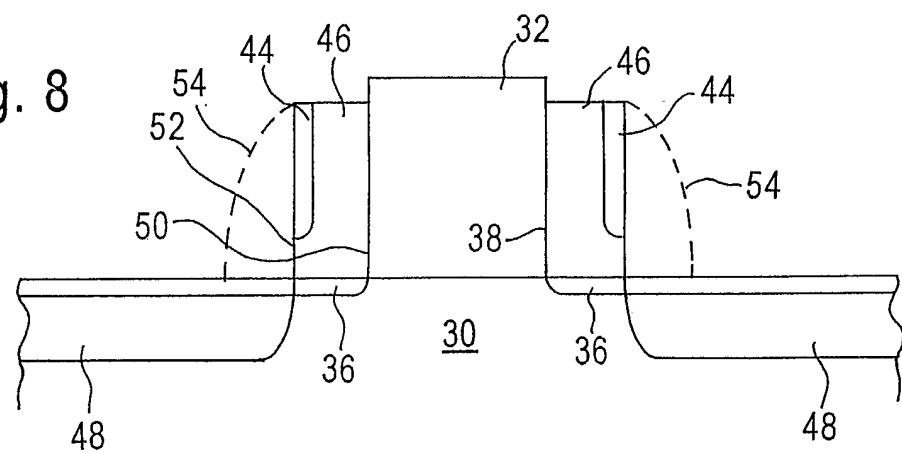

Fig. 8 depicts the structure of Fig. 7 during a source/drain implantation process performed in accordance with embodiments of the present invention.

## 5 DETAILED DESCRIPTION OF THE INVENTION

The present invention addresses and solves problems related to the formation of spacers and the source/drain implantation dose profile in advanced CMOSFET device technology. In particular, the invention overcomes problems related to the relatively thinner outer edge of the spacer created in the prior art with a D-shape that allowed punch-through during the source/drain implantation process, degrading the control of the 10 implant dose profile. The invention achieves improvement in the implant dose profiling during the source/drain implantation process by creating a substantially rectangular (I-shape) spacer on the gate and employing the spacer as a mask during the source/drain implantation process. Since the spacer of the present invention does not have a thinner region through which punch-through may occur, the invention provides a 15 precise source/drain implantation dose profiling. A further advantage is the increased conformity provided due to the steep sidewalls, allowing for improved film deposition. This is an important advantage for deep sub-micron CMOSFET fabrications since a thinner film deposition may be used to form a second spacer due to the improved conformity. Larger spacers are therefore possible for devices with a smaller pitch.

Fig. 4 is a schematic, cross-sectional view of a semiconductor device during one phase of manufacture in accordance with embodiments of the present invention. In Fig. 4, a substrate 30 has a gate 20 electrode 32, such as a polysilicon gate, formed thereon by conventional techniques. A source/drain extension formation process is formed, employing the gate 32 as a mask to create source/drain extensions 36.

The gate 32 has sidewalls 38 and a top surface 40. The sidewalls 38 of the gate 32 are typically formed by a dry etching technique, such as reactive ion etching (RIE), and are substantially vertical and planar.

25 A spacer layer 34 is shown deposited on the substrate 30 and over the gate 32. The spacer layer 34 may be made of any suitable dielectric material, such as a nitride, an oxide, a low-k dielectric material, etc. The deposition may be by any suitable technique, such as chemical vapor deposition, for example. A suitable depth or thickness of the spacer layer 34 is provided, and is dependent upon the desired width of the spacers that will eventually be formed after etching of the spacer layer 34. In certain exemplary embodiments of the 30 invention, the spacer layer is deposited to a thickness of between about 300 Å to about 800 Å.

In conventional techniques, the formation of the spacer layer 34 is followed by an isotropic etching to 35 form D-shaped spacers, such as depicted in Fig. 2. The present invention, however, instead forms a protective layer 42, as shown in Fig. 5, that is conformally deposited on the spacer layer 34. The material of the protective layer 42 is different from the material forming the spacer layer 34. In particular, the material in the protective layer 42 should be such that it is not substantially etched when the spacer layer 34 is subjected to an etching by a particular etchant. In other words, during the etching of the spacer layer 34 to form spacers, an etchant should be used that is highly selective to the material in the spacer layer 34. When the spacer layer 34 is made of nitride, for example, a suitable material for the protective layer 42 is an oxide, for example. Further, the material of the protective layer 42 should exhibit good conformity.

The thickness of the protective layer 42 is much less than that of the spacer layer 34 in embodiments of the present invention. For example, a thickness of between about 10 Å to about 100 Å may be employed to provide an adequate protection to the sidewalls of the spacers that will be formed from the spacer layer 34, as will be seen. As the remainder of the protective layer 42 is removed and serves no purpose, only a thickness 5 that provides a sufficient amount of protection to the sidewalls of the spacers formed from the spacer layer 34 is needed, so that a relatively thin protective layer 42 is desirable to reduce material costs and processing time.

Fig. 6 depicts the structure of Fig. 5 following an etching process to remove the protective layer 42 except along the vertically extending sidewalls of the spacer layer 34 that are parallel to the sidewalls 38 of the gate 32. These regions of the protective layer 44 are designated with reference numeral 44 in Fig. 6. The 10 etching is a dry etching, such as a reactive ion etching. The portions of the protective layer 42 are removed except for the vertically extending regions 44. A conventional dry etching technique may be employed.

Fig. 7 shows the structure of Fig. 6 after another etching has been performed to etch the spacer layer 34 and remove it from the substrate 30 and from over the top surface 40 of the gate electrode 32. This action forms spacers 46 on the gate sidewalls 38 of the gate 32.

15 During the etching process, which may be either a dry etch or an isotropic wet etch, the protective layer 44 on the outer sidewalls 52 of the spacers 46 protects the spacer layer material from being attacked during the etching process. Hence, vertical, or substantially vertical, outer sidewalls 52 of the spacers 46 are created. In cross-section, the spacers 46 exhibit a rectangular shape or "I-shape". The spacers 46 therefore do not present a thin outer region susceptible to punch-through during a source/drain implantation process.

20 A source/drain implantation process is performed, as shown in Fig. 8, to create source/drain regions 48. Because of the I-shape of the spacers 46, the source/drain implant dose profile is precise and does not extend underneath the outer edge of the spacers 46. Although the protective regions 44 are depicted in Fig. 8, this embodiment is exemplary only as in other embodiments, the protective regions 44 are removed as being unnecessary after the etching of the spacer layer 34. The lack of protective regions 44, which are very thin 25 (such as 10 angstroms) in any event, does not have a noticeable effect on the doping profile achieved by the I-shaped spacers 46.

Due to the vertical nature of the outer sidewalls 52 of the first sidewall spacers 46, an improved 30 conformity is provided for further film deposition, such as formation of a second sidewall spacer (shown as second sidewall spacers 54 in dashed lines in Fig. 8). Alternatively, conformity is also improved for other film depositions, such as interconnect layer dielectric material. Due to the increased conformity, a thinner film deposition for a second spacer formation may be employed. This makes larger spacers possible for devices with a smaller pitch.

The present invention thus provides a semiconductor device and method for making the same that exhibits a more controlled source/drain implant dose profile since there is no implantation penetration from the 35 corner of the spacer, and also allows larger spacers for devices with smaller pitch.

Although the present invention has been described and illustrated in detail, it is to be clearly understood that the same is by way of illustration and example only and is not to be taken by way of limitation, the scope of the present invention being limited only by the terms of the appended claims.

## WHAT IS CLAIMED IS:

1. A method of forming a spacer, comprising the steps:

- depositing a spacer layer (34) over a substrate (30) and a gate electrode (32) having a top surface (40) and vertically extending sidewalls (38);

- 5 forming a protective layer (42) on the spacer layer (34);

- etching the protective layer (42) to remove the protective layer (42) from the spacer layer (34) over the top surface (40) of the gate electrode (32) and maintain the protective layer (42) on the spacer layer (34) parallel to the sidewalls (38) of the gate electrode (40);

- 10 etching the spacer layer (34) to remove the spacer layer (34) from the substrate (30) and over the top surface (40) of the gate electrode (32) to form spacers (46) on the gate electrode (42) with each spacer (46) having two substantially vertical sidewalls (52) extending parallel to the gate electrode sidewalls (38).

2. The method of claim 1, wherein the spacer layer (34) is deposited to a thickness greater than 200 Å.

3. The method of claim 2, wherein the protective layer (42) is formed to a thickness between 15 about 10 Å to about 100 Å.

4. The method of claim 3, wherein the spacer layer (34) is a nitride and the protective layer (42) is an oxide.

5. A method of forming a semiconductor device, comprising the steps:

- forming a gate electrode (32) having vertically extending sidewalls (38) on a substrate (30);

- 20 forming first sidewall spacers (46) on the gate electrode (32), each first sidewall spacer (46) having a pair of vertically extending planar sidewalls (52) that are substantially parallel to the gate electrode sidewalls (38); and

- performing a source/drain implantation with the gate electrode (32) and the first sidewall spacers (46) masking the substrate (30).

6. The method of claim 5, wherein the step of forming first sidewall spacers (38) includes:

- depositing a spacer layer (34) over the substrate (30) and the gate electrode (32);

- 25 forming a protective layer (42) on the spacer layer (34); and

- etching the protective layer (42) and the spacer layer (34) to form the first sidewall spacer (46).

7. The method of claim 6, wherein the step of etching includes dry etching the protective layer 30 (42) to remove the protective layer (42) except for vertically extending portions of the protective layer (42) that are planar and substantially parallel to the gate electrode sidewalls (38).

8. The method of claim 7, wherein the step of etching further includes etching the spacer layer (34) to remove the spacer layer (34) from the substrate (30) and over a top surface (40) of the gate electrode

(32), leaving the spacer layer (34) between the gate electrode sidewalls (38) and the vertically extending portions of the protective layer (42).

9. The method of claim 8, further comprising forming a second sidewall spacer (44) in the first

5 sidewall spacer (46).

10. The method of claim 8, wherein the spacer layer (34) is etched with an etchant that is highly

selective to the spacer layer (34) and does not substantially etch the protective layer (42).

Fig. 1

(PRIOR ART)

Fig. 2

(PRIOR ART)

Fig. 3

(PRIOR ART)

Fig. 4

Fig. 5

Fig. 6

Fig. 7

Fig. 8

# INTERNATIONAL SEARCH REPORT

International Application No

PCT/US2004/035407

**A. CLASSIFICATION OF SUBJECT MATTER**

IPC 7 H01L21/336 H01L21/266

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

IPC 7 H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category <sup>o</sup> | Citation of document, with indication, where appropriate, of the relevant passages                                     | Relevant to claim No. |

|-----------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X                     | US 6 004 851 A (PENG ET AL)<br>21 December 1999 (1999-12-21)<br>column 3, line 46 - column 4, line 25<br>-----         | 1-8,10                |

| X                     | US 2003/227054 A1 (SAIKI TAKASHI)<br>11 December 2003 (2003-12-11)<br>paragraph '0045! - paragraph '0052!<br>-----     | 5-10                  |

| X                     | US 6 426 524 B1 (LAM CHUNG HON ET AL)<br>30 July 2002 (2002-07-30)<br>the whole document<br>-----                      | 1-4                   |

| X                     | US 4 488 351 A (MOMOSE ET AL)<br>18 December 1984 (1984-12-18)<br>column 5, line 28 - column 6, line 7<br>-----<br>-/- | 1-3,5-8,<br>10        |

Further documents are listed in the continuation of box C.

Patent family members are listed in annex.

<sup>o</sup> Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier document but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

- "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

- "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

- "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

- "&" document member of the same patent family

Date of the actual completion of the international search

22 April 2005

Date of mailing of the international search report

02/05/2005

Name and mailing address of the ISA

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,

Fax: (+31-70) 340-3016

Authorized officer

Gélibart, J

## INTERNATIONAL SEARCH REPORT

International Application No

PCT/US2004/035407

## C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT

| Category | Citation of document, with indication, where appropriate, of the relevant passages                                     | Relevant to claim No. |

|----------|------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X        | US 2003/045061 A1 (KWON HYUNG-SHIN ET AL)<br>6 March 2003 (2003-03-06)<br>paragraph '0005! – paragraph '0013!<br>----- | 1,2,5-10              |

| X        | US 2002/140100 A1 (YOKOYAMA YUJI)<br>3 October 2002 (2002-10-03)<br>figure 2<br>-----                                  | 1,4                   |

## INTERNATIONAL SEARCH REPORT

## Information on patent family members

International Application No

PCT/US2004/035407

| Patent document cited in search report |    | Publication date |      | Patent family member(s) |  | Publication date |

|----------------------------------------|----|------------------|------|-------------------------|--|------------------|

| US 6004851                             | A  | 21-12-1999       | NONE |                         |  |                  |

| US 2003227054                          | A1 | 11-12-2003       | JP   | 2004014875 A            |  | 15-01-2004       |

| US 6426524                             | B1 | 30-07-2002       | US   | 6190961 B1              |  | 20-02-2001       |

| US 4488351                             | A  | 18-12-1984       | JP   | 1746637 C               |  | 25-03-1993       |

|                                        |    |                  | JP   | 4034819 B               |  | 09-06-1992       |

|                                        |    |                  | JP   | 59138379 A              |  | 08-08-1984       |

|                                        |    |                  | DE   | 3462969 D1              |  | 07-05-1987       |

|                                        |    |                  | EP   | 0127725 A1              |  | 12-12-1984       |

| US 2003045061                          | A1 | 06-03-2003       | KR   | 2003018795 A            |  | 06-03-2003       |

| US 2002140100                          | A1 | 03-10-2002       | JP   | 2002299281 A            |  | 11-10-2002       |

|                                        |    |                  | US   | 2004104485 A1           |  | 03-06-2004       |