(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5528667号

(P5528667)

(45) 発行日 平成26年6月25日(2014.6.25)

(24) 登録日 平成26年4月25日(2014.4.25)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 21/8234 | (2006.01) | HO1L 27/08 | 102A |

| HO1L 27/088  | (2006.01) | HO1L 27/08 | 102B |

| HO1L 27/08   | (2006.01) | HO1L 27/08 | 331E |

| HO1L 27/12   | (2006.01) | HO1L 27/08 | 331D |

| HO1L 21/02   | (2006.01) | HO1L 27/12 | B    |

請求項の数 6 (全 24 頁) 最終頁に続く

(21) 出願番号

特願2007-307760 (P2007-307760)

(22) 出願日

平成19年11月28日(2007.11.28)

(65) 公開番号

特開2009-135140 (P2009-135140A)

(43) 公開日

平成21年6月18日(2009.6.18)

審査請求日

平成22年8月30日(2010.8.30)

前置審査

(73) 特許権者

302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人

100088672

弁理士 吉竹 英俊

(74) 代理人

100088845

弁理士 有田 貴弘

(72) 発明者

土屋 龍太

東京都千代田区大手町二丁目6番2号 株

式会社ルネサステクノロジ内

(72) 発明者

岩松 俊明

東京都千代田区大手町二丁目6番2号 株

式会社ルネサステクノロジ内

審査官 安田 雅彦

最終頁に続く

(54) 【発明の名称】半導体装置および半導体装置の制御方法

(57) 【特許請求の範囲】

【請求項 1】

半導体支持基板と、

前記半導体支持基板上に形成される、厚さ10nm以下の絶縁膜と、

前記絶縁膜上に形成される半導体層と、

前記半導体層の上面内に配置され、第2導電型の第一のソース・ドレイン領域と第一のゲート電極を有する第一の電界効果型トランジスタと、

前記半導体層の上面内に配置され、前記半導体層の表面内に配置された素子分離膜により前記第一の電界効果型トランジスタと電気的に絶縁されており、第2導電型の第二のソース・ドレイン領域と第二のゲート電極を有する第二の電界効果型トランジスタとを、備えており、

前記第一のゲート電極下方において、前記半導体支持基板には、

第1導電型の前記半導体支持基板に第2導電型の第1不純物領域が配置され、前記第1不純物領域内に第1導電型の第2不純物領域が配置され、

前記第一のゲート電極の直下で前記第2不純物領域と前記絶縁膜の間に第1導電型の第3不純物領域が配置され、

前記第二のゲート電極下方において、前記半導体支持基板には、

第1導電型の前記半導体支持基板に第2導電型の第4不純物領域が配置され、前記第4不純物領域内に第1導電型の第5不純物領域が配置され、

前記第二のゲート電極の直下で前記第5不純物領域と前記絶縁膜の間に第1導電型の第

10

20

## 6 不純物領域が配置され、

前記第一のソース・ドレイン領域の直下で前記第2不純物領域と前記絶縁膜の間に第2導電型の第7不純物領域が配置されており、

前記第6不純物領域の不純物濃度は、前記第3不純物領域の不純物濃度よりも、低く、前記第一の電界効果型トランジスタは、ロジック回路を構成し、前記第二の電界効果型トランジスタは、メモリ回路を構成する、ことを特徴とする半導体装置。

## 【請求項2】

10

前記第一のゲート電極の両脇における前記半導体層の表面内に前記第一のソース・ドレイン領域は配置されており、

平面視において、前記第一のソース・ドレイン領域の前記第一のゲート電極形成側の端部は、

前記第一のゲート電極の端部と一致しているか、または前記第一のゲート電極の前記端部と前記第一のゲート電極非形成側に所定の距離だけ隔てて配置されている、ことを特徴とする請求項1に記載の半導体装置。

## 【請求項3】

前記第一のソース・ドレイン領域の前記第一のゲート電極形成側の前記端部と、前記第一のゲート電極の前記端部との平面視における間隔は、

20

0以上、2nm以下である、

ことを特徴とする請求項2に記載の半導体装置。

## 【請求項4】

前記第二のゲート電極の両脇における前記半導体層の表面内に前記第二のソース・ドレイン領域は配置されており、

平面視において、前記第二のソース・ドレイン領域の前記第二のゲート電極形成側の端部は、

前記第二のゲート電極の端部と一致しているか、または前記第二のゲート電極の前記端部と前記第二のゲート電極非形成側に所定の距離だけ隔てて配置されている、ことを特徴とする請求項1に記載の半導体装置。

30

## 【請求項5】

前記第二のソース・ドレイン領域の前記第二のゲート電極形成側の端部と、前記第二のゲート電極の前記端部との平面視における間隔は、

0以上、2nm以下である、

ことを特徴とする請求項4に記載の半導体装置。

## 【請求項6】

半導体支持基板と、前記半導体支持基板上に配置される、厚さ10nm以下の絶縁膜と、前記絶縁膜上に形成される半導体層と、前記半導体層の上面内に配置され、第2導電型の第一のソース・ドレイン領域と第一のゲート電極を有し、ロジック回路を構成する第一の電界効果型トランジスタと、前記半導体層の上面内に配置され、前記半導体層の表面内に形成された素子分離膜により前記第一の電界効果型トランジスタと電気的に絶縁されており、第2導電型の第二のソース・ドレイン領域と第二のゲート電極を有し、メモリ回路を構成する第二の電界効果型トランジスタとを、備えており、前記第一のゲート電極下方において、前記半導体支持基板には、第1導電型の前記半導体支持基板に第2導電型の第1不純物領域が配置され、前記第1不純物領域内に第1導電型の第2不純物領域が配置され、前記第一のゲート電極の直下で前記第2不純物領域と前記絶縁膜の間に第1導電型の第3不純物領域が配置され、前記第二のゲート電極下方において、前記半導体支持基板には、第1導電型の前記半導体支持基板に第2導電型の第4不純物領域が配置され、前記第4不純物領域内に第1導電型の第5不純物領域が配置され、前記第二のゲート電極の直下で前記第5不純物領域と前記絶縁膜の間に第1導電型の第6不純物領域が配置され、前記

40

50

第一のソース・ドレイン領域の直下で前記第2不純物領域と前記絶縁膜の間に第2導電型の第7不純物領域が配置されており、前記第6不純物領域の不純物濃度は、前記第3不純物領域の不純物濃度よりも、低い、半導体装置の制御方法であって、

前記第一のゲート電極の下方の前記第2不純物領域に、前記第一の電界効果型トランジスタの順方向バイアスを印加し、

前記第二のゲート電極の下方の前記第5不純物領域に、前記第二の電界効果型トランジスタの逆方向のバイアスを印加する、

ことを特徴とする半導体装置の制御方法。

【発明の詳細な説明】

【技術分野】

10

【0001】

この発明は、半導体装置および半導体装置の制御方法に係る発明であり、たとえば、SOI構造を有する半導体装置および、その制御方法に適用することができる。

【背景技術】

【0002】

SOI (Silicon On Insulating) デバイスは、低消費電力、高速動作やラッチアップフリーなどの多くの優れた特性を有する。特に、BOX (Buried Oxide) 層を 10 nm 程度まで薄膜化した薄膜 BOX - SOI デバイスでは、プレーナ型のダブルゲートとなる。したがって、SOI 層の不純物濃度を低く保ったままで、短チャネル化することができ、65 nm 世代以降で顕在化してきた不純物揺らぎに起因したしきい値電圧のバラツキを小さくできるという利点を有する。当該 BOX - SOI デバイスに関する先行技術文献として、たとえば特許文献 1 および非特許文献 1 などが存在する。

20

【0003】

ここで、しきい値電圧バラツキと SRAM (Static Random Access Memory) 動作安定性との関係について述べる。しきい値電圧のバラツキが 20 mV では、動作マージンに余裕がある。しかしながら、しきい値電圧のバラツキが 40 mV 存在する場合には、動作マージンはほぼ消失する。65 nm 世代以降のトランジスタにおいて、従来バルクトランジスタを使用した場合、しきい値電圧のバラツキを 40 mV 以下にすることは難しい。したがって、SRAM の安定動作の維持は困難となる。

30

【0004】

薄膜 BOX - SOI デバイスでは、しきい値電圧のバラツキを低減できるだけでなく、膜厚 10 nm 程度の薄膜 BOX 層を採用しているため、バックバイアス印加により、トランジスタ特性を制御できるという特徴を併せ持つ。バックバイアスにて、トランジスタのしきい値電圧をはじめとした諸特性を制御できることは、上記非特許文献 1 にて示されている。また、非特許文献 1 には、SOI 構造を採用しているため、フォワード・バイアスを印加しても接合リーキ電流が流れず、結果として、従来バルクデバイスに比べ、非常に広範囲にバックバイアスを印加できることも、同時に示されている。

【0005】

【特許文献 1】特開 2005 - 251776 号公報

40

【非特許文献 1】R. Tsuchiya et al. "Silicon on Thin BOX: A New Paradigm of The CMOSFET for Low-Power and High-Performance Application Featuring Wide-Range Back-Bias Control", IEDM Tech., 2004, pp 631

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかし、半導体デバイスに、ロジック回路と SRAM メモリセルとを形成する場合において、上記バックバイアスを具体的にどのように印加してデバイスを動作させる方が良い

50

のかについては、明確には示されていなかった。つまり、非特許文献1では、薄膜B O X - S O I構造で、同一半導体基板にロジック回路とS R A Mとが形成されている半導体装置、およびバックバイアスに関する事項は、開示されている。しかしながら、非特許文献1では、ロジック回路の高速動作とS R A Mの安定動作とを両立させることができると、半導体装置、および当該半導体装置の制御方法について何も言及されていない。

【0007】

そこで、本発明は、薄膜B O X - S O I構造で、同一半導体基板にロジック回路とメモリ回路とが形成されている半導体装置において、ロジック回路の高速動作およびメモリ回路の安定動作を両立させることができる半導体装置および、その制御方法を提供することを目的とする。

10

【課題を解決するための手段】

【0008】

本発明に係る1の実施の形態においては、半導体装置は、薄膜絶縁膜を有するS O I構造を有している。そして、半導体装置には、ロジック回路を構成する第一のゲート電極を有するトランジスタと、メモリ回路を構成する第二のゲート電極を有するトランジスタと、を備えている。少なくとも第一のゲート電極下方において、半導体支持基板には、トリプルウェルが形成されている。

【発明の効果】

【0009】

上記1の実施例により、ロジック回路を構成するトランジスタに印加させるバックバイアスと、メモリ回路を構成するトランジスタに印加させるバックバイアスとを、異なる極性とすることができます。したがって、前者のバックバイアスとして順方向のバイアスを印加し、後者のバックバイアスとして逆方向のバイアスを印加することができる。当該バックバイアスの印加により、ロジック回路の高速化とメモリ回路の動作安定性とを両立させることができる。

20

【発明を実施するための最良の形態】

【0010】

本発明は、本発明者らが、下記新現象が生じることを見出した結果に基づく。その結果について以下に示す。

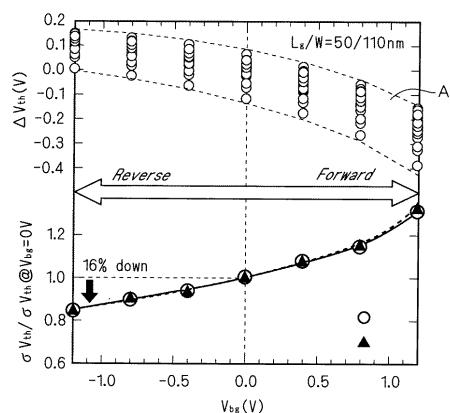

【0011】

30

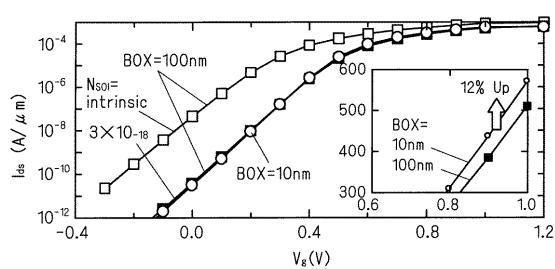

図1に、トランジスタのしきい値電圧のバラツキのバックバイアス依存性を示す。しきい値電圧のバラツキは、バックバイアス依存性を示すが、従来のバルクデバイスの場合、バック・バイアスに逆方向バイアスを印加すると、しきい値電圧のバラツキが増加することが分かっている。

【0012】

しかし、薄膜B O X - S O Iデバイスの場合、バックバイアスとして逆方向バイアスを印加する。すると、図1の領域Aに示す通り、しきい値電圧のバラツキはむしろ低減することを見出した（領域Aの縦幅が、逆方向バイアスの値が大きくなるほど狭くなっている）。

【0013】

40

従来のバルクデバイスの場合、基板バイアスを印加すると、この基板バイアスが直接チャネル下部の空乏層幅の変動に影響を与える。したがって、バックバイアスとして逆方向バイアスを印加すると、チャネル下部の空乏層は増大し、結果として、空乏層幅はバックバイアスを印加しないときよりも広がる。つまり、チャネル下方深くまで空乏層幅は、広がることになる。したがって、従来のバルクデバイスの場合には、この空乏層幅の増大とともに、この空乏層幅内に含まれる不純物数も増大するため、結果として、不純物電荷量のばらつきが増大する。

【0014】

一方、従来のバルクデバイスにおいて、バックバイアスとして逆方向バイアスを印加すると、急峻なサブスレッショルド係数が得られるようになる。このため、プロセスバラツ

50

キに起因したしきい値電圧のバラツキは、低減させることができる。

【0015】

しかし、従来のバルクデバイスの場合には、このプロセスバラツキに起因したしきい値電圧のバラツキの低減効果よりも、不純物電荷ばらつきに起因したしきい値電圧のバラツキ増大の寄与の方が大きくなる。このため、結果として、バックバイアスとして逆方向バイアスを印加すると、しきい値電圧のバラツキは増大すると考えられる。

【0016】

ところが、薄膜BOX-SOIの場合には、完全空乏型のSOI構造を採用している。このため、チャネル下部の空乏層がSOI/BOX層まで広がった状態で、デバイスは動作する。したがって、バックバイアスとして逆方向バイアスを印加した場合には、空乏層幅の変動量は、上記バルクデバイスに比べて小さく、不純物電荷量のバラツキも小さくなる。

10

【0017】

したがって、不純物電荷ばらつきに起因したしきい値電圧のバラツキ増大の寄与は小さく、プロセスバラツキに起因したしきい値電圧のバラツキの低減効果が大きくなる。このため、薄膜BOX-SOIでは、バックバイアスとして逆方向バイアスを印加すると、しきい値電圧のバラツキは、低減すると考えられる。なお、薄膜BOX-SOIで、バックバイアスとして逆方向バイアスを印加する。すると、図1中の下方に示した通り、バックバイアスがゼロである場合と比較して、バックバイアスが-1.2Vである場合の方が、しきい値電圧のバラツキを、約16%低減できることを確認した。

20

【0018】

本発明は、上記現象を元に、上記発明が解決しようとする課題に鑑みてなされたものである。以下、この発明をその実施の形態を示す図面に基づいて具体的に説明する。

【0019】

<実施の形態1>

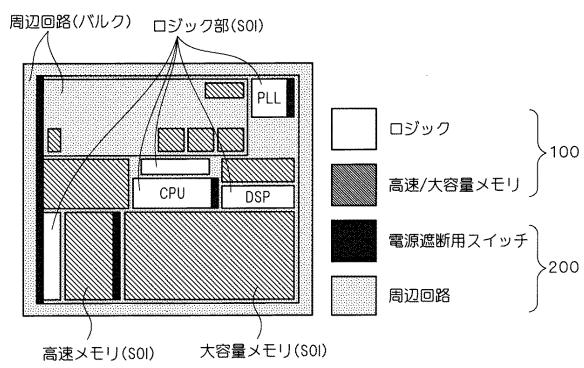

半導体装置のフロアプラン例を図2に示す。高い素子性能が要求されるロジック回路および、高速/大容量メモリ回路をSOI型MISFET (Metal Insulator Semiconductor Field Effect Transistor) 100で作製する。他方、高耐圧系の素子が必要となる電源遮断用スイッチや周辺回路にバルク型MISFET200を作製する。これにより、図2に示す、高性能なシステムLSI (Large Scale Integration) の作製が可能になる。

30

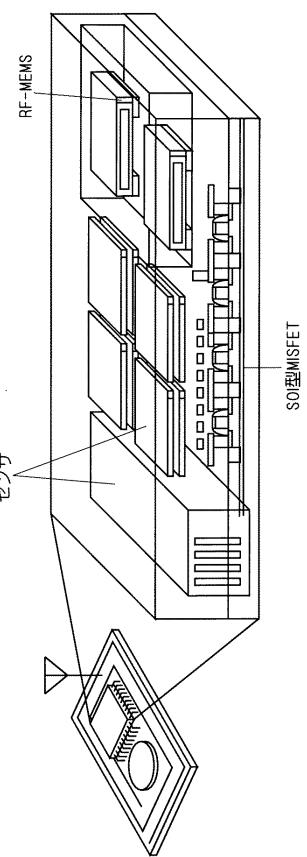

【0020】

また、図3にMEMS (Micro Electro Mechanical Systems)との混載例を示す。高速処理が必要なLSIをSOI型MISFETで作製し、RF (Radio Frequency) モジュールやセンサなどのMEMSをバルク領域に形成する。これにより、高性能MEMS混載集積回路を安価に提供することができる。

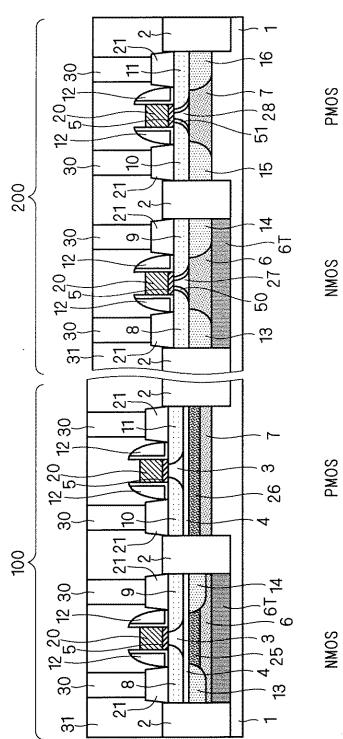

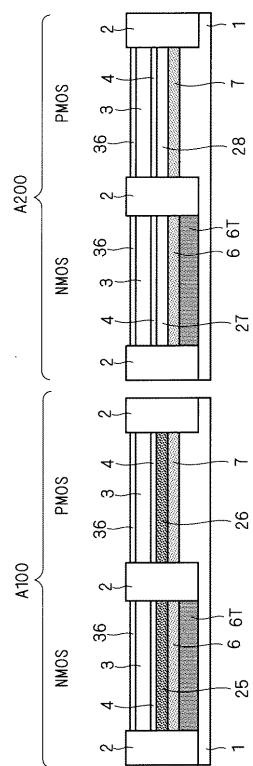

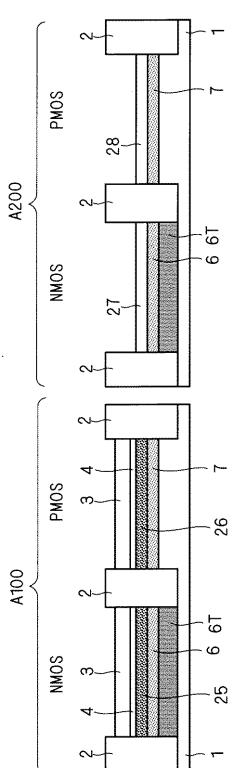

【0021】

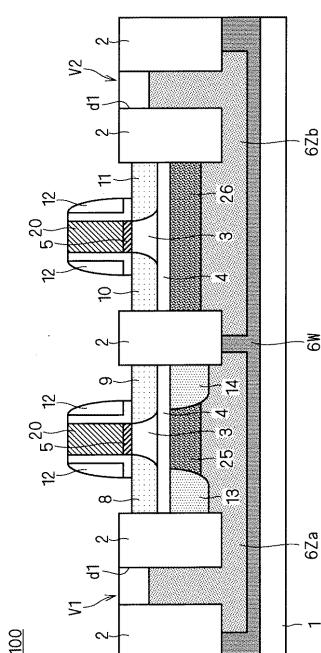

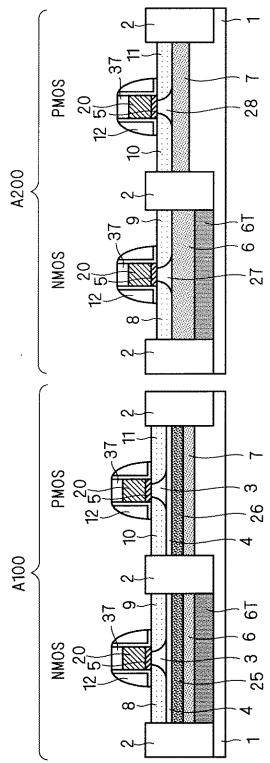

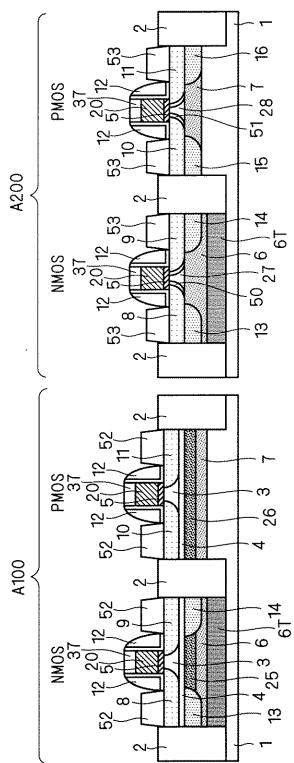

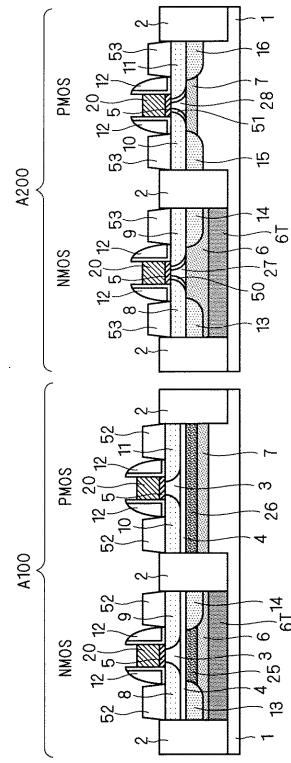

図4は、SOI型MISFET100およびバルク型MISFET200の構成を示す断面図である。ここで、図4において、SOI型MISFET100の左側がNMOSであり、SOI型MISFET100の右側がPMOSである。また、バルク型MISFET200の左側がNMOSであり、バルク型MISFET200の右側がPMOSである。なお、図5に示すように、SOI型MISFET100である両方のトランジスタが、同じ導電型のトランジスタであっても良い。図4において、絶縁膜31内に形成されているプラグ30は、シリサイド膜21を介してソース・ドレイン領域8~11に接続されている。当該シリサイド膜21により、プラグ30とソース・ドレイン領域8~11とのコンタクト抵抗を低減させることができる。図5において、V1は、順方向のバックバイアスである。V2は、逆方向のバックバイアスである。

40

【0022】

次に、本実施の形態に係るSOI型MISFET100の主要部の構成について説明す

50

る。

【0023】

図4, 5に示すように、SOI型MISFET100は、半導体支持基板1、絶縁膜4、および半導体層3を有する。ここで、半導体支持基板1上に形成される絶縁膜4の膜厚は、10nm以下である。なお、半導体層3は、絶縁膜(BOX層)4上に形成されている。

【0024】

また、図4, 5に示すSOI型MISFET100の左側のトランジスタ(第一の電界効果型トランジスタと把握できる)は、半導体層3の上面内に形成されており、ロジック回路を構成する。当該第一の電界効果型トランジスタは、半導体層3の表面内に形成されるソース・ドレイン領域8, 9と、半導体層3上に形成されるゲート構造とを備えている。ここで、当該ゲート構造は、半導体層3上に形成されるゲート絶縁膜5と、当該ゲート絶縁膜5上に形成されるゲート電極(第一のゲート電極と把握できる)20とから成る。また、当該ゲート構造の両側面には、サイドウォール膜12が形成されている。また、ソース・ドレイン領域8, 9は、第一のゲート電極20の両脇における半導体層3の表面内に形成されている。

【0025】

また、図4, 5に示すSOI型MISFET100の右側のトランジスタ(第二の電界効果型トランジスタと把握できる)は、半導体層3の上面内に形成されており、メモリ回路を構成する。当該第二の電界効果型トランジスタは、半導体層3の表面内に形成されるソース・ドレイン領域10, 11と、半導体層3上に形成されるゲート構造とを備えている。ここで、当該ゲート構造は、半導体層3上に形成されるゲート絶縁膜5と、当該ゲート絶縁膜5上に形成されるゲート電極(第二のゲート電極と把握できる)20とから成る。また、当該ゲート構造の両側面には、サイドウォール膜12が形成されている。なお、上記第一の電界効果型トランジスタと上記第二の電界効果型トランジスタとは、素子分離膜2により、電気的に絶縁されている。また、ソース・ドレイン領域10, 11は、第二のゲート電極20の両脇における半導体層3の表面内に形成されている。

【0026】

ここで、上記第一のゲート電極下方および上記第二のゲート電極下方における、半導体層3(すなわち、チャネル領域)の不純物濃度は、 $1 \times 10^{16} / \text{cm}^3$ 程度である。

【0027】

また、図4, 5のSOI型MISFET100の半導体支持基板1に注目する。図4に示す構成では、上記第一のゲート電極20下方において、半導体支持基板1には、トリプルウェルが形成されている。他方、図5に示す構成では、上記第一のゲート電極20下方および上記第二のゲート電極20下方において、半導体支持基板1には、トリプルウェルが形成されている。ここで、トリプルウェルは、第1導電型の半導体支持基板1に第2導電型の第1ウェルを形成し、当該第1ウェル内に第1導電型の第2ウェルを形成することにより、構成(作成)される。

【0028】

たとえば、図4に示すSOI型MISFET100では、第一のゲート電極20の下方のP型の半導体支持基板1には、N型ウェル領域6TとP型ウェル領域6とが下方向から当該順に形成されている。他方、第二のゲート電極20の下方のP型の半導体支持基板1には、N型ウェル領域7が形成されている。図4に示すように、各ウェル6, 6T, 7の形成により(トリプルウェルの形成により)、第一のゲート電極20の下方の半導体支持基板1の領域と第二のゲート電極20の下方の半導体支持基板1の領域とを電気的に分離することができる。

【0029】

また、図5に示すSOI型MISFET100では、第一のゲート電極20の下方のP型の半導体支持基板1および第二のゲート電極20の下方のP型の半導体支持基板1には、N型ウェル領域6WとP型ウェル領域6Za, 6Zbとが下方向から当該順に形成され

10

20

30

40

50

ている。ここで、ウェル領域 6 Z a とウェル領域 6 Z b とは、図 5 に示すように電気的に分離されている。したがって、図 5 に示すように、各ウェル 6 W, 6 Z a, 6 Z b の形成により（トリプルウェルの形成により）、第一のゲート電極 2 0 の下方の半導体支持基板 1 の領域と第二のゲート電極の下方の半導体支持基板 1 の領域とを電気的に分離することができる。

【0030】

なお、図 5 において、素子分離膜 2 を介して、ウェル領域 6 Z a には、第一の電界効果型トランジスタの順方向バイアスが、バックバイアスとして印加される。他方、図 5 において、ウェル領域 6 Z b には、第二の電界効果型トランジスタの逆方向バイアスが、バックバイアスとして印加される。

10

【0031】

また、図 4 では具体的には図示されていないが、ウェル領域 6 には、第一の電界効果型トランジスタの順方向バイアスが、バックバイアスとして印加される。他方、ウェル領域 7 には、第二の電界効果型トランジスタの逆方向バイアスが、バックバイアスとして印加される。

【0032】

また、図 4 の S O I 型 M I S F E T 1 0 0 において、上記第一のゲート電極 2 0 の下方の半導体支持基板 1 に注目する。すると、半導体支持基板 1 には、ソース・ドレイン領域 8, 9 の下方における半導体支持基板 1 の表面内に形成される、ウェル領域 6 の導電型と異なる導電型を有する不純物領域 1 3, 1 4 が形成されている。また、図 5 の S O I 型 M I S F E T 1 0 0 において、上記第一のゲート電極 2 0 の下方の半導体支持基板 1 に注目する。すると、半導体支持基板 1 には、ソース・ドレイン領域 8, 9 の下方における半導体支持基板 1 の表面内に形成される、ウェル領域 6 Z a の導電型と異なる導電型を有する不純物領域 1 3, 1 4 が形成されている。

20

【0033】

ここで、上記各不純物領域 1 3, 1 4 の不純物濃度は、 $1 \times 10^{18} / \text{cm}^3$  程度である。

【0034】

また、図 4 の S O I 型 M I S F E T 1 0 0 において、上記第一のゲート電極 2 0 の下方に位置する、半導体支持基板 1 の表面内には、第一の電界効果型トランジスタのしきい値電圧調整のための不純物領域 2 5 が形成されている。上記第二のゲート電極 2 0 の下方に位置する、半導体支持基板 1 の表面内には、第二の電界効果型トランジスタのしきい値電圧調整のための不純物領域 2 6 が形成されている。ここで、不純物領域 2 5 の導電型は、ウェル領域 6 の導電型と同じである。また、不純物領域 2 6 の導電型は、ウェル領域 7 の導電型と同じである。ただし、不純物領域 2 6 の不純物濃度は、不純物領域 2 5 の不純物濃度よりも低い。

30

【0035】

また、図 5 の S O I 型 M I S F E T 1 0 0 において、上記第一のゲート電極 2 0 の下方に位置する、半導体支持基板 1 の表面内には、第一の電界効果型トランジスタのしきい値電圧調整のための不純物領域 2 5 が形成されている。上記第二のゲート電極 2 0 の下方に位置する、半導体支持基板 1 の表面内には、第二の電界効果型トランジスタのしきい値電圧調整のための不純物領域 2 6 が形成されている。ここで、不純物領域 2 5 の導電型は、ウェル領域 6 Z a の導電型と同じである。また、不純物領域 2 6 の導電型は、ウェル領域 6 Z b の導電型と同じである。ただし、不純物領域 2 6 の不純物濃度は、不純物領域 2 5 の不純物濃度よりも低い。

40

【0036】

たとえば、ここで、上記不純物領域 2 5 の不純物濃度は、 $1 \times 10^{18} / \text{cm}^3$  程度であり、上記不純物領域 2 6 の不純物濃度は、 $1 \times 10^{17} / \text{cm}^3$  程度である。

【0037】

次に、図 5 の構成の製造方法を簡単に説明する。

50

## 【0038】

図5において、従来の方法により、素子分離膜2の形成、ウェル形成6W, 6Za, 6Zbを行う。ここで、各トランジスタには異なる極性のバックバイアスを印加して、デバイスを動作させる。このため、上記ウェル形成の際には、各ゲート電極20の下方の半導体支持基板1には、上述したトリプルウェルを形成する。こうすることで、ウェル領域6Za, 6Zb同士が電気的に分離されるので、各トランジスタに上記異なる極性のバックバイアスを印加できる。さらに、トリプルウェル構造側において、順方向バイアスを印加したとしても、半導体支持基板1内において、リーク電流が流れなくなる。

## 【0039】

続いて、しきい値電圧調整用のイオン注入を行う（不純物領域25, 26形成のためのイオン注入）。この際、第一の電界効果型トランジスタ側では、当該第一の電界効果型トランジスタのしきい値電圧がターゲットのしきい値電圧となるように、所望の不純物濃度で前記イオン注入を行う。他方、第二の電界効果型トランジスタ側では、前記所望の不純物濃度よりも低濃度の不純物濃度で前記イオン注入を行う。これにより、当該第二の電界効果型トランジスタにバックバイアスとして逆方向バイアスを印加した状態において、当該第二の電界効果型トランジスタのしきい値電圧は、高くなる。

10

## 【0040】

なお、上記のように、不純物領域26の不純物濃度は、より低濃度である。このため、第二の電界効果型トランジスタ側において、当該不純物濃度に起因したしきい値電圧のバラツキ増大をより抑制できる。

20

## 【0041】

続いて、ゲート構造5, 20の形成、エクステンションイオン注入、サイドウォール膜12形成を行う。サイドウォール膜12を形成した後、選択エピタキシャル成長を利用して、拡散層領域にシリコンを選択エピタキシャル成長させる。しかる後に、ソース・ドレイン領域8, 9, 10, 11の形成を行う。その際、第一の電界効果型トランジスタの形成領域のみ、接合容量低減のための絶縁膜4より下層へ不純物の導入を行う。つまり、図5に示したように、第一の電界効果型トランジスタを構成する電極利用域8, 9の下方における半導体支持基板1の表面内に、不純物領域13, 14を形成する。

## 【0042】

当該不純物領域13, 14の形成は、絶縁膜4より下層に導入された不純物の低濃度化が目的である。このため、上記不純物領域25の不純物濃度と同等の不純物濃度での、不純物領域13, 14形成のためのイオン注入が実施される。ここで、上記のとおり、不純物領域25の不純物の導電型と不純物領域13, 14の不純物の導電型とは、相違する。このように、絶縁膜4より下層へ所定の導電型の不純物導入を行うことにより、上述したように、接合容量の低減を行う。

30

## 【0043】

なお、当該不純物導入は、ゲート構造およびサイドウォール膜12をマスクとして使用し、不純物の導入深さを調整して実施する。このように、ソース・ドレイン領域形成のためのイオン注入後に、連続して接合容量低減のための不純物導入を行うことができる。したがって、当該接合容量低減のための不純物導入工程の追加に伴う、マスク増大は発生しない。しかる後は、従来半導体デバイスの製造フローを実施し、半導体素子を完成させる。

40

## 【0044】

次に、図4に示す構造の製造方法を、工程断面図を用いて具体的に説明する。

## 【0045】

面方位(100)、P導電型、抵抗率100hm·cm、直径20cmの単結晶Siよりなり、主表面が鏡面研磨された半導体基板を用意する。そして、当該半導体基板上に10nm厚のシリコン熱酸化膜を形成する。その後、シリコン熱酸化膜が形成された半導体基板に対して、公知の超薄膜SOI基板の製造法に基づき水素のイオン注入を実施した。注入量は $5 \times 10^{16} / \text{cm}^2$ とした。当該イオン注入の結果、単結晶Si基板主表面から

50

およそ 40 nm の深さに、結晶欠陥層が形成される。この状態より表面にシリコン酸化膜を有しない第一の半導体基板と同一仕様の第二の半導体基板の各々に親水化処理を施した後、室温で主表面同士を密着させる。

#### 【0046】

次に、密着させた二枚の Si 基板を 500 に加熱する。この熱処理により結晶欠陥層に微小空孔の形成とその増大化が生じ、結晶欠陥層部分で単結晶 Si 基板が剥離される。これにより、半導体支持基板 1 上に、10 nm 厚のシリコン熱酸化膜（絶縁膜）4 が密着し、当該絶縁膜 4 上に、約 20 nm 厚の単結晶 Si 薄膜（半導体層）3 が密着する。この状態より 1100 の高温熱処理を施す。これにより、絶縁膜 4 と半導体支持基板 1 との接着強度が格段に向上し、通常の単結晶基板並みの接着強度となる。

10

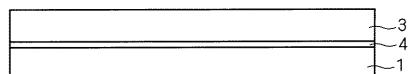

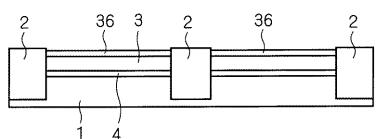

#### 【0047】

この状態より、半導体層 3 の表面、すなわち剥離面、を砥粒を含まない表面研磨法により鏡面研磨する。これにより、図 6 に示す SOI 基板が用意できる。図 6 から分かるように、半導体支持基板 1、絶縁膜 4 および半導体層 3 が下から当該順に積層されることにより、SOI 基板は構成される。ここで、当該絶縁膜（BOX 層）4 の膜厚は、10 nm 以下の薄膜である。また、半導体支持基板 1 は、N 型の導電型を有している。

#### 【0048】

なお、図 6 に示す SOI 基板は、同様な仕様の市販のものを購入しても良い。この場合には、SOI 基板上にシリコン酸化膜を形成した後、シリコン酸化膜を除去することで、所望の単結晶 Si 層になるまで、Si 層を薄層化して使用する。また、ELO (E pit axial Lateral Overgrowth) や SPE (Solid Phase Epitaxy) 等のエピタキシャル薄膜成長技術を用い、バブル基板上に SOI 構造を作製する手法も採用できる。

20

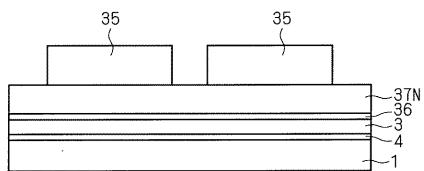

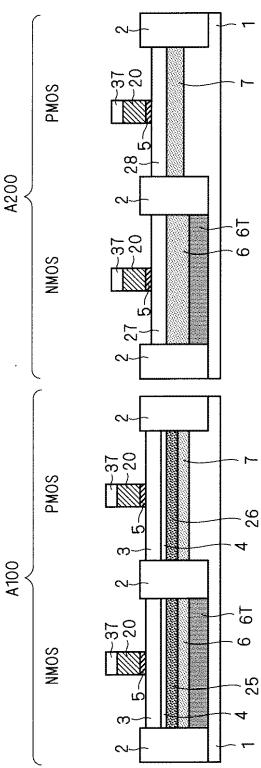

#### 【0049】

図 6 の構成において、シリコン酸化膜 36 およびシリコン窒化膜 37N を当該順に形成する（図 7）。ここで、形成したシリコン窒化膜 37N は、後の浅溝素子分離形成における化学的機械的研磨での研磨ストッパーとして用いられる。

#### 【0050】

次に、レジストマスク 35 を塗布した後に、所望領域のレジストマスク 35 のみ除去する（図 7）。つまり、後に形成されるトランジスタのアクティブエリア上方にのみ、レジストマスク 35 を残存させる。その後、レジストマスク 35 をマスクとして、所望領域の、シリコン窒化膜 37N、シリコン酸化膜 36、半導体層 3、絶縁膜 4、および半導体支持基板 1 の一部を除去する（図 8）。つまり、図 8 に示すように、素子分離膜 2 形成用のトレンチ T1 が、形成される。

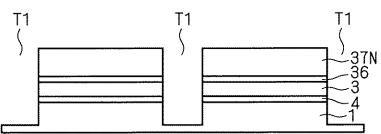

30

#### 【0051】

次に、トレンチ T1 を充填するように、図 8 に示す構造体上に、シリコン酸化膜を形成する。その後、当該シリコン酸化膜およびシリコン窒化膜 37N に対して研磨処理を施す。これにより、図 9 に示すように、トレンチ T1 に素子分離膜 2 が形成されると共に、シリコン窒化膜 37N が除去される。当該素子分離膜 2 により、隣接して形成される各トランジスタは、電気的に分離される。

40

#### 【0052】

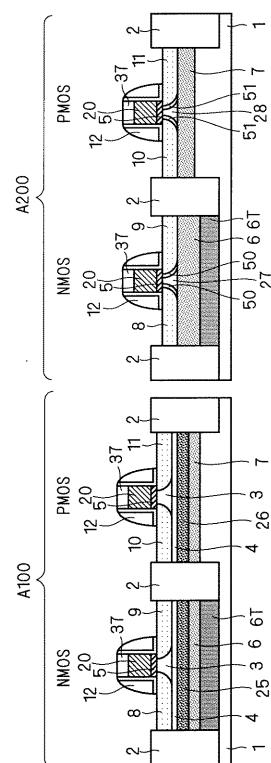

次に、図 9 の構造体の NMOS 形成領域に対して、P 型のウェル領域 6T 形成のためのイオン注入および N 型ウェル領域 6 形成のためのイオン注入を施す。これに対して、図 9 の構造体の PMOS 形成領域に対しては、P 型のウェル領域 7 形成のイオン注入処理を施す。つまり、図 10 に示すように、NMOS 形成領域の半導体支持基板 1 内には、ウェル領域 6, 6T から成るトリプルウェルが形成される。他方、図 10 に示すように、PMOS 形成領域の半導体支持基板 1 内には、ウェル領域 7 のみが形成される。

#### 【0053】

つまり、少なくとも第一のゲート電極 20 下方において、半導体支持基板 1 には、第 1 導電型の前記半導体支持基板に第 2 導電型の第 1 ウェルが形成され、第 1 ウェル内に第 1

50

導電型の第2ウェルが形成された、トリプルウェルが形成される。そして、当該トリプルウェルの形成により、第一のゲート電極20の下方の半導体支持基板1の領域と第二のゲート電極20の下方の半導体支持基板1の領域とを電気的に分離することができる。

【0054】

なお、上記の通り、第一のゲート電極20は、ロジック回路を構成する第一の電界効果型トランジスタ（図4の領域100の左側のトランジスタ）の構成要素ある。また、第二のゲート電極20は、メモリ回路を構成する第二の電界効果型トランジスタ（図4の領域100の右側のトランジスタ）の構成要素ある。

【0055】

次に、図10に示す構造体のSOI型MISFET形成領域A100のNMOS形成領域に、N型の不純物イオンを注入する。これにより、図11に示すように、SOI型MISFET形成領域A100のNMOS形成領域の半導体支持基板1の表面内に、不純物領域25を形成する。当該不純物領域25は、当該NMOSトランジスタ（上記第一の電界効果型トランジスタと把握できる）のしきい値電圧調整のための領域である。また、図10に示す構造体のSOI型MISFET形成領域A100のPMOS形成領域に、P型の不純物イオンを注入する。これにより、図11に示すように、SOI型MISFET形成領域A100のPMOS形成領域の半導体支持基板1の表面内に、不純物領域26を形成する。当該不純物領域26は、当該PMOSトランジスタ（上記第二の電界効果型トランジスタと把握できる）のしきい値電圧調整のための領域である。

【0056】

ここで、上記各不純物イオン注入により、上記第二の電界効果型トランジスタを構成するゲート電極20の下方に位置する半導体支持基板1の表面付近の不純物濃度は、次のようになる。つまり、当該不純物濃度は、上記第一の電界効果型トランジスタを構成するゲート電極20の下方に位置する半導体支持基板1の表面付近の不純物濃度よりも、低くなる。

【0057】

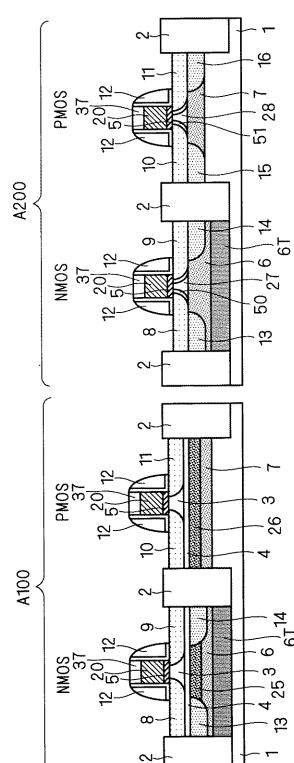

また、図10に示す構造体のバルク型MISFET形成領域A200のNMOS形成領域に、N型の不純物イオンを注入する。これにより、図11に示すように、バルク型MISFET形成領域A200のNMOS形成領域の半導体支持基板1の表面内に、不純物領域27を形成する。当該不純物領域27は、当該NMOSトランジスタのしきい値電圧調整のための領域である。さらに、図10に示す構造体のバルク型MISFET形成領域A200のPMOS形成領域に、P型の不純物イオンを注入する。これにより、図11に示すように、バルク型MISFET形成領域A200のPMOS形成領域の半導体支持基板1の表面内に、不純物領域28を形成する。当該不純物領域28は、当該PMOSトランジスタのしきい値電圧調整のための領域である。

【0058】

ここで、図6～10の工程断面図では、SOI型MISFETの形成領域A100とバルク型MISFETの形成領域A200は、同じフローであるため、共通の工程断面図を用いて説明した。しかし、図11以降では、説明をわかり易くするため、SOI型MISFETの形成領域A100とバルク型MISFETの形成領域A200とを、夫々別々に図示し、説明を行う。

【0059】

次に、バルク型MISFET形成領域A200に形成されている、シリコン酸化膜36、半導体層3および絶縁層4を除去する。また、当該除去処理と同時に、SOI型MISFET形成領域A100に形成されるバックバイアスの給電部（図5の符号d1）に形成されている、シリコン酸化膜36、半導体層3および絶縁層4を除去する。続いて、残存しているシリコン酸化膜36をフッ酸洗浄等により選択除去する。当該工程により、図12に示すように、SOI型MISFETの形成領域A100のアクティブ領域からは、半導体層3の上面が露出する。他方、バルク型MISFETの形成領域A200のアクティブエリアからは、半導体支持基板1が露出する。

10

20

30

40

50

## 【0060】

上記のように、バックバイアス給電部の半導体層3、絶縁層4等の除去処理と、バルク型MISFETの形成領域A200の半導体層3、絶縁層4等の除去処理とを同時に実施することにより、工程の簡略を図ることができる。ここで、バックバイアス給電部形成領域付近の工程断面図は、図示を省略している。

## 【0061】

次に、熱酸化膜1.8nmの形成とその表面をNOガスにより窒化することにより0.2nmの窒化膜を主表面に積層形成し、ゲート絶縁膜5を形成する。続いてゲート絶縁膜5上に、たとえば100nm厚の多結晶Si膜を化学気相堆積法により堆積する。次に、多結晶Si膜上に、主にシリコン窒化膜で構成されるゲート保護膜を堆積する。そして、従来公知のMISFETの製造方法により、ゲート構造5,20とゲート保護膜37のパターニングを行う(図13)。ここで、ゲート構造は、ゲート絶縁膜5と多結晶Siから成るゲート電極20とが当該順に積層された積層体である。

10

## 【0062】

続いて、領域A100, A200のNMOs形成領域に、たとえばAsイオンを注入する。ここで、ソース・ドレイン領域8~11の端部とゲート電極20の端部との距離(Lov)を制御するため、Asイオンを注入する前に、酸化膜をデポ、エッチバックして形成したオフセット・スペーサ12を形成しても良い。また、このとき、スペーサ12はエッチバックを行わず、酸化膜を堆積したままで、形成することもできる。いずれの場合も、堆積する酸化膜の膜厚にて距離(Lov)を制御することができるようになる。これにより、図14に示すように、SOI型MISFET形成領域A100のNMOs形成領域における、半導体層3の表面内に、N型のソース・ドレイン領域8,9が形成される。また、バルク型MISFETの形成領域A200のNMOs形成領域における、半導体支持基板1の表面内に、N型のソース・ドレイン領域8,9が形成される。ここで、各ソース・ドレイン領域8,9は、各NMOs領域に存する各ゲート電極20の両脇に形成される。なお、ゲート電極20の両側面には、二重構造のスペーサ12が形成される。

20

## 【0063】

また、領域A100, A200のPMOS形成領域に、たとえばBF2イオンを注入する。これにより、図14に示すように、SOI型MISFET形成領域A100のPMOS形成領域における、半導体層3の表面内に、P型のソース・ドレイン領域10,11が形成される。また、バルク型MISFETの形成領域A200のPMOS形成領域における、半導体支持基板1の表面内に、P型のソース・ドレイン領域10,11が形成される。ここで、各ソース・ドレイン領域10,11は、各PMOS領域に存する各ゲート電極20の両脇に形成される。

30

## 【0064】

続いて、バルク型MISFET形成領域A200における、NMOs形成領域に、たとえば、B(ホウ素)イオンを注入する。これにより、当該NMOs形成領域に存するゲート電極20の下方付近において、半導体支持基板1の表面内に、ハロー領域50が形成される(図15)。また、バルク型MISFET形成領域A200における、PMOS形成領域に、たとえば、P(リン)イオンを注入する。これにより、当該PMOS形成領域に存するゲート電極20の下方付近において、半導体支持基板1の表面内に、ハロー領域51が形成される(図15)。当該ハロー領域50,51は、バルク型MISFETの短チャネル効果を抑制するために、形成する。ここで、より短チャネル効果の抑制効果を高めるため、ハロー形成条件を、たとえばチルト角20度の斜めイオン注入としても、何ら差し支えない。

40

## 【0065】

次に、図15の構造体上全面に、シリコン酸化膜を形成する。その後、当該シリコン酸化膜に対して、異方性ドライエッティングを施す。これにより、各ゲート電極20側壁部に、各々サイドウォール膜12が形成される(図16)。

## 【0066】

50

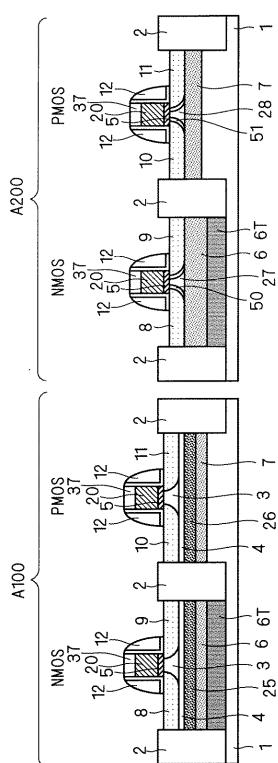

続いて、図16に示す構造体において、SOI型MISFET形成領域A100のNMOS形成領域およびバルク型MISFET形成領域A200にNMOS形成領域に対して、P型の不純物イオン注入を行う。当該不純物イオン注入の際に、サイドウォール膜12が側面に形成されているゲート電極20は、マスクとして機能する。

#### 【0067】

当該不純物イオン注入により、図17に示すように、SOI型MISFET形成領域A100のNMOS形成領域の半導体支持基板1の表面内に、P型の不純物領域13, 14が形成される。なお、ゲート電極20をマスクとした上記不純物イオン注入処理が実施されたので、不純物領域13, 14は、ソース・ドレイン領域8, 9の下方に形成される。なお、不純物領域13, 14の不純物濃度は、ウェル領域6の不純物濃度と同程度であり、不純物領域13, 14の不純物の導電型は、ウェル領域6の不純物の導電型と異なる。

#### 【0068】

また、当該不純物イオン注入により、図17に示すように、バルク型MISFET形成領域A200のNMOS形成領域の半導体支持基板1の表面内に、P型の不純物領域13, 14が形成される。なお、ゲート電極20をマスクとした上記不純物イオン注入処理が実施されたので、不純物領域13, 14は、ソース・ドレイン領域8, 9の直下に形成される。つまり、ソース・ドレイン領域8, 9と不純物領域13, 14とにより、2段構造のソース・ドレイン領域が形成される。ここで、不純物領域13, 14の不純物濃度は、ウェル領域6の不純物濃度と同程度であり、不純物領域13, 14の不純物の導電型は、ウェル領域6の不純物の導電型と異なる。

#### 【0069】

続いて、図16に示す構造体において、バルク型MISFET形成領域A200にPMOS形成領域に対して、N型の不純物イオン注入を行う。当該N型の不純物イオン注入の際に、サイドウォール膜12が側面に形成されているゲート電極20は、マスクとして機能する。

#### 【0070】

当該N型の不純物イオン注入により、図17に示すように、バルク型MISFET形成領域A200のPMOS形成領域の半導体支持基板1の表面内に、N型の不純物領域15, 16が形成される。なお、ゲート電極20をマスクとしたN型の不純物イオン注入処理が実施されたので、不純物領域15, 16は、ソース・ドレイン領域10, 11の直下に形成される。つまり、ソース・ドレイン領域10, 11と不純物領域15, 16とにより、2段構造のソース・ドレイン領域が形成される。なお、不純物領域15, 16の不純物濃度は、ウェル領域7の不純物濃度と同程度であり、不純物領域15, 16の不純物の導電型は、ウェル領域7の不純物の導電型と異なる。

#### 【0071】

ここで、不純物領域13, 14は、SOI型MISFET形成領域A100のNMOSにおける、ソース・ドレイン領域8, 9に起因した容量の低減を目的として形成される。これは、従来公知のバルク型MISFETの接合容量を低減するための方法と、同様の製造方法にて形成されたものである。すなわち、注入素子マスクとするイオン注入により先に注入したしきい値電圧調整用の注入イオンを補償すべき濃度および加速エネルギーで反対導電型のイオンを注入し真性不純物領域に近づける不純物補償領域を形成することが、その目的である。一方、バルク型MISFET形成領域A200側では、不純物領域13, 14は、低抵抗の2段構造ソース・ドレイン領域の形成を目的として形成される。

#### 【0072】

以上のように、SOI型MISFET形成領域A100における寄生容量低減のためのイオン注入工程と、バルク型MISFET形成領域A200におけるソース・ドレイン領域の低抵抗化のためのイオン注入工程とを共通工程・同一条件にて形成することができる。これにより、プロセスを簡略化することができる。

#### 【0073】

その後、工程断面図では、図示しないが、SOI型MISFET形成領域において、バ

10

20

30

40

50

ツクバイアスをウェル領域に印加するための、当該バックバイアスの給電口となる開口部を作成する。

【0074】

次に、選択エピタキシャル法を用いて、露出された単結晶Si領域上にたとえば60nm厚でSi膜52および53を選択的に成長させる。これにより、図18に示すように、SOI型MISFET形成領域A100側では、各ソース・ドレイン領域8～11上に、エピ成長膜52が形成される。また、バルク型MISFET形成領域A200側では、各ソース・ドレイン領域8～11上に、エピ成長膜53が形成される。なお、当該エピタキシャル法により、上記給電部である開口部の底面部に、エピ成長膜を同時に形成しても良い。

10

【0075】

次に、ゲート保護膜37が除去された図18に示す構造において、バルク型MISFET形成領域A200側のみに、スパッタ法により30nm厚のNi(ニッケル)膜を形成する。その後熱処理を施すことにより、シリサイド化処理を実施する。これにより、図19に示すように、バルク型MISFET形成領域A200の各ゲート電極20および各エピ成長膜53のみが、シリサイド化される。上記シリサイド化後、未反応のNi膜のみを塩酸と過酸化水素水の混合水溶液により選択的にエッティング液で除去する。

【0076】

その後、配線層間絶縁膜の堆積と平坦化研磨、および配線層間絶縁膜31を含む配線工程等を実施する。以上により、図4に示す構成を含む半導体装置が完成する。

20

【0077】

図4,5に示す構成において、ロジック部に対してバックバイアスとして順方向バイアスを印加し、メモリ部に対してバックバイアスとして逆方向バイアスを印加する。

【0078】

したがって、ロジック部では、トランジスタにおいて発生する接合容量が低減でき、メモリ部では、トランジスタのしきい値調整用の不純物領域26の低濃度化が可能となる。よって、上記各バックバイアスを印加させて半導体装置を動作させることにより、ロジック部では高速動作が可能となり、メモリ部では安定動作が可能となる。

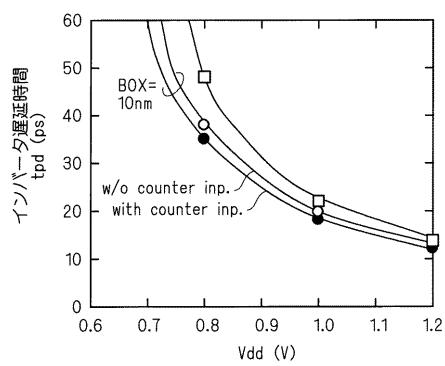

【0079】

次に、シミュレーション結果等を用いて、本実施の形態に係る半導体装置の効果を説明する。図20は、不純物領域13,14の形成に伴う、インバータ遅延における寄生容量低減効果(高速動作効果)を示す図である。図20の横軸は、第一の電界効果型トランジスタのゲート電圧(V)であり、横軸は当該トランジスタの動作速度(ps)を示す。なお、「w/o counter in p.」は、絶縁層4が10nmである図4,5に示す構成において、不純物領域13,14を形成しない場合(以下、単に不純物領域無し構造と称する)の計算結果である。また、「with counter in p.」は、不純物領域13,14を有する図4,5に示す構成(以下、単に不純物領域有り構造と称する)における計算結果である。また、他の一の曲線データは、絶縁層4が数100nm以上の膜厚である場合の通常のSOI構造(以下、単に従来構造と称する)における計算結果である。

30

【0080】

図20から分かるように、不純物領域13,14を有する図4,5に示す構成を採用することにより、ロジック回路を構成する第一の電界効果型トランジスタの動作速度を高速化させることができる。たとえば、不純物領域有り構造の動作速度は、不純物領域無し構造の動作速度よりも、約10%程度早くなる。つまり、不純物領域有り構造の方が、不純物領域無し構造と比較して、インバータ遅延は約10%低減できる。

40

【0081】

このように、本実施の形態に係る半導体装置において、第一の電界効果型トランジスタの動作速度が高速化されるのは、次の理由によると考えられる。ここで、トランジスタの動作速度は、寄生容量Cjが大きくなると遅くなり、トランジスタ駆動電流IdSが大き

50

くなると速くなる。

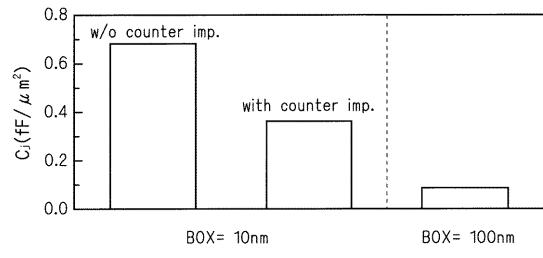

【0082】

図21に示すように、トランジスタ内で発生する寄生容量は、従来構造が最も小さく、次に、不純物領域有り構造が小さくなる。そして、図21に示すように、不純物領域無し構造の場合の寄生容量が最も大きい。これにより、不純物領域有り構造の方が、不純物領域無し構造よりも、インバータ遅延を削減できることが分かる。しかし、図21のデータからでは、図20の結果、つまり、不純物領域有り構造の方が、従来構造よりもインバータ遅延が削減できることは、説明できない。以下、このことについて説明する。

【0083】

従来構造では、トランジスタを微細化した際に発生する短チャネル効果の抑制が難しく、半導体層3内の不純物を高濃度化しなければならない。ところが、発明者らの検討結果によれば、従来構造を適用した場合、半導体層3内の不純物を低濃度（図22のNo i = i n t r i n c tのデータ）にすると、短チャネル効果によりオフリード電流が大幅に増大してしまう。よって、チャネル低電力用と向けトランジスタ（L S T P : L O W S t a n d - b y P o w e r）のオフリード電流（ $\sim 10^{-11} A / \mu m$ ）を実現するためには、半導体層3の不純物濃度を $10^{18} c m^{-3}$ 以上に高濃度化しなければならなくなる。

10

【0084】

そこで、従来構造および絶縁膜4の厚さが $10 nm$ 程度の薄膜B O X構造において、共に、半導体層3の不純物濃度を $3 \times 10^{18} c m^{-3}$ とする。この場合の、ゲート電圧Vdに対するトランジスタ駆動電流Id sの計算結果を図22に示す。図22の丸印の拡大図をみると、薄膜B O X構造の方が、従来構造と比較して、トランジスタ駆動電流Id sが12%増加していることが分かる。

20

【0085】

さらに、薄膜B O X構造では、ダブルゲート構造の採用により、短チャネル特性に優れるため、半導体層3の不純物を低濃度化しても、L S T P向けのオフリード電流を実現できる。従来構造を採用するS O I構造では、この半導体層3内の不純物高濃度化により、移動度が劣化し、トランジスタ駆動電流が、薄膜B O X構造を採用するS O I構造よりも低下することになる（図22）。

【0086】

上記の通り、インバータ遅延は、（寄生容量 / トランジスタ駆動電流）、に比例する。従来構造では、接合容量が低減する効果よりも、トランジスタ駆動電流が劣化する効果の寄与が大きくなる。このため、結果として、従来構造のインバータ遅延は、薄膜B O X構造（たとえば、上記不純物領域有り構造）を採用した場合よりも遅くなる。

30

【0087】

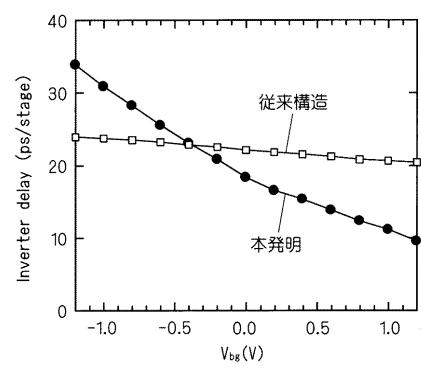

また、図4, 5に示した半導体装置では、上述した如く、接合リード電流を増加させることなく、バック・バイアスを印加して、トランジスタをさらに高駆動能力化することもできる。その効果を図23に示す。図23に示した通り、第一の電界効果型トランジスタのバックバイアスとして、1.2V程度の順方向バイアスを印加する。これにより、従来構造と比較して、インバータ遅延を、さらに半減させることが可能になる。

【0088】

40

以上の結果の通り、不純物領域13, 14を有する図4, 5に示す構成により、第一の電界効果型トランジスタの動作が高速化される。よって、当該第一の電界効果型トランジスタを構成要素として含むロジック回路の高速化も可能となる。

【0089】

また、本実施の形態では、第二の電界効果型トランジスタのバックバイアスとして、逆方向バイアスを印加する。さらに、不純物領域26の不純物濃度は、不純物領域25の不純物濃度よりも低い。ここで、不純物領域26の不純物濃度は、第二の電界効果型トランジスタを構成するゲート電極20の下方に位置する、半導体支持基板1の表面内付近の不純物濃度である。また、不純物領域25の不純物濃度は、第一の電界効果型トランジスタを構成するゲート電極の下方に位置する、半導体支持基板1の表面付近の不純物濃度であ

50

る。

【0090】

したがって、上記第二の電界効果型トランジスタを有するメモリ回路の動作安定性を向上させることができる。シミュレーション結果等を用いて、当該メモリ回路の動作安定性向上効果を説明する。

【0091】

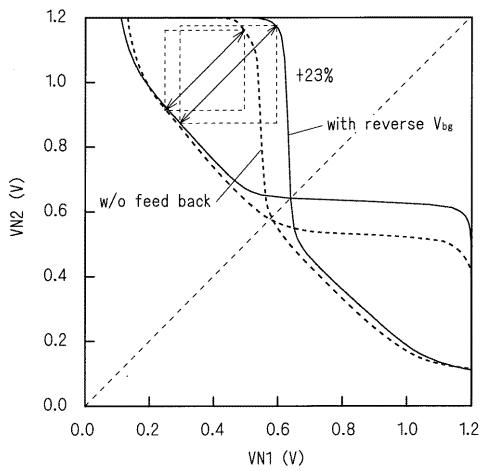

図24は、図4, 5に示す半導体装置において、第二の電界効果型トランジスタのバックバイアスとして、逆方向バイアスを印加した場合のスタティック・ノイズ・マージンをシミュレーションにより求めた結果である。図24の点線は、上記第二の電界効果型トランジスタにバックバイアスを印加しなかった場合の結果である。図24の実線は、上記第二の電界効果型トランジスタにバックバイアスを印加した場合の結果である。また、SRAMは通常インバータ回路を構成している。図24の横軸は、インバータを構成する一方側のトランジスタのゲート電圧であり、図24の縦軸は、インバータを構成する他方側のトランジスタのゲート電圧である。

10

【0092】

図24に示す曲線で囲まれる領域の面積が大きいほど、マージンが大きくSRAMが安定的に動作することを示す。図24に示す通り、バックバイアスとして逆バイアスを印加することにより、バックバイアスを印加しないときと比較して、ノイズマージンは約23%改善する。

【0093】

20

また、既に図1にて示した通り、発明者らは、薄膜（絶縁膜4の膜厚10nm以下）SOIトランジスタに、バックバイアスとして逆方向バイアスを印加することで、しきい値電圧バラツキが約16%低減できる。よって、図4, 5に示す構造の第二の電界効果型トランジスタに、バックバイアスとして逆方向バイアスを印加することで、メモリ回路動作の安定性は劇的に改善する。

【0094】

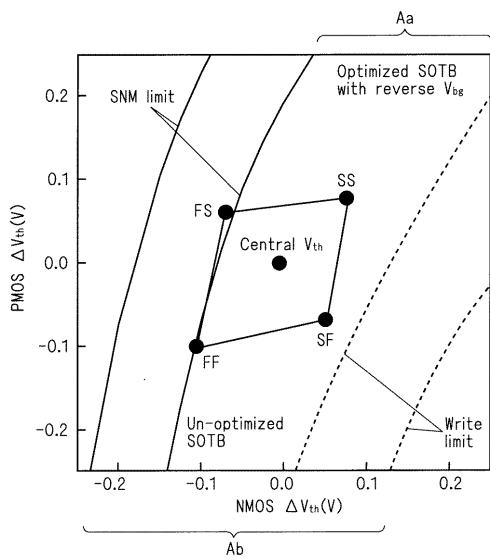

さらに、PMOSとNMOSとから成るインバータ構成を有するSRAMにおける、しきい値電圧V<sub>th</sub>バラツキと当該SRAM動作安定性との関係を、図25を用いて説明する。図25の横軸は、NMOSのしきい値電圧であり、図25の縦軸は、PMOSのしきい値電圧である。

30

【0095】

SRAMの動作マージンは、図25に示すSNMリミットとWriteリミットとの、両方の制限がかかる。結果として、動作マージンは、図25の領域Aa若しくは領域Ab内の範囲である。ここで、領域Aaは、図4, 5に示す構造の第二の電界効果型トランジスタに、バックバイアスとして逆方向バイアスを印加しない場合である。また、領域Abは、図4, 5に示す構造の第二の電界効果型トランジスタに、バックバイアスとして逆方向バイアスを印加する場合である。そして、トランジスタしきい値電圧バラツキが反映されるコーナーモデル（点F<sub>S</sub>, F<sub>F</sub>, S<sub>S</sub>, S<sub>F</sub>で囲まれた範囲）が、上記SNMリミットとWriteリミットとで囲まれる範囲内に収まつていれば、SRAMは安定動作できることになる。

40

【0096】

図25から分かるように、上記逆方向バイアスを印加しない場合では、SRAMの動作マージンがほぼ消失してしまう。つまり、領域Aaとコーナーモデルとの間に、あまりマージンが設けられない。これに対して、上記逆方向バイアスを印加した場合には、SRAMの動作マージンに十分な余裕ができる。つまり、領域Abとコーナーモデルとの間に、十分なマージンが設けることができる。

【0097】

このように、図25に示すデータからも、図4, 5に示す構造の第二の電界効果型トランジスタに、バックバイアスとして逆方向バイアスを印加する場合には、メモリ回路の動作の安定性が向上することが分かる。

50

## 【0098】

## &lt;実施の形態2&gt;

本実施の形態に係る半導体装置は、実施の形態1に係る半導体装置において、ゲート電極に対するソース・ドレイン領域の形成位置を限定したものである。したがって、ゲート電極とソース・ドレイン領域との位置関係以外の構成は、実施の形態1と同じである。よって、以下では、当該同じ構成の説明は省略し、異なる構成部分（つまり、ゲート電極とソース・ドレイン領域との位置関係）のみについて説明する。

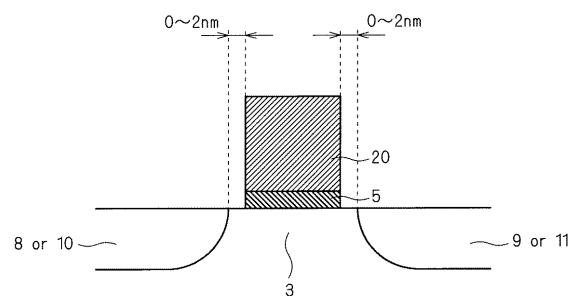

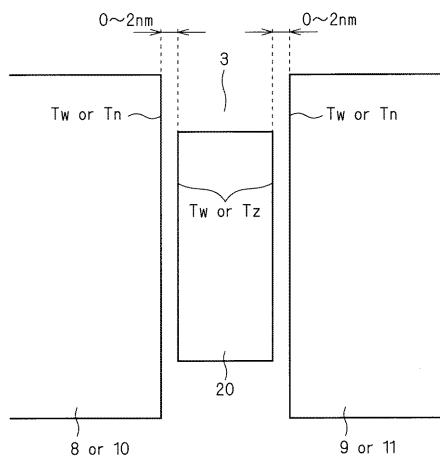

## 【0099】

図26は、実施の形態1で説明した第一の電界効果型トランジスタを構成する、第一のゲート電極20とソース・ドレイン領域8,9との位置関係を示す概略断面図である。または、図26は、実施の形態2で説明した第二の電界効果型トランジスタを構成する、第二のゲート電極20とソース・ドレイン領域10,11との位置関係を示す概略断面図である。図27は、図26の構成を上方から見た平面図である。

10

## 【0100】

図26に示すように、半導体層3上には、ゲート構造が形成されている。ここで、実施の形態1でも説明したように、ゲート構造は、ゲート絶縁膜5とゲート電極20とが当該順に積層した積層体である。また、図26に示すように、第一、二のゲート電極20の両脇における半導体層3の表面内には、ソース・ドレイン領域8,9（or 10,11）が形成されている。

## 【0101】

20

図26および図27から分かるように、平面視において、ソース・ドレイン領域8,9の第一のゲート電極20形成側の端部Tmは、第一のゲート電極20の端部Twと一致している。または、ソース・ドレイン領域8,9の第一のゲート電極20形成側の端部Tmは、第一のゲート電極20の非形成側に、上記端部Twと所定の距離だけ離れて形成されている。

## 【0102】

また同様に、平面視において、ソース・ドレイン領域10,11の第二のゲート電極20形成側の端部Tnは、第二のゲート電極20の端部Tzと一致している。または、ソース・ドレイン領域10,11の第二のゲート電極20形成側の端部Tnは、第二のゲート電極20の非形成側に、上記端部Tzと所定の距離だけ離れて形成されている。

30

## 【0103】

具体的に、ソース・ドレイン領域8～11の端部Tm（or端部Tn）とゲート電極20の端部Tw（or端部Tz）との平面視における間隔は、図26,27に示すように、0以上、2nm以下である。

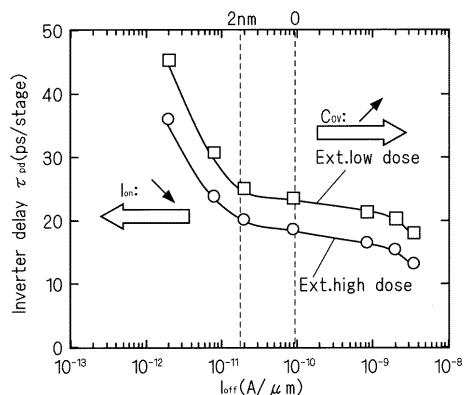

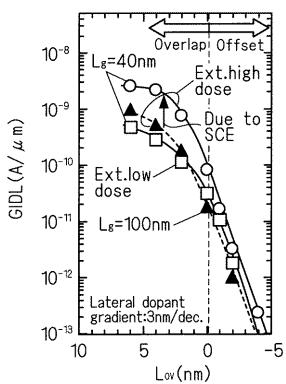

## 【0104】

一般的に、ゲート電極20をマスクとして用いて、ソース・ドレイン領域8～11の形成のための不純物イオン注入を行い、活性化のための熱処理を施すと、不純物イオンはゲート電極20の下方にも少し拡散する。結果、平面視において、ゲート電極20とソース・ドレイン領域8～11とは、一部領域において重複する。当該重複が生じるとGIDL（Gate Induced drain leakage）電流が増加することを発明者らはシミュレーション結果で確認した。また、当該重複領域が増大すればする程、当該GIDL電流が増加することも発明者らは、シミュレーション結果で確認した（たとえば、図28参照（横軸、オーバラック長、縦軸GIDL電流））。

40

## 【0105】

よって、当該GIDL電流低減のためには、平面視において、ゲート電極20とソース・ドレイン領域8～11とは重複し無いことが望ましい。つまり、ソース・ドレイン領域8～11の端部Tm（or端部Tn）とゲート電極20の端部Tw（or端部Tz）との平面視における間隔は、少なくとも0以上であることが望ましい。

## 【0106】

なお、平面視において、ゲート電極20とソース・ドレイン領域8～11とが重複する

50

と、両部材間で寄生容量が発生する。当該寄生容量が大きくなると、トランジスタの動作遅延を増大させる。当該寄生容量低減のためにも、平面視において、ゲート電極 20 とソース・ドレイン領域 8 ~ 11 とは重複し無いことが望ましい。

【0107】

しかしながら、ソース・ドレイン領域 8 ~ 11 がゲート電極 20 から離れれば離れるほど、ドレイン電流が減少し、結果としてトランジスタの動作が遅くなる（動作遅延時間が長くなる）。したがって、当該動作遅延の観点から、ゲート電極 20 に対してソース・ドレイン領域 8 ~ 11 を離し過ぎることは好ましくない。

【0108】

発明者らのシミュレーションの結果、図 29 の結果得ることができた。つまり、動作遅延の抑制と GIDL 電流の抑制とを両立させることができるために、ソース・ドレイン領域 8 ~ 11 の端部  $T_m$  (or 端部  $T_n$ ) とゲート電極 20 の端部  $T_w$  (or 端部  $T_z$ ) との平面視における間隔は、0 以上、2 nm 以下である必要がある。図 29 には、ソース・ドレイン領域 8 ~ 11 における不純物領域の濃度が高い場合と低い場合のシミュレーション結果を図示している。図 29 に示すように、上記平面視における間隔が、2 nm より大きくなると、トランジスタの動作遅延が急激に増加する。

【0109】

以上により、本実施の形態に係る半導体装置では、ソース・ドレイン領域 8 ~ 11 の端部  $T_m$  (or 端部  $T_n$ ) とゲート電極 20 の端部  $T_w$  (or 端部  $T_z$ ) との平面視における間隔は、図 26, 27 に示すように、0 以上、2 nm 以下である。

【0110】

したがって、トランジスタ動作の高速化を維持しつつ、GIDL 電流の低減を図ることができる。なお、本実施の形態に係る半導体装置は、実施の形態 1 に係る半導体装置を基礎としている。よって、実施の形態 1 で説明した効果も、本実施の形態に係る半導体装置は当然に有する。

【図面の簡単な説明】

【0111】

【図 1】バックバイアスの極性としきい値電圧のバラツキとの関係を示す図である。

【図 2】本発明に係る半導体装置を含む集積回路の概略構成例を示す平面図である。

【図 3】本発明に係る半導体装置を含む集積回路の概略構成例を示すフロアーフィギュアである。

【図 4】実施の形態 1 に係る半導体装置の構成の一例を示す断面図である。

【図 5】実施の形態 1 に係る半導体装置の構成の他の例を示す断面図である。

【図 6】実施の形態 1 に係る半導体装置の製造方法を説明するための工程断面図である。

【図 7】実施の形態 1 に係る半導体装置の製造方法を説明するための工程断面図である。

【図 8】実施の形態 1 に係る半導体装置の製造方法を説明するための工程断面図である。

【図 9】実施の形態 1 に係る半導体装置の製造方法を説明するための工程断面図である。

【図 10】実施の形態 1 に係る半導体装置の製造方法を説明するための工程断面図である。

。

【図 11】実施の形態 1 に係る半導体装置の製造方法を説明するための工程断面図である。

。

【図 12】実施の形態 1 に係る半導体装置の製造方法を説明するための工程断面図である。

。

【図 13】実施の形態 1 に係る半導体装置の製造方法を説明するための工程断面図である。

。

【図 14】実施の形態 1 に係る半導体装置の製造方法を説明するための工程断面図である。

。

【図 15】実施の形態 1 に係る半導体装置の製造方法を説明するための工程断面図である。

。

【図 16】実施の形態 1 に係る半導体装置の製造方法を説明するための工程断面図である。

。

10

20

30

40

50

【図17】実施の形態1に係る半導体装置の製造方法を説明するための工程断面図である。

【図18】実施の形態1に係る半導体装置の製造方法を説明するための工程断面図である。

【図19】実施の形態1に係る半導体装置の製造方法を説明するための工程断面図である。

【図20】実施の形態1に係る半導体装置の効果を説明するためのシミュレーション結果を示す図である。

【図21】実施の形態1に係る半導体装置の効果を説明するためのシミュレーション結果を示す図である。 10

【図22】実施の形態1に係る半導体装置の効果を説明するためのシミュレーション結果を示す図である。

【図23】実施の形態1に係る半導体装置の効果を説明するためのシミュレーション結果を示す図である。

【図24】実施の形態1に係る半導体装置の効果を説明するためのシミュレーション結果を示す図である。

【図25】実施の形態1に係る半導体装置の効果を説明するためのシミュレーション結果を示す図である。

【図26】実施の形態2に係る半導体装置の構成を示す断面図である。

【図27】実施の形態2に係る半導体装置の構成を示す平面図である。 20

【図28】実施の形態2に係る半導体装置の効果を説明するためのシミュレーション結果を示す図である。

【図29】実施の形態2に係る半導体装置の効果を説明するためのシミュレーション結果を示す図である。

【符号の説明】

【0112】

1 半導体支持基板、2 素子分離膜、3 SOI層、4 絶縁膜、5 ゲート絶縁膜、6, 6T, 6Za, 6Zb, 6W, 7 ウエル領域、8~11 ソース・ドレイン領域、12 サイドウォール膜、13, 14, 25, 26 不純物領域、20 ゲート電極、100 SOI型電界効果型トランジスタ、200 バルク型電界効果型トランジスタ、V1 順方向バイアス、V2 逆方向バイアスTw, Tz ゲート電極の端部、Tm, Tn ソース・ドレイン領域の端部。 30

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

### 【図20】

【図21】

### 【図22】

### 【図23】

【図24】

【図25】

【図26】

【図27】

【図29】

【図28】

---

フロントページの続き

| (51)Int.Cl.             | F I                  |

|-------------------------|----------------------|

| H 01 L 21/76 (2006.01)  | H 01 L 21/76 L       |

| H 01 L 21/762 (2006.01) | H 01 L 21/76 D       |

| H 01 L 27/10 (2006.01)  | H 01 L 27/10 4 6 1   |

| H 01 L 29/786 (2006.01) | H 01 L 29/78 6 1 3 Z |

(56)参考文献 特開2007-242950 (JP, A)

特開2006-049628 (JP, A)

特開2007-180402 (JP, A)

特開平10-242460 (JP, A)

特開平04-352467 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |                    |

|--------|--------------------|

| H 01 L | 27 / 0 8 8 - 0 9 2 |

| H 01 L | 27 / 1 2           |

| H 01 L | 29 / 7 8 6         |

| H 01 L | 27 / 0 2 - 0 4     |

| H 01 L | 21 / 7 6 2         |