(19)中華民國智慧財產局

(12)發明說明書公告本 (11)證書號數：TW I660552 B

(45)公告日：中華民國 108 (2019) 年 05 月 21 日

(21)申請案號：103133200

(22)申請日：中華民國 103 (2014) 年 09 月 25 日

(51)Int. Cl. : **H02H9/04 (2006.01)**

(30)優先權：2013/09/26 美國

14/038,127

(71)申請人：美商三胞半導體公司 (美國) TRIQUINT SEMICONDUCTOR, INC. (US)

美國

(72)發明人：泰許 布魯斯 J TESCH, BRUCE J. (US)

(74)代理人：閻啟泰；林景郁

(56)參考文獻：

TW 200739872A

TW 201330437A

CN 101658071A

JP 2013-118256A

US 5946177

US 2007/0076338A1

審查人員：林迺信

申請專利範圍項數：18 項 圖式數：12 共 38 頁

(54)名稱

靜電放電電路、製造方法和系統

ELECTROSTATIC DISCHARGE (ESD) CIRCUITRY, FABRICATING METHOD AND SYSTEM

(57)摘要

本揭露內容的實施例係描述靜電放電(ESD)電路以及相關的技術與配置。在一實施例中，ESD 電路係包含一和一供應電壓節點以及一接地節點耦接的第一節點、一和該第一節點以及該供應電壓節點耦接的第一電晶體、一和該第一節點以及該接地節點耦接的第二電晶體、一和該第一電晶體以及該第二電晶體耦接的第二節點、一和該第二節點耦接的第三電晶體、以及一和該第三電晶體耦接的第三節點，其中一用以充電該第一節點的第一時間期間係小於一用以放電該第三節點的第二時間期間。其它實施例亦可能被描述及/或主張。

Embodiments of the present disclosure describe electrostatic discharge (ESD) circuitry and associated techniques and configurations. In one embodiment, ESD circuitry includes a first node coupled with a supply voltage node and a ground node, a first transistor coupled with the first node and the supply voltage node, a second transistor coupled with the first node and the ground node, a second node coupled with the first transistor and the second transistor, a third transistor coupled with the second node and a third node coupled with the third transistor, wherein a first time period to charge the first node is less than a second time period to discharge the third node. Other embodiments may be described and/or claimed.

指定代表圖：

圖2

符號簡單說明：

200 · · · ESD 電路

M1 · · · 第一電晶體

M2 · · · 第二電晶體

M3 · · · 第三電晶體

M4 · · · 第四電晶體

M5 · · · 第五電晶體

M6 · · · 第六電晶體

M7 · · · 第七電晶體

n1 · · · 第一節點

n2 · · · 第二節點

n3 · · · 第三節點

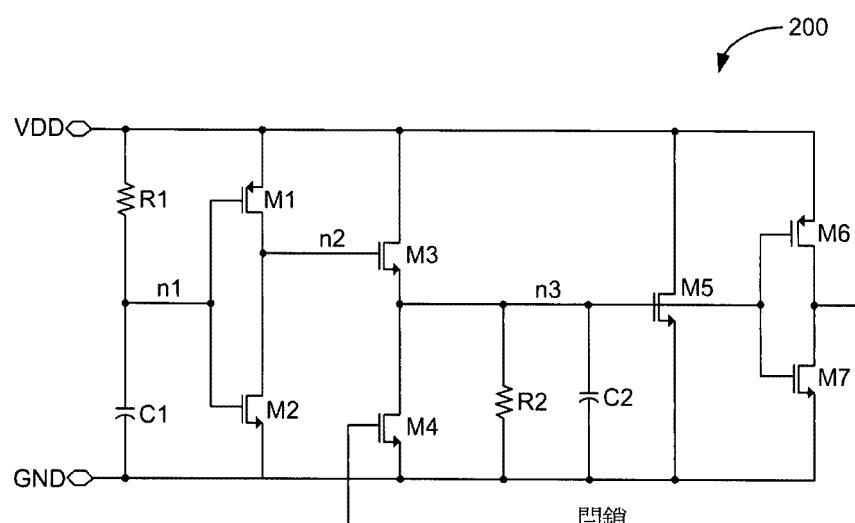

圖 2 係概要地描繪根據各種實施例的 ESD 電路。

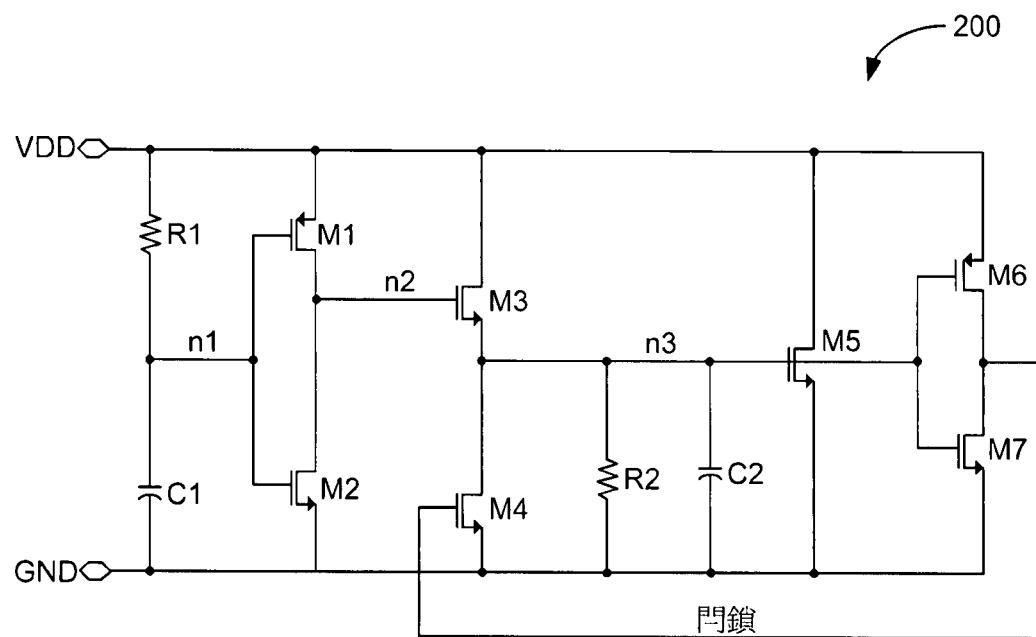

圖 3 係概要地描繪根據各種實施例的 ESD 電路之一替代的配置。

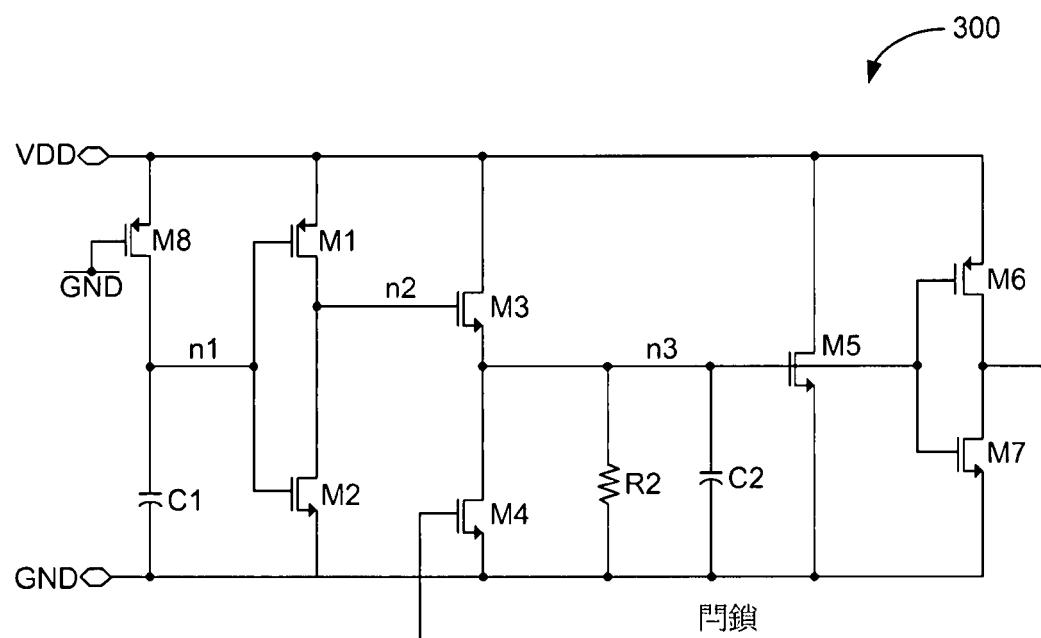

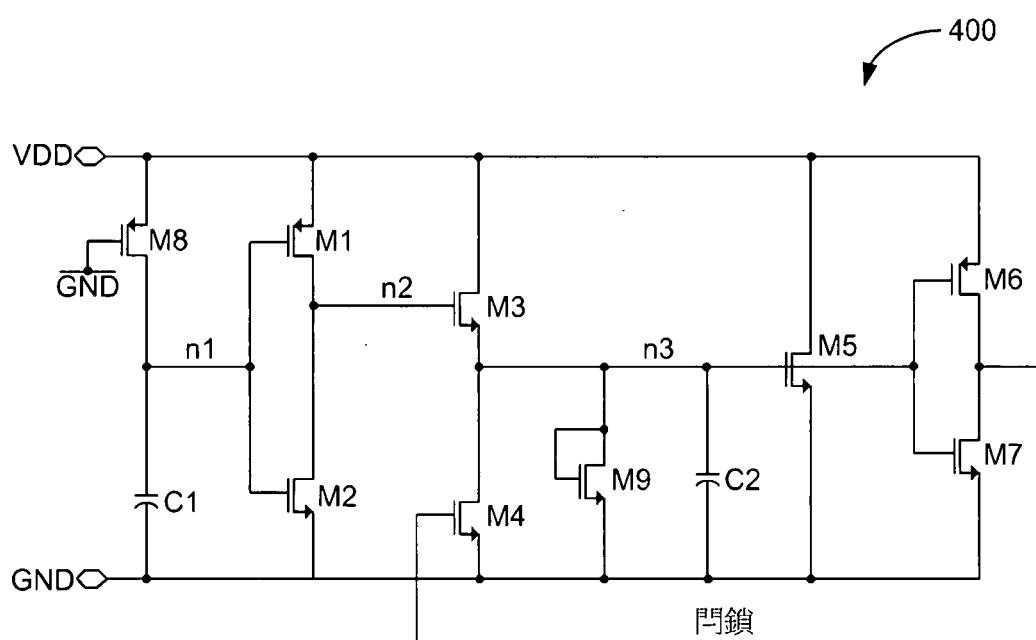

圖 4 係概要地描繪根據各種實施例的 ESD 電路之一替代的配置。

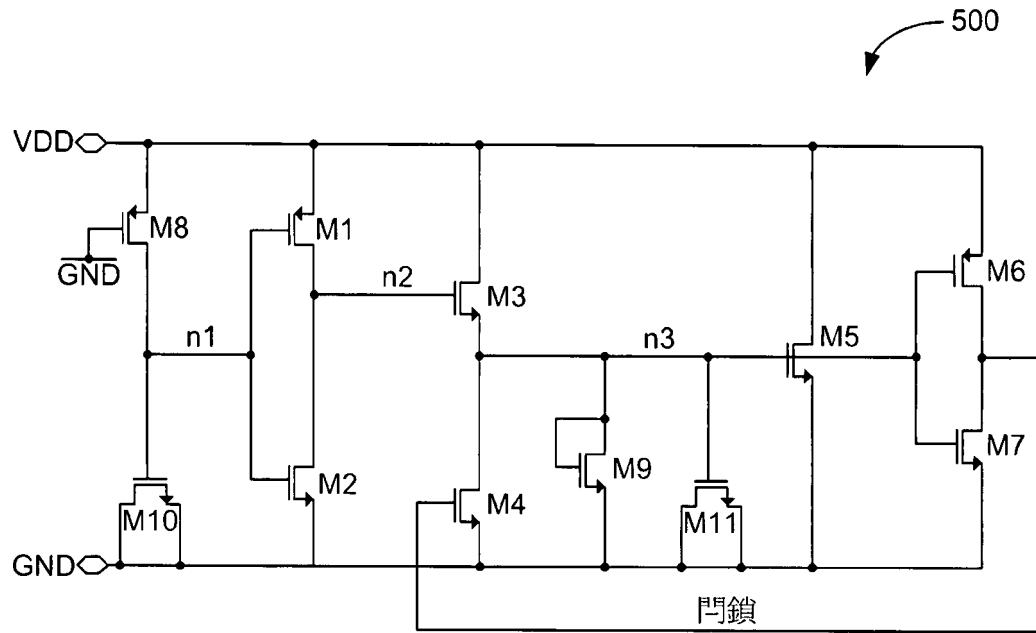

圖 5 係概要地描繪根據各種實施例的 ESD 電路之一替代的配置。

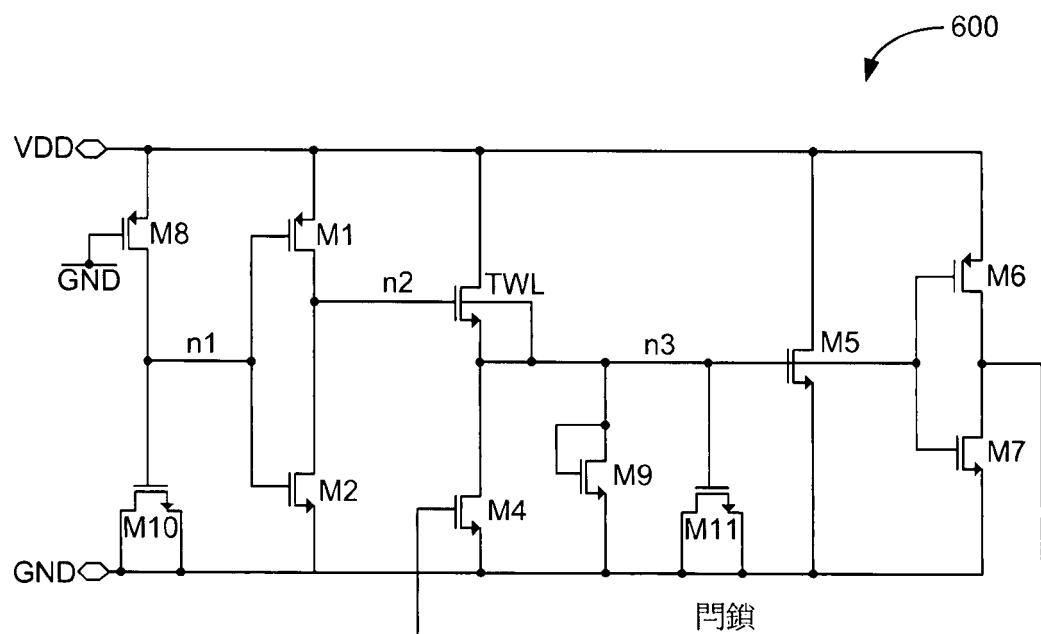

圖 6 係概要地描繪根據各種實施例的 ESD 電路之一替代的配置。

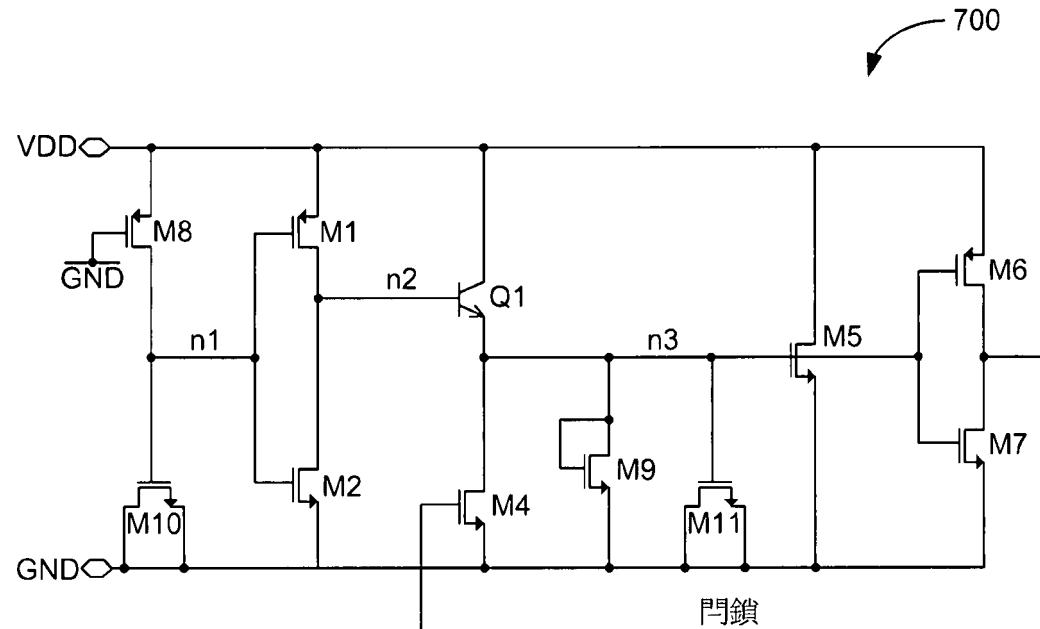

圖 7 係概要地描繪根據各種實施例的 ESD 電路之一替代的配置。

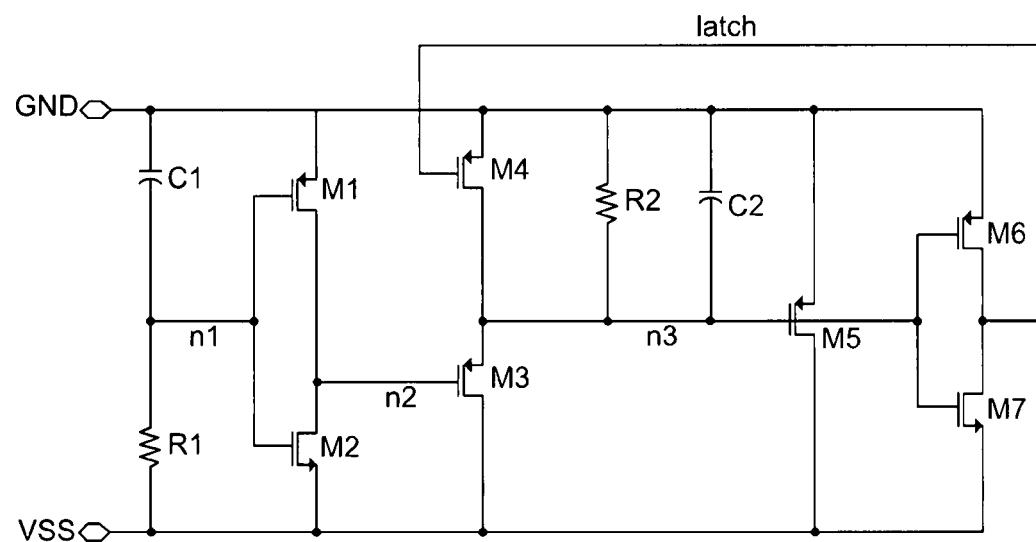

圖 8a 係概要地描繪根據各種實施例的 ESD 電路之一替代的配置。

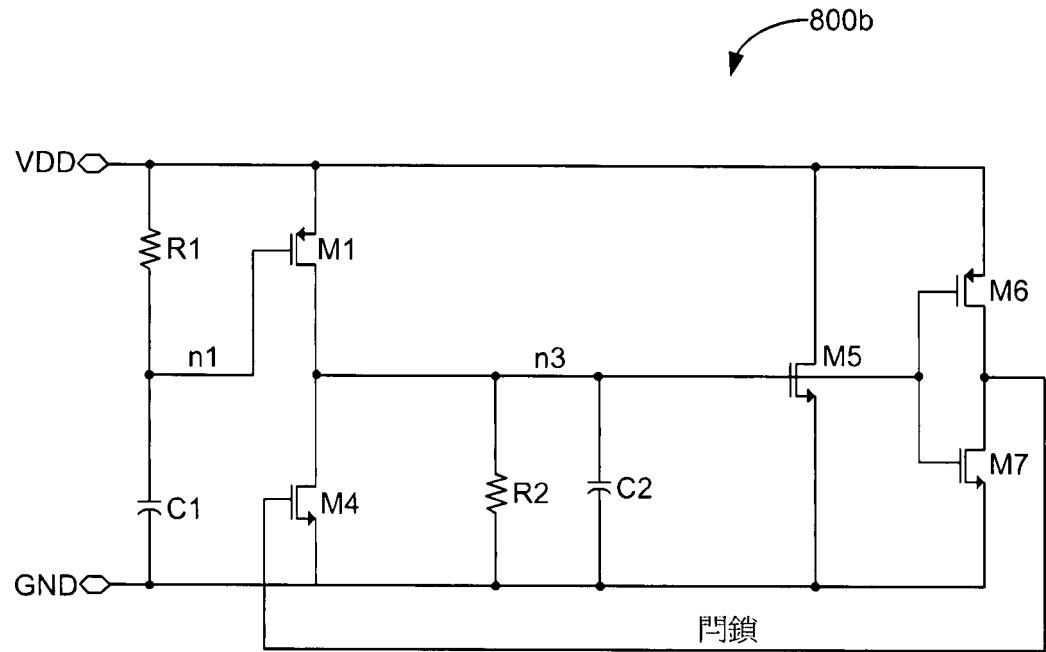

圖 8b 係概要地描繪根據各種實施例的 ESD 電路之一替代的配置。

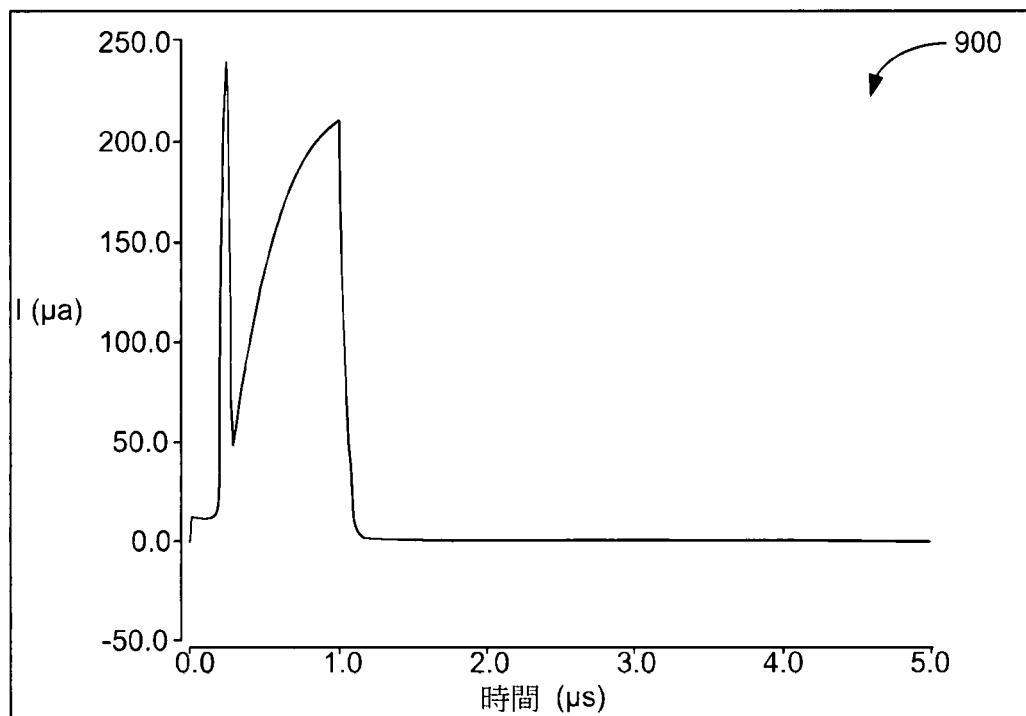

圖 9 係概要地描繪根據各種實施例的圖 2 的 ESD 電路的一供應電壓節點的電流相對於時間的一範例圖。

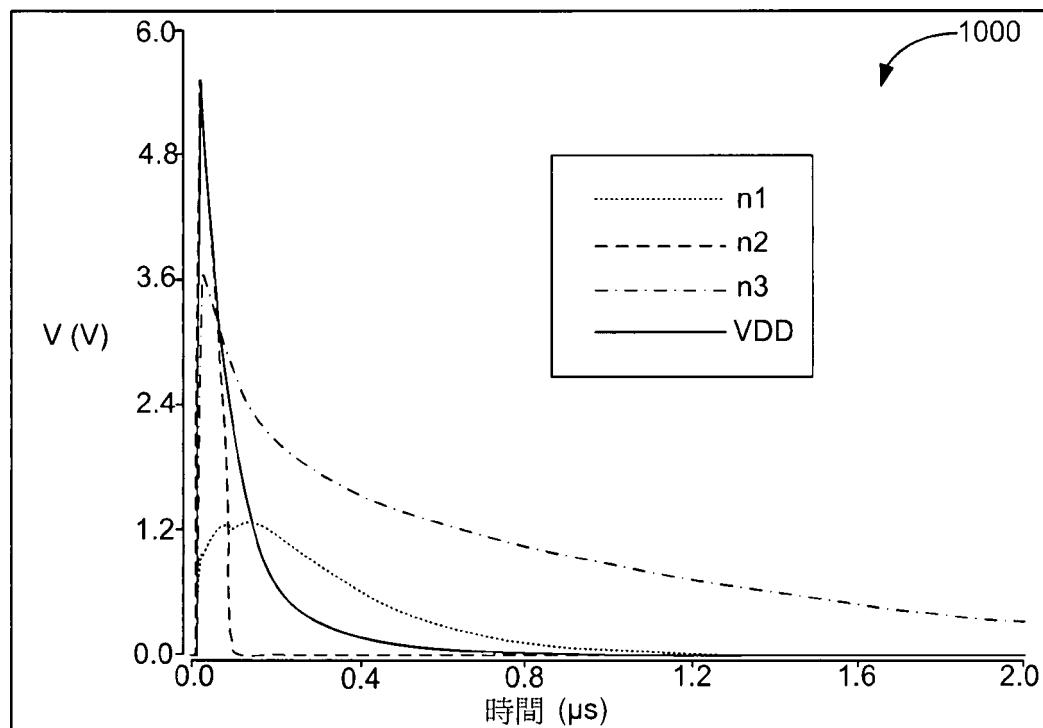

圖 10 係概要地描繪根據各種實施例的圖 2 的 ESD 電路的各種節點的電壓相對於時間的一範例圖。

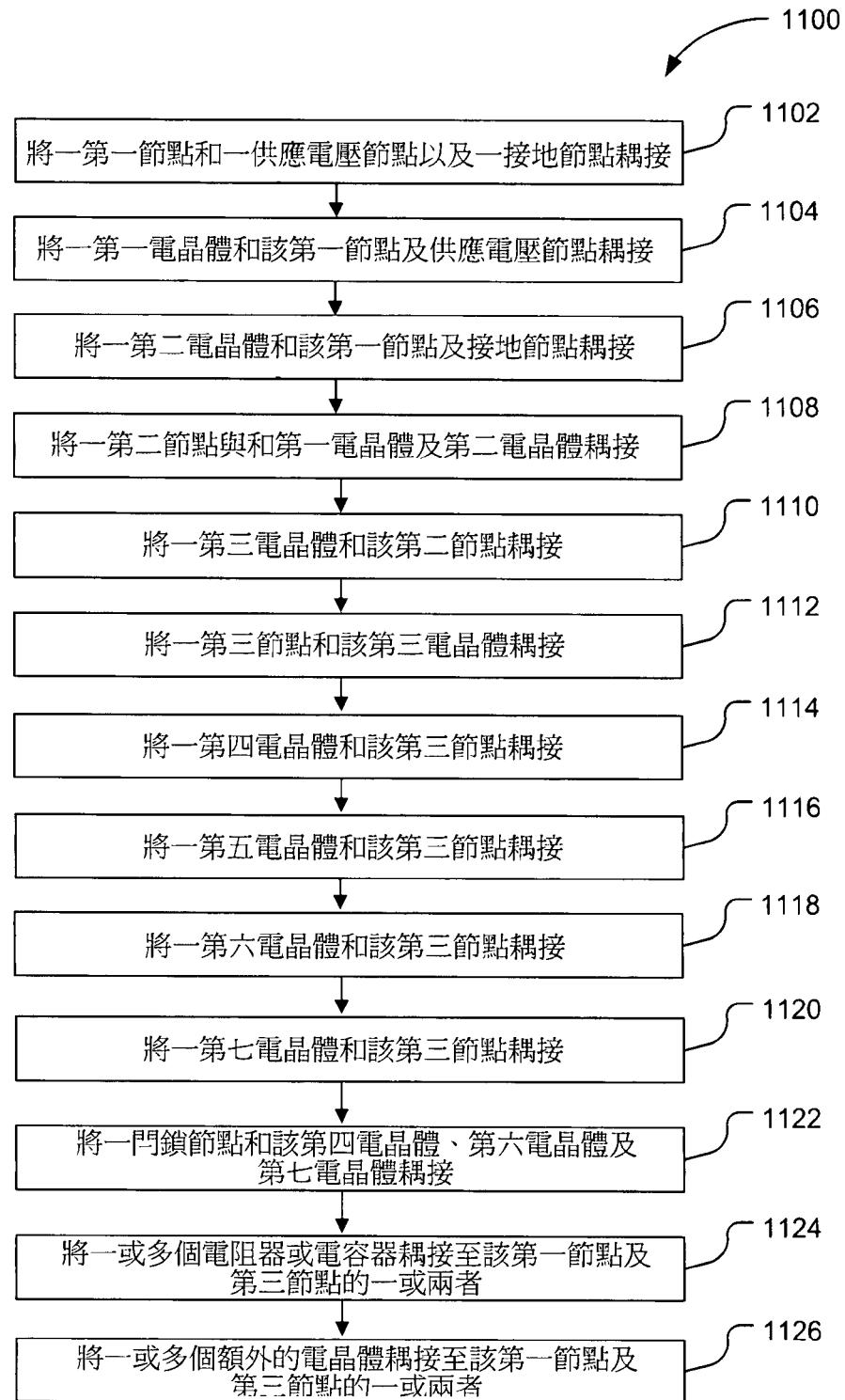

圖 11 是根據各種實施例的一種用於製造或設計 ESD 電路之方法的流程圖。

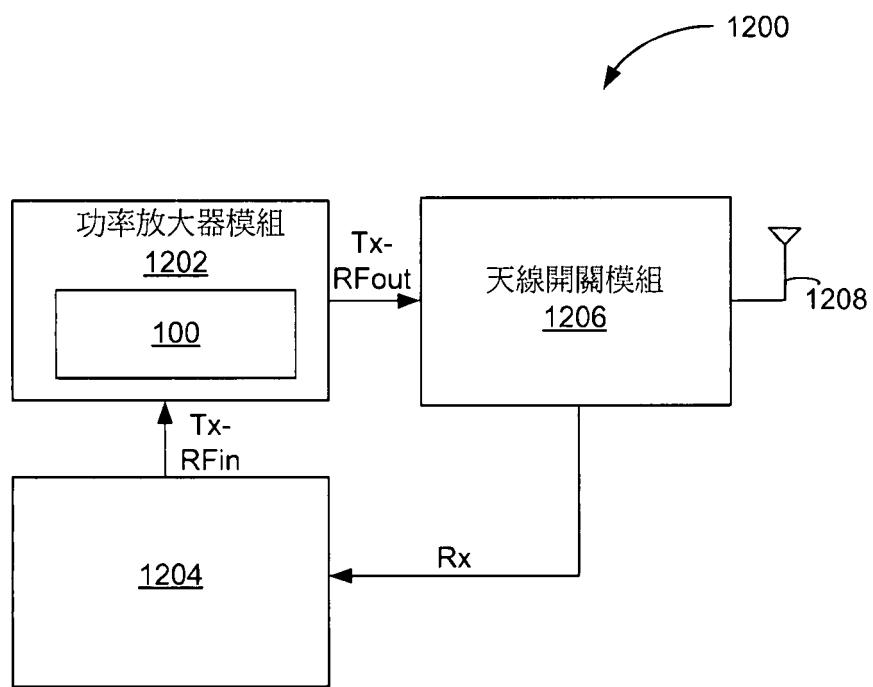

圖 12 係概要地描繪根據各種實施例的一種包含一具有 ESD 電路的晶粒之範例的系統。

## 【實施方式】

**【0007】** 本揭露內容的實施例係描述靜電放電(ESD)電路以及相關的技術與配置。在以下的詳細說明中係參考到構成其之一部分的所附的圖式，其中相同的元件符號係指整篇的類似的元件，並且在圖式中係展示本揭露內容之標的可被實施於其中的舉例的實施例。將瞭解到的是，其它實施例亦可被利用，並且可以做成結構或邏輯的改變而不脫離本揭露內容的

範疇。因此，以下的詳細說明不應當被視為限制性的涵義，並且實施例的範疇係藉由所附的申請專利範圍及其等同物所界定。

**【0008】** 為了本揭露內容之目的，該措辭"A 及/或 B"是表示(A)、(B)或(A 及 B)。為了本揭露內容之目的，該措辭"A、B 及/或 C"是表示(A)、(B)、(C)、(A 及 B)、(A 及 C)、(B 及 C)、或是(A、B 及 C)。

**【0009】** 該說明可能會使用該些措辭"在一實施例中"或是"在實施例中"，其分別可以指相同或是不同的實施例中的一或多個。再者，相關本揭露內容的實施例所用的術語"包括"、"包含"、"具有"與類似者是同義的。該術語"耦接"可以指一直接的連接、一間接的連接、或是一間接的通訊。

**【0010】** 該術語"和…耦接"及其衍生語可被使用於此。"耦接"可以是表示下列中的一或多個。"耦接"可能表示兩個或多個元件是直接實體或電性接觸。然而，"耦接"亦可能表示兩個或多個元件彼此間接接觸，但是仍然彼此合作或互動，並且可能表示一或多個其它元件被耦接或連接在該些被稱為彼此耦接的元件之間。

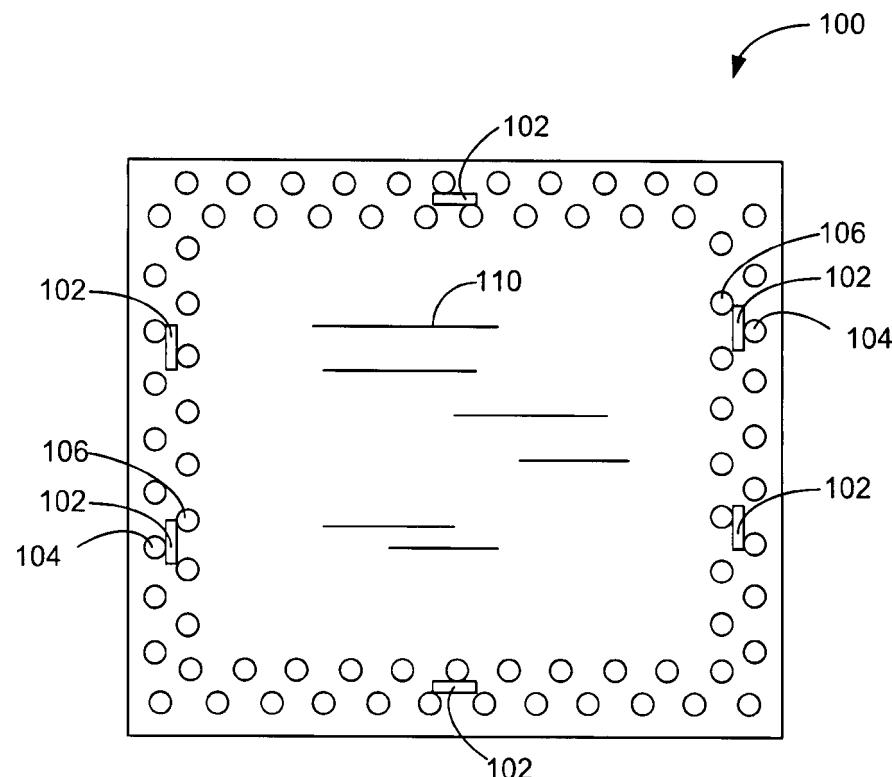

**【0011】** 圖 1 係概要地描繪根據各種實施例的一包含靜電放電(ESD)電路之晶粒 100。在某些實施例中，該晶粒 100 可包含具有一或多個暫態 ESD 箔制電路(ESD clamp，在以下稱為"ESD 箔制電路 102")的形式之 ESD 電路。該 ESD 箔制電路 102 可被配置以例如是在靜電衝擊或其它電源突波的 ESD 事件中保護在該晶粒上的其它電路 110。該其它電路 110 例如可包含一或多個電晶體、記憶單元或是其它的主動元件及/或用以指定路由給電性信號往返該些主動元件的互連電路、或是任何其它可能會對於一 ESD 事件敏感的電路。

【0012】 在某些實施例中，該 ESD 箔制電路 102 可以利用例如是互補金屬氧化物半導體(CMOS)技術的半導體製造技術或是其它適當的技術來形成在該晶粒 100 的一主動側上。該 ESD 箔制電路 102 可被設置成相鄰該晶粒 100 的電源連線 104 及接地連線 106、或是介於兩者之間。例如，在某些實施例中，該些電源連線中的一或多個可以和圖 2-8 的 ESD 電路 200 中的供應電壓(VDD 或 VSS)節點耦接，並且該些接地連線 106 中的一或多個可以和在圖 2-8 的 ESD 電路 200 中的接地(GND)節點耦接。

【0013】 該些電源連線 104 以及接地連線 106 例如可包含像是凸塊、柱、線路、貫孔、墊或是其它適當的結構之互連結構或接點，並且可被配置以分別提供一用於該晶粒的操作(例如，處理、傳送/接收輸入/輸出信號、儲存資訊、執行碼、等等)之供應電壓及接地。如同在此所用的，"接地"可以代表包含非零電壓的任何適當的電壓。

【0014】 在所描繪的實施例中，電源連線 104、接地連線 106 以及 ESD 箔制電路 102 係被設置在該晶粒 100 的一週邊區域中，並且該其它電路 110 係被設置在該晶粒 100 的一中央區域中。在其它實施例中，電源連線 104、接地連線 106、ESD 箔制電路 102 及/或其它電路 110 可以用所描繪者以外的其它適當的配置來加以安排。

【0015】 圖 2 係概要地描繪根據各種實施例的 ESD 電路 200。該 ESD 電路 200 例如可以代表在圖 1 中描繪的 ESD 箔制電路 102 中之一 ESD 箔制電路。在某些實施例中，該 ESD 電路 200 係包含一正供應電壓節點(在以下稱為"VDD")以及一接地節點(在以下稱為"GND")。在某些實施例中，該 VDD 可以和相關圖 1 所敘述的電源連線 104 中的一或多個耦接，並且該 GND 可

以和該些接地連線 106 中的一或多個耦接。

**【0016】** 根據各種實施例，該 ESD 電路 200 可包含一和 VDD 及 GND 耦接的第一節點 n1、一和該第一節點 n1 及 VDD 耦接的第一電晶體 M1、一和該第一節點 n1 及 GND 耦接的第二電晶體 M2、一和該第一電晶體 M1 及第二電晶體 M2 耦接的第二節點 n2、一和該第二節點 n2 耦接的第三電晶體 M3、以及一和該第三電晶體 M3 耦接的第三節點 n3。在某些實施例中，如同可見的，該 ESD 電路 200 可進一步包含一和該第三節點 n3 耦接的第四電晶體 M4、一和該第三節點 n3 耦接的第五電晶體 M5、一和該第三節點 n3 耦接的第六電晶體 M6、一和該第三節點 n3 耦接的第七電晶體 M7、以及一被配置以耦接該第四電晶體 M4 及第三節點 n3 的門鎖節點。

**【0017】** 在某些實施例中，如同可見的，該第一節點 n1 可以和一包含該第一電晶體 M1 及第二電晶體 M2 的反相器耦接。如同可見的，該第一節點 n1 可以和該第一電晶體 M1 及第二電晶體 M2 的一閘極耦接，該第一電晶體 M1 的一源極可以和 VDD 耦接，該第二電晶體 M2 的一源極可以和 GND 耦接，並且該第一電晶體 M1 的一汲極可以和該第二電晶體 M2 的一汲極耦接。該第二節點 n2 可以和該第一電晶體 M1 的一汲極以及該第二電晶體 M2 的一汲極耦接。

**【0018】** 在某些實施例中，該第三電晶體 M3 可以作為一源極隨耦器。該第二節點 n2 可以和該第三電晶體 M3 的一閘極耦接。該第三電晶體 M3 的一汲極可以和 VDD 耦接。該第三節點 n3 可以和該第三電晶體 M3 的一源極以及該第四電晶體 M4 的一汲極耦接。該第四電晶體 M4 的一源極可以和 GND 耦接。在某些實施例中，該第三節點 n3 可以和該第五電晶體 M5

的一閘極、該第六電晶體 M6 的一閘極、以及該第七電晶體 M7 的一閘極耦接。該門鎖節點可以和該第六電晶體的一汲極、該第七電晶體的一汲極、以及該第四電晶體的一閘極耦接。

**【0019】** 根據各種實施例，一或多個電阻器及/或電容器可耦接至該第一節點 n1 以及第三節點 n3 中的一或多個。該節點 n1 及/或 n3 的一電阻或電容可以至少部分是基於該一或多個電阻器或電容器。例如，該第一節點 n1 的一電阻可以根據一或多個和該第一節點 n1 耦接的電阻器(在以下稱為"R1")來加以決定，並且該第一節點 n1 的一電容可以根據一或多個和該第一節點 n1 耦接的電容器(在以下稱為"C1")來加以決定。該第三節點 n3 的電阻及電容可以根據和該第三節點 n3 耦接的一或多個電阻器(在以下稱為"R2")以及一或多個電容器(在以下稱為"C2")來加以決定。在某些實施例中，該第三節點 n3 的電容可以是主要基於該第五電晶體 M5 的一閘極電容，而例如是 C2 的電容器在該 ESD 電路 200 中可以是非必要的。

**【0020】** 根據各種實施例，R1 及 C1 可被調諧或配置以提供一第一時間期間(例如，常數 $\tau_1$ )來充電該第一節點 n1。R2 及 C2 可被調諧或配置以提供一第二時間期間(例如，常數 $\tau_2$ )來放電該第三節點 n3。在某些實施例中，該第一時間期間(例如， $\tau_1$ )可以是小於該第二時間期間(例如， $\tau_2$ )，以提供一具有相對於其它暫態 ESD 箍制電路之改良的穩定性及降低的湧入電流的暫態 ESD 箍制電路給 ESD 電路 200。例如，一較短的第一時間期間(例如， $\tau_1$ )可以限制湧入電流至該 ESD 電路 200，並且一較長的第二時間期間(例如， $\tau_2$ )可以容許一外部的 ESD 電容(例如，對於人體模型而言為 100 微微法拉)透過該 ESD 電路 200 的完全放電。該 ESD 電路 200 可具有 1 個反相器的

箝制電路的穩定性，並且對於 1 微秒( $\mu$ s)的上升時間的電源維持 ESD 保護的位準，而同時降低湧入電流一約  $10^5$  的因數。

**【0021】** 在某些實施例中，該第一時間期間可以開始於 VDD 被導通以提供一供應電壓時，並且在 C1 已經充電至其中該第二節點 n2 是低到足以關斷該第三電晶體 M3 的一時點結束。該第二時間期間可以開始於該第三電晶體 M3 被設定為一關斷狀態，並且可以在該第四電晶體 M4 被設定為一導通狀態(正常的開啓電源)時結束。該第一時間期間以及第二時間期間在其它實施例中可以利用其它適當的技術來加以組態設定。

**【0022】** 在某些實施例中，該第二時間期間可以是比該第一時間期間長大約一個數量級。例如，在某些實施例中，該第二時間期間可以是大於該第一時間期間至少七倍。在某些實施例中，該第一時間期間可具有一從 30 奈秒(ns)到 300ns 的值，並且該第二時間期間可具有一從 300ns 到 3000ns 的值。在一實施例中，該第一時間期間可以是大約 40ns，並且該第二時間期間可以是大約 800ns。在另一實施例中，該第一時間期間可以是 100ns，並且該第二時間期間可以是大約 1000ns。在一實施例中，該第一時間期間可以是 180ns，並且該第二時間期間可以是 1230ns。在一實施例中，該第一時間期間係具有一小於 1 微秒的值，並且該第二時間期間係大於該第一時間期間。該第一時間期間以及第二時間期間在其它實施例中可具有廣泛而多樣的其它適當的值。

**【0023】** 根據某些實施例，R1 及 C1 可以產生一較短的第一時間期間，其可以只容許該第二節點 n2 的電壓在 VDD(例如，5 伏特(V))具有一快速的上升時間(例如，小於 1 $\mu$ s)時變為高的。當第二節點 n2 的電壓變為高的

時候，該第三電晶體 M3 可以導通並且將該第三節點 n3 的一電壓拉高，使得該第五電晶體 M5 可以灌入該 ESD 電流(例如，在某些實施例中為大約 1.33 安培(A))。該第一時間期間可以使得該第二節點 n2 的電壓快速地變低，此係關斷該第三電晶體 M3。藉由 R2 及 C2(及/或第五電晶體 M5 的閘極電容)所產生之較長的第二時間期間可以在一較慢的速率下放電該第三節點 n3 的一電壓。以此種方式利用該第一時間期間以及第二時間期間可以限制湧入電流，同時容許一外部的 ESD 電容器(例如，對於人體模型而言為 100 微微法拉)透過該 ESD 電路 200 的完全放電。該第五電晶體 M5 的一閘極電容可以是大於該 ESD 電路 200 中的其它電晶體的一閘極電容，以便於有利地調諧該較長的第二時間期間以放電該第三節點 n3。利用該第五電晶體的閘極電容以主要提供用於調諧該第二時間期間的電容可以節省在該晶粒(例如，圖 1 的晶粒 100)上用於該 ESD 電路 200 的面積。一旦該第五電晶體 M5 的閘極已經放電到第五電晶體 M5 的一臨界電壓，則該門鎖節點可以在正常的操作期間確保該第五電晶體 M5 的一閘極能夠藉由該第四電晶體 M4 被快速地拉到接地。在某些實施例中，該 ESD 電路 200 對抗振盪的穩定性可加以改善，因為單一反相器可以驅動該第三電晶體 T3。在某些實施例中，該第三電晶體 T3 可具有一小於 1 的電壓增益。

**【0024】** 在該 ESD 電路 200 的一第一實施例中，該第一電晶體 M1 可具有一 40 微米的寬度以及一 0.6 微米的通道長度，該第二電晶體 M2 可具有一 10 微米的寬度以及一 0.6 微米的通道長度，該第三電晶體 M3 可具有一 40 微米的寬度以及一 0.6 微米的通道長度，該第四電晶體 M4 可具有一 10 微米的寬度以及一 0.6 微米的通道長度，該第五電晶體 M5 可具有一

2000 微米的寬度以及一 0.6 微米的通道長度，該第六電晶體 M6 可具有一 2 微米的寬度以及一 0.6 微米的通道長度，並且該第七電晶體 M7 可具有一 10 微米的寬度以及一 0.6 微米的通道長度。在該第一實施例中，R1 可具有一 400,000 歐姆的有效電阻，並且 R2 可具有一 200,000 歐姆的有效電阻。

**【0025】** 在其它實施例中，該些電晶體(例如，M1、M2、等等)及/或電阻器(例如，R1、R2)可具有其它適當的值。該些其它適當的值可包含和上述不同的標稱值，但是當和該 ESD 電路 200 的其它電晶體或電阻器比較時可具有一相同的相對值(例如，大於或小於)。例如，在某些實施例中，該第一電晶體的寬度可以是大於該第二電晶體的寬度，其可以增高藉由電晶體 M1 及 M2 所形成的反相器的一切換點。該第五電晶體 M5 可具有一寬度是實質大於在該 ESD 電路 200 中的其它電晶體的寬度。該第六電晶體 M6 可具有一寬度是小於該第七電晶體 M7 的一寬度，此可以減低藉由電晶體 M6 及 M7 所形成的反相器的一切換點。

**【0026】** 在該 ESD 電路 200 的一第二實施例中，該第一電晶體 M1 可具有一 40 微米的寬度以及一 0.7 微米的通道長度，該第二電晶體 M2 可具有一 10 微米的寬度以及一 0.7 微米的通道長度，該第三電晶體 M3 可具有一 20 微米的寬度以及一 0.7 微米的通道長度，該第四電晶體 M4 可具有一 10 微米的寬度以及一 0.7 微米的通道長度，該第五電晶體 M5 可具有一 2880 微米的寬度以及一 0.7 微米的通道長度，該第六電晶體 M6 可具有一 2 微米的寬度以及一 0.7 微米的通道長度，並且該第七電晶體 M7 可具有一 10 微米的寬度以及一 0.6 微米的通道長度。在該第二實施例中，R1 可具有一大約 400,000 歐姆的有效電阻，並且 R2 可具有一大約 200,000 歐姆的有效電

阻。在其它實施例中，該電晶體(例如，M1、M2、等等)及/或電阻器(例如，R1、R2)可具有其它適當的值。

**【0027】** 圖 3 係概要地描繪根據各種實施例的 ESD 電路 300 的一替代的配置。該 ESD 電路 300 可以與相關圖 2 的 ESD 電路 200 所敘述的實施例相稱，除了圖 2 的一或多個電阻器 R1 已經被一或多個額外的電晶體(在以下稱為"第八電晶體 M8")所取代之外。根據各種實施例，該第一節點 n1 的一電阻可以是基於該第八電晶體 M8。

**【0028】** 如同可見的，該第八電晶體 M8 可包含一和 VDD 耦接的源極、一和該第一節點 n1 耦接的汲極、以及一和 GND 耦接的閘極。在某些實施例中，該第八電晶體 M8 可以是一 P 型場效電晶體(PFET)。利用該第八電晶體 M8 來取代該 ESD 電路 200 的 R1 可以相對於該 ESD 電路 200 來縮減在該 ESD 電路 300 中的晶粒面積。

**【0029】** 圖 4 係概要地描繪根據各種實施例的 ESD 電路 400 的一替代的配置。該 ESD 電路 400 可以與相關圖 3 的 ESD 電路 300 所敘述的實施例相稱，除了圖 3 的一或多個電阻器 R2 已經被一或多個額外的電晶體(在以下稱為"第九電晶體 M9")所取代之外。根據各種實施例，該第三節點 n3 的一電阻可以是基於該第九電晶體 M9。

**【0030】** 如同可見的，該第九電晶體 M9 可包含一和 GND 耦接的源極、一和該第三節點 n3 耦接的汲極、以及一和該第三節點 n3 耦接的閘極。在某些實施例中，該第九電晶體 M9 可以是一零臨界電壓的電晶體。利用該第九電晶體 M9 來取代該 ESD 電路 300 的 R2 可以相對於該 ESD 電路 300 縮減在該 ESD 電路 400 中的晶粒面積。

**【0031】** 圖 5 係概要地描繪根據各種實施例的 ESD 電路 500 的一替代的配置。該 ESD 電路 500 可以與相關圖 4 的 ESD 電路 400 所敘述的實施例相稱，除了圖 4 的 C1 及 C2 的一或多個電容器已經被一或多個額外的電晶體(在以下分別稱為"第十電晶體 M10"以及"第十一電晶體 M11")所取代之外。根據各種實施例，該第一節點 n1 及/或第三節點 n3 的一電容可以是基於該第十電晶體 M10 及/或第十一電晶體 M11。

**【0032】** 如同可見的，該第十電晶體 M10 可包含一和 GND 耦接的源極、一和 GND 耦接的汲極、以及一和該第一節點 n1 耦接的閘極。如同可見的，該第十一電晶體 M11 可包含一和 GND 耦接的源極、一和 GND 耦接的汲極、以及一和該第三節點 n3 耦接的閘極。該第十電晶體 M10 以及第十一電晶體 M11 的一閘極電容可被配置、調諧或是選擇，以提供相關圖 2 的 ESD 電路 200 所敘述的第一節點 n1 的一第一時間期間(例如， $\tau_1$ )以及第三節點 n3 的一第二時間期間(例如， $\tau_2$ )。在某些實施例中，該第九電晶體 M9 可以是一零臨界電壓的電晶體。利用該第十電晶體 M10 及第十一電晶體 M11 來取代該 ESD 電路 400 的 C1 及 C2 可以相對於該 ESD 電路 400 縮減在該 ESD 電路 500 中的晶粒面積。

**【0033】** 在一對應相關圖 2 的 ESD 電路 200 所敘述的第一實施例之實施例中，該第八電晶體 M8 可具有一 2 微米的寬度以及一 10 微米的通道長度，該第九電晶體 M9 可具有一 1 微米的寬度以及一 20 微米的通道長度，該第十電晶體 M10 可具有一 10 微米的寬度以及一 10 微米的通道長度，該第十一電晶體 M11 可具有一 80 微米的寬度以及一 10 微米的通道長度。該些電晶體 M8-M11 在其它實施例中可具有其它適當的尺寸。

**【0034】** 圖 6 係概要地描繪根據各種實施例的 ESD 電路 600 的一替代的配置。該 ESD 電路 600 可以與相關圖 5 的 ESD 電路 500 所敘述的實施例相稱，除了圖 5 的第三電晶體 M3 已經被一個三井的電晶體 TWL 所取代之外。

**【0035】** 如同可見的，該三井的電晶體 TWL 可包含一和該第三節點 n3 耦接的源極、一和 VDD 耦接的汲極、以及一和該第二節點 n2 耦接的閘極。再者，如同可見的，該三井的電晶體 TWL 的一主體(body)可以是和該第三節點 n3 耦接的。在某些實施例中，該三井的電晶體 TWL 可以是一隔離電晶體，例如，該電晶體的一主體係與基體矽(bulk silicon)隔離。在某些實施例中，該三井的電晶體 TWL 可以藉由一絕緣體上矽(SOI)製程來與該基體隔離開。在某些實施例中，該三井的電晶體可以是一 SOI 電晶體。在某些實施例中，該三井的電晶體 TWL 可以是一 N 型 FET(NFET)。在某些實施例中，利用該三井的電晶體 TWL 來取代圖 5 的第三電晶體 M3 可降低在該 ESD 電路 600 中的一本體效應(body effect)及/或一波峰暫態電壓(例如，當該第二節點 n2 正在上升並且該第三電晶體 M3 正在將該第三節點 n3 拉高時)。在一對應相關圖 2 的 ESD 電路 200 所敘述的第一實施例之實施例中，該三井的電晶體 TWL 可具有類似該第三電晶體 M3 的尺寸。

**【0036】** 圖 7 係概要地描繪根據各種實施例的 ESD 電路 700 的一替代的配置。該 ESD 電路 700 可以與相關圖 5 的 ESD 電路 500 所敘述的實施例相稱，除了圖 5 的第三電晶體 M3 已經被一個雙載子電晶體 Q1 所取代之外。

**【0037】** 如同可見的，該雙載子電晶體 Q1 可包含一和該第三節點 n3

耦接的射極、一和 VDD 耦接的集極、以及一和該第二節點 n2 耦接的基極。

在某些實施例中，該雙載子電晶體 Q1 可以根據一 BiCMOS 製程來加以形成。在某些實施例中，利用該三井的電晶體 TWL 來取代圖 5 的第三電晶體 M3 可以降低在該 ESD 電路 700 中的一波峰暫態電壓(例如，當該第二節點 n2 正在上升並且該第三電晶體 M3 正在將該第三節點 n3 拉高時)。

**【0038】** 圖 8a 係概要地描繪根據各種實施例的 ESD 電路 800a 的一替代的配置。如同可見的，該 ESD 電路 800a 可以代表圖 2 的 ESD 電路 200 的一種重新配置，以保護一負供應電壓節點(VSS)。該 ESD 電路 800a 的構件可以與相關圖 2 的 ESD 電路 200 所敘述的實施例相稱。該 ESD 電路 800a 的各種構件可被相關圖 3-7 所敘述者的替代構件所取代。

**【0039】** 圖 8b 係概要地描繪根據各種實施例的 ESD 電路 800b 的一替代的配置。該 ESD 電路 800b 可以代表圖 2 的 ESD 電路 200 的一簡化的配置，其中電晶體 M2、M3 以及節點 n2 已經從該電路被省略。在某些實施例中，該 ESD 電路 800b 可以進一步加以簡化。例如，藉由電晶體 M4、M6 及 M7 所形成的門鎖在某些實施例中可以是選配的，且/或可被其它適當的電路所取代。

**【0040】** 圖 9 係針對根據各種實施例的圖 2 的 ESD 電路 200 概要地描繪一供應電壓節點(例如，VDD)相對於時間的電流(I)的一範例圖 900。該電流係以微安培( $\mu$ A)來加以表示，並且時間係以微秒( $\mu$ s)來加以表示。在該圖 900 中，該電流係代表一種具有 1 微秒的上升時間以及一 20 歐姆的串聯電阻  $R_s$  之 5V 電源的湧入電流。

**【0041】** 如同可見的，該電流的波峰是在  $250\mu$ A 或是較低的。該供

應電壓(例如，ESD 電路 200 的 VDD)可以到達一大約 5.5V 的波峰電壓，並且可以在無如同可能會發生於包含多個反相器的 ESD 電路的振盪下快速地放電。一在時間上的第一波峰可以對應於該第一時間期間(例如， $\tau_1$ )，並且在時間上的第二波峰可以對應於該第二時間期間(例如， $\tau_2$ )。該電流係在該門鎖節點變為高的，而將節點 n3 拉向 GND 的約  $1\mu\text{s}$  時下降到約  $0\mu\text{A}$ 。

**【0042】** 圖 10 係針對於根據各種實施例的圖 2 的 ESD 電路 200 概要地描繪各種節點的電壓相對於時間的一範例圖 1000。尤其，VDD、第一節點 n1、第二節點 n2 以及第三節點 n3 的電壓係被描繪。該電壓係以伏特(V)來加以表示，並且時間係以 $\mu\text{s}$ 來加以表示。該圖 1000 可以代表根據相關圖 2 的 ESD 電路 200 所敘述的第二實施例的一種配置的響應於一人體模型 ESD 事件之電壓相對於時間。

**【0043】** 參照圖 2 及 10，最初一 ESD 脈衝係以一  $10\text{ns}$  上升時間來施加，此係使得 VDD 快速地增高到一約 5.5V 的波峰。該第一節點 n1 的一電壓可以因為該第一時間期間(例如， $\tau_1=180\text{ns}$ )而延遲在後，此係使得該第二節點 n2 的一電壓追蹤 VDD 向上並且接著向下。該第三節點 n3 的一電壓可以藉由該第三電晶體 M3 而被拉高至大約 3.7V，此係導通該第五電晶體 M5。電流可能會具有藉由一 2000V 人體模型 ESD 事件所決定之約 1.33 安培(A)(例如， $ID=2000\text{V}/1.5\text{K}\Omega$ )的一波峰。VDD 開始快速地從該波峰電壓衰減，此係關斷該第三電晶體 M3。該第三節點 n3 係根據該第二時間期間(例如， $\tau_2=1.23\mu\text{s}$ )從其波峰衰減，其係在關斷該第五電晶體 M5 之前完全放電該外部的 ESD 電容。當 VDD 下降到低於該第一節點的波峰電壓的大約兩倍(例如，約 2.4V)時，該第二節點 n2 的電壓可以快速地切換成低的。

【0044】 圖 11 是根據各種實施例的一種用於製造或設計 ESD 電路之方法 1100 的流程圖。該方法 1100 可以與相關圖 1-10 所敘述的實施例相稱。

【0045】 在 1102，該方法 1100 可包含將一第一節點(例如，圖 2-8 的第一節點 n1)和一供應電壓節點(例如，圖 2-7 的 VDD 或是圖 8a 的 VSS)以及一接地節點(例如，圖 2-8 的 GND)耦接。在 1104，該方法 1100 可包含將一第一電晶體(例如，圖 2-7 的第一電晶體 M1 或是圖 8a 的第二電晶體 M2)和該第一節點及供應電壓節點耦接。在 1106，該方法 1100 可包含將一第二電晶體(例如，圖 2-7 的第二電晶體 M2 或是圖 8a 的第一電晶體 M1)和該第一節點及接地節點耦接。在 1108，該方法 1100 可包含將一第二節點(例如，圖 2-8 的第二節點 n2)與該第一電晶體及第二電晶體耦接。在 1110，該方法 1100 可包含將一第三電晶體(例如，圖 2-5、8 的第三電晶體 M3、或是圖 6 的三井的電晶體 TWL 或 SOI 電晶體、或是圖 7 的雙載子電晶體 Q1)與該第二節點耦接。

【0046】 在 1112，該方法 1100 可包含將一第三節點(例如，圖 2-8 的第三節點 n3)和該第三電晶體耦接。在 1114，該方法 1100 可包含將一第四電晶體(例如，圖 2-8 的第四電晶體 M4)和該第三節點耦接。在 1116，該方法 1100 可包含將一第五電晶體(例如，圖 2-8 的第五電晶體 M5)和該第三節點耦接。在 1118，該方法 1100 可包含將一第六電晶體(例如，圖 2-8 的第六電晶體 M6)和該第三節點耦接。在 1120，該方法 1100 可包含將一第七電晶體(例如，圖 2-8 的第七電晶體 M7)和該第三節點耦接。

【0047】 在 1122，該方法 1100 可包含將一門鎖節點(例如，圖 2-8 的門鎖節點)和該第四電晶體、第六電晶體及第七電晶體耦接。在 1124，該方

法 1100 可包含將一或多個電阻器(例如，圖 2-3、8 的 R1 及/或 R2)或電容器(例如，圖 2-4、8 的 C1 及/或 C2)耦接至該第一節點及第三節點的一或兩者。在 1126，該方法 1100 可包含將一或多個額外的電晶體(例如，圖 3-7 的第八電晶體 M8、圖 4-7 的第九電晶體 M9、圖 5-7 的第十電晶體 M10、或是圖 5-7 的第十一電晶體 M11)耦接至該第一節點及第三節點的一或兩者。

**【0048】** 各種的操作係以一種最有助於理解所主張的標的之方式被描述為多個依序的離散的操作。然而，該說明的順序不應該被解釋為意指這些操作一定是順序相依的。尤其，這些操作可以不用該呈現的順序來加以執行。所敘述的操作可以用和該所述的實施例不同的順序來加以執行。在另外的實施例中，各種額外的操作可加以執行，且/或所敘述的操作可被省略。

**【0049】** 在此所述的 ESD 電路的實施例以及包含此種 ESD 電路的裝置(例如，圖 1 的晶粒 100)可被納入各種其它的裝置及系統內。圖 12 係概要地描繪根據各種實施例的一種包含一具有 ESD 電路(例如，個別的圖 2、3、4、5、6、7 或 8 的 ESD 電路 200、300、400、500、600、700 或 800)的晶粒 100 之範例的系統 1200。如同所繪的，該系統 1200 係包含一功率放大器(PA)模組 1202，其在某些實施例中可以是一射頻(RF)PA 模組。如同所繪的，該系統 1200 可包含一和該功率放大器模組 1202 耦接的收發器 1204。該功率放大器模組 1202 可包含一具有如同在此所述的 ESD 電路之晶粒 100。

**【0050】** 該功率放大器模組 1202 可以從該收發器 1204 接收一 RF 輸入信號 RFin。該功率放大器模組 1202 可以放大該 RF 輸入信號 RFin，以提供該 RF 輸出信號 RFout。該 RF 輸入信號 RFin 以及 RF 輸出信號 RFout 都可

以是一發送鏈路的部分，其在圖 12 中分別藉由 Tx-RFin 以及 Tx-RFout 來加以表示。

**【0051】** 該放大後的 RF 輸出信號 RFout 可被提供至一天線開關模組(ASM)1206，該 ASM 1206 係經由一天線結構 1208 來完成該 RF 輸出信號 RFout 的空中(OTA)發送。該 ASM 1206 亦可以經由該天線結構 1208 來接收 RF 信號，並且將接收到的 RF 信號 Rx 沿著一接收鏈路以耦接至該收發器 1204。

**【0052】** 在各種的實施例中，該天線結構 1208 可包含一或多個定向及/或全向的天線，其例如包含一雙極天線、一單極天線、一貼片天線、一環形天線、一微帶天線或是任何其它類型的適合用於 RF 信號的 OTA 發送/接收之天線。

**【0053】** 該系統 1200 可以是任何包含功率放大的系統。該晶粒 100 的電路可以提供一用於包含例如是交流(AC)-直流(DC)轉換器、DC-DC 轉換器、DC-AC 轉換器、與類似者的電源調節應用的電源開關應用之有效的開關裝置。在各種的實施例中，該系統 1200 對於在高射頻功率及頻率下的功率放大而言可以是特別有用的。例如，該系統 1200 可以是適合用於地面及衛星通訊、雷達系統中的任一或多個、並且可能適合用於各種的產業應用及醫療應用中。更明確地說，在各種的實施例中，該系統 1200 可以是一雷達裝置、一衛星通訊裝置、一行動手機、一行動電話基地台、一廣播無線電、或是一電視放大器系統中之一所選的一個。

**【0054】** 儘管某些實施例已經為了說明之目的而在此被描繪及敘述，但是經推測用以達成相同的目的之廣泛而多樣的替代及/或等同的實施

例或實施方式亦可以取代所展示及敘述的實施例，而不脫離本揭露內容的範疇。此申請案係欲涵蓋在此論述的實施例的任何調適或變化。因此，明顯所要的是在此所述的實施例僅受限於申請專利範圍及其等同物。

### 【符號說明】

#### 【0055】

100 晶粒

102 ESD 箔制電路

104 電源連線

106 接地連線

110 其它電路

200 ESD 電路

300 ESD 電路

400 ESD 電路

500 ESD 電路

600 ESD 電路

700 ESD 電路

800a ESD 電路

800b ESD 電路

900 圖

1000 圖

1100 方法

1102 步驟

1104 步驟

1106 步驟

1108 步驟

1110 步驟

1112 步驟

1114 步驟

1116 步驟

1118 步驟

1120 步驟

1122 步驟

1124 步驟

1126 步驟

1200 系統

1202 功率放大器(PA)模組

1204 收發器

1206 天線開關模組(ASM)

1208 天線結構

M1 第一電晶體

M2 第二電晶體

M3 第三電晶體

M4 第四電晶體

M5 第五電晶體

M6 第六電晶體

M7 第七電晶體

M8 第八電晶體

M9 第九電晶體

M10 第十電晶體

M11 第十一電晶體

n1 第一節點

n2 第二節點

n3 第三節點

Q1 雙載子電晶體

TWL 三井的電晶體

圖式

圖1

圖2

圖3

圖4

圖5

圖6

圖7

圖8a

圖8b

圖9

圖10

圖11

圖12

107年09月14日修正替換頁

# 發明專利說明書

(本說明書格式、順序，請勿任意更動)

## 【發明名稱】(中文/英文)

靜電放電電路、製造方法和系統

ELECTROSTATIC DISCHARGE (ESD) CIRCUITRY, FABRICATING METHOD AND SYSTEM

## 【技術領域】

【0001】 本揭露內容的實施例係大致有關於積體電路的領域，並且更具體而言係有關於靜電放電(ESD)電路及相關的技術。

## 【先前技術】

【0002】 目前的靜電放電(ESD)電路可能會在電源供應器具有一快速的上升時間之際遭受到一高的湧入(in-rush)電流，並且在某些情形中可能會在晶片的正常操作期間遭受到來自增益回授的振盪。對於快速上升的電源提供具有降低的湧入電流的穩定的 ESD 保護之技術及配置可能是所期望的。

## 【發明內容】

【0003】 本發明的一實施例是一種靜電放電(ESD)電路，其係包括：一和一供應電壓節點以及一接地節點耦接的第一節點；一和該第一節點以及該供應電壓節點耦接的第一電晶體；一和該第一節點以及該接地節點耦接的第二電晶體；一和該第一電晶體以及該第二電晶體耦接的第二節點；一和該第二節點耦接的第三電晶體；以及一和該第三電晶體耦接的第三節點，其中一用以充電該第一節點的第一時間期間係小於一用以放電該第三節點的第二時間期間。

【0004】 本發明的另一實施例是一種製造靜電放電(ESD)電路之方

107年09月14日修正替換頁

法，其係包括：將一第一節點和一供應電壓節點以及一接地節點耦接；將一第一電晶體和該第一節點以及該供應電壓節點耦接；將一第二電晶體和該第一節點以及該接地節點耦接；將一第二節點和該第一電晶體以及該第二電晶體耦接；將一第三電晶體和該第二節點耦接；以及將一第三節點和該第三電晶體耦接，其中一用以充電該第一節點的第一時間期間係小於一用以放電該第三節點的第二時間期間。

**【0005】** 本發明的另一實施例是一種系統，其係包括：一包含一晶粒的功率放大器模組，該晶粒係包含：一被配置以提供一用於該晶粒的操作的供應電壓節點的電源連線；一被配置以提供一接地節點的接地連線；以及一和該供應電壓節點以及該接地節點耦接的靜電放電(ESD)箝制電路，該ESD 箝制電路係包括：一和該供應電壓節點以及該接地節點耦接的第一節點；一和該第一節點以及該供應電壓節點耦接的第一電晶體；一和該第一節點以及該接地節點耦接的第二電晶體；一和該第一電晶體以及該第二電晶體耦接的第二節點；一和該第二節點耦接的第三電晶體；以及一和該第三電晶體耦接的第三節點，其中一用以充電該第一節點的第一時間期間係小於一用以放電該第三節點的第二時間期間。

### **【圖式簡單說明】**

**【0006】** 實施例將會藉由以下結合所附的圖式的詳細說明而輕易地加以理解。為了有助於此說明，類似的元件符號係指類似的結構元件。實施例係在所附的圖式的圖中藉由舉例而非藉由限制性地加以描繪。

圖 1 係概要地描繪根據各種實施例的一包含靜電放電(ESD)電路的晶粒。

I660552

107年09月14日修正替換頁

## 發明摘要

※ 申請案號：103133200

※ 申請日：103/09/25

公告本

※IPC 分類：*H02H 9/04 (2006.01)*

## 【發明名稱】(中文/英文)

靜電放電電路、製造方法和系統

ELECTROSTATIC DISCHARGE (ESD) CIRCUITRY, FABRICATING

METHOD AND SYSTEM

## 【中文】

本揭露內容的實施例係描述靜電放電(ESD)電路以及相關的技術與配置。在一實施例中，ESD 電路係包含一和一供應電壓節點以及一接地節點耦接的第一節點、一和該第一節點以及該供應電壓節點耦接的第一電晶體、一和該第一節點以及該接地節點耦接的第二電晶體、一和該第一電晶體以及該第二電晶體耦接的第二節點、一和該第二節點耦接的第三電晶體、以及一和該第三電晶體耦接的第三節點，其中一用以充電該第一節點的第一時間期間係小於一用以放電該第三節點的第二時間期間。其它實施例亦可能被描述及/或主張。

## 【英文】

Embodiments of the present disclosure describe electrostatic discharge (ESD) circuitry and associated techniques and configurations. In one embodiment, ESD circuitry includes a first node coupled with a supply voltage node and a ground node, a first transistor coupled with the first node and the supply voltage node, a second

|                 |

|-----------------|

| 107年09月14日修正替換頁 |

|-----------------|

transistor coupled with the first node and the ground node, a second node coupled with the first transistor and the second transistor, a third transistor coupled with the second node and a third node coupled with the third transistor, wherein a first time period to charge the first node is less than a second time period to discharge the third node. Other embodiments may be described and/or claimed.

|                 |

|-----------------|

| 107年09月14日修正替換頁 |

|-----------------|

**【代表圖】**

【本案指定代表圖】：第（ 2 ）圖。

【本代表圖之符號簡單說明】：

200 ESD 電路

M1 第一電晶體

M2 第二電晶體

M3 第三電晶體

M4 第四電晶體

M5 第五電晶體

M6 第六電晶體

M7 第七電晶體

n1 第一節點

n2 第二節點

n3 第三節點

【本案若有化學式時，請揭示最能顯示發明特徵的化學式】：

無

107年09月14日修正替換頁

## 申請專利範圍

1.一種靜電放電(ESD)電路，其係包括：

一第一節點，其和一供應電壓節點以及一接地節點耦接；

一第一電晶體，其和該第一節點以及該供應電壓節點耦接；

一第二電晶體，其和該第一節點以及該接地節點耦接；

一第二節點，其和該第一電晶體以及該第二電晶體耦接；

一第三電晶體，其和該第二節點耦接；

一第三節點，其和該第三電晶體耦接，其中一用以充電該第一節點的第一時間期間係小於一用以放電該第三節點的第二時間期間；以及

一和該第三節點耦接的第四電晶體，其中用以放電該第三節點的該第二時間期間係開始於該第三電晶體被設定為一關斷狀態時，並且結束於該第四電晶體被設定為一導通狀態時。

2.如申請專利範圍第1項之ESD電路，其中：

該第一節點係和該第一電晶體的一閘極以及該第二電晶體的一閘極耦接；

該第二節點係和該第一電晶體的一汲極以及該第二電晶體的一汲極耦接；

該第一電晶體的一源極係和該供應電壓節點耦接；以及

該第二電晶體的一源極係和該接地節點耦接。

3.如申請專利範圍第2項之ESD電路，其中：

該第二節點係和該第三電晶體的一閘極或基極耦接；

該第三節點係和該第三電晶體的一源極或射極以及該第四電晶體的一

|                 |

|-----------------|

| 107年09月14日修正替換頁 |

|-----------------|

汲極耦接；

該第三電晶體的一汲極或集極係和該供應電壓節點耦接；以及

該第四電晶體的一源極係和該接地節點耦接。

4.如申請專利範圍第 1 項之 ESD 電路，其進一步包括：

一和該第三節點耦接的第五電晶體，其中該第三節點係和該第五電晶體的一閘極耦接；

一和該第五電晶體耦接的第六電晶體，其中該第五電晶體的該閘極係和該第六電晶體的一閘極耦接；

一和該第五電晶體耦接的第七電晶體，其中該第五電晶體的該閘極係和該第七電晶體的一閘極耦接；以及

一和該第六電晶體、第七電晶體以及第四電晶體耦接的門鎖節點，其中該門鎖節點係和該第六電晶體的一汲極、該第七電晶體的一汲極、以及該第四電晶體的一閘極耦接。

5.如申請專利範圍第 1 項之 ESD 電路，其中該第二時間期間是大於該第一時間期間至少七倍。

6.如申請專利範圍第 1 項之 ESD 電路，其中：

該第一時間期間係具有一小於 1 微秒( $\mu\text{s}$ )的值；以及

該第二時間期間係大於該第一時間期間。

7.如申請專利範圍第 1 項之 ESD 電路，其進一步包括：

一或多個耦接至該第一節點以及該第三節點中的一或兩者的電阻器或電容器，其中至少該第一節點或是該第三節點的一電阻或電容係基於該一或多個電阻器或電容器。

107年09月14日修正替換頁

8.如申請專利範圍第 1 項之 ESD 電路，其進一步包括：

一或多個和該第一節點以及該第三節點中的一或兩者耦接之額外的電晶體，其中至少該第一節點或是該第三節點的一電阻或電容係基於該一或多個額外的電晶體。

9.如申請專利範圍第 1 項之 ESD 電路，其中該第三電晶體是一個三井的電晶體或是一絕緣體上矽(SOI)電晶體。

10.一種製造靜電放電(ESD)電路之方法，其係包括下列步驟：

將一第一節點和一供應電壓節點以及一接地節點耦接；

將一第一電晶體和該第一節點以及該供應電壓節點耦接；

將一第二電晶體和該第一節點以及該接地節點耦接；

將一第二節點和該第一電晶體以及該第二電晶體耦接；

將一第三電晶體和該第二節點耦接；

將一第三節點和該第三電晶體耦接，其中一用以充電該第一節點的第一時間期間係小於一用以放電該第三節點的第二時間期間；以及

將一第四電晶體和該第三電晶體耦接，其中用以放電該第三節點的該第二時間期間係開始於該第三電晶體被設定為一關斷狀態時，並且結束於該第四電晶體被設定為一導通狀態時。

11.如申請專利範圍第 10 項之方法，其中：

該第一節點係和該第一電晶體的一閘極以及該第二電晶體的一閘極耦接；

該第二節點係和該第一電晶體的一汲極以及該第二電晶體的一汲極耦接；

107年09月14日修正替換頁

該第一電晶體的一源極係和該供應電壓節點耦接；以及

該第二電晶體的一源極係和該接地節點耦接。

12.如申請專利範圍第 11 項之方法，其中：

該第二節點係和該第三電晶體的一閘極或基極耦接；

該第三節點係和該第三電晶體的一源極或射極以及該第四電晶體的一汲極耦接；

該第三電晶體的一汲極或集極係和該供應電壓節點耦接；以及

該第四電晶體的一源極係和該接地節點耦接。

13.如申請專利範圍第 10 項之方法，其進一步包括下列步驟：

將一第五電晶體和該第三節點耦接，其中該第三節點係和該第五電晶體的一閘極耦接；

將一第六電晶體和該第五電晶體耦接，其中該第五電晶體的該閘極係和該第六電晶體的一閘極耦接；

將一第七電晶體和該第五電晶體耦接，其中該第五電晶體的該閘極係和該第七電晶體的一閘極耦接；以及

將一門鎖節點和該第六電晶體、第七電晶體以及第四電晶體耦接，其中該門鎖節點係和該第六電晶體的一汲極、該第七電晶體的一汲極、以及該第四電晶體的一閘極耦接。

14.如申請專利範圍第 10 項之方法，其中該第二時間期間是大於該第一時間期間至少七倍。

15.如申請專利範圍第 10 項之方法，其中：

該第一時間期間是小於 1 微秒( $\mu\text{s}$ )；以及

107年09月14日修正替換頁

該第二時間期間是大於該第一時間期間。

16.如申請專利範圍第 10 項之方法，其進一步包括下列步驟：

將一或多個電阻器或電容器耦接至該第一節點以及該第三節點中的一或兩者，其中至少該第一節點或是該第三節點的一電阻或電容是基於該一或多個電阻器或電容器。

17.如申請專利範圍第 10 項之方法，其進一步包括下列步驟：

將一或多個額外的電晶體和該第一節點以及該第三節點中的一或兩者耦接，其中至少該第一節點或是該第三節點的一電阻或電容是基於該一或多個額外的電晶體。

18.一種靜電放電(ESD)系統，其係包括：

一包含一晶粒的功率放大器模組，該晶粒係包含：

一被配置以提供一用於該晶粒的操作的供應電壓節點的電源連線；

一被配置以提供一接地節點的接地連線；以及

一和該供應電壓節點以及該接地節點耦接的靜電放電(ESD)箝制電路，該 ESD 箝制電路係包括：

一和該供應電壓節點以及該接地節點耦接的第一節點；

一和該第一節點以及該供應電壓節點耦接的第一電晶體；

一和該第一節點以及該接地節點耦接的第二電晶體；

一和該第一電晶體以及該第二電晶體耦接的第二節點；

一和該第二節點耦接的第三電晶體；

一和該第三電晶體耦接的第三節點，其中一用以充電該第一

107年09月14日修正替換頁

節點的第一時間期間係小於一用以放電該第三節點的第二時間期間；以及

一和該第三電晶體耦接的第四電晶體，其中用以放電該第三節點的該

第二時間期間係開始於該第三電晶體被設定為一關斷狀態時，並且結束於

該第四電晶體被設定為一導通狀態時。