(12) 特許協力条約に基づいて公開された国際出願

(19) 世界知的所有権機関

国際事務局

(43) 国際公開日

2020年1月30日(30.01.2020)

W I P O I P C T

圓\_\_\_\_\_

關\_1\_11 圓1\_1

(10) 国際公開番号

¥0 2020 /022054 入1

(51) 国際特許分類 :

H01L 27/146 (2006.01) H04N 5/3745 (2011.01)

神奈川県厚木市旭町四丁目14番

1号 Kanagawa (JP).

(21) 国際出願番号 :

PCT/JP2019/027260

(72) 発明者 : 熊谷至通 (KUMAGAI Yoshimichi);

(22) 国際出願日 :

2019年7月10日(10.07.2019)

〒2430014 神奈川県厚木市旭町四丁目14番

1号 ソニーセミコンダクタソリューションズ

(25) 国際出願の言語 :

日本語

株式会社内 Kanagawa (JP). 阿部高志 (ABE

Takashi);

(26) 国際公開の言語 :

日本語

旭町四丁目14番1号 ソニーセミコンダクタソリュ

ー・ソニーセミコンダクタソリューションズ株式会社内

Kanagawa (JP). 吉田遼人 (YOSHITA Kyoto);

(30) 優先権データ :

特願 2018-138644 2018年7月24日(24.07.2018) JP

〒2430014 神奈川県厚木市旭町四丁目14番

1号 ソニーセミコンダクタソリューションズ株式会社内

Kanagawa (JP). 福井僚 (FUKUI Ryo);

特願 2018-142341 2018年7月30日(30.07.2018) JP

旭町四丁目14番1号 ソニーセミコンダクタソリュ

ー・ソニーセミコンダクタソリューションズ株式会社内

Kanagawa (JP).

(71) 出願人 : ソニーセミコンダクタソリューションズ株式会社 (SONY SEMICONDUCTOR SOLUTIONS CORPORATION) [JP/JP]; 〒2430014

(54) Title: IMAGING DEVICE AND ELECTRONIC EQUIPMENT

(54) 発明の名称 : 撮像装置、電子機器

(57) Abstract: The present technology pertains to: an imaging device that enables photographing by a global shutter method without decreasing the electric charge amount of a saturation signal; and electronic equipment. This imaging device is provided with: pixels each including a photoelectric conversion unit for converting received light to an electric charge and a holding unit for holding the electric charge transferred from the photoelectric conversion unit; floating diffusions shared by a plurality of the pixels and holding the electric charges transferred from the respective holding units; and a

WO 2019/022054 A1

(74) 代理人: 西川 孝, 外 (NISHIKAWA Takashi et al.); 〒1600023 東京都新宿区西新宿 7 丁目 5 番 25 号 西新宿プライムスクエア 9 階 Tokyo (JP).

(81) 指定国(表示のない限り、全ての種類の国内保護が可能): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JO, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) 指定国(表示のない限り、全ての種類の広域保護が可能): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), ユーラシア (AM, AZ, BY, KG, KZ, RU, TJ, TM), ヨーロッパ (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

添付公開書類 :

- 國際調査報告 (條約第21条(β))

---

boosting line for boosting the floating diffusions. The present technology is applicable, for example, to a photographing device that performs photographing by the global shutter method.

67)要約 :本技術は、飽和信号電荷量を低下させずにグローバルシャッタ方式で撮影できるようにする撮像装置、電子機器に関する。受光した光を電荷に変換する光電変換部と、光電変換部から転送された電荷を保持する保持部とを含む画素と、複数の画素で共有され、保持部から転送された電荷を保持するフローテイングディフュージョンと、フローテイングディフュージョンを昇圧する昇圧線とを備える。本技術は、例えば、グローバルシャッタ方式で撮影を行う撮影装置に適用できる。

## 明 細 書

発明の名称：撮像装置、電子機器

技術分野

[0001] 本技術は撮像装置、電子機器に関し、例えば、グローバルシャッタ方式で撮影する際に適用して好適な撮像装置、電子機器に関する。

背景技術

[0002] CMOS (Complementary Metal Oxide Semiconductor) イメージセンサやCCD (Charge Coupled Device) などの撮像素子は、デジタルスチルカメラやデジタルビデオカメラなどに広く用いられている。

[0003] 例えば、CMOSイメージセンサに入射した光は、画素が有するPD (Photodiode : フォトダイオード)において光電変換される。そして、PDで発生した電荷が、転送トランジスタを介してFD (Floating Diffusion : フローティングディフュージョン) に転送され、受光量に応じたレベルの画素信号に変換される。

[0004] ところで、従来のCMOSイメージセンサでは、一般的に各画素から画素信号を行毎に順次読み出す方式、いわゆるローリングシャッタ方式が採用されているため、露光タイミングの違いによって画像に歪みが発生することがあった。

[0005] そこで、例えば、特許文献1には、画素内に電荷保持部を設けることによって、全ての画素から画素信号を同時に読み出す方式、いわゆるグローバルシャッタ方式を採用し、全画素同時電子シャッタ機能を備えたCMOSイメージセンサが開示されている。グローバルシャッタ方式を採用することにより、露光タイミングが全ての画素で同一になり、画像に歪みが発生することを回避することができる。

先行技術文献

特許文献

[0006] 特許文献1：特開2008-103647号公報

## 発明の概要

### 発明が解決しようとする課題

- [0007] ところで近年、固体撮像装置の微細化が求められ、個々の画素サイズが縮小される傾向にある。またグローバルシャッタ方式を採用することで、画素内に電荷保持部を設けた構成の場合、フォトダイオードのサイズが縮小され飽和電荷量（○3）が低下してしまう可能性があった。

- [0008] 本技術は、このような状況に鑑みてなされたものであり、飽和信号電荷量を低下させずにグローバルシャッタ方式で撮影できるようにするものである。

### 課題を解決するための手段

- [0009] 本技術の一側面の撮像装置は、受光した光を電荷に変換する光電変換部と、前記光電変換部から転送されてきた電荷を保持する保持部とを含む画素と、複数の前記画素で共有され、前記保持部から転送されてきた電荷を保持するフローティングデイフュージョンと、前記フローティングデイフュージョンを昇圧する昇圧線とを備える。

- [0010] 本技術の一側面の電子機器は、受光した光を電荷に変換する光電変換部と、前記光電変換部から転送されてきた電荷を保持する保持部とを含む画素と、複数の前記画素で共有され、前記保持部から転送されてきた電荷を保持するフローティングデイフュージョンと、前記フローティングデイフュージョンを昇圧する昇圧線とを備える撮像装置と、前記撮像装置からの信号を処理する処理部とを備える。

- [0011] 本技術の一側面の撮像装置においては、受光した光を電荷に変換する光電変換部と、光電変換部から転送されてきた電荷を保持する保持部とを含む画素と、複数の画素で共有され、保持部から転送されてきた電荷を保持するフローティングデイフュージョンと、フローティングデイフュージョンを昇圧する昇圧線とが備えられる。

- [0012] 本技術の一側面の電子機器においては、前記撮像装置が含まれる構成とされている。

[0013] なお、撮像装置、電子機器は、独立した装置であっても良いし、1つの装置を構成している内部ブロックであっても良い。

### 発明の効果

[0014] 本技術の一側面によれば、飽和信号電荷量を低下させずにグローバルシャッタ方式で撮影できる。

[0015] なお、ここに記載された効果は必ずしも限定されるものではなく、本開示中に記載されたいずれかの効果であってもよい。

### 図面の簡単な説明

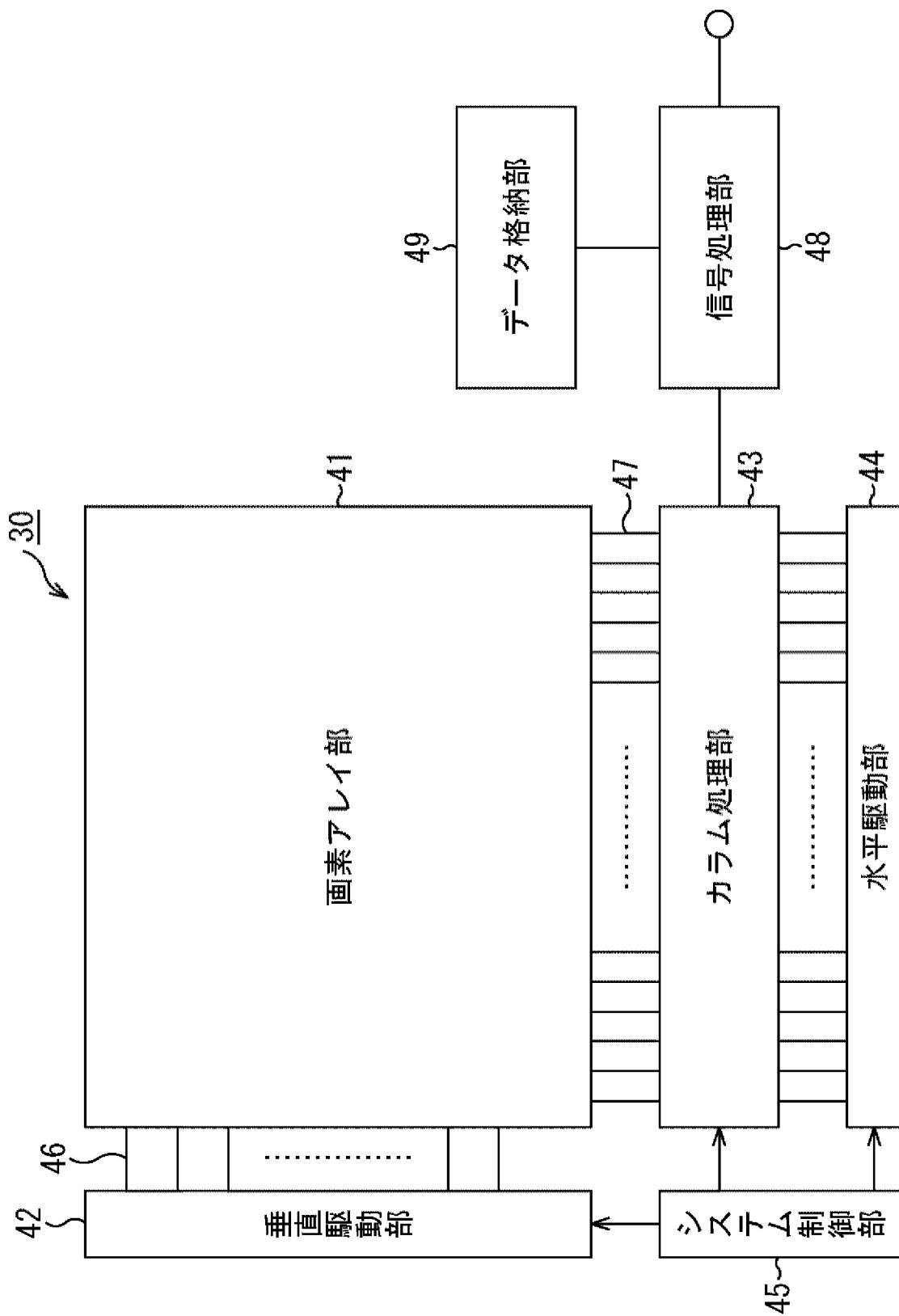

[0016] [図1]イメージセンサの構成を示す図である。

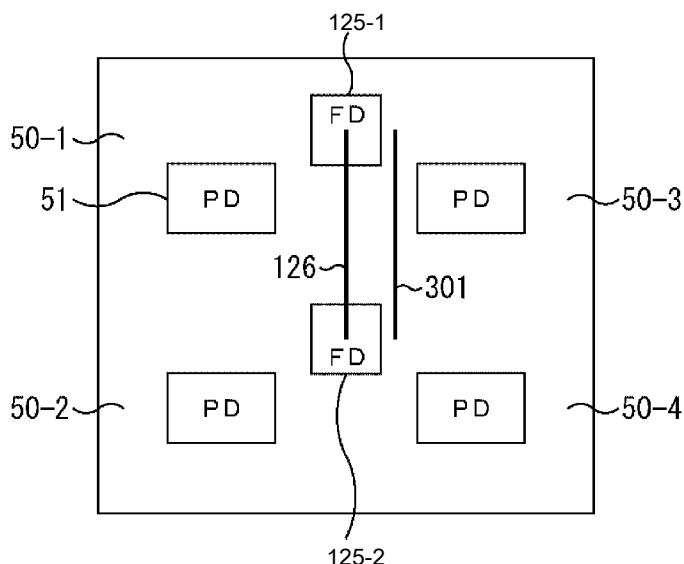

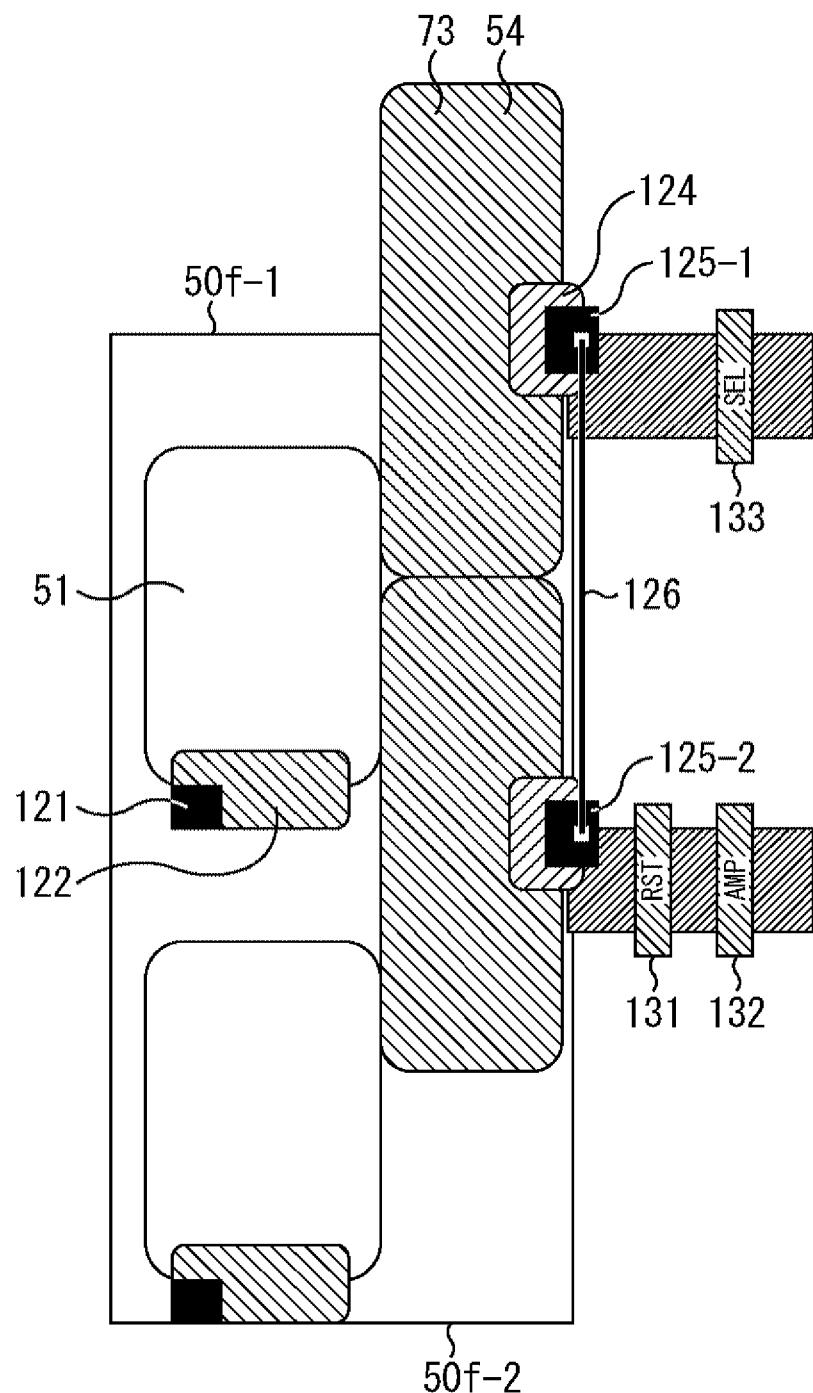

[図2]画素の構成を示す断面図である。

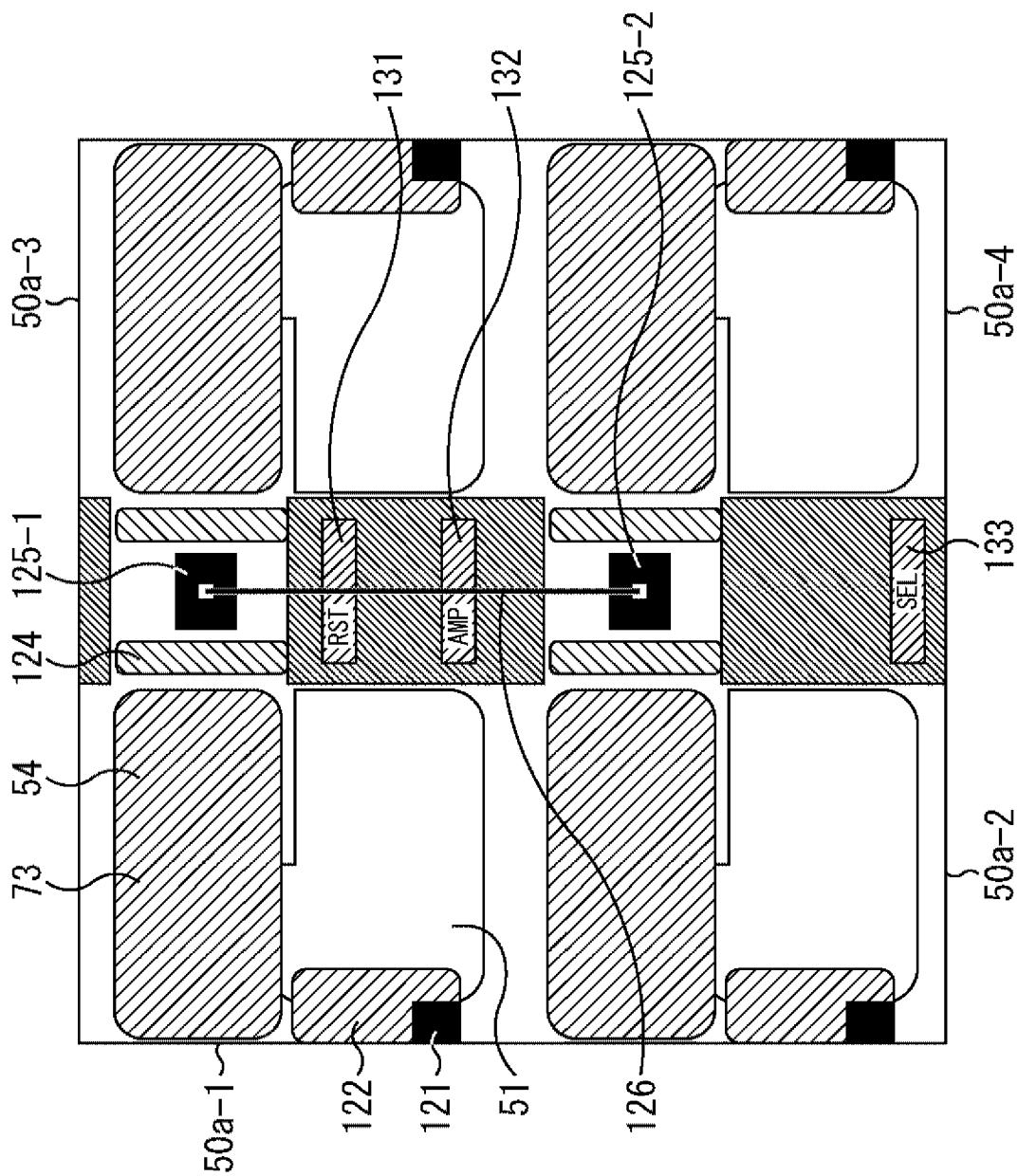

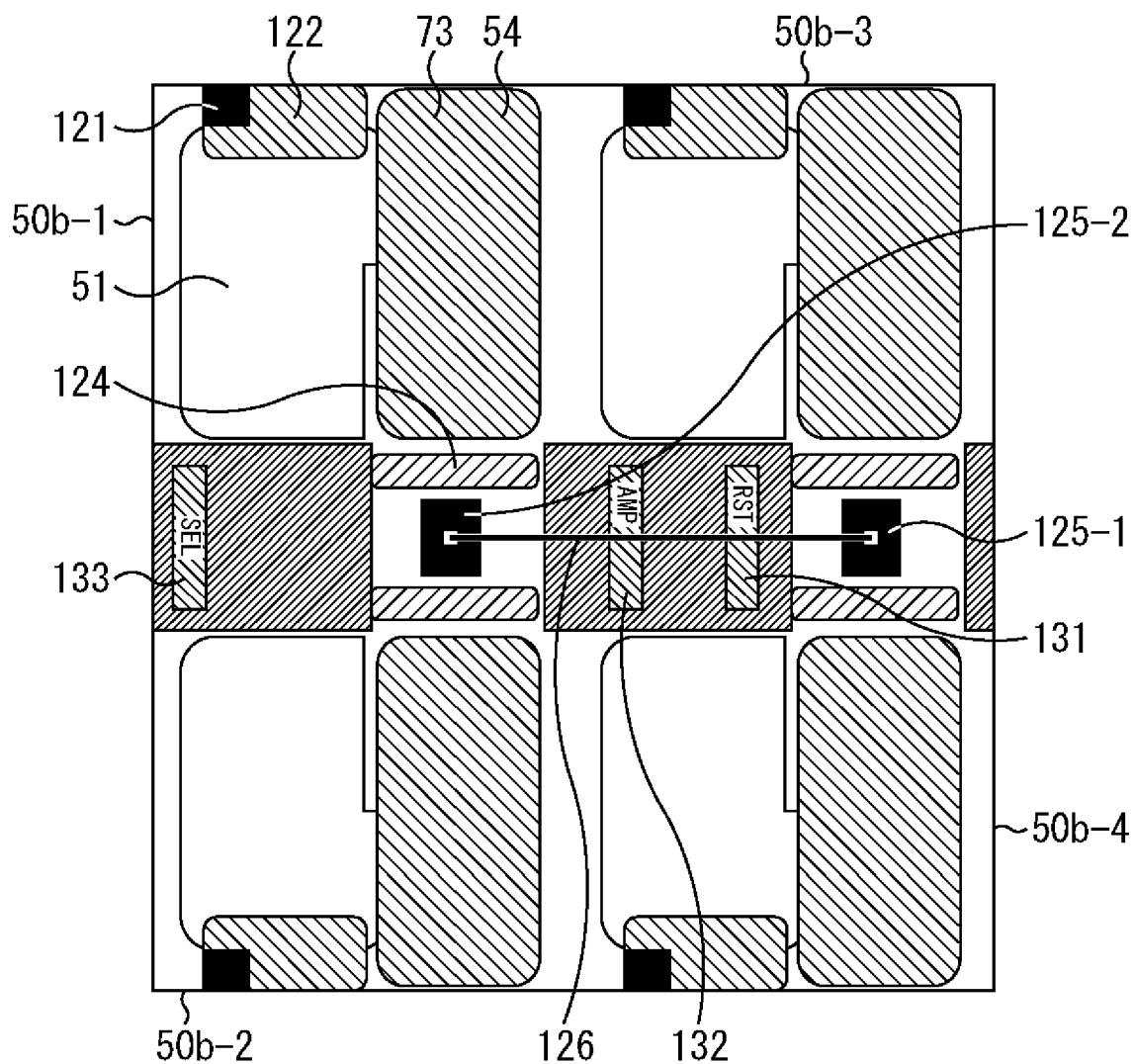

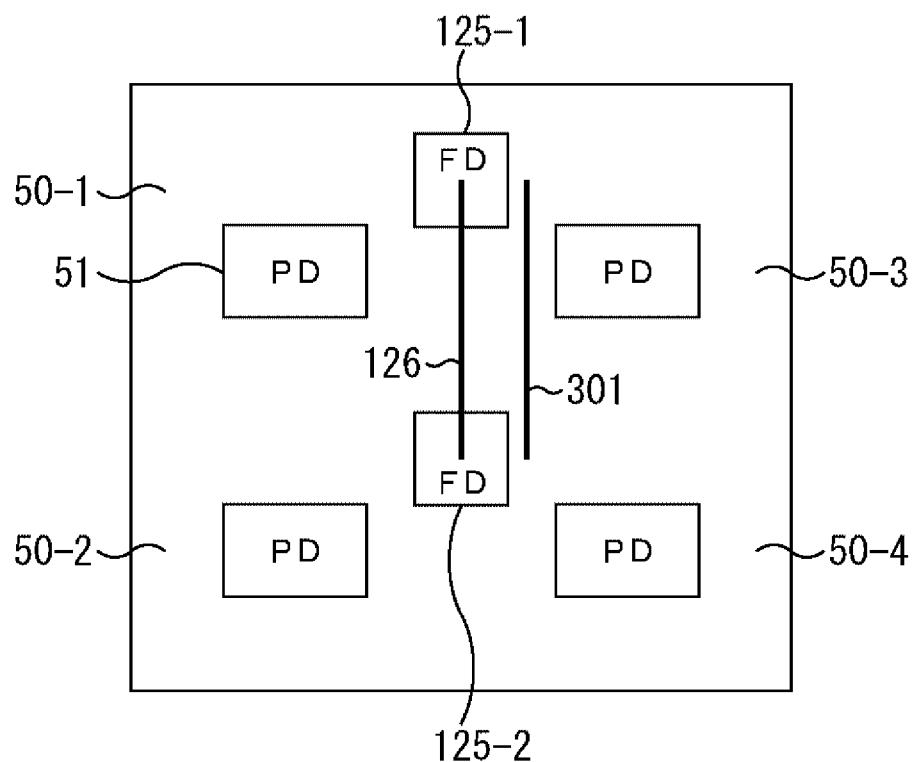

[図3]画素の構成を示す平面図である。

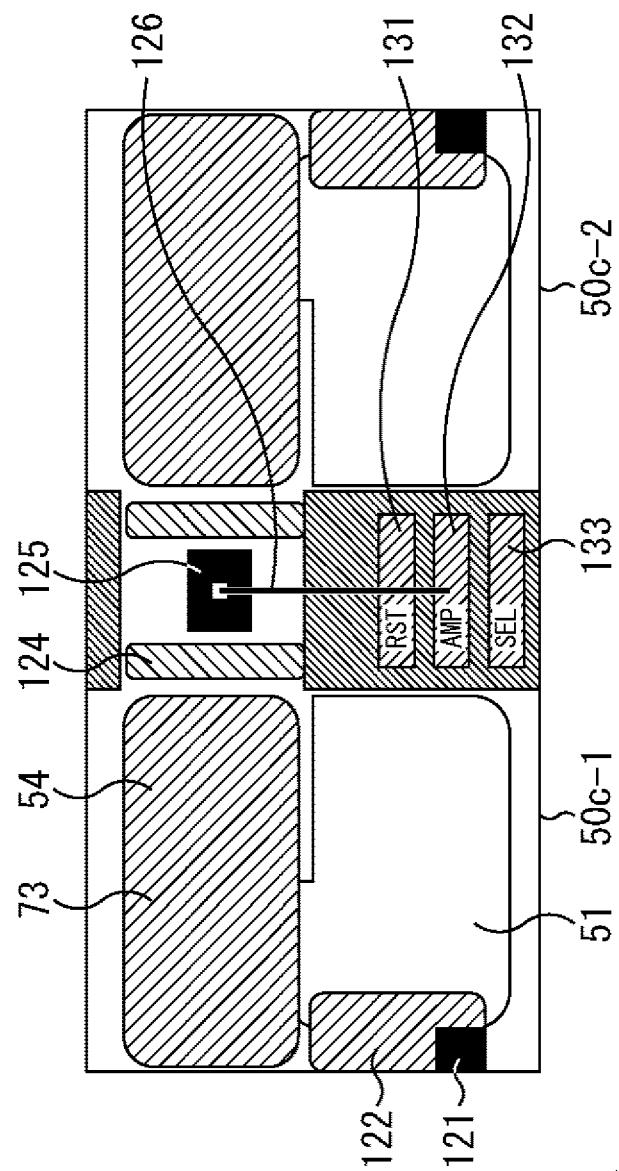

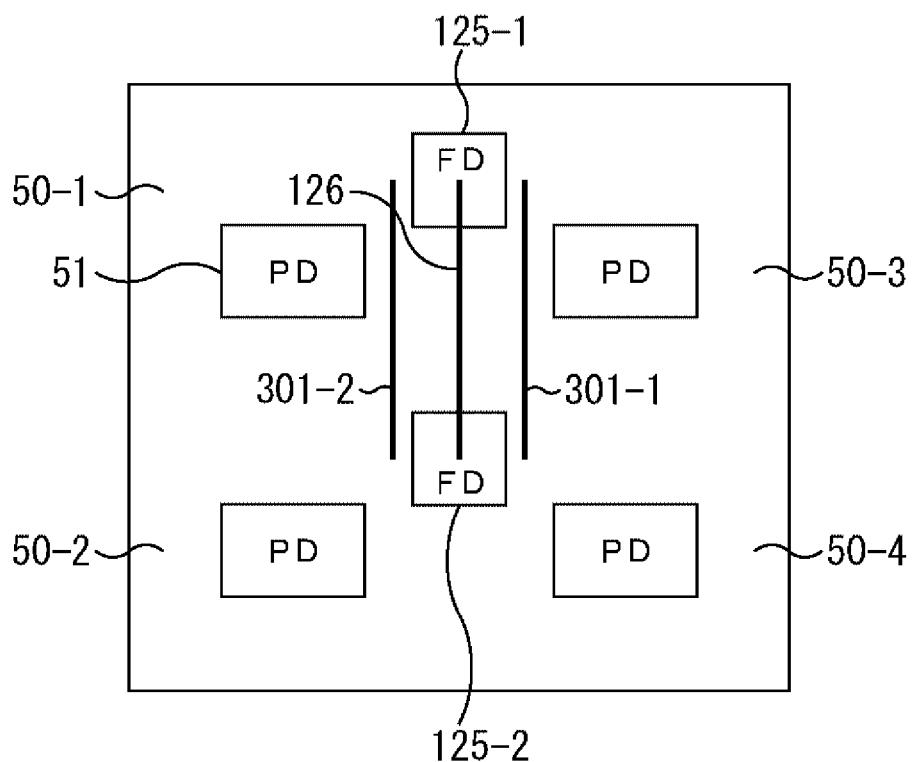

[図4]画素の他の構成を示す平面図である。

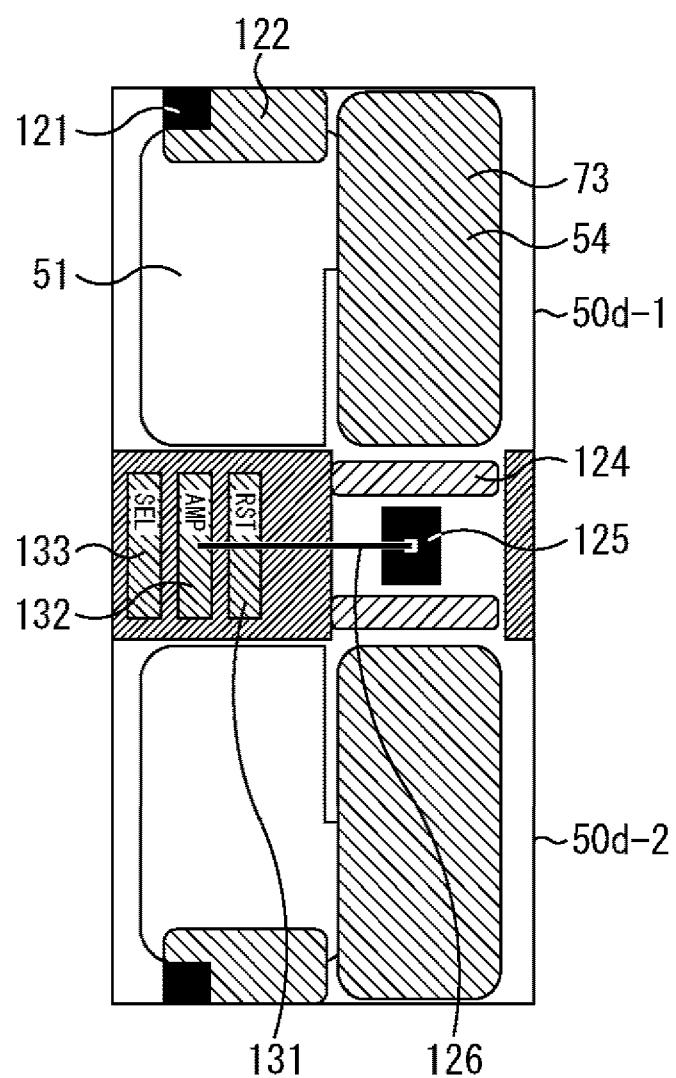

[図5]画素の他の構成を示す平面図である。

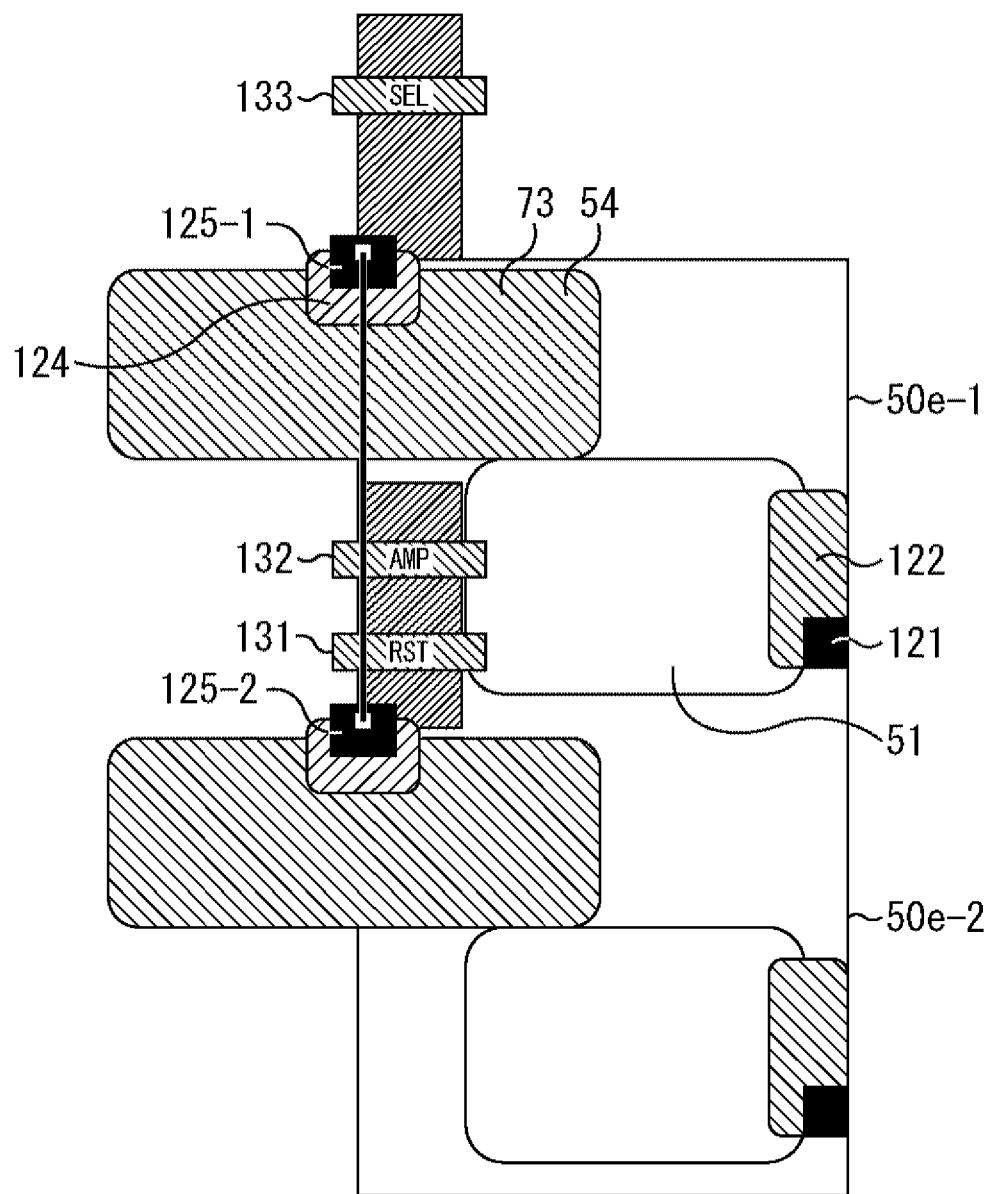

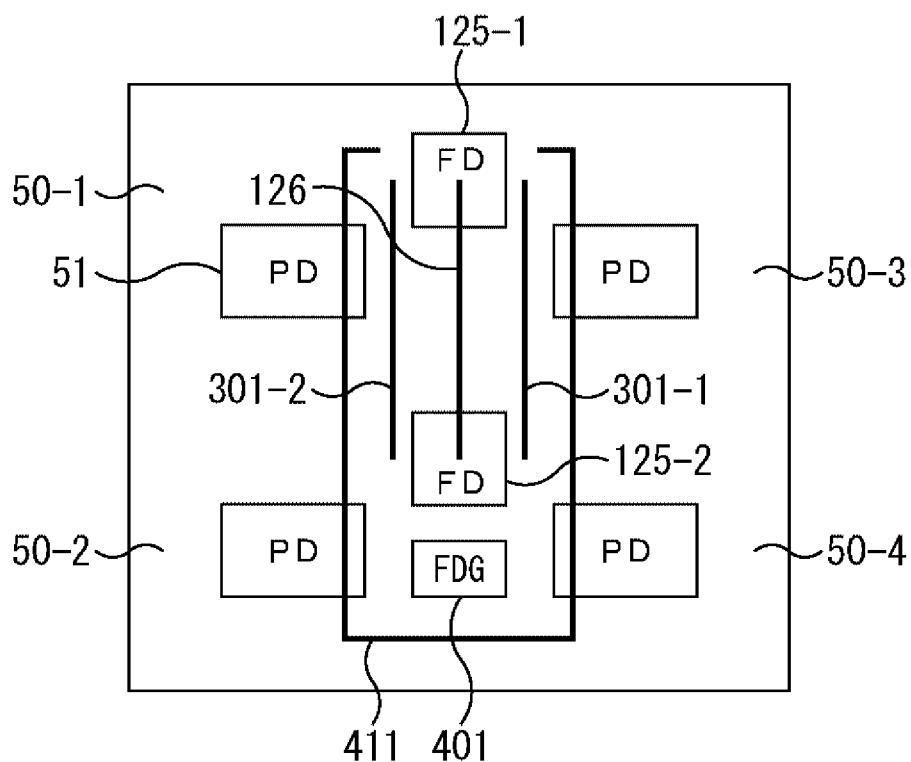

[図6]画素の他の構成を示す平面図である。

[図7]画素の他の構成を示す平面図である。

[図8]画素の他の構成を示す平面図である。

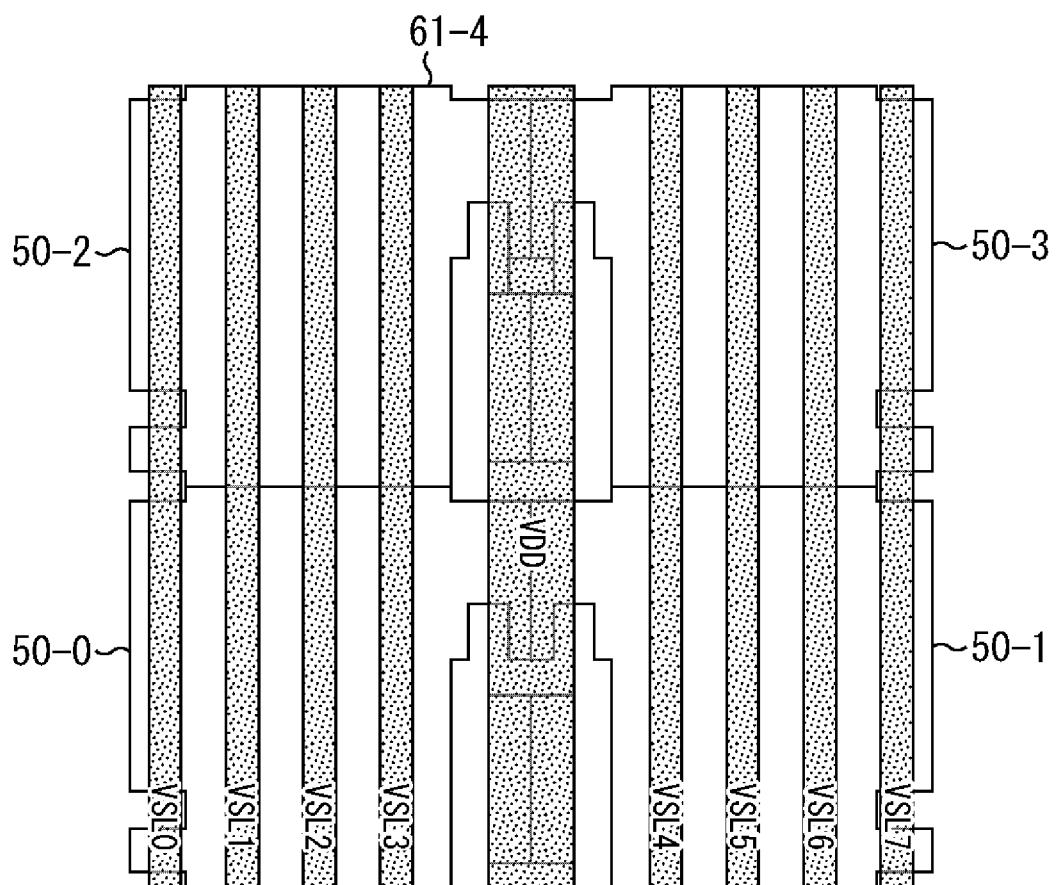

[図9]ドロップ圧配線について説明するための図である。

[図10]ドロップ圧配線について説明するための図である。

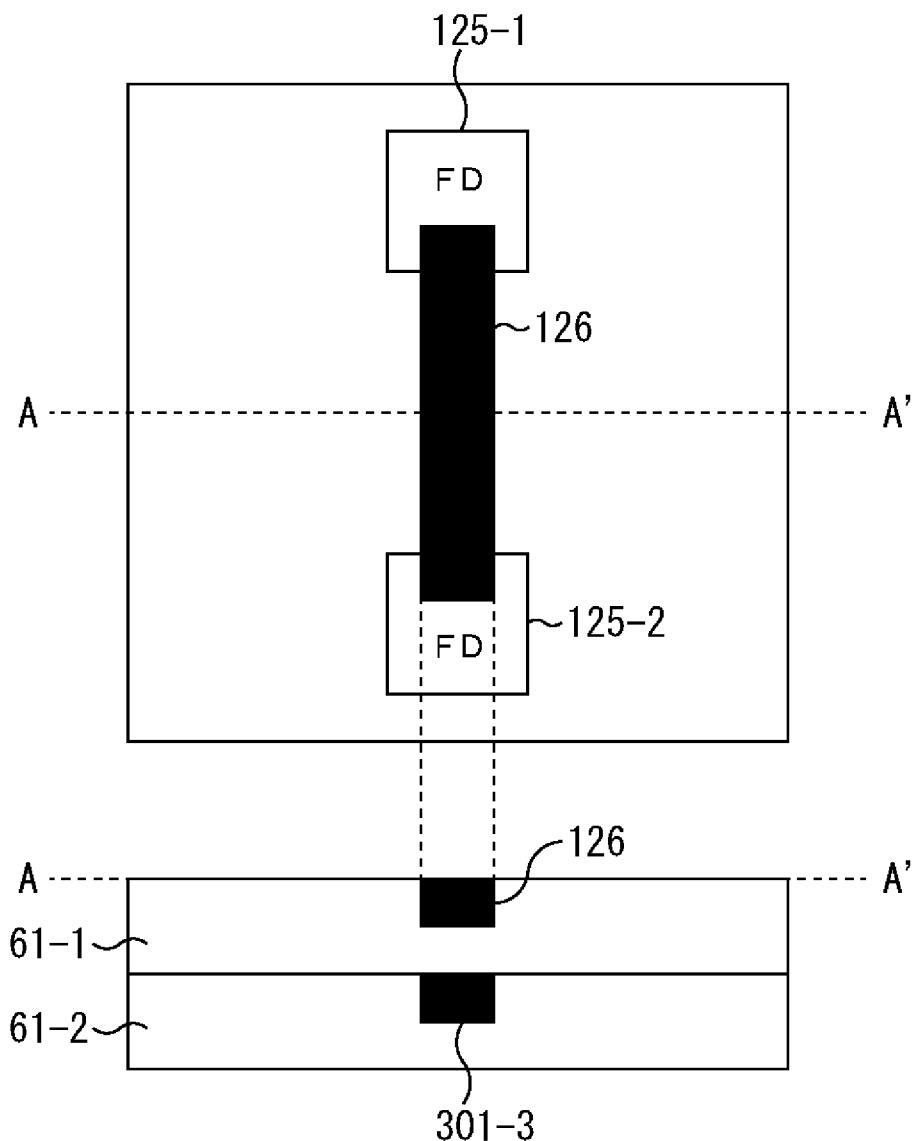

[図11]ドロップ圧配線について説明するための図である。

[図12]ドロップ圧配線について説明するための図である。

[図13]画素の構成を示す回路図である。

[図14]画素の動作を説明するための図である。

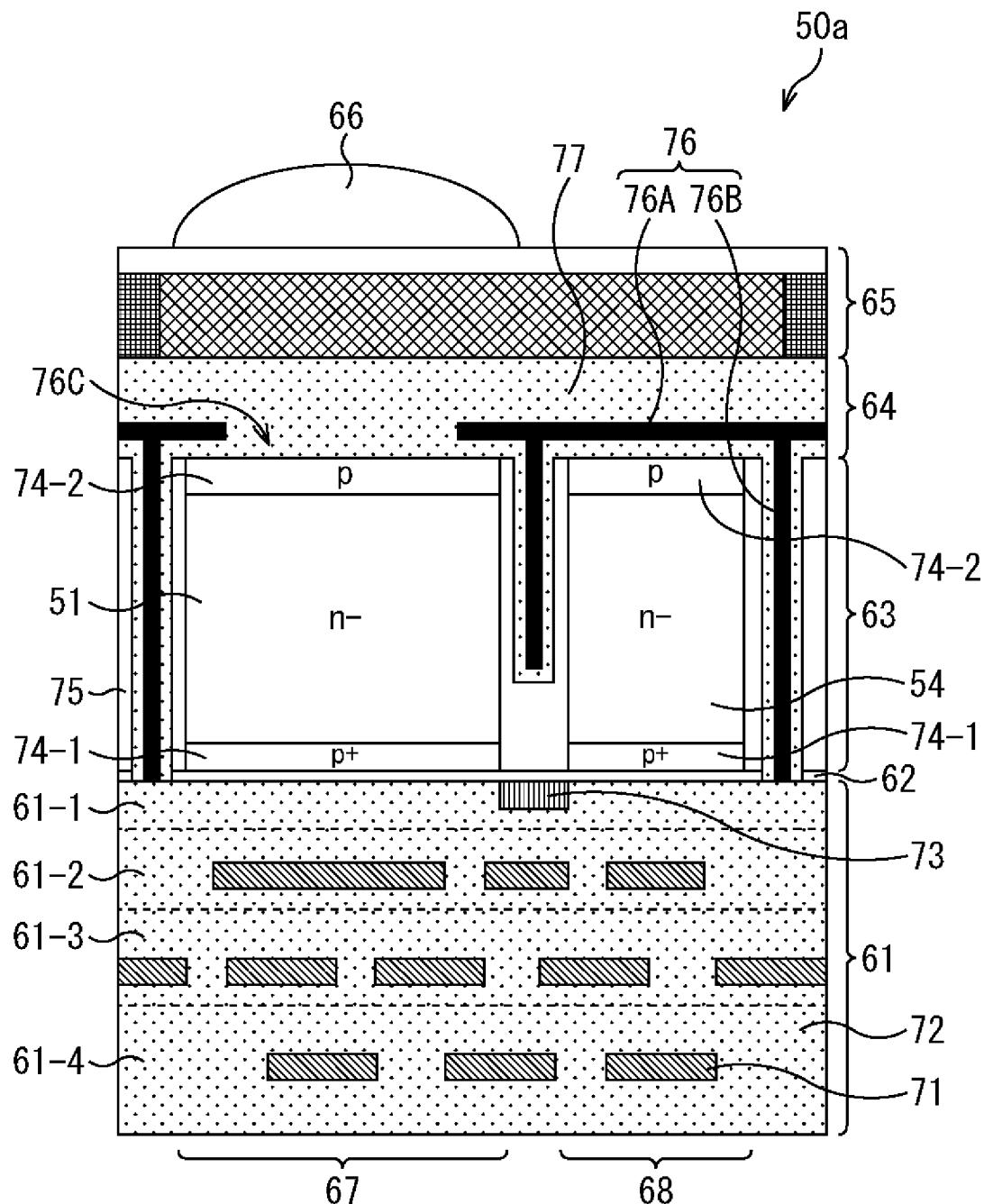

[図15]画素の構成を示す断面図である。

[図16]画素のポテンシャルの遷移について説明するための図である。

[図17]画素のポテンシャルの遷移について説明するための図である。

[図18]画素の動作を説明するための図である。

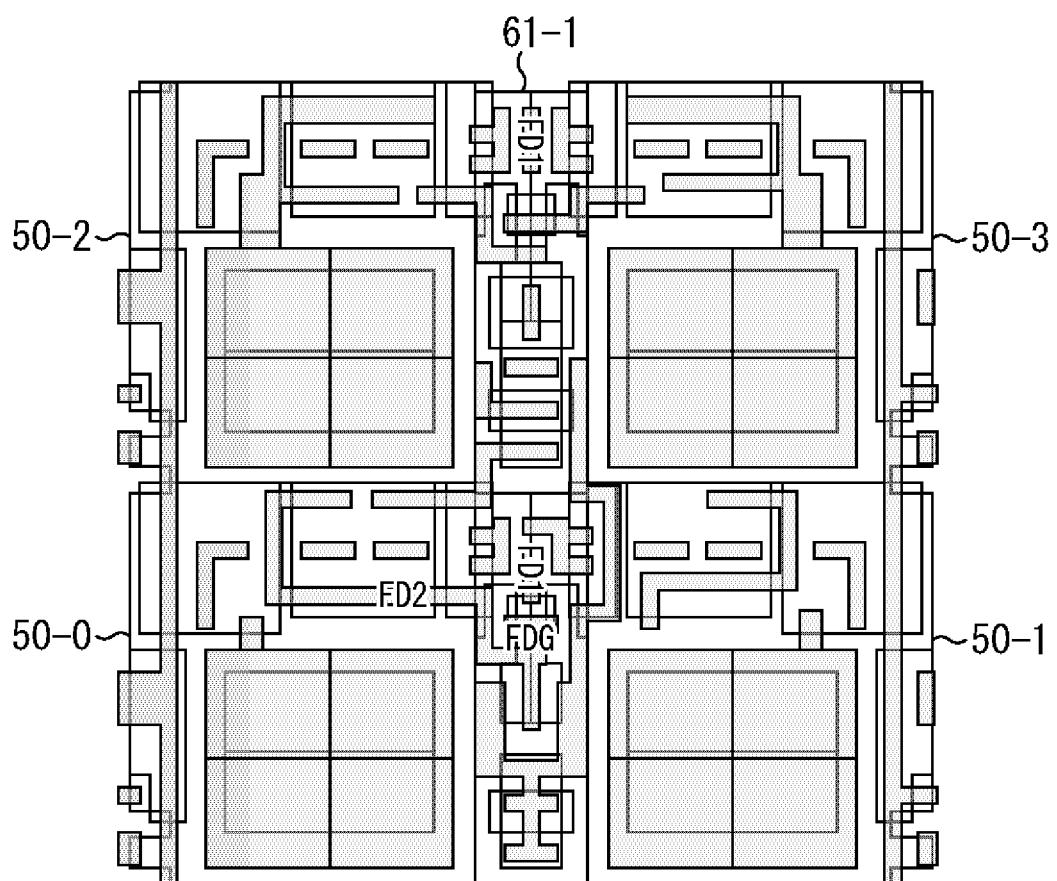

[図19]画素の配線の位置や形状について説明するための図である。

[図20]画素の構成を示す回路図である。

[図 21] 画素の配線の位置や形状について説明するための図である。

[図 22] 画素の配線の位置や形状について説明するための図である。

[図 23] 画素の配線の位置や形状について説明するための図である。

[図 24] 画素の配線の位置や形状について説明するための図である。

[図 25] 画素の構成を示す平面図である。

[図 26] 画素の構成を示す断面図である。

[図 27] 画素の他の構成を示す平面図である。

[図 28] FD 変換用配線について説明するための図である。

[図 29] 画素の配線の位置や形状について説明するための図である。

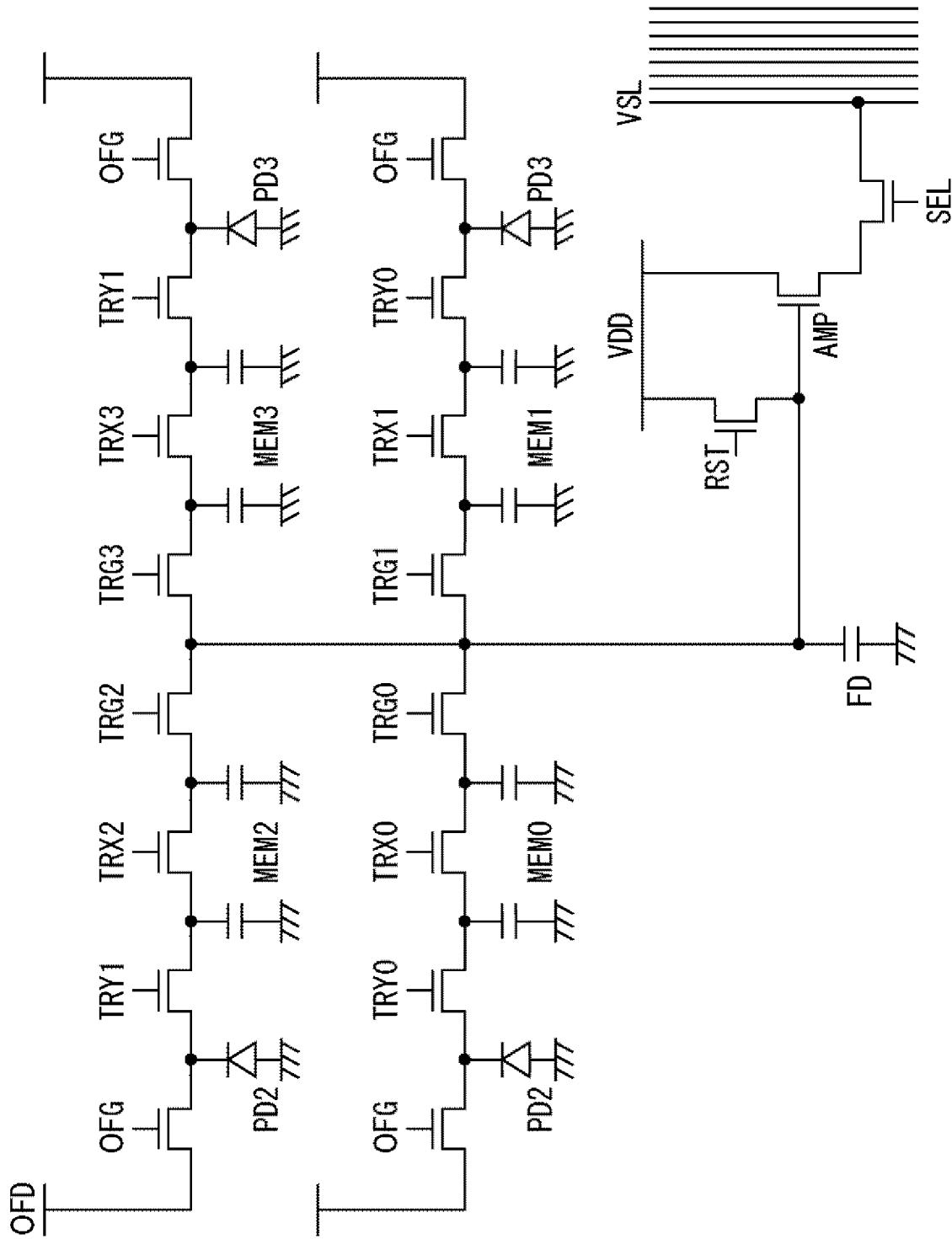

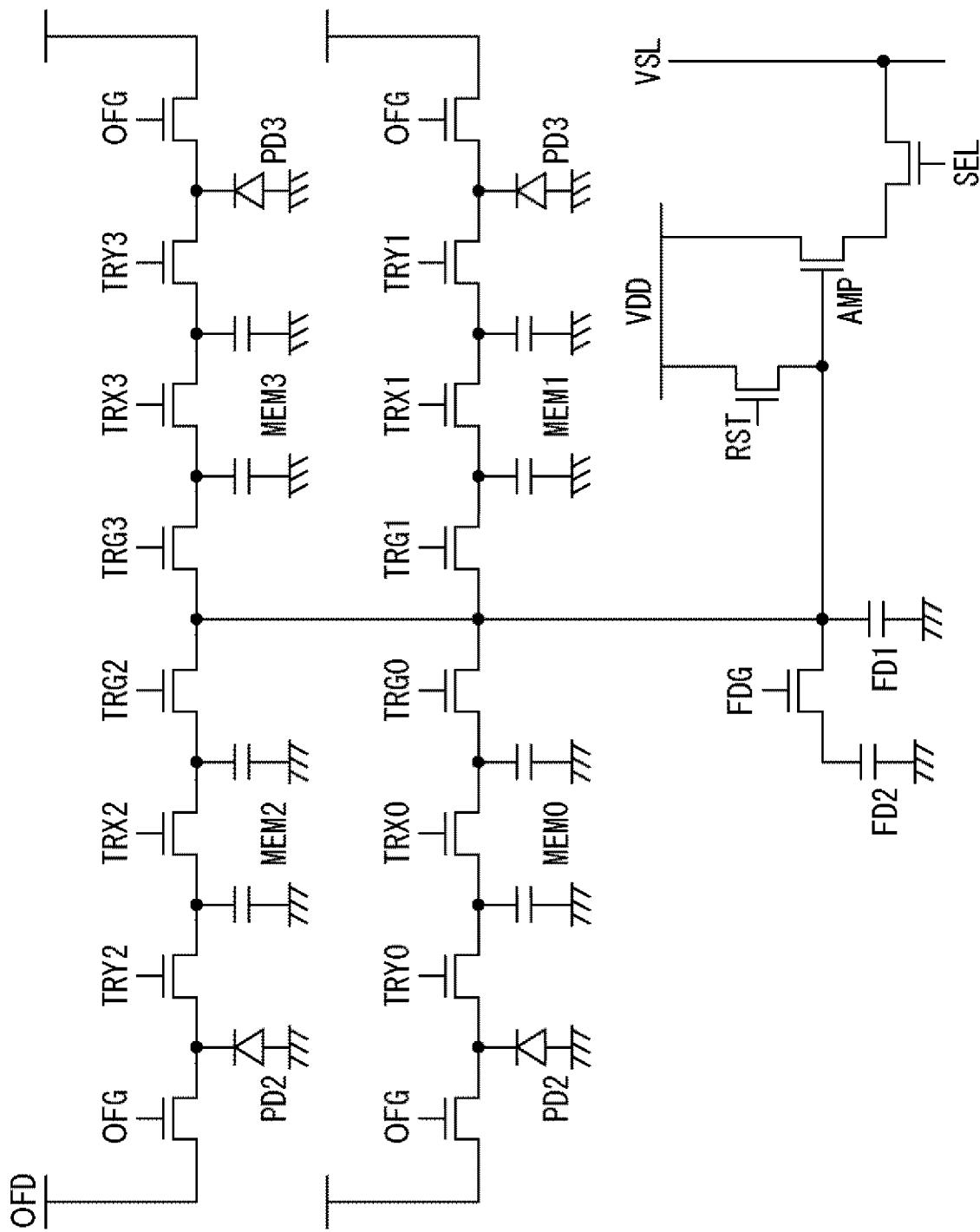

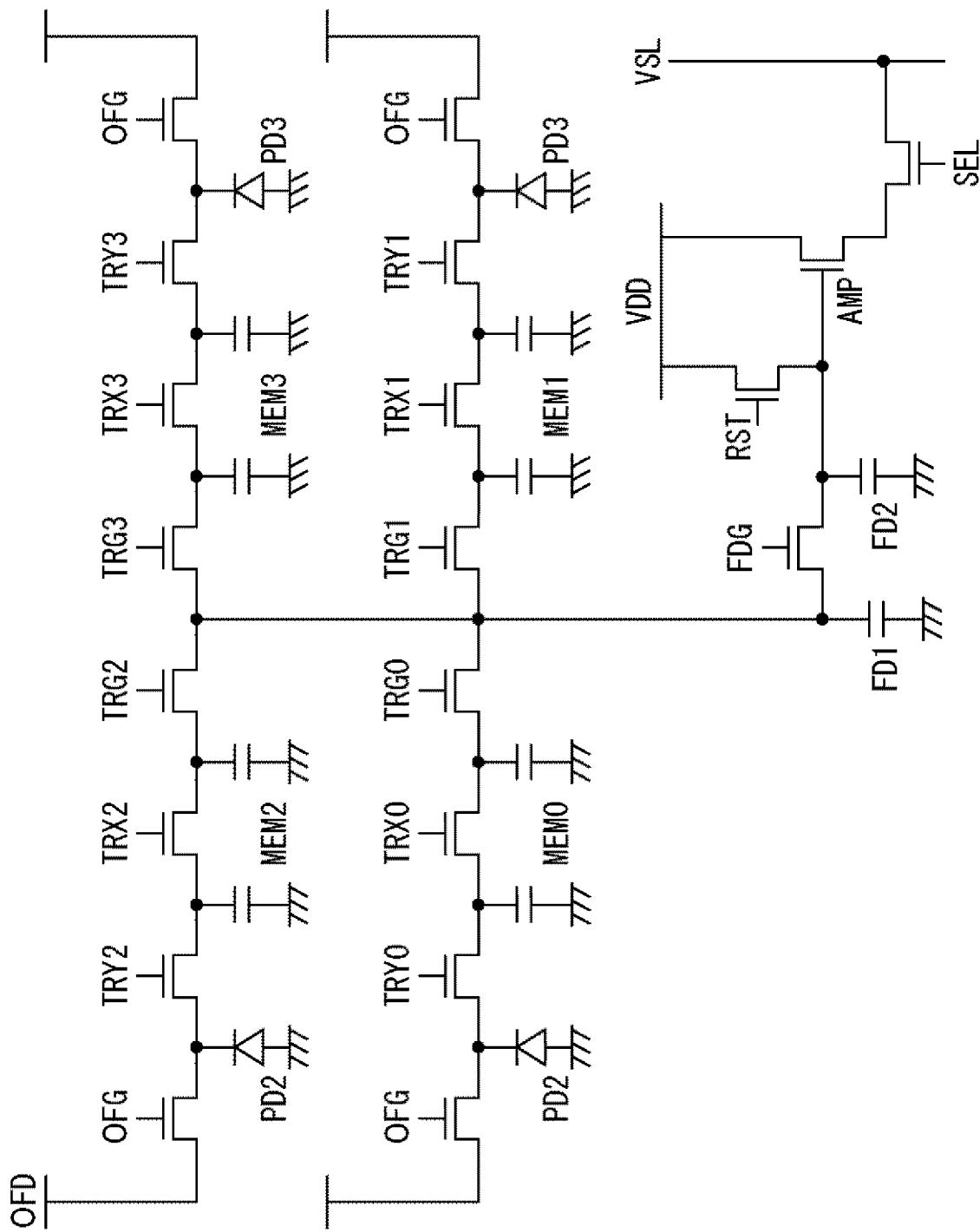

[図 30] 画素の構成を示す回路図である。

[図 31] 画素の構成を示す回路図である。

[図 32] 画素の配線の位置や形状について説明するための図である。

[図 33] 画素の配線の位置や形状について説明するための図である。

[図 34] 画素の配線の位置や形状について説明するための図である。

[図 35] 画素の配線の位置や形状について説明するための図である。

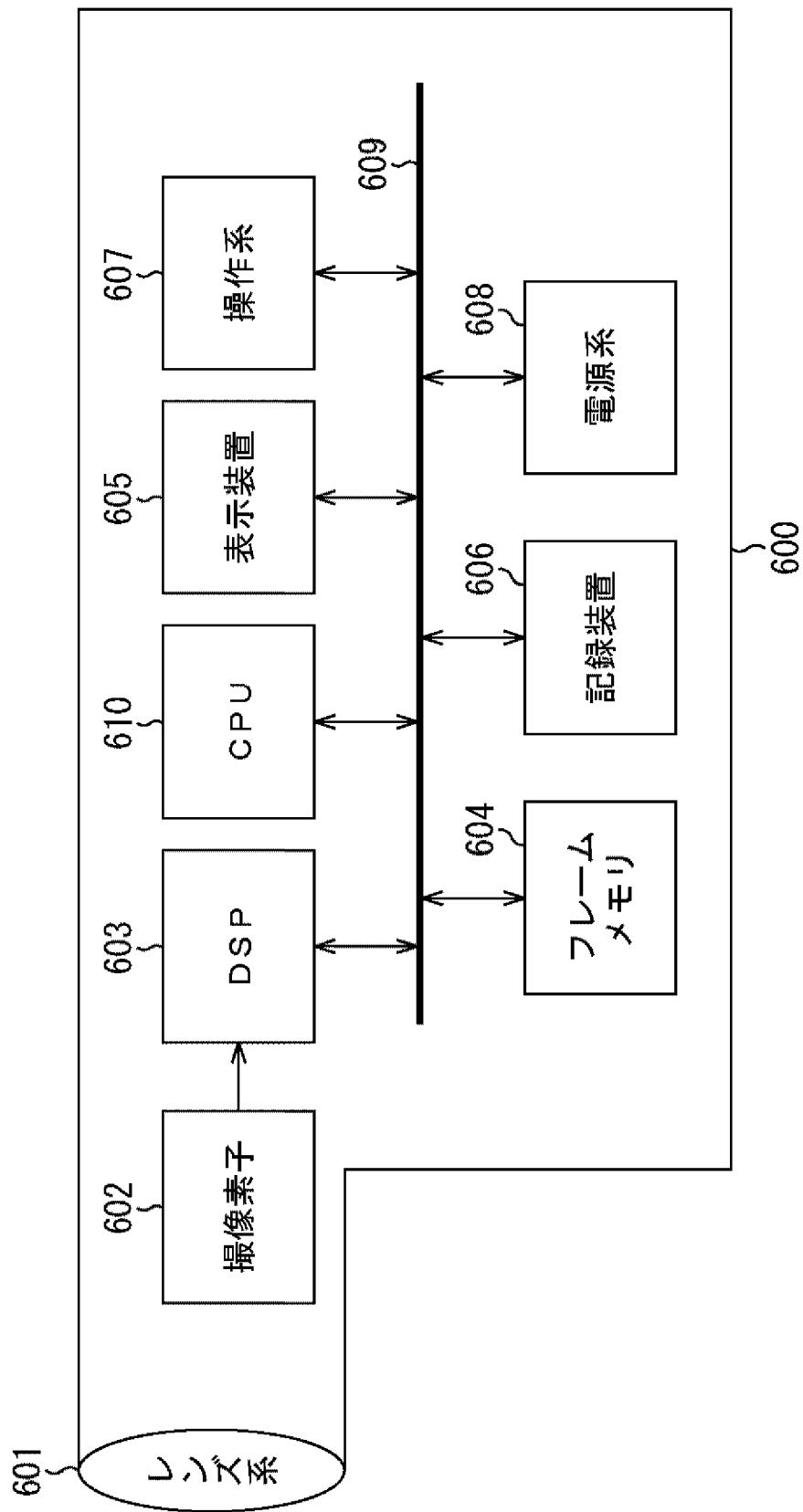

[図 36] 電子機器の構成について説明するための図である。

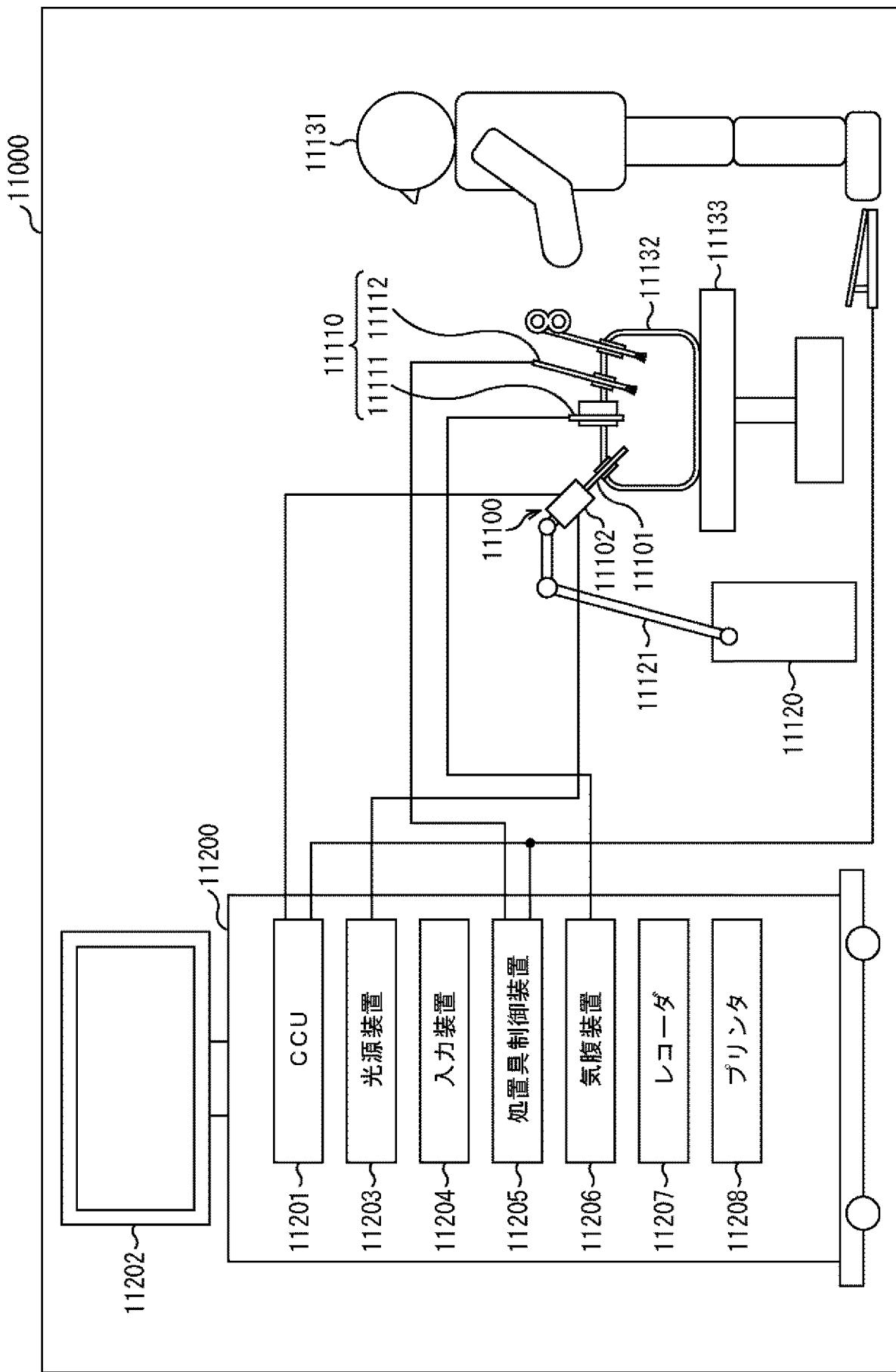

[図 37] 内視鏡手術システムの概略的な構成の一例を示す図である。

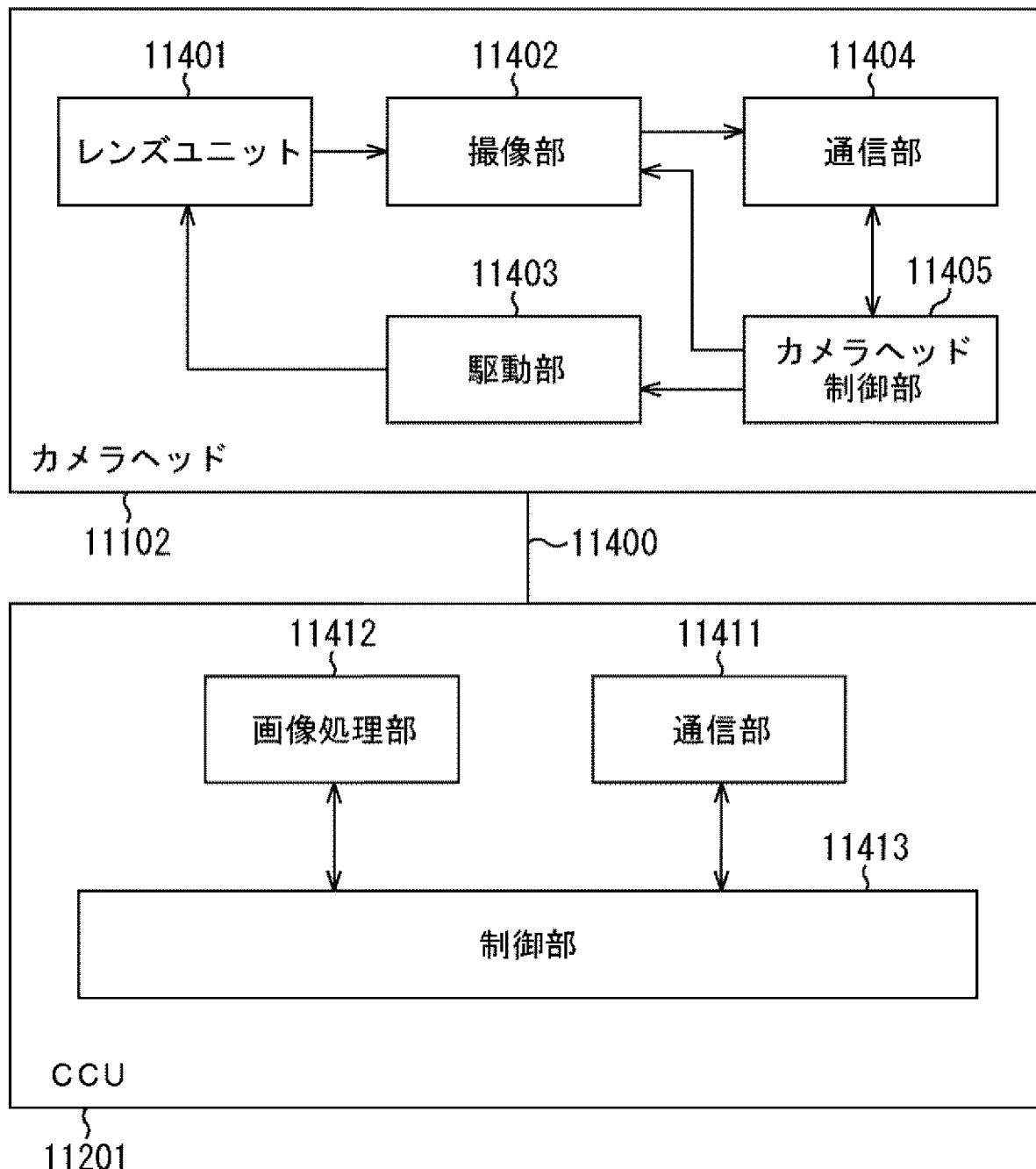

[図 38] カメラヘッド及びCCUの機能構成の一例を示すブロック図である。

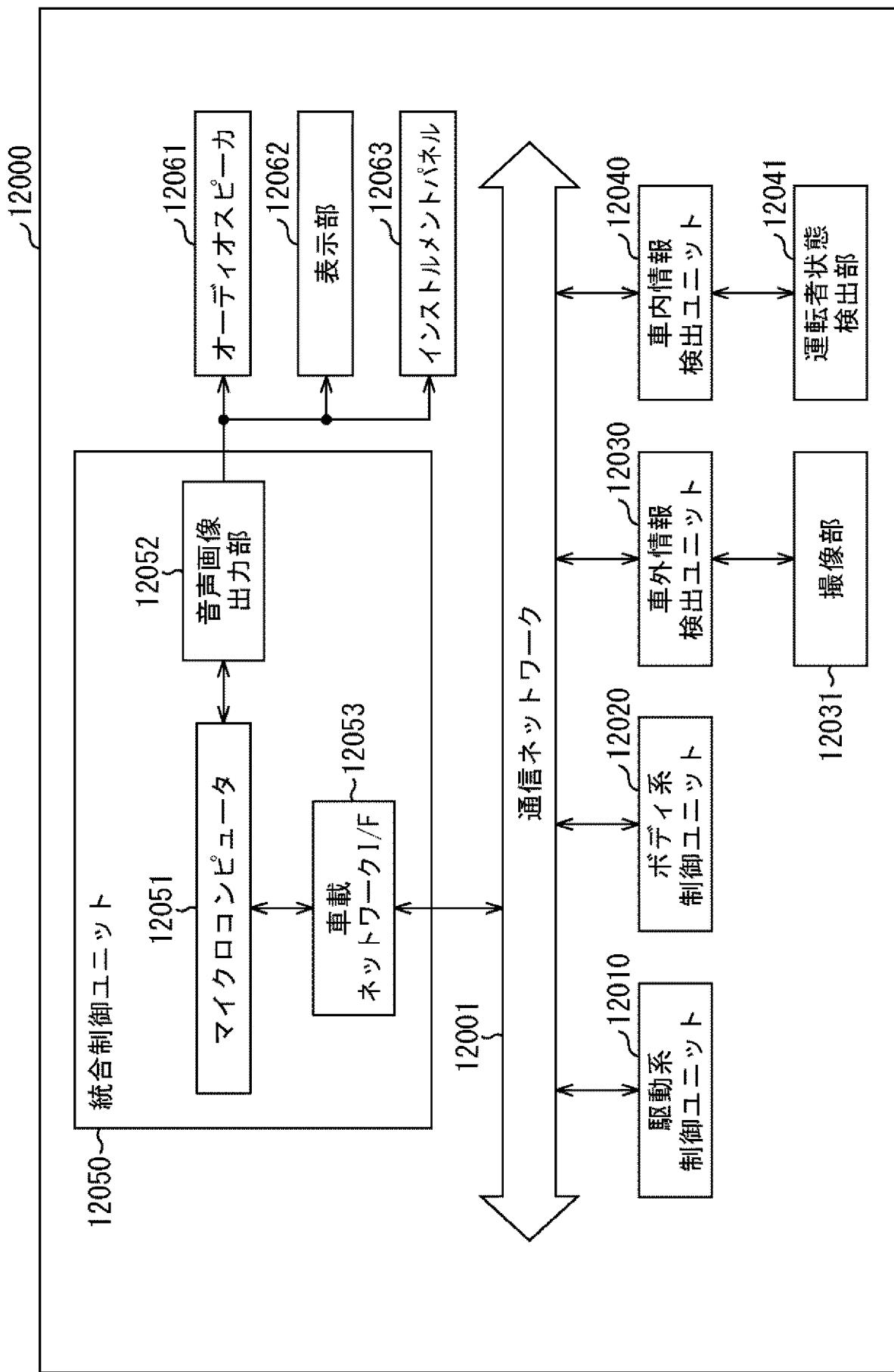

[図 39] 車両制御システムの概略的な構成の一例を示すブロック図である。

[図 40] 車外情報検出部及び撮像部の設置位置の一例を示す説明図である。

### 発明を実施するための形態

[0017] 以下に、本技術を実施するための形態（以下、実施の形態という）について説明する。

[0018] <撮像素子の構成>

図1は、本発明が適用される撮像素子としてのCMOS (Complementary Metal Oxide Semiconductor) イメージセンサの構成例を示すブロック図である。

[0019] CMOSイメージセンサ30は、画素アレイ部41、垂直駆動部42、カラム処理部43、水平駆動部44、およびシステム制御部45を含んで構成され

る。画素アレイ部41、垂直駆動部42、カラム処理部43、水平駆動部44、およびシステム制御部45は、図示しない半導体基板(チップ)上に形成されている。

[0020] 画素アレイ部41には、入射光量に応じた電荷量の光電荷を発生して内部に蓄積する光電変換素子を有する単位画素(図2の画素50)が行列状に2次元配置されている。なお、以下では、入射光量に応じた電荷量の光電荷を、単に「電荷」と記述し、単位画素を、単に「画素」と記述する場合もある。

[0021] 画素アレイ部41にはさらに、行列状の画素配列に対して行毎に画素駆動線46が図の左右方向(画素行の画素の配列方向)に沿って形成され、列毎に垂直信号線47が図の上下方向(画素列の画素の配列方向)に沿って形成されている。画素駆動線46の一端は、垂直駆動部42の各行に対応した出力端に接続されている。

[0022] CMOSイメージセンサ30はさらに、信号処理部48およびデータ格納部49を備えている。信号処理部48およびデータ格納部49については、CMOSイメージセンサ30とは別の基板に設けられる外部信号処理部、例えばDSP(Digital Signal Processor)やソフトウェアによる処理でも良いし、CMOSイメージセンサ30と同じ基板上に搭載しても良い。

[0023] 垂直駆動部42は、シフトレジスタやアドレスデコーダなどによって構成され、画素アレイ部41の各画素を、全画素同時あるいは行単位等で駆動する画素駆動部である。この垂直駆動部42は、その具体的な構成については図示を省略するが、読み出し走査系と、書き出し走査系あるいは、一括書き出し、一括転送を有する構成となっている。

[0024] 読み出し走査系は、単位画素から信号を読み出すために、画素アレイ部41の単位画素を行単位で順に選択走査する。行駆動(リングシャッタ動作)の場合、書き出しについては、読み出し走査系によって読み出し走査が行われる読み出し行に対して、その読み出し走査よりもシャッタスピードの時間分だけ先行して書き出し走査が行われる。また、グローバル露光(グロ

一 バル シャッタ動作 ) の 場合 は、一括 転送 よりも シャッタスピード の 時間 分 先行 し て 一括 掃き出し が 行わ れる。

[0025] この 掃き出し に より、読み出し 行の 単位画素 の 光電変換 素子 から 不要な 電荷 が 掃き出さ れる (リセッ トされる)。そ して、不要 電荷 の 掃き出し (リセッ ト) に より、いわゆる 電子シャッタ動作 が 行わ れる。ここで、電子シャッタ 動作 と は、光電変換 素子 の 光電荷 を 捨てて、新たに 露光 を 開始する (光電荷 の 蓄積 を 開始する) 動作 の こと を 言う。

[0026] 読み出し走査系 による 読み出し動作 に よって 読み出さ れる 信号 は、その直前の 読み出し動作 または 電子シャッタ動作 以降 に 入射した 光量 に 対応するもの である。行駆動の 場合 は、直前の 読み出し動作 による 読み出しタイミング または 電子シャッタ動作 による 掃き出しタイミング から、今回 の 読み出し動作 による 読み出しタイミングまでの期間 が、単位画素 における 光電荷 の 蓄積期間 (露光期間) となる。グローバル露光の 場合 は、- 括き出しがから - 括転送までの期間 が 蓄積期間 (露光期間) となる。

[0027] 垂直駆動部 4 2 によつて選択走査された画素行の各 単位画素 から 出力さ れる 画素信号 は、垂直信号線 4 7 の 各々 を通して カラム処理部 4 3 に 供給さ れる。カラム処理部 4 3 は、画素アレイ部 4 1 の 画素列毎に、選択行の各 単位画素 から 垂直信号線 4 7 を通して 出力さ れる 画素信号 に 対して 所定の 信号処理 を 行うとともに、信号処理後の 画素信号 を 一時的に 保持する。

[0028] 具体的には、カラム処理部 4 3 は、信号処理として 少なくとも、ノイズ除去処理、例え ば CDS (Correlated Double Sampling; 相関二重サンプリング) 処理を 行う。このカラム処理部 4 3 による 相関二重サンプリング により、リセッ トノイズや 増幅トランジスタの 閾値ばらつき 等の 画素固有の 固定パターンノイズ が 除去さ れる。なお、カラム処理部 4 3 にノイズ除去処理以外に、例え ば、AD (アナログ-デジタル) 変換機能を持たせ、信号レベルをデジタル信号で 出力することも 可能である。

[0029] 水平駆動部 4 4 は、シフトレジスタやアドレスデコーダなど に よつて構成され、カラム処理部 4 3 の 画素列 に 対応する 単位回路 を 順番に 選択する。こ

の水平駆動部44による選択走査により、カラム処理部43で信号処理された画素信号が順番に信号処理部48に出力される。

[0030] システム制御部45は、各種のタイミング信号を生成するタイミングジエレータ等によって構成され、タイミングジエレータで生成された各種のタイミング信号を基に垂直駆動部42、カラム処理部43、および水平駆動部44などの駆動制御を行う。

[0031] 信号処理部48は、少なくとも加算処理機能を有し、カラム処理部43から出力される画素信号に対して加算処理等の種々の信号処理を行う。データ格納部49は、信号処理部48での信号処理に当たって、その処理に必要なデータを一時的に格納する。

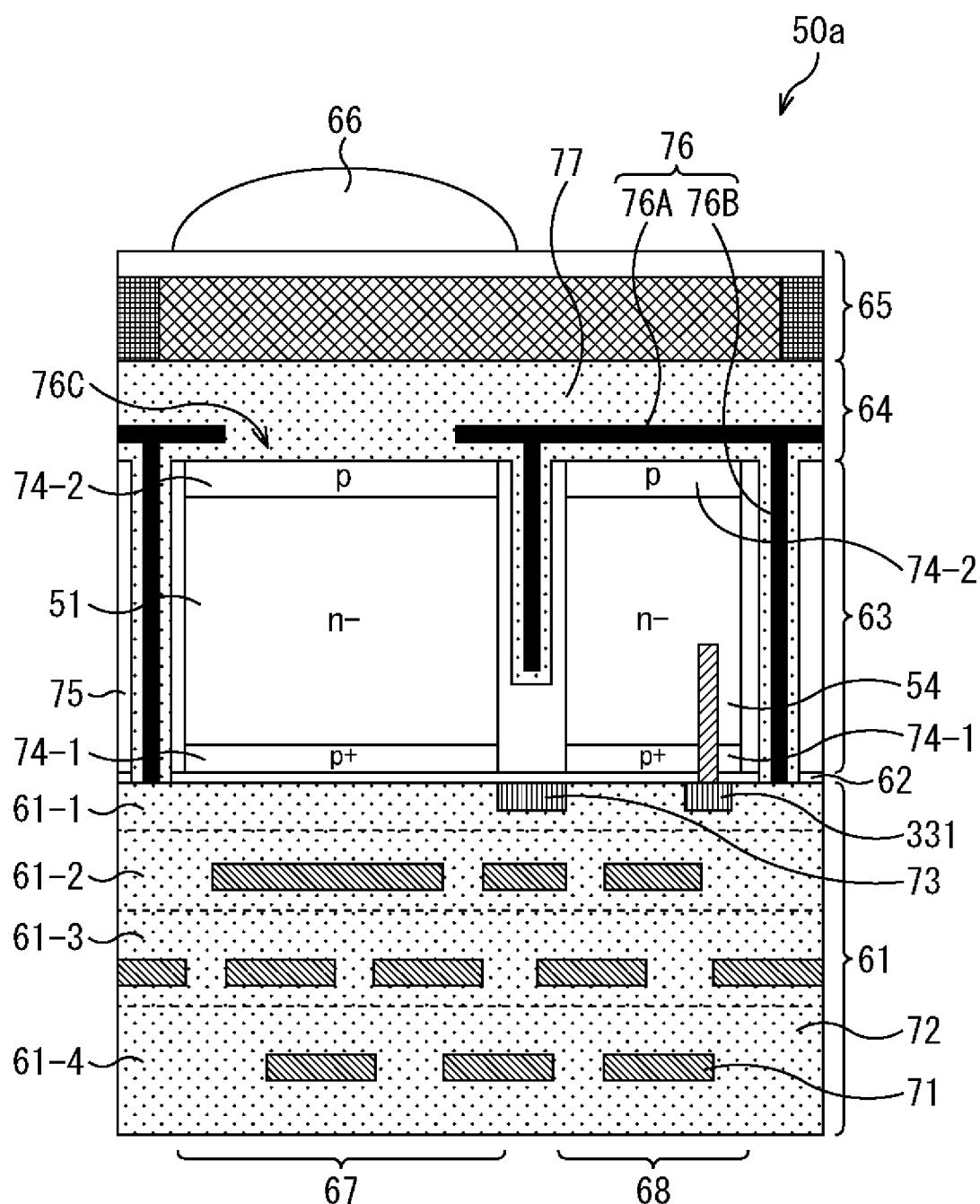

[0032] <単位画素の構造>

次に、図1の画素アレイ部41に行列状に配置されている単位画素50の具体的な構造について説明する。図2は、画素50の断面的な構成例を示す図である。

[0033] 図2を示した画素508は、グローバルシャッタを実現するために、電荷保持部を備える。図2に示すように、画素50<sub>3</sub>は、図2の下側から順に、配線層61、酸化膜62、半導体基板63、遮光層64、カラーフィルタ層65、およびオンチップレンズ66が積層されて構成されている。また、画素50<sub>3</sub>において、半導体基板63にP051が形成されている領域がP口領域67とされ、半導体基板63に電荷保持部54が形成されている領域が電荷保持領域68とされる。

[0034] なお、イメージセンサ30は、半導体基板63に対して配線層61が設けられる半導体基板63の表面に対して反対側となる裏面（図2の上側を向く面）に対して入射光が照射される、いわゆる裏面照射型CMOSイメージセンサである。ここでは、裏面照射型CMOSイメージセンサを例に挙げて説明を続けるが、表面照射型のイメージセンサに対しても、本技術を適用することはできる。

[0035] 配線層61は、例えば、その下側に配置されている基板支持材（図示せず）

)により支持されており、半導体基板63に形成されているP051の電荷の読み出しなどを行う複数の配線71が層間絶縁膜72に埋め込まれて構成されている。

[0036] また、配線層61には、P051および電荷保持部54の間の領域に、半導体基板63に対して酸化膜62を介して、転送トランジスタを構成する丁<sup>¶</sup>又ゲート73が配置されている。丁<sup>¶</sup>又ゲート73に所定の電圧が印加されることにより、[905]に蓄積されている電荷が電荷保持部54に転送される。

[0037] 配線層61は、図2に示した例では、配線層61—1乃至61—4の4層構造とされている。配線層61—1は、半導体基板63に積層され、配線層61—2は、配線層61—1に積層され、配線層61—3は、配線層61—2に積層され、配線層61—4は、配線層61—3に積層されている。各配線層61—1乃至61—4の配線パターンなどについては、後述する。

[0038] 酸化膜62は、絶縁性を備えており、半導体基板63の表面側を絶縁する。半導体基板63には、P051を構成する<sub>11</sub>型領域と、電荷保持部54を構成する問型領域とが形成されている。

[0039] また、P051および電荷保持部54の裏面側には表面ピニング層74—1が形成され、P051および電荷保持部54の表面側には表面ピニング層74—2が形成されている。さらに、半導体基板63には、画素503と、隣接する他の画素503とを分離するための画素間分離領域75が、画素503の外周を囲うように形成されている。

[0040] 遮光層64は、遮光性を有する材料により形成される遮光部76が、高誘電率材料膜77に埋め込まれて形成されている。例えば、遮光部76は、タンクスチン(IV)や、アルミ(八I)、銅(O10)などの材料により形成され、図示しないGNOに接続されている。高誘電率材料膜77は、二酸化ケイ素(<sub>3</sub>102)や、酸化ハフニウム(HfO<sub>2</sub>)、五酸化タンタル(13205)、二酸化ジルコニウム(ZrO<sub>2</sub>)などの材料により形成される。

[0041] また、遮光部76は、半導体基板63を覆うように配置される蓋部76八

と、凹口 5 1 および電荷保持部 5 4 の周囲を囲うように半導体基板 6 3 に形成される縦溝に埋め込まれるように配置される埋め込み部 7 6 巳とを有して形成される。即ち、蓋部 7 6 六は、画素 5 0 3 を構成する各層に対して略平行に形成され、埋め込み部 7 6 巳は、蓋部 7 6 六に対して略直交する方向に延在するように所定の深さまで形成されている。

[0042] ここで、遮光部 7 6 の埋め込み部 7 6 巳は、9051 および電荷保持部 5 4 の周囲を囲うように画素間分離領域 7 5 に形成されるような構成とする他、例えば、電荷保持部 5 4 の周囲を形成するような構成や、凹口 5 1 および電荷保持部 5 4 の間に形成するような構成としてもよい。即ち、少なくとも 9051 および電荷保持部 5 4 の間に埋め込み部 7 6 巳が形成され、凹口 5 1 および電荷保持部 5 4 が埋め込み部 7 6 巳により分離されればよい。

[0043] また、遮光部 7 6 には、9051 に光を入射するための開口部 7 6 ○が形成されている。すなわち開口部 7 6 ○は、9051 に対応した領域に形成されており、それ以外の領域は、例えば、電荷保持部 5 4 やド055などが形成されている領域は、遮光部 7 6 により遮光されている。

[0044] また、図 2 に示した例では、埋め込み部 7 6 巳の一部が半導体基板 6 3 を貫通するように遮光部 7 6 が形成されている。すなわち、遮光部 7 6 は、凹口 5 1 および電荷保持部 5 4 の間の領域以外、即ち、9051 から電荷保持部 5 4 へ電荷を転送する転送経路となる領域以外における埋め込み部 7 6 巳が、半導体基板 6 3 を貫通するように形成されている。

[0045] すなわち、凹口 5 1 および電荷保持部 5 4 の間の領域は、電荷の転送に使用されるために遮光部を形成することはできないが、その領域以外において埋め込み部 7 6 巳を形成することにより、同一の画素 5 0 3 の凹口 5 1 以外から電荷保持部 5 4 に光が漏れ込むことを効果的に抑制することができる。

[0046] カラーフィルタ層 6 5 では、画素 5 0 3 每に、それぞれ対応する色の光を透過するフィルタが配置されており、例えば、緑色、青色、および赤色の光を透過するフィルタが、いわゆるベイヤー配列で画素 5 0 8 每配置される。オンチップレンズ 6 6 は、画素 5 0 3 に入射する入射光を凹口 5 1 に集光す

るための小型のレンズである。

[0047] <半導体基板におけるレイアウト>

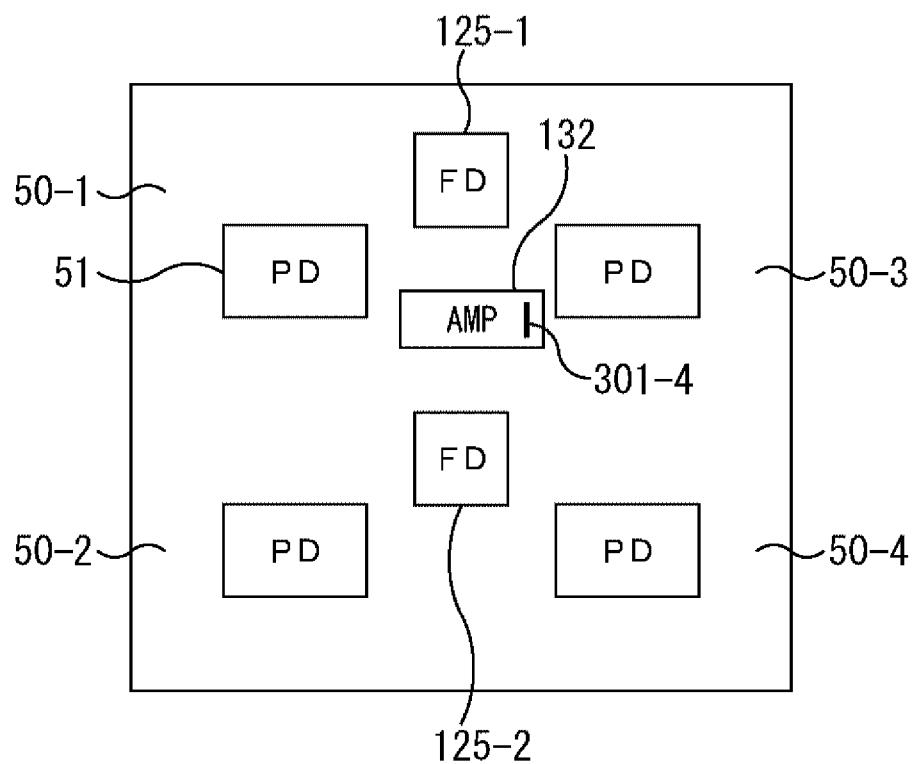

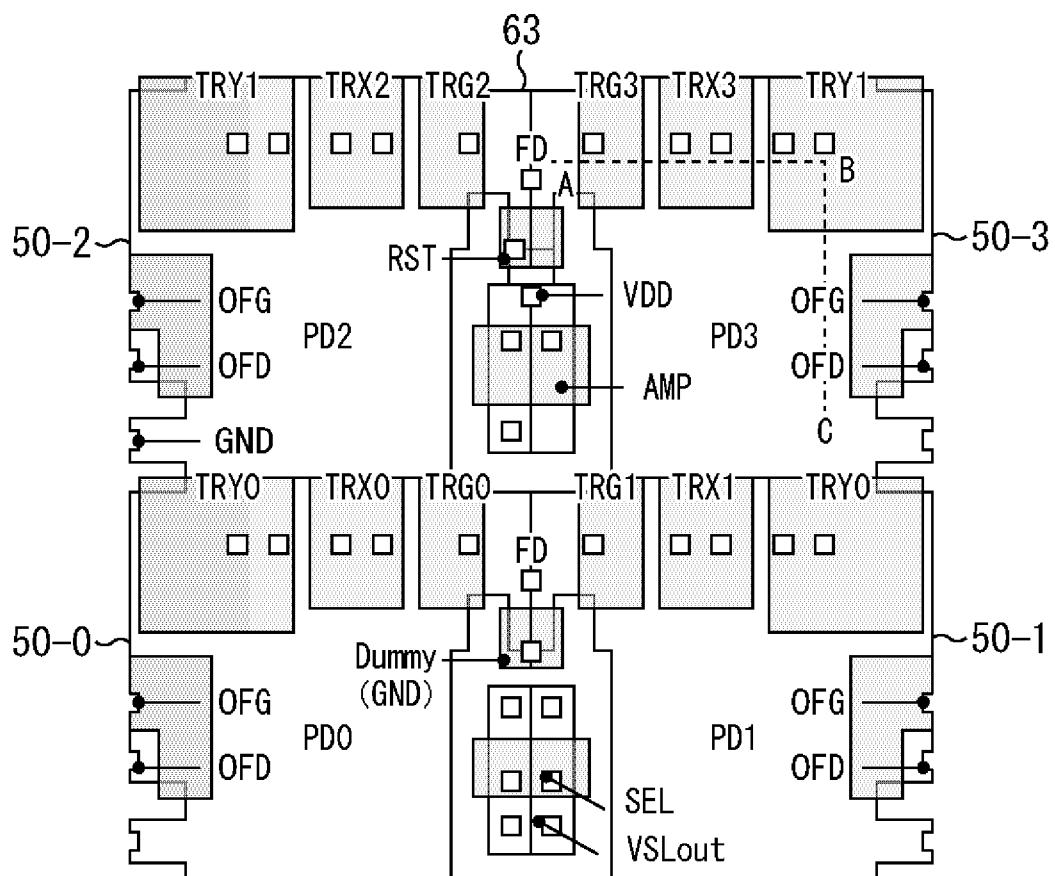

図3は、図2に示した画素50を下部(図2中の下側)から見たときの平面図である。本技術は、特に複数の画素で所定のトランジスタを共有する構成のときに効果を得られるため、まず $2 \times 2$ の4画素で所定のトランジスタ等を共有した場合の平面図を図3に示す。なお、図3以降に示す平面図においては、遮光部76の図示は省略するが、貫通して遮光部76と非貫通の遮光部76が、?056や電荷保持部54の周りに形成されている。

[0048] 図3は、画素アレイ部41に配置されている画素503—1乃至503—4の4画素を図示している。図中左上に、画素508\_1が配置され、図中左下に、画素503\_2が配置され、図中右上に、画素503—3が配置され、図中右下に、画素508\_4が配置されている。各画素508は、基本的に同一の構成を有しているため、図中左上に配置されている画素503—1を例に挙げて説明を続ける。

[0049] 画素50a-1の左下側に○ド0121が配置されている。○ド0121は、□口51のリセットゲートに接続しているドレインを表す。○ド0121は、○ドGゲート122を介して、□口51と接続されている。

[0050] 9051の上側には、電荷保持部54が配置されている。画素503を下部(配線層61側)から見たとき、電荷保持部54が配置されている領域内には、丁<sub>¶</sub>又ゲート73が配置されている。丁<sub>¶</sub>又ゲート73は、9051から電荷保持部54への電荷の転送を制御するために設けられている。

[0051] 電荷保持領域68の図中右側には、丁<sub>¶</sub>又ゲート73を介して、浮遊拡散領域125(ド0125)が配置されている。TRGゲート124は、電荷保持部54からド0125に電荷を転送するために設けられている。

[0052] ド0125—1は、画素503—1と画素503—3の間に配置され、ド0125—2は、画素503—2と画素503—4の間に配置されている。また、ド0125—1とド0125—2は、ド0配線126で接続されている。ド0125—1とド0125—2が、ド0配線126で接続されること

で、1つのドロップとして機能する。また、この1つのドロップとして機能するドロップ125-1とドロップ125-2は、画素50a-}乃至503\_4で共有される。

[0053] 画素50a-1と画素503-3の間には、リセットトランジスタ131(図中、図3丁と記述)と増幅トランジスタ132が配置されている。また、画素503-2と画素503-4の間には、選択トランジスタ133(図中、3已!と記述)が配置されている。図3では図示していないが、変換効率切替トランジスタを、画素503-2と画素503\_4の間に配置する構成とすることもできる。変換効率切替トランジスタを有する構成については、後述する。また、図3に示したように、変換効率切替トランジスタを設けない構成とした場合、対象性を確保するためにダミーを配置しても良い。

[0054] 図3に示した例では、4個の画素503で、リセットトランジスタ131、増幅トランジスタ132、および選択トランジスタ133を共有する構成とされている。

[0055] このように、複数の画素で、トランジスタを共有する構成とすることで、1つのトランジスタに割り当てる領域を大きくすることができる。1つのトランジスタに割り当てる領域を広くできることで、トランジスタのソースとドレインの距離を広げた構成とすることもでき、リークを防止する構成とすることができる。

[0056] また、複数の画素で、トランジスタを共有する構成とすることで、小型化することもできる。

[0057] 図3に示した共有画素の構成は、図中、縦方向にリセットトランジスタ131、増幅トランジスタ132、選択トランジスタ133が配置され、ド0配線126を対称軸としたとき、D051、電荷保持部54、○D0121などは、左右対称となるように配置されている。

[0058] 本技術は、図3に示した左右対称の構造に適用できるし、図4に示した上下対称の構造にも適用できる。図4は、画素50の他の配置例を示す平面図である。図4中左上に、画素50!○\_1が配置され、図中左下に、画素50

ヒ\_2が配置され、図中右上に、画素50ヒ\_3が配置され、図中右下に、画素50ヒ\_4が配置されている。

- [0059] 画素506-3と画素50ヒ\_4の間にド0125-1が配置され、画素506-1と画素50ヒー2の間にド0125-2が配置され、ド0125-1とド0125-2は、ド0配線126で接続されている。このド0配線126を対称軸として、上下対称に、□051、電荷保持部54、○ド0121などが配置されている。

- [0060] また画素50ヒー3と画素50ヒー4の間には、リセットトランジスタ131と増幅トランジスタ132が配置され、画素50ヒ\_1と画素50b\_2の間には、選択トランジスタ133が配置されている。図4に示した共有画素の構成においては、図中、横方向にリセットトランジスタ131、増幅トランジスタ132、選択トランジスタ133が配置されている。

- [0061] 図4に示したように、本技術は、画素同士が上下対称に配置されている場合にも適用できる。

- [0062] 図3、図4に示した構成は、2×2の4画素で所定のトランジスタなどを共有する場合を示したが、2画素で所定のトランジスタなどを共有する場合にも適用できる。

- [0063] 図5は、2画素共有のときの画素50〇の配置例を示す平面図である。図5中左側に、画素50〇\_1が配置され、図中右側に、画素50〇\_2が配置されている。

- [0064] 図中横方向に配置されている画素50〇-1と画素50〇-2の間にド0125、リセットトランジスタ131、増幅トランジスタ132、および選択トランジスタ133が配置されている。ド0125と増幅トランジスタ132は、ド0配線126により接続されている。

- [0065] このド0配線126を対称軸として、左右対称に、□051、電荷保持部54、○ド0121などが配置されている。本技術は、図5に示した2画素共有であり、左右対称の構造に適用できるし、図6に示すように、2画素共有であり上下対称の構造にも適用できる。

- [0066] 図 6 は、画素 50 の他の配置例を示す平面図である。図 6 中上側に、画素 50\_づ\_1 が配置され、図中下側に、画素 50\_づ\_2 が配置されている。図中縦方向に配置されている画素 50\_d-1 と画素 50\_づ-2 の間にド 0\_125、リセットトランジスタ 13\_1、増幅トランジスタ 13\_2、および選択トランジスタ 13\_3 が配置されている。ド 0\_125 と増幅トランジスタ 13\_2 は、ド 0 配線 126 により接続されている。

- [0067] このド 0 配線 126 を対称軸として、上下対称に、□0\_5\_1、電荷保持部 5\_4、○ド 0\_12\_1 などが配置されている。本技術は、図 5 に示した 2 画素共有であり、左右対称の構造に適用できるし、図 6 に示したように、2 画素共有であり上下対称の構造にも適用できる。

- [0068] さらに、縦方向に配置されている 2 画素で所定のトランジスタなどを共有する 2 画素共有において、□0\_5\_1 に対して、電荷保持部 5\_4 を半ピッチずらした位置に配置した構成とすることもできる。

- [0069] 図 7 は、画素 50 の他の配置例を示す平面図である。図 7 中上側に、画素 5\_〇6\_-1 が配置され、図中下側に、画素 50\_⊖\_2 が配置されている。図 7 に示した配置例では、画素 50\_6-1 の右下側に○ド 0\_12\_1 と○ド〇ゲート 12\_2 が配置されている。

- [0070] □0\_5\_1 の左上側であり、□0\_5\_1 と半ピッチずれた位置には、電荷保持部 5\_4 が配置されている。画素 5\_〇6 を下部（配線層 6\_1 側）から見たとき、電荷保持部 5\_4 が配置されている領域内には、丁 R X ゲート 7\_3 が配置されている。丁  $\sqcap$  イゲート 7\_3 の図中中央上部側には、丁  $\sqcap$  ○ゲート 12\_4 が配置されている。さらに、丁 R G ゲート 12\_4 の図中中央上部側には、ド 0\_12\_5 が形成されている。

- [0071] 画素 50\_6-2 も、画素 50\_⊖-1 と同様の構成を有している。画素 50\_6-1 には、ド 0\_12\_5-1 が配置され、画素 50\_6-2 には、ド 0\_12\_5-2 が配置されている。「0\_12\_5-1」と「0\_12\_5-2」は、ド 0 西線 126 により接続されている。

- [0072] 画素 50\_6-1 と画素 50\_6-2 の間には、リセットトランジスタ 13\_1

と増幅トランジスタ132が配置され、画素506\_1の図中上部には、選択トランジスタ133が配置されている。図7に示した例では、2個の画素506で、リセットトランジスタ131、増幅トランジスタ132、および選択トランジスタ133を共有する構成とされている。

[0073] 画素506\_1に注目した場合、画素506\_1に含まれるP051に蓄積された電荷が転送される先は、画素506\_1の図中左上部側に配置されている丁<sub>η</sub>又ゲート73の下に形成されている電荷保持部54である。同じく、画素506\_2に注目した場合、画素506\_2に含まれるP051に蓄積された電荷が転送される先は、画素506\_2の図中左上部側に配置されている丁<sub>η</sub>又ゲート73の下に形成されている電荷保持部54である。

[0074] P051と電荷保持部54は、半ピッチずれた位置に配置されている関係にある。P051に対して電荷保持部54を、半ピッチずれた位置に配置することで、電荷保持部54(丁<sub>η</sub>又ゲート73)の中央部分に丁RGゲート124を配置することができる。電荷保持部54の中央部分に丁RGゲート124が位置することで、電荷保持部54内の転送長を短くすることが可能となり、転送効率を向上させることが可能となる。

[0075] 図7は、9051の長辺が横方向に配置され、電荷保持部54がP051の長辺側に配置され、半ピッチずれた位置に配置されている例を示したが、図8に示すように、P051の長辺が縦方向に配置され、電荷保持部54が9051の長辺側に配置され、半ピッチずれた位置に配置されている場合にも本技術を適用できる。

[0076] 図8は、画素50の他の配置例を示す平面図である。図7に示した配置例と同じく、画素50\_1と画素50\_2は縦方向に配置されている。図8に示した配置例では、画素50\_1の下側に○ド0121と○ド○ゲート122が配置されている。

[0077] 9051の図中右側であり、9051と半ピッチずれた上側の位置には、電荷保持部54(丁<sub>η</sub>又ゲート73)が配置されている。丁<sub>η</sub>又ゲート73の図中中央右側には、丁RGゲート124が配置されている。さらに、丁<sub>η</sub>

○ゲ\_ ト124 の図中中央右側には、「0 125 が形成されている。

[0078] 画素50チ\_2も、画素50チ\_1と同様の構成を有している。画素50干\_1には、ド0125-1が配置され、画素50干\_2には、ド0125-2が配置されている。「0 125 - 1」と「0 125 - 2」は、ド0西線126により接続されている。

[0079] 図3乃至図8に示した構成に対して、以下に説明するド0を昇圧する構成を適用できる。また、図3乃至図8には図示していないが、例えば、8画素でド0125やリセットトランジスタ131などを共有する構成に対しても適用でき、本技術の適用は、図3乃至図8に示した構成に限定される記載ではない。

[0080] <ド0を昇圧する構成>

上記したような画素50は、905]で蓄積された電荷を電荷保持部54で一旦蓄積するグローバルシャッタ構造を有している。電荷保持部54を備える画素は、電荷保持部54を備えない構造の画素と比較して、飽和電荷量(03)確保に寄与できる面積が小さくなってしまう傾向にある。電荷保持部54を備える画素において、飽和電荷量を確保できるようにポテンシャルを深化させると、ド0125のダイナミックレンジの確保とくみ上げ特性が悪化してしまう可能性がある。

[0081] 以下に説明するように、ド0配線126の近傍にド0125を昇圧するための配線を配置し、ド0125を昇圧することで、ド0124のダイナミックレンジを確保し、くみ上げ特性の悪化を抑制する。

[0082] 以下の説明においては、図3乃至図8に示した画素50の構成のうち、図3に示した構成を例に挙げてド0125を昇圧する構成について説明を続ける。

[0083] 図9は、ド0125を昇圧する構成を有する4画素共有の画素構造を示す図である。図9では、説明のためP051、ド0125、ド0配線126を示すが、図3に示したように、丁<sup>¶</sup>又ゲート73なども配置されている。

[0084] 図9に示した画素50を構成するP051とド0125は、半導体基板6

3 (図2)内に形成されている。FD125-1とFD125-2を接続するド○配線126は、配線層6\_1に形成されている。ここでは、配線層6\_1を構成する配線層6\_1\_1に、ド0配線126が形成されている場合を一例としてあげ、説明を続ける。

[0085] 画素50\_1乃至50\_4の4画素を1共有単位としたとき、1共有単位に2つのD0\_125(2つのド0領域)が半導体基板6\_3内に形成され、その2つのド0領域が、下部に積層されている配線層6\_1\_1内に形成されているド0配線126により接続されている構成とされている。D0\_125とド0配線126は、縦方向(半導体基板6\_3から配線層6\_1\_1側)に形成されているビアにより接続されている。

[0086] 図9に示したように、ド0配線126と平行にド口昇圧配線3\_0\_1が形成されている。ド○昇圧配線3\_0\_1は、ド○配線126と同層、すなわちこの場合、配線層6\_1\_1内に形成されている。また、ド口昇圧配線3\_0\_1は、ド0配線126と少なくとも一部が平行となる部分があるように形成されている。

[0087] ド0配線126やド0昇圧配線3\_0\_1は、図9などでは説明のため直線形状で示したが、トランジスタの配置位置や形状、他の層と配線に接続するためのビアの位置などの関係により、所定の角度を有する直線の組み合わせの形状(折れ線形状)で形成されていたり、直線以外の形状、例えば円弧状を含む形状で形成されていたりしても良い。具体的なレイアウトについては一例を示し後述する。

[0088] 図9に示したように、少なくとも一部は、ド0配線126とド0昇圧配線3\_0\_1が平行な状態の直線形状で形成されている。その平行とされ、直線形状とされているド0昇圧配線3\_0\_1の部分は、ド○配線126の長さと同等の長さであっても良いし、短く形成されていても良いし、長く形成されても良い。

[0089] またド0昇圧配線3\_0\_1の太さは、ド0配線126と同等の太さであっても良いし、細いまたは太く形成されていても良い。ド○昇圧配線3\_0\_1の長

さ、太さ、形状などは、上記したように、ド〇配線126の長さ、太さ、形状に合わせて、適宜設計される。

[0090] また、図9に示すようにド0昇圧配線301は、ド〇配線126右側に1本形成されている構成とすることができます。また、図10に示すように、ド口昇圧配線301は、ド0配線126の右側に1本（ド口昇圧配線301\_1とする）、左側に1本（ド0昇圧配線301\_2とする）形成されている構成とすることができます。以下、ド0昇圧配線301\_1とド0昇圧配線301\_2を個々に区別する必要が無い場合、単にド0昇圧配線301と記述する。

[0091] 図10に示したように、ド0昇圧配線301\_1とド0昇圧配線301\_2をド0配線126の左右にそれぞれ形成する場合、ド口昇圧配線301\_1とド0昇圧配線301\_2は、ド0配線126を対称軸として、対象に形成されている。また、非対称に形成されているようにすることも可能である。例えば、ド0配線126の上部側の右側に、ド0昇圧配線301\_1を形成し、ド0配線126の下部の左側に、ド0昇圧配線301\_2を形成するといった非対称な構成であっても良い。

[0092] ド0昇圧配線301\_1, 301\_2は、図9、図10では、ド0125やド051を避けた位置に配置されているように図示したが、重なるような位置に配置されていても良い。ただし、ド0配線126とド0昇圧配線301の間隔は、100乃至420nmの範囲内に収まるのが良い。間隔が、100nm以下で構成する場合、ド0配線126とド口昇圧配線301を形成するときに高精度が要求され、形成するのが難しい。

[0093] 一方で、間隔が420nm以上であると、ド口昇圧配線301を形成しても、ド0125を適切に昇圧することが難しくなったり、ド〇配線126とド口昇圧配線301との間に、他の配線を形成することができ、他の配線が間に形成されることでド0125を適切に昇圧することが難しくなったりする可能性がある。

[0094] また、ド0配線126とド口昇圧配線301との間を、420nm以上あ

け、その間に他の配線を形成しなければ、画素の小型化が妨げられることがある。

[0095] よって、ド0配線126とド口昇圧配線301の間隔は、1〇〇乃至420nmの範囲内で形成される。なお、このような数値は、一例であり、限定を示す記載ではない。

[0096] 図9と図10に示したド0配線126とド0昇圧配線301は、それぞれ、配線層61\_1に形成されている。換言すれば、ド0配線126とド0昇圧配線301は同層に形成されている。図11に示すように、ド〇配線126とド口昇圧配線301を異なる層に形成することもできる。

[0097] 図11の上図は、4画素共有の1共有単位内のド0配線126の部分を拡大した平面図であり、図11の下図は、平面図における線分八\_八'の部分での断面図である。上述してきた場合と同じくド0125-1とド0125-2は、ド〇配線126により接続されている。このド〇配線126は、下図に示すように、配線層61\_1に形成されている。

[0098] 配線層61\_1にド0配線126が形成され、配線層61\_1の直下に積層されている配線層61\_2に、ド0昇圧配線301\_3が形成されている。ド0配線126とド0昇圧配線301\_3との関係は、上記したド0配線126とド0昇圧配線301\_1(またはド0昇圧配線301\_2)との関係と同じである。すなわち、少なくとも一部は、ド〇配線126とド0昇圧配線301\_3が平行な状態の直線形状で形成されている。

[0099] その平行とされ、直線形状とされているド口昇圧配線301\_3の部分は、ド0配線126の長さと同等の長さであっても良いし、短く形成されても良いし、長く形成されていても良い。またド0昇圧配線301\_3の太さは、ド〇配線126と同等の太さであっても良いし、細いまたは太く形成されていても良い。ド0昇圧配線301の長さ、太さ、形状などは、上記したように、ド〇配線126の長さ、太さ、形状に合わせて、適宜設計される。

[0100] 図11に示したように、ド0配線126とド0昇圧配線301\_3を別の

層に形成することで、ド0昇圧配線301\_3をド0配線126へのシールドを兼ねた構造とすることができる。

- [0101] 図9乃至図11に示したように、ド○配線126の同層、または異層に、またド○配線126の近傍に、ド0125を昇圧させるためのド0昇圧配線301が形成されている。

- [0102] なお、ここでは、ド0配線126との記載をし、ド0配線126は配線であるとして説明を行っているが、ド○配線126自体も、□口51から転送されてきた電荷を蓄積する機能を有し、ド0125として機能する。よって、ド0配線126との記載をしているが、ド0配線126は、単なる配線ではなく、ド○配線126も、ド0125の一部を構成する。

- [0103] すなわち、本技術は、ド○125の近傍に、ド0125を昇圧するためのド口昇圧配線301が、FD]25の近傍に形成されている。ここでは、画素間でドD125を共有する場合、半導体基板63の異なる領域にド0領域を形成し、配線により接続されるため、その配線（ド○配線126）の近傍にド口昇圧配線126が形成される例を示した。

- [0104] さらに、図12に示すように、ド0125が接続される増幅トランジスタ132の一部に、ド○昇圧配線126が接続されている構成とすることができる。図12に示した1共有単位の画素を参照するに、画素50—1乃至50—4で共有される増幅トランジスタ132に接続するようにド0昇圧配線301—4が形成されている。

- [0105] 増幅トランジスタ132の一部である増幅トランジスタゲートは、配線層61-1に形成されている。この増幅トランジスタゲートに接続するようにド0昇圧配線301-4が形成されている。ド0昇圧配線301\_4は、線の形状を有していても良い。または、増幅トランジスタゲートに点、例えばビアで接し、他の層に設けられているド口昇圧用の電源に接続されている配線と接続されているように形成し、増幅トランジスタゲートに点で接している部分をド0昇圧配線301\_4としても良い。

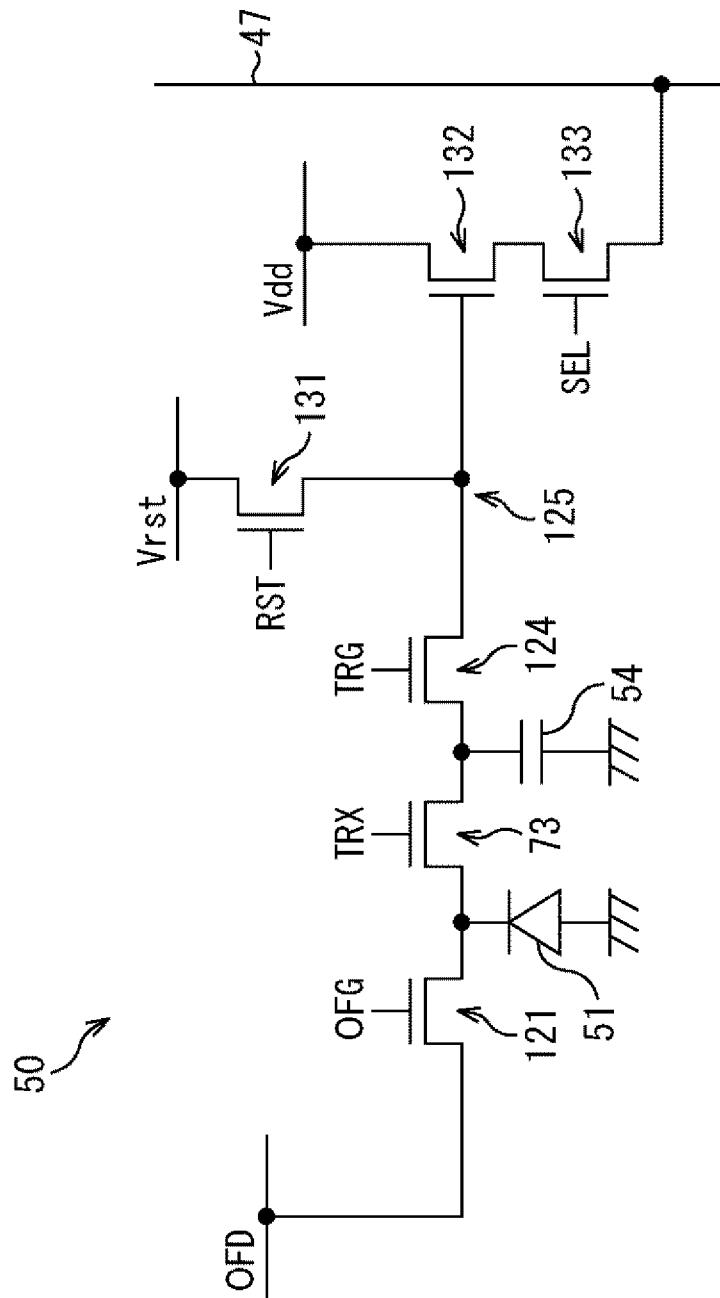

- [0106] ここで、図13に1画素50における回路図を示し、増幅トランジスタゲ

—トに FD 昇圧配線 301—4 が接するように構成することで、FD125 を昇圧できることについて説明を加える。

- [01 07] 画素 50 は、PD51、第 1 の転送トランジスタ 73 (丁<sup>14</sup>又ゲ\_ト 73 を含む転送トランジスタ)、電荷保持部 54、第 2 の転送トランジスタ 124 (TRG ゲート 124 を含む転送トランジスタ)、FD125、増幅トランジスタ 132、選択トランジスタ 133、リセットトランジスタ 131、並びに、排出トランジスタ 121 (OFG121) を備えて構成される。

- [01 08] PD51 は、入射した光を光電変換により電荷に変換して蓄積する光電変換部であり、アノード端子が接地されているとともに、カソード端子が第 1 の転送トランジスタ 73 および排出トランジスタ 121 に接続されている。

- [01 09] 第 1 の転送トランジスタ 73 は、垂直駆動回路 13 から供給される転送信号 TRX に従って駆動し、第 1 の転送トランジスタ 73 がオンになると、PD51 に蓄積されている電荷が電荷保持部 54 に転送される。

- [01 10] 電荷保持部 54 は、第 1 の転送トランジスタ 73 を介して PD51 から転送される電荷を一時的に保持する。

- [01 11] 第 2 の転送トランジスタ 124 は、垂直駆動回路 13 から供給される転送信号 TRG に従って駆動し、第 2 の転送トランジスタ 124 がオンになると、電荷保持部 54 に蓄積されている電荷が FD125 に転送される。

- [01 12] FD125 は、増幅トランジスタ 132 のゲート電極に接続された所定の蓄積容量を有する浮遊拡散領域であり、電荷保持部 54 から転送される電荷を蓄積する。

- [01 13] 増幅トランジスタ 132 は、FD125 に蓄積されている電荷に応じたレベル (即ち、FD125 の電位) の画素信号を、選択トランジスタ 133 を介して垂直信号線 47 に出力する。すなわち、FD125 が増幅トランジスタ 132 のゲート電極に接続される構成により、FD125 および増幅トランジスタ 132 は、PD51において発生した電荷を、その電荷に応じたレベルの画素信号に変換する変換部として機能する。

- [01 14] 選択トランジスタ 133 は、垂直駆動部 42 (図 1) から供給される選択

信号 3 已<sub>1</sub> に従って駆動し、選択トランジスタ 133 がオンになると、増幅トランジスタ 132 から出力される画素信号が垂直信号線 47 に出力可能な状態となる。

- [01 15] リセットトランジスタ 131 は、垂直駆動部 42 から供給されるリセット信号 R3 丁に従って駆動し、リセットトランジスタ 131 がオンになると、FDJ25 に蓄積されている電荷がリセット電源 V「3I に排出されて、D0\_125 がリセットされる。

- [01 16] 排出トランジスタ 121 は、P051 とオーバーフロー ドレイン○D0（排出部）との間に直列的に配置される。また、排出トランジスタ 121 は、垂直駆動部 42 から供給される排出信号○DG に従って駆動する。

- [01 17] 上記したように、D0\_125 は、増幅トランジスタ 132 のゲート電極に接続されている。よって、増幅トランジスタ 132 のゲート電極に接続されている部分や、D0\_125 と増幅トランジスタ 132 のゲート電極を接続している配線の一部に D0 昇圧配線 301\_4 を接続することで、D0\_125 を昇圧することができる。

- [01 18] 図 9 乃至 図 13 に示したドロップ昇圧配線 301-1 乃至 301\_4 のうちのいずれかが形成されていれば、D0\_125 を昇圧する構成とすることができる。また、D0 昇圧配線 301-1 乃至 301-4 の複数が形成されていても良い。例えば、図 10 に示したように、D0 昇圧配線 301\_1 と D0 昇圧配線 301\_2 が形成されている画素とすることもできるし、さらに D0\_301-3 が形成されている画素とすることもできる。

- [01 19] また、ドロップ昇圧配線 301-1 乃至 301-3 のいずれかまたは複数の配線と、増幅トランジスタ 132 のゲート電極に接続されるドロップ昇圧配線 301-4 を備える構成とすることもできる。

- [01 20] 複数の D0 昇圧配線 301 を備えることで、より効率良く D0\_125 を昇圧することができる構成とすることができる。

- [01 21] ドロップ昇圧配線 301 は、他の層（図 2 のような構成の場合、配線層 61-2 乃至 61\_4 のいずれかの層）に形成され、所定の電圧を供給する電圧源

と接続されている配線と接続されている。FD昇圧配線301に電圧がかけられるタイミングについて、図14のタイミングチャートを参照して説明する。

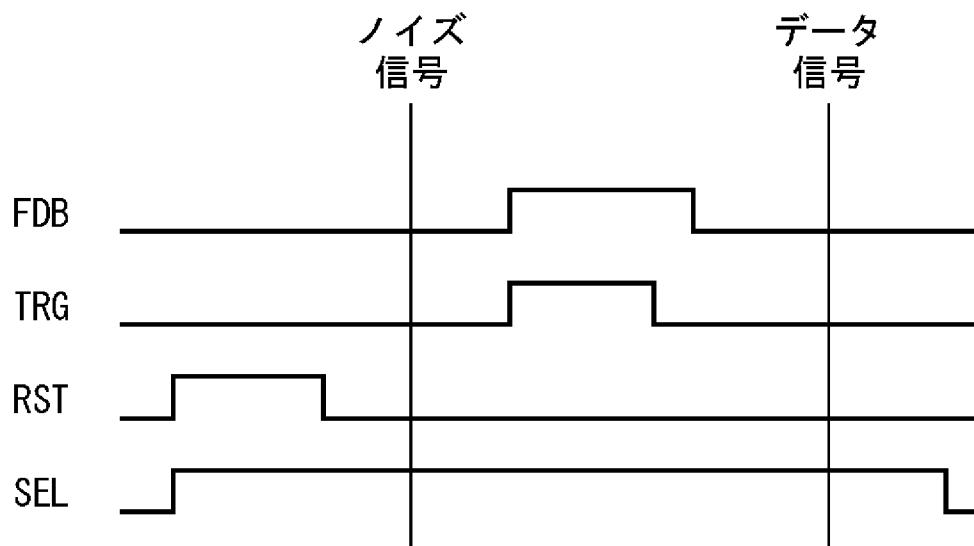

- [0122] 図14では、FD昇圧配線301に電圧を印加する時にオン(High)にされる制御信号を信号FDBと表し、第2の転送トランジスタ124が電荷を転送する時にオン(High)にされる制御信号を信号TRGと表し、リセットトランジスタ131がリセット動作を行う時にオン(High)にされる制御信号を信号RSTと表し、選択トランジスタ133が選択されたときにオン(High)にされる制御信号を信号SELと表す。

- [0123] 画素50に対する読み出し動作としては、読み出し行の単位画素の光電変換素子から不要な電荷が掃き出される(リセットされる)。このリセット動作時には、信号SELはHighの状態とされ、信号RSTは、所定の時間だけHighの状態とされる。リセット動作により、ノイズ信号が取得される。

- [0124] ノイズ信号が取得されたあと、露光が開始され、PD51に電荷が蓄積される。図14では図示していないが、露光終了後、PD51から電荷保持部54への電荷の転送が行われ、電荷保持部54に電荷が蓄積される。このPD51から電荷保持部54への電荷の転送は、全画素同時に行われることで、グローバルシャッタが実現される。

- [0125] 電荷保持部54に蓄積された電荷をFD125に転送するとき、第2の転送トランジスタ124を制御する信号TRGがHighにされ、FD昇圧配線301への電圧を制御する信号FOBがHighにされる。第2の転送トランジスタ124の動作により、電荷保持部54からFD125に電荷が転送されるとき、FD昇圧配線301に電圧がかけられることで、FD125が昇圧される。

- [0126] 信号TRGがLowの状態に戻された少し後の時点で、信号FOBがLowの状態に戻される。FD125に転送された電荷は、データ信号として、垂直信号線47を介してカラム処理部43(図1)に供給される。カラム処理部43にて、データ信号からノイズ信号が除去される等の処理が実行されること

で、画素 50 の画素値が算出される。

[01 27] このように、D0 125 に電荷が転送されるとき、D○昇圧配線 301 に電圧がかけられ、「0 125 が昇圧される。よって、本技術によれば、昇圧量を確保し、変換効率を上げることが可能となる。またダイナミックレンジを確保し、ノイズを低減させることに対しても効果がある。

[01 28] <縦型トランジスタに適用した場合>

上記した D0 昇圧配線 301 を備える画素 50において、読み出しを行うトランジスタを縦型トランジスタとして構成することができる。図 15 に、電荷保持部 54 からの電荷の読み出しを行う第 2 の転送トランジスタ 124 を、縦型トランジスタで構成した場合の画素 50 の断面図を示す。

[01 29] 図 15 に示した画素 50 は、図 2 に示した画素 50 に、縦型トランジスタを追加した構成とされている点が異なり、他の部分は同様であるため、その説明は省略する。第 2 の転送トランジスタ 124 を構成する読み出しへ 331 は、電荷保持部 54 の内部にまで達する位置まで形成されている。すなわち、電荷保持部 54 から電荷を読み出す読み出しへ 331 は、電荷保持部 54 に対して垂直方向と水平方向に形成され、垂直方向に形成されている読み出しへ 331 は、電荷保持部 54 に接するように形成されている。

[01 30] このような縦型トランジスタを用いることで、変調力を向上させることができ、ポテンシャルを深化させることができる。一方で、D0 昇圧配線 301 が形成されていない構成であり、FD]25 が昇圧されない場合、D0 125 からのくみ上げが弱くなってしまう可能性がある。このことについて、図 16 を参照して説明する。

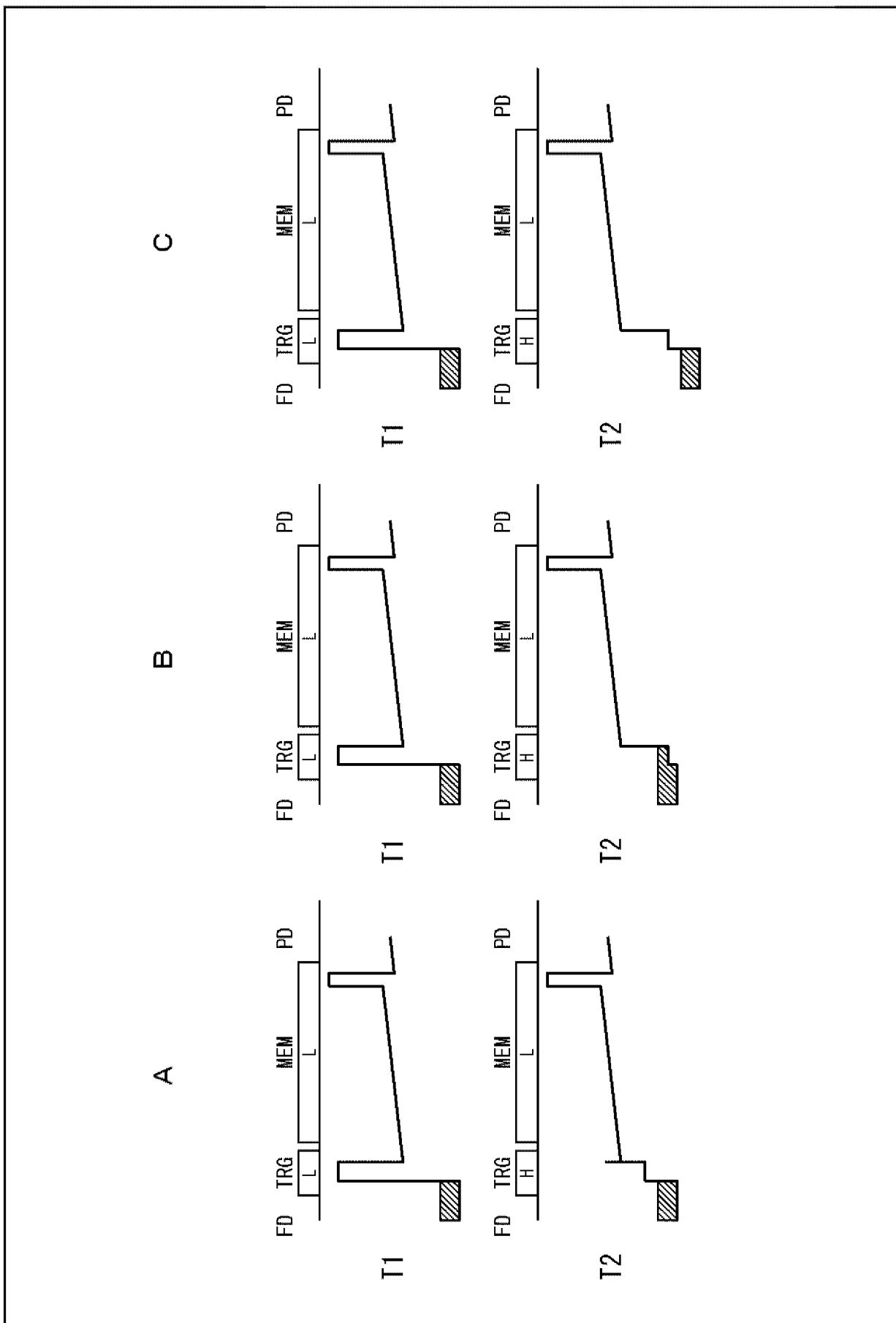

[01 31] 図 16において、D○は D0 125 を表し、TRG は第 2 の転送トランジスタ 124 を表し、M! 己 M! は電荷保持部 54 を表し、P○は P0 51 を表す。図 16 の八は、第 2 の転送トランジスタ 124 が縦型トランジスタでは無い場合のポテンシャルの変化を表し、図 16 の巳は、第 2 の転送トランジスタ 124 が縦型トランジスタの場合のポテンシャルの変化を表し、図 16 の

○は、第2の転送トランジスタ124が縦型トランジスタであり、ド○昇圧配線301による昇圧が行われるときのポテンシャルの変化を表す。

- [0132] 図16の八を参照するに、時刻丁1において、第2の転送トランジスタ124と電荷保持部54が、の状態である。時刻丁2において、第2の転送トランジスタ124が山<sub>9</sub>トの状態にされると、第2の転送トランジスタ124のゲート下はポテンシャルは浅くなるが、バリアが発生してしまい、電荷保持部54からド0125への転送が妨げられる可能性がある。

- [0133] 図16の巳を参照するに、図16の八の時刻丁1と同じく、第2の転送トランジスタ124と電荷保持部54が、の状態である。時刻丁2において、第2の転送トランジスタ124が山<sub>9</sub>トの状態にされると、縦型トランジスタのため、変調力が向上し、バリアがない状態とすることができます。しかしながら、ゲート下が深くなり、ゲート下に電荷が残ってしまう可能性がある。

- [0134] 図16の○を参照するに、図16の八の時刻丁1と同じく、第2の転送トランジスタ124と電荷保持部54が、の状態であるとき、ド0125には、所定の電荷が蓄積されている状態のときに、時刻丁2において、第2の転送トランジスタ124がHセトの状態にされ、かつドロ昇圧配線301に電圧がかけられることで、「0125が昇圧される。「0125が昇圧されることで、ド0125のポテンシャルが深くなる。よって、図16の巳の時刻丁2のときと同じく、ゲート下が深くなつても、さらに、ド○125を深い状態にできるため、ゲート下に電荷が残ってしまうような状況が発生することを防ぐことができる。

- [0135] このように、縦型トランジスタを用いた場合も、ド○昇圧配線301を形成し、ド0125を昇圧させることで、昇圧量を確保し、変換効率を上げることが可能となり、ダイナミックレンジを確保し、ノイズを低減させることができる。

- [0136] <○○○方式による読み出しに適用した場合>

上記したド0昇圧配線301を備える画素50を、00方式で読み出しき

行うイメージセンサに適用することができる。○○○方式での読み出しあとは、隣り合った素子間の電気的な結合を利用して、電荷を次々に移動させることによりP051に蓄積された電荷（信号）を読み出す方式である。

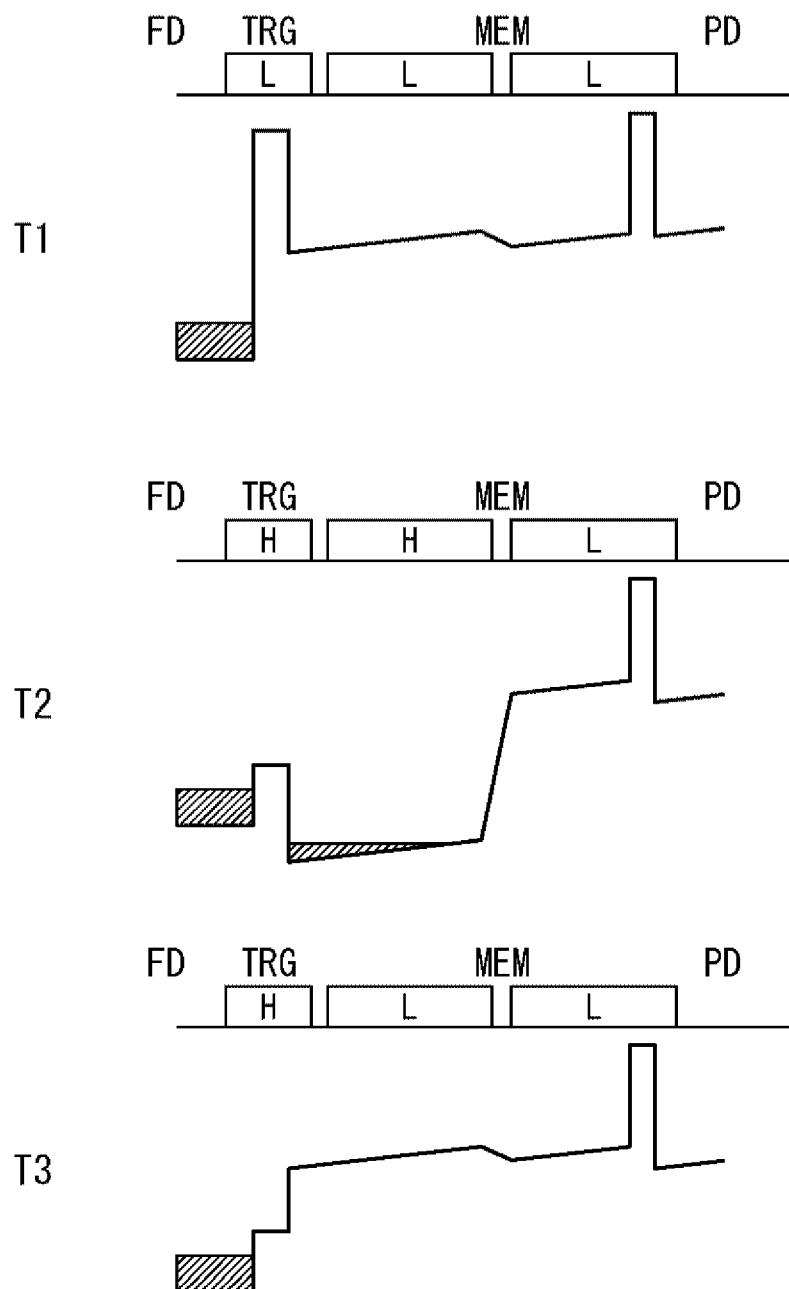

- [0137] 図17は、○○○方式による読み出し時のポテンシャルの変化を説明するための図である。図17に示した例では、電荷保持部54（図中M!巳M!と表記）が2つ形成され、P051、第1の電荷保持部54、第2の電荷保持部54、FD]25の順で、電荷が移動する場合を示している。時刻丁1において、第1の電荷保持部54、第2の電荷保持部54、および第2の転送トランジスタ124が、 $\text{L}_{\text{O}\text{E}\%}$ の状態であるとき、「0125には、所定の電荷が蓄積されている。

- [0138] このような状態のときに、時刻丁2において、第2の電荷保持部54と第2の転送トランジスタ124が山<sub>9</sub>トの状態にされると、D0125よりも、第2の電荷保持部54のポテンシャルが深くなる。このような状態が発生すると、D0125から第2の電荷保持部54に電荷が逆流してしまう可能性がある。

- [0139] 時刻丁2の後の時点の時刻丁3において、第2の電荷保持部54が $\text{L}_{\text{O}\text{E}}$ の状態に戻され、第2の転送トランジスタ124は山<sub>9</sub>トの状態のまま維持される。このとき、D0昇圧配線301に電圧がかけられることで、D0125が昇圧されることで、「0125のポテンシャルを電荷保持部54のポテンシャルよりも深くすることが可能となる。

- [0140] 電荷が逆流することを防ぐためには、D0125を昇圧し、電荷保持部54よりも深いポテンシャルとなるようにする。このD0125の昇圧に対しても、上記したD0昇圧配線301が形成された構造とすることで、対応することができる。

- [0141] よって、C00方式での読み出しに対しても本技術を適用することで、昇圧量を確保し、変換効率を上げることが可能となり、ダイナミックレンジを確保し、ノイズを低減させることができる。

- [0142] 縦型トランジスタとC00方式が適用された画素50における動作について

て、図18を参照して説明する。

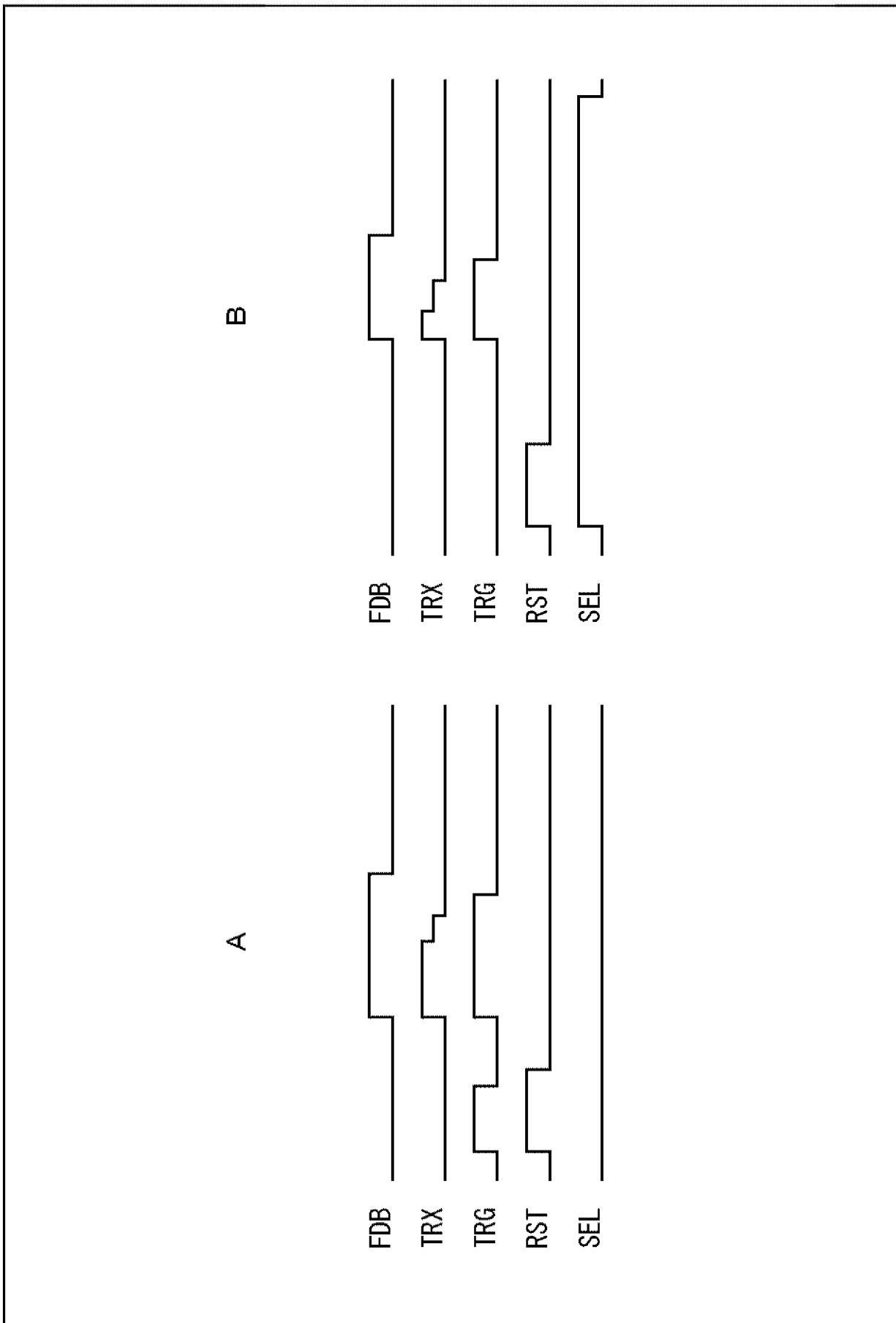

- [0143] 図18の八は、 $\sqcap$ 口5 1からの電荷を電荷保持部5 4に転送するときの各制御信号の山<sub>911</sub>と<sub>101</sub>の状態のタイミングを表し、図18の巳は、電荷保持部5 4からの電荷を「0 125」に転送するときの各制御信号の山<sub>9</sub>ト<sub>10</sub>の状態のタイミングを表す。図18中、ド○巳、丁<sub>14</sub>○、R S T、および3 巳<sub>1</sub>は、図14と同じである。図18中、丁<sub>14</sub>又は、第1の転送トランジスタ7 3を制御する制御信号であり、 $\sqcap$ 口5 1から電荷保持部5 4に電荷を転送させるときオン(High)にされる制御信号を表す。

- [0144] 図18の八を参照するに、信号丁<sub>14</sub>○と信号<sub>14</sub>3 丁が山<sub>9</sub>トの状態にされることで、ド0 125がリセットされる。リセット後、信号ド○巳、信号丁<sub>14</sub>X、および信号丁RGがHighの状態にされることで、ド○昇圧配線3 0 1に所定の電圧がかけられ、FD] 2 5が昇圧された状態で、9 0 5]から電荷保持部5 4への電荷の転送が行われ、電荷保持部5 4からド巳1 2 5への電荷の転送が行われる。

- [0145] ? 0 5 1から電荷保持部5 4への電荷の読み出しは、全画素一斉に行われるため、信号3 巳<sub>1</sub>は、Lowの状態のままである。図18の巳を参照するに、電荷保持部5 4に蓄積された電荷を転送するときは、画素毎に順次行われるため、読み出し対象とされた画素の選択トランジスタ1 3 3に対する信号3 巳<sub>1</sub>は、山<sub>9</sub>トの状態にされる。信号3 巳<sub>1</sub>が山<sub>9</sub>トの状態にされたとき、信号R S TもHighの状態にされ、一定の期間だけ、リセットトランジスタ1 3 1がオンの状態にされる。

- [0146] 電荷保持部5 4からFD1 2 5に電荷が転送されるとき、信号ド○巳、信号丁<sub>14</sub>又、および信号丁RGがHighの状態にされる。よって、ド0昇圧配線3 0 1に所定の電圧がかけられ、ド0 125が昇圧された状態で、9 0 5 1から電荷保持部5 4への電荷の転送が行われ、電荷保持部5 4からド巳1 2 5への電荷の転送が行われる。

- [0147] このような動作が順次繰り返されることで、 $\sqcap$ 口5 1で蓄積された電荷が、順次電荷保持部5 4やド0 125に転送される。また、電荷が転送される

とき、D0\_125が昇圧されるため、昇圧量を確保し、変換効率を上げることが可能となり、ダイナミックレンジを確保し、ノイズを低減させることができる。

[0148] なお、リセット時のくみ上げを抑制したいときには、一度フローティング状態を作つてからリセット動作が行われるようにも良い。また、縦型トランジスタで、00方式を適用した場合、電荷保持部54を完全にリセットするために、一度D0\_125がフローティングとなるタイミングでD0昇圧配線30\_1に電圧をかけ、FD\_125を昇圧するようにしても良い。

[0149] <具体的な配線形状>

以下に、D0配線126やドロ昇圧配線30\_1の具体的な形状の一例を示す。上記したように、ドロ昇圧配線30\_1の形状や配置位置は、J口5\_1や電荷保持部54の配置や、他の配線との関わりにより設定される。そこで、以下に、J口5\_1、電荷保持部54、他の配線などの配置や形状の具体的な一例を示し、ドロ昇圧配線30\_1の形状や配置位置について説明を加える。

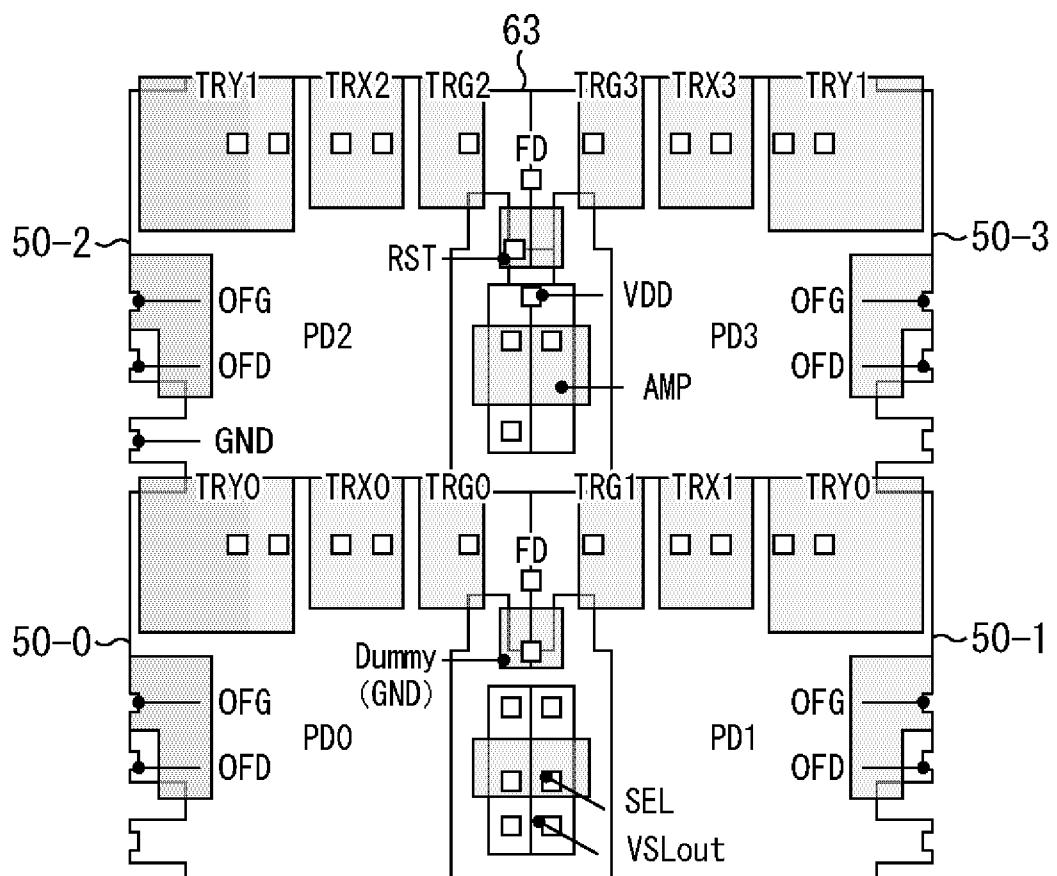

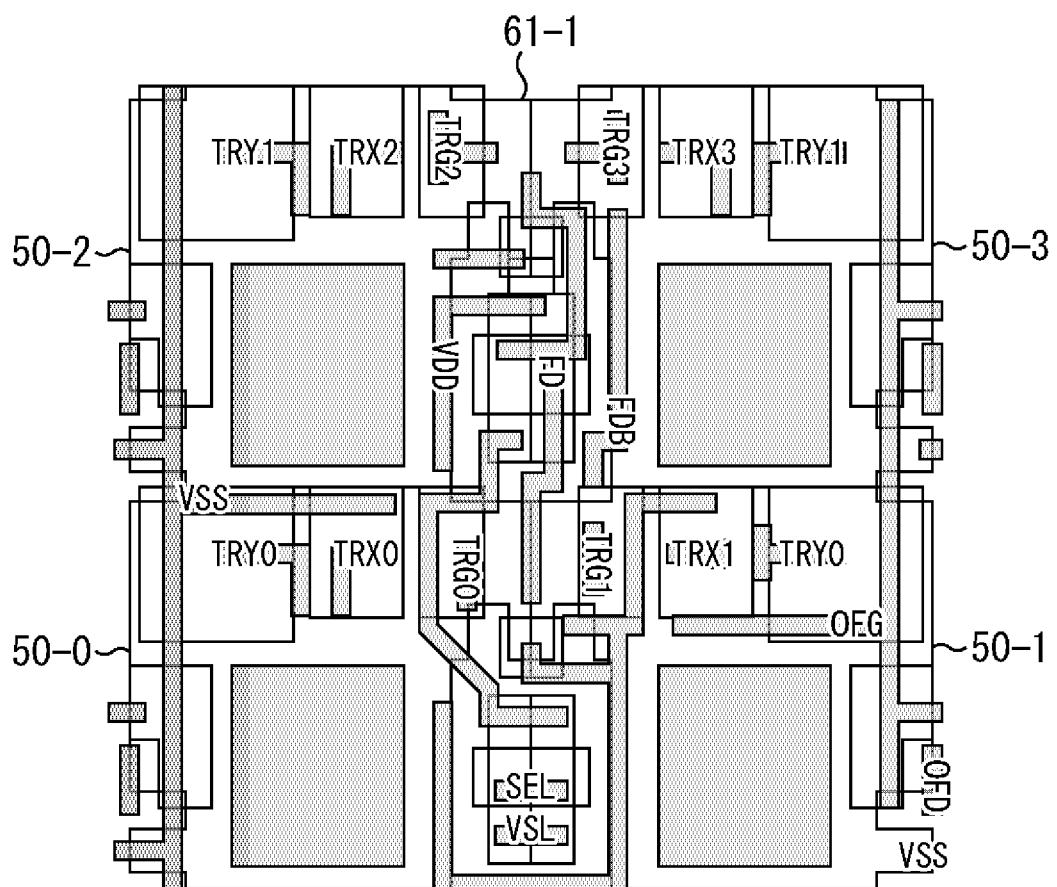

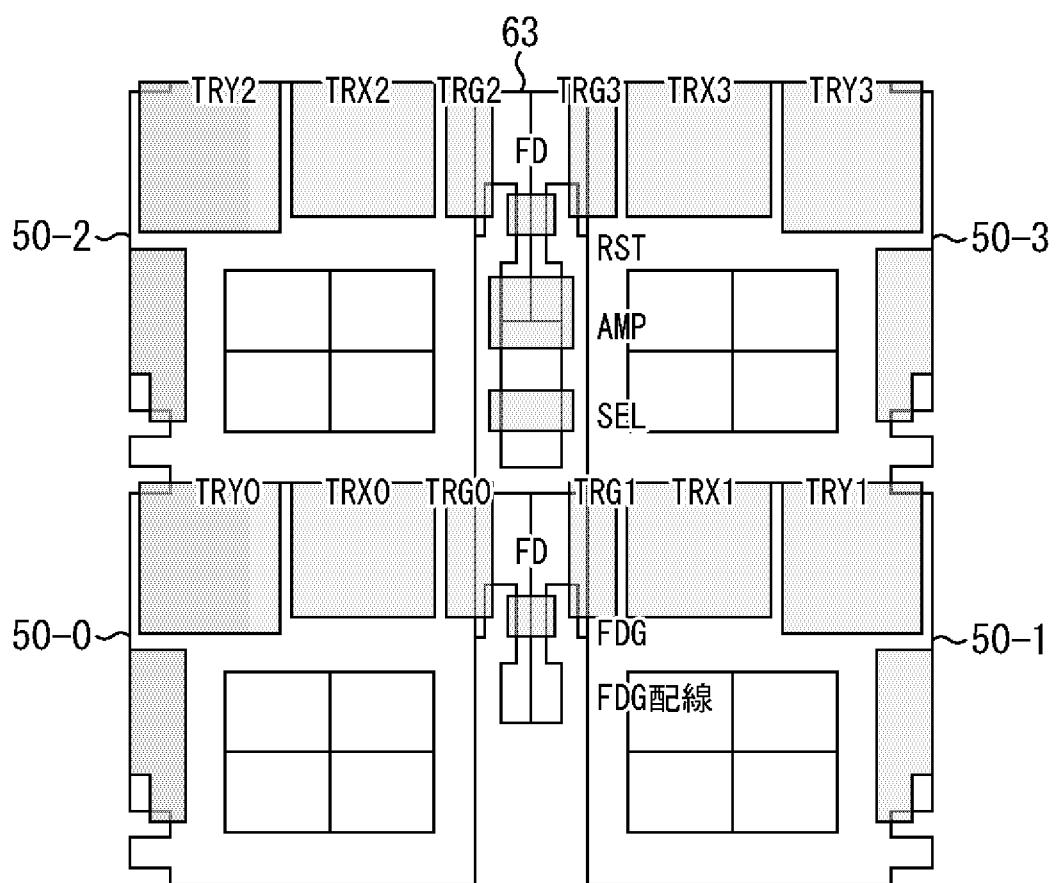

[0150] 図19は、半導体基板63の平面図であり、J口5\_1などの配置位置や形状の具体的な一例を示す図である。図20は、図19に示した構成に対応する回路図である。図19は、2×2に配置された4画素を1共有単位としたときの図である。左下に画素50\_0が配置され、右下に画素50\_1が配置され、左上に画素50\_2が配置され、右上に画素50\_3が配置されている。

[0151] 画素50\_1にはJ0\_2が含まれている。図19乃至図24では共通の符号を用い、各層の配線などの接続関係がわかりやすくなるように、上述した説明に用いた符号とは異なる符号を付す。画素50\_0に含まれるJ0\_0は、上記した説明においてはJ口5\_1に該当する。他の部分も同様に、符号以外の部分は、上記した説明と同様であり、その説明は適宜省略する。

[0152] 画素50\_0のJ0\_0の左側には、○DGと○DGが形成され、上部には、丁<sub>1%</sub>Y0、丁RX0、および丁<sub>1%</sub>G0が形成されている。図19では図示していないが、丁<sub>1%</sub>Y0と丁RX0が形成されている領域には、IVI\_EIVI0(

電荷保持部 54 に該当)が形成されている。

[0153] 画素 50-0 に形成されている P00、○ド〇、○ド〇、P〇〇、丁<sub>¶</sub>Y0、丁RX0、丁<sub>¶</sub>〇〇、<sub>1V1</sub>巳<sub>1V1</sub>0 は、図 20 に示した回路図のように接続されている。1 画素における回路構成については、図 13 を参照して説明したので、ここでは説明を省略する。

[0154] 図 19、図 20 に示した構成においては、丁<sub>¶</sub>Y0 が追加された構成とされている。丁<sub>¶</sub>Y0 は、電荷保持部 54 から P051 (図 19、図 20 に示した画素 50-0においては、<sub>1V1</sub>巳<sub>1V1</sub>0 から P〇〇) に電荷が逆流するのを防止するゲートとして機能し、図 19、図 20 に示したように、P〇〇と丁RX0との間に設けられる。

[0155] 丁<sub>¶</sub>Y0 (第 3 の転送トランジスタと適宜記述する) を設け、丁<sub>¶</sub>Y0 を P〇〇から<sub>1V1</sub>巳<sub>1V1</sub>0 へ電荷を転送するときにオンにし、その後、P〇〇に電荷が逆流しないように、オフにすることで、P口0への電荷の逆流を防ぐことができる。

[0156] また、丁<sub>¶</sub>Y0 は、電荷を蓄積するメモリ機能を有するように構成することができる。図 20 の回路図に示したように、<sub>1V1</sub>巳<sub>1V1</sub>0 は、丁<sub>¶</sub>Y0 と丁<sub>¶</sub>父〇の間と、丁RX0 と丁<sub>¶</sub>G0 の間に形成されている。電荷保持部 54 は、2 つの電荷保持部 54 で形成され、そのうちの 1 つは、丁<sub>¶</sub>Y0 と丁<sub>¶</sub>父〇の間に形成され、丁<sub>¶</sub>Y0 が有するメモリ機能とすることができます。

[0157] 画素 50-0 と同様に、画素 50-1 には、90}、○ド〇、○ド〇、丁<sub>¶</sub>Y0、丁<sub>¶</sub>父1、丁<sub>¶</sub>〇1、<sub>1V1</sub>巳<sub>1V1</sub>1 が形成されている。画素 50-2 には、902、○ド〇、○ド〇、丁<sub>¶</sub>Y1、TRX2<sub>S</sub> TRG2<sub>S</sub> <sub>1V1</sub>巳<sub>1V1</sub>2 が形成されている。画素 50-3 には、P03、○ド〇、○ド〇、丁<sub>¶</sub>Y1、丁RX3、丁<sub>¶</sub>〇3、<sub>1V1</sub>巳<sub>1V1</sub>3 が形成されている。

[0158] 図 3 等を参照して説明した場合を同じく、図 19 に示した P0 などの配置は、左右に配置された画素同士、例えば、画素 50-0 と画素 50-1 は、左右対称となる配置とされ、上下に配置された画素同士、例えば、画素 50-0-〇と画素 50-2 は、周期的な対象性を有する配置とされている。

- [01 59] 周期的な対象性とは、例えば、画素 $50_0$ においては $\text{P}00$ の上部に $\text{R}\times0$ が配置され、同様に、画素 $50_2$ においては $\text{P}02$ の上部に $\text{T}_{\frac{1}{2}}2$ が配置されているといったように、1画素内で見たときに、同一の位置に同一のものが配置されていることを意味する。

- [01 60] さらに、図19に示したように、画素 $50_0$ と画素 $50_1$ の間には、 $3\text{E}_1$ （選択トランジスタ $133$ に該当）と $\text{D}0$ （ $\text{D}0125$ に該当）が形成されている。また、画素 $50_2$ と画素 $50_3$ との間には、 $\text{A}_{1V1}$ （増幅トランジスタ $132$ に該当）、 $\text{R}3\text{T}$ （リセットトランジスタ $131$ に該当）、および $\text{D}0$ が形成されている。

- [01 61]  $3\text{E}_1$ 、 $\text{D}0$ 、 $\text{A}_{1V1}$ 、および $\text{R}3\text{T}$ は、画素 $50_0$ 乃至 $50_3$ で共有されるため、図20に示したように、 $\text{T}_{\frac{1}{2}}\text{O}0$ 、 $\text{T}_{\frac{1}{2}}\text{O}1$ 、 $\text{T}_{\frac{1}{2}}\text{O}2$ 、および $\text{TRG}3$ は、 $\text{FD}$ と $\text{AMP}$ に接続されている。図20に示した回路図は、 $\text{S}3\text{L}$ （垂直信号線 $47$ に該当）8本を同時読み出し時の構成を示している。すなわち、図20に示したように、 $\text{S}3\text{L}$ は、8本形成され、そのうちの1本に、 $3\text{E}_1$ が接続された構成とされている。

- [01 62] ここで例えば、 $\text{TRY}\text{O}$ は、画素 $50_0$ と画素 $50_1$ にそれぞれ形成されているが、画素 $50_0$ の $\text{TRY}\text{O}$ と画素 $50_1$ の $\text{TRY}\text{O}$ は、後述する $\text{T}_{\frac{1}{2}}\text{Y}0$ 配線（図23）に接続されている。すなわち、同一の配線に接続されている $\text{T}_{\frac{1}{2}}\text{Y}0$ には、同一の符号（ $\text{T}_{\frac{1}{2}}\text{Y}0$ の場合、 $\text{O}$ が符号に該当）を付してある。他の部分も同様である。

- [01 63] 図21は、図19に示した半導体基板 $63$ に積層されている配線層 $61_1$ に配線されている配線などの配置や形状を表す図である。配線層 $61_1$ には、半導体基板 $63$ に形成されている $\text{P}$ 口の位置に、例えば金属で形成された遮光膜が形成されている。

- [01 64] また、例えば、図19に示した半導体基板 $63$ の画素 $50_0$ の $\text{T}_{\frac{1}{2}}\text{Y}0$ が形成されている部分には、その $\text{TRY}\text{O}$ のゲートが、配線層 $61_1$ に形成されている。同じく、配線層 $61_1$ には、図19に示した半導体基板 $63$ の画素 $50_0$ の $\text{T}_{\frac{1}{2}}\text{Y}0$ が形成されている部分に、その $\text{T}_{\frac{1}{2}}\text{Y}0$ のゲー

トが形成されている。また配線層 6\_1\_1 には、図 19 に示した半導体基板 6\_3 の画素 50—0 の  $\text{丁}_{\frac{1}{4}}$  G0 が形成されている部分に、その  $\text{丁RG}\bigcirc$  のゲートが形成されている。

- [0165] 配線層 6\_1\_1 には、他の画素 50\_1 乃至 50\_3 にそれぞれ形成されている  $\text{丁}_{\frac{1}{4}}$  Y、 $\text{丁}_{\frac{1}{4}}$  ハ、 $\text{丁RG}$  に対するゲートも、対応する位置に形成されている。また、選択トランジスタ (3 己<sub>L</sub>)、増幅トランジスタ ( $\text{八}_{1V1}$  P)、リセットトランジスタ (RS<sub>T</sub>) のゲートも、それぞれ配線層 6\_1\_1 に形成されている。

- [0166] また配線層 6\_1\_1 には、半導体基板 6\_3 に形成されているド0を接続するド0配線 12\_6 も形成されている。ド○配線 12\_6 (図中、ド○と記述してある線)は、例えば、図 3 に示した例では、直線形状で形成されている例を示したが、図 2\_1 では、直線を組み合わせた折れ線で形成され、図中上部に形成されているド口と下部に形成されているド口を接続するように形成されている。

- [0167] 図 2\_1 に示したド0配線 12\_6 は、 $\text{八}_{N!}P$  に接続される V0\_0 配線を避けるように形成するパターンとされている。VDD 配線は、図 19 の  $\text{八}_{1V1}$  P の上側に形成されている V0\_0 という記載したビアと接続されている。このように、図 19、図 2\_1 に示した P0 や配線などのパターンにおいては、ド0配線 12\_6 は、他の配線との関係で、一部、他の配線を迂回する形状で形成されている。

- [0168] ド○昇圧配線 3\_0\_1 (図中、ド○已と記述してある線)は、ド○配線 12\_6 の近傍に、平行して形成されている。ド0昇圧配線 3\_0\_1 は、ド○配線 12\_6 と少なくとも一部が平行した部分を有するように形成されている。

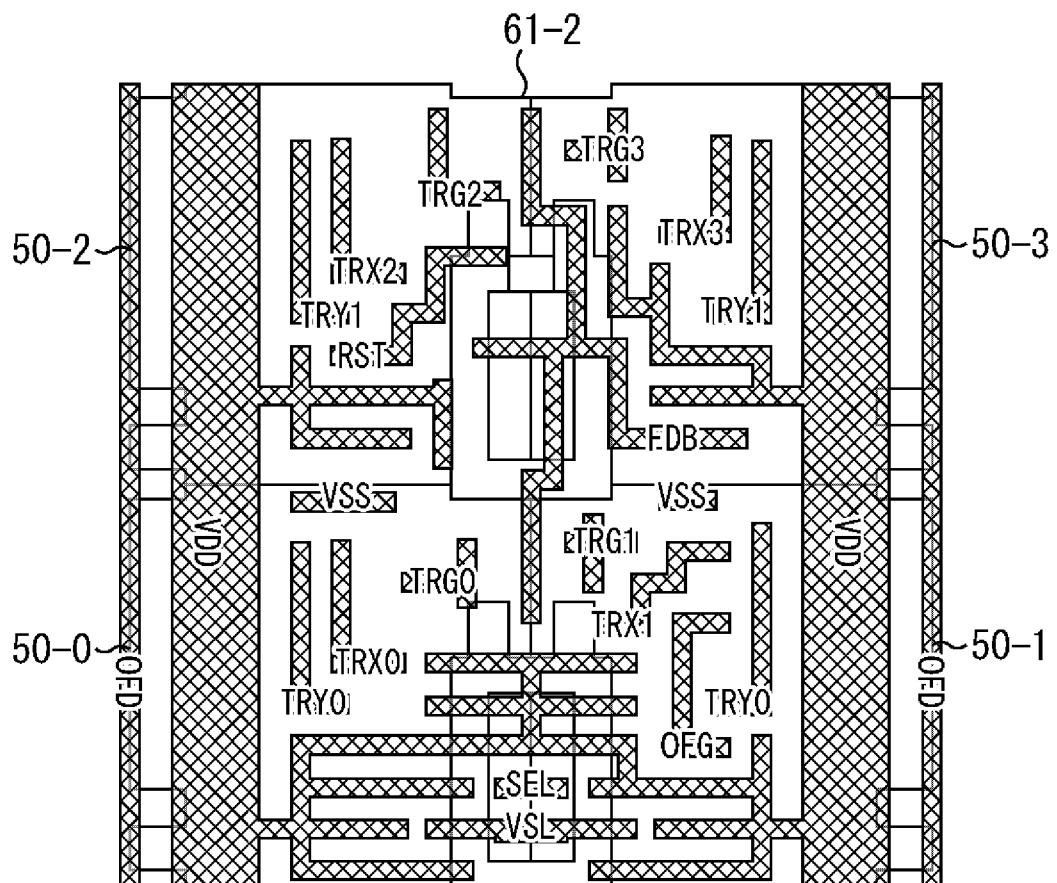

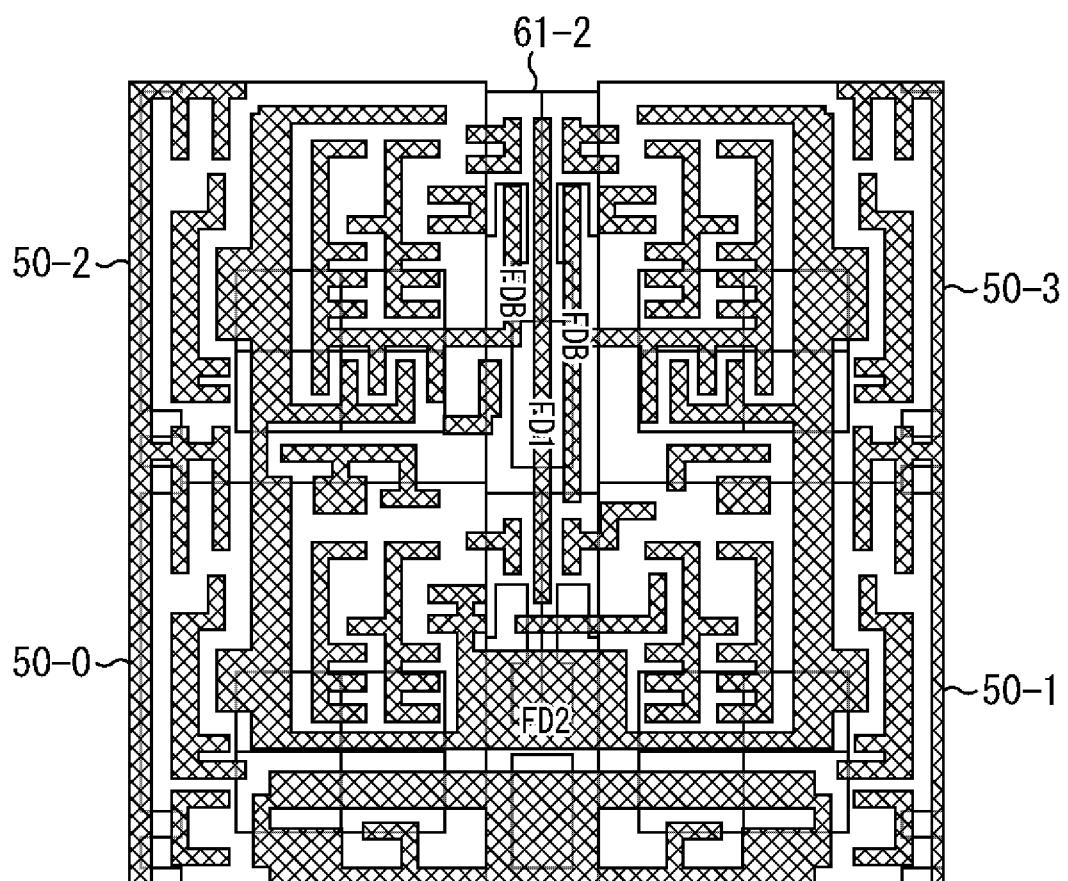

- [0169] 図 2\_2 は、図 2\_1 に示した配線層 6\_1\_1 に積層されている配線層 6\_1\_2 に配線されている配線などの配置や形状を表す図である。配線層 6\_1\_2 には、配線層 6\_1\_1 に形成されている配線と配線層 6\_1\_3 や配線層 6\_1\_4 の配線とを接続するための配線が形成されている。

- [0170] 図 2\_2 に示した例は、図 1\_1 を参照して説明した他の層にド0昇圧配線 3

○1\_3を形成した場合を示しているため、配線層61—2にも、ド○昇圧配線301(図中、ド0巳と記述してある線)が形成されている。すなわち、図21、図22に示した例は、図9を参照して説明したド0昇圧配線301\_1と図11を参照して説明したド0昇圧配線301\_3を備える構成とされている場合を示している。

[0171] 図11を参照して説明したように、ド0配線126が形成されている配線層61—1とは異なる配線層61—2に形成されているド0昇圧配線301は、ド0配線126と略同位置に、略同一の形状で形成されている。

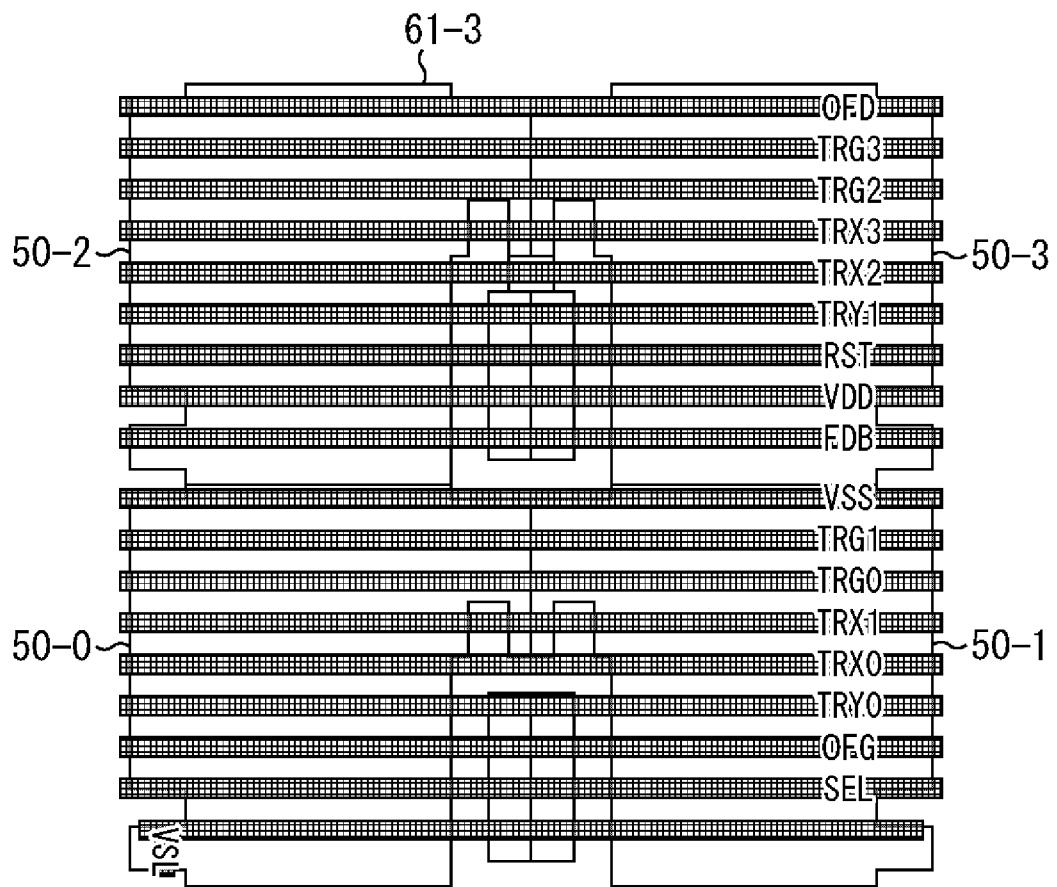

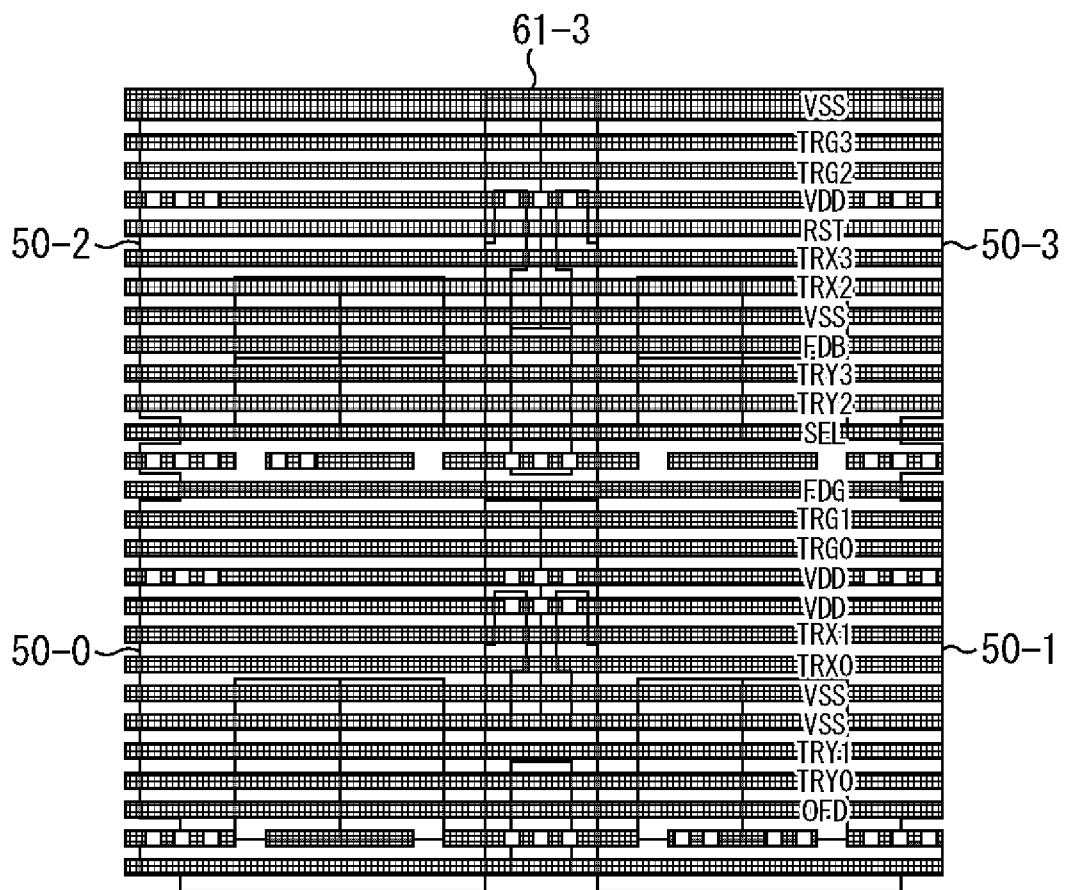

[0172] 図23は、図22に示した配線層61\_2に積層されている配線層61\_3に配線されている配線などの配置や形状を表す図である。配線層61\_3には、制御信号を流す信号線が形成されている。

[0173] 図23に示した配線層61\_3には、図中横方向に制御信号線が直線形状で形成されている。図中上部には、半導体基板63(図19)、配線層61-1(図21)、および配線層61-2(図22)にそれぞれ形成されている○ド口領域と、縦型のビアで接続される信号線○ド口が形成されている。

[0174] ○ド0信号線の図中下側には、半導体基板63(図19)、配線層61-1(図21)、および配線層61\_2(図22)にそれぞれ形成されている丁<sub>¶</sub>○3領域(ゲート)と、縦型のビアで接続される信号線丁<sub>¶</sub>○3が形成されている。信号線丁<sub>¶</sub>○3は、画素50—3(図19)の第2の転送トランジスタ(丁RG3)を制御する信号を流す信号線である。

[0175] 信号線丁RG3の図中下側には、半導体基板63(図19)、配線層61-1(図21)、および配線層61-2(図22)にそれぞれ形成されている丁<sub>¶</sub>○2領域(ゲート)と、縦型のビアで接続される信号線丁<sub>¶</sub>○2が形成されている。信号線丁<sub>¶</sub>○2は、画素50—2(図19)の第2の転送トランジスタ(丁RG2)を制御する信号を流す信号線である。

[0176] 信号線丁RG2の図中下側には、半導体基板63(図19)、配線層61-1(図21)、および配線層61-2(図22)にそれぞれ形成されている丁<sub>¶</sub>又3領域(ゲート)と、縦型のビアで接続される信号線丁<sub>¶</sub>又3が形

成されている。信号線  $\text{丁}_{\text{B}} \text{X} 3$  は、画素 50—3 (図 19) の第 1 の転送トランジスタ ( $\text{丁}_{\text{B}} \text{X} 3$ ) を制御する信号を流す信号線である。

[0177] 信号線  $\text{丁}_{\text{R}} \text{X} 3$  の図中下側には、半導体基板 63 (図 19)、配線層 61-1 (図 21)、および配線層 61-2 (図 22) にそれぞれ形成されている  $\text{丁}_{\text{B}} \text{X} 2$  領域 (ゲート) と、縦型のビアで接続される信号線  $\text{丁}_{\text{B}} \text{X} 2$  が形成されている。信号線  $\text{丁}_{\text{B}} \text{X} 2$  は、画素 50—2 (図 19) の第 1 の転送トランジスタ ( $\text{丁}_{\text{B}} \text{X} 2$ ) を制御する信号を流す信号線である。

[0178] 信号線  $\text{丁}_{\text{R}} \text{X} 2$  の図中下側には、半導体基板 63 (図 19)、配線層 61-1 (図 21)、および配線層 61-2 (図 22) にそれぞれ形成されている  $\text{丁}_{\text{B}} \text{Y} 1$  領域 (ゲート) と、縦型のビアで接続される信号線  $\text{丁}_{\text{B}} \text{Y} 1$  が形成されている。信号線  $\text{丁}_{\text{B}} \text{Y} 1$  は、画素 50—3 と画素 50—2 (図 19) の第 3 の転送トランジスタ ( $\text{丁}_{\text{B}} \text{Y} 1$ ) を制御する信号を流す信号線である

○

[0179] 信号線  $\text{丁}_{\text{B}} \text{Y} 1$  の図中下側には、半導体基板 63 (図 19)、配線層 61-1 (図 21)、および配線層 61-2 (図 22) にそれぞれ形成されている  $\text{丁}_{\text{B}} \text{Y} 3$  領域 (ゲート) と、縦型のビアで接続される信号線  $\text{R}_3 \text{丁}$  が形成されている。信号線  $\text{R}_3 \text{丁}$  は、画素 50—0 乃至 50—4 (図 19) で共有されるリセットトランジスタ (RS 丁) を制御する信号を流す信号線である。

[0180] 信号線  $\text{R}_3 \text{丁}$  の図中下側には、半導体基板 63 (図 19)、配線層 61-1 (図 21)、および配線層 61-2 (図 22) にそれぞれ形成されている  $\text{ソ}\text{○}\text{○}$  領域 (配線) と、縦型のビアで接続される信号線  $\text{VDD}$  が形成されている。信号線  $\text{V}00$  は、画素 50—0 乃至 50—4 (図 19) の所定の箇所に所定の電圧  $\text{V}00$  を供給する信号線である。

[0181] 信号線  $\text{V}00$  の図中下側には、半導体基板 63 (図 19)、配線層 61-1 (図 21)、および配線層 61-2 (図 22) にそれぞれ形成されている  $\text{ド}\text{○}\text{巳}$  領域 (配線) と、縦型のビアで接続される信号線  $\text{D}0\text{巳}$  が形成されている。信号線  $\text{D}0\text{巳}$  は、 $\text{D}0$  昇圧配線  $301$  ( $\text{ド}\text{○}\text{巳}$ ) に、所定の電圧を供給する信号線である。

- [0182] ここまで配線（図中上半分にある配線）は、主に、 $2 \times 2$  の 4 画素のうち、上部に配置されている画素 50—2 と画素 50—3 に係わる信号線であり、また画素 50—2 と画素 50—3 の間に配置されているトランジスタに係わる信号線である。

- [0183] 信号線 D0 左の図中下側には、半導体基板 63（図 19）、配線層 61—1（図 21）、および配線層 61—2（図 22）にそれぞれ形成されているゾ33 領域（比あせん）と、縦型のビアで接続される信号線 V33 が形成されている。信号線 V33 は、画素 50—0 乃至 50—4（図 19）の所定の箇所に所定の電圧 V33 を供給する信号線である。なお、電圧 V00 は正電圧であり、電圧 V33 は負電圧を示す。

- [0184] 信号線 V33 の図中下側には、半導体基板 63（図 19）、配線層 61—1（図 21）、および配線層 61—2（図 22）にそれぞれ形成されている丁<sub>1/4</sub>○1 領域（ゲート）と、縦型のビアで接続される信号線 丁RG1 が形成されている。信号線 丁RG1 は、画素 50—1（図 19）の第 2 の転送トランジスタ（丁RG1）を制御する信号を流す信号線である。

- [0185] 信号線 丁<sub>1/4</sub>○1 の図中下側には、半導体基板 63（図 19）、配線層 61—1（図 21）、および配線層 61—2（図 22）にそれぞれ形成されている丁<sub>1/4</sub>○0 領域（ゲート）と、縦型のビアで接続される信号線 丁<sub>1/4</sub>G0 が形成されている。信号線 丁<sub>1/4</sub>○0 は、画素 50—0（図 19）の第 2 の転送トランジスタ（丁<sub>1/4</sub>G0）を制御する信号を流す信号線である。

- [0186] 信号線 丁<sub>1/4</sub>G0 の図中下側には、半導体基板 63（図 19）、配線層 61—1（図 21）、および配線層 61—2（図 22）にそれぞれ形成されている丁<sub>1/4</sub>又1 領域（ゲート）と、縦型のビアで接続される信号線 丁<sub>1/4</sub>又1 が形成されている。信号線 丁<sub>1/4</sub>又1 は、画素 50—1（図 19）の第 1 の転送トランジスタ（丁<sub>1/4</sub>又1）を制御する信号を流す信号線である。

- [0187] 信号線 丁<sub>1/4</sub>又1 の図中下側には、半導体基板 63（図 19）、配線層 61—1（図 21）、および配線層 61—2（図 22）にそれぞれ形成されている丁<sub>1/4</sub>又○領域（ゲート）と、縦型のビアで接続される信号線 丁<sub>1/4</sub>又○が形

成されている。信号線  $\text{丁}_{\text{P}4}\text{X}_0$  は、画素 50—0 (図 19) の第 1 の転送トランジスタ ( $\text{丁}_{\text{P}4}\text{X}_0$ ) を制御する信号を流す信号線である。

[0188] 信号線  $\text{丁R}_{\text{X}0}$  の図中下側には、半導体基板 63 (図 19)、配線層 61-1 (図 21)、および配線層 61-2 (図 22) にそれぞれ形成されている  $\text{丁}_{\text{P}4}\text{Y}_0$  領域 (ゲート) と、縦型のビアで接続される信号線  $\text{丁}_{\text{P}4}\text{Y}_0$  が形成されている。信号線  $\text{丁R}_{\text{Y}0}$  は、画素 50—1 と画素 50—0 (図 19) の第 3 の転送トランジスタ ( $\text{丁}_{\text{P}4}\text{Y}_0$ ) を制御する信号を流す信号線である

○

[0189] 信号線  $\text{丁}_{\text{P}4}\text{Y}_0$  の図中下側には、半導体基板 63 (図 19)、配線層 61-1 (図 21)、および配線層 61-2 (図 22) にそれぞれ形成されている  $\text{O}_{\text{D}}\text{G}$  領域と、縦型のビアで接続される信号線  $\text{O}_{\text{D}}\text{G}$  が形成されている。

[0190] 信号線  $\text{O}_{\text{D}}\text{G}$  の図中下側には、半導体基板 63 (図 19)、配線層 61-1 (図 21)、および配線層 61-2 (図 22) にそれぞれ形成されている  $3_{\text{H}}\text{L}$  領域 (ゲート) と、縦型のビアで接続される信号線  $3_{\text{H}}\text{L}$  が形成されている。信号線  $3_{\text{H}}\text{L}$  は、画素 50—0 乃至 50—4 (図 19) で共有される選択トランジスタ ( $3_{\text{H}}\text{L}$ ) を制御する信号を流す信号線である。

[0191] 図中下半分にある配線は、主に、 $2 \times 2$  の 4 画素のうち、下部に配置されている画素 50—1 と画素 50—0 に係わる信号線であり、また画素 50—1 と画素 50—0 の間に配置されているトランジスタに係わる信号線である

○

[0192] このように配線層 61-3 には、信号線が形成されている。

[0193] ここで図 23 に示した配線層 61-3 に配線されている信号線  $\text{D}_0\text{H}$  と、 $\text{D}_0$  配線 126 (ドロ昇圧配線 301) に注目した場合、信号線  $\text{D}_0\text{H}$  とドロ配線 126 が直交する構造である場合と平行する構造である場合とがある

○

[0194] 図 3、図 5、図 7、図 8 に示した  $\text{D}_0$  配線 126 は、図中縦方向に形成されているため、これらの構造が採用された画素においては、図 23 中横方向に形成されている信号線  $\text{D}_0\text{H}$  とは直交する構造となる。この場合、ドロ昇

圧配線 301 も、ド0配線 126 と同方向に形成されるため、ド口昇圧配線 301 と信号線 ド○巳も、直交する構造となる。

[0195] 一方で、図4、図6に示したド0配線 126 は、図中横方向に形成されているため、これらの構造が採用された画素においては、図23中横方向に形成されている信号線 ド0 巳とは平行する構造となる。この場合、ド○昇圧配線 301 も、ド0配線 126 と同方向に形成されるため、ド口昇圧配線 301 と信号線 ド0 巳も、平行する構造となる。

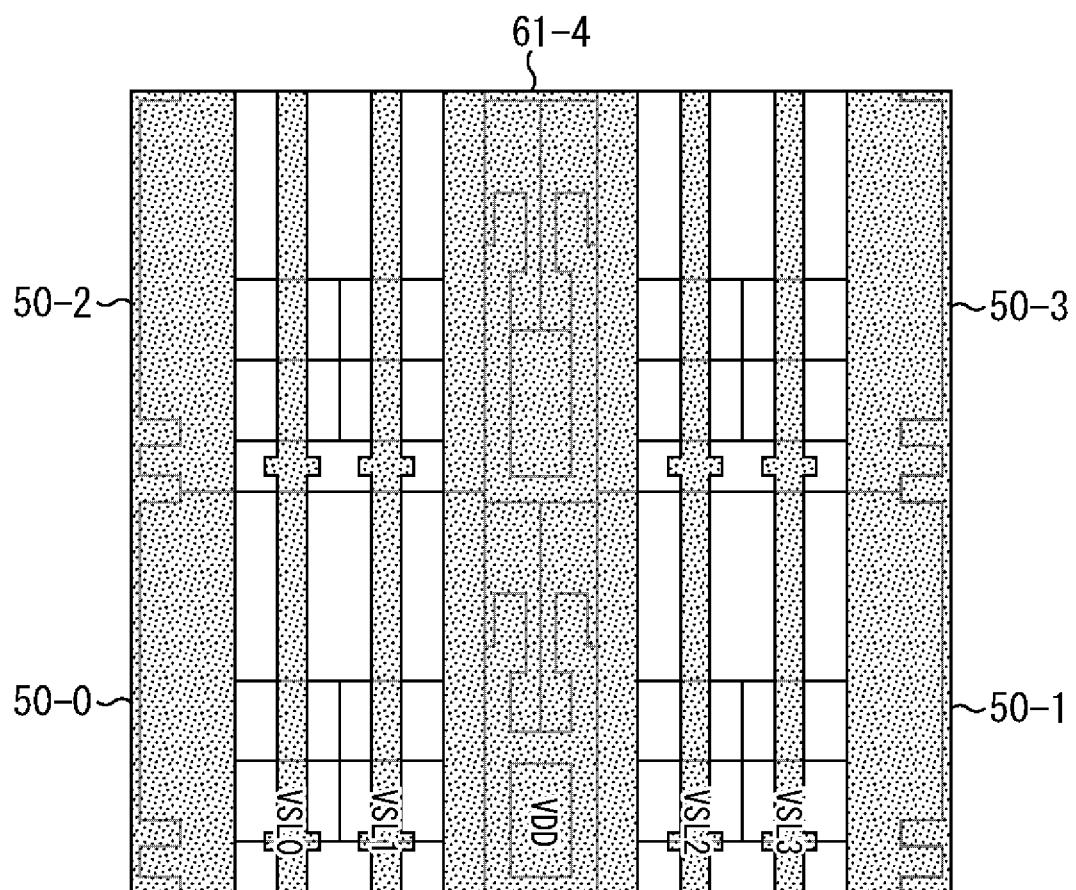

[0196] 図24は、図23に示した配線層 61\_3 に積層されている配線層 61\_4 に配線されている配線などの配置や形状を表す図である。配線層 61\_4 には、垂直信号線が形成されている。

[0197] 図20の回路図を参照して説明したように、垂直信号線が8本形成されている場合、配線層 61\_4 には、垂直信号線 VS\_0 乃至 7 が、図中縦方向に形成される。図19を再度参照するに、選択トランジスタ (3 巳) の下側に選択トランジスタからの出力を垂直信号線に出力するビア V3\_1 ○リ I が形成されており、このビア V3\_1 ○リ I は、配線層 61\_2 (図22) の V3\_1 と記載されている配線を介して、配線層 61\_3 (図23) の信号線 V3\_1 に接続されている。

[0198] 配線層 61\_3 の信号線 V3\_1 は、信号線 3 巳の下部に形成され、他の信号線と同じく、横方向に直線形状で形成されている。この信号線 V3\_1 は、配線層 61\_4 の垂直信号線 V3\_1\_0 乃至 7 のうちのいずれか1本の垂直信号線 V3\_1 と、ビアにより接続されている。

[0199] 上記した配線の位置や形状などは、一例であり、限定を示す記載ではない。

[0200] 図19乃至図23に示した例では、第3の転送トランジスタである丁<sub>14</sub> Y は、画素 50\_0 と画素 50\_1 にそれぞれ丁<sub>14</sub> Y\_0 が形成され、この丁<sub>14</sub> Y\_0 は、1本の信号線 丁<sub>14</sub> Y\_0 に接続されている。また画素 50\_2 と画素 50\_3 にそれぞれ丁<sub>14</sub> Y\_1 が形成され、この丁<sub>14</sub> Y\_1 は、1本の信号線 丁<sub>14</sub> Y\_1 に接続されている。

- [0201] 第3の転送トランジスタ( $\text{TR}_Y$ )は、905]( $\square$ 口○乃至3)から電荷保持部54( $\text{H}_{1V1} 0$ 乃至3)に、電荷を転送するときに用いられるトランジスタである。グローバルシャッタ方式である場合、 $\square$ 口51から電荷保持部54は、全画素同時に行われる。よって、第3の転送トランジスタ( $\text{TR}_Y$ )の制御は、全画素同一の制御で行うことも可能である。仮に、全画素同一の制御とした場合、全画素で共有される信号線 $\text{TR}_Y$ が形成された構成とすることも可能である。

- [0202] 上記したように、水平方向に配置されている画素、例えば、図19に示した例では、画素50\_0と画素50\_1で信号線 $\text{TR}_Y\bigcirc$ を共有し、画素50\_2と画素50\_3で信号線 $\text{TR}_Y1$ を共有する構成とすることで、水平方向に配置された画素50に対しては、同一の制御が行え、垂直方向に配置された画素50に対して、異なる制御を行うことが可能となる。

- [0203] このようなことが可能となることで、行毎に読み出し制御を行うことが可能となる。行毎に露光時間を迎えるといった制御を行うことも可能となる。なお、上記したように、全画素で共有される信号線 $\text{TR}_Y$ が形成された構成とすることも可能であり、全画素で共有される信号線 $\text{TR}_Y$ とすることで、信号線の数を減らすことができる。よって小スペース化したいときなどには、信号線 $\text{TR}_Y$ を、水平方向と垂直方向の両方向で共通化された構成としても良い。

- [0204] <縦型トランジスタを適用した場合>

- 図15、図16を参照して説明したように、電荷保持部54からの電荷の読み出しを行うトランジスタを、シリコン基板内まで到達しているゲートを備える縦型トランジスタで読み出すことで、変調力を向上させ、ポテンシャルを深化させた状態で読み出しが行える。

- [0205] このような縦型トランジスタを、フォトダイオード( $\square$ 口)からの読み出しに適用することもでき、 $\square$ 口からの読み出しに適用することで、その読み出しに対しても、変調力を向上させ、ポテンシャルを深化させた状態で読み出しが行えるようになる。

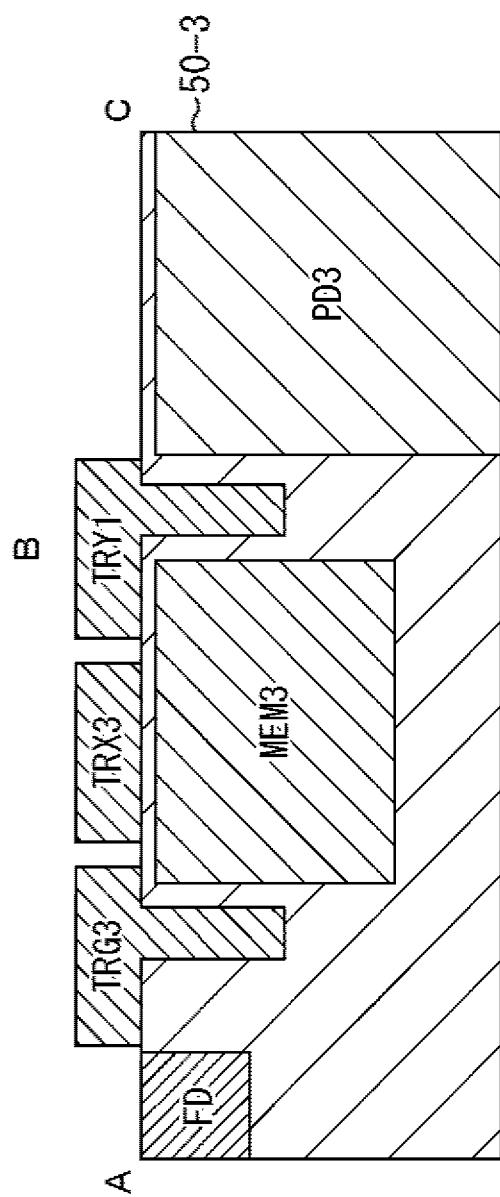

- [0206] 図25、図26を参照し、PDからの読み出しにも縦型トランジスタを適用した場合の画素50の構造について説明する。図25は、図19に示した半導体基板63の平面図と同図であるが、線分A—B—Cを画素50—3の部分に追加してある。この線分A—B—Cにおける断面図を、図26に示す。

- [0207] 図25、図26を参照するに、線分A—B—Cの部分には、点A側から順に、FD、TRG3、TRX3、TRY1、PD3が配置されている。なお、FD、TRG3、TRX3、TRY1、PD3は、図19乃至24に示した場合と同じ符号を用いている。

- [0208] FDとMEM3との間には、TRG3が形成されており、このTRG3は、縦型トランジスタで形成されている。図15を参照して説明したように、縦型トランジスタは、MEM3に対して垂直方向と水平方向に形成され、垂直方向に形成されている部分は、シリコン内まで掘り込まれて形成されている。

- [0209] 同様に、PD3とMEM3との間には、TRY1が形成されており、このTRY1は、縦型トランジスタで形成され、MEM3に対して垂直方向と水平方向に形成され、垂直方向に形成されている部分は、シリコン内まで掘り込まれて形成されている。

- [0210] TRY1は、PD3からMEM3に、電荷を転送するときに用いられるトランジスタである。TRY1を縦型トランジスタで構成することで、PD3からの電荷の読み出しを、変調力を向上させ、ポテンシャルを深化させた状態で行うことができる。

- [0211] このように、PD3(フォトダイオード51)からの読み出しを行うトランジスタ(TRY)と、MEM3(電荷保持部54)からの読み出しを行うトランジスタ(TRG)を、それぞれ縦型トランジスタで構成することで、フォトダイオード51からの読み出しと、電荷保持部54からの読み出しを、変調力を向上させ、ポテンシャルを深化させた状態で行うことができる。

- [0212] よって、フォトダイオード51と電荷保持部54の飽和(ダイナミックレ

ンジ)を向上させることができる。

[0213] フォトダイオード51からの読み出しを行うトランジスタを、縦型トランジスタで形成するのは、上記した実施の形態、および以下に説明する実施の形態に対して適用可能である。

[0214] <変換効率切替トランジスタを有する構成>

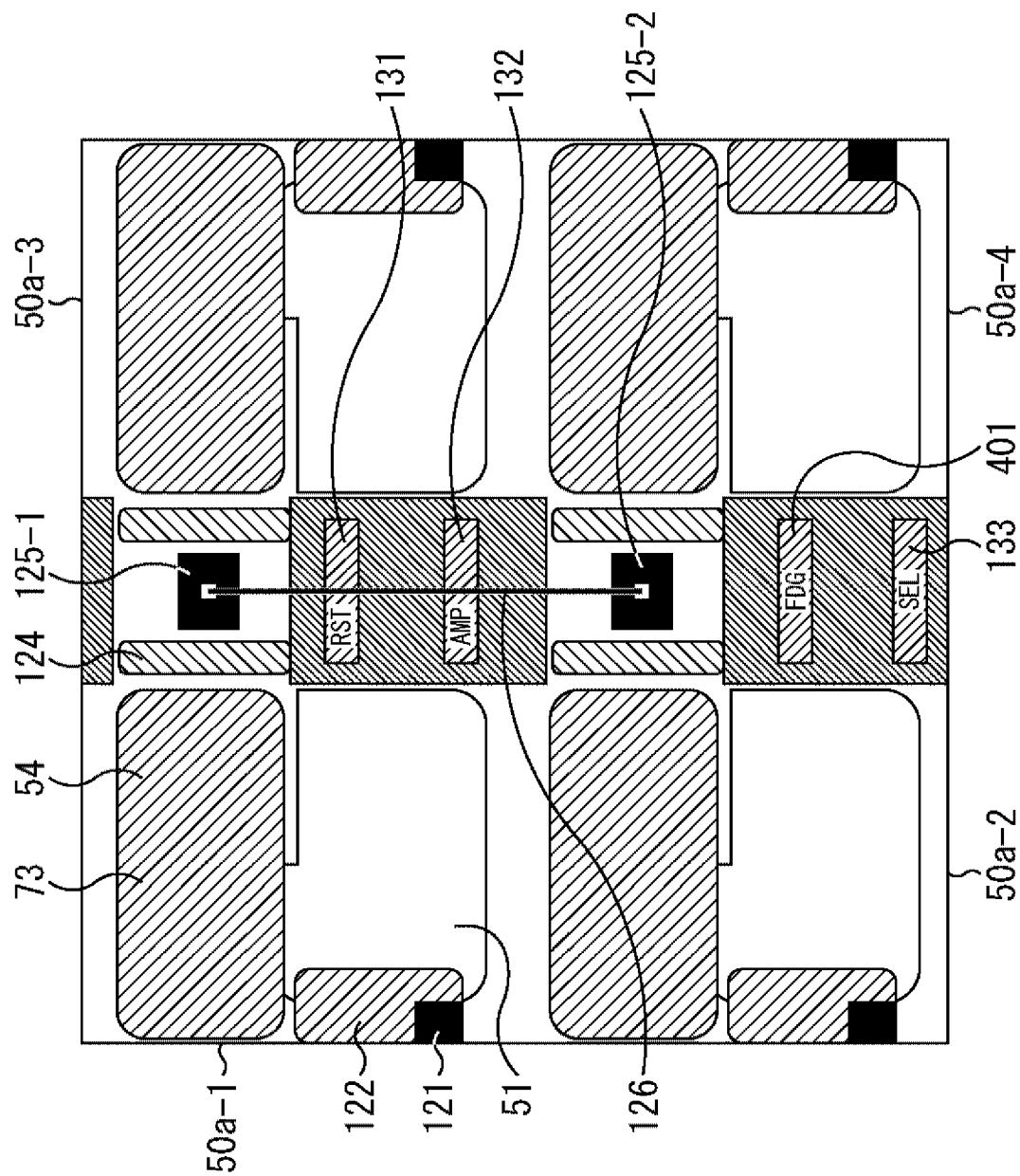

次に、変換効率切替トランジスタを有する画素(共有単位の画素群)について説明する。図27は、変換効率切替トランジスタ401を備える1共有単位の画素群の構成を示す図である。

[0215] 図27に示した1共有単位の画素群の構成は、図3に示した1共有単位の画素群の構成に、変換効率切替トランジスタ401を追加した点以外は、基本的に同様であるため、その説明は省略する。

[0216] 変換効率切替トランジスタ401はオンにされると、D0125の浮遊拡散領域が拡大し、D0125の容量が増え、変換効率が下げられるように構成されている。

[0217] 図28は、図10と同じく、D0125を昇圧する構成を有する4画素共有の画素構造を示す図である。図28では説明のためP051、「0125、D0配線126を示したが、図27に示したように、丁<sub>12</sub>ゲート73なども配置されている。

[0218] D0125-1とD0125-2は、D0配線126で接続されている。D0配線126の右側には、D0昇圧配線301-1が形成され、左側には、D0昇圧配線301\_2が形成されている。このような構成は、図10に示した構成と同様である。

[0219] さらに、図28に示した構成においては、D0昇圧配線301の外側に、ドロ変換用配線411が形成されている。また、D0125-2の下側には、変換効率切替トランジスタ401(図中、D0Gと記載)が形成されている。

[0220] 変換効率切替トランジスタ401がオフの状態のときは、D0配線126とドロ変換用配線411は、非接続の状態であり、D0125の容量として

は、ド0 125-1、ド0 125-2、およびド0配線126を合わせた容量の状態である。

[0221] 変換効率切替トランジスタ401がオンにされると、ド○配線126とドロ変換用配線411は、接続された状態となり、ド0 125の容量としては、ド0 125-1、ド0 125-2、ド0配線126、およびドロ変換用配線411を合わせた容量の状態となる。

[0222] 変換効率切替トランジスタ401がオンの状態のときは、ド0変換用配線411の分だけ、ド0 125の浮遊拡散領域が拡大し、変換効率が下がった状態となる。

[0223] 変換効率切替トランジスタ401と、ド0変換用配線411を備える画素においては、変換効率切替トランジスタ401がオフの状態のときに、ド0昇圧配線301によるド0 125の昇圧が行われるようにも良い。また変換効率切替トランジスタ401がオンの状態のときに、ド0昇圧配線301によるド0 125の昇圧が行われるようにも良い。また変換効率切替トランジスタ401のオン、オフに係わらず、ド0昇圧配線301によるド0 125の昇圧が行われるようにも良い。

[0224] 変換効率切替トランジスタ401がオンの状態のときは、ド0 125の浮遊拡散領域が拡大し、変換効率が下がった状態となるため、ド0昇圧配線301によるド0 125の昇圧が行われるようにすることで、変換効率が下がるようなことを防ぐことができる。

[0225] 変換効率切替トランジスタ401のオン、オフに係わらず、ド0昇圧配線301によるド0 125の昇圧が行われるようにした場合、変換効率切替トランジスタ401がオンのときにド0 125を昇圧させるためのド0昇圧配線301と、変換効率切替トランジスタ401がオフのときにド0 125を昇圧させるためのド0昇圧配線301とは異なる配線として別々に設けても良い。

[0226] 例えば、図27に示したようにド○昇圧配線301\_1とド0昇圧配線301-2が形成されている場合、変換効率切替トランジスタ401がオフの

ときには、FD昇圧配線301—1によるFD125の昇圧が行われ、変換効率切替トランジスタ401がオンのときには、FD昇圧配線301—1とFD昇圧配線301\_2によるFD125の昇圧が行われるようにしても良い。

[0227] また、変換効率切替トランジスタ401がオンのときとオフのときとでは、FD昇圧配線301にかけられる電圧が異なるように制御されるようにしても良い。

[0228] <具体的な配線形状>

次に、変換効率切替トランジスタ401を有する画素におけるFD配線126やFD昇圧配線301の具体的な形状の一例について説明を加える。図29は、半導体基板63の平面図であり、PD51などの配置位置や形状の具体的な一例を示す図である。図30、図31は、図29に示した構成に対応する回路図である。

[0229] 図29は、2×2に配置された4画素を1共有単位としたときの図である。左下に画素50\_0が配置され、右下に画素50\_1が配置され、左上に画素50\_2が配置され、右上に画素50\_3が配置されている。基本的な配置や形状は、図19に示した画素と同様であり、図19に示した画素に、変換効率切替トランジスタ401を追加した構成とされている点が異なる。

[0230] 変換効率切替トランジスタ401(図29中ではFDGと記載)は、画素50\_0と画素50\_1との間に形成されている。画素50\_2と画素50\_3との間には、SEL(選択トランジスタ133に該当)、AMP(増幅トランジスタ132に該当)、RST(リセットトランジスタ131に該当)、およびFD(FD125に該当)が形成されている。

[0231] 各画素50には、PD、OFD、OFG、TRY、TRX、およびTRGが形成されている。また、TRYとTRXが形成されている領域には、MEM(電荷保持部54に該当)が形成されている。

[0232] 画素50に形成されているPD、OFD、OFG、TRY、TRY、TRG、MEMは、図30、図31に示した回路図のように接続されている。1

画素における回路構成については、図13を参照して説明したので、ここでは説明を省略する。ただし、図29以降に示した画素の構成においては、丁<sub>¶</sub>丫は、画素毎に形成され、画素毎に制御されるように構成されている場合を例示してある。

- [0233] 図30、図31に示した回路図において、ド0\_1は、「0\_125に該当する部分を表し、ド0\_2は、ド○変換用配線4\_1\_1を表す。変換効率切替トランジスタ4\_0\_1がオンの状態になると、ド0\_1とド0\_2が1つのド0として機能するように構成されている。

- [0234] 図32は、図29に示した半導体基板6\_3に積層されている配線層6\_1\_1に配線されている配線などの配置や形状を表す図である。配線層6\_1\_1には、半導体基板6\_3に形成されている凹口の位置に、例えば金属で形成された遮光膜が形成されている。

- [0235] また配線層6\_1\_1には、図29に示した半導体基板6\_3の画素5\_0の丁<sub>¶</sub>丫が形成されている部分には、丁<sub>¶</sub>丫のゲートが形成されている。同じく、配線層6\_1\_1には、丁<sub>¶</sub>乂のゲート、TRGのゲートが形成されている。また、配線層6\_1\_1には、変換効率切替トランジスタ4\_0\_1(ド0G)のゲートも形成されている。

- [0236] また配線層6\_1\_1には、半導体基板6\_3内に形成されているド0領域を配線層6\_1\_2に形成されたド0配線126と接続されるビアが形成されている。また、配線層6\_1\_1には、ド口変換用配線4\_1\_1(図32中、ド0\_2と記載してある配線)が形成されている。

- [0237] 図33は、図32に示した配線層6\_1\_1に積層されている配線層6\_1\_2に配線されている配線などの配置や形状を表す図である。配線層6\_1\_2には、半導体基板6\_3に形成されているド0\_125の領域を接続するド0配線126(図中、ド0\_1と記載してある配線)が形成されている。このド○配線126に近接し、平行する形状で、ド0昇圧配線3\_0\_1(図33中、ド○巳と記載されている配線)が形成されている。図33に示した例は、ド0配線126を中心として、左右にド口昇圧配線3\_0\_1が形成されている例を

示している。

[0238] 図34は、図33に示した配線層61\_2に積層されている配線層61\_3に配線されている配線などの配置や形状を表す図である。配線層61\_3には、制御信号線が図中横方向(水平方向)に形成されている。図23に示した変換効率切替トランジスタ401が無い場合の画素の配線層61\_3と同じく、制御信号線として、信号線○ド○、信号線○ド○、信号線丁<sub>4</sub>丫、信号線丁<sub>4</sub>乂、信号線<sub>4</sub>3丁、信号線V00、信号線V33、信号線3巳<sub>1</sub>が形成されている。また、変換効率切替トランジスタ401を制御する信号を供給する信号線DGも形成されている。また、画素毎に、丁<sub>4</sub>丫が設けられているため、丁<sub>4</sub>丫0乃至丁<sub>4</sub>丫3も形成されている。

[0239] 図35は、図34に示した配線層61\_3に積層されている配線層61\_4に配線されている配線などの配置や形状を表す図である。配線層61\_4には、垂直信号線が形成されている。配線層61\_4には、垂直信号線V3<sub>1</sub>0乃至3<sub>1</sub>が、図中縦方向(垂直方向)に形成されている。

[0240] 上記した配線の位置や形状などは、一例であり、限定を示す記載ではない。

[0241] 本技術によれば、ドロからの電荷を一旦蓄積する電荷保持部を有し、グローバルシャッタ方式で撮影を行うときに、ド○の昇圧量を確保し、変換効率を向上させることができる。また本技術によれば、複数の画素で、ド○を共有する構成のときに、共有するド○を接続する配線の近傍にド○を昇圧させるための配線を形成することで、ドロの昇圧量を確保する構成とすることができる。

[0242] 本技術によれば、ダイナミックレンジを確保し、ノイズを低減させることができる。

[0243] <電子機器>

本技術は、撮像装置への適用に限られるものではなく、デジタルスチルカメラやビデオカメラ等の撮像装置や、携帯電話機などの撮像機能を有する携帯端末装置や、画像読み取り部に撮像装置を用いる複写機など、画像取込部(光

電変換部)に撮像装置を用いる電子機器全般に対して適用可能である。なお、電子機器に搭載されるモジュール状の形態、即ちカメラモジュールを撮像装置とする場合もある。

- [0244] 図36は、本開示の電子機器の一例である撮像装置の構成例を示すブロック図である。図36に示すように、本開示の撮像装置600は、レンズ群601等を含む光学系、撮像素子602、カメラ信号処理部であるO3印回路603、フレームメモリ604、表示装置605、記録装置606、操作系607、及び、電源系608等を有している。

- [0245] そして、O3印回路603、フレームメモリ604、表示装置605、記録装置606、操作系607、及び、電源系608がバスライン609を介して相互に接続された構成となっている。○印1610は、撮像装置600内の各部を制御する。

- [0246] レンズ群601は、被写体からの入射光(像光)を取り込んで撮像素子602の撮像面上に結像する。撮像素子602は、レンズ群601によって撮像面上に結像された入射光の光量を画素単位で電気信号に変換して画素信号として出力する。この撮像素子602として、先述した実施の形態に係る撮像素子(イメージセンサ)を用いることができる。

- [0247] 表示装置605は、液晶表示装置や有機EL(electro luminescence)表示装置等のパネル型表示装置からなり、撮像素子602で撮像された動画または静止画を表示する。記録装置606は、撮像素子602で撮像された動画または静止画を、ビデオテープやDVD(Digit31×61s3t160is0)等の記録媒体に記録する。

- [0248] 操作系607は、ユーザによる操作の下に、本撮像装置が持つ様々な機能について操作指令を発する。電源系608は、O3印回路603、フレームメモリ604、表示装置605、記録装置606、及び、操作系607の動作電源となる各種の電源を、これら供給対象に対して適宜供給する。

- [0249] このような撮像装置600は、ビデオカメラやデジタルスチルカメラ、さらには、携帯電話機等のモバイル機器向けカメラモジュールに適用される。

そして、この撮像装置 600において、撮像素子 602として先述した実施形態に係る撮像素子を用いることができる。

[0250] <内視鏡手術システムへの応用例>

本開示に係る技術は、様々な製品へ応用することができる。例えば、本開示に係る技術は、内視鏡手術システムに適用されてもよい。

[0251] 図37は、本開示に係る技術（本技術）が適用され得る内視鏡手術システムの概略的な構成の一例を示す図である。

[0252] 図37では、術者（医師）11131が、内視鏡手術システム11000を用いて、患者ベッド11133上の患者11132に手術を行っている様子が図示されている。図示するように、内視鏡手術システム11000は、内視鏡111〇〇と、気腹チューブ11111やエネルギー処置具11112等の、その他の術具11110と、内視鏡111〇〇を支持する支持アーム装置11120と、内視鏡下手術のための各種の装置が搭載されたカート11200と、から構成される。

[0253] 内視鏡11100は、先端から所定の長さの領域が患者11132の体腔内に挿入される鏡筒11101と、鏡筒11101の基端に接続されるカメラヘッド11102と、から構成される。図示する例では、硬性の鏡筒111〇1を有するいわゆる硬性鏡として構成される内視鏡11100を図示しているが、内視鏡11100は、軟性の鏡筒を有するいわゆる軟性鏡として構成されてもよい。

[0254] 鏡筒11101の先端には、対物レンズが嵌め込まれた開口部が設けられている。内視鏡111〇〇には光源装置11203が接続されており、当該光源装置11203によって生成された光が、鏡筒11101の内部に延設されるライトガイドによって当該鏡筒の先端まで導光され、対物レンズを介して患者11132の体腔内の観察対象に向かって照射される。なお、内視鏡11100は、直視鏡であってもよいし、斜視鏡又は側視鏡であってもよい。

[0255] カメラヘッド11102の内部には光学系及び撮像素子が設けられており

、観察対象からの反射光（観察光）は当該光学系によって当該撮像素子に集光される。当該撮像素子によって観察光が光電変換され、観察光に対応する電気信号、すなわち観察像に対応する画像信号が生成される。当該画像信号は、RAWデータとしてカメラコントロールユニット（CCU：Camera Control Unit）11201に送信される。

[0256] CCU11201は、CPU（Central Processing Unit）やGPU（Graphics Processing Unit）等によって構成され、内視鏡11100及び表示装置11202の動作を統括的に制御する。さらに、CCU11201は、カメラヘッド11102から画像信号を受け取り、その画像信号に対して、例えば現像処理（デモザイク処理）等の、当該画像信号に基づく画像を表示するための各種の画像処理を施す。

[0257] 表示装置11202は、CCU11201からの制御により、当該CCU11201によって画像処理が施された画像信号に基づく画像を表示する。

[0258] 光源装置11203は、例えばLED（Light Emission Diode）等の光源から構成され、術部等を撮影する際の照射光を内視鏡11100に供給する。

[0259] 入力装置11204は、内視鏡手術システム11000に対する入力インターフェースである。ユーザは、入力装置11204を介して、内視鏡手術システム11000に対して各種の情報の入力や指示入力をを行うことができる。例えば、ユーザは、内視鏡11100による撮像条件（照射光の種類、倍率及び焦点距離等）を変更する旨の指示等を入力する。

[0260] 処置具制御装置11205は、組織の焼灼、切開又は血管の封止等のためのエネルギー処置具11112の駆動を制御する。気腹装置11206は、内視鏡11100による視野の確保及び術者の作業空間の確保の目的で、患者11132の体腔を膨らめるために、気腹チューブ11111を介して当該体腔内にガスを送り込む。レコーダ11207は、手術に関する各種の情報を記録可能な装置である。プリンタ11208は、手術に関する各種の情

報を、テキスト、画像又はグラフ等各種の形式で印刷可能な装置である。

[0261] なお、内視鏡 111〇〇に術部を撮影する際の照射光を供給する光源装置 11203 は、例えば LED、レーザ光源又はこれらの組み合わせによって構成される白色光源から構成することができる。RGB レーザ光源の組み合せにより白色光源が構成される場合には、各色（各波長）の出力強度及び出力タイミングを高精度に制御することができるため、光源装置 11203において撮像画像のホワイトバランスの調整を行うことができる。また、この場合には、RGB レーザ光源それぞれからのレーザ光を時分割で観察対象に照射し、その照射タイミングに同期してカメラヘッド 11102 の撮像素子の駆動を制御することにより、RGB それぞれに対応した画像を時分割で撮像することも可能である。当該方法によれば、当該撮像素子にカラーフィルタを設けなくても、カラー画像を得ることができる。

[0262] また、光源装置 11203 は、出力する光の強度を所定の時間ごとに変更するようにその駆動が制御されてもよい。その光の強度の変更のタイミングに同期してカメラヘッド 111〇2 の撮像素子の駆動を制御して時分割で画像を取得し、その画像を合成することにより、いわゆる黒つぶれ及び白飛びのない高ダイナミックレンジの画像を生成することができる。

[0263] また、光源装置 11203 は、特殊光観察に対応した所定の波長帯域の光を供給可能に構成されてもよい。特殊光観察では、例えば、体組織における光の吸収の波長依存性を利用して、通常の観察時における照射光（すなわち、白色光）に比べて狭帯域の光を照射することにより、粘膜表層の血管等の所定の組織を高コントラストで撮影する、いわゆる狭帯域光観察（Narrow Band Imaging）が行われる。あるいは、特殊光観察では、励起光を照射することにより発生する蛍光により画像を得る蛍光観察が行われてもよい。蛍光観察では、体組織に励起光を照射し当該体組織からの蛍光を観察すること（自家蛍光観察）、又はインドシアニングリーン（ICG）等の試薬を体組織に局注するとともに当該体組織にその試薬の蛍光波長に対応した励起光を照射し蛍光像を得ること等を行うことができる。光源装置

11203は、このような特殊光観察に対応した狭帯域光及び/又は励起光を供給可能に構成され得る。

[0264] 図38は、図37に示すカメラヘッド11102及びCCU11201の機能構成の一例を示すブロック図である。

[0265] カメラヘッド11102は、レンズユニット11401と、撮像部11402と、駆動部11403と、通信部11404と、カメラヘッド制御部11405と、を有する。CCU11201は、通信部11411と、画像処理部11412と、制御部11413と、を有する。カメラヘッド11102とCCU11201とは、伝送ケーブル11400によって互いに通信可能に接続されている。

[0266] レンズユニット11401は、鏡筒11101との接続部に設けられる光学系である。鏡筒11101の先端から取り込まれた観察光は、カメラヘッド11102まで導光され、当該レンズユニット11401に入射する。レンズユニット11401は、ズームレンズ及びフォーカスレンズを含む複数のレンズが組み合わされて構成される。

[0267] 撮像部11402は、撮像素子で構成される。撮像部11402を構成する撮像素子は、1つ（いわゆる単板式）であってもよいし、複数（いわゆる多板式）であってもよい。撮像部11402が多板式で構成される場合には、例えば各撮像素子によってRGBそれぞれに対応する画像信号が生成され、それらが合成されることによりカラー画像が得られてもよい。あるいは、撮像部11402は、3D（Dimensional）表示に対応する右目用及び左目用の画像信号をそれぞれ取得するための1対の撮像素子を有するように構成されてもよい。3D表示が行われることにより、術者11131は術部における生体組織の奥行きをより正確に把握することが可能になる。なお、撮像部11402が多板式で構成される場合には、各撮像素子に対応して、レンズユニット11401も複数系統設けられ得る。

[0268] また、撮像部11402は、必ずしもカメラヘッド11102に設けられなくてもよい。例えば、撮像部11402は、鏡筒11101の内部に、対

物 レンズの直後に設けられてもよい。

- [0269] 駆動部 11403 は、アクチュエータによって構成され、カメラヘッド制御部 11405 からの制御により、レンズユニット 11401 のズームレンズ及びフォーカスレンズを光軸に沿って所定の距離だけ移動させる。これにより、撮像部 11402 による撮像画像の倍率及び焦点が適宜調整され得る。

- [0270] 通信部 11404 は、CCU11201との間で各種の情報を送受信するための通信装置によって構成される。通信部 11404 は、撮像部 11402 から得た画像信号をRAWデータとして伝送ケーブル 11400 を介して CCU11201 に送信する。

- [0271] また、通信部 11404 は、CCU11201 から、カメラヘッド 11102 の駆動を制御するための制御信号を受信し、カメラヘッド制御部 11405 に供給する。当該制御信号には、例えば、撮像画像のフレームレートを指定する旨の情報、撮像時の露出値を指定する旨の情報、並びに/又は撮像画像の倍率及び焦点を指定する旨の情報等、撮像条件に関する情報が含まれる。

- [0272] なお、上記のフレームレートや露出値、倍率、焦点等の撮像条件は、ユーザによって適宜指定されてもよいし、取得された画像信号に基づいて CCU11201 の制御部 11413 によって自動的に設定されてもよい。後者の場合には、いわゆる AE (Auto Exposure) 機能、AF (Auto Focus) 機能及び AWB (Auto White Balance) 機能が内視鏡 11100 に搭載されていることになる。

- [0273] カメラヘッド制御部 11405 は、通信部 11404 を介して受信した CCU11201 からの制御信号に基づいて、カメラヘッド 11102 の駆動を制御する。

- [0274] 通信部 11411 は、カメラヘッド 11102 との間で各種の情報を送受信するための通信装置によって構成される。通信部 11411 は、カメラヘッド 11102 から、伝送ケーブル 11400 を介して送信される画像信号

を受信する。

- [0275] また、通信部 11411 は、カメラヘッド 11102 に対して、カメラヘッド 11102 の駆動を制御するための制御信号を送信する。画像信号や制御信号は、電気通信や光通信等によって送信することができる。

- [0276] 画像処理部 11412 は、カメラヘッド 11102 から送信された[R]八八データである画像信号に対して各種の画像処理を施す。

- [0277] 制御部 11413 は、内視鏡 11100 による術部等の撮像、及び、術部等の撮像により得られる撮像画像の表示に関する各種の制御を行う。例えば、制御部 11413 は、カメラヘッド 11102 の駆動を制御するための制御信号を生成する。

- [0278] また、制御部 11413 は、画像処理部 11412 によって画像処理が施された画像信号に基づいて、術部等が映った撮像画像を表示装置 11202 に表示させる。この際、制御部 11413 は、各種の画像認識技術を用いて撮像画像内における各種の物体を認識してもよい。例えば、制御部 11413 は、撮像画像に含まれる物体のエッジの形状や色等を検出することにより、鉗子等の術具、特定の生体部位、出血、エネルギー処置具 11112 の使用時のミスト等を認識することができる。制御部 11413 は、表示装置 11202 に撮像画像を表示させる際に、その認識結果を用いて、各種の手術支援情報を当該術部の画像に重畳表示させてもよい。手術支援情報が重畳表示され、術者 11131 に提示されることにより、術者 11131 の負担を軽減することや、術者 11131 が確実に手術を進めることが可能になる。

- [0279] カメラヘッド 11102 及び ○○II11201 を接続する伝送ケーブル 11400 は、電気信号の通信に対応した電気信号ケーブル、光通信に対応した光ファイバ、又はこれらの複合ケーブルである。

- [0280] ここで、図示する例では、伝送ケーブル 11400 を用いて有線で通信が行われていたが、カメラヘッド 11102 と ○○II11201との間の通信は無線で行われてもよい。

- [0281] なお、ここでは、一例として内視鏡手術システムについて説明したが、本

開示に係る技術は、その他、例えば、顕微鏡手術システム等に適用されてもよい。

[0282] < 移動体への応用例 >

本開示に係る技術は、様々な製品へ応用することができる。例えば、本開示に係る技術は、自動車、電気自動車、ハイブリッド電気自動車、自動二輪車、自転車、パーソナルモビリティ、飛行機、ドローン、船舶、ロボット等のいずれかの種類の移動体に搭載される装置として実現されてもよい。

[0283] 図39は、本開示に係る技術が適用され得る移動体制御システムの一例である車両制御システムの概略的な構成例を示すブロック図である。

[0284] 車両制御システム12000は、通信ネットワーク12001を介して接続された複数の電子制御ユニットを備える。図39に示した例では、車両制御システム12000は、駆動系制御ユニット12010、ボディ系制御ユニット12020、車外情報検出ユニット12030、車内情報検出ユニット12040、及び統合制御ユニット12050を備える。また、統合制御ユニット12050の機能構成として、マイクロコンピュータ12051、音声画像出力部12052、及び車載ネットワークI/F(I n I ø r f 3○ø)12053が図示されている。

[0285] 駆動系制御ユニット12010は、各種プログラムにしたがって車両の駆動系に関連する装置の動作を制御する。例えば、駆動系制御ユニット12010は、内燃機関又は駆動用モータ等の車両の駆動力を発生させるための駆動力発生装置、駆動力を車輪に伝達するための駆動力伝達機構、車両の舵角を調節するステアリング機構、及び、車両の制動力を発生させる制動装置等の制御装置として機能する。

[0286] ボディ系制御ユニット12020は、各種プログラムにしたがって車体に装備された各種装置の動作を制御する。例えば、ボディ系制御ユニット12020は、キーレスエントリシステム、スマートキーシステム、パワーウィンドウ装置、あるいは、ヘッドライトランプ、バックランプ、ブレーキランプ、ウインカー又はフォグランプ等の各種ランプの制御装置として機能する。この

場合、ボディ系制御ユニット12020には、鍵を代替する携帯機から発信される電波又は各種スイッチの信号が入力され得る。ボディ系制御ユニット12020は、これらの電波又は信号の入力を受け付け、車両のドアロック装置、パワーウィンドウ装置、ランプ等を制御する。

- [0287] 車外情報検出ユニット12030は、車両制御システム12000を搭載した車両の外部の情報を検出する。例えば、車外情報検出ユニット12030には、撮像部12031が接続される。車外情報検出ユニット12030は、撮像部12031に車外の画像を撮像させるとともに、撮像された画像を受信する。車外情報検出ユニット12030は、受信した画像に基づいて、人、車、障害物、標識又は路面上の文字等の物体検出処理又は距離検出処理を行ってもよい。

- [0288] 撮像部12031は、光を受光し、その光の受光量に応じた電気信号を出力する光センサである。撮像部12031は、電気信号を画像として出力することもできるし、測距の情報として出力することもできる。また、撮像部12031が受光する光は、可視光であっても良いし、赤外線等の非可視光であっても良い。

- [0289] 車内情報検出ユニット12040は、車内の情報を検出する。車内情報検出ユニット12040には、例えば、運転者の状態を検出する運転者状態検出部12041が接続される。運転者状態検出部12041は、例えば運転者を撮像するカメラを含み、車内情報検出ユニット12040は、運転者状態検出部12041から入力される検出情報に基づいて、運転者の疲労度合い又は集中度合いを算出してもよいし、運転者が居眠りをしていないかを判別してもよい。

- [0290] マイクロコンピュータ12051は、車外情報検出ユニット12030又は車内情報検出ユニット12040で取得される車内外の情報に基づいて、駆動力発生装置、ステアリング機構又は制動装置の制御目標値を演算し、駆動系制御ユニット12010に対して制御指令を出力することができる。例えば、マイクロコンピュータ12051は、車両の衝突回避あるいは衝撃緩

和、車間距離に基づく追従走行、車速維持走行、車両の衝突警告、又は車両のレーン逸脱警告等を含むA D A S (Advanced Driver Assistance System) の機能実現を目的とした協調制御を行うことができる。

[0291] また、マイクロコンピュータ12051は、車外情報検出ユニット12030又は車内情報検出ユニット12040で取得される車両の周囲の情報に基づいて駆動力発生装置、ステアリング機構又は制動装置等を制御することにより、運転者の操作に拘らずに自律的に走行する自動運転等を目的とした協調制御を行うことができる。

[0292] また、マイクロコンピュータ12051は、車外情報検出ユニット12030で取得される車外の情報に基づいて、ボディ系制御ユニット12020に対して制御指令を出力することができる。例えば、マイクロコンピュータ12051は、車外情報検出ユニット12030で検知した先行車又は対向車の位置に応じてヘッドライトランプを制御し、ハイビームをロービームに切り替える等の防眩を図ることを目的とした協調制御を行うことができる。

[0293] 音声画像出力部12052は、車両の搭乗者又は車外に対して、視覚的又は聴覚的に情報を通知することが可能な出力装置へ音声及び画像のうちの少なくとも一方の出力信号を送信する。図39の例では、出力装置として、オーディオスピーカ12061、表示部12062及びインストルメントパネル12063が例示されている。表示部12062は、例えば、オンボードディスプレイ及びヘッドアップディスプレイの少なくとも一つを含んでいてもよい。

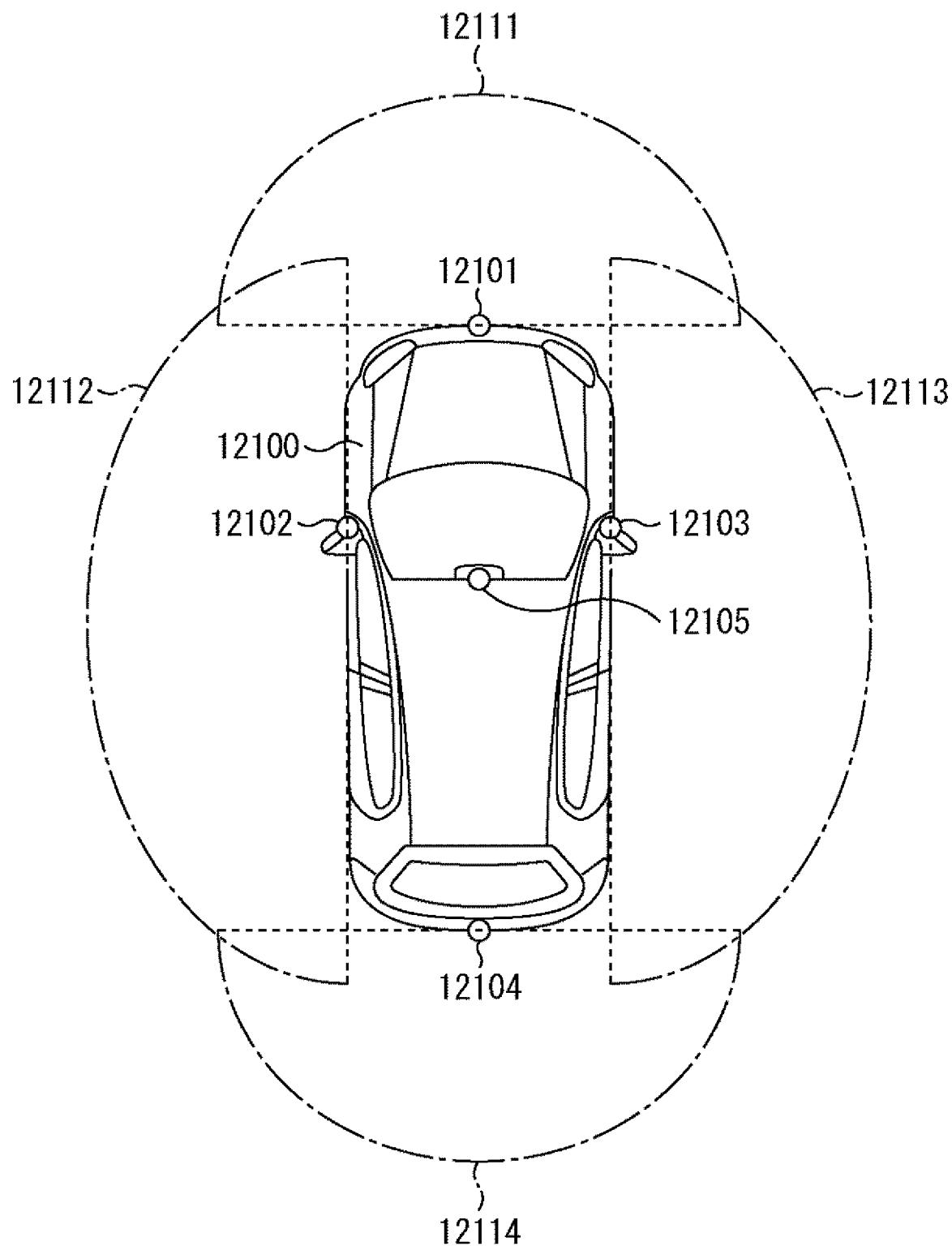

[0294] 図40は、撮像部12031の設置位置の例を示す図である。

[0295] 図40では、車両12100は、撮像部12031として、撮像部12101, 12102, 12103, 12104, 12105を有する。

[0296] 撮像部12101, 12102, 12103, 12104, 12105は、例えば、車両12100のフロントノーズ、サイドミラー、リアバンパ、バックドア及び車室内のフロントガラスの上部等の位置に設けられる。フロ

ントノーズに備えられる撮像部 12101 及び車室内のフロントガラスの上部に備えられる撮像部 12105 は、主として車両 12100 の前方の画像を取得する。サイドミラーに備えられる撮像部 12102, 12103 は、主として車両 12100 の側方の画像を取得する。リアバンパ又はバックドアに備えられる撮像部 12104 は、主として車両 12100 の後方の画像を取得する。撮像部 12101 及び 12105 で取得される前方の画像は、主として先行車両又は、歩行者、障害物、信号機、交通標識又は車線等の検出に用いられる。

[0297] なお、図40には、撮像部 12101 ないし 12104 の撮影範囲の一例が示されている。撮像範囲 12111 は、フロントノーズに設けられた撮像部 12101 の撮像範囲を示し、撮像範囲 12112, 12113 は、それサイドミラーに設けられた撮像部 12102, 12103 の撮像範囲を示し、撮像範囲 12114 は、リアバンパ又はバックドアに設けられた撮像部 12104 の撮像範囲を示す。例えば、撮像部 12101 ないし 12104 で撮像された画像データが重ね合わせられることにより、車両 12100 を上方から見た俯瞰画像が得られる。

[0298] 撮像部 12101 ないし 12104 の少なくとも 1 つは、距離情報を取得する機能を有していてもよい。例えば、撮像部 12101 ないし 12104 の少なくとも 1 つは、複数の撮像素子からなるステレオカメラであってもよいし、位相差検出用の画素を有する撮像素子であってもよい。

[0299] 例えば、マイクロコンピュータ 12051 は、撮像部 12101 ないし 12104 から得られた距離情報を基に、撮像範囲 12111 ないし 12114 内における各立体物までの距離と、この距離の時間的变化（車両 12100 に対する相対速度）を求めることにより、特に車両 12100 の進行路上にある最も近い立体物で、車両 12100 と略同じ方向に所定の速度（例えば、0 km/h 以上）で走行する立体物を先行車として抽出することができる。さらに、マイクロコンピュータ 12051 は、先行車の手前に予め確保すべき車間距離を設定し、自動ブレーキ制御（追従停止制御も含む）や自動

加速制御（追従発進制御も含む）等を行うことができる。このように運転者の操作に拘らずに自律的に走行する自動運転等を目的とした協調制御を行うことができる。

[0300] 例えば、マイクロコンピュータ12051は、撮像部12101ないし12104から得られた距離情報を元に、立体物に関する立体物データを、2輪車、普通車両、大型車両、歩行者、電柱等その他の立体物に分類して抽出し、障害物の自動回避に用いることができる。例えば、マイクロコンピュータ12051は、車両12100の周辺の障害物を、車両12100のドライバが視認可能な障害物と視認困難な障害物とに識別する。そして、マイクロコンピュータ12051は、各障害物との衝突の危険度を示す衝突リスクを判断し、衝突リスクが設定値以上で衝突可能性がある状況であるときには、オーディオスピーカ12061や表示部12062を介してドライバに警報を出力することや、駆動系制御ユニット12010を介して強制減速や回避操舵を行うことで、衝突回避のための運転支援を行うことができる。

[0301] 撮像部12101ないし12104の少なくとも1つは、赤外線を検出する赤外線カメラであってもよい。例えば、マイクロコンピュータ】2051は、撮像部12101ないし12104の撮像画像中に歩行者が存在するか否かを判定することで歩行者を認識することができる。かかる歩行者の認識は、例えば赤外線カメラとしての撮像部12101ないし12104の撮像画像における特徴点を抽出する手順と、物体の輪郭を示す一連の特徴点にパターンマッチング処理を行って歩行者か否かを判別する手順によって行われる。マイクロコンピュータ12051が、撮像部12101ないし12104の撮像画像中に歩行者が存在すると判定し、歩行者を認識すると、音声画像出力部12052は、当該認識された歩行者に強調のための方形輪郭線を重畳表示するように、表示部12062を制御する。また、音声画像出力部12052は、歩行者を示すアイコン等を所望の位置に表示するように表示部12062を制御してもよい。

[0302] 本明細書において、システムとは、複数の装置により構成される装置全体

を表すものである。

[0303] なお、本明細書に記載された効果はあくまで例示であつて限定されるものでは無く、また他の効果があつてもよい。

[0304] なお、本技術の実施の形態は、上述した実施の形態に限定されるものではなく、本技術の要旨を逸脱しない範囲において種々の変更が可能である。

[0305] なお、本技術は以下のような構成も取ることができる。

(1)

受光した光を電荷に変換する光電変換部と、

前記光電変換部から転送してきた電荷を保持する保持部と

を含む画素と、

複数の前記画素で共有され、前記保持部から転送してきた電荷を保持する

フローティングディフュージョンと、

前記フローティングディフュージョンを昇圧する昇圧線と

を備える撮像装置。

(2)

グローバルシャッタ方式で撮影を行う

前記(1)に記載の撮像装置。

(3)

前記昇圧線は、複数の前記フローティングディフュージョンを接続する接

続配線の近傍に、少なくとも一部が平行となる形状で形成されている

前記(1)または(2)に記載の撮像装置。

(4)

前記昇圧線と前記接続配線は、同層に形成されている

前記(3)に記載の撮像装置。

(5)

前記昇圧線と前記接続配線は、異層に形成されている

前記(3)に記載の撮像装置。

(6)

前記昇圧線は、前記フローティングディフュージョンの電位に応じた電圧信号を出力する増幅トランジスタのゲートに接続されている

前記(1)乃至(5)のいずれかに記載の撮像装置。

(7)

前記フローティングディフュージョンの容量を切り替える切替部をさらに備える

前記(1)乃至(6)のいずれかに記載の撮像装置。

(8)

前記保持部から電荷を読み出す読み出しゲートをさらに備え、

前記読み出しゲートは、前記光電変換部に対して垂直方向と水平方向に形成されている

前記(1)乃至(7)のいずれかに記載の撮像装置。

(9)

前記光電変換部からの電荷の読み出しは、CCD方式で行われる

前記(1)乃至(8)のいずれかに記載の撮像装置。

(10)

前記昇圧線に所定の電圧の印加を制御する制御線と、前記接続配線は、直交している

前記(3)乃至(9)のいずれかに記載の撮像装置。

(11)

前記昇圧線に所定の電圧の印加を制御する制御線と、前記接続配線は、平行している

前記(3)乃至(9)のいずれかに記載の撮像装置。

(12)

受光した光を電荷に変換する光電変換部と、

前記光電変換部から転送されてきた電荷を保持する保持部とを含む画素と、

複数の前記画素で共有され、前記保持部から転送されてきた電荷を保持す

るフローティングデイフュージョンと、

前記フローティングデイフュージョンを昇圧する昇圧線と

を備える撮像装置と

前記撮像装置からの信号を処理する処理部と

を備える電子機器。

### 符号の説明

- [0306] 30 イメージセンサ, 41 画素アレイ部, 42 垂直駆動部,

43 カラム処理部, 44 水平駆動部, 45 システム制御部, 4

6 画素駆動線, 47 垂直信号線, 48 信号処理部, 49 デー

タ格納部, 50 画素, 54 電荷保持部, 61 配線層, 62

酸化膜, 63 半導体基板, 64 遮光層, 65 カラーフィルタ層

, 66 オンチップレンズ, 67 P〇領域, 68 電荷保持領域,

71 配線, 72 層間絶縁膜, 73 TRXゲート, 74 表面

ピニング層, 75 画素間分離領域, 76 遮光部, 77 高誘電率

材料膜, 121 排出トランジスタ, 122 ○ド〇ゲート, 124

第2の転送トランジスタ, 125 浮遊拡散領域, 126 ド〇昇圧

配線, 131 リセットトランジスタ, 132 増幅トランジスタ,

133 選択トランジスタ, 301 D0 昇圧配線, 331 読み出し

ゲート, 401 変換効率切替トランジスタ, 411 D0 変換用配線

## 請求の範囲

- [請求項 1] 受光した光を電荷に変換する光電変換部と、

前記光電変換部から転送されてきた電荷を保持する保持部と

を含む画素と、

複数の前記画素で共有され、前記保持部から転送されてきた電荷を

保持するフローティングディフェュージョンと、

前記フローティングディフェュージョンを昇圧する昇圧線と

を備える撮像装置。

- [請求項 2] グローバルシャッタ方式で撮影を行う

請求項 1に記載の撮像装置。

- [請求項 3] 前記昇圧線は、複数の前記フローティングディフェュージョンを接続

する接続配線の近傍に、少なくとも一部が平行となる形状で形成され

ている

請求項 1に記載の撮像装置。

- [請求項 4] 前記昇圧線と前記接続配線は、同層に形成されている

請求項 3に記載の撮像装置。

- [請求項 5] 前記昇圧線と前記接続配線は、異層に形成されている

請求項 3に記載の撮像装置。

- [請求項 6] 前記昇圧線は、前記フローティングディフェュージョンの電位に応じ

た電圧信号を出力する増幅トランジスタのゲートに接続されている

請求項 1に記載の撮像装置。

- [請求項 7] 前記フローティングディフェュージョンの容量を切り替える切替部を

さらに備える

請求項 1に記載の撮像装置。

- [請求項 8] 前記保持部から電荷を読み出す読み出しゲートをさらに備え、

前記読み出しゲートは、前記光電変換部に対して垂直方向と水平方

向に形成されている

請求項 1に記載の撮像装置。

- [請求項 9] 前記光電変換部からの電荷の読み出しへ、CCO 方式で行われる

請求項 1 に記載の撮像装置。

- [請求項 10] 前記昇圧線に所定の電圧の印加を制御する制御線と、前記接続配線

は、直交している

請求項 3 に記載の撮像装置。

- [請求項 11] 前記昇圧線に所定の電圧の印加を制御する制御線と、前記接続配線

は、平行している

請求項 3 に記載の撮像装置。

- [請求項 12] 受光した光を電荷に変換する光電変換部と、

前記光電変換部から転送されてきた電荷を保持する保持部と

を含む画素と、

複数の前記画素で共有され、前記保持部から転送されてきた電荷を

保持するフローティングディフェュージョンと、

前記フローティングディフェュージョンを昇圧する昇圧線と

を備える撮像装置と、

前記撮像装置からの信号を処理する処理部と

を備える電子機器。

[図1]

FIG. 1

[図2]

FIG. 2

[図3]

FIG. 3

[図4]

FIG. 4

[図5]

FIG. 5

[図6]

FIG. 6

[図7]

FIG. 7

[図8]

FIG. 8

[図9]

FIG. 9

[図10]

FIG. 10

[図11]

FIG. 11

[図12]

FIG. 12

[図13]

FIG. 13

[図14]

FIG. 14

[図15]

FIG. 15

[図16]

FIG. 16

[図17]

FIG. 17

[図18]

FIG. 18

[図19]

FIG. 19

[図20]

FIG. 20

[図21]

FIG. 21

[図22]

FIG. 22

[図23]

FIG. 23

[図24]

FIG. 24

[図25]

FIG. 25

[図26]

FIG. 26

[図27]

FIG. 27

[図28]

FIG. 28

[図29]

FIG. 29

[図30]

FIG. 30

[図31]

FIG. 31

[図32]

FIG. 32

[図33]

FIG. 33

[図34]

FIG. 34

[図35]

FIG. 35

[図36]

FIG. 36

[図37]

[図38]

[図39]

[図40]

**INTERNATIONAL SEARCH REPORT**

International application No.

PCT/JP2019/027260

**A. CLASSIFICATION OF SUBJECT MATTER**

Int.Cl. H01L27/146 (2006.01) i, H04N5/3745 (2011.01) i

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

Int.Cl. H01L27/146, H04N5/3745

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

|                                                          |           |

|----------------------------------------------------------|-----------|

| Published examined utility model applications of Japan   | 1922–1996 |

| Published unexamined utility model applications of Japan | 1971–2019 |

| Registered utility model specifications of Japan         | 1996–2019 |

| Published registered utility model applications of Japan | 1994–2019 |

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                | Relevant to claim No. |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Y<br>A    | JP 2015-056878 A (TOSHIBA CORP.) 26 March 2015, paragraphs [0010]–[0116], [0166]–[0179], [0191]–[0203], fig. 1–5, 8–9, 12 & US 2015/0077611 A1, paragraphs [0017]–[0124], [0175]–[0189], [0202]–[0215], fig. 1–5, 8–9, 12 & CN 104469198 A & KR 10-2015-0031154 A | 1–5, 7–12<br>6        |

| Y<br>A    | JP 2011-217315 A (SONY CORP.) 27 October 2011, paragraphs [0031], [0044]–[0114], fig. 2–7 & US 2011/0242378 A1, paragraphs [0032], [0057]–[0126], fig. 2–7 & CN 102215351 A                                                                                       | 1–5, 7–12<br>6        |

Further documents are listed in the continuation of Box C.

See patent family annex.

|                                                                                                                                                                         |                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| * Special categories of cited documents:                                                                                                                                |                                                                                                                                                                                                                                                  |

| "A" document defining the general state of the art which is not considered to be of particular relevance                                                                | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention                                              |

| "E" earlier application or patent but published on or after the international filing date                                                                               | "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone                                                                     |

| "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) | "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art |

| "O" document referring to an oral disclosure, use, exhibition or other means                                                                                            | "&" document member of the same patent family                                                                                                                                                                                                    |

| "P" document published prior to the international filing date but later than the priority date claimed                                                                  |                                                                                                                                                                                                                                                  |

Date of the actual completion of the international search

20 September 2019 (20.09.2019)

Date of mailing of the international search report

01 October 2019 (01.10.2019)

Name and mailing address of the ISA/

Japan Patent Office

3-4-3, Kasumigaseki, Chiyoda-ku,

Tokyo 100-8915, Japan

Authorized officer

Telephone No.

**INTERNATIONAL SEARCH REPORT**

International application No.

PCT/JP2019/027260

**C (Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                            | Relevant to claim No. |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Y<br>A    | WO 2018/110303 A1 (SONY SEMICONDUCTOR SOLUTIONS CORPORATION) 21 June 2018, paragraphs [0033], [0041]-[0046], fig. 2 & TW 201826515 A                                                                                                                          | 7<br>6                |

| Y<br>A    | JP 2015-082592 A (SONY CORP.) 27 April 2015, paragraphs [0105]-[0110], fig. 16 & US 2016/0268322 A1, paragraphs [0137]-[0142], fig. 16 & WO 2015/059898 A1 & TW 201523853 A & KR 10-2016-0077055 A                                                            | 8<br>6                |

| A         | US 2015/0229859 A1 (RAMBUS INC.) 13 August 2015, entire text, all drawings & US 2016/0198108 A1, entire text, all drawings & US 2019/0045149 A1 & US 2017/0208272 A1 & US 9894304 B1 & WO 2015/120328 A1 & WO 2015/187884 A1 & EP 3103255 A1 & CN 105981370 A | 1-12                  |

## A. 発明の属する分野の分類（国際特許分類（IPC））

Int.Cl. H01L27/146(2006.01)i, H04N5/3745(2011.01)i

## B. 調査を行った分野

## 調査を行った最小限資料（国際特許分類（IPC））

Int.Cl. H01L27/146, H04N5/3745

## 最小限資料以外の資料で調査を行った分野に含まれるもの

|             |            |

|-------------|------------|

| 日本国実用新案公報   | 1922-1996年 |

| 日本国公開実用新案公報 | 1971-2019年 |

| 日本国実用新案登録公報 | 1996-2019年 |

| 日本国登録実用新案公報 | 1994-2019年 |

## 国際調査で使用した電子データベース（データベースの名称、調査に使用した用語）

## C. 関連すると認められる文献

| 引用文献の<br>カテゴリーエ | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                                                                                                                                                                                               | 関連する<br>請求項の番号 |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Y               | JP 2015-056878 A (株式会社東芝)                                                                                                                                                                                                       | 1-5, 7-12      |

| A               | 2015.03.23, 段落 [0010]-[0116], [0166]-[0179], [0191]-[0203],<br>[図1]-[図5], [図8]-[図9], [図12]<br>& US 2015/0077611 A1, 段落 [0017]-[0124], [0175]-[0189],<br>[0202]-[0215], 図1-5, 8-9, 12<br>& CN 104469198 A & KR 10-2015-0031154 A | 6              |

| Y               | JP 2011-217315 A (ソニー株式会社)                                                                                                                                                                                                      | 1-5, 7-12      |

| A               | 2011.10.27, 段落 [0031], [0044]-[0114], [図2]-[図7]                                                                                                                                                                                 | 6              |

☞ C欄の続きにも文献が列挙されている。

☞ パテントファミリーに関する別紙を参照。

## \* 引用文献のカテゴリー

- 「A」特に関連のある文献ではなく、一般的技術水準を示すもの

「E」国際出願日前の出願または特許であるが、国際出願日以後に公表されたもの

「L」優先権主張に疑義を提起する文献又は他の文献の発行日若しくは他の特別な理由を確立するために引用する文献（理由を付す）

「O」口頭による開示、使用、展示等に言及する文献

「P」国際出願日前で、かつ優先権の主張の基礎となる出願

## の日の後に公表された文献

- 「T」国際出願日又は優先日後に公表された文献であって出願と矛盾するものではなく、発明の原理又は理論の理解のために引用するもの

「X」特に関連のある文献であって、当該文献のみで発明の新規性又は進歩性がないと考えられるもの

「Y」特に関連のある文献であって、当該文献と他の1以上の文献との、当業者にとって自明である組合せによって進歩性がないと考えられるもの

「&」同一パテントファミリー文献

|                                                                         |                                                                  |

|-------------------------------------------------------------------------|------------------------------------------------------------------|

| 国際調査を完了した日<br>20.09.2019                                                | 国際調査報告の発送日<br>01.10.2019                                         |

| 国際調査機関の名称及びあて先<br>日本国特許庁 (ISA/JP)<br>郵便番号 100-8915<br>東京都千代田区霞が関三丁目4番3号 | 特許庁審査官（権限のある職員）<br>田邊 顕人<br>電話番号 03-3581-1101 内線 3516<br>5F 5894 |

| C (続き) . 関連すると認められる文献 |                                                                                                                                                                                                                            | 関連する<br>請求項の番号 |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 引用文献の<br>カテゴリー*       | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                                                                                                                                                                                          |                |

|                       | & US 2011/0242378 A1, 段落 [0032], [0057] - [0126], 図 2-7<br>& CN 102215351 A                                                                                                                                                |                |

| Y                     | WO 2018/110303 A1 (ソニーセミコンダクタソリューションズ株式会社)<br>2018.06.21, 段落 [0033], [0041] - [0046], [図 2]<br>& TW 201826515 A                                                                                                            | 7<br>6         |

| A                     | JP 2015-082592 A (ソニー株式会社)<br>2015.04.27, 段落 [0105] - [0110], [図 16]<br>& US 2016/0268322 A1, 段落 [0137] - [0142], 図 16<br>& WO 2015/059898 A1 & TW 201523853 A & KR 10-2016-0077055 A                                      | 8<br>6         |

| A                     | US 2015/0229859 A1 (RAMBUS INC.)<br>2015.08.13, 全文、全図<br>& US 2016/0198108 A1, 全文、全図<br>& US 2019/0045149 A1 & US 2017/0208272 A1 & US 9894304 B1 & WO 2015/120328 A1 & WO 2015/187884 A1 & EP 3103255 A1 & CN 105981370 A | 1-12           |