(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6314034号

(P6314034)

(45) 発行日 平成30年4月18日(2018.4.18)

(24) 登録日 平成30年3月30日(2018.3.30)

(51) Int.Cl.

F 1

H01L 29/786 (2006.01)

H01L 21/336 (2006.01)H01L 29/78 618E

H01L 29/78 617N

H01L 29/78 618B

H01L 29/78 619A

請求項の数 4 (全 41 頁)

(21) 出願番号 特願2014-103197 (P2014-103197)

(22) 出願日 平成26年5月19日 (2014.5.19)

(65) 公開番号 特開2015-5734 (P2015-5734A)

(43) 公開日 平成27年1月8日 (2015.1.8)

審査請求日 平成29年5月12日 (2017.5.12)

(31) 優先権主張番号 特願2013-106331 (P2013-106331)

(32) 優先日 平成25年5月20日 (2013.5.20)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 須澤 英臣

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 岡崎 豊

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 綿引 隆

最終頁に続く

(54) 【発明の名称】半導体装置

(57) 【特許請求の範囲】

【請求項 1】

第1の酸化物層と、

前記第1の酸化物層上の第2の酸化物層と、

前記第2の酸化物層に接する領域を有するソース電極層と、

前記第2の酸化物層に接する領域を有するドレイン電極層と、

前記ソース電極層上及び前記ドレイン電極層上に位置し、且つ、前記第2の酸化物層の上面と、前記ソース電極層と、前記ドレイン電極層と、それぞれ接する領域を有する第3の酸化物層と、

前記第3の酸化物層上の第1の絶縁層と、

前記第1の絶縁層上の第1の導電層と、を有し、

前記第1の絶縁層は、トランジスタのゲート絶縁層として機能する領域を有し、

前記第1の導電層は、前記トランジスタのゲート電極層として機能する領域を有し、

前記第1乃至第3の酸化物層は、それぞれインジウム、ガリウム及び亜鉛を有し、

前記第1の酸化物のガリウムの原子数比は、前記第2の酸化物のガリウムの原子数比よりも高く、

前記第3の酸化物のガリウムの原子数比は、前記第2の酸化物のガリウムの原子数比よりも高く、

前記トランジスタのチャネル幅方向の断面において、前記第3の酸化物層は、前記第2の酸化物層の側面と接する領域と、前記第1の酸化物層の側面と接する領域を有すること

10

20

を特徴とする半導体装置。

【請求項 2】

第 1 の酸化物層と、

前記第 1 の酸化物層上の第 2 の酸化物層と、

前記第 2 の酸化物層に接する領域を有するソース電極層と、

前記第 2 の酸化物層に接する領域を有するドレイン電極層と、

前記ソース電極層上及び前記ドレイン電極層上に位置し、且つ、前記第 2 の酸化物層の上面と、前記ソース電極層と、前記ドレイン電極層と、それぞれ接する領域を有する第 3 の酸化物層と、

前記第 3 の酸化物層上の第 1 の絶縁層と、

前記第 1 の絶縁層上の第 1 の導電層と、

前記第 1 の酸化物層の下方の第 2 の絶縁層と、

前記第 2 の絶縁層の下方の第 2 の導電層と、を有し、

前記第 1 の絶縁層は、トランジスタの第 1 のゲート絶縁層として機能する領域を有し、

前記第 1 の導電層は、前記トランジスタの第 1 のゲート電極層として機能する領域を有し、

前記第 2 の絶縁層は、前記トランジスタの第 2 のゲート絶縁層として機能する領域を有し、

前記第 2 の導電層は、前記トランジスタの第 2 のゲート電極層として機能する領域を有し、

前記第 1 乃至第 3 の酸化物層は、それぞれインジウム、ガリウム及び亜鉛を有し、

前記第 1 の酸化物のガリウムの原子数比は、前記第 2 の酸化物のガリウムの原子数比よりも高く、

前記第 3 の酸化物のガリウムの原子数比は、前記第 2 の酸化物のガリウムの原子数比よりも高く、

前記トランジスタのチャネル幅方向の断面において、前記第 3 の酸化物層は、前記第 2 の酸化物層の側面と接する領域と、前記第 1 の酸化物層の側面と接する領域を有することを特徴とする半導体装置。

【請求項 3】

請求項 1 又は 2 において、

前記第 2 の酸化物層は、前記第 1 の酸化物層の膜厚より大きい膜厚を有し、

前記第 2 の酸化物層は、前記第 3 の酸化物層の膜厚より大きい膜厚を有することを特徴とする半導体装置。

【請求項 4】

請求項 1 乃至 3 のいずれか一において、

前記第 1 の導電層上に接する酸化アルミニウム膜を有することを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本明細書等で開示する発明は、半導体装置及び半導体装置の作製方法に関する。

【0 0 0 2】

なお、本明細書等において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、画像表示装置、半導体回路及び電子機器は、すべて半導体装置である。

【背景技術】

【0 0 0 3】

絶縁表面を有する基板上に形成された半導体薄膜を用いてトランジスタを構成する技術が注目されている。該トランジスタは集積回路 (IC) や画像表示装置 (単に表示装置とも表記する) のような電子デバイスに広く応用されている。トランジスタに適用可能な半導

10

20

30

40

50

体薄膜としてシリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

【0004】

例えば、酸化物半導体として、酸化亜鉛、In-Ga-Zn系酸化物半導体を用いてトランジスタを作製する技術が開示されている（特許文献1及び特許文献2参照）。

【0005】

また、トランジスタのキャリア移動度の向上を目的として、電子親和力（または伝導帯下端準位）が異なる酸化物半導体層を積層させる技術が開示されている（特許文献3及び特許文献4参照）。

【先行技術文献】

10

【特許文献】

【0006】

【特許文献1】特開2007-123861号公報

【特許文献2】特開2007-96055号公報

【特許文献3】特開2011-124360号公報

【特許文献4】特開2011-138934号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

酸化物半導体を用いたトランジスタを有する半導体装置において、高信頼性の達成は、製品化にむけて重要事項である。特に、半導体装置の電気特性の変動や低下は信頼性の低下を招く要因である。

20

【0008】

このような問題に鑑み、本発明の一態様は、酸化物半導体を用いた半導体装置であって、信頼性の高い半導体装置を提供することを課題の一とする。

【0009】

また、トランジスタの動作の高速化、トランジスタの低消費電力化、低価格化、高集積化等を達成するためにはトランジスタの微細化が必須である。

【0010】

そこで、本発明の一態様は、酸化物半導体を用いた半導体装置であって、良好な電気特性を維持しつつ、微細化を達成した半導体装置を提供することを課題の一とする。

30

【0011】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。本発明の一態様は、これらの課題の全てを解決する必要はないものとする。また、上記以外の課題は、明細書等の記載から自ずと明らかになるものであり、明細書等の記載から上記以外の課題を抽出することが可能である。

【課題を解決するための手段】

【0012】

酸化物半導体を用いてトランジスタを作製する場合、酸化物半導体のキャリアの供給源の一つとして、酸素欠損があげられる。酸化物半導体に含まれる酸素欠損は、酸化物半導体のエネルギーギャップ内の深いエネルギー位置に存在する局在準位として顕在化する。このような局在準位にキャリアがトラップされることで、トランジスタのノーマリオン化、リーク電流の増大、ストレス印加によるしきい値電圧の変動（シフト）など、電気特性の不良を引き起こす要因となる。よって、トランジスタの信頼性を向上させるためには、酸化物半導体に含まれる酸素欠損を低減することが必要となる。

40

【0013】

また、酸化物半導体層において、水素、シリコン、窒素、炭素及び主成分以外の金属元素は不純物となる。例えば、酸化物半導体層中で水素の一部はドナー準位を形成し、キャリア密度を増大させる。

【0014】

50

そのため、酸化物半導体を用いた半導体装置において安定した電気特性を得るためには、酸化物半導体層に十分な酸素を供給することで酸素欠損を低減し、且つ、水素等の不純物濃度を低減する措置を講じることが求められる。

#### 【0015】

そこで、本発明の一態様の半導体装置では、酸化物半導体層の下側に設けられたゲート絶縁層、及び酸化物半導体層の上側に設けられた保護絶縁層として機能する絶縁層から、チャネル形成領域へ酸素を供給することで、チャネル形成領域に生じうる酸素欠損を補填する。

#### 【0016】

本発明の一態様において、チャネル形成領域へ酸素を供給するためのゲート絶縁層及び保護絶縁層としては、過剰酸素を含有する酸化アルミニウム膜を含む絶縁層を適用するものとする。ここで、過剰酸素とは、例えば、化学量論的組成を超えて含まれる酸素、または、半導体装置の作製工程中に加わる熱処理温度以下の温度の加熱より放出されうる酸素をいう。例えば、過剰酸素を含む酸化アルミニウム膜として、 $A1O_x$  ( $x$  は 1.5 より大きい) 膜を設けることができる。酸化アルミニウム膜に含まれる過剰酸素は、加熱によって放出され酸化物半導体層へと供給することができるため、このような酸化アルミニウム膜を含む絶縁層を酸化物半導体層の下側及び上側に設けることで、チャネル形成領域に効果的に酸素を供給することができる。

#### 【0017】

なお、過剰酸素を含有する酸化アルミニウム膜は、例えば、酸素を含む雰囲気にてスパッタリング法等によって成膜することで形成することができる。

#### 【0018】

また、酸化アルミニウム膜は、酸化シリコン膜、酸化窒化シリコン膜等の絶縁層、または酸化物半導体層と比較して酸素及び水素に対する透過性が低い絶縁層である。換言すると、酸素及び水素に対するバリア性を有する絶縁層である。よって、酸化アルミニウム膜を含む絶縁層を設けることで、当該絶縁層で囲まれた領域の酸素の脱離による酸素欠損の形成を抑制し、且つ、水素又は水素化合物の混入を抑制することができる。

#### 【0019】

本発明の一態様において、酸化物半導体層の上側又は下側の一方に設けられたゲート絶縁層と、酸化物半導体層の上側又は下側の他方に設けられた保護絶縁層は、酸化物半導体層と、該酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層とが存在しない領域において、互いに接する領域を有する。すなわち、本発明の一態様の半導体装置は、酸化物半導体層を包み込むように酸化アルミニウム膜が設けられた構成を有する。このような構成を有することで、酸化物半導体層のフロントチャネル側及びバックチャネル側界面に加えて、酸化物半導体層側面における酸素の脱離及び / または水素等の不純物の混入を抑制し、且つ酸素の供給を行うことが可能となる。よって、当該酸化物半導体層にチャネルが形成されるトランジスタの電気特性の変動を抑制し、信頼性の高い半導体装置を形成することが可能となる。

#### 【0020】

より具体的には、例えば以下の構成とすることができます。

#### 【0021】

本発明の一態様は、第 1 のゲート電極層と、第 1 のゲート電極層上に接して設けられた第 1 のゲート絶縁層と、第 1 のゲート絶縁層を介して第 1 のゲート電極層と重なる酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層と、ソース電極層及びドレイン電極層上に位置し、酸化物半導体層と重なる第 2 のゲート絶縁層と、第 2 のゲート絶縁層を介して酸化物半導体層と重なる第 2 のゲート電極層と、ソース電極層、ドレイン電極層及び第 2 のゲート電極層を覆う保護絶縁層と、を有し、第 1 のゲート絶縁層及び保護絶縁層は、過剰酸素を含有する酸化アルミニウム膜を含み、且つソース電極層、ドレイン電極層及び第 2 のゲート電極層の存在しない領域において互いに接する領域を有する半導体装置である。

10

20

30

40

50

## 【0022】

また、本発明の一態様は、第1の絶縁層と、第1の絶縁層中に埋め込まれ、上面が露出した第1のゲート電極層と、第1の絶縁層及び第1のゲート電極層上に接する第1のゲート絶縁層と、第1のゲート絶縁層を介して第1のゲート電極層と重なる酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層と、ソース電極層及びドレイン電極層上に位置し、酸化物半導体層と重なる第2のゲート絶縁層と、第2のゲート絶縁層を介して酸化物半導体層と重なる第2のゲート電極層と、ソース電極層、ドレイン電極層及び第2のゲート電極層を覆う保護絶縁層と、を有し、第1のゲート絶縁層及び保護絶縁層は、過剰酸素を含有する酸化アルミニウム膜を含み、且つソース電極層、ドレイン電極層及び第2のゲート電極層の存在しない領域において互いに接する領域を有する半導体装置である。 10

## 【0023】

上記の半導体装置において、チャネル幅の方向の断面において、第2のゲート電極層は、第2のゲート絶縁層を介して酸化物半導体層の側面及び上面を覆うことが好ましい。

## 【0024】

また、上記の半導体装置において、第1のゲート絶縁層と酸化物半導体層との間に設けられ、酸化物半導体層を構成する金属元素のうち少なくとも一の金属元素を構成元素として含む第1の酸化物層と、第2のゲート絶縁層と酸化物半導体層との間に設けられ、酸化物半導体層を構成する金属元素のうち少なくとも一の金属元素を構成元素として含む第2の酸化物層と、を有し、酸化物半導体層の伝導帯下端のエネルギーは、第1の酸化物層及び第2の酸化物層の伝導帯下端のエネルギーよりも、0.05 eV以上2 eV以下の範囲で真空準位に近いことが好ましい。 20

## 【0025】

また、上述の構成において、第2の酸化物層は、ソース電極層とドレイン電極層から露出した酸化物半導体層を覆うように、ソース電極層及びドレイン電極層上に設けられることが好ましい。

## 【0026】

本発明の一態様にかかる構成の効果は、例えば以下のように説明することができる。

## 【0027】

本発明の一態様の半導体装置は、過剰酸素を含有する酸化アルミニウム膜を含む絶縁層を、酸化物半導体層を包み込むように設ける。酸化アルミニウム膜に含まれる過剰酸素は、半導体装置の作製工程における加熱処理によって、チャネルが形成される酸化物半導体層へ供給される。さらに、酸化アルミニウム膜は、酸素及び水素に対するバリア性を有するため、酸化アルミニウム膜を含む絶縁層で包まれた酸化物半導体層からの酸素の脱離、及び酸化物半導体層への水素等の不純物の混入を抑制することが可能となる。十分に酸素が供給され、且つ水素等の不純物の混入を抑制された酸化物半導体層は、高純度真性化された酸化物半導体層である。 30

## 【0028】

また、上記の半導体装置において、酸化物半導体層の下側及び上側に重なるように設けられた第1のゲート電極層及び第2のゲート電極層によって、酸化物半導体層は、垂直方向の電界が上下方向から印加される。よって、半導体装置のしきい値電圧を良好に制御することが可能となる。また、上述の第2のゲート電極層を、第2のゲート絶縁層を介して酸化物半導体層の側面を覆うように形成することで、チャネル形成領域に対して垂直方向及び側面方向から全体的に電界を印加することが可能となり、しきい値電圧の制御性をさらに良好とすることができます。また、トランジスタのサブスレッショルド係数（S値）を小さくすることができる。 40

## 【0029】

また、本発明の一態様の半導体装置は、酸化物半導体層と、該酸化物半導体層と重なる第1のゲート絶縁層及び保護絶縁層との間に、酸化物半導体層を構成する金属元素のうち、少なくとも一の金属元素を構成元素として含む酸化物層を有することが好ましい。これに 50

より、酸化物半導体層と、該酸化物半導体層と重なる絶縁層との界面にトラップ準位が形成されることを抑制することができるため、トランジスタの電気特性の劣化を抑制することができる。

【0030】

すなわち、本発明の一態様は、酸化物半導体層の上面及び底面が酸化物半導体層の界面準位形成防止のためのバリア膜として機能する酸化物層によって覆われ、チャネル幅方向における酸化物半導体層の側面及び底面がゲート絶縁層を介してゲート電極層によって覆われ、且つ、酸化物半導体層を包み込むように酸化アルミニウム膜を含む絶縁層を設けた構成とすることがより好ましい。このような構成とすることで、酸化物半導体層中及び界面においてキャリアの生成要因となる酸素欠損の生成及び不純物の混入を抑制することが可能となるため、酸化物半導体層を高純度真性化することができる。高純度真性化とは、酸化物半導体層を真性または実質的に真性にすることをいう。よって、当該酸化物半導体層を含むトランジスタの電気特性の変動を抑制し、信頼性の高い半導体装置を提供することが可能となる。

【発明の効果】

【0031】

本発明の一態様によって、酸化物半導体を用いた半導体装置であって、信頼性の高い半導体装置を提供することができる。

【0032】

また、本発明の一態様によって、酸化物半導体を用いた半導体装置であって、良好な電気特性を維持しつつ、微細化を達成した半導体装置を提供することができる。

【図面の簡単な説明】

【0033】

【図1】半導体装置の一態様を説明する平面図及び断面図。

【図2】半導体装置の一態様を説明する平面図及び断面図。

【図3】半導体装置の作製方法を説明する断面図。

【図4】半導体装置の作製方法を説明する断面図。

【図5】半導体装置の一態様を説明する平面図、断面図及びバンド図。

【図6】半導体装置の一態様を説明する平面図及び断面図。

【図7】半導体装置の一例を説明する回路図。

【図8】半導体装置の一例を説明するブロック図。

【図9】半導体装置の一例を説明する回路図。

【図10】半導体装置の一例を説明する回路図。

【図11】半導体装置の一例を説明する図。

【図12】電子機器の一態様を説明する図。

【発明を実施するための形態】

【0034】

以下では、開示する発明の実施の形態について図面を用いて詳細に説明する。ただし、本明細書に開示する発明は、以下の説明に限定されず、その形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本明細書に開示する発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に示す本発明の一態様の構成において、同一部分または同様の機能を有する部分には、同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。また、同様の機能を有する部分を指す場合には、ハッシュパターンを同じくし、特に符号を付さない場合がある。

【0035】

なお、本明細書等における「第1」、「第2」等の序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではない。

【0036】

なお、本明細書等において実質的に真性という場合、酸化物半導体層のキャリア密度は、 $1 \times 10^{17} / \text{cm}^3$  未満、 $1 \times 10^{15} / \text{cm}^3$  未満、または $1 \times 10^{13} / \text{cm}^3$  未

10

20

30

40

50

満である。酸化物半導体層を高純度真性化することで、トランジスタに安定した電気特性を付与することができる。

【0037】

また、本明細書等において「上」や「下」の用語は、構成要素の位置関係が「直上」または「直下」であることを限定するものではない。例えば、「ゲート絶縁層上のゲート電極」の表現であれば、ゲート絶縁層とゲート電極との間に他の構成要素を含むものを除外しない。「下」についても同様である。

【0038】

また、本明細書等において、膜の上面とは、基板表面と略平行な面のうち、基板表面からの距離が離れた側の面を示し、膜の底面とは、基板表面と略平行な面のうち、基板表面に近い側の面を示す。

10

【0039】

本明細書において、「平行」とは、二つの直線が -10°以上10°以下の角度で配置されている状態をいう。従って、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。従って、85°以上95°以下の場合も含まれる。

【0040】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

【0041】

20

(実施の形態1)

本実施の形態では、半導体装置及び半導体装置の作製方法の一態様を、図1乃至図4を用いて説明する。本実施の形態では、半導体装置の一例として酸化物半導体を有するトランジスタを示す。

【0042】

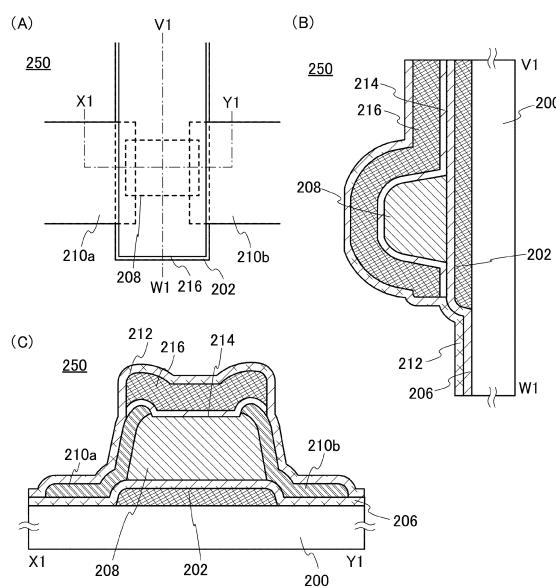

図1にトランジスタ250の構成例を示す。図1(A)は、トランジスタ250の平面図であり、図1(B)は、図1(A)のV1-W1における断面図であり、図1(C)は、図1(A)のX1-Y1における断面図である。なお、図1(A)では、煩雑になることを避けるため、トランジスタ250の構成要素の一部(例えば、絶縁層212等)を省略して図示している。本明細書の以降の平面図においても同様である。

30

【0043】

図1に示すトランジスタ250は、基板200上に設けられた第1のゲート電極層202と、第1のゲート電極層202に接して設けられた絶縁層206と、絶縁層206を介して第1のゲート電極層202と重なる酸化物半導体層208と、酸化物半導体層208と電気的に接続するソース電極層210a及びドレイン電極層210bと、ソース電極層210a及びドレイン電極層210b上に位置し、酸化物半導体層208と重なる絶縁層214と、絶縁層214を介して酸化物半導体層208と重なる第2のゲート電極層216と、ソース電極層210a、ドレイン電極層210b及び第2のゲート電極層216を覆うように、絶縁層206上に設けられた絶縁層212と、を有する。

【0044】

40

トランジスタ250において、第1のゲート電極層202と、酸化物半導体層208との間に設けられた絶縁層206は、第1のゲート絶縁層として機能する。また、第2のゲート電極層216と酸化物半導体層208との間に設けられた絶縁層214は、第2のゲート絶縁層として機能する。また、ソース電極層210a、ドレイン電極層210b及び第2のゲート電極層216を覆うように酸化物半導体層208の上側に設けられた絶縁層212は、保護絶縁層として機能する。

【0045】

トランジスタ250において、酸化物半導体層208の下側に設けられた絶縁層206と、酸化物半導体層208の上側に設けられた絶縁層212には、過剰酸素を含有する酸化アルミニウム膜を含む絶縁層を適用する。

50

## 【0046】

図1( B )及び図1( C )の断面図に示すように、第1のゲート絶縁層として機能する絶縁層206と、保護絶縁層として機能する絶縁層212とは、チャネル長方向(キャリアが流れる方向)及びチャネル幅方向の双方において、酸化物半導体層208、ソース電極層210a、ドレイン電極層210b及び第2のゲート電極層216が存在しない領域で、互いに接する領域を有している。すなわち、トランジスタ250に含まれる酸化物半導体層208は、酸化アルミニウム膜を含む絶縁層によって包まれた構成を有する。

## 【0047】

上述したように、酸化アルミニウム膜に含まれる過剰酸素は、トランジスタ250の作製工程中の加熱処理によって放出され、酸化物半導体層208へと供給される。また、該加熱処理と、酸化物半導体層208上に絶縁層等を成膜する際の加熱処理とを兼ねることも可能である。さらに、酸化アルミニウム膜は、酸素及び水素に対するバリア性を有する膜である。よって、酸化物半導体層208は、酸素の脱離が抑制され、且つ酸素が十分に供給されることで酸素欠損が低減されるとともに、水素等の不純物の混入が低減された、酸化物半導体層である。換言すると、酸化物半導体層208は、高純度真性化された酸化物半導体層である。高純度化し、i型(真性)化した酸化物半導体層208を有するトランジスタ250は、電気特性変動が抑制されており、電気的に安定である。

## 【0048】

なお、酸化物半導体層208を真性または実質的に真性とするためには、二次イオン分析法( SIMS : Secondary Ion Mass Spectrometry )における分析において、水素濃度は、 $2 \times 10^{20}$  atoms / cm<sup>3</sup>以下、好ましくは $5 \times 10^{19}$  atoms / cm<sup>3</sup>以下、より好ましくは $1 \times 10^{19}$  atoms / cm<sup>3</sup>以下、さらに好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup>以下とする。

## 【0049】

なお、酸化物半導体層208の下側に設けられる絶縁層206及び酸化物半導体層208の上側に設けられる絶縁層212は、含有する水素濃度を低減することが好ましい。具体的には、絶縁層206及び絶縁層212に含まれる水素濃度は、 $5 \times 10^{19}$  atoms / cm<sup>3</sup>未満とすることが好ましく、 $5 \times 10^{18}$  atoms / cm<sup>3</sup>未満とすることがより好ましい。

## 【0050】

高純度化された酸化物半導体層208をチャネル形成領域に用いたトランジスタ250のオフ電流は極めて小さい。例えば、高純度化された酸化物半導体層を用いたトランジスタがオフ状態のときのドレイン電流は、室温(25程度)にて $1 \times 10^{-18}$  A以下、好ましくは $1 \times 10^{-21}$  A以下、さらに好ましくは $1 \times 10^{-24}$  A以下、または85にて $1 \times 10^{-15}$  A以下、好ましくは $1 \times 10^{-18}$  A以下、さらに好ましくは $1 \times 10^{-21}$  A以下とすることができる。なお、トランジスタがオフ状態とは、nチャネル型のトランジスタの場合、ゲート電圧がしきい値電圧よりも十分小さい状態をいう。具体的には、ゲート電圧がしきい値電圧よりも1V以上、2V以上または3V以上小さければ、トランジスタはオフ状態となる。

## 【0051】

なお、トランジスタを微細化することで、高密度化(高集積化)が実現される。例えば、トランジスタのチャネル長を100nm以下、好ましくは40nm以下、さらに好ましくは30nm以下とする。

## 【0052】

半導体装置の高密度化(高集積化)を達成するためには、トランジスタの微細化が必須であるものの、トランジスタの微細化によりトランジスタの電気特性が悪化することが知られている。例えば、シリコンを用いたトランジスタでは、チャネル長を短縮すると、サブスレッショルド係数( S 値)の劣化、しきい値電圧がマイナス側へ変動等の短チャネル効果が生じることが知られている。

## 【0053】

10

20

30

40

50

しかしながら、酸化物半導体を用いたトランジスタは、電子を多数キャリアとする蓄積型トランジスタであるため、シリコン等の反転型トランジスタと比較して短チャネルでのDIBL (D r a i n - I n d u c e d B a r r i e r L o w e r i n g ) が起こりにくい。酸化物半導体を用いたトランジスタでは、短チャネル効果に対する耐性を有すると言い換えることもでき、酸化物半導体を用いたトランジスタは、微細化に適したトランジスタである。

【0054】

また、トランジスタ250において、酸化物半導体層208の下側に重なるように設けられた第1のゲート電極層202及び酸化物半導体層208の上側に重なるように設けられた第2のゲート電極層216によって、酸化物半導体層208は、垂直方向の電界が上下方向から印加される。このような構成とすることで、チャネル形成領域に対して垂直方向及び側面方向の全体的に電界が印加されるようになるため、トランジスタ250のしきい値電圧の制御を良好に行うことができる。また、トランジスタ250のS値を小さくすることができる。第1のゲート電極層202と第2のゲート電極層216の電位は、例えば同電位とすることができる。ただし、第1のゲート電極層202及び第2のゲート電極層216の電位はこれに限られない。

10

【0055】

なお、トランジスタ250のチャネル幅を拡大しすぎると、チャネル形成領域の側面方向から第2のゲート電極層216の電界が印加されにくくなり、しきい値電圧の制御性が低下する。酸化物半導体層208の側面方向に、第2のゲート電極層216からの電界を十分に印加するためには、酸化物半導体層208の膜厚を、チャネル幅以上とすることが好みしい。

20

【0056】

一般に、トランジスタのチャネル幅を縮小すると、オン電流の低下が懸念される。オン電流の向上を目的として、活性層の側面にもチャネルが形成されるよう活性層を厚膜化する方法も知られているが、チャネルが形成される表面積が増大することで、チャネル形成領域とゲート絶縁層との界面にキャリアの散乱が増加するため、十分なオン電流の向上を見込むのは容易ではない。

【0057】

しかしながら、本実施の形態のトランジスタ250においては、チャネルが形成される酸化物半導体層208を包み込む様で、過剰酸素を含有する酸化アルミニウム膜を含む絶縁層206、212を有することで、酸化アルミニウム膜に含まれる過剰酸素を酸化物半導体層208に供給し、且つ、酸化物半導体層208からの酸素の脱離及び水素等の不純物の混入を抑制することができる。酸化物半導体層208にとって、酸素欠損及び水素はキャリアの生成要因となるため、過剰酸素を含む酸化アルミニウム膜を設けることで、チャネルが形成される酸化物半導体層208の界面で生じうるキャリアの散乱を抑えることができる。

30

【0058】

したがって、チャネル幅を縮小した場合であっても、酸化物半導体層208の膜厚を厚膜化して第2のゲート電極層216と重なる表面積を増加させることで、オン電流を十分に向上させることが可能となる。

40

【0059】

なお、酸化物半導体層中の水素の一部は、酸素欠損に捕獲され、酸化物半導体層をn型化するため、フェルミ準位(E<sub>f</sub>)が伝導帯下端(E<sub>c</sub>)に近づく。よって、水素が多量に含まれた酸化物半導体層は、電気特性の変動が懸念される一方で、トランジスタの電界効果移動度の向上が実現される。一方、酸化物半導体層208を真性又は実質的に真性とすると、酸化物半導体層208のフェルミエネルギーはミッドギャップ(酸化物半導体層のエネルギー-ギャップの中間のエネルギー)と一致する、又は限りなく近づく。この場合、酸化物半導体層208に含まれるキャリア数の減少により、電界効果移動度の低下が懸念される。

50

## 【0060】

しかしながら、トランジスタ250においては、酸化物半導体層208に垂直方向からのゲート電界に加えて、側面方向からのゲート電界が印加される。すなわち、酸化物半導体層208の全体的にゲート電界が印加されることとなり、電流は酸化物半導体層208のバルクを流れる。これによって、高純度真性化による、電気特性の変動の抑制を達成しつつ、トランジスタ250の電界効果移動度の向上を図ることが可能となる。

## 【0061】

また、トランジスタのチャネル長及びチャネル幅を微細化すると、レジストマスクを用いて加工される配線、半導体層等の端面が丸みを帯びる（曲面を有する）場合がある。厚膜化した酸化物半導体層を覆うように、薄膜の絶縁層（例えば、ゲート絶縁層）を形成する場合、被覆性の低下による形状不良を招き、安定した電気特性が得られないことがあるが、酸化物半導体層208の端面が曲面を有することで、酸化物半導体層208上に設けられる絶縁層214の被覆性を向上させることができるために、好ましい。

10

## 【0062】

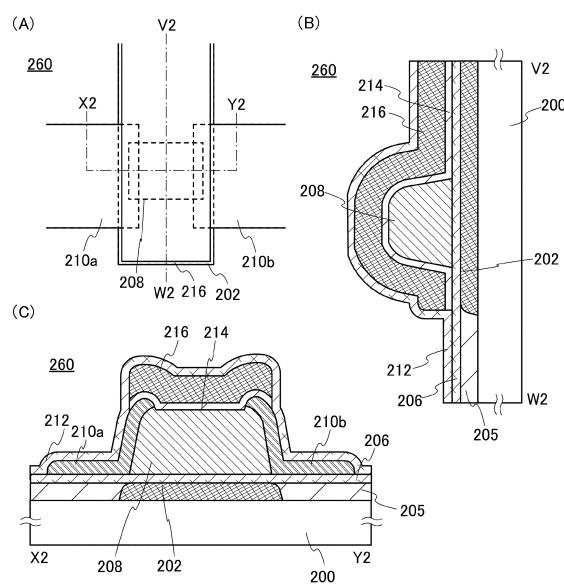

図2に本実施の形態のトランジスタの別の構成例として、トランジスタ260の構成例を示す。図2（A）は、トランジスタ260の平面図であり、図2（B）は、図2（A）のV2-W2における断面図であり、図2（C）は、図2（A）のX2-Y2における断面図である。

## 【0063】

図2に示すトランジスタ260は、基板200上の絶縁層205と、絶縁層205中に埋め込まれ上面が露出した第1のゲート電極層202と、絶縁層205から露出した第1のゲート電極層202の上面に接するように絶縁層205上に設けられた絶縁層206と、絶縁層205及び絶縁層206を介して第1のゲート電極層202と重なる酸化物半導体層208と、酸化物半導体層208と電気的に接続するソース電極層210a及びドレイン電極層210bと、ソース電極層210a及びドレイン電極層210b上に位置し、酸化物半導体層208と重なる絶縁層214と、絶縁層214を介して酸化物半導体層208と重なる第2のゲート電極層216と、ソース電極層210a、ドレイン電極層210b及び第2のゲート電極層216を覆うように、絶縁層206上に設けられた絶縁層212と、を有する。

20

## 【0064】

トランジスタ260において、第1のゲート電極層202と、酸化物半導体層208との間に設けられた絶縁層206は、第1のゲート絶縁層として機能する。また、第2のゲート電極層216と酸化物半導体層208との間に設けられた絶縁層214は、第2のゲート絶縁層として機能する。また、ソース電極層210a、ドレイン電極層210b及び第2のゲート電極層216を覆うように酸化物半導体層208の上側に設けられた絶縁層212は、保護絶縁層として機能する。

30

## 【0065】

図2に示すトランジスタ260は、第1のゲート電極層202の構成において図1のトランジスタ250と相違する。すなわち、トランジスタ250では、基板上に形成された第1のゲート電極層202を覆うように絶縁層206を形成している。一方、トランジスタ260では、第1のゲート電極層202は、絶縁層205に埋め込まれ、上面が露出した構成を有し、当該露出した上面において第1のゲート絶縁層として機能する絶縁層206と接している。

40

## 【0066】

トランジスタ260において、その他の構成要素は、トランジスタ250と同様の構成とすることができる。

## 【0067】

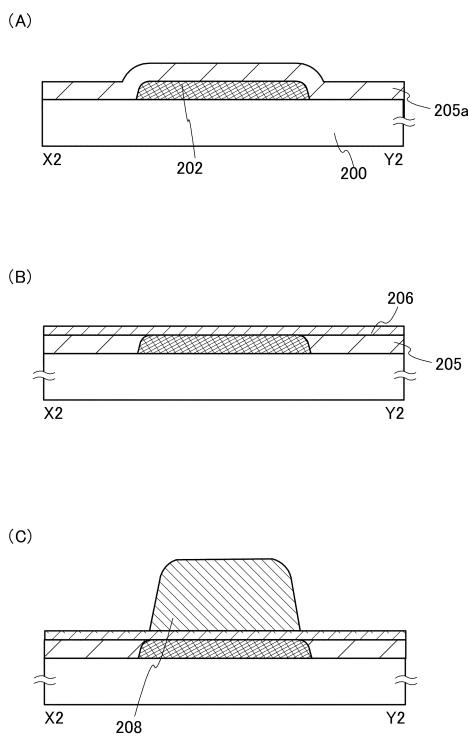

以下、図3及び図4を用いて、トランジスタ260の作製方法の一例を説明する。

## 【0068】

絶縁表面を有する基板200上に第1のゲート電極層202（これと同じ層で形成される

50

配線を含む)を形成し、第1のゲート電極層202上に絶縁膜205aを形成する(図3(A)参照)。

【0069】

絶縁表面を有する基板200に使用することができる基板に大きな制限はないが、少なくとも後の熱処理工程に耐えうる程度の耐熱性を有していることが必要となる。例えば、バリウムホウケイ酸ガラスやアルミニノホウケイ酸ガラスなどのガラス基板、セラミック基板、石英基板、サファイア基板などを用いることができる。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することもでき、これらの基板上に半導体素子が設けられたものを、基板200として用いてもよい。

10

【0070】

また、基板200として、可撓性基板を用いて半導体装置を作製してもよい。可撓性を有する半導体装置を作製するには、可撓性基板上にトランジスタ260を直接作製してもよいし、他の作製基板にトランジスタ260を作製し、その後可撓性基板に剥離、転置してもよい。なお、作製基板から可撓性基板に剥離、転置するために、作製基板とトランジスタ260との間に剥離層を設けるとよい。

【0071】

第1のゲート電極層202の材料は、モリブデン、チタン、タンタル、タンゲステン、アルミニウム、銅、クロム、ネオジム、スカンジウムから選ばれた元素を含む金属膜、または上述した元素を成分とする金属窒化物膜(窒化チタン膜、窒化モリブデン膜、窒化タンゲステン膜)等を用いることができる。また、第1のゲート電極層202としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜、ニッケルシリサイドなどのシリサイド膜を用いてもよい。又は、インジウム錫酸化物、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの導電性材料を適用することもできる。また、上記導電性材料と、上記金属材料の積層構造とすることもできる。

20

【0072】

また、第1のゲート電極層202は単層構造又は積層構造とすることができます。なお、絶縁膜205aと接する第1のゲート電極層202の一層として、窒素を含む金属酸化物、具体的には、窒素を含むIn-Ga-Zn-O膜や、窒素を含むIn-Sn-O膜や、窒素を含むIn-Ga-O膜や、窒素を含むIn-Zn-O膜や、窒素を含むSn-O膜や、窒素を含むIn-O膜や、金属窒化膜( InN、SnNなど)を用いることができる。これらの膜は5eV(電子ボルト)以上、好ましくは5.5eV(電子ボルト)以上の仕事関数を有し、ゲート電極層として用いた場合、トランジスタのしきい値電圧をプラス側にシフトさせることができ、所謂ノーマリオフのスイッチング素子を実現できる。

30

【0073】

第1のゲート電極層202は、プラズマCVD法またはスパッタリング法等により形成することができる。

【0074】

絶縁膜205aとしては、酸化シリコン膜、酸化窒化シリコン膜、または窒化酸化シリコン膜等を用いて、単層構造または積層構造とすることができます。なお、絶縁膜205aの膜厚は、少なくとも第1のゲート電極層202の膜厚以上とすることが好ましい。

40

【0075】

次いで、絶縁膜205aにエッチバック処理またはCMP(化学的機械研磨)処理を施して、第1のゲート電極層202の一部を露出させる。なお、CMP処理とエッチバック処理を組み合わせて用いてもよい。ここでエッチバック処理またはCMP処理により、第1のゲート電極層202上に設けられた絶縁膜205aが除去され、第1のゲート電極層202を埋め込む絶縁層205が形成される。

【0076】

50

次いで、絶縁層 205 上に接して、絶縁層 206 を形成する（図 3（B）参照）。

【0077】

絶縁層 206 は、少なくとも過剰酸素を含有する酸化アルミニウム膜を含む。また、酸化アルミニウム膜と、酸化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜との積層構造としてもよい。なお、積層構造とする場合には、酸化アルミニウム膜の他に含まれる絶縁膜も、酸化アルミニウム膜と同様に過剰酸素を含有していてもよい。

【0078】

例えば、第 1 のゲート電極層 202 に近い側から過剰酸素を含有する酸化アルミニウム膜と、過剰酸素を含有する酸化シリコン膜とを順に積層することにより、絶縁層 206 を積層構造としてもよい。この場合、酸化物半導体層に対して酸化シリコン膜の外側に設けられた酸化アルミニウム膜によって、酸化シリコン膜に含まれる過剰酸素の外方拡散を抑制しつつ、後に形成される酸化物半導体層 208 へ効果的に酸素を供給することができる。

10

【0079】

また、絶縁層 206 に含まれる酸化アルミニウム膜は、酸化アルミニウムターゲットを用いたスパッタリング法によって形成することが好ましい。または、アルミニウムターゲットを用いた反応性スパッタリングによって、酸化アルミニウム膜を形成してもよい。酸化アルミニウム膜の成膜を、酸素を含む雰囲気において行うことで、成膜後の酸化アルミニウム膜に過剰酸素を含有させることができる。成膜ガス中の酸素割合は 30 体積 % 以上とすることが好ましい。なお、酸素に加えて希ガス（例えば、アルゴン）を含有していてもよい。

20

【0080】

または、絶縁層 206 に含まれる酸化アルミニウム膜を成膜する際の酸化アルミニウムターゲットに、0.1 % 以上 30 % 以下の割合で酸化シリコンを含有させて、酸化シリコンを含む酸化アルミニウム膜を形成してもよい。酸化シリコンは、酸化アルミニウムと比較して酸素の透過性が高いため、酸化アルミニウム膜が酸化シリコンを含有すると、該酸化アルミニウム膜に含まれる過剰酸素が放出されやすくなる。また、酸化シリコンを含有する酸化アルミニウム膜をトランジスタに適用することで、応力緩和の効果を奏する。一方、酸化シリコンの含有割合が高いと酸素に対するバリア性が低下するため、酸化アルミニウムターゲットに含まれる酸化シリコンの割合は 30 % 以下とすることが好ましい。例えば、5 % または 10 % の割合で酸化シリコンを添加すればよい。

30

【0081】

また、絶縁層 206 の成膜時の基板温度を高めることで、絶縁層 206 中に含まれる水素濃度を低減することが可能であるため好ましい。基板温度は、例えば 100 以上 500 以下、好ましくは 150 以上 450 以下とする。

【0082】

次いで、絶縁層 206 上に酸化物半導体層 208 となる酸化物半導体膜を成膜し、島状に加工して酸化物半導体層 208 を形成する（図 3（C）参照）。

【0083】

酸化物半導体膜は、単層構造であってもよいし、積層構造であってもよい。また、非晶質構造であってもよいし、結晶性であってもよい。

40

【0084】

酸化物半導体膜の成膜方法は、スパッタリング法、MBE (Molecular Beam Epitaxy) 法、CVD 法、パルスレーザ堆積法、ALD (Atomic Layer Deposition) 法等を適宜用いることができる。

【0085】

酸化物半導体膜を成膜する際、できる限り酸化物半導体に含まれる水素濃度を低減させることが好ましい。水素濃度を低減させるには、例えば、スパッタリング法を用いて成膜を行う場合には、スパッタリング装置の成膜室内に供給する雰囲気ガスとして、水素、水、水酸基又は水素化物などの不純物が除去された高純度の希ガス（代表的にはアルゴン）、

50

酸素、及び希ガスと酸素との混合ガスを適宜用いる。

【0086】

また、成膜室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入して成膜を行うことで、成膜された酸化物半導体膜の水素濃度を低減させることができる。成膜室内の残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプは、水素分子、水( $H_2O$ )など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等の排気能力が高いため、当該ポンプで排気した成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

10

【0087】

また、酸化物半導体膜をスパッタリング法で成膜する場合、成膜に用いる金属酸化物ターゲットの相対密度(充填率)は90%以上100%以下、好ましくは95%以上99.9%以下とする。相対密度の高い金属酸化物ターゲットを用いることにより、成膜した酸化物半導体膜を緻密な膜とすることができます。

【0088】

また、基板200を高温に保持した状態で酸化物半導体膜を形成することも、酸化物半導体膜中に含まれる不純物濃度を低減するのに有効である。基板200を加熱する温度としては、150以上450以下とすればよく、好ましくは基板温度が200以上350以下とすればよい。また、成膜時に基板を高温で加熱することで、結晶性の酸化物半導体膜を形成することができる。

20

【0089】

酸化物半導体膜に用いる酸化物半導体としては、少なくともインジウム( $In$ )を含む。特に、インジウムと亜鉛( $Zn$ )を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム( $Ga$ )を有することが好ましい。また、スタビライザーとしてスズ( $Sn$ )、ハフニウム( $Hf$ )、アルミニウム( $Al$ )、ジルコニウム( $Zr$ )のいずれか一種または複数種を有することが好ましい。

【0090】

また、他のスタビライザーとして、ランタノイドである、ランタン( $La$ )、セリウム( $Ce$ )、プラセオジム( $Pr$ )、ネオジム( $Nd$ )、サマリウム( $Sm$ )、ユウロピウム( $Eu$ )、ガドリニウム( $Gd$ )、テルビウム( $Tb$ )、ジスプロシウム( $Dy$ )、ホルミウム( $Ho$ )、エルビウム( $Er$ )、ツリウム( $Tm$ )、イッテルビウム( $Yb$ )、ルテチウム( $Lu$ )のいずれか一種または複数種を有してもよい。

30

【0091】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物である $In - Zn$ 系酸化物、 $In - Mg$ 系酸化物、 $In - Ga$ 系酸化物、三元系金属の酸化物である $In - Ga - Zn$ 系酸化物( $IGZO$ とも表記する)、 $In - Al - Zn$ 系酸化物、 $In - Sn - Zn$ 系酸化物、 $In - Hf - Zn$ 系酸化物、 $In - La - Zn$ 系酸化物、 $In - Ce - Zn$ 系酸化物、 $In - Pr - Zn$ 系酸化物、 $In - Nd - Zn$ 系酸化物、 $In - Sm - Zn$ 系酸化物、 $In - Eu - Zn$ 系酸化物、 $In - Gd - Zn$ 系酸化物、 $In - Tb - Zn$ 系酸化物、 $In - Dy - Zn$ 系酸化物、 $In - Ho - Zn$ 系酸化物、 $In - Er - Zn$ 系酸化物、 $In - Tm - Zn$ 系酸化物、 $In - Yb - Zn$ 系酸化物、 $In - Lu - Zn$ 系酸化物、四元系金属の酸化物である $In - Sn - Ga - Zn$ 系酸化物、 $In - Hf - Ga - Zn$ 系酸化物、 $In - Al - Ga - Zn$ 系酸化物、 $In - Sn - Al - Zn$ 系酸化物、 $In - Sn - Hf - Zn$ 系酸化物、 $In - Hf - Al - Zn$ 系酸化物を用いることができる。

40

【0092】

なお、例えば、 $In - Ga - Zn$ 系酸化物とは、 $In$ と $Ga$ と $Zn$ を主成分として有する酸化物という意味であり、 $In$ と $Ga$ と $Zn$ の比率は問わない。また、 $In$ と $Ga$ と $Zn$

50

以外の金属元素が入っていてもよい。

【0093】

インジウムを含む酸化物半導体を用いたトランジスタは、これらに限られず、必要とする電気特性（電界効果移動度、しきい値等）に応じて適切な組成のものを用いればよい。また、必要とする電気特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

【0094】

酸化物半導体膜を形成後、熱処理を行うことが好ましい。熱処理は、250以上650

以下、好ましくは300以上500以下の温度で、不活性ガス雰囲気、酸化性ガスを10 ppm以上含む雰囲気、又は減圧雰囲気で行えばよい。また、熱処理の雰囲気は、不活性ガス雰囲気で熱処理を行った後に、脱離した酸素を補うために酸化性ガスを10 ppm以上含む雰囲気で行ってもよい。ここで加熱処理によって、酸化物半導体膜から水素や水などの不純物を除去することができる。なお、当該熱処理は、酸化物半導体膜を島状の酸化物半導体層208に加工した後に行ってもよい。

10

【0095】

次に、絶縁層206及び島状の酸化物半導体層208上に導電膜を形成し、該導電膜を加工してソース電極層210a及びドレイン電極層210b（これと同じ層に形成される配線を含む。）を形成する（図4（A）参照）。

【0096】

ソース電極層210a及びドレイン電極層210bは、第1のゲート電極層202と同様の材料を用いることが可能であり、単層構造または積層構造とすることができます。

20

【0097】

なお、図示しないが、ソース電極層210a及びドレイン電極層210bの端部は階段状に複数の段を設けた形状としてもよい。当該端部の加工は、アッティングによってレジストマスクを後退させる工程とエッチングの工程を交互に複数回行うことで形成することができる。ソース電極層210a及びドレイン電極層210bの膜厚が厚いほど、当該段数を増やすことが好ましい。ソース電極層210a及びドレイン電極層210bを上記のような複数の段を設けた形状とすることで、それらの上方に形成される絶縁層212の被覆性が向上し、トランジスタの電気特性や長期信頼性を向上させることができるためである。

【0098】

30

なお、ソース電極層210a及びドレイン電極層210bの加工の際に、導電膜のオーバーエッチングによって、酸化物半導体層208の一部（ソース電極層210a及びドレイン電極層210bから露出した領域）がエッチングされ膜厚が減少することがある。

【0099】

次いで、ソース電極層210a及びドレイン電極層210bを覆うように、絶縁層206上に絶縁膜214aを形成する（図4（B）参照）。

【0100】

絶縁膜214aは、絶縁膜205aと同様の材料、同様の作製方法によって形成することが可能である。

【0101】

40

次いで、絶縁膜214a上に、第2のゲート電極層216となる導電膜を形成し、これを加工して第2のゲート電極層216（これと同じ層で形成される配線を含む）を形成する。その後、第2のゲート電極層216をマスクとして絶縁膜214aを加工して、絶縁層214を形成する。第2のゲート電極層216をマスクとして自己整合的に絶縁層214の加工を行うと、マスク枚数を増加することがないため好適である。

【0102】

その後、ソース電極層210a、ドレイン電極層210b及び第2のゲート電極層216を覆うように、絶縁層206上に絶縁層212を形成する（図4（C）参照）。絶縁層212は、少なくとも過剰酸素を含有する酸化アルミニウム膜を含む絶縁層とし、絶縁層206と同様の構成、同様の作製方法によって形成することができる。

50

## 【0103】

なお、絶縁層212を形成後、熱処理を行ってもよい。熱処理の条件は、先の酸化物半導体膜を形成後の熱処理と同様とすることができる。

## 【0104】

以上によって、本実施の形態のトランジスタ260を形成することができる。

## 【0105】

本実施の形態で示す半導体装置は、過剰酸素を含有する酸化アルミニウム膜を含む絶縁層を、酸化物半導体層を包み込むように設けることで、酸化物半導体層に酸素を供給し、且つ、酸化物半導体層からの酸素の脱離、及び酸化物半導体層への水素等の不純物の混入を抑制することが可能となる。

10

## 【0106】

よって、チャネル形成領域の酸素欠損に起因して起こりうるしきい値電圧の変動等の電気特性の変動を抑制することができる。具体的には、例えば、しきい値電圧のノーマリオ化を安定に成就することができる。したがって、良好な電気特性を示すとともに長期信頼性の高い半導体装置を提供することができる。

## 【0107】

また、本実施の形態で示す半導体装置は、酸化物半導体層の下側及び上側に重なるように設けられた第1のゲート電極層及び第2のゲート電極層によって、酸化物半導体層の垂直方向の上下からゲート電極層の電界が印加される。よって、トランジスタのしきい値電圧を良好に制御することが可能となる。

20

## 【0108】

さらに、第2のゲート絶縁層を介して酸化物半導体層と重なる第2のゲート電極層を、チャネル幅方向においてチャネル形成領域の側面及び底面と重なるように設けることで、酸化物半導体層の側面及び底面と重なるゲート電極層を形成する。これによって、チャネル形成領域に対して側面方向及び底面方向から電界が印加されるため、トランジスタのしきい値電圧をより良好に制御し、且つS値を小さくすることができる。

## 【0109】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

## 【0110】

30

## (実施の形態2)

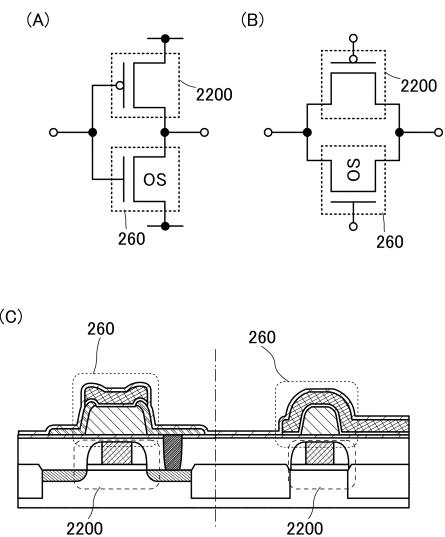

本実施の形態では、実施の形態1とは異なる半導体装置の構成について、図5及び図6を参照して説明する。なお、実施の形態1と共に通する構成については、実施の形態1を参照することが可能であり、繰り返しの説明を省略することがある。

## 【0111】

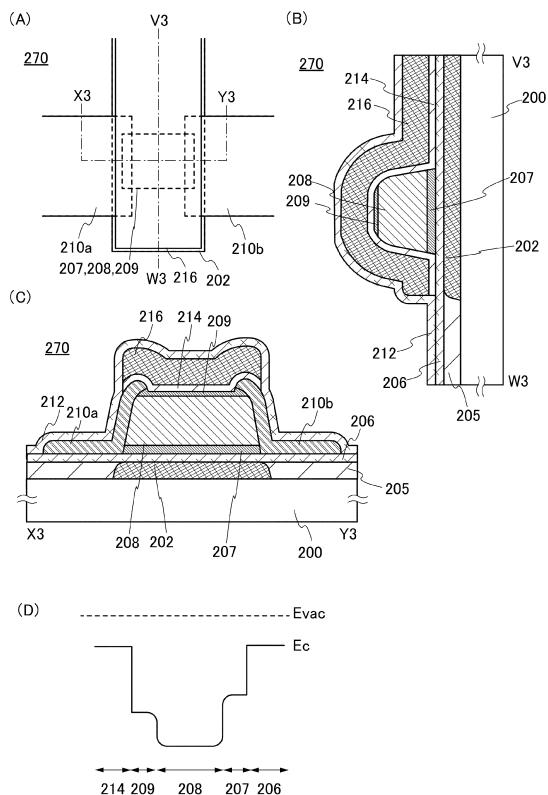

図5に本実施の形態のトランジスタ270の構成例を示す。図5(A)は、トランジスタ270の平面図であり、図5(B)は、図5(A)のV3-W3における断面図であり、図5(C)は、図5(A)のX3-Y3における断面図である。また、図5(D)は、トランジスタ270に含まれる積層構造の伝導帯下端のエネルギーを模式的に示すバンド図である。

40

## 【0112】

図5に示すトランジスタ270は、実施の形態1のトランジスタ260と同様に、基板200上に、絶縁層205と、絶縁層205中に埋め込まれ、上面が露出した第1のゲート電極層202と、第1のゲート電極層202の上面に接するように絶縁層205上に設けられた絶縁層206と、絶縁層206を介して第1のゲート電極層202と重なる酸化物半導体層208と、酸化物半導体層208と電気的に接続するソース電極層210a及びドレイン電極層210bと、ソース電極層210a及びドレイン電極層210b上に位置し、酸化物半導体層208と重なる絶縁層214と、絶縁層214を介して酸化物半導体層208と重なる第2のゲート電極層216と、ソース電極層210a、ドレイン電極層210b及び第2のゲート電極層216を覆うように、絶縁層206上に設けられた絶縁

50

層 212 と、を有する。

【 0113 】

また、本実施の形態のトランジスタ 270 は、上述のトランジスタ 260 の構成に加えてさらに、絶縁層 206 と酸化物半導体層 208 との間に設けられ、酸化物半導体層 208 を構成する金属元素のうち少なくとも一の金属元素を構成元素として含む第 1 の酸化物層 207 と、絶縁層 214 と酸化物半導体層 208 との間に設けられ、酸化物半導体層 208 を構成する金属元素のうち少なくとも一の金属元素を構成元素として含む第 2 の酸化物層 209 と、を有する。

【 0114 】

トランジスタ 270 では、実施の形態 1 で示したトランジスタ 260 の作製工程において 10 、絶縁層 205 上に接して絶縁層 206 を形成した後、第 1 の酸化物層 207 となる第 1 の酸化物膜と、酸化物半導体膜と、第 2 の酸化物層 209 となる第 2 の酸化物膜とを連続的に成膜し、フォトリソグラフィ工程によりレジストマスクを形成し、レジストマスクを用いた第 2 の酸化物膜、酸化物半導体膜及び第 1 の酸化物膜のエッチングによって島状に加工することで、第 1 の酸化物層 207 、酸化物半導体層 208 及び第 2 の酸化物層 209 の積層構造を形成することができる。

【 0115 】

なお、上述の通り、トランジスタ 270 に含まれる第 1 の酸化物層 207 、酸化物半導体層 208 及び第 2 の酸化物層 209 は同じレジストマスクを用いて加工されるため、第 1 の酸化物層 207 の上端部と酸化物半導体層 208 の下端部は略一致し、酸化物半導体層 208 の上端部と第 2 の酸化物層 209 の下端部は略一致する。または、第 1 の酸化物層 207 、酸化物半導体層 208 及び第 2 の酸化物層 209 は、略一致した上面形状を有する。 20

【 0116 】

なお、上記において第 1 の酸化物膜、酸化物半導体膜、及び第 2 の酸化物膜を大気開放することなく連続的に形成すると、各層の界面への水素や水分等の不純物の吸着を防止することができるため、好ましい。

【 0117 】

トランジスタ 270 に含まれる酸化物半導体層 208 としては、少なくともインジウム、亜鉛及び M ( M は Al 、 Ga 、 Ge 、 Y 、 Zr 、 Sn 、 La 、 Ce または Hf 等の金属 ) を含む In - M - Zn 酸化物で表記される層を含む。酸化物半導体層 208 がインジウムを含むと、トランジスタのキャリア移動度が高くなるため、好ましい。 30

【 0118 】

酸化物半導体層 208 の下層の第 1 の酸化物層 207 としては In - M - Zn 酸化物 ( M は Al 、 Ti 、 Ga 、 Ge 、 Y 、 Zr 、 Sn 、 La 、 Ce または Hf 等の金属 ) で表記され、酸化物半導体層 208 よりも M の原子数比が高い酸化物層を含む。具体的には、第 1 の酸化物層 207 として、酸化物半導体層 208 よりも前述の元素を 1.5 倍以上、好ましくは 2 倍以上、さらに好ましくは 3 倍以上高い原子数比で含む酸化物層を用いる。前述の元素はインジウムよりも酸素と強く結合するため、酸素欠損が酸化物層に生じることを抑制する機能を有する。即ち、第 1 の酸化物層 207 は酸化物半導体層 208 よりも酸素欠損が生じにくい酸化物層である。 40

【 0119 】

また、酸化物半導体層 208 の上層の第 2 の酸化物層 209 としては、第 1 の酸化物層 207 と同様に In - M - Zn 酸化物 ( M は Al 、 Ti 、 Ga 、 Ge 、 Y 、 Zr 、 Sn 、 La 、 Ce または Hf 等の金属 ) で表記され、酸化物半導体層 208 よりも M の原子数比が高い酸化物層を含む。具体的には、第 2 の酸化物層 209 として、酸化物半導体層 208 よりも前述の元素を 1.5 倍以上、好ましくは 2 倍以上、さらに好ましくは 3 倍以上高い原子数比で含む酸化物層を用いる。

【 0120 】

つまり、第 1 の酸化物層 207 、酸化物半導体層 208 、第 2 の酸化物層 209 が、少な 50

くともインジウム、亜鉛およびM（MはAl、Ti、Ga、Ge、Y、Zr、Sn、La、CeまたはHf等の金属）を含むIn-M-Zn酸化物であるとき、第1の酸化物層207をIn:M:Zn=x<sub>1</sub>:y<sub>1</sub>:z<sub>1</sub> [原子数比]、酸化物半導体層208をIn:M:Zn=x<sub>2</sub>:y<sub>2</sub>:z<sub>2</sub> [原子数比]、第2の酸化物層209をIn:M:Zn=x<sub>3</sub>:y<sub>3</sub>:z<sub>3</sub> [原子数比]とすると、y<sub>1</sub>/x<sub>1</sub>およびy<sub>3</sub>/x<sub>3</sub>がy<sub>2</sub>/x<sub>2</sub>よりも大きくなることが好ましい。y<sub>1</sub>/x<sub>1</sub>およびy<sub>3</sub>/x<sub>3</sub>はy<sub>2</sub>/x<sub>2</sub>よりも1.5倍以上、好ましくは2倍以上、さらに好ましくは3倍以上とする。このとき、酸化物半導体層208において、y<sub>2</sub>がx<sub>2</sub>以上であるとトランジスタの電気特性を安定させることができる。ただし、y<sub>2</sub>がx<sub>2</sub>の3倍以上になると、トランジスタの電界効果移動度が低下してしまうため、y<sub>2</sub>はx<sub>2</sub>の3倍未満であることが好ましい。

10

#### 【0121】

なお、第1の酸化物層207がIn-M-Zn酸化物であるとき、ZnおよびOを除いてのInおよびMの原子数比率は好ましくはInが50atomic%未満、Mが50atomic%以上、さらに好ましくはInが25atomic%未満、Mが75atomic%以上とする。また、酸化物半導体層208がIn-M-Zn酸化物であるとき、ZnおよびOを除いてのInおよびMの原子数比率は好ましくはInが25atomic%以上、Mが75atomic%未満、さらに好ましくはInが34atomic%以上、Mが66atomic%未満とする。また、第2の酸化物層209がIn-M-Zn酸化物であるとき、ZnおよびOを除いてのInおよびMの原子数比率は好ましくはInが50atomic%未満、Mが50atomic%以上、さらに好ましくはInが25atomic%未満、Mが75atomic%以上とする。

20

#### 【0122】

なお、第1の酸化物層207と、第2の酸化物層209とは、異なる金属元素を構成元素として含む層としてもよいし、同じ金属元素を同一の原子数比で、又は異なる原子数比で含む層としてもよい。

#### 【0123】

第1の酸化物層207、酸化物半導体層208、及び第2の酸化物層209には、例えば、インジウム、亜鉛及びガリウムを含んだ酸化物半導体を用いることができる。

#### 【0124】

また、第1の酸化物層207及び第2の酸化物層209は、酸化物半導体層208を構成する金属元素を一種以上含み、伝導帯下端のエネルギーが酸化物半導体層208よりも、0.05eV、0.07eV、0.1eV、0.15eVのいずれか以上であって、2eV、1eV、0.5eV、0.4eVのいずれか以下の範囲で真空準位に近い酸化物半導体で形成することが好ましい。

30

#### 【0125】

このような構造において、第1のゲート電極層202及び/または第2のゲート電極層216に電界を印加すると、第1のゲート絶縁層の一部として機能する絶縁層206と、第2のゲート電極層として機能する絶縁層214に挟まれた、第1の酸化物層207、酸化物半導体層208及び第2の酸化物層209からなる積層構造のうち、伝導帯下端のエネルギーが最も小さい酸化物半導体層208にチャネルが形成される。すなわち、第1の酸化物層207及び第2の酸化物層209が形成されていることによって、トランジスタのチャネルを、酸化物半導体層208と構成元素（ただし、酸素を除く）が異なる絶縁層である絶縁層206及び絶縁層214と接しない構造とすることができる。

40

#### 【0126】

図5(D)に、絶縁層206、第1の酸化物層207、酸化物半導体層208、第2の酸化物層209及び絶縁層214を含む積層構造のバンド構造を模式的に示す。図5(D)において、Evacは真空準位のエネルギー、Ecは伝導帯下端のエネルギーを示す。

#### 【0127】

図5(D)より、酸化物層に挟まれた酸化物半導体層がウェル（井戸）となり、当該積層構造を用いたトランジスタにおいて、チャネルが酸化物半導体層に形成されることがわか

50

る。なお、第1の酸化物層207、酸化物半導体層208及び第2の酸化物層209は伝導帯下端のエネルギーが連続的に変化しているため、U字型井戸(U Shape Well)、または、ラウンドウェルとも呼ぶことができる。また、このような構成で形成されたチャネルを埋め込みチャネルということもできる。

【0128】

図5(D)に示すように、第1の酸化物層207、酸化物半導体層208及び第2の酸化物層209の界面近傍において、伝導帯下端のエネルギーが曲線を描くように連続的に変化する。In-M-Zn酸化物で表記される酸化物層において、組成に対するMの割合が高いほど該酸化物層のエネルギー・バンドギャップが広くなるため、第1の酸化物層207、酸化物半導体層208、及び第2の酸化物層209の界面近傍で各々の層の混合領域(混合層)が形成され、該混合領域においては前述の元素Mの組成が徐々に変化することにより、図5(D)に示すようなラウンドウェルが形成されると理解される。また、第1の酸化物層207、酸化物半導体層208、第2の酸化物層209の組成が近似することにより、酸素が相互に拡散しやすい。一方で、構成元素の異なる絶縁層206と第1の酸化物層207との間、及び第2の酸化物層209と絶縁層214との間には、上述の混合領域が形成されにくいため、エネルギー・バンド図においても連続的な変化は見られない。

【0129】

第1の酸化物層207、酸化物半導体層208及び第2の酸化物層209の界面近傍において、伝導帯下端のエネルギーにラウンドウェルが形成されることで、該界面近傍における電界集中を緩和することができる。

【0130】

なお、図5(D)では第1の酸化物層207の伝導帯下端のエネルギーが第2の酸化物層209の伝導帯下端のエネルギーよりも真空準位に近い場合を例に示したが、双方が同じ伝導帯下端のエネルギーを有する酸化物層であってもよいし、第2の酸化物層209が第1の酸化物層207の伝導帯下端のエネルギーよりも真空準位に近い伝導帯下端のエネルギーを有していてもよい。

【0131】

第1の酸化物層207及び第2の酸化物層209は、酸化物半導体層208を構成する金属元素を一種以上含む酸化物層であるから、これらの積層構造は主成分を共通して積層された酸化物積層ともいえる。主成分を共通として積層された酸化物積層は、各層を単に積層するのではなく連続接合(ここでは、特に伝導帯下端のエネルギーが各層の間で連続的に変化するU字型(ラウンド)の井戸構造)が形成されるように作製する。なぜなら、各層の界面にトラップ中心や再結合中心のような欠陥準位を形成するような不純物が混在していると、エネルギー・バンドの連続性が失われ、界面でキャリアがトラップあるいは再結合により消滅してしまうためである。

【0132】

連続接合を形成するためには、ロードロック室を備えたマルチチャンバー方式の成膜装置(スパッタリング装置)を用いて各層を大気に触れさせることなく連続して積層することが必要となる。スパッタリング装置における各チャンバーは、酸化物半導体にとって不純物となる水等を可能な限り除去すべくクライオポンプのような吸着式の真空排気ポンプを用いて高真空排気( $5 \times 10^{-7}$  Pa以上 $1 \times 10^{-4}$  Pa以下)することが好ましい。または、ターボ分子ポンプとコールドトラップを組み合わせて排気系からチャンバー内に気体が逆流しないようにしておくことが好ましい。

【0133】

なお、高純度真性酸化物半導体を得るために、チャンバー内を高真空排気するのみならずスパッタガスの高純度化も必要である。スパッタガスとして用いる酸素ガスやアルゴンガスは、露点が-40以下、好ましくは-80以下、より好ましくは-100以下にまで高純度化したガスを用いることで酸化物半導体に水分等が取り込まれることを可能な限り防ぐことができる。

【0134】

10

20

30

40

50

酸化物半導体層 208 の上層又は下層に設けられる第1の酸化物層 207 及び第2の酸化物層 209 はバリア層として機能し、酸化物積層に接する絶縁層（絶縁層 206 及び絶縁層 214）と、酸化物積層との界面に形成されるトラップ準位の影響が、トランジスタのキャリアの主な経路（キャリアパス）となる酸化物半導体層 208 へと及ぶことを抑制することができる。

【0135】

具体的には、酸化物半導体層 208 と比較して酸素欠損の生じにくい第1の酸化物層 207 及び第2の酸化物層 209 を酸化物半導体層 208 の上下に接して設けることで、酸化物半導体層 208 における酸素欠損を低減することができる。これによって、酸化物半導体層 208 の界面に酸素欠損に起因するトラップ準位が形成されることを抑制する。例えば、酸化物半導体層 208 は、一定電流測定法（CPM: Constant Photo current Method）により測定された局在準位による吸収係数を  $1 \times 10^{-3} / \text{cm}^2$  未満、好ましくは  $1 \times 10^{-4} / \text{cm}^2$  未満とすることができる。

10

【0136】

また、酸化物半導体層 208 のバックチャネル側に構成元素の異なる絶縁層 214（例えば、酸化シリコン膜を含む絶縁層）が接する場合、2層の界面に界面準位が形成され、該界面準位はチャネルを形成することがある。このような場合、しきい値電圧の異なる第2のトランジスタが出現し、トランジスタの見かけ上のしきい値電圧が変動することがある。しかしながら、トランジスタ 280 においては酸化物半導体層 208 を構成する金属元素を一種以上含んで第2の酸化物層 209 が構成されるため、酸化物半導体層 208 のバックチャネル側界面に界面準位を形成しにくくなる。よって第2の酸化物層 209 を設けることにより、トランジスタのしきい値電圧などの電気特性のばらつきを低減することができる。

20

【0137】

また、ゲート絶縁層として機能する絶縁層 206 と酸化物半導体層 208 との界面にチャネルが形成される場合、該界面で界面散乱が起こり、トランジスタの電界効果移動度が低くなる。しかしながら、トランジスタ 280 においては、酸化物半導体層 208 を構成する金属元素を一種以上含んで第1の酸化物層 207 が構成されるため、酸化物半導体層 208 のフロントチャネル側界面ではキャリアの散乱が起こりにくく、トランジスタの電界効果移動度を高くすることができる。

30

【0138】

また、第1の酸化物層 207 及び第2の酸化物層 209 は、絶縁層 206 及び絶縁層 212 の構成元素が、酸化物半導体層 208 へ混入して、不純物による準位が形成されることを抑制するためのバリア層としても機能する。

【0139】

例えば、酸化物半導体層 208 に含まれるシリコンの濃度は  $3 \times 10^{18} / \text{cm}^3$  以下、好ましくは  $3 \times 10^{17} / \text{cm}^3$  以下とする。また、酸化物半導体層 208 に含まれる炭素の濃度は  $3 \times 10^{18} / \text{cm}^3$  以下、好ましくは  $3 \times 10^{17} / \text{cm}^3$  以下とする。

【0140】

なお、酸化物半導体層中の不純物濃度は二次イオン分析法（SIMS: Secondary Ion Mass Spectrometry）で測定することができる。

40

【0141】

なお、第1の酸化物層 207 及び第2の酸化物層 209 は、酸化物半導体にとって不純物となる絶縁層 206 及び絶縁層 214 の構成元素が酸化物半導体層 208 に混入することを抑制する厚さ以上とする。また、酸化物半導体層 208 の膜厚を大きくすることで、トランジスタ 280 のオン電流を向上させることができるために、酸化物半導体層 208 の膜厚は、少なくとも第1の酸化物層 207 及び第2の酸化物層 209 の膜厚よりも大きく形成することが好ましい。

【0142】

また、第1の酸化物層 207 は、ゲート電極層とチャネルとして機能する酸化物半導体層

50

208との間に設けられる層であるため、トランジスタのオン電流を向上させるためには可能な限り薄くすることが好ましい。具体的には、第1の酸化物層207の膜厚は、例えば、0.3nm以上10nm未満、好ましくは0.3nm以上5nm以下とすることができる。

【0143】

また、水素や水分が不純物として酸化物半導体層に含まれてしまうとドナーを作りn型化するため、第1の酸化物層207の下側に水素や水分が外部から侵入することを防止する酸化アルミニウム膜を含む絶縁層206を設け、第2の酸化物層209の上側に水素や水分が外部から侵入することを防止する酸化アルミニウム膜を含む絶縁層212を設けることは、井戸型構造を実現する上で有用である。

10

【0144】

なお、第1の酸化物層207または第2の酸化物層209の伝導帯下端のエネルギーと、酸化物半導体層208の伝導帯下端のエネルギーとのエネルギー差が小さい場合、酸化物半導体層208の電子が該エネルギー差を越えてトラップ準位に達することがある。トラップ準位に電子が捕獲されることで、絶縁膜界面にマイナスの固定電荷が生じ、トランジスタのしきい値電圧はプラス方向にシフトしてしまう。

【0145】

したがって、第1の酸化物層207または第2の酸化物層209の伝導帯下端のエネルギーと、酸化物半導体層208の伝導帯下端のエネルギーとのエネルギー差を、それぞれ0.1eV以上、好ましくは0.15eV以上とすることで、トランジスタのしきい値電圧の変動が低減され、安定した電気特性を得ることができる。

20

【0146】

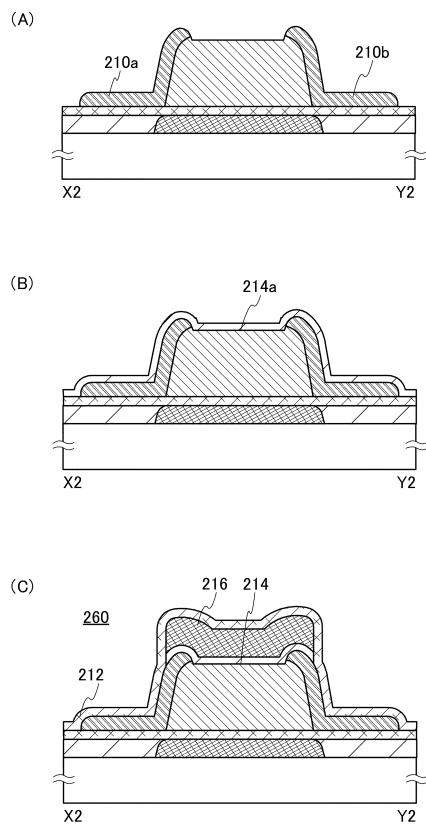

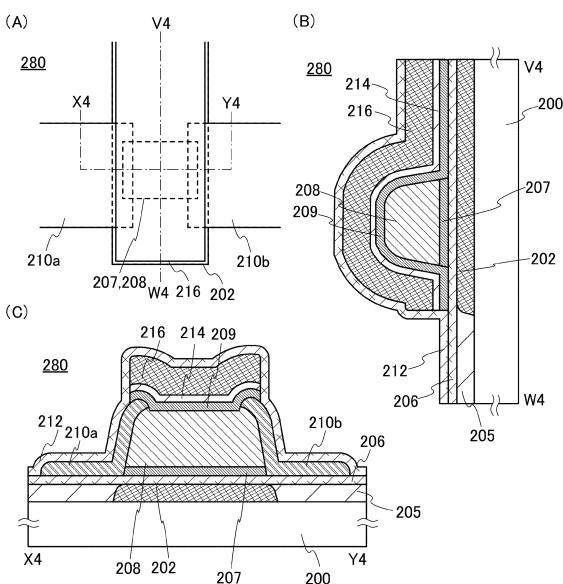

図6に本実施の形態のトランジスタの別の構成例を示す。図6(A)は、トランジスタ280の平面図であり、図6(B)は、図6(A)のV4-W4における断面図であり、図6(C)は、図6(A)のX4-Y4における断面図である。

【0147】

図6に示すトランジスタ280は、第2の酸化物層209が、ソース電極層210a及びドレイン電極層210bから露出した酸化物半導体層208を覆うように、ソース電極層210a及びドレイン電極層210b上に設けられる点において、図5のトランジスタ270と相違する。その他の構成は、トランジスタ270と同様とすることができる。

30

【0148】

トランジスタ280では、絶縁層206上に、第1の酸化物層207となる第1の酸化物膜と、酸化物半導体膜を連続的に成膜し、レジストマスクを用いたエッチングによって第1の酸化物膜及び酸化物半導体膜を島状に加工することで、第1の酸化物層207及び酸化物半導体層208が形成される。また、第1の酸化物層207及び酸化物半導体層208の一部に接するソース電極層210a及びドレイン電極層210bを形成後、該ソース電極層210a及びドレイン電極層210bから露出した酸化物半導体層208を覆うようにソース電極層210a及びドレイン電極層210b上に接して、第2の酸化物層209となる第2の酸化物膜及び絶縁膜214aとを連続的に形成し、第2のゲート電極層216をマスクとして第2の酸化物膜及び絶縁膜214aを加工することで、第2の酸化物層209及び絶縁層214が形成される。

40

【0149】

なお、上記において第1の酸化物膜及び酸化物半導体膜、または、第2の酸化物膜及び絶縁膜214aを大気開放することなく連続的に形成すると、2層の界面への水素や水分等の不純物の吸着を防止することができるため、好ましい。

【0150】

なお、上述の通り、トランジスタ280に含まれる第1の酸化物層207、酸化物半導体層208は同じレジストマスクを用いて加工されるため、第1の酸化物層207の上端部と酸化物半導体層208の下端部は略一致する。または、第1の酸化物層207及び酸化物半導体層208は、略一致した上面形状を有する。また、第2の酸化物層209及び絶

50

縁層 214 は、第2のゲート電極層 216 をマスクとして加工されるため、第2の酸化物層 209 の上端部と絶縁層 214 の下端部は略一致し、絶縁層 214 の上端部と第2のゲート電極層 216 の下端部は略一致する。または、第2の酸化物層 209 、絶縁層 214 及び第2のゲート電極層 216 は、略一致した上面形状を有する。

【0151】

トランジスタ 280 は、第1の酸化物層 207 及び酸化物半導体層 208 を島状に加工した後に、島状の第1の酸化物層 207 及び島状の酸化物半導体層 208 を覆うように第2の酸化物層 209 となる第2の酸化物膜を形成することで、酸化物半導体層 208 及び第1の酸化物層 207 のチャネル幅方向の側面が、第2の酸化物層 209 によって覆われた構成を有する。これによって、酸化物半導体層 208 のチャネル幅方向の側面においても界面準位の生成を抑制することが可能である。

10

【0152】

本実施の形態で示すトランジスタは、酸化物半導体層 208 と、該酸化物半導体層 208 と重なるゲート絶縁層及び保護絶縁層との間に、酸化物半導体層 208 を構成する金属元素のうち、少なくとも一の金属元素を構成元素として含む酸化物層を有することにより、酸化物半導体層 208 と、該酸化物半導体層と重なる絶縁層との界面にトラップ準位が形成されることを抑制することができる。よって、トランジスタの電気特性の劣化を抑制することができる。

【0153】

また、本実施の形態で示すトランジスタは、酸化物半導体層 208 の下側及び上側に重なるように設けられた第1のゲート電極層 202 及び第2のゲート電極層 216 によって、酸化物半導体層 208 の垂直方向の上下からゲート電極層の電界が印加される。よって、トランジスタのしきい値電圧を良好に制御することが可能となる。

20

【0154】

また、本実施の形態において、第2のゲート絶縁層を介して酸化物半導体層 208 と重なる第2のゲート電極層 216 は、酸化物半導体層 208 のチャネル形成領域の側面及び底面と重なるように設けられているため、チャネル形成領域に対して側面方向及び底面方向から電界が印加される。よって、トランジスタのしきい値電圧をより良好に制御し、且つ S 値を小さくすることができる。

【0155】

30

さらに本実施の形態のトランジスタは、過剰酸素を含有する酸化アルミニウム膜を含む絶縁層 206 、 212 を、酸化物半導体層 208 を包み込むように設けることで、酸化アルミニウム膜を含む絶縁層 206 、 212 で包まれた酸化物半導体層 208 へ十分に酸素を供給するとともに、酸化物半導体層 208 からの酸素の脱離、及び酸化物半導体層 208 への水素等の不純物の混入を抑制することができる。

【0156】

また、酸化物半導体層 208 を、過剰酸素を含有する酸化アルミニウム膜を含む絶縁層で包み込むとともに、酸化物半導体層 208 に接して、酸化物半導体層 208 を構成する金属元素のうち少なくとも一の金属元素を構成元素として含む酸化物層を設けることで、チャネルが形成される酸化物半導体層 208 の界面で生じうるキャリアの散乱をより抑制することができるため、効果的である。

40

【0157】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

【0158】

(実施の形態 3 )

本実施の形態では、実施の形態 1 又は実施の形態 2 のトランジスタに適用可能な酸化物半導体層の一例について説明する。

【0159】

酸化物半導体層は、非単結晶酸化物半導体層と単結晶酸化物半導体層とに大別される。非

50

単結晶酸化物半導体層とは、 C A A C - O S ( C A x i s A l i g n e d C r y s t a l l i n e O x i d e S e m i c o n d u c t o r ) 層、 多結晶酸化物半導体層、 微結晶酸化物半導体層、 非晶質酸化物半導体層などをいう。

【 0 1 6 0 】

まずは、 C A A C - O S 膜について説明する。

【 0 1 6 1 】

C A A C - O S 膜は、 c 軸配向した複数の結晶部を有する酸化物半導体層の一つである。

【 0 1 6 2 】

C A A C - O S 膜を透過型電子顕微鏡 ( T E M : T r a n s m i s s i o n E l e c t r o n M i c r o s c o p e ) によって観察すると、 明確な結晶部同士の境界、 即ち結晶粒界 ( グレインバウンダリーともいう。 ) を確認することが困難である。そのため、 C A A C - O S 膜は、 結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

10

【 0 1 6 3 】

C A A C - O S 膜を、 試料面と概略平行な方向から T E M によって観察 ( 断面 T E M 観察 ) すると、 結晶部において、 金属原子が層状に配列していることを確認できる。 金属原子の各層は、 C A A C - O S 膜の膜を形成する面 ( 被形成面ともいう。 ) または上面の凹凸を反映した形状であり、 C A A C - O S 膜の被形成面または上面と平行に配列する。

【 0 1 6 4 】

一方、 C A A C - O S 膜を、 試料面と概略垂直な方向から T E M によって観察 ( 平面 T E M 観察 ) すると、 結晶部において、 金属原子が三角形状または六角形状に配列していることを確認できる。 しかしながら、 異なる結晶部間で、 金属原子の配列に規則性は見られない。

20

【 0 1 6 5 】

断面 T E M 観察および平面 T E M 観察より、 C A A C - O S 膜の結晶部は配向性を有していることがわかる。

【 0 1 6 6 】

なお、 C A A C - O S 膜に含まれるほとんどの結晶部は、 一辺が 1 0 0 n m 未満の立方体内に収まる大きさである。 従って、 C A A C - O S 膜に含まれる結晶部は、 一辺が 1 0 n m 未満、 5 n m 未満または 3 n m 未満の立方体内に収まる大きさの場合も含まれる。 ただし、 C A A C - O S 膜に含まれる複数の結晶部が連結することで、 一つの大きな結晶領域を形成する場合がある。 例えば、 平面 T E M 像において、 2 5 0 0 n m <sup>2</sup> 以上、 5 μ m <sup>2</sup> 以上または 1 0 0 0 μ m <sup>2</sup> 以上となる結晶領域が観察される場合がある。

30

【 0 1 6 7 】

C A A C - O S 膜に対し、 X 線回折 ( X R D : X - R a y D i f f r a c t i o n ) 装置を用いて構造解析を行うと、 例えば I n G a Z n O <sub>4</sub> の結晶を有する C A A C - O S 膜の o u t - o f - p l a n e 法による解析では、 回折角 ( 2  $\theta$  ) が 3 1  $^{\circ}$  近傍にピークが現れる場合がある。 このピークは、 I n G a Z n O <sub>4</sub> の結晶の ( 0 0 9 ) 面に帰属されることから、 C A A C - O S 膜の結晶が c 軸配向性を有し、 c 軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

【 0 1 6 8 】

一方、 C A A C - O S 膜に対し、 c 軸に概略垂直な方向から X 線を入射させる i n - p l a n e 法による解析では、 2  $\theta$  が 5 6  $^{\circ}$  近傍にピークが現れる場合がある。 このピークは、 I n G a Z n O <sub>4</sub> の結晶の ( 1 1 0 ) 面に帰属される。 I n G a Z n O <sub>4</sub> の単結晶酸化物半導体層であれば、 2  $\theta$  を 5 6  $^{\circ}$  近傍に固定し、 試料面の法線ベクトルを軸 ( c 軸 ) として試料を回転させながら分析 ( スキャン ) を行うと、 ( 1 1 0 ) 面と等価な結晶面に帰属されるピークが 6 本観察される。 これに対し、 C A A C - O S 膜の場合は、 2  $\theta$  を 5 6  $^{\circ}$  近傍に固定して スキャンした場合でも、 明瞭なピークが現れない。

40

【 0 1 6 9 】

以上のことから、 C A A C - O S 膜では、 異なる結晶部間では a 軸および b 軸の配向は不規則であるが、 c 軸配向性を有し、 かつ c 軸が被形成面または上面の法線ベクトルに平行

10

20

30

40

50

な方向を向いていることがわかる。従って、前述の断面TEM観察で確認された層状に配列した金属原子の各層は、結晶のa b面に平行な面である。

【0170】

なお、結晶部は、CAAC-OS膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶のc軸は、CAAC-OS膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えば、CAAC-OS膜の形状をエッチングなどによって変化させた場合、結晶のc軸がCAAC-OS膜の被形成面または上面の法線ベクトルと平行にならないこともある。

【0171】

また、CAAC-OS膜中において、c軸配向した結晶部の分布が均一でなくてもよい。10 例えば、CAAC-OS膜の結晶部が、CAAC-OS膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりもc軸配向した結晶部の割合が高くなることがある。また、CAAC-OS膜に不純物を添加する場合、不純物が添加された領域が変質し、部分的にc軸配向した結晶部の割合の異なる領域が形成されることもある。

【0172】

なお、InGaN<sub>n</sub>O<sub>4</sub>の結晶を有するCAAC-OS膜のout-of-plane法による解析では、2θが31°近傍のピークの他に、2θが36°近傍にもピークが現れる場合がある。2θが36°近傍のピークは、CAAC-OS膜中の一部に、c軸配向性を有さない結晶が含まれることを示している。CAAC-OS膜は、2θが31°近傍にピークを示し、2θが36°近傍にピークを示さないことが好ましい。

【0173】

CAAC-OS膜は、不純物濃度の低い酸化物半導体層である。不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体層の主成分以外の元素である。特に、シリコンなどの、酸化物半導体層を構成する金属元素よりも酸素との結合力の強い元素は、酸化物半導体層から酸素を奪うことで酸化物半導体層の原子配列を乱し、結晶性を低下させる要因となる。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径（または分子半径）が大きいため、酸化物半導体層内部に含まれると、酸化物半導体層の原子配列を乱し、結晶性を低下させる要因となる。なお、酸化物半導体層に含まれる不純物は、キャリアトラップやキャリア発生源となる場合がある。

【0174】

また、CAAC-OS膜は、欠陥準位密度の低い酸化物半導体層である。例えば、酸化物半導体層中の酸素欠損は、キャリアトラップとなることや、水素を捕獲することによってキャリア発生源となることがある。

【0175】

不純物濃度が低く、欠陥準位密度が低い（酸素欠損の少ない）、すなわち高純度真性または実質的に高純度真性である酸化物半導体層は、キャリア発生源が少ないため、キャリア密度を低くすることができる。従って、当該酸化物半導体層を用いたトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリオンともいう。）になることが少ない。また、高純度真性または実質的に高純度真性である酸化物半導体層は、キャリアトラップが少ない。そのため、当該酸化物半導体層を用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる。なお、酸化物半導体層のキャリアトラップに捕獲された電荷は、放出するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、不純物濃度が高く、欠陥準位密度が高い酸化物半導体層を用いたトランジスタは、電気特性が不安定となる場合がある。

【0176】

また、CAAC-OS膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

【0177】

次に、微結晶酸化物半導体層について説明する。

10

20

30

40

50

## 【0178】

微結晶酸化物半導体層は、TEMによる観察像では、明確に結晶部を確認することができない場合がある。微結晶酸化物半導体層に含まれる結晶部は、1nm以上100nm以下、または1nm以上10nm以下の大きさであることが多い。特に、1nm以上10nm以下、または1nm以上3nm以下の微結晶であるナノ結晶(nc:nanocrystalline)を有する酸化物半導体層を、nc-OS(nanocrystalline Oxide Semiconductor)膜と呼ぶ。また、nc-OS膜は、例えば、TEMによる観察像では、結晶粒界を明確に確認できない場合がある。

## 【0179】

nc-OS膜は、微小な領域(例えば、1nm以上10nm以下の領域、特に1nm以上3nm以下の領域)において原子配列に周期性を有する。また、nc-OS膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。従って、nc-OS膜は、分析方法によっては、非晶質酸化物半導体層と区別が付かない場合がある。例えば、nc-OS膜に対し、結晶部よりも大きい径のX線を用いるXRD装置を用いて構造解析を行うと、out-of-plane法による解析では、結晶面を示すピークが検出されない。また、nc-OS膜に対し、結晶部よりも大きいプローブ径(例えば50nm以上)の電子線を用いる電子線回折(制限視野電子線回折ともいう。)を行うと、ハローパターンのような回折パターンが観測される。一方、nc-OS膜に対し、結晶部の大きさと近いか結晶部よりも小さいプローブ径(例えば1nm以上30nm以下)の電子線を用いる電子線回折(ナノビーム電子線回折ともいう。)を行うと、スポットが観測される。また、nc-OS膜に対しナノビーム電子線回折を行うと、円を描くように(リング状に)輝度の高い領域が観測される場合がある。また、nc-OS膜に対しナノビーム電子線回折を行うと、リング状の領域内に複数のスポットが観測される場合がある。

10

20

## 【0180】

nc-OS膜は、非晶質酸化物半導体層よりも規則性の高い酸化物半導体層である。そのため、nc-OS膜は、非晶質酸化物半導体層よりも欠陥準位密度が低くなる。ただし、nc-OS膜は、異なる結晶部間で結晶方位に規則性が見られない。そのため、nc-OS膜は、CAAC-OS膜と比べて欠陥準位密度が高くなる。

30

## 【0181】

なお、酸化物半導体層は、例えば、非晶質酸化物半導体層、微結晶酸化物半導体層、CAAC-OS膜のうち、二種以上を有する積層膜であってもよい。

## 【0182】

以下に、CAAC-OS膜の成膜方法の例について説明する。

## 【0183】

CAAC-OS膜は、例えば、多結晶である酸化物半導体スパッタリング用ターゲットを用い、スパッタリング法によって成膜する。当該スパッタリング用ターゲットにイオンが衝突すると、スパッタリング用ターゲットに含まれる結晶領域がa-b面から劈開し、a-b面に平行な面を有する平板状またはペレット状のスパッタリング粒子として剥離することがある。この場合、当該平板状またはペレット状のスパッタリング粒子が、結晶状態を維持したまま基板に到達することで、CAAC-OS膜を成膜することができる。

40

## 【0184】

平板状またはペレット状のスパッタリング粒子は、例えば、a-b面に平行な面の円相当径が3nm以上10nm以下、厚さ(a-b面に垂直な方向の長さ)が0.7nm以上1nm未満である。なお、平板状またはペレット状のスパッタリング粒子は、a-b面に平行な面が正三角形または正六角形であってもよい。ここで、面の円相当径とは、面の面積と等しい正円の直径をいう。

## 【0185】

また、CAAC-OS膜を成膜するために、以下の条件を適用することが好ましい。

## 【0186】

50

成膜時の基板温度を高めることで、基板到達後にスパッタリング粒子のマイグレーションが起こる。具体的には、基板温度を100以上740以下として成膜する。成膜時の基板温度を高めることで、平板状またはペレット状のスパッタリング粒子が基板に到達した場合、基板上でマイグレーションが起こり、スパッタリング粒子の平らな面が基板に付着する。このとき、スパッタリング粒子が正に帯電することで、スパッタリング粒子同士が反発しながら基板に付着するため、スパッタリング粒子が偏って不均一に重なることがなく、厚さの均一なCAC-OS膜を成膜することができる。一方、成膜雰囲気の温度が高すぎると、ターゲットに含まれる亜鉛が昇華してしまうことがあるため、基板温度は、好ましくは200以上500以下、より好ましくは200以上350以下とする。

10

#### 【0187】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物濃度（水素、水、二酸化炭素及び窒素など）を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が-80以下、好ましくは-100以下である成膜ガスを用いる。

#### 【0188】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30体積%以上、好ましくは100体積%とする。

#### 【0189】

または、CAC-OS膜は、以下の方法により形成する。

20

#### 【0190】

まず、第1の酸化物半導体膜を1nm以上10nm未満の厚さで成膜する。第1の酸化物半導体膜はスパッタリング法を用いて成膜する。具体的には、基板温度を100以上500以下、好ましくは150以上450以下とし、成膜ガス中の酸素割合を30体積%以上、好ましくは100体積%として成膜する。

#### 【0191】

次に、加熱処理を行い、第1の酸化物半導体膜を結晶性の高い第1のCAC-OS膜とする。加熱処理の温度は、350以上740以下、好ましくは450以上650以下とする。また、加熱処理の時間は1分以上24時間以下、好ましくは6分以上4時間以下とする。また、加熱処理は、不活性雰囲気または酸化性雰囲気で行えばよい。好ましくは、不活性雰囲気で加熱処理を行った後、酸化性雰囲気で加熱処理を行う。不活性雰囲気での加熱処理により、第1の酸化物半導体膜の不純物濃度を短時間で低減することができる。一方、不活性雰囲気での加熱処理により第1の酸化物半導体膜に酸素欠損が生成されることがある。その場合、酸化性雰囲気での加熱処理によって該酸素欠損を低減することができる。なお、加熱処理は10000Pa以下、100Pa以下、10Pa以下または1Pa以下の減圧下で行ってもよい。減圧下では、第1の酸化物半導体膜の不純物濃度をさらに短時間で低減することができる。

30

#### 【0192】

第1の酸化物半導体膜は、厚さが1nm以上10nm未満であることにより、厚さが10nm以上である場合と比べ、加熱処理によって容易に結晶化させることができる。

40

#### 【0193】

次に、第1の酸化物半導体膜と同じ組成である第2の酸化物半導体膜を10nm以上50nm以下の厚さで成膜する。第2の酸化物半導体膜はスパッタリング法を用いて成膜する。具体的には、基板温度を100以上500以下、好ましくは150以上450以下とし、成膜ガス中の酸素割合を30体積%以上、好ましくは100体積%として成膜する。

#### 【0194】

次に、加熱処理を行い、第2の酸化物半導体膜を第1のCAC-OS膜から固相成長させることで、結晶性の高い第2のCAC-OS膜とする。加熱処理の温度は、350

50

以上 740 以下、好ましくは 450 以上 650 以下とする。また、加熱処理の時間は 1 分以上 24 時間以下、好ましくは 6 分以上 4 時間以下とする。また、加熱処理は、不活性雰囲気または酸化性雰囲気で行えればよい。好ましくは、不活性雰囲気で加熱処理を行った後、酸化性雰囲気で加熱処理を行う。不活性雰囲気での加熱処理により、第 2 の酸化物半導体膜の不純物濃度を短時間で低減することができる。一方、不活性雰囲気での加熱処理により第 2 の酸化物半導体膜に酸素欠損が生成されることがある。その場合、酸化性雰囲気での加熱処理によって該酸素欠損を低減することができる。なお、加熱処理は 1000 Pa 以下、100 Pa 以下、10 Pa 以下または 1 Pa 以下の減圧下で行ってもよい。減圧下では、第 2 の酸化物半導体膜の不純物濃度をさらに短時間で低減することができる。

10

#### 【0195】

以上のようにして、合計の厚さが 10 nm 以上である CAC-OS 膜を形成することができる。当該 CAC-OS 膜を、酸化物積層における酸化物半導体層として好適に用いることができる。

#### 【0196】

次に、例えば、基板加熱しないことなどにより被形成面が低温（例えば、130 未満、100 未満、70 未満または室温（20 以上 25 以下）程度）である場合の酸化物膜の形成方法について説明する。

#### 【0197】

被形成面が低温の場合、スパッタ粒子は被成膜面に不規則に降り注ぐ。スパッタ粒子は、例えば、マイグレーションをしないため、既に他のスパッタ粒子が堆積している領域も含め、無秩序に堆積していく。即ち、堆積して得られる酸化物膜は、例えば、厚さが均一でなく、結晶の配向も無秩序になる場合がある。このようにして得られた酸化物膜は、スパッタ粒子の結晶性を、ある程度維持するため、結晶部（ナノ結晶）を有する。

20

#### 【0198】

また、例えば、成膜時の圧力が高い場合、飛翔中のスパッタ粒子は、アルゴンなどの他の粒子（原子、分子、イオン、ラジカルなど）と衝突する頻度が高まる。スパッタ粒子は、飛翔中に他の粒子と衝突する（再スパッタされる）ことで、結晶構造が崩れる場合がある。例えば、スパッタ粒子は、他の粒子と衝突することで、平板状の形状を維持することができず、細分化（例えば各原子に分かれた状態）される場合がある。このとき、スパッタ粒子から分かれた各原子が被形成面に堆積していくことで、非晶質酸化物膜が形成される場合がある。

30

#### 【0199】

また、出発点に多結晶酸化物を有するターゲットを用いたスパッタリング法ではなく、液体を用いて成膜する方法の場合、またはターゲットなどの固体を気体化することで成膜する方法の場合、各原子に分かれた状態で飛翔して被形成面に堆積するため、非晶質酸化物膜が形成される場合がある。また、例えば、レーザアブレーション法では、ターゲットから放出された原子、分子、イオン、ラジカル、クラスターなどが飛翔して被形成面に堆積するため、非晶質酸化物膜が形成される場合がある。

40

#### 【0200】

本発明の一態様のトランジスタにおいて、酸化物半導体層を挟む酸化物層を設ける場合、第 1 の酸化物層、酸化物半導体層又は第 2 の酸化物層にはそれぞれ、上述のいずれの結晶状態の酸化物層又は酸化物半導体層を適用してもよい。但し、チャネルとして機能する酸化物半導体層には、CAC-OS 膜を適用することが好ましい。

#### 【0201】

以上、本実施の形態で示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【0202】

（実施の形態 4）

本実施の形態では、実施の形態 1 又は 2 のいずれかで一例を示したトランジスタを利用し

50

た回路の一例について、図面を参照して説明する。

【0203】

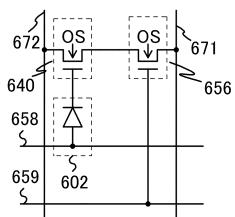

図11(A)に半導体装置の回路図を、図11(C)に半導体装置の断面図をそれぞれ示す。図11(C)は、左側にトランジスタ260のチャネル長方向の断面図を示し、右側にチャネル幅方向の断面図を示している。また回路図には、酸化物半導体が適用されたトランジスタであることを明示するために、「O S」の記載を付している。

【0204】

図11(C)に示す半導体装置は、下部に第1の半導体材料を用いたトランジスタ2200を有し、上部に第2の半導体材料を用いたトランジスタを有する。ここでは、第2の半導体材料を用いたトランジスタとして、実施の形態1で例示したトランジスタ260を適用した例について説明する。

10

【0205】

ここで、第1の半導体材料と第2の半導体材料は異なる禁制帯幅を持つ材料とすることが望ましい。例えば、第1の半導体材料を酸化物半導体以外の半導体材料(シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等など)とし、第2の半導体材料を実施の形態1で説明した酸化物半導体とすることができる。酸化物半導体以外の材料として単結晶シリコンなどを用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、オフ電流が低い。

【0206】

ここでは、トランジスタ2200がpチャネル型のトランジスタであるものとして説明するが、nチャネル型のトランジスタを用いて異なる回路を構成できることは言うまでもない。また、酸化物半導体を用いた実施の形態1又は2に示すようなトランジスタを用いる他は、半導体装置に用いられる材料や半導体装置の構造など、半導体装置の具体的な構成をここで示すものに限定する必要はない。

20

【0207】

図11(A)、(C)に示す構成は、pチャネル型のトランジスタとnチャネル型のトランジスタを直列に接続し、且つ、それぞれのゲートを接続した、いわゆるCMOS回路の構成例について示している。

【0208】

なお、図11(C)に示すように、トランジスタ260は、トランジスタ2200上に積層して設けられている。このように、2つのトランジスタを積層することにより、回路の占有面積が低減され、より高密度に複数の回路を配置することができる。さらに、トランジスタ260の第1のゲート電極層は、トランジスタ2200のゲート電極層と共通の電極とすることができます。これによって、半導体装置のさらなる高集積化が図れ、また半導体装置の作製工程の短縮化を図ることができるため、好ましい。

30

【0209】

なお、図11(C)では、トランジスタ260のソースまたはドレインの一方と、トランジスタ2200のソースまたはドレインの一方がプラグによって電気的に接続されている。

【0210】

40

本発明の一態様の酸化物半導体が適用されたトランジスタは、オン電流が高められているため、回路の高速動作が可能となる。

【0211】

なお、図11(C)に示す構成において、トランジスタ260やトランジスタ2200の電極の接続構成を異ならせることにより、様々な回路を構成することができる。例えば図11(B)に示すように、トランジスタ260のソースまたはドレインの一方とトランジスタ2200のソースまたはドレインの一方を接続し、トランジスタ260のソースまたはドレインの他方とトランジスタ2200のソースまたはドレインの他方を接続した回路構成とすることにより、いわゆるアナログスイッチとして機能させることができる。

【0212】

50

本実施の形態は、本明細書中に記載する他の実施の形態と適宜組み合わせて実施することができる。

【0213】

(実施の形態5)

本実施の形態では、実施の形態1又は2のいずれかで一例を示したトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限がない半導体装置(記憶装置)の一例を、図面を用いて説明する。

【0214】

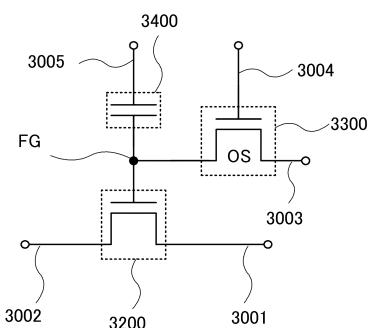

図7に半導体装置の回路図を示す。

【0215】

図7に示す半導体装置は、第1の半導体材料を用いたトランジスタ3200と第2の半導体材料を用いたトランジスタ3300、および容量素子3400を有している。なお、トランジスタ3300としては、実施の形態1又は2で説明したトランジスタを用いることができる。なお、図7では、トランジスタ3300が、酸化物半導体を含むことを明確に判明できるよう、トランジスタの記号に「OS」と付記している。

10

【0216】

トランジスタ3300は、酸化物半導体を有する半導体層にチャネルが形成されるトランジスタである。トランジスタ3300は、オフ電流が小さいため、これを用いることにより長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作を必要としない、或いは、リフレッシュ動作の頻度が極めて少ない半導体記憶装置とすることが可能となるため、消費電力を十分に低減することができる。

20

【0217】

図7において、第1の配線3001はトランジスタ3200のソース電極と電気的に接続され、第2の配線3002はトランジスタ3200のドレイン電極と電気的に接続されている。また、第3の配線3003はトランジスタ3300のソース電極またはドレイン電極の一方と電気的に接続され、第4の配線3004はトランジスタ3300のゲート電極と電気的に接続されている。そして、トランジスタ3200のゲート電極、およびトランジスタ3300のソース電極またはドレイン電極の他方は、容量素子3400の電極の一方と電気的に接続され、第5の配線3005は容量素子3400の電極の他方と電気的に接続されている。

30

【0218】

図7に示す半導体装置では、トランジスタ3200のゲート電極の電位が保持可能という特徴を活かすことで、次のように、情報の書き込み、保持、読み出しが可能である。

【0219】

情報の書き込みおよび保持について説明する。まず、第4の配線3004の電位を、トランジスタ3300がオン状態となる電位にして、トランジスタ3300をオン状態とする。これにより、第3の配線3003の電位が、トランジスタ3200のゲート電極、および容量素子3400に与えられる。すなわち、トランジスタ3200のゲート電極には、所定の電荷が与えられる(書き込み)。ここでは、異なる二つの電位レベルを与える電荷(以下Lowレベル電荷、Highレベル電荷という)のいずれかが与えられるものとする。その後、第4の配線3004の電位を、トランジスタ3300がオフ状態となる電位にして、トランジスタ3300をオフ状態とすることにより、トランジスタ3200のゲート電極に与えられた電荷が保持される(保持)。

40

【0220】

トランジスタ3300のオフ電流は極めて小さいため、トランジスタ3200のゲート電極の電荷は長時間にわたって保持される。

【0221】

次に情報の読み出しについて説明する。第1の配線3001に所定の電位(定電位)を与えた状態で、第5の配線3005に適切な電位(読み出し電位)を与えると、トランジスタ3200のゲート電極に保持された電荷量に応じて、第2の配線3002は異なる電位

50

をとる。一般に、トランジスタ3200をnチャネル型とすると、トランジスタ3200のゲート電極にHighレベル電荷が与えられている場合の見かけのしきい値 $V_{th\_H}$ は、トランジスタ3200のゲート電極にLowレベル電荷が与えられている場合の見かけのしきい値 $V_{th\_L}$ より低くなるためである。ここで、見かけのしきい値電圧とは、トランジスタ3200を「オン状態」とするために必要な第5の配線3005の電位をいうものとする。したがって、第5の配線3005の電位を $V_{th\_H}$ と $V_{th\_L}$ の間の電位 $V_0$ とすることにより、トランジスタ3200のゲート電極に与えられた電荷を判別できる。例えば、書き込みにおいて、Highレベル電荷が与えられていた場合には、第5の配線3005の電位が $V_0 (> V_{th\_H})$ となれば、トランジスタ3200は「オン状態」となる。Lowレベル電荷が与えられていた場合には、第5の配線3005の電位が $V_0 (< V_{th\_L})$ となっても、トランジスタ3200は「オフ状態」のままである。このため、第2の配線3002の電位を判別することで、保持されている情報を読み出すことができる。10

#### 【0222】

なお、メモリセルをアレイ状に配置して用いる場合、所望のメモリセルの情報のみを読み出せることが必要になる。このように情報を読み出さない場合には、ゲート電極の状態にかかわらずトランジスタ3200が「オフ状態」となるような電位、つまり、 $V_{th\_H}$ より小さい電位を第5の配線3005に与えればよい。または、ゲート電極の状態にかかわらずトランジスタ3200が「オン状態」となるような電位、つまり、 $V_{th\_L}$ より大きい電位を第5の配線3005に与えればよい。20

#### 【0223】

本実施の形態に示す半導体装置では、チャネル形成領域に酸化物半導体を用いたオフ電流の極めて小さいトランジスタを適用することで、極めて長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合（ただし、電位は固定されていることが望ましい）であっても、長期にわたって記憶内容を保持することが可能である。

#### 【0224】

また、本実施の形態に示す半導体装置では、情報の書き込みに高い電圧を必要とせず、素子の劣化の問題もない。例えば、従来の不揮発性メモリのように、フローティングゲートへの電子の注入や、フローティングゲートからの電子の引き抜きを行う必要がないため、ゲート絶縁層の劣化といった問題が生じない。すなわち、開示する発明に係る半導体装置では、従来の不揮発性メモリで問題となっている書き換え可能回数に制限はなく、信頼性が飛躍的に向上する。さらに、トランジスタのオン状態、オフ状態によって、情報の書き込みが行われるため、高速な動作も容易に実現しうる。30

#### 【0225】

以上のように、微細化および高集積化を実現し、かつ高い電気特性を付与された半導体装置を提供することができる。

#### 【0226】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。40

#### 【0227】

（実施の形態6）

本実施の形態では、少なくとも実施の形態1又は2のいずれかで一例を示したトランジスタを用いることができ、先の実施の形態で説明した記憶装置を含むCPUについて説明する。

#### 【0228】

図8は、実施の形態1又は2で説明したトランジスタを少なくとも一部に用いたCPUの一例の構成を示すブロック図である。

#### 【0229】

50

20

30

40

50

図8に示すCPUは、基板1190上に、ALU1191(ALU:Arithmetical logic unit、演算回路)、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、タイミングコントローラ1195、レジスタ1196、レジスタコントローラ1197、バスインターフェース1198(Bus I/F)、書き換え可能なROM1199、およびROMインターフェース1189(ROM I/F)を有している。基板1190は、半導体基板、SOI基板、ガラス基板などを用いる。ROM1199およびROMインターフェース1189は、別チップに設けてもよい。もちろん、図8に示すCPUは、その構成を簡略化して示した一例にすぎず、実際のCPUはその用途によって多種多様な構成を有している。例えば、図8に示すCPUまたは演算回路を含む構成を一つのコアとし、当該コアを複数含み、それぞれのコアが並列で動作するような構成としてもよい。また、CPUが内部演算回路やデータバスで扱えるビット数は、例えば8ビット、16ビット、32ビット、64ビットなどとすることができます。

10

#### 【0230】

バスインターフェース1198を介してCPUに入力された命令は、インストラクションデコーダ1193に入力され、デコードされた後、ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195に入力される。

#### 【0231】

ALUコントローラ1192、インタラプトコントローラ1194、レジスタコントローラ1197、タイミングコントローラ1195は、デコードされた命令に基づき、各種制御を行なう。具体的にALUコントローラ1192は、ALU1191の動作を制御するための信号を生成する。また、インタラプトコントローラ1194は、CPUのプログラム実行中に、外部の入出力装置や、周辺回路からの割り込み要求を、その優先度やマスク状態から判断し、処理する。レジスタコントローラ1197は、レジスタ1196のアドレスを生成し、CPUの状態に応じてレジスタ1196の読み出しや書き込みを行なう。

20

#### 【0232】

また、タイミングコントローラ1195は、ALU1191、ALUコントローラ1192、インストラクションデコーダ1193、インタラプトコントローラ1194、およびレジスタコントローラ1197の動作のタイミングを制御する信号を生成する。例えばタイミングコントローラ1195は、基準クロック信号CLK1を元に、内部クロック信号CLK2を生成する内部クロック生成部を備えており、内部クロック信号CLK2を上記各種回路に供給する。

30

#### 【0233】

図8に示すCPUでは、レジスタ1196に、メモリセルが設けられている。レジスタ1196のメモリセルとして、先の実施の形態に示したトランジスタを用いることができる。

。

#### 【0234】

図8に示すCPUにおいて、レジスタコントローラ1197は、ALU1191からの指示に従い、レジスタ1196における保持動作の選択を行う。すなわち、レジスタ1196が有するメモリセルにおいて、フリップフロップによるデータの保持を行うか、容量素子によるデータの保持を行うかを、選択する。フリップフロップによるデータの保持が選択されている場合、レジスタ1196内のメモリセルへの、電源電圧の供給が行われる。容量素子におけるデータの保持が選択されている場合、容量素子へのデータの書き換えが行われ、レジスタ1196内のメモリセルへの電源電圧の供給を停止することができる。

40

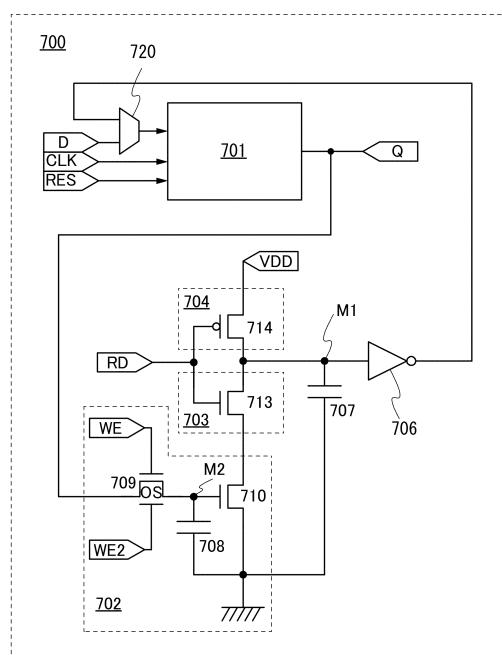

#### 【0235】

図9は、レジスタ1196として用いることのできる記憶素子の回路図の一例である。記憶素子700は、電源遮断で記憶データが揮発する回路701と、電源遮断で記憶データが揮発しない回路702と、スイッチ703と、スイッチ704と、論理素子706と、容量素子707と、選択機能を有する回路720と、を有する。回路702は、容量素子

50

708と、トランジスタ709と、トランジスタ710と、を有する。なお、記憶素子700は、必要に応じて、ダイオード、抵抗素子、インダクタなどのその他の素子をさらに有していても良い。

【0236】

ここで、回路702には、先の実施の形態で説明した記憶装置を用いることができる。記憶素子700への電源電圧の供給が停止した際、回路702のトランジスタ709のゲートには接地電位(0V)、またはトランジスタ709がオフする電位が入力され続ける構成とする。例えば、トランジスタ709のゲートが抵抗等の負荷を介して接地される構成とする。

【0237】

スイッチ703は、一導電型(例えば、nチャネル型)のトランジスタ713を用いて構成され、スイッチ704は、一導電型とは逆の導電型(例えば、pチャネル型)のトランジスタ714を用いて構成した例を示す。ここで、スイッチ703の第1の端子はトランジスタ713のソースとドレインの一方に対応し、スイッチ703の第2の端子はトランジスタ713のゲートに入力される制御信号RDによって、第1の端子と第2の端子の間の導通または非導通(つまり、トランジスタ713のオン状態またはオフ状態)が選択される。スイッチ704の第1の端子はトランジスタ714のソースとドレインの一方に対応し、スイッチ704の第2の端子はトランジスタ714のソースとドレインの他方に対応し、スイッチ704はトランジスタ714のゲートに入力される制御信号RDによって、第1の端子と第2の端子の間の導通または非導通(つまり、トランジスタ714のオン状態またはオフ状態)が選択される。

10

20

30

40

【0238】

トランジスタ709のソースとドレインの一方は、容量素子708の一対の電極のうちの一方、およびトランジスタ710のゲートと電気的に接続される。ここで、接続部分をノードM2とする。トランジスタ710のソースとドレインの一方は、低電位電源を供給することのできる配線(例えばGND線)に電気的に接続され、他方は、スイッチ703の第1の端子(トランジスタ713のソースとドレインの一方)と電気的に接続される。スイッチ703の第2の端子(トランジスタ713のソースとドレインの他方)はスイッチ704の第1の端子(トランジスタ714のソースとドレインの一方)と電気的に接続される。スイッチ704の第2の端子(トランジスタ714のソースとドレインの他方)は電源電位VDDを供給することのできる配線と電気的に接続される。スイッチ703の第2の端子(トランジスタ713のソースとドレインの他方)と、スイッチ704の第1の端子(トランジスタ714のソースとドレインの一方)と、論理素子706の入力端子と、容量素子707の一対の電極のうちの一方と、は電気的に接続される。ここで、接続部分をノードM1とする。容量素子707の一対の電極のうちの他方は、一定の電位が入力される構成とすることができます。例えば、低電源電位(GND等)または高電源電位(VDD等)が入力される構成とすることができます。容量素子707の一対の電極のうちの他方は、低電位電源を供給することのできる配線(例えばGND線)と電気的に接続される。容量素子708の一対の電極のうちの他方は、一定の電位が入力される構成とすることができます。例えば、低電源電位(GND等)または高電源電位(VDD等)が入力される構成とすることができます。容量素子708の一対の電極のうちの他方は、低電位電源を供給することのできる配線(例えばGND線)と電気的に接続される。

【0239】

なお、容量素子707および容量素子708は、トランジスタや配線の寄生容量等を積極的に利用することによって省略することも可能である。

【0240】

トランジスタ709の第1ゲート(第1のゲート電極)には、制御信号WEが入力される。スイッチ703およびスイッチ704は、制御信号WEとは異なる制御信号RDによって第1の端子と第2の端子の間の導通状態または非導通状態を選択され、一方のスイッチ

50

の第1の端子と第2の端子の間が導通状態のとき他方のスイッチの第1の端子と第2の端子の間は非導通状態となる。

【0241】

トランジスタ709のソースとドレインの他方には、回路701に保持されたデータに対応する信号が入力される。図9では、回路701から出力された信号が、トランジスタ709のソースとドレインの他方に入力される例を示した。スイッチ703の第2の端子(トランジスタ713のソースとドレインの他方)から出力される信号は、論理素子706によってその論理値が反転された反転信号となり、回路720を介して回路701に入力される。

【0242】

なお、図9では、スイッチ703の第2の端子(トランジスタ713のソースとドレインの他方)から出力される信号は、論理素子706および回路720を介して回路701に入力する例を示したがこれに限定されない。スイッチ703の第2の端子(トランジスタ713のソースとドレインの他方)から出力される信号が、論理値を反転させられることなく、回路701に入力されてもよい。例えば、回路701内に、入力端子から入力された信号の論理値が反転した信号が保持されるノードが存在する場合に、スイッチ703の第2の端子(トランジスタ713のソースとドレインの他方)から出力される信号を当該ノードに入力することができる。

【0243】

図9におけるトランジスタ709は、実施の形態1又は2で説明したトランジスタを用いることができる。第1ゲートには制御信号WEを入力し、第2ゲートには制御信号WE2を入力することができる。制御信号WE2は、一定の電位の信号とすればよい。当該一定の電位には、例えば、接地電位GNDやトランジスタ709のソース電位よりも小さい電位などが選ばれる。制御信号WE2は、トランジスタ709のしきい値電圧を制御するための電位信号であり、トランジスタ709のIcutをより低減することができる。

【0244】

また、図9において、記憶素子700に用いられるトランジスタのうち、トランジスタ709以外のトランジスタは、酸化物半導体以外の半導体でなる層または基板1190にチャネルが形成されるトランジスタとすることができる。例えば、シリコン層またはシリコン基板にチャネルが形成されるトランジスタとすることができる。また、記憶素子700に用いられるトランジスタ全てを、チャネルが酸化物半導体層で形成されるトランジスタとすることもできる。または、記憶素子700は、トランジスタ709以外にも、チャネルが酸化物半導体層で形成されるトランジスタを含んでいてもよく、残りのトランジスタは酸化物半導体以外の半導体でなる層または基板1190にチャネルが形成されるトランジスタとすることもできる。

【0245】

図9における回路701には、例えばフリップフロップ回路を用いることができる。また、論理素子706としては、例えばインバータやクロックドインバータ等を用いることができる。

【0246】

本発明の一態様の半導体装置では、記憶素子700に電源電圧が供給されない間は、回路701に記憶されていたデータを、回路702に設けられた容量素子708によって保持することができる。

【0247】

また、酸化物半導体層にチャネルが形成されるトランジスタはオフ電流が極めて小さい。例えば、酸化物半導体層にチャネルが形成されるトランジスタのオフ電流は、結晶性を有するシリコンにチャネルが形成されるトランジスタのオフ電流に比べて著しく低い。そのため、当該トランジスタをトランジスタ709として用いることによって、記憶素子700に電源電圧が供給されない間も容量素子708に保持された信号は長期間にわたり保たれる。こうして、記憶素子700は電源電圧の供給が停止した間も記憶内容(データ)を

10

20

30

40

50

保持することが可能である。

【0248】

また、スイッチ703およびスイッチ704を設けることによって、プリチャージ動作を行うことを特徴とする記憶素子であるため、電源電圧供給再開後に、回路701が元のデータを保持しなおすまでの時間を短くすることができる。

【0249】

また、回路702において、容量素子708によって保持された信号はトランジスタ710のゲートに入力される。そのため、記憶素子700への電源電圧の供給が再開された後、容量素子708によって保持された信号を、トランジスタ710の状態（オン状態、またはオフ状態）に変換して、回路702から読み出すことができる。それ故、容量素子708に保持された信号に対応する電位が多少変動していても、元の信号を正確に読み出すことが可能である。

【0250】

このような記憶素子700を、プロセッサが有するレジスタやキャッシュメモリなどの記憶装置に用いることで、電源電圧の供給停止による記憶装置内のデータの消失を防ぐことができる。また、電源電圧の供給を再開した後、短時間で電源供給停止前の状態に復帰することができる。よって、プロセッサ全体、もしくはプロセッサを構成する一つ、または複数の論理回路において、短い時間でも電源停止を行うため、消費電力を抑えることができる。

【0251】

本実施の形態では、記憶素子700をCPUに用いる例として説明したが、記憶素子700は、DSP (Digital Signal Processor)、カスタムLSI、PLD (Programmable Logic Device) 等のLSI、RF-ID (Radio Frequency Identification) にも応用可能である。

【0252】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【0253】

（実施の形態7）

本実施の形態では、実施の形態1又は2のいずれかで一例を示したトランジスタを用いた、対象物の情報を読み取るイメージセンサ機能を有する半導体装置について説明する。

【0254】

図10に、イメージセンサ機能を有する半導体装置の等価回路の一例を示す。

【0255】

フォトダイオード602は、一方の電極がフォトダイオードリセット信号線658に、他方の電極がトランジスタ640のゲートに電気的に接続されている。トランジスタ640は、ソース又はドレインの一方がフォトセンサ基準信号線672に、ソース又はドレインの他方がトランジスタ656のソース又はドレインの一方に電気的に接続されている。トランジスタ656は、ゲートがゲート信号線659に、ソース又はドレインの他方がフォトセンサ出力信号線671に電気的に接続されている。

【0256】

フォトダイオード602には、例えば、p型の導電型を有する半導体層と、高抵抗な（i型の導電型を有する）半導体層と、n型の導電型を有する半導体層を積層するpin型のフォトダイオードを適用することができる。

【0257】

フォトダイオード602に入射する光を検出することによって、被検出物の情報を読み取ることができる。なお、被検出物の情報を読み取る際に、バックライトなどの光源を用いることができる。

【0258】

10

20

30

40

50

なお、トランジスタ 640 及びトランジスタ 656 には、実施の形態 1 又は 2 のいずれかで一例を示した、酸化物半導体にチャネルが形成されるトランジスタを用いることができる。図 10 では、トランジスタ 640 及びトランジスタ 656 が、酸化物半導体を含むことを明確に判明できるよう、トランジスタの記号に「OS」と付記している。

【0259】

トランジスタ 640 及びトランジスタ 656 は、上記実施の形態で一例を示したトランジスタであり、チャネルが形成される酸化物半導体層を、過剰酸素を含有する酸化アルミニウム膜を含む絶縁層で包み込む構成を有する。また、酸化物半導体層をゲート電極層によって電気的に囲い込む構成を有することが好ましい。よって、トランジスタ 640 及びトランジスタ 656 は、電気特性変動が抑制された電気的に安定なトランジスタである。該トランジスタを含むことで、図 10 で示すイメージセンサ機能を有する半導体装置として信頼性の高い半導体装置を提供することができる。

10

【0260】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

【0261】

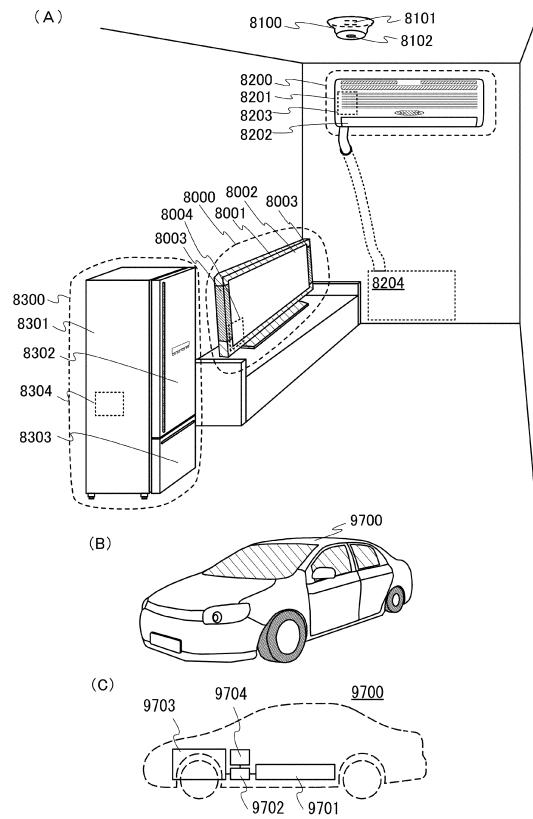

(実施の形態 8)

本実施の形態では、上記実施の形態で説明したトランジスタ、記憶装置、または CPU 等 (DSP、カスタムLSI、PLD、RF-ID を含む) を用いることのできる電子機器の例について説明する。

20

【0262】

上記実施の形態で説明したトランジスタ、記憶装置、または CPU 等は、さまざまな電子機器 (遊技機も含む) に適用することができる。電子機器としては、テレビ、モニタ等の表示装置、照明装置、パーソナルコンピュータ、ワードプロセッサ、画像再生装置、ポータブルオーディオプレーヤ、ラジオ、テープレコーダ、ステレオ、電話、コードレス電話、携帯電話、自動車電話、トランシーバ、無線機、ゲーム機、電卓、携帯情報端末、電子手帳、電子書籍、電子翻訳機、音声入力機器、ビデオカメラ、デジタルスチルカメラ、電気シェーバ、ICチップ、電子レンジ等の高周波加熱装置、電気炊飯器、電気洗濯機、電気掃除機、エアコンディショナーなどの空調設備、食器洗い機、食器乾燥機、衣類乾燥機、布団乾燥機、電気冷蔵庫、電気冷凍庫、電気冷凍冷蔵庫、DNA 保存用冷凍庫、放射線測定器、透析装置、X線診断装置等の医療機器、などが挙げられる。また、煙感知器、熱感知器、ガス警報装置、防犯警報装置などの警報装置も挙げられる。さらに、誘導灯、信号機、ベルトコンベア、エレベータ、エスカレータ、産業用ロボット、電力貯蔵システム等の産業機器も挙げられる。また、燃料を用いたエンジンや、非水系二次電池からの電力を用いて電動機により推進する移動体なども、電子機器の範疇に含まれるものとする。上記移動体として、例えば、電気自動車 (EV)、内燃機関と電動機を併せ持ったハイブリッド車 (HEV)、プラグインハイブリッド車 (PHEV)、これらのタイヤ車輪を無限軌道に変えた装軌車両、電動アシスト自転車を含む原動機付自転車、自動二輪車、電動車椅子、ゴルフ用カート、小型または大型船舶、潜水艦、ヘリコプター、航空機、ロケット、人工衛星、宇宙探査機や惑星探査機、宇宙船が挙げられる。これらの電子機器の一部の具体例を図 12 に示す。

30

【0263】

図 12 (A) に示すテレビジョン装置 8000 は、筐体 8001 に表示部 8002 が組み込まれており、表示部 8002 により映像を表示し、スピーカ部 8003 から音声を出力することが可能である。先の実施の形態で例示したトランジスタを筐体 8001 に組み込まれた表示部 8002 を動作するための駆動回路または画素に用いることが可能である。

40

【0264】

表示部 8002 は、液晶表示装置、有機EL素子などの発光素子を各画素に備えた発光装置、電気泳動表示装置、DMD (Digital Micromirror Device)、PDP (Plasma Display Panel) 等の半導体表示装置を用い

50

ることができる。

【0265】

テレビジョン装置8000は、受信機やモデムなどを備えていてもよい。テレビジョン装置8000は、受信機により一般的なテレビ放送の受信を行うことができ、さらにモデムを介して有線又は無線による通信ネットワークに接続することにより、一方向（送信者から受信者）又は双方向（送信者と受信者間、あるいは受信者間同士など）の情報通信を行うことも可能である。

【0266】

また、テレビジョン装置8000は、情報通信を行うためのCPU8004や、メモリを備えていてもよい。CPU8004やメモリに、先の実施の形態に示したトランジスタ、記憶装置、またはCPUを用いることによって省電力化を図ることができる。

10

【0267】

図12（A）に示す警報装置8100は、住宅用火災警報器であり、煙または熱の検出部8102と、マイクロコンピュータ8101を有している。マイクロコンピュータ8101は、先の実施の形態に示したトランジスタ、記憶装置、またはCPUを含む電気機器の一例である。

【0268】

また、図12（A）に示す室内機8200および室外機8204を有するエアコンディショナーは、先の実施の形態に示したトランジスタ、記憶装置、またはCPU等を含む電気機器の一例である。具体的に、室内機8200は、筐体8201、送風口8202、CPU8203等を有する。図12（A）においては、CPU8203が、室内機8200に設けられている場合を例示しているが、CPU8203は室外機8204に設けられてもよい。または、室内機8200と室外機8204の両方に、CPU8203が設けられてもよい。先の実施の形態に示したトランジスタをエアコンディショナーのCPUに用いることによって省電力化を図ることができる。

20

【0269】

また、図12（A）に示す電気冷凍冷蔵庫8300は、先の実施の形態に示したトランジスタ、記憶装置、またはCPU等を含む電気機器の一例である。具体的に、電気冷凍冷蔵庫8300は、筐体8301、冷蔵室用扉8302、冷凍室用扉8303、CPU8304等を有する。図12（A）では、CPU8304が、筐体8301の内部に設けられている。先の実施の形態に示したトランジスタを電気冷凍冷蔵庫8300のCPU8304に用いることによって省電力化が図れる。

30

【0270】

図12（B）、（C）には、電気機器の一例である電気自動車の例を示す。電気自動車9700には、二次電池9701が搭載されている。二次電池9701の電力は、回路9702により出力が調整されて、駆動装置9703に供給される。回路9702は、図示しないROM、RAM、CPU等を有する処理装置9704によって制御される。先の実施の形態に示したトランジスタを電気自動車9700のCPUに用いることによって省電力化が図れる。

40

【0271】

駆動装置9703は、直流電動機もしくは交流電動機単体、または電動機と内燃機関と、を組み合わせて構成される。処理装置9704は、電気自動車9700の運転者の操作情報（加速、減速、停止など）や走行時の情報（上り坂や下り坂等の情報、駆動輪にかかる負荷情報など）の入力情報に基づき、回路9702に制御信号を出力する。回路9702は、処理装置9704の制御信号により、二次電池9701から供給される電気エネルギーを調整して駆動装置9703の出力を制御する。交流電動機を搭載している場合は、図示していないが、直流を交流に変換するインバータも内蔵される。

【0272】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

50

## 【符号の説明】

## 【0273】

|       |                 |    |

|-------|-----------------|----|

| 200   | 基板              |    |

| 202   | ゲート電極層          |    |

| 205   | 絶縁層             |    |

| 205 a | 絶縁膜             |    |

| 206   | 絶縁層             |    |

| 207   | 酸化物層            |    |

| 208   | 酸化物半導体層         | 10 |

| 209   | 酸化物層            |    |

| 210 a | ソース電極層          |    |

| 210 b | ドレイン電極層         |    |

| 212   | 絶縁層             |    |

| 214   | 絶縁層             |    |

| 214 a | 絶縁膜             |    |

| 216   | ゲート電極層          |    |

| 250   | トランジスタ          |    |

| 260   | トランジスタ          |    |

| 270   | トランジスタ          |    |

| 280   | トランジスタ          | 20 |

| 602   | フォトダイオード        |    |

| 640   | トランジスタ          |    |

| 656   | トランジスタ          |    |

| 658   | フォトダイオードリセット信号線 |    |

| 659   | ゲート信号線          |    |

| 671   | フォトセンサ出力信号線     |    |

| 672   | フォトセンサ基準信号線     |    |

| 700   | 記憶素子            |    |

| 701   | 回路              |    |

| 702   | 回路              | 30 |

| 703   | スイッチ            |    |

| 704   | スイッチ            |    |

| 706   | 論理素子            |    |

| 707   | 容量素子            |    |

| 708   | 容量素子            |    |

| 709   | トランジスタ          |    |

| 710   | トランジスタ          |    |

| 713   | トランジスタ          |    |

| 714   | トランジスタ          |    |

| 720   | 回路              | 40 |

| 1189  | ROMインターフェース     |    |

| 1190  | 基板              |    |

| 1191  | ALU             |    |

| 1192  | ALUコントローラ       |    |

| 1193  | インストラクションデコーダ   |    |

| 1194  | インターフェースコントローラ  |    |

| 1195  | タイミングコントローラ     |    |

| 1196  | レジスタ            |    |

| 1197  | レジスタコントローラ      |    |

| 1198  | バスインターフェース      | 50 |

|         |            |    |

|---------|------------|----|

| 1 1 9 9 | R O M      |    |

| 2 2 0 0 | トランジスタ     |    |

| 3 0 0 1 | 配線         |    |

| 3 0 0 2 | 配線         |    |

| 3 0 0 3 | 配線         |    |

| 3 0 0 4 | 配線         |    |

| 3 0 0 5 | 配線         |    |

| 3 2 0 0 | トランジスタ     |    |

| 3 3 0 0 | トランジスタ     |    |

| 3 4 0 0 | 容量素子       | 10 |

| 8 0 0 0 | テレビジョン装置   |    |

| 8 0 0 1 | 筐体         |    |

| 8 0 0 2 | 表示部        |    |

| 8 0 0 3 | スピーカ部      |    |

| 8 0 0 4 | C P U      |    |

| 8 1 0 0 | 警報装置       |    |

| 8 1 0 1 | マイクロコンピュータ |    |

| 8 1 0 2 | 検出部        |    |

| 8 2 0 0 | 室内機        |    |

| 8 2 0 1 | 筐体         | 20 |

| 8 2 0 2 | 送風口        |    |

| 8 2 0 3 | C P U      |    |

| 8 2 0 4 | 室外機        |    |

| 8 3 0 0 | 電気冷凍冷蔵庫    |    |

| 8 3 0 1 | 筐体         |    |

| 8 3 0 2 | 冷蔵室用扉      |    |

| 8 3 0 3 | 冷凍室用扉      |    |

| 8 3 0 4 | C P U      |    |

| 9 7 0 0 | 電気自動車      |    |

| 9 7 0 1 | 二次電池       | 30 |

| 9 7 0 2 | 回路         |    |

| 9 7 0 3 | 駆動装置       |    |

| 9 7 0 4 | 処理装置       |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(56)参考文献 特開2013-021315(JP,A)

特開2012-134467(JP,A)

特開2013-038400(JP,A)

特開2012-033908(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/336

H01L 29/786