(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4748943号

(P4748943)

(45) 発行日 平成23年8月17日(2011.8.17)

(24) 登録日 平成23年5月27日(2011.5.27)

(51) Int.Cl.

F 1

|               |           |              |         |

|---------------|-----------|--------------|---------|

| HO 1 L 27/12  | (2006.01) | HO 1 L 27/12 | B       |

| HO 1 L 21/02  | (2006.01) | HO 1 L 29/78 | 6 2 7 D |

| HO 1 L 21/336 | (2006.01) |              |         |

| HO 1 L 29/786 | (2006.01) |              |         |

請求項の数 16 (全 54 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2004-56931 (P2004-56931)    |

| (22) 出願日     | 平成16年3月1日 (2004.3.1)          |

| (65) 公開番号    | 特開2004-282063 (P2004-282063A) |

| (43) 公開日     | 平成16年10月7日 (2004.10.7)        |

| 審査請求日        | 平成19年2月28日 (2007.2.28)        |

| (31) 優先権主張番号 | 特願2003-53243 (P2003-53243)    |

| (32) 優先日     | 平成15年2月28日 (2003.2.28)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

| (31) 優先権主張番号 | 特願2003-53193 (P2003-53193)    |

| (32) 優先日     | 平成15年2月28日 (2003.2.28)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 今井 駿太郎<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内  |

| (72) 発明者  | 高山 徹<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| (72) 発明者  | 後藤 裕吾<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 丸山 純矢<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項1】

第1の基板上に金属層を形成し、

前記金属層上的一部分に、前記金属層に含まれる金属と反応する材料を用いて接着体を形成し、

前記金属層および前記接着体を覆って酸化物層を形成し、

前記酸化物層上に薄膜トランジスタを含む素子形成層を形成し、

前記素子形成層の一部をエッチングすることにより前記接着体を除去し、

前記素子形成層上に第1の接着剤を介して第2の基板を貼付し、

前記第2の基板および前記素子形成層を前記第1の基板から物理的手段により剥離することを特徴とする半導体装置の作製方法。 10

## 【請求項2】

第1の基板上に金属層を形成し、

前記金属層上的一部分に、前記金属層に含まれる金属と反応する材料を用いて接着体を形成し、

前記金属層および前記接着体を覆って酸化物層を形成し、

前記酸化物層上に薄膜トランジスタを含む素子形成層を形成し、

前記素子形成層の一部をエッチングすることにより前記接着体を除去し、

前記素子形成層上に第1の接着剤を介して第2の基板を貼付し、

前記第2の基板および前記素子形成層を前記第1の基板から物理的手段により剥離し、 20

前記第2の基板および前記素子形成層を第2の接着剤を介して第3の基板上に貼付し、前記第2の基板を前記素子形成層から除去することを特徴とする半導体装置の作製方法。

【請求項3】

第1の基板上に金属層を形成し、

前記金属層上の一部に、前記金属層に含まれる金属と反応する材料を用いて接着体を形成し、

前記金属層および前記接着体を覆って酸化物層を形成し、

前記酸化物層上に薄膜トランジスタを含む素子形成層を形成し、

前記素子形成層の一部をエッチングすることにより前記接着体を除去し、

前記素子形成層上に第1の接着剤を介して第2の基板を貼付し、

前記第2の基板および前記素子形成層を前記第1の基板から物理的手段により剥離し、

前記第2の基板および前記素子形成層を第2の接着剤を介して第3の基板上に貼付し、

前記第2の基板を前記素子形成層から除去し、

前記素子形成層上に絶縁膜を形成することを特徴とする半導体装置の作製方法。

【請求項4】

第1の基板上に金属層を形成し、

前記金属層上の一部に、前記金属層に含まれる金属と反応する材料を用いて接着体を形成し、

前記金属層および前記接着体を覆って酸化物層を形成し、

前記酸化物層上に薄膜トランジスタを含む素子形成層を形成し、

前記素子形成層の一部および前記接着体をエッチングにより除去して開口部を形成し、

前記素子形成層上に設けられ、かつ前記開口部を埋める絶縁膜を形成し、

前記絶縁膜上に第1の接着剤を介して第2の基板を貼付し、

前記第2の基板および前記素子形成層を前記第1の基板から物理的手段により剥離することを特徴とする半導体装置の作製方法。

【請求項5】

第1の基板上に金属層を形成し、

前記金属層上の一部に、前記金属層に含まれる金属と反応する材料を用いて接着体を形成し、

前記金属層および前記接着体を覆って酸化物層を形成し、

前記酸化物層上に薄膜トランジスタを含む素子形成層を形成し、

前記素子形成層の一部および前記接着体をエッチングにより除去して開口部を形成し、

前記素子形成層上に設けられ、かつ前記開口部を埋める絶縁膜を形成し、

前記絶縁膜上に第1の接着剤を介して第2の基板を貼付し、

前記第2の基板および前記素子形成層を前記第1の基板から物理的手段により剥離し、

前記第2の基板および前記素子形成層を第2の接着剤を介して第3の基板上に貼付し、

前記第2の基板を前記素子形成層から除去することを特徴とする半導体装置の作製方法。

【請求項6】

第1の基板上に金属層を形成し、

前記金属層上の一部に、前記金属層に含まれる金属と反応する材料を用いて接着体を形成し、

前記金属層および前記接着体を覆って酸化物層を形成し、

前記酸化物層上に薄膜トランジスタを含む素子形成層を形成し、

前記素子形成層の一部および前記接着体をエッチングにより除去して開口部を形成し、

前記素子形成層上に設けられ、かつ前記開口部を埋める第1の絶縁膜を形成し、

前記第1の絶縁膜上に第1の接着剤を介して第2の基板を貼付し、

前記第2の基板および前記素子形成層を前記第1の基板から物理的手段により剥離し、

前記第2の基板および前記素子形成層を第2の接着剤を介して第3の基板上に貼付し、

10

20

30

40

50

前記第2の基板を前記素子形成層から除去し、

前記素子形成層上に第2の絶縁膜を形成することを特徴とする半導体装置の作製方法。

**【請求項7】**

請求項1乃至請求項3のいずれか一において、

前記素子形成層と前記第1の接着剤との間に、水溶性の有機樹脂からなる膜を形成し、

前記第2の基板および前記素子形成層を前記第1の基板から物理的手段により剥離した後、前記水溶性の有機樹脂を水洗することを特徴とする半導体装置の作製方法。

**【請求項8】**

請求項3において、

前記絶縁膜は窒化シリコン、酸化シリコン、アクリル、ポリイミド及びポリアミドのいずれか一を用いた単層構造または、組み合わせた積層構造であることを特徴とする半導体装置の作製方法。 10

**【請求項9】**

請求項2、請求項3、請求項5、請求項6および請求項8のいずれか一において、

前記第3の基板としてプラスチックを用いることを特徴とする半導体装置の作製方法。

**【請求項10】**

請求項1乃至請求項9のいずれか一において、

前記金属層として、タンゲステン、モリブデン、テクネチウム、レニウム、ルテニウム、オスミウム、ロジウム、イリジウム、パラジウム、白金、銀、または金のいずれか一を用いることを特徴とする半導体装置の作製方法。 20

**【請求項11】**

請求項1乃至請求項10のいずれか一において、

前記素子形成層は、その作製工程の一部に400以上熱処理工程を含むことを特徴とする半導体装置の作製方法。

**【請求項12】**

請求項1乃至請求項11のいずれか一において、

前記薄膜トランジスタは、前記接着体と重ならない位置に形成されることを特徴とする半導体装置の作製方法。

**【請求項13】**

請求項1乃至請求項12のいずれか一において、

前記接着体は、複数の薄膜トランジスタが整列している間に、長辺が剥離方向と平行となる長方形に配置されることを特徴とする半導体装置の作製方法。 30

**【請求項14】**

請求項1乃至請求項12のいずれか一において、

前記接着体は、複数の薄膜トランジスタが整列している間に、底辺が剥離方向と垂直となる三角形状に配置されることを特徴とする半導体装置の作製方法。

**【請求項15】**

請求項1乃至請求項12のいずれか一において、

前記接着体は、複数の薄膜トランジスタが整列している間に、ライン状に配置されることを特徴とする半導体装置の作製方法。 40

**【請求項16】**

請求項1乃至請求項15のいずれか一において、

前記接着体として珪素、ゲルマニウム、炭素、硼素、マグネシウム、アルミニウム、チタン、タンタル、鉄、コバルト、ニッケル、またはマンガンのいずれか一を用いることを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、基板上に形成された薄膜トランジスタ(TFT)等の半導体素子を別の基板上に転写させる工程を含む半導体装置の作製方法及びこの方法によって作成される半導体

装置に関する。

【0002】

また、本発明は、基板上に形成された複数の半導体素子（薄膜トランジスタ（TFT）を含む）で構成された集積回路を別の基板上に転写させる工程を含む半導体装置の作製方法及びこの方法によって作成される半導体装置に関する。

【背景技術】

【0003】

近年、同一基板上に形成された半導体薄膜（厚さ数～数百nm程度）を用いて形成された薄膜トランジスタ（TFT）に代表される半導体素子に関して、様々な技術開発が進められている。

10

【0004】

半導体素子の特性の確保においては、作製プロセス上ある程度の高温が要求される。現在、作製プロセスの一部にレーザー結晶化を導入することにより、工程温度の大幅な低下が実現され、この結果、高温プロセスには不可能とされていたガラス基板上への半導体素子の作製が可能となっている。

【0005】

しかしながら、例えばプラスチックなどの可撓性基板上に半導体素子を形成する場合には、より一層の低温化が必要となるため、基板の耐熱性の視点から極めて難しい。

【0006】

これに対し、ガラス基板上に半導体素子を形成した後、半導体素子をプラスチックなどの可撓性基板上に転写する方法は、基板に対する熱的阻害要因を本質的に除外できるため、有効な方法として示されるに至っている。

20

【0007】

基板上に形成された半導体素子と基板とを分離させる方法として、いくつかの方法が提案されており、1) ガラス基板上に半導体素子を形成した後、ガラス基板をエッティング法により溶解させて半導体素子を単離させた後、プラスチック基板上に貼り付ける方法（例えば、特許文献1参照）や、2) 基板上に形成された半導体素子を基板から引き剥がした後、プラスチック等の可撓性基板上に貼り付ける方法（例えば、特許文献2参照）が知られている。

【特許文献1】特開2002-184959号公報

30

【特許文献2】特開平10-125931号公報

【0008】

1) の方法の場合には、基板上に半導体素子形成後、基板と半導体素子とを確実に分離できる反面、工程時間が長くなることや、エッティング剤やガラス基板の材料コストが大きいといった問題がある。

【0009】

また、2) の方法の場合には、密着性および膜応力の制御が極めて重要となる。すなわち、密着性を下げ、膜応力を高めてやれば剥離しやすくなるが、半導体素子を作製する途中で剥離が生じるという問題がある。また、密着性を上げれば半導体素子の作製中に剥離が生じることはないが、半導体素子形成後に基板から引き剥がすのが困難になるという問題がある。

40

【発明の開示】

【発明が解決しようとする課題】

【0010】

本発明では、2) のように基板上に形成された半導体素子を含む素子形成層を基板から引き剥がした後、別の基板上に貼り付ける場合において、基板と素子形成層との密着性が制御可能な転写工程を含む半導体装置の作製方法を提供することを目的とする。

【課題を解決するための手段】

【0011】

そこで、上記課題を解決するために本発明では、素子形成層の作製時には、基板と半導

50

体素子との密着性を高める一方で、素子形成層を形成した後には、基板と素子形成層との密着性を低くすることを特徴とする。

【0012】

具体的には、基板（第1の基板ともいう）上に形成される半導体素子と基板との間に接着体を形成することにより、半導体素子の作製中に基板から半導体素子が剥離するのを防ぎ、半導体素子が形成された後、接着剤を除去することにより、基板からの半導体素子の剥離を容易にするというものである。

【0013】

なお、本発明における接着体とは、基板から半導体素子を剥離しやすくするために基板上に予め形成される金属層に対して、密着性の高い材料からなり、具体的には、金属層と接して形成されることにより金属層中の金属と反応して金属化合物（シリサイドを含む）や合金を形成することができる材料を用いることができる。

10

【0014】

また、金属層中の金属と接着体との反応は、意図的に熱処理を加えることもできるが、後の工程において素子形成層（TFTを含む）の作製における熱処理等により促進させることができる。

【0015】

基板上に金属層を設け、接着体を形成し、金属層と接着体を覆うように酸化物層を形成し、接着体により基板上の金属層と酸化物層との密着性を高める。さらに、酸化物層上に半導体素子を含む素子形成層を形成する。

20

【0016】

なお、素子形成層を形成した後の接着体の除去方法としては、エッチング法を用いることができ、それまで形成されている素子形成層の一部と共にエッチングにより除去することができる。エッチング法としては、ウェットエッチング法またはドライエッチング法を用いることができる。

【0017】

なお、エッチングにより素子形成層の一部に形成された開口部は、そのままにしても良いが、接着体を除去した後でエッチングにより除去された材料と同一の絶縁材料、若しくは別の絶縁材料を用いて埋めても良い。

【0018】

30

そして、物理的な力を加えることにより、基板と素子形成層とを分離させることができる。これは、予め基板上に形成される金属層と酸化物層が、酸化物層上に半導体素子を形成するプロセス等によってその積層界面に剥離が起こりやすくなっているのに対し、界面に接着体を形成して密着性を高めていたのであるが、接着体が除去されることにより、界面における密着性が再び低下してしまうためである。そして、剥離した素子形成層を別の基板に貼り付けることにより、素子形成層の転写が完成する。

【0019】

なお、本発明の構成は、第1の基板上に金属層を形成し、前記金属層上的一部分に接着体を形成し、前記金属層および前記接着体を覆って酸化物層を形成し、前記酸化物層上に半導体素子を形成し、前記接着体を除去することを特徴とする半導体装置の作製方法である。この場合、半導体素子の形成において400以上、好ましくは600以上の熱処理工程を含むことにより、前記金属層と前記接着体との密着性をより高めることができる。400以上の熱処理を加えることにより、前記金属層と前記接着体との界面を安定化させることができ、また、600以上の熱処理を加えることにより、前記金属層と前記接着体とを反応させることができる。

40

【0020】

なお、上記構成において、半導体素子（TFT等）は、素子形成層に含まれるものである。また、接着体の除去方法としては、素子形成層の一部をエッチングすることにより同時に除去するのが好ましい。

【0021】

50

なお、上記構成において、金属層と酸化物層との界面は、素子形成層を作製する工程において熱処理が加わることにより、界面における密着力が低下するが、金属層上に形成された接着体は、素子形成層を作製する工程において熱処理が加わることにより、金属層中に含まれる金属材料と反応するため密着力が高められる。これにより、基板から素子形成層が剥離することなく素子形成層を形成することができる。

#### 【0022】

また、素子形成層を形成した後、接着体を素子形成層の一部と共にエッチングして除去することにより、第1の基板と素子形成層との密着力を低下させることができる。

#### 【0023】

なお、上記構成において、接着体を除去した後、前記素子形成層上に第1の接着剤を介して第2の基板を貼付けることは、前記第1の基板から前記素子形成層を容易に剥離することができるため、より好ましい。

10

#### 【0024】

さらに、上記構成において前記第1の基板から剥離した前記第2の基板および前記素子形成層を第2の接着剤を介して第3の基板上に貼付けることにより、素子形成層が形成された第1の基板とは異なる第3の基板上に素子形成層を転写することができる。なお、転写した後、前記第2の基板を前記素子形成層から除去してもよい。

#### 【0025】

また、本発明では、2)のように基板上に形成された複数の半導体素子で構成された集積回路を含む素子形成層を基板から引き剥がした後、別の基板上に貼り付ける場合において、基板と素子形成層との密着性が制御可能な転写工程を含む半導体装置の作製方法を提供することを目的とする。

20

#### 【0026】

そこで、上記課題を解決するために本発明では、素子形成層の作製時には、基板と半導体素子との密着性を高める一方で、素子形成層を形成した後には、基板と素子形成層との密着性を低くすることを特徴とする。

#### 【0027】

具体的には、基板(第1の基板ともいう)上に形成される複数の半導体素子で構成された集積回路と基板との間に密着性の高い材料からなる接着体を形成することにより、集積回路の作製中に基板から半導体素子が剥離するのを防ぎ、集積回路が形成された後、接着剤を除去することにより、基板からの集積回路の剥離を容易にするというものである。なお、ここでいう集積回路には、CPU(Central Processing unit)、MPU(Micro Processor unit)、メモリー、マイコン、画像処理プロセッサ等の回路を含めることとする。

30

#### 【0028】

なお、本発明における接着体とは、基板から集積回路を剥離しやすくするために基板上に予め形成される金属層に対して、密着性の高い材料からなり、具体的には、金属層と接して形成されることにより金属層中の金属と反応して金属化合物(シリサイドを含む)や合金を形成することができる材料を用いることができる。

#### 【0029】

また、金属層中の金属と接着体との反応は、意図的に熱処理を加えることもできるが、後の工程において素子形成層(集積回路を含む)の作製における熱処理等により促進させることができる。

40

#### 【0030】

このようにして、接着体により基板上の金属層と酸化物層との密着性を高めた上で酸化物層上に複数の半導体素子で構成された集積回路を含む素子形成層を形成する。

#### 【0031】

なお、素子形成層を形成した後の接着体の除去方法としては、エッチング法を用いることができ、それまで形成されている素子形成層の一部と共にエッチングにより除去することができる。エッチング法としては、ウエットエッチング法またはドライエッチング法を用いることができる。

50

## 【0032】

なお、エッティングにより素子形成層の一部に形成された開口部は、そのままにしても良いが、接着体を除去した後でエッティングにより除去された材料と同一の絶縁材料、若しくは別の絶縁材料を用いて埋めても良い。

## 【0033】

そして、物理的な力を加えることにより、基板と素子形成層とを分離させることができる。これは、予め基板上に形成される金属層と酸化物層が、酸化物層上に集積回路（複数のTFT）を形成するプロセス等によってその積層界面に剥離が起こりやすくなっているのに対し、界面に接着体を形成して密着性を高めていたのであるが、接着体が除去されることにより、界面における密着性が再び低下してしまうためである。そして、剥離した素子形成層を別の基板に貼り付けることにより、素子形成層の転写が完成する。

10

## 【0034】

なお、本発明の構成は、第1の基板上に金属層を形成し、前記金属層上的一部分に接着体を形成し、前記金属層および前記接着体を覆って酸化物層を形成し、前記酸化物層上に複数の半導体素子で構成された集積回路を形成し、前記接着体を除去することを特徴とする半導体装置の作製方法である。この場合、半導体素子の形成において400以上、好ましくは600以上の熱処理工程を含むことにより、前記金属層と前記接着体との密着性をより高めることができる。400以上の熱処理を加えることにより、前記金属層と前記接着体との界面を安定化させることができ、また、600以上の熱処理を加えることにより、前記金属層と前記接着体とを反応させることができる。

20

## 【0035】

なお、上記構成において、複数の半導体素子（TFT等）で構成される集積回路は、素子形成層に含まれるものである。また、接着体の除去方法としては、素子形成層の一部をエッティングすることにより同時に除去するのが好ましい。

## 【0036】

なお、上記構成において、金属層と酸化物層との界面は、素子形成層の作製工程において熱処理が加わることにより、界面における密着力が低下するが、金属層上に形成された接着体は、素子形成層を作製する工程において熱処理が加わることにより、金属層中に含まれる金属材料と反応するため密着力が高められる。これにより、基板から素子形成層が剥離することなく素子形成層を形成することができる。

30

## 【0037】

また、素子形成層を形成した後、接着体を素子形成層の一部と共にエッティングして除去することにより、第1の基板と素子形成層との密着力を低下させることができる。

## 【0038】

なお、上記構成において、接着体を除去した後、前記素子形成層上に第1の接着剤を介して第2の基板を貼付けることは、前記第1の基板から前記素子形成層を容易に剥離することができるため、より好ましい。

## 【0039】

さらに、上記構成において前記第1の基板から剥離した前記第2の基板および前記素子形成層を第2の接着剤を介して第3の基板上に貼付けることにより、素子形成層が形成された第1の基板とは異なる第3の基板上に素子形成層を転写することができる。なお、転写した後、前記第2の基板を前記素子形成層から除去してもよい。

40

## 【0040】

また、本発明の要旨の一つは、基板上に接着層を有し、この接着層上に第1の絶縁膜を有し、この第1の絶縁膜は少なくとも接着層を介して基板と接着しており、第1の絶縁膜上に少なくとも1つの薄膜トランジスタを有し、この薄膜トランジスタを覆う第2の絶縁膜を有し、第1の絶縁膜及び第2の絶縁膜が除去され且つ接着層を曝す開口部を有し、この開口部を埋め、さらに第2の絶縁膜を覆う第3の絶縁膜を有することを特徴とする半導体装置である。

## 【0041】

50

また、本発明の要旨の一つは、基板上に接着層を有し、この接着層上に第1の絶縁膜を有し、この第1の絶縁膜は少なくとも接着層を介して基板と接着しており、第1の絶縁膜上に複数の薄膜トランジスタからなる集積回路を有し、この集積回路を覆う第2の絶縁膜を有し、第1の絶縁膜及び第2の絶縁膜が除去され且つ接着層を曝す開口部を有し、この開口部を埋め、さらに第2の絶縁膜を覆う第3の絶縁膜を有することを特徴とする半導体装置である。

【0042】

なお、上記構成において基板はプラスチックなどの可撓性基板を用いることができる。

【0043】

また、接着層は反応硬化型、熱硬化型、紫外線硬化型などの光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤等の接着剤を用いて形成することができる。 10

【0044】

さらに、絶縁膜は、酸化珪素、窒化珪素、酸化窒化珪素などの無機材料や、アクリル(感光性アクリルを含む)、ポリアクリル(感光性ポリアクリルを含む)、ポリイミド、ポリアミド、BCB(ベンゾシクロブテン)等の有機材料を用いることができる。

【発明の効果】

【0045】

本発明によれば、基板上に予め接着体を形成することにより、半導体素子( TFT 等)を含む素子形成層の作製時における基板との密着性を高めることができるために、作製途中における基板からの素子形成層の剥離を防ぐことができる。一方、素子形成層が形成された後、接着体を除去することができるので、基板と素子形成層との密着性を低下させることにより剥離を容易に行うことができる。すなわち、半導体装置の作製における基板と素子形成層との密着性を制御することができる。 20

【0046】

また、本発明によれば、基板上に予め接着体を形成することにより、集積回路を含む素子形成層の作製時における基板との密着性を高めることができるために、作製途中における基板からの素子形成層の剥離を防ぐことができる。一方、素子形成層を形成した後、接着体を除去することができるので、基板と素子形成層との密着性を低下させることにより基板からの剥離を容易に行うことができる。すなわち、半導体装置の作製における基板と素子形成層との密着性を制御することができる。 30

【発明を実施するための最良の形態】

【0047】

[実施の形態1]

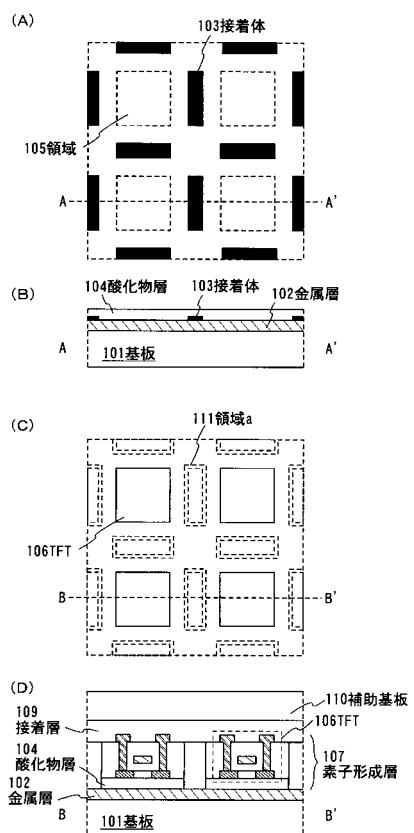

本発明の実施の形態について図1を用いて説明する。

【0048】

図1(A)には、本発明の接着体が形成される基板の上面図を示し、図1(B)には、図1(A)における破線AA'で切断した際の断面図を示す。すなわち、接着体103は、図1(B)に示すように基板101上に形成された金属層102上に接して島状に形成される。なお、ここで形成される接着体は、金属層102と次に形成される酸化物層104との間に形成され、金属層102と酸化物層104との密着性を高めることができる。 40

【0049】

基板101に用いる材料としては、石英基板やガラス基板等を用いることができるが、後の工程において基板上に形成された素子形成層(TFTを含む)を基板から剥離する際に、その強度等が不十分である場合には、複数の基板を貼り合わせて用いることもできる。

【0050】

なお、金属層102を形成する材料としては、タンゲステン(W)、モリブデン(Mo)、テクネチウム(Tc)、レニウム(Re)、ルテニウム(Ru)、オスミウム(Os)、ロジウム(Rh)、イリジウム(Ir)、パラジウム(Pd)、白金(Plt)、銀(Ag)、または金(Au)から選ばれた元素、前記元素を主成分とする合金、または窒化

10

20

30

40

50

物（例えば、窒化チタン、窒化タンゲステン、窒化タンタル、窒化モリブデン）を単層、または積層して用いることができる。

【0051】

また、金属層102の上に形成される接着体103は、酸化物層104の上に形成されるTFTの周囲に形成される。すなわち、図1(A)に示すように、接着体103が形成された後、点線で覆われた領域105にTFTが形成される。なお、接着体103の配置、及び形状については、図1(A)示すものに限られることはなく適宜設計することができる。

【0052】

なお、接着体103は、基板から素子形成層(TFTを含む)を剥離しやすくするために基板101上に形成される金属層102と密着性の高い材料からなり、具体的には、金属層102と接して形成されることにより金属層102中の金属と反応して金属化合物や合金を形成する材料、例えば、シリサイドを形成する珪素の他、ゲルマニウム、炭素、硼素、マグネシウム、アルミニウム、チタン、タンタル、鉄、コバルト、ニッケル、マンガン等の金属材料を用いることにより形成される。

【0053】

また、接着体103は、CVD(Chemical Vapor Deposition)法、スパッタリング法、蒸着法等の成膜法により成膜した後、これをパターンニングし、形成することができる。

【0054】

また、本発明における酸化物層には、酸化珪素、酸化窒化珪素( $\text{SiO}_x\text{N}_y$ )、窒化珪素等を用いることができ、スパッタリング法、CVD法等により成膜することができる。

【0055】

また、本発明において、酸化物層104上に半導体素子であるTFT106を形成した後、図1(C)及び図1(D)に示すように、接着体が除去される。なお、図1(C)には、TFT106が形成された基板の上面図を示し、図1(D)には、図1(C)における破線BB'で切断した際の断面図を示す。接着体103の除去方法としては、エッティング法(ドライエッティング法、ウエットエッティング法)を用いることができ、素子形成層107における層間絶縁膜および酸化物層104の一部と共に接着体103が除去される。すなわち、図1(C)の領域a(111)は、接着体103が除去された部分を示す。

【0056】

なお、接着体103を除去することにより、接着体103により高められていた基板101上の金属層102と酸化物層104との密着力は、低下する。

【0057】

次に、TFT106を含む素子形成層107の上に接着層(第1の接着層ともいう)109を介して補助基板(第2の基板ともいう)110を貼り付けた後、物理的な力を加えることにより、素子形成層107および補助基板110を基板101から分離させることができる。なお、この場合、基板101上の金属層102と酸化物層104との界面において剥離することができる。以下、接着剤によって形成される層を接着層とする。

【0058】

また、本発明では、上記接着体103を除去する際に形成された開口部を絶縁材料により埋めることもできる。なお、ここで用いる絶縁材料としては、有機絶縁材料であっても、無機絶縁材料であってもよい。具体的には、無機絶縁材料として、酸化珪素、窒化珪素、酸化窒化珪素などを用いることができ、有機絶縁材料として、アクリル(感光性アクリルを含む)、ポリアクリル(感光性ポリアクリルを含む)、ポリイミド、ポリアミド、BCB(ベンゾシクロブテン)等を用いることができる。

【0059】

また、接着層(第1の接着層)109には、後で補助基板(第2の基板)110を素子形成層107から剥離することのできる材料を用いることとする。例えば、紫外線を照射したり、加熱したりすることにより、接着力が低下するような接着材料を用いる。また、接着材料としては、両面テープ等を用いることもできる。さらに、補助基板(第2の基板

10

20

30

40

50

) 110を剥がした後、接着層(第1の接着層)109の残りを除去しやすくするため、素子形成層107と接着層(第1の接着層)109との間に水溶性の有機樹脂からなる膜を形成しておくこともできる。この場合、水洗して水溶性の有機樹脂からなる膜を除去することにより、同時に接着層(第1の接着層)109の残りを除去することができる。

【0060】

素子形成層107に補助基板110を貼り付けた後、基板101から素子形成層107を補助基板110と共に剥離する。このとき、基板101上の金属層102と、酸化物層104との間で剥離することができる。そして、剥離した素子形成層107を別の基板(第3の基板ともいう)、例えば、プラスチック等の可撓性基板上に接着層(第2の接着層ともいう)(ここでは図示しない)を用いて貼り付ける。

10

【0061】

なお、上記プラスチック等の可撓性基板としては、熱可塑性や熱硬化性の合成樹脂を用いることができる。例えば、ポリエチレン、ポリプロピレン、ポリスチレン、ポリアミド、ポリイミド、ポリアミドイミド、ポリカーボネート(PC)、アクリル系樹脂、ナイロン、ポリメチルメタクリレート、アクリル-スチレン共重合体(AS樹脂)、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルファン(PES)、ポリイミドポリエチレン、ポリプロピレン、フッ素系樹脂、スチレン系樹脂、ポリオレフィン系樹脂、メラミン樹脂、フェノール樹脂、ノルボルネン樹脂等を用いることができる。

【0062】

20

また、接着層(第2の接着層)には、反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤等の接着剤を用いることができるが、作業効率の点から紫外線硬化型接着剤が好ましい。

【0063】

30

最後に、補助基板110を除去することにより本発明の転写が完了する。具体的には、紫外線を照射したり、加熱したりすることにより、接着層(第1の接着層)109の接着力を低下させ、基板(第3の基板)に貼り付けられた素子形成層107から補助基板110を剥離する。さらに、素子形成層107と接着層(第1の接着層)109との間に水溶性の有機樹脂からなる膜が形成されている場合には、水洗することにより水溶性の有機樹脂からなる膜、および接着層(第1の接着層)109の残りを除去することができる。

【0064】

[実施の形態2]

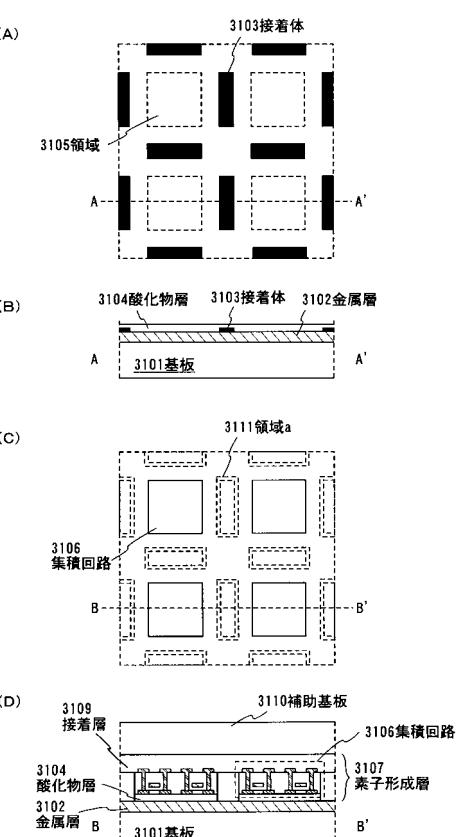

本発明の実施の形態について図14を用いて説明する。

【0065】

図14(A)には、本発明の接着体が形成される基板の上面図を示し、図14(B)には、図14(A)における破線AA'で切断した際の断面図を示す。すなわち、接着体3103は、図14(B)に示すように基板3101上に形成された金属層3102上に接して島状に形成される。なお、ここで形成される接着体は、次に形成される酸化物層3104との間に形成され、金属層3102と酸化物層3104との密着性を高めることができる。

40

【0066】

基板3101に用いる材料としては、石英基板やガラス基板等を用いることができるが、後の工程において基板上に形成された素子形成層(複数の集積回路を含む)を基板から剥離する際に、その強度等が不十分である場合には、複数の基板を貼り合わせて用いることもできる。

【0067】

なお、金属層3102を形成する材料としては、タンゲステン(W)、モリブデン(Mo)、テクネチウム(Tc)、レニウム(Re)、ルテニウム(Ru)、オスミウム(Os)、ロジウム(Rh)、イリジウム(Ir)、パラジウム(Pd)、白金(Plt)、銀(Ag)、または金(Au)から選ばれた元素、前記元素を主成分とする合金、または窒

50

化物（例えば、窒化チタン、窒化タンゲステン、窒化タンタル、窒化モリブデン）を単層、または積層して用いることができる。

【0068】

また、金属層3102の上に形成される接着体3103は、酸化物層3104の上に形成される複数のTFTからなる集積回路の周囲に形成される。すなわち、図14(A)に示すように、接着体3103が形成された後、点線で覆われた領域3105に複数のTFTで構成される集積回路が形成される。なお、接着体3103の配置、及び形状については、図14(A)示すものに限られることはなく適宜設計することができる。

【0069】

なお、接着体3103は、基板から素子形成層（複数のTFTで構成された複数の集積回路を含む）を剥離しやすくするために基板3101上に形成される金属層3102と密着性の高い材料からなり、具体的には、金属層3102と接して形成されることにより金属層3102中の金属と反応して金属化合物や合金を形成する材料、例えば、シリサイドを形成する珪素の他、ゲルマニウム、炭素、硼素、マグネシウム、アルミニウム、チタン、タンタル、鉄、コバルト、ニッケル、マンガン等の金属材料を用いることにより形成される。

【0070】

また、接着体3103は、CVD(Chemical Vapor Deposition)法、スパッタリング法、蒸着法等の成膜法により成膜した後、これをパターンニングし、形成することができる。

【0071】

また、本発明における酸化物層には、酸化珪素、酸化窒化珪素( $\text{SiO}_x\text{N}_y$ )、窒化珪素等を用いることができ、スパッタリング法、CVD法等により成膜することができる。

【0072】

また、本発明において、酸化物層3104上に複数のTFTからなる複数の集積回路3106を形成した後、図14(C)及び図14(D)に示すように、接着体3103が除去される。なお、図14(C)には、集積回路3106が形成された基板の上面図を示し、図14(D)には、図14(C)における破線BB'で切断した際の断面図を示す。接着体3103の除去方法としては、エッティング法（ドライエッティング法、ウエットエッティング法）を用いることができ、素子形成層3107における層間絶縁膜および酸化物層3104の一部と共に接着体3103が除去される。すなわち、図14(C)の領域a(111)は、接着体3103が除去された部分を示す。

【0073】

なお、接着体3103を除去することにより、接着体3103により高められていた基板3101上の金属層3102と酸化物層3104との密着力は、低下する。

【0074】

次に、集積回路3106を含む素子形成層3107の上に接着層（第1の接着層ともいう）3109を介して補助基板（第2の基板ともいう）3110を貼り付けた後、物理的な力を加えることにより、素子形成層3107および補助基板3110を基板3101から分離させることができる。なお、この場合、基板3101上の金属層3102と酸化物層3104との界面において剥離することができる。

【0075】

また、本発明では、上記接着体3103を除去する際に形成された開口部を絶縁材料により埋めることもできる。なお、ここで用いる絶縁材料としては、有機絶縁材料であっても、無機絶縁材料であってもよい。具体的には、無機絶縁材料として、酸化珪素、窒化珪素、酸化窒化珪素などを用いることができ、有機絶縁材料として、アクリル（感光性アクリルを含む）、ポリアクリル（感光性ポリアクリルを含む）、ポリイミド、ポリアミド、BCB（ベンゾシクロブテン）等を用いることができる。

【0076】

また、接着層（第1の接着層）3109には、後で補助基板（第2の基板）3110を

10

20

30

40

50

素子形成層 3107 から剥離することのできる材料を用いることとする。例えば、紫外線を照射したり、加熱したりすることにより、接着力が低下するような接着材料を用いる。また、接着材料としては、両面テープ等を用いることもできる。さらに、補助基板（第2の基板）3110 を剥がした後、接着層（第1の接着層）3109 の残りを除去しやすくなるため、素子形成層 3107 と接着層（第1の接着層）3109との間に水溶性の有機樹脂からなる膜を形成しておくこともできる。この場合、水洗して水溶性の有機樹脂からなる膜を除去することにより、同時に接着層（第1の接着層）3109 の残りを除去することができる。

【0077】

素子形成層 3107 に補助基板 3110 を貼り付けた後、基板 3101 から素子形成層 3107 を補助基板 3110 と共に剥離する。このとき、基板 3101 上の金属層 3102 と、酸化物層 3104 との間で剥離することができる。そして、剥離した素子形成層 3107 を別の基板（第3の基板ともいう）、例えば、プラスチック等の可撓性基板上に接着層（第2の接着層ともいう）（ここでは図示しない）を用いて貼り付ける。

10

【0078】

なお、上記プラスチック等の可撓性基板としては、熱可塑性や熱硬化性の合成樹脂を用いることができる。例えば、ポリエチレン、ポリプロピレン、ポリスチレン、ポリアミド、ポリイミド、ポリアミドイミド、ポリカーボネート（P C）、アクリル系樹脂、ナイロン、ポリメチルメタクリレート、アクリル-スチレン共重合体（A S樹脂）、ポリエチレンテレフタレート（P E T）、ポリエチレンナフタレート（P E N）、ポリエーテルサルファン（P E S）、ポリイミドポリエチレン、ポリプロピレン、フッ素系樹脂、スチレン系樹脂、ポリオレフィン系樹脂、メラミン樹脂、フェノール樹脂、ノルボルネン樹脂等を用いることができる。

20

【0079】

また、接着層（第2の接着層）には、反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤等の接着剤を用いることができるが、作業効率の点から紫外線硬化型接着剤が好ましい。

【0080】

最後に、補助基板 3110 を除去することにより本発明の転写が完了する。具体的には、紫外線を照射したり、加熱したりすることにより、接着層（第1の接着層）3109 の接着力を低下させ、基板（第3の基板）に貼り付けられた素子形成層 3107 から補助基板 3110 を剥離する。さらに、素子形成層 3107 と接着層（第1の接着層）3109との間に水溶性の有機樹脂からなる膜が形成されている場合には、水洗することにより水溶性の有機樹脂からなる膜、および接着層（第1の接着層）3109 の残りを除去することができる。

30

【0081】

以下に、本発明の実施例について説明する。

【実施例1】

【0082】

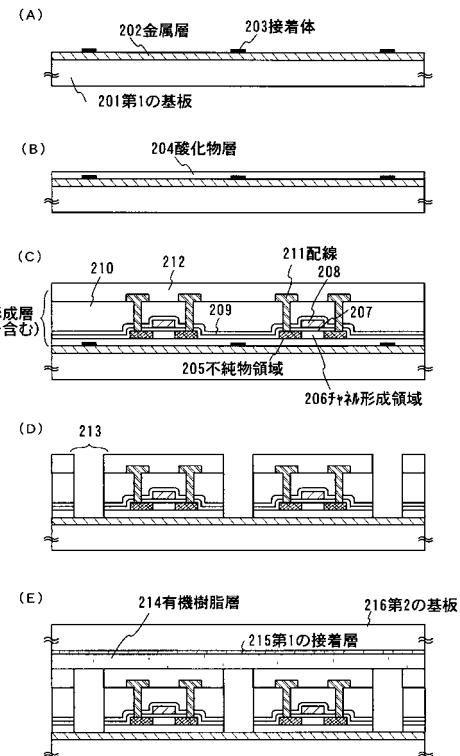

本実施例では、本発明の転写工程を含む作製方法について図2、図3を用いて説明する。

40

【0083】

図2（A）において、第1の基板 201 上に金属層 202 が積層され、その上に複数の接着体 203 が形成される。

【0084】

なお、本実施例において、第1の基板 201 としては、ガラス基板、石英基板を用いることができる。なお、ガラス基板としては、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス、アルミノシリケートガラスなどを素材とするガラス基板を用いることができ、代表的には、コーニング社製の 1737 ガラス基板（歪み点 667）、旭硝子社製の AN100（歪み点 670）などが適用可能である。本実施例では、AN100 を用い

50

ることとする。

【0085】

また、金属層202には、タングステン(W)、モリブデン(Mo)、テクネチウム(Tc)、レニウム(Re)、ルテニウム(Ru)、オスミウム(Os)、ロジウム(Rh)、イリジウム(Ir)、パラジウム(Pd)、白金(Pt)、銀(Ag)、または金(Au)から選ばれた元素、前記元素を主成分とする合金、または窒化物(例えば、窒化チタン、窒化タングステン、窒化タンタル、窒化モリブデン)を単層、または積層して用いることができるが、本実施例では、W(タングステン)を主成分とする金属層202を用いることとする。なお、金属層202の膜厚は10nm~200nm、好ましくは50nm~75nmとすればよい。

10

【0086】

金属層202は、スパッタリング法、CVD法、蒸着法により形成することができるが、本実施例では、スパッタリング法により成膜することとする。また、スパッタリング法により金属層202を形成する場合には、第1の基板201を固定するため、第1の基板201の周縁部付近における膜厚が不均一になりやすい。そのため、ドライエッチングによって周縁部のみを除去することが好ましい。

【0087】

金属層202の上に形成される接着体203は、非晶質シリコン膜を成膜した後、これをパターニングすることにより形成される。

【0088】

次に、酸化物層204を形成する(図2(B))。本実施例では酸化シリコンからなる膜を酸化シリコンターゲットを用いたスパッタリング法により、膜厚150nm~200nmで形成する。なお、酸化物層204の膜厚は、金属層202の膜厚の2倍以上することが望ましい。

20

【0089】

次に、酸化物層204上に素子形成層301が形成される(図2(C))。素子形成層301には、TFT(pチャネル型TFT、またはnチャネル型TFT)が複数形成され、これらのTFTを接続する配線211、絶縁膜(210、212)の他、これらのTFTと接続された素子(発光素子、液晶素子)が含まれるものとする。なお、TFTを含む素子形成層の作製方法は、本発明において特に限定されるものではなく、実施例5で示すような作製方法の他、公知の作製方法を組み合わせて用いることができる。なお、TFTは、酸化物層204上の半導体膜の一部に形成された不純物領域205およびチャネル形成領域206、絶縁膜207、およびゲート電極208により構成される。

30

【0090】

本実施例では、素子形成層301を形成する際に、少なくとも水素を含む材料膜(半導体膜または金属膜)を形成した後、水素を含む材料膜中に含まれる水素を拡散するための熱処理を行う。この熱処理は420以上であればよく、素子形成層301の形成プロセスとは別途行ってもよいし、兼用させて工程を省略してもよい。例えば、水素を含む材料膜として水素を含むアモルファスシリコン膜をCVD法により成膜した後、結晶化させるため500以上の熱処理を行えば、加熱によりポリシリコン膜が形成できると同時に水素の拡散を行うことができる。

40

【0091】

なお、この熱処理を行うことにより、金属層202と酸化物層204との間に結晶構造を有する金属酸化物からなる層(図示せず)が形成される。なお、金属層202上に接着体203を形成し、その上に酸化物層204を積層形成する際に、金属層202と酸化物層204との間に2nm~5nm程度形成されるアモルファス状態の金属酸化物層(本実施例では酸化タングステン膜)も、この熱処理により結晶構造を形成し、金属酸化物からなる層(図示せず)を形成する。

【0092】

なお、この金属酸化物からなる層(図示せず)が金属層202と酸化物層204との界

50

面に形成されることにより、後の工程での基板と素子形成層との剥離が容易になる。なお、本実施例では、素子形成層 301 を形成する途中の熱処理において、金属酸化物からなる層が形成される場合について説明したが、本発明はこの方法に限られることではなく、金属層 202 および接着体 203 を形成した後、金属酸化物層を形成し、酸化物層 204 を形成する方法で行うこともできる。

#### 【0093】

一方、素子形成層 301 を形成する途中の熱処理により、接着体 203 と金属層 202 との密着性を高めることができる。すなわち、本実施例において、非晶質シリコン膜で形成された接着体 203 は、熱処理を加えることにより、先に形成された金属層 202 中のタンゲステン (W) と反応して、シリサイド (タンゲステンシリサイド:  $W_{Si_2}$ ) を形成する。そのため、接着体 203 と金属層 202 との密着性が高められる。なお、本発明では、素子形成層 301 を形成する途中の熱処理により、金属層中の金属と接着体とを反応させる方法に限られることなく、金属層と接着体を形成した後、金属層中の金属と接着体とを反応させるための熱処理を素子形成層 301 の作製とは別に行うこともできる。

10

#### 【0094】

素子形成層 301 が完成したところで、接着体 203 を除去する。具体的には、ドライエッティング法により絶縁膜 (207、209、210、212) および酸化物層 204 の一部と接着体 203 とをエッティングし、開口部 213 を形成する (図 2 (D))。

#### 【0095】

例えば、絶縁膜 (207、209、210、212) および酸化物層 204 をエッティングする場合であって、これらが、酸化珪素で形成されている場合には、炭化フッ素 ( $CF_4$ ) を主成分とするエッティングガスを用いてドライエッティングを行い、また接着体 203 をエッティングする場合であって、接着体 203 が珪素で形成されており、金属層 (例えば W) との反応にも拘わらずその一部に珪素を主成分とする部分が残っている場合には、これを臭化水素 ( $HBr$ ) および塩素 ( $Cl_2$ ) を主成分とするエッティングガスを用いてエッティングすることができる。さらに、接着体 203 が珪素で形成されており、金属層 (W) との反応によってその一部がシリサイド ( $WSi$ ) を形成している場合には、これをフッ化硫黄 ( $SF_6$ ) と臭化水素 ( $HBr$ ) を主成分とするエッティングガスを用いてエッティングすることができる。

20

#### 【0096】

30

次に、素子形成層 301 上に有機樹脂層 214 を形成する。有機樹脂層 214 に用いる材料としては、水またはアルコール類に可溶な有機材料を用い、これを全面に塗布、硬化することにより形成する。この有機材料の組成としては、例えば、エポキシ系、アクリレート系、シリコン系等のいかなるものでもよい。具体的には、スピンコート法により水溶性樹脂 (東亜合成製: VL-WSHL10) (膜厚 30  $\mu m$ ) を塗布し、仮硬化するために 2 分間の露光を行ったあと、UV 光を裏面から 2.5 分、表面から 10 分、合計 12.5 分の露光を行って本硬化させることにより有機樹脂層 214 が形成される (図 2 (E))。

#### 【0097】

40

なお、後の剥離を行いやすくするために、金属層 202 と酸化物層 204 との界面 (金属酸化物を含む層) における密着性を部分的に低下させる処理を行う。密着性を部分的に低下させる処理は、剥離しようとする領域の周縁に沿って金属層 202 または酸化物層 204 にレーザー光を部分的に照射する処理、或いは、剥離しようとする領域の周縁に沿って外部から局所的に圧力を加えて酸化物層 204 の層内または界面の一部分に損傷を与える処理である。具体的にはダイヤモンドペンなどで硬い針を垂直に押しつけて荷重をかけて動かせばよい。好ましくは、スクライバー装置を用い、押し込み量を 0.1 mm ~ 2 mm とし、圧力をかけて動かせばよい。このように、剥離を行う前に剥離現象が生じやすくなるような部分、即ち、きっかけをつくることが重要であり、密着性を選択的 (部分的) に低下させる前処理を行うことで、剥離不良がなくなり、さらに歩留まりも向上する。

#### 【0098】

50

次に、第1の接着層215を形成することにより、有機樹脂層214上に第1の接着層215を介して補助基板である第2の基板216を貼り付けることができる（図2（E））。なお、第1の接着層215を形成する材料としては、後の工程において、所定の処理を行うことにより接着性が弱まる公知の材料を用いることができるが、本実施例では、後の工程において、光照射により接着力が低下する感光性の両面テープを用いる場合について説明する。

#### 【0099】

次に、第1の基板201を物理的手段により補助基板が貼り付けられた素子形成層301から引き剥がす。本実施例の場合には、金属層202と酸化物層204との界面（金属酸化物を含む層）部分において、比較的小さな力（例えば、人間の手、ノズルから吹付けられるガスの風圧、超音波等）で引き剥がすことができる。具体的には、酸化タンゲステン膜中、または酸化タンゲステン膜と酸化シリコン膜との界面、または酸化タンゲステン膜とタンゲステン膜との界面で分離させ、引き剥がすことができる。こうして、酸化物層204上に形成された素子形成層301を第1の基板201から分離することができる。剥離時の状態を図3（A）に示す。

10

#### 【0100】

また、剥離により露出した表面には、金属酸化物を含む層の一部が残っており、これは、後の工程において、露出面を基板等に接着する際に密着性を低下させる原因となることから、露出面に残っている金属酸化物を含む層の一部を除去する処理を行うことが好ましい。なお、これらを除去するためには、アンモニア水溶液などのアルカリ性の水溶液や酸性水溶液などを用いることができる。

20

#### 【0101】

次に、第2の接着層217を形成し、第2の接着層217を介して第3の基板218と酸化物層204（及び素子形成層301）とを接着する（図3（B））。なお、第1の接着層215により接着された第2の基板216と有機樹脂層214との密着性よりも、第2の接着層217により接着された酸化物層204（及び素子形成層301）と第3の基板218との密着性の方が高いことが重要である。

#### 【0102】

第3の基板218としては、可撓性基板（プラスチック基板）を用いることが好ましく、本実施例では、極性基のついたノルボルネン樹脂からなるARTON（JSR製）を用いることとする。

30

#### 【0103】

また、第2の接着層217に用いる材料としては、反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤が挙げられる。さらに好ましくは、銀、ニッケル、アルミニウム、窒化アルミニウムからなる粉末、またはフィラーを含ませることにより、高い熱伝導性を持たせることができること。

#### 【0104】

次に、第2の基板216側から紫外線を照射することにより、第1の接着層215に用いている両面テープの接着力を低下させ、素子形成層301から第2の基板216を分離させる（図3（C））。さらに、本実施例では、露出した表面を水洗することにより、第1の接着層215および有機樹脂層214を溶かして除去することができ、図3（D）に示す構造を得ることができる。

40

#### 【0105】

以上により、第1の基板201上に形成されたTFTを剥離し、別の基板（第3の基板218）上に転写することができる。

#### 【実施例2】

#### 【0106】

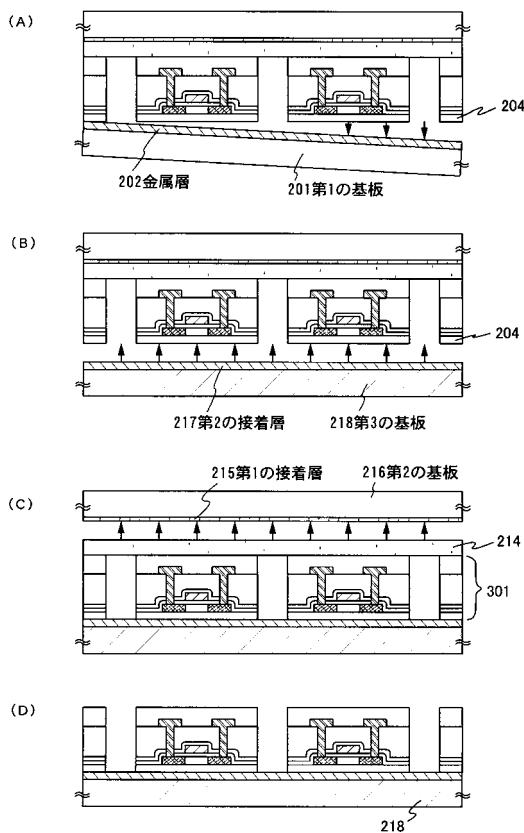

本実施例では、本発明の転写工程を含む作製方法であって、実施例1とはその一部が異なる場合について図4、図5を用いて説明する。

50

## 【0107】

図4(A)において、第1の基板401上に金属層402が積層され、その上に複数の接着体403が形成される。

## 【0108】

なお、本実施例において、第1の基板401としては、実施例1と同様のガラス基板(AN100)を用いることとする。また、金属層402についても実施例1と同様にW(タンゲステン)を主成分とする金属層を用いることとする。なお、金属層402は、スパッタリング法により成膜し、その膜厚は10nm~200nm、好ましくは50nm~75nmとすればよい。

## 【0109】

金属層402の上に形成される接着体403は、非晶質シリコン膜を成膜した後、これをパターニングすることにより形成される。

## 【0110】

次に、酸化物層404を形成する(図4(B))。本実施例では酸化シリコンからなる膜を酸化シリコンターゲットを用いたスパッタリング法により、膜厚150nm~200nmで形成する。なお、酸化物層404の膜厚は、金属層402の膜厚の2倍以上することが望ましい。

## 【0111】

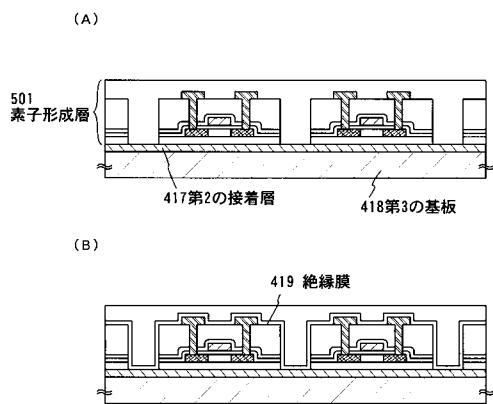

次に、酸化物層404上に素子形成層501が形成される(図4(C))。素子形成層501には、TFT(pチャネル型TFT、またはnチャネル型TFT)が複数形成され、これらのTFTを接続する配線411、絶縁膜410の他、これらのTFTと接続された素子(発光素子、液晶素子)が含まれるものとする。なお、TFTを含む素子形成層の作製方法は、本発明において特に限定されるものではなく、実施例5で示すような作製方法の他、公知の作製方法を組み合わせて用いることができる。なお、TFTは、酸化物層404上の半導体膜の一部に形成された不純物領域405およびチャネル形成領域406、絶縁膜407、およびゲート電極408により構成される。

## 【0112】

本実施例でも実施例1の場合と同様に素子形成層501を形成する際に、少なくとも水素を含む材料膜(半導体膜または金属膜)を形成した後、水素を含む材料膜中に含まれる水素を拡散するための熱処理を行う。なお、この熱処理を行うことにより、金属層402と酸化物層404との間に結晶構造を有する金属酸化物からなる層(図示せず)が形成される。

## 【0113】

なお、この金属酸化物からなる層(図示せず)が金属層402と酸化物層404との界面に形成されることにより、後の工程での基板と素子形成層との剥離が容易になる。

## 【0114】

一方、素子形成層501を形成する途中の熱処理により、接着体403と金属層402との密着性を高めることができる。

## 【0115】

本実施例では、素子形成層501に含まれる配線411まで形成したところで、接着体403を除去する。具体的には、ドライエッティング法により絶縁膜410の一部と接着体403とをエッティングし、開口部412を形成する(図4(D))。

## 【0116】

例えば、絶縁膜(407、409、410)および酸化物層404をエッティングする場合であって、これらが、酸化珪素で形成されている場合には、炭化フッ素(CF<sub>4</sub>)を主成分とするエッティングガスを用いてドライエッティングを行い、また接着体403をエッティングする場合であって、接着体403が珪素で形成されており、金属層(例えばW)との反応にも拘わらずその一部に珪素を主成分とする部分が残っている場合には、これを臭化水素(HBr)および塩素(Cl<sub>2</sub>)を主成分とするエッティングガスを用いてエッティングすることができる。さらに、接着体403が珪素で形成されており、金属層(W)との反

応によってその一部がシリサイド (WSi) を形成している場合には、これをフッ化硫黄 (SF<sub>6</sub>) と臭化水素 (HBr) を主成分とするエッティングガスを用いてエッティングすることができる。

【0117】

次に、開口部 412 を埋め、素子形成層 501 の表面を平坦化するために絶縁膜 413 を形成する (図 4 (E))。なお、本実施例では、プラズマ CVD 法により形成された膜厚 1 ~ 3 μm の窒化酸化シリコン膜を用いる。勿論、この絶縁膜は窒化酸化シリコン膜に限定されるものでなく、窒化シリコン、酸化シリコンといった絶縁材料や、アクリル、ポリイミド、ポリアミドなどの有機絶縁材料からなる単層構造や、これらを組み合わせた積層構造としても良い。

10

【0118】

なお、絶縁膜 413 により素子形成層 501 の表面を平坦化した後の工程である (1) 素子形成層 501 の上に有機樹脂層を形成し、その上に第 1 の接着層を介して補助基板である第 2 の基板を貼り付ける工程、(2) 素子形成層 501 から第 1 の基板 401 を物理的手段により補助基板 (第 2 の基板) が貼り付けられた素子形成層 501 から引き剥がす工程、(3) 第 2 の接着層を形成し、第 2 の接着層を介して第 3 の基板と酸化物層 (及び素子形成層) とを接着する工程、および (4) 素子形成層から第 2 の基板を分離させる工程、については実施例 1 に示すものと同様の材料を用いて、同様の方法により形成することができるので説明は省略することとする。

【0119】

20

以上により、素子形成層 501 が第 2 の接着層 417 を介して第 3 の基板 418 上に転写された図 5 (A) に示す構造を得ることができる。

【0120】

また、本実施例では、図 4 (D) において開口部 412 を形成した後、絶縁膜 419 を形成することにより、図 5 (B) に示す構造を形成しても良い。

【0121】

以上により、第 1 の基板 401 上に形成された TFT を剥離し、別の基板 (第 3 の基板 418) 上に転写することができる。

【実施例 3】

【0122】

30

本実施例では、本発明の転写工程を含む作製方法であって、実施例 1 や実施例 2 とはその一部が異なる場合について図 6、図 7 を用いて説明する。

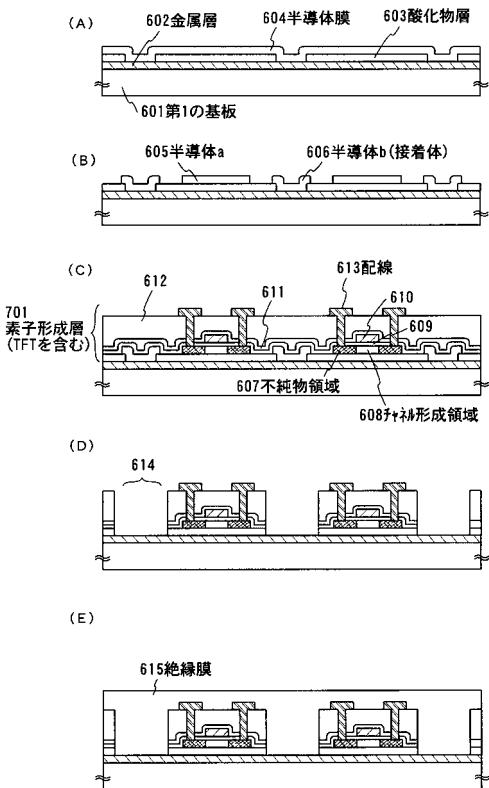

【0123】

図 6 (A) において、第 1 の基板 601 上に金属層 602 が積層され、その上に酸化物層 603 が形成される。

【0124】

なお、本実施例において、第 1 の基板 601 としては、実施例 1 と同様のガラス基板 (AN100) を用いることとする。また、金属層 602 についても実施例 1 と同様に W (タンゲステン) を主成分とする金属層 602 を用いることとする。なお、金属層 602 は、スパッタリング法により成膜し、その膜厚は 10 nm ~ 200 nm、好ましくは 50 nm ~ 75 nm とすればよい。

40

【0125】

金属層 602 の上に形成される酸化物層 603 は、酸化シリコンからなる膜を酸化シリコンターゲットを用いたスパッタリング法により、膜厚 150 nm ~ 200 nm で形成する。なお、酸化物層 603 の膜厚は、金属層 602 の膜厚の 2 倍以上とすることが望ましい。また、本実施例において、酸化物層 603 は、パターニングにより複数の島状に分離形成される。

【0126】

次に、酸化物層 603 を覆って、半導体膜 604 が形成される。本実施例では、非晶質シリコン膜をプラズマ CVD 法により成膜することにより形成される (図 6 (A))。そ

50

して、この半導体膜 604 をパターニングすることにより、酸化物層 603 上に形成される半導体 a (605)、分離形成された 2 つの酸化物層 603 の間に形成された半導体 b (606) が得られる。なお、ここで形成される半導体 a (605) は、後で形成される TFT の不純物領域およびチャネル形成領域となり、半導体 b (606) が、本発明における接着体となる。

【0127】

すなわち、本発明では、TFT の一部を形成する半導体 a (605) と、接着体を形成する半導体 b (606) が同時に形成される点に特徴がある。

【0128】

次に、半導体 a (605) を一部に含む素子形成層 701 が形成される（図 6 (C)）10。素子形成層 701 には、TFT (p チャネル型 TFT、または n チャネル型 TFT) が複数形成され、これらの TFT を接続する配線 613、絶縁膜 612 の他、これらの TFT と接続された素子（発光素子、液晶素子）が含まれるものとする。なお、TFT を含む素子形成層の作製方法は、本発明において特に限定されるものではなく、実施例 5 で示すような作製方法の他、公知の作製方法を組み合わせて用いることができる。なお、TFT は、酸化物層 603 上の半導体 a (605) の一部に形成された不純物領域 607 およびチャネル形成領域 608、ゲート絶縁膜 609、およびゲート電極 610 により構成される。

【0129】

本実施例でも実施例 1 の場合と同様に素子形成層 701 を形成する際に、少なくとも水素を含む材料膜（半導体膜または金属膜）を形成した後、水素を含む材料膜中に含まれる水素を拡散するための熱処理を行う。なお、この熱処理を行うことにより、金属層 602 と酸化物層 603 との間に結晶構造を有する金属酸化物からなる層（図示せず）が形成される。20

【0130】

なお、この金属酸化物からなる層（図示せず）が金属層 602 と酸化物層 603 との界面に形成されることにより、後の工程での第 1 の基板 601 と素子形成層 701 との剥離が容易になる。

【0131】

一方、素子形成層 701 を形成する途中の熱処理により、接着体である半導体 b (606) と金属層 602 との密着性を高めることができる。30

【0132】

本実施例では、素子形成層 701 に含まれる配線 613 まで形成したところで、半導体 b (606) を除去する（図 6 (D)）。具体的には、ドライエッチング法により絶縁膜 612 の一部と半導体 b (606) とをエッチングし、開口部 614 を形成する。

【0133】

例えば、絶縁膜 (609、611、612) および酸化物層 603 をエッチングする場合であって、これらが、酸化珪素で形成されている場合には、炭化フッ素 (CF<sub>4</sub>) を主成分とするエッチングガスを用いてドライエッチングを行い、また接着体である半導体 b (606) をエッチングする場合であって、半導体 b (606) が珪素で形成されており、金属層 (例えば W) との反応にも拘わらずその一部に珪素を主成分とする部分が残っている場合には、これを臭化水素 (HBr) および塩素 (Cl<sub>2</sub>) を主成分とするエッチングガスを用いてエッチングすることができる。さらに、半導体 b (606) が珪素で形成されており、金属層 (W) との反応によってその一部がシリサイド (WSi) を形成している場合には、これをフッ化硫黄 (SF<sub>6</sub>) と臭化水素 (HBr) を主成分とするエッチングガスを用いてエッチングすることができる。40

【0134】

次に、開口部 614 を埋め、素子形成層 701 の表面を平坦化するために絶縁膜 615 を形成する（図 6 (E)）。なお、本実施例では、プラズマ CVD 法により形成された膜厚 1 ~ 3 μm の窒化酸化シリコン膜を用いる。勿論、この絶縁膜は窒化酸化シリコン膜に50

限定されるものでなく、窒化シリコン、窒化シリコン、酸化シリコンといった絶縁材料や、アクリル、ポリイミド、ポリアミドなどの有機絶縁材料からなる単層構造や、これらを組み合わせた積層構造としても良い。

【0135】

なお、絶縁膜615により素子形成層701の表面を平坦化した後の工程である(1)素子形成層701の上に有機樹脂層を形成し、その上に第1の接着層を介して補助基板である第2の基板を貼り付ける工程、(2)素子形成層701から第1の基板601を物理的手段により補助基板(第2の基板)が貼り付けられた素子形成層701から引き剥がす工程、(3)第2の接着層を形成し、第2の接着層を介して第3の基板と酸化物層(及び素子形成層)とを接着する工程、および(4)素子形成層から第2の基板を分離させる工程、については実施例1に示すものと同様の材料を用いて、同様の方法により形成することができる。10

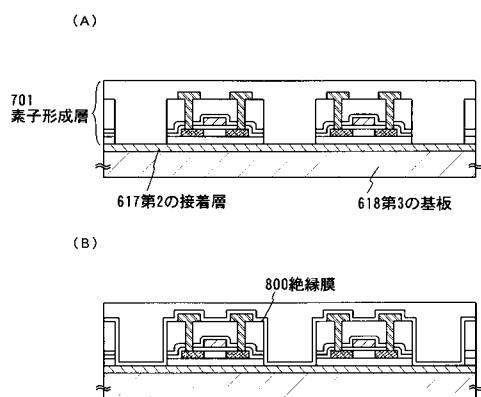

【0136】

以上により、素子形成層701が第2の接着層617を介して第3の基板618上に転写された図7(A)に示す構造を得ることができる。

【0137】

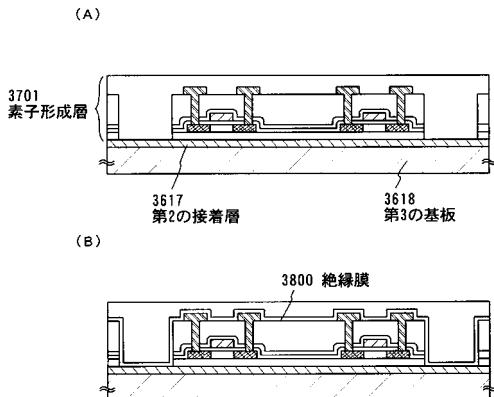

また、本実施例では、図6(D)において開口部614を形成した後、絶縁膜800を形成することにより、図7(B)に示す構造を形成しても良い。

【0138】

以上により、第1の基板601上に形成されたTFTを剥離し、別の基板(第3の基板618)上に転写することができる。20

【実施例4】

【0139】

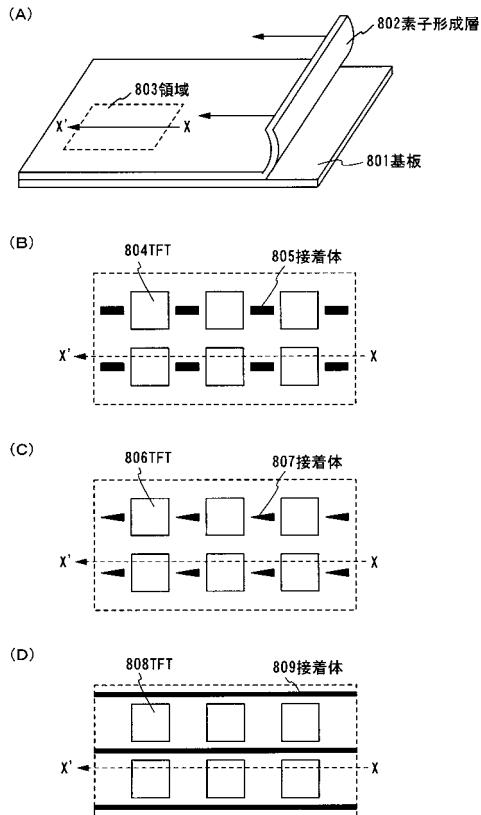

本実施例では、本発明における接着体の配置およびその形状について、図8を用いて説明する。

【0140】

本発明では、図8(A)に示すように基板801上に形成された素子形成層802が、物理的手段によって剥離され、別の基板上に貼付けられることにより、転写が行われる。なお、図8(A)の場合には、素子形成層802は、矢印の方向に剥離されるものとする。

【0141】

そこで、素子形成層802に形成される接着体の配置および形状について、素子形成層802の一部である領域803に素子形成層802の作製途中に形成され、剥離直前に除去される接着体の配置および形状の一例を図8(B)~図8(D)に示す。

【0142】

図8(B)では、TFT804が複数形成される領域803において、剥離方向XX'に配列されるTFT804の間に四角形状の接着体805が形成される場合について示す。なお、この場合、四角形状の接着体805が長方形を有し、剥離方向AA'に平行に長方形の長辺が並ぶように配置されるのがより好ましい。このように接着体805を四角形状とすることにより、接着体805を除去した後、素子形成層802を基板801から容易に剥離することができる。40

【0143】

図8(C)では、TFT806が複数形成される領域803において、剥離方向AA'に配列されるTFT806の間に三角形状の接着体807が形成される場合について示す。なお、この場合、三角形状の接着体807の底辺が、剥離方向XX'に垂直になるように配置されるのがより好ましい。このように接着体807を三角形状とした場合にも、接着体807を除去した後、素子形成層802を基板801から容易に剥離することができる。

【0144】

図8(D)では、TFT808が複数形成される領域803において、剥離方向XX'50

に複数配列される TFT 808 の列と列との間にライン状の接着体 809 が形成される場合について示す。なお、この場合、ライン状の接着体 809 は、剥離方向 XX' に複数の TFT 808 が配列されるのと同じ長さで形成しても良いが、TFT 808 1 つ分の長さで形成しても良い。このように接着体 809 をライン状とした場合にも、接着体 807 を除去した後、素子形成層 802 を基板 801 から容易に剥離することができる。

【0145】

なお、本実施例で示した接着体の配置および形状は、本発明における好ましい一例に過ぎず、本発明の接着体の形状を何ら限定するものではない。

【実施例 5】

【0146】

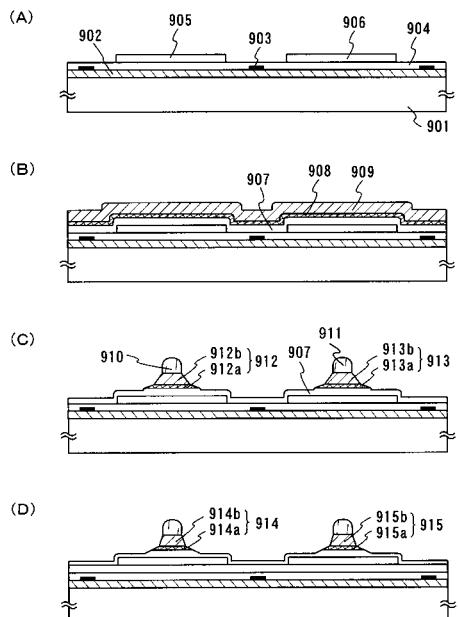

本実施例では、同一基板上に n チャネル型 TFT 及び p チャネル型 TFT を同時に作製する方法について、図 9、図 10 を用いて説明する。

【0147】

基板 901 上に金属層 902 が形成され、その上に接着体 903 が形成される。

【0148】

本実施例では、基板 901 として、ガラス基板 (#1737) を用い、金属層 902 には、実施例 1 と同様にタンゲステン (W) を主成分とする金属材料を用いる。なお、接着体 903 は、後で形成される TFT の間に配置されるように所望の形状にパターニングされ、形成される。

【0149】

次に金属層 902 および接着体 903 上に下地絶縁膜としても機能する酸化物層 904 を形成する。本実施例では、プラズマ CVD 法で成膜温度 300 、原料ガス SiH<sub>4</sub>、N<sub>2</sub>O から作製される酸化窒化シリコン膜 (組成比 Si = 32%、O = 59%、N = 7%、H = 2%) を 100 nm の厚さに成膜することにより、酸化物層 904 を形成する。

【0150】

さらに、大気開放せず連続的にプラズマ CVD 法で成膜温度 300 、成膜ガス SiH<sub>4</sub> で非晶質構造を有する半導体層 (ここでは非晶質シリコン層) を 54 nm の厚さで形成する。この非晶質シリコン層は水素を含んでおり、後の熱処理によって水素を拡散させ、物理的手段で酸化物層の層内、あるいは界面において剥離することができる。

【0151】

次に、重量換算で 10 ppm のニッケルを含む酢酸ニッケル塩溶液をスピナーで塗布する。塗布に代えてスパッタ法でニッケル元素を全面に散布する方法を用いてもよい。次いで、加熱処理を行い結晶化させて結晶構造を有する半導体膜 (ここではポリシリコン層) を形成する。ここでは脱水素化のための熱処理 (500 、 1 時間) の後、結晶化のための熱処理 (550 、 4 時間) を行って結晶構造を有するシリコン膜を得る。また、この脱水素化のための熱処理 (500 、 1 時間) は、非晶質シリコン膜に含まれる水素を金属層 902 と酸化物層 904 との界面に拡散する熱処理を兼ねている。なお、ここではシリコンの結晶化を助長する金属元素としてニッケルを用いた結晶化技術を用いるが、他の公知の結晶化技術、例えば固相成長法やレーザー結晶化法を用いてもよい。

【0152】

次に、結晶構造を有するシリコン膜表面の酸化膜を希フッ酸等で除去した後、結晶化率を高め、結晶粒内に残される欠陥を補修するためのレーザー光 (XeCl : 波長 308 nm) の照射を大気中、または酸素雰囲気中で行う。レーザー光には波長 400 nm 以下のエキシマレーザー光や、YAG レーザーの第 2 高調波、第 3 高調波を用いる。ここでは、繰り返し周波数 10 ~ 1000 Hz 程度のパルスレーザー光を用い、当該レーザー光を光学系にて 100 ~ 500 mJ / cm<sup>2</sup> に集光し、90 ~ 95% のオーバーラップ率をもつて照射し、シリコン膜表面を走査させればよい。ここでは、繰り返し周波数 30 Hz 、エネルギー密度 470 mJ / cm<sup>2</sup> でレーザー光の照射を大気中で行う。

【0153】

なお、大気中、または酸素雰囲気中で行うため、レーザー光の照射により表面に酸化膜

10

20

30

40

50

が形成される。なお、ここではパルスレーザーを用いる例を示したが、連続発振のレーザーを用いてもよく、非晶質半導体膜の結晶化に際し、大粒径に結晶を得るためには、連続発振が可能な固体レーザーを用い、基本波の第2高調波～第4高調波を適用するのが好ましい。代表的には、Nd:YVO<sub>4</sub>レーザー（基本波1064nm）の第2高調波（532nm）や第3高調波（355nm）を適用すればよい。連続発振のレーザーを用いる場合には、出力10Wの連続発振のYVO<sub>4</sub>レーザーから射出されたレーザー光を非線形光学素子により高調波に変換する。また、共振器の中にYVO<sub>4</sub>結晶と非線形光学素子を入れて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または橢円形状のレーザー光に成形して、被処理体に照射する。このときのエネルギー密度は0.01～100MW/cm<sup>2</sup>程度（好ましくは0.1～10MW/cm<sup>2</sup>）が必要である。そして、10～2000cm/s程度の速度でレーザー光に対して相対的に半導体膜を移動させて照射すればよい。10

#### 【0154】

次に、上記レーザー光の照射により形成された酸化膜に加え、オゾン水で表面を120秒処理して合計1～5nmの酸化膜からなるバリア層を形成する。本実施の形態ではオゾン水を用いてバリア層を形成するが、酸素雰囲気下の紫外線の照射で結晶構造を有する半導体膜の表面を酸化する方法や酸素プラズマ処理により結晶構造を有する半導体膜の表面を酸化する方法やプラズマCVD法やスパッタ法や蒸着法などで1～10nm程度の酸化膜を堆積してバリア層を形成してもよい。また、バリア層を形成する前にレーザー光の照射により形成された酸化膜を除去してもよい。20

#### 【0155】

次に、バリア層上にスパッタリング法にてゲッタリングサイトとなるアルゴン元素を含む非晶質シリコン膜を10nm～400nm、ここでは膜厚100nmで成膜する。本実施例では、アルゴン元素を含む非晶質シリコン膜は、シリコンターゲットを用いてアルゴンを含む雰囲気下で形成する。プラズマCVD法を用いてアルゴン元素を含む非晶質シリコン膜を形成する場合、成膜条件は、モノシランとアルゴンの流量比（SiH<sub>4</sub>:Ar）を1:99とし、成膜圧力を6.665Pa（0.05Torr）とし、RFパワー密度を0.087W/cm<sup>2</sup>とし、成膜温度を350とする。20

#### 【0156】

その後、650に加熱された炉に入れて3分の熱処理を行いゲッタリングして、結晶構造を有する半導体膜中のニッケル濃度を低減する。炉に代えてランプアニール装置を用いてもよい。30

#### 【0157】

次に、バリア層をエッチングストッパーとして、ゲッタリングサイトであるアルゴン元素を含む非晶質シリコン膜を選択的に除去した後、バリア層を希フッ酸で選択的に除去する。なお、ゲッタリングの際、ニッケルは酸素濃度の高い領域に移動しやすい傾向があるため、酸化膜からなるバリア層をゲッタリング後に除去することが望ましい。

#### 【0158】

次いで、得られた結晶構造を有するシリコン膜（ポリシリコン膜とも呼ばれる）の表面にオゾン水で薄い酸化膜を形成した後、レジストからなるマスクを形成し、所望の形状にエッチング処理して島状に分離された半導体層905、906を形成する。半導体層905、906を形成した後、レジストからなるマスクを除去する（図9（A））。

#### 【0159】

次に、フッ酸を含むエッチャントで酸化膜を除去すると同時にシリコン膜（半導体層905、906）の表面を洗浄した後、ゲート絶縁膜907となるシリコンを主成分とする絶縁膜を形成する。本実施例では、プラズマCVD法により115nmの厚さで酸化シリコン膜を形成する（図9（B））。

#### 【0160】

さらに、ゲート絶縁膜907上に膜厚20～100nmの第1の導電膜908と、膜厚100～400nmの第2の導電膜909とを積層形成する。本実施例では、ゲート絶縁50

膜907上に第1の導電膜908となる膜厚50nmの窒化タンタル膜、第2の導電膜909となる膜厚370nmのタンゲステン膜を順次積層する。

#### 【0161】

なお、第1の導電膜908及び第2の導電膜909を形成する導電性材料としてはTa、W、Ti、Mo、Al、Cuから選ばれた元素、または前記元素を主成分とする合金材料もしくは化合物材料を用いることができる。また、第1の導電膜908及び第2の導電膜909としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜や、AgPdCu合金を用いてもよい。また、2層構造に限定されず、例えば、膜厚50nmのタンゲステン膜、膜厚500nmのアルミニウムとシリコンの合金(Al-Si)膜、膜厚30nmの窒化チタン膜を順次積層した3層構造としてもよい。また、3層構造とする場合、第1の導電膜のタンゲステンに代えて窒化タンゲステンを用いてもよいし、第2の導電膜のアルミニウムとシリコンの合金(Al-Si)膜に代えてアルミニウムとチタンの合金膜(Al-Ti)を用いてもよいし、第3の導電膜の窒化チタン膜に代えてチタン膜を用いてもよい。また、単層構造であってもよい。

#### 【0162】

次に、図9(C)に示すように光露光工程によりレジストからなるマスク910、911を形成し、ゲート電極及び配線を形成するための第1のエッチング処理を行う。第1のエッチング処理では第1及び第2のエッチング条件で行う。エッチングにはICP(Inductively Coupled Plasma: 誘導結合型プラズマ)エッチング法を用いると良い。ICPエッチング法を用い、エッチング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等)を適宜調節することによって所望のテーパー形状に膜をエッチングすることができる。なお、エッチング用ガスとしては、Cl<sub>2</sub>、BCl<sub>3</sub>、SiCl<sub>4</sub>、CCl<sub>4</sub>などを代表とする塩素系ガスまたはCF<sub>4</sub>、SF<sub>6</sub>、NF<sub>3</sub>などを代表とするフッ素系ガス、またはO<sub>2</sub>を適宜用いることができる。

#### 【0163】

本実施例では、基板側(試料ステージ)にも150WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。なお、基板側の電極面積サイズは、12.5cm×12.5cmであり、コイル型の電極面積サイズ(ここではコイルの設けられた石英円板)は、直径25cmの円板である。この第1のエッチング条件によりW膜をエッチングして第1の導電層の端部をテーパー形状とする。第1のエッチング条件でのWに対するエッチング速度は200.39nm/min、TaNに対するエッチング速度は80.32nm/minであり、TaNに対するWの選択比は約2.5である。また、この第1のエッチング条件によって、Wのテーパー角は、約26°となる。この後、レジストからなるマスク910、911を除去せずに第2のエッチング条件に変え、エッチング用ガスにCF<sub>4</sub>とCl<sub>2</sub>とを用い、それぞれのガス流量比を30/30(ccm)とし、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約30秒程度のエッチングを行った。基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。CF<sub>4</sub>とCl<sub>2</sub>を混合した第2のエッチング条件ではW膜及びTaN膜とも同程度にエッチングされる。第2のエッチング条件でのWに対するエッチング速度は58.97nm/min、TaNに対するエッチング速度は66.43nm/minである。なお、ゲート絶縁膜上に残渣を残すことなくエッチングするためには、10~20%程度の割合でエッチング時間を増加させると良い。

#### 【0164】

上記第1のエッチング処理では、レジストからなるマスクの形状を適したものとすることにより、基板側に印加するバイアス電圧の効果により第1の導電層及び第2の導電層の端部がテーパー形状となる。このテーパー部の角度は15~45°とすればよい。

#### 【0165】

こうして、第1のエッチング処理により第1の導電層と第2の導電層からなる第1の形状の導電層912、913(第1の導電層912a、913aと第2の導電層912b、

10

20

30

40

50

913b)を形成する。ゲート絶縁膜となる絶縁膜907は、10~20nm程度エッチングされ、第1の形状の導電層912、913で覆われない領域が薄くなつたゲート絶縁膜907となる。

#### 【0166】

次に、図9(D)に示すように、レジストからなるマスクを除去せずに第2のエッティング処理により第2の形状の導電層914、915を形成する。ここでは、エッティング用ガスにSF<sub>6</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、それぞれのガス流量比を24/12/24(ccm)とし、1.3Paの圧力でコイル型の電極に700WのRF(13.56MHz)電力を投入してプラズマを生成してエッティングを25秒行う。基板側(試料ステージ)にも10WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。第2のエッティング処理でのWに対するエッティング速度は227.3nm/min、TaNに対するエッティング速度は32.1nm/minであり、TaNに対するWの選択比は7.1であり、ゲート絶縁膜911であるSiONに対するエッティング速度は33.7nm/minであり、SiONに対するWの選択比は6.83である。このようにエッティングガス用ガスにSF<sub>6</sub>を用いた場合、ゲート絶縁膜911との選択比が高いので膜減りを抑えることができる。本実施例におけるゲート絶縁膜907の膜減りは8nm程度である。

#### 【0167】

この第2のエッティング処理によりWのテーパー角を70°とすることができる。この第2のエッティング処理により第2の導電層914b、915bを形成する。このとき、第1の導電層は、ほとんどエッティングされず、第1の導電層914a、915aとなる。なお、第1の導電層914a、915aは、第1の導電層912a、913aとほぼ同一サイズである。実際には、第1の導電層の幅は、第2のエッティング処理前に比べて約0.3μm程度、即ち線幅全体で0.6μm程度後退する場合もあるがほとんどサイズに変化がない。

#### 【0168】

また、2層構造に代えて、膜厚50nmのタンゲステン膜、膜厚500nmのアルミニウムとシリコンの合金(AL-Si)膜、膜厚30nmの窒化チタン膜を順次積層した3層構造とした場合、第1のエッティング処理における第1のエッティング条件としては、BCl<sub>3</sub>とCl<sub>2</sub>とO<sub>2</sub>とを原料ガスに用い、それぞれのガス流量比を65/10/5(ccm)とし、基板側(試料ステージ)に300WのRF(13.56MHz)電力を投入し、1.2Paの圧力でコイル型の電極に450WのRF(13.56MHz)電力を投入してプラズマを生成して117秒のエッティングを行えばよく、第1のエッティング処理における第2のエッティング条件としては、CF<sub>4</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、それぞれのガス流量比を25/25/10(ccm)とし、基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約30秒程度のエッティングを行えばよく、第2のエッティング処理としてはBCl<sub>3</sub>とCl<sub>2</sub>を用い、それぞれのガス流量比を20/60(ccm)とし、基板側(試料ステージ)には100WのRF(13.56MHz)電力を投入し、1.2Paの圧力でコイル型の電極に600WのRF(13.56MHz)電力を投入してプラズマを生成してエッティングを行えばよい。

#### 【0169】

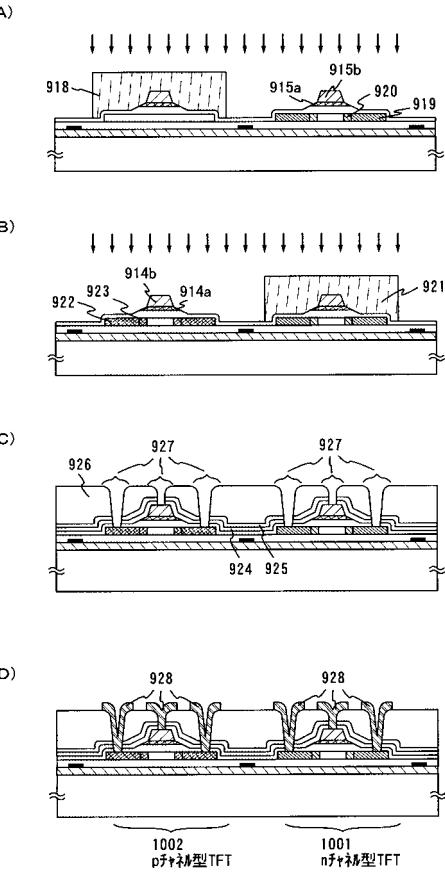

次に、レジストからなるマスク910、911を除去した後、図10(A)に示すようにレジストからなるマスク918を形成し第1のドーピング処理を行う。ドーピング処理はイオンドープ法、もしくはイオン注入法で行えば良い。なお、マスク918はpチャネル型TFTを形成する半導体膜及びその周辺の領域を保護するマスクである。

#### 【0170】

第1のドーピング処理におけるイオンドープ法の条件はドーズ量を $1.5 \times 10^{15}$ at<sub>oms/cm<sup>2</sup></sub>とし、加速電圧を60~100keVとしてリン(P)をドーピングする。なお、n型を付与する不純物元素として、典型的にはリン(P)または砒素(As)を

用いることができる。ここでは、第2の導電層914b、915bをマスクとして各半導体層に不純物領域が自己整合的に形成される。勿論、マスク918で覆われた領域には添加されない。こうして、第1の不純物領域919と、第2の不純物領域920が形成される。第1の不純物領域919には $1 \times 10^{20} \sim 1 \times 10^{21} / \text{cm}^3$ の濃度範囲でn型を付与する不純物元素が添加されている。ここでは、第1の不純物領域と同じ濃度範囲の領域をn<sup>+</sup>領域とも呼ぶ。

#### 【0171】

また、第2の不純物領域920は第1の導電層915aにより第1の不純物領域919よりも低濃度に形成され、 $1 \times 10^{18} \sim 1 \times 10^{19} / \text{cm}^3$ の濃度範囲でn型を付与する不純物元素が添加されることになる。なお、第2の不純物領域920は、テーパー形状である第1の導電層915aの部分を通過させてドーピングを行うため、テーパー部の端部に向かって不純物濃度が増加する濃度勾配を有している。ここでは、第2の不純物領域920と同じ濃度範囲の領域をn<sup>-</sup>領域とも呼ぶ。

#### 【0172】

次いで、レジストからなるマスク918を除去した後、新たにレジストからなるマスク921を形成して図10(B)に示すように第2のドーピング処理を行う。ドーピング処理はイオンドーピング、もしくはイオン注入法で行えばよい。なお、マスク921はnチャネル型TFTを形成する半導体膜及びその周辺の領域を保護するマスクである。

#### 【0173】

第2のドーピング処理におけるイオンドーピングの条件は、ドーズ量を $1 \times 10^{15} \sim 2 \times 10^{16} \text{ atoms/cm}^2$ とし、加速電圧を50～100keVとしてボロン(B)をドーピングする。ここでは、第2の導電層914b、915bをマスクとして、各半導体層に不純物領域が自己整合的に形成される。勿論、マスク921で覆われた領域にはボロンは添加されない。上記第2のドーピング処理により、pチャネル型TFTを形成する半導体層にp型の導電型を付与する不純物元素が添加された第3の不純物領域922及び第4の不純物領域923を形成する。

#### 【0174】

また、第3の不純物領域922には $1 \times 10^{20} \sim 1 \times 10^{21} / \text{cm}^3$ の濃度範囲でp型を付与する不純物元素が添加されるようにする。

#### 【0175】

また、第4の不純物領域923は第1の導電層914aのテーパー部と重なる領域に形成されるものであり、 $1 \times 10^{18} \sim 1 \times 10^{20} / \text{cm}^3$ の濃度範囲でp型を付与する不純物元素が添加されるようにする。なお、第4の不純物領域923は、テーパー形状である第1の導電層914aの部分を通過させてドーピングを行うため、テーパー部の端部に向かって不純物濃度が増加する濃度勾配を有する。ここでは、第4の不純物領域923と同じ濃度範囲の領域をp<sup>-</sup>領域とも呼ぶ。

#### 【0176】

以上の工程により、それぞれの半導体層にn型またはp型の導電型を有する不純物領域が形成される。第2の形状の導電層914、915はTFTのゲート電極となる。

#### 【0177】

次に、それぞれの半導体層に添加された不純物元素を活性化処理する工程を行う。この活性化工程は、ランプ光源を用いたラピッドサーマルアニール法(RTA法)、或いはYAGレーザーまたはエキシマレーザーを裏面から照射する方法、或いは炉を用いた熱処理、或いはこれらの方のうち、いずれかと組み合わせた方法によって行う。

#### 【0178】

次に、第1の絶縁膜924を形成する。なお、本実施例では、プラズマCVD法により形成された膜厚50nmの窒化酸化シリコン膜を用いる。勿論、この絶縁膜は窒化酸化シリコン膜に限定されるものでなく、窒化シリコン、酸化シリコンといった絶縁膜を単層または積層構造として用いても良い。

#### 【0179】

10

20

30

40

50

次に、第1の絶縁膜924上に第2の絶縁膜925を形成する。ここで形成される第2の絶縁膜925には、窒化シリコン、窒化酸化シリコン、酸化シリコンなどの絶縁膜を用いることができるが、本実施例では、プラズマCVD法により形成された膜厚50nmの窒化シリコン膜を用いることとする。

【0180】

次に、窒化シリコン膜からなる第2の絶縁膜925を形成した後、熱処理(300~550で1~12時間の熱処理)を行い、半導体層を水素化する工程を行う(図10(C))。この工程は第2の絶縁膜925に含まれる水素により半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、水素雰囲気下で350程度の熱処理や、プラズマ水素化(プラズマにより励起された水素を用いる)を行うこともできる。

10

【0181】

次に、第2の絶縁膜925上に有機絶縁物材料からなる第3の絶縁膜926を形成する。ここでは、膜厚1.6μmのアクリル樹脂膜を形成する。次に、各不純物領域に達するコンタクトホール927を形成する。

【0182】

なお、本実施例で用いるアクリル樹脂は感光性アクリルであるため、露光して現像することにより所望の位置を開孔することができる。また、第1の絶縁膜924および第2の絶縁膜925の一部のエッチングには、ドライエッチング法を用い、第1の絶縁膜924をエッチングストッパーとして第2の絶縁膜925のエッチングを行ってから、第1の絶縁膜924のエッチングを行う。これによりコンタクトホール927を得る。

20

【0183】

なお、本実施例では、有機樹脂膜で形成された第3の絶縁膜926を形成した後でコンタクトホールを形成する場合について説明したが、第3の絶縁膜926を形成する前に第2の絶縁膜925および第1の絶縁膜924をドライエッチングすることもできる。なお、この場合には、エッチング処理後、第3の絶縁膜926を形成する前に基板を熱処理(300~550で1~12時間の熱処理)するのが好ましい。

【0184】

そして、図10(D)に示すようにA1、Ti、Mo、W等を用いて配線928を形成することにより、nチャネル型TFT1001、pチャネル型TFT1002を同一基板上に形成することができる。

30

【実施例6】

【0185】

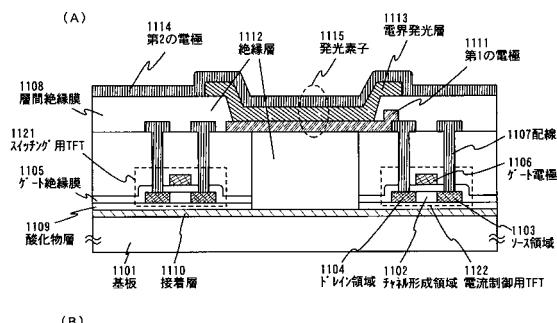

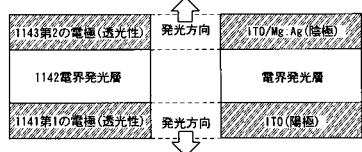

本実施例では、本発明により作製される半導体装置のうち、パネルの画素部に発光素子を有する発光装置の場合について、図11を用いて説明する。なお、図11(A)は、発光素子の断面構造について示すものであり、図11(B)(C)は、発光素子の素子構造について示したものである。なお、ここで示す発光素子は、電流制御用TFTと電気的に接続された第1の電極と、電界発光層を挟んで形成された第2の電極により形成される。

【0186】

図11(A)において、基板1101上に接着層1110および酸化物層1109が形成され、その上に薄膜トランジスタ(TFT)が形成されている。なお、ここでは、発光素子1115の第1の電極1111と電気的に接続され、発光素子1115に供給される電流を制御する機能を有する電流制御用TFT1122と、電流制御用TFT1122のゲート電極に印加されるビデオ信号を制御するためのスイッチング用TFT1121を示す。

40

【0187】

基板1101としては、遮光性を有するシリコン基板を用いるが、ガラス基板、石英基板、樹脂基板、フレキシブルな基板材料(プラスチック)を用いても良い。また、各TFTの活性層は、少なくともチャネル形成領域1102、ソース領域1103、ドレイン領域1104を備えている。

【0188】

50

また、各TFTの活性層は、ゲート絶縁膜1105で覆われ、ゲート絶縁膜1105を介してチャネル形成領域1102と重なるゲート電極1106が形成されている。また、ゲート電極1106を覆って層間絶縁膜1108が設けられている。なお、層間絶縁膜1108を形成する材料としては、酸化珪素、窒化珪素および窒化酸化珪素等の珪素を含む絶縁膜の他、ポリイミド、ポリアミド、アクリル(感光性アクリルを含む)、BCB(ベンゾシクロブテン)といった有機樹脂膜を用いることができる。

#### 【0189】

次に、層間絶縁膜1108に開口部を形成し、電流制御用TFT1122のソース領域1103と電気的に接続された配線1107を形成し、さらにドレイン領域1104と電気的に接続された第1の電極1111を形成する。なお、第1の電極1111が陽極である場合には、電流制御用TFT1122をpチャネル型で形成し、陰極である場合には電流制御用TFT1122をnチャネル型で形成するのが望ましい。

10

#### 【0190】

以上は、本発明の他の実施例を用いて形成することができるので、説明は省略する。なお、剥離・転写を行う過程で形成された開口部は、層間絶縁膜1112を形成することによって埋められる。さらに、エッチバックによって配線1107の頭出しを行った後に、第1の電極1111は配線1107に接続されるように形成される。第1の電極1111の端部、および配線1107等を覆って絶縁層1112が形成される。次に、第1の電極1111上に電界発光層1113が形成され、その上に、第2の電極1114を形成することにより発光素子1115を完成させることができる。

20

#### 【0191】

なお、本実施例において、第1の電極1111および第2の電極1114の材料を適宜選択することができるが、陽極として機能させる電極を形成する場合には、一般的に仕事関数の大きい導電性材料(例えば、仕事関数が4.0eV以上)を用いることが好ましく、陰極として機能させる電極を形成する場合には、一般的に仕事関数の小さい導電性材料(例えば、仕事関数が3.5eV以下)を用いることが好ましい。また、電界発光層において生じた光を透過させる電極を形成する場合には、透光性の材料を用いて電極を形成する必要がある。なお、この場合において、いずれか一方の電極のみを透光性の材料で形成し、他方を遮光性の材料で形成しても良いが、両方の電極材料を透光性の材料で形成することにより、両電極から光を出射させることのできる発光素子を形成することができる。

30

#### 【0192】

また、図11(A)に示す発光素子において、陽極となる電極から電界発光層1113に正孔が注入され、陰極となる電極から電界発光層1113に電子が注入される。そして、電界発光層1113において、正孔と電子が再結合することにより発光が得られる。

#### 【0193】

また、電界発光層1113は、少なくとも発光層を含み、正孔注入層、正孔輸送層、ブロッキング層、電子輸送層、および電子注入層といったキャリアに対する機能の異なる層のいずれか一つ、もしくは複数を組み合わせて積層することにより形成される。

#### 【0194】

また、電界発光層1113を形成する材料としては、低分子系、高分子系、もしく中分子系の公知の有機化合物を用いることができる。なお、ここでいう中分子系の有機化合物とは、昇華性を有さず、分子数が20以下、又は連鎖する分子の長さが10μm以下の材料のことをいう。

40

#### 【0195】

なお、電界発光層1113を形成する材料として、具体的には以下に示すような材料を用いることができる。

#### 【0196】

正孔注入層を形成する正孔注入材料としては、有機化合物であればポルフィリン系の化合物が有効であり、フタロシアニン(以下、H<sub>2</sub>-Pcと示す)、銅フタロシアニン(以下、Cu-Pcと示す)などがある。導電性高分子化合物に化学ドーピングを施した材料

50

もあり、ポリスチレンスルホン酸（以下、PSSと示す）をドープしたポリエチレンジオキシチオフェン（以下、PEDOTと示す）や、ポリアニリン、ポリビニルカルバゾール（以下、PVKと示す）などが挙げられる。

【0197】

正孔輸送層を形成する正孔輸送材料としては、芳香族アミン系（すなわち、ベンゼン環-窒素の結合を有するもの）の化合物が好適である。広く用いられている材料として、例えば、先に述べたTPDの他、その誘導体である4,4'-ビス[N-(1-ナフチル)-N-フェニル-アミノ]-ビフェニル（以下、「-NPD」と記す）や、4,4',4'''-トリス(N,N-ジフェニル-アミノ)-トリフェニルアミン（以下、「TDA」と記す）、4,4',4'''-トリス[N-(3-メチルフェニル)-N-フェニル-アミノ]-トリフェニルアミン（以下、「MTDATA」と記す）などのスターバースト型芳香族アミン化合物が挙げられる。

【0198】

発光層を形成する発光材料としては、具体的には、トリス(8-キノリノラト)アルミニウム（以下、Alq<sub>3</sub>と示す）、トリス(4-メチル-8-キノリノラト)アルミニウム（以下、Almq<sub>3</sub>と示す）、ビス(10-ヒドロキシベンゾ[h]-キノリナト)ベリリウム（以下、BeBq<sub>2</sub>と示す）、ビス(2-メチル-8-キノリノラト)-(4-ヒドロキシ-ビフェニル)-アルミニウム（以下、BA1qと示す）、ビス[2-(2-ヒドロキシフェニル)-ベンゾオキサゾラト]亜鉛（以下、Zn(BOX)<sub>2</sub>と示す）、ビス[2-(2-ヒドロキシフェニル)-ベンゾチアゾラト]亜鉛（以下、Zn(BTZ)<sub>2</sub>と示す）などの金属錯体の他、各種蛍光色素が有効である。また、三重項発光材料も可能であり、白金ないしはイリジウムを中心金属とする錯体が主体である。三重項発光材料としては、トリス(2-フェニルピリジン)イリジウム（以下、Ir(ppy)<sub>3</sub>と示す）、2,3,7,8,12,13,17,18-オクタエチル-21H,23H-ポルフィリン-白金（以下、PtOEPと示す）などが知られている。

【0199】

電子輸送層を形成する電子輸送材料としては、金属錯体がよく用いられ、先に述べたAlq<sub>3</sub>、Almq<sub>3</sub>、BeBq<sub>2</sub>などのキノリン骨格またはベンゾキノリン骨格を有する金属錯体や、混合配位子錯体であるBA1qなどが好適である。また、Zn(BOX)<sub>2</sub>、Zn(BTZ)<sub>2</sub>などのオキサゾール系、チアゾール系配位子を有する金属錯体もある。さらに、金属錯体以外にも、2-(4-ビフェニル)-5-(4-tert-ブチルフェニル)-1,3,4-オキサジアゾール（以下、PBDと示す）、1,3-ビス[5-(p-tert-ブチルフェニル)-1,3,4-オキサジアゾール-2-イル]ベンゼン（以下、OXD-7と示す）などのオキサジアゾール誘導体、3-(4-tert-ブチルフェニル)-4-フェニル-5-(4-ビフェニル)-1,2,4-トリアゾール（以下、TAZと示す）、3-(4-tert-ブチルフェニル)-4-(4-エチルフェニル)-5-(4-ビフェニル)-1,2,4-トリアゾール（以下、p-EtTAZと示す）などのトリアゾール誘導体、バソフェナントロリン（以下、BPhenと示す）、バソキュプロイン（以下、BCPと示す）などのフェナントロリン誘導体が電子輸送性を有する。

【0200】

その他、電界発光層にプロッキング層を含める場合には、プロッキング層を形成する正孔阻止材料として、上で述べたBA1q、OXD-7、TAZ、p-EtTAZ、BPhen、BCPなどが、励起エネルギーレベルが高いため有効である。

【0201】

図11(B)には、第1の電極1131が透光性の材料で形成された陽極であり、第2の電極1133が遮光性の材料で形成された陰極である場合の構成について示す。この場合には、第1の電極1131は、酸化インジウム・スズ(ITO)膜、酸化インジウムに2~20[%]の酸化亜鉛(ZnO)を混合した透明導電膜、IZO、およびIn<sub>2</sub>O<sub>3</sub>-ZnOといった透明導電膜を用いて形成することができ、第2の電極1133は、Al、Ti、W、等を用いて形成することができるが、ここでは、第1の電極1131にITOを

10

20

30

40

50

用い、第2の電極1133には、A1を用いた場合について示す。そして、電界発光層1132で生じた光は、第1の電極1131側から出射される。なお、この構成において、電界発光層1132を形成する材料は、先に示した材料を適宜選択して用いることができる。

【0202】

なお、本発明は上記構成に限られることではなく、第1の電極1131を遮光性の陽極で形成し、第2の電極1133を透光性の陰極となるように形成することもできる。この場合には、第2の電極1133側から光が出射される。

【0203】

図11(C)には、第1の電極1141および第2の電極1143の両方が、透光性の材料で形成されており、第1の電極1141が陽極で、第2の電極1143が陰極である場合の構成について示す。この場合には、第1の電極1141は、図11(B)で示した場合と同様に酸化インジウム・スズ(ITO)膜、酸化インジウムに2~20[%]の酸化亜鉛(ZnO)を混合した透明導電膜、IZO、およびIn<sub>2</sub>O<sub>3</sub>-ZnOといった透明導電膜を用いて形成することができ、第2の電極1143は、仕事関数の小さい材料であるMg:Ag(マグネシウムと銀の合金)とITOを積層することにより形成することができる。この場合には、電界発光層1142で生じた光は、第1の電極1141および第2の電極1143の両方側から出射される。なお、この構成においても、電界発光層1142を形成する材料は、先に示した材料を適宜選択して用いることができる。

【0204】

なお、本発明により作製される半導体装置において、パネルの画素部に発光素子を有する発光装置の構造はこの限りではない。例えば、図26に挙げるような構造をとることもできる。

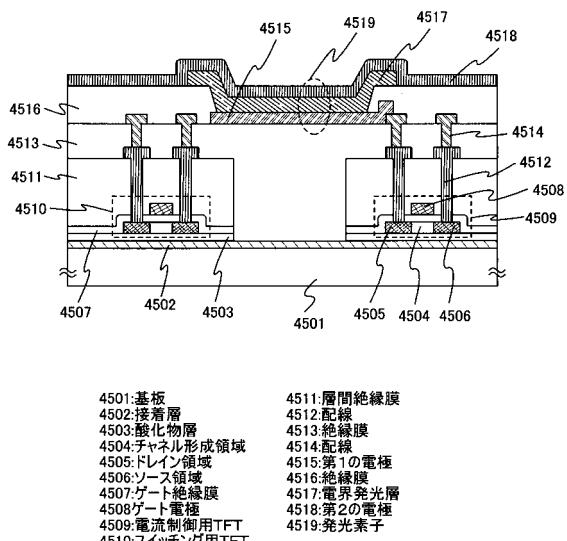

【0205】

まず、基板4501上に接着層4502および酸化物層4503が形成される。その上に、チャネル形成領域4504、ソース領域4505、ドレイン領域4506、ゲート絶縁膜4507及びゲート電極4508からなる電流制御用TFT4509、スイッチング用TFT4510が形成されている。各TFTの活性層は、ゲート絶縁膜4507で覆われ、ゲート絶縁膜4507を介してチャネル形成領域4504と重なるゲート電極4508が形成されている。また、ゲート電極4508を覆って層間絶縁膜4511が設けられている。

【0206】

電流制御用TFT4509は、発光素子4519の第1の電極4515と電気的に接続され、発光素子4515に供給される電流を制御する機能を有する。スイッチング用TFT4510は、電流制御用TFT4509のゲート電極に印加されるビデオ信号を制御する。

【0207】

基板4501は、ここでは遮光性を有するシリコン基板を用いているが、ガラス基板、石英基板、樹脂基板、フレキシブルな基板材料(プラスチック)を用いても良い。また、各TFTの活性層は、少なくともチャネル形成領域4504、ソース領域4505、ドレイン領域4506を備えている。

【0208】

次に、層間絶縁膜4511に開口部を形成し、電流制御用TFT4509のソース領域4505と電気的に接続された配線4512を形成する。さらに、絶縁膜4513を形成する。この絶縁膜4513にコンタクトホールを形成し、配線4512と電気的に接続された配線4514を形成する。その後、配線4514と電気的に接続された第1の電極4515を形成する。これによって電流制御用TFT4509のソース領域4505と第1の電極4515とが接続される。なお、第1の電極4515が陽極である場合には、電流制御用TFT4509をpチャネル型で形成し、陰極である場合には電流制御用TFT4509をpチャネル型で形成するのが望ましい。

【0209】

10

20

30

40

50

また、第1の電極4515の端部、および配線4514等を覆って絶縁層4516が形成される。次に、第1の電極4515上に電界発光層4517が形成され、その上に、第2の電極4518を形成することにより発光素子4519を完成させることができる。

#### 【0210】

なお、図26に挙げた半導体装置を製作する材料は、先に示した材料を適宜選択して用いることができる。

#### 【実施例7】

#### 【0211】

本実施例では、本発明により作製される半導体装置のうち、パネルの画素部に液晶素子を有する液晶装置の場合について、図12を用いて説明する。

10

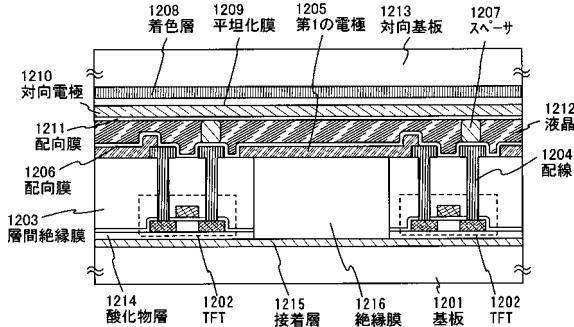

#### 【0212】

図12に示すように基板1201上には、接着層及び酸化物層1214が形成され、その上にTFT1202が形成される。層間絶縁膜1203に開口部が形成された後に、TFT1202は配線1204を介して、画素電極となる第1の電極1205と電気的に接続される。また、第1の電極1205上には配向膜1206が形成されており、ラビング処理がなされている。また、基板間隔を保持するための有機樹脂からなる柱状のスペーサ1207が設けられている。なお、スペーサ1207および配向膜1206の形成順序は逆でも良い。

#### 【0213】

以上は、本発明の他の実施例を用いて形成することができるので、説明は省略する。なお、剥離・転写を行う過程で形成された開口部は、絶縁膜1216を形成することによって埋められる。さらに、エッチバックによって配線1204の頭出しを行った後に、第1の電極1205は配線1204に接続されるように形成される。

20

#### 【0214】

一方、対向基板1213は、基板上に着色層1208、平坦化膜1209、透明性導電膜からなる対向電極1210および配向膜1211を有している。なお、着色層1208として、赤色の着色層、青色の着色層、および緑色の着色層がそれぞれ形成されていてもよい。

#### 【0215】

素子が形成された基板1201と対向基板1213とは、シール剤(図示せず)で貼り合わされている。なお、シール剤にはフィラーが混入されていて、このフィラーとスペーサによって均一な間隔(好ましくは2.0~3.0μm)を維持しつつ2枚の基板が貼り合わされている。また、両基板の間には液晶1212が注入されており、封止剤によって完全に封止されている。なお、液晶1212には公知の液晶材料を用いることができる。

30

#### 【0216】

なお、図12に示した構造とした場合、光は、対向基板1213側から入射し、液晶1212で変調されて、素子が形成された基板1201側から出射する。

#### 【0217】

本発明においては、第1の電極に反射性を有する金属膜(具体的には、アルミニウム(合金)膜等)を用いて形成することもできる。この場合には、光が対向基板1213側から入射し、液晶1212で変調された後、再び対向基板1213側から出射する。なお、このような構造とした場合には、第1の電極の下方に光が透過することができないため、メモリ素子や抵抗素子等を設けることもできる。

40

#### 【0218】

なお、本発明により作製される半導体装置において、パネルの画素部に液晶素子を有する液晶装置の構造はこの限りではなく、他の構成を用いることもできる。

#### 【実施例8】

#### 【0219】

本実施例では、本発明により作製された半導体素子をその一部に組み込むことにより完成する様々な電子機器について説明する。

50

## 【0220】

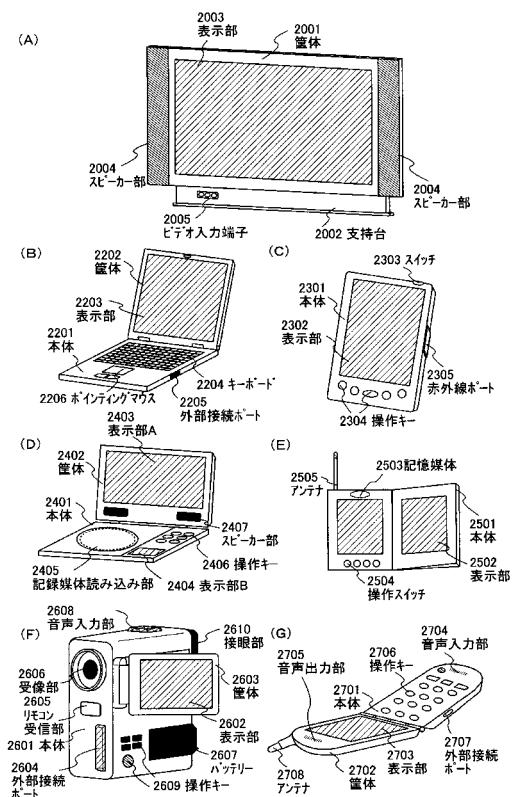

これらの電子機器としては、ビデオカメラ、デジタルカメラ、ヘッドマウントディスプレイ、（ゴーグル型ディスプレイ）、カーナビゲーション、プロジェクタ、カーステレオ、パーソナルコンピュータ、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等）等の記録媒体を再生し、その画像を表示しうる半導体装置を備えた装置）等が挙げられる。これら電子機器の具体例を図13に示す。

## 【0221】

図13（A）は表示装置であり、筐体2001、支持台2002、表示部2003、スピーカー部2004、ビデオ入力端子2005等を含む。なお、表示部2003は、実施例6で説明した発光素子や実施例7で説明した液晶素子を有している。なお、表示装置は、パソコン用、TV放送受信用、広告表示用などの全ての情報表示用装置が含まれる。

10

## 【0222】

図13（B）はノート型パーソナルコンピュータであり、本体2201、筐体2202、表示部2203、キーボード2204、外部接続ポート2205、ポインティングマウス2206等を含む。なお、表示部2203は、実施例6で説明した発光素子や実施例7で説明した液晶素子を有している。

## 【0223】

図13（C）はモバイルコンピュータであり、本体2301、表示部2302、スイッチ2303、操作キー2304、赤外線ポート2305等を含む。なお、表示部2302は、実施例6で説明した発光素子や実施例7で説明した液晶素子を有している。

20

## 【0224】

図13（D）はプログラムを記録した記録媒体（以下、記録媒体と呼ぶ）を用いるプレーヤーであり、本体2401、筐体2402、表示部A2403、表示部b2404、記録媒体読み込み部2405、操作キー2406、スピーカー部2407等を含む。なお、表示部A2403、表示部B2404は、実施例6で説明した発光素子や、実施例7で説明した液晶素子を有する。このプレーヤーは記録媒体としてDVD（Digital Versatile Disc）、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。

## 【0225】

図13（E）は携帯書籍（電子書籍）であり、本体2501、表示部2502、記憶媒体2503、操作スイッチ2504、アンテナ2505等を含む。なお、表示部2502は、実施例6で説明した発光素子や実施例7で説明した液晶素子を有している。

30

## 【0226】

図13（F）はビデオカメラであり、本体2601、表示部2602、筐体2603、外部接続ポート2604、リモコン受信部2605、受像部2606、バッテリー2607、音声入力部2608、操作キー2609、接眼部2610等を含む。なお、表示部2602は、実施例6で説明した発光素子や実施例7で説明した液晶素子を有している。

## 【0227】

ここで図13（G）は携帯電話であり、本体2701、筐体2702、表示部2703、音声入力部2704、音声出力部2705、操作キー2706、外部接続ポート2707、アンテナ2708等を含む。なお、表示部2703は、実施例6で説明した発光素子や実施例7で説明した液晶素子を有している。

40

## 【0228】

以上の様に、本発明により作製された半導体素子の適用範囲は極めて広く、あらゆる分野の電子機器に適用することが可能である。

## 【実施例9】

## 【0229】

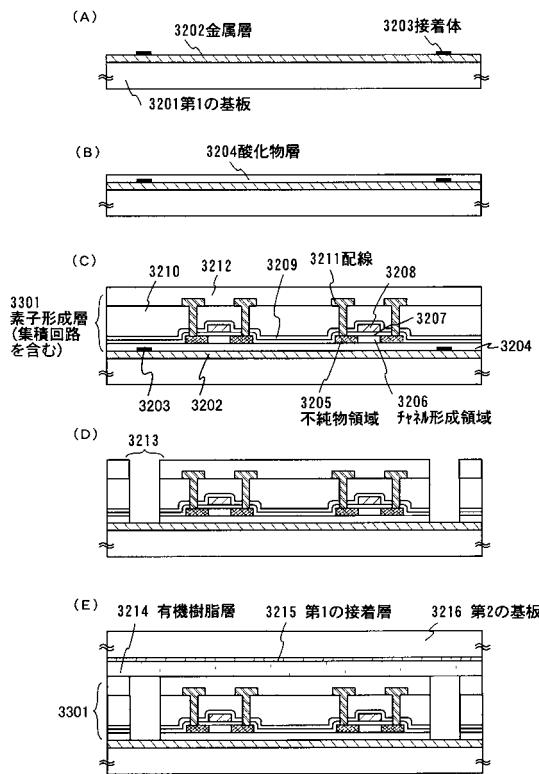

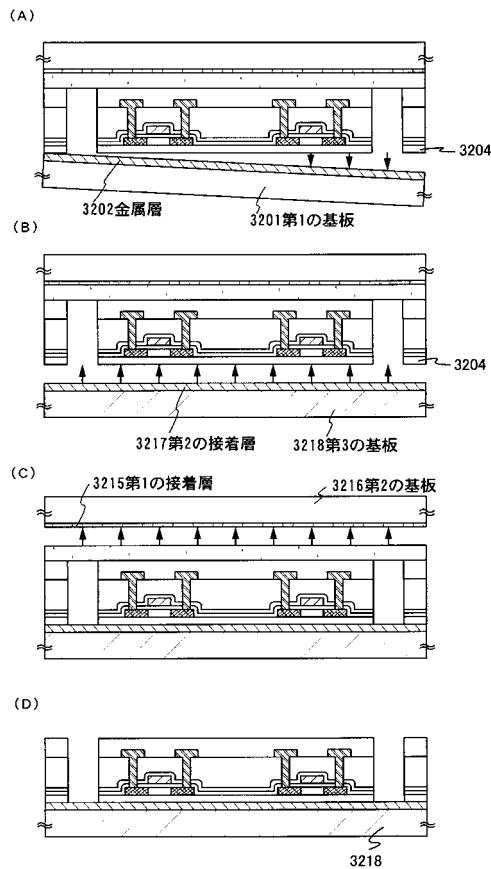

本実施例では、本発明の転写工程を含む作製方法について図15、図16を用いて説明する。

## 【0230】

50

図15(A)において、第1の基板3201上に金属層3202が積層され、その上に複数の接着体3203が形成される。

【0231】

なお、本実施例において、第1の基板3201としては、ガラス基板、石英基板を用いることができる。なお、ガラス基板としては、バリウムホウケイ酸ガラス、アルミニウムホウケイ酸ガラス、アルミニウムシリケートガラスなどを素材とするガラス基板を用いることができる、代表的には、コーニング社製の1737ガラス基板(歪み点667)、旭硝子社製のAN100(歪み点670)などが適用可能である。本実施例では、AN100を用いることとする。

【0232】

また、金属層3202には、タングステン(W)、モリブデン(Mo)、テクネチウム(Tc)、レニウム(Re)、ルテニウム(Ru)、オスミウム(Os)、ロジウム(Rh)、イリジウム(Ir)、パラジウム(Pd)、白金(Pt)、銀(Ag)、または金(Au)から選ばれた元素、前記元素を主成分とする合金、または窒化物(例えば、窒化チタン、窒化タンクステン、窒化タンタル、窒化モリブデン)を単層、または積層して用いることができるが、本実施例では、W(タングステン)を主成分とする金属層3202を用いることとする。なお、金属層3202の膜厚は10nm~200nm、好ましくは50nm~75nmとすればよい。

【0233】

金属層3202は、スパッタリング法、CVD法、蒸着法により形成することができるが、本実施例では、スパッタリング法により成膜することとする。また、スパッタリング法により金属層3202を形成する場合には、第1の基板3201を固定するため、第1の基板3201の周縁部付近における膜厚が不均一になりやすい。そのため、ドライエッティングによって周縁部のみを除去することが好ましい。

【0234】

金属層3202の上に形成される接着体3203は、非晶質シリコン膜を成膜した後、これをパターニングすることにより形成される。

【0235】

次に、酸化物層3204を形成する(図15(B))。本実施例では酸化シリコンからなる膜を酸化シリコンターゲットを用いたスパッタリング法により、膜厚150nm~200nmで形成する。なお、酸化物層3204の膜厚は、金属層3202の膜厚の2倍以上とすることが望ましい。

【0236】

次に、酸化物層3204上に素子形成層3301が形成される(図15(C))。素子形成層3301には、集積回路を構成するTFT(pチャネル型TFT、またはnチャネル型TFT)が複数形成され、これらのTFTを接続する配線3211、絶縁膜(3210、3212)等が含まれるものとする。なお、このような素子形成層の作製方法は、本発明において特に限定されるものではなく、実施例13で示すような作製方法の他、公知の作製方法を組み合わせて用いることができる。なお、TFTは、酸化物層3204上の半導体膜の一部に形成された不純物領域3205およびチャネル形成領域3206、絶縁膜3207、およびゲート電極3208により構成される。

【0237】

本実施例では、素子形成層3301を形成する際に、少なくとも水素を含む材料膜(半導体膜または金属膜)を形成した後、水素を含む材料膜中に含まれる水素を拡散するための熱処理を行う。この熱処理は420以上であればよく、素子形成層3301の形成プロセスとは別途行ってもよいし、兼用させて工程を省略してもよい。例えば、水素を含む材料膜として水素を含むアモルファスシリコン膜をCVD法により成膜した後、結晶化させるため500以上の熱処理を行えば、加熱によりポリシリコン膜が形成できると同時に水素の拡散を行うことができる。

【0238】

なお、この熱処理を行うことにより、金属層3202と酸化物層3204との間に結晶構造を有する金属酸化物からなる層（図示せず）が形成される。なお、金属層3202上に接着体3203を形成し、その上に酸化物層3204を積層形成する際に、金属層3202と酸化物層3204との間に2nm～5nm程度形成されるアモルファス状態の金属酸化物層（酸化タンゲステン膜）も、この熱処理により結晶構造を形成し、金属酸化物からなる層（図示せず）を形成する。

#### 【0239】

なお、この金属酸化物からなる層（図示せず）が金属層3202と酸化物層3204との界面に形成されることにより、後の工程での基板と素子形成層との剥離が容易になる。なお、本実施例では、素子形成層3301を形成する途中の熱処理において、金属酸化物からなる層が形成される場合について説明したが、本発明はこの方法に限られることはなく、金属層3202および接着体3203を形成した後、金属酸化物層を形成し、酸化物層3204を形成する方法で行うこともできる。

#### 【0240】

一方、素子形成層3301を形成する途中の熱処理により、接着体3203と金属層3202との密着性を高めることができる。すなわち、本実施例において、非晶質シリコン膜で形成された接着体3203は、熱処理を加えることにより、先に形成された金属層3202中のタンゲステン（W）と反応して、シリサイド（タンゲステンシリサイド：WSi<sub>2</sub>）を形成する。そのため、接着体3203と金属層3202との密着性が高められる。なお、本発明では、素子形成層3301を形成する途中の熱処理により、金属層中の金属と接着体とを反応させる方法に限られることなく、金属層と接着体を形成した後、金属層中の金属と接着体とを反応させるための熱処理を素子形成層301の作製とは別に行うこともできる。

#### 【0241】

素子形成層3301が完成したところで、接着体3203を除去する。具体的には、ドライエッティング法により絶縁膜（3210、3212）の一部と接着体3203とをエッティングし、開口部3213を形成する（図15（D））。

#### 【0242】

例えば、絶縁膜（3207、3209、3210、3212）および酸化物層3204をエッティングする場合であって、これらが、酸化珪素で形成されている場合には、炭化フッ素（CF<sub>4</sub>）を主成分とするエッティングガスを用いてドライエッティングを行い、また接着体3203をエッティングする場合であって、接着体3203が珪素で形成されており、金属層（例えばW）との反応にも拘わらずその一部に珪素を主成分とする部分が残っている場合には、これを臭化水素（HBr）および塩素（Cl<sub>2</sub>）を主成分とするエッティングガスを用いてエッティングすることができる。さらに、接着体3203が珪素で形成されており、金属層（W）との反応によってその一部がシリサイド（WSi）を形成している場合には、これをフッ化硫黄（SF<sub>6</sub>）と臭化水素（HBr）を主成分とするエッティングガスを用いてエッティングすることができる。

#### 【0243】

次に、素子形成層3301上に有機樹脂層3214を形成する。有機樹脂層3214に用いる材料としては、水またはアルコール類に可溶な有機材料を用い、これを全面に塗布、硬化することにより形成する。この有機材料の組成としては、例えば、エポキシ系、アクリレート系、シリコン系等のいかなるものでもよい。具体的には、スピンドル法により水溶性樹脂（東亜合成製：VL-WSHL10）（膜厚30μm）を塗布し、仮硬化するために2分間の露光を行ったあと、UV光を裏面から2.5分、表面から10分、合計12.5分の露光を行って本硬化させることにより有機樹脂層3214が形成される（図15（E））。

#### 【0244】

なお、後の剥離を行いやすくするために、金属層3202と酸化物層3204との界面（金属酸化物を含む層）における密着性を部分的に低下させる処理を行う。密着性を部分

10

20

30

40

50

的に低下させる処理は、剥離しようとする領域の周縁に沿って金属層3202または酸化物層3204にレーザー光を部分的に照射する処理、或いは、剥離しようとする領域の周縁に沿って外部から局所的に圧力を加えて酸化物層3204の層内または界面の一部分に損傷を与える処理である。具体的にはダイヤモンドペンなどで硬い針を垂直に押しつけて荷重をかけて動かせばよい。好ましくは、スクライバー装置を用い、押し込み量を0.1mm～2mmとし、圧力をかけて動かせばよい。このように、剥離を行う前に剥離現象が生じやすくなるような部分、即ち、きっかけをつくることが重要であり、密着性を選択的（部分的）に低下させる前処理を行うことで、剥離不良がなくなり、さらに歩留まりも向上する。

## 【0245】

10

次に、第1の接着層3215を形成することにより、有機樹脂層3214上に第1の接着層3215を介して補助基板である第2の基板3216を貼り付けることができる（図15（E））。なお、第1の接着層3215を形成する材料としては、後の工程において、所定の処理を行うことにより接着性が弱まる公知の材料を用いることができるが、本実施例では、後の工程において、光照射により接着力が低下する感光性の両面テープを用いる場合について説明する。

## 【0246】

次に、第1の基板3201を物理的手段により補助基板が貼り付けられた素子形成層301から引き剥がす。本実施例の場合には、金属層3202と酸化物層3204との界面（金属酸化物を含む層）部分において、比較的小さな力（例えば、人間の手、ノズルから吹付けられるガスの風圧、超音波等）で引き剥がすことができる。具体的には、酸化タンゲステン膜中、または酸化タンゲステン膜と酸化シリコン膜との界面、または酸化タンゲステン膜とタンゲステン膜との界面で分離させ、引き剥がすことができる。こうして、酸化物層3204上に形成された素子形成層3301を第1の基板3201から分離することができる。剥離時の状態を図16（A）に示す。

20

## 【0247】

また、剥離により露出した表面には、金属酸化物を含む層の一部が残っており、これは、後の工程において、露出面を基板等に接着する際に密着性を低下させる原因となることから、露出面に残っている金属酸化物を含む層の一部を除去する処理を行うことが好ましい。なお、これらを除去するためには、アンモニア水溶液などのアルカリ性の水溶液や酸性水溶液などを用いることができる。その他、金属酸化物を含む層の一部が剥離しやすくなる温度（430℃）以下で、以降の工程を行っても良い。

30

## 【0248】

次に、第2の接着層3217を形成し、第2の接着層3217を介して第3の基板3218と酸化物層3204（及び素子形成層3301）とを接着する（図16（B））。なお、第1の接着層3215により接着された第2の基板3216と有機樹脂層3214との密着性よりも、第2の接着層3217により接着された酸化物層3204（及び素子形成層3301）と第3の基板3218との密着性の方が高いことが重要である。

## 【0249】

40

第3の基板3218としては、可撓性基板（プラスチック基板）を用いることが好ましく、本実施例では、極性基のついたノルボルネン樹脂からなるARTON（JSR製）を用いることとする。

## 【0250】

また、第2の接着層3217に用いる材料としては、反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤が挙げられる。さらに好ましくは、銀、ニッケル、アルミニウム、窒化アルミニウムからなる粉末、またはフィラーを含ませることにより、高い熱伝導性を持たせることがより好ましい。

## 【0251】

次に、第2の基板3216側から紫外線を照射することにより、第1の接着層3215

50

に用いている両面テープの接着力を低下させ、素子形成層 3301 から第 2 の基板 3216 を分離させる（図 16（C））。さらに、本実施例では、露出した表面を水洗することにより、第 1 の接着層 3215 および有機樹脂層 3214 を溶かして除去することができる、図 16（D）に示す構造を得ることができる。

【0252】

以上により、第 1 の基板 3201 上に形成され、複数の TFT で構成された集積回路を別の基板（第 3 の基板 3218）上に作製することができる。

【実施例 10】

【0253】

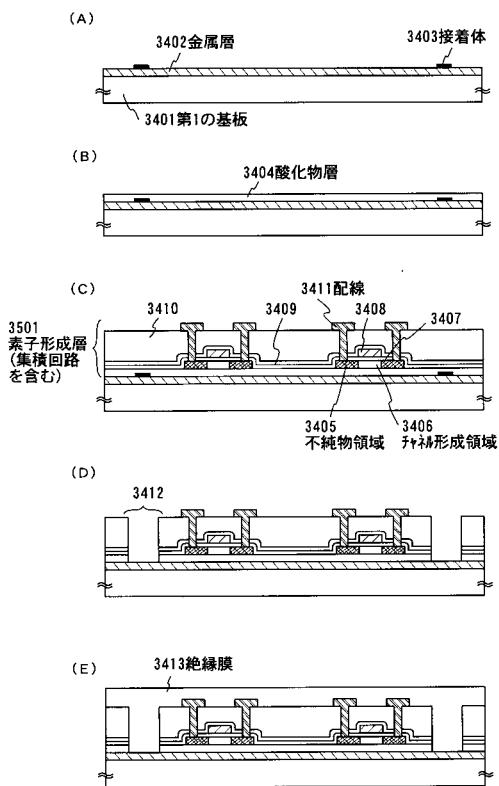

本実施例では、本発明の転写工程を含む作製方法であって、実施例 9 とはその一部が異なる場合について図 17、図 18 を用いて説明する。

【0254】

図 17（A）において、第 1 の基板 3401 上に金属層 3402 が積層され、その上に複数の接着体 3403 が形成される。

【0255】

なお、本実施例において、第 1 の基板 3401 としては、実施例 9 と同様のガラス基板（AN100）を用いることとする。また、金属層 3402 についても実施例 9 と同様に W（タンゲステン）を主成分とする金属層 3402 を用いることとする。なお、金属層 3402 は、スパッタリング法により成膜し、その膜厚は 10 nm ~ 200 nm、好ましくは 50 nm ~ 75 nm とすればよい。

【0256】

金属層 3402 の上に形成される接着体 3403 は、非晶質シリコン膜を成膜した後、これをパターニングすることにより形成される。

【0257】

次に、酸化物層 3404 を形成する（図 17（B））。本実施例では酸化シリコンからなる膜を酸化シリコンターゲットを用いたスパッタリング法により、膜厚 150 nm ~ 200 nm で形成する。なお、酸化物層 3404 の膜厚は、金属層 3402 の膜厚の 2 倍以上とすることが望ましい。

【0258】

次に、酸化物層 3404 上に素子形成層 3501 が形成される（図 17（C））。素子形成層 3501 には、集積回路を構成する TFT（p チャネル型 TFT、または n チャネル型 TFT）が複数形成され、これらの TFT を接続する配線 3411、絶縁膜 3410 等が含まれるものとする。なお、このような素子形成層の作製方法は、本発明において特に限定されるものではなく、実施例 13 で示すような作製方法の他、公知の作製方法を組み合わせて用いることができる。なお、TFT は、酸化物層 3404 上の半導体膜の一部に形成された不純物領域 3405 およびチャネル形成領域 3406、絶縁膜 3407、およびゲート電極 3408 により構成される。

【0259】

本実施例でも実施例 9 の場合と同様に素子形成層 3501 を形成する際に、少なくとも水素を含む材料膜（半導体膜または金属膜）を形成した後、水素を含む材料膜中に含まれる水素を拡散するための熱処理を行う。なお、この熱処理を行うことにより、金属層 3402 と酸化物層 3404 との間に結晶構造を有する金属酸化物からなる層（図示せず）が形成される。

【0260】

なお、この金属酸化物からなる層（図示せず）が金属層 3402 と酸化物層 3404 との界面に形成されることにより、後の工程での基板と素子形成層との剥離が容易になる。

【0261】

一方、素子形成層 3501 を形成する途中の熱処理により、接着体 3403 と金属層 3402 との密着性を高めることができる。

【0262】

10

20

30

40

50

本実施例では、素子形成層 3501 に含まれる配線 3411 まで形成したところで、接着体 3403 を除去する。具体的には、ドライエッティング法により絶縁膜 3410 の一部と接着体 3403 とをエッティングし、開口部 3412 を形成する（図 17（D））。

#### 【0263】

例えは、絶縁膜（3407、3409、3410）および酸化物層 3404 をエッティングする場合であって、これらが、酸化珪素で形成されている場合には、炭化フッ素（CF<sub>4</sub>）を主成分とするエッティングガスを用いてドライエッティングを行い、また接着体 3403 をエッティングする場合であって、接着体 3403 が珪素で形成されており、金属層（例えは W）との反応にも拘わらずその一部に珪素を主成分とする部分が残っている場合には、これを臭化水素（HBr）および塩素（Cl<sub>2</sub>）を主成分とするエッティングガスを用いてエッティングすることができる。さらに、接着体 3403 が珪素で形成されており、金属層（W）との反応によってその一部がシリサイド（WSi）を形成している場合には、これをフッ化硫黄（SF<sub>6</sub>）と臭化水素（HBr）を主成分とするエッティングガスを用いてエッティングすることができる。

#### 【0264】

次に、開口部 3412 を埋め、素子形成層 3501 の表面を平坦化するために絶縁膜 3413 を形成する（図 17（E））。なお、本実施例では、プラズマ CVD 法により形成された膜厚 1～3 μm の窒化酸化シリコン膜を用いる。勿論、この絶縁膜は窒化酸化シリコン膜に限定されるものでなく、窒化シリコン、窒化シリコン、酸化シリコンといった絶縁材料や、アクリル、ポリイミド、ポリアミドなどの有機絶縁材料からなる単層構造や、これらを組み合わせた積層構造としても良い。

#### 【0265】

なお、絶縁膜 3413 により素子形成層 3501 の表面を平坦化した後の工程である（1）素子形成層 3501 の上に有機樹脂層を形成し、その上に第 1 の接着層を介して補助基板である第 2 の基板を貼り付ける工程、（2）素子形成層 501 から第 1 の基板 3401 を物理的手段により補助基板（第 2 の基板）が貼り付けられた素子形成層 3501 から引き剥がす工程、（3）第 2 の接着層を形成し、第 2 の接着層を介して第 3 の基板と酸化物層（及び素子形成層）とを接着する工程、および（4）素子形成層から第 2 の基板を分離させる工程、については実施例 9 に示すものと同様の材料を用いて、同様の方法により形成することができるので説明は省略することとする。

#### 【0266】

以上により、素子形成層 3501 が第 2 の接着層 3417 を介して第 3 の基板 3418 上に転写された図 18（A）に示す構造を得ることができる。

#### 【0267】

また、本実施例では、図 17（D）において開口部 3412 を形成した後、絶縁膜 3419 を形成することにより、図 18（B）に示す構造を形成しても良い。

#### 【0268】

以上により、第 1 の基板 3401 上に形成され、複数の TFT で構成された集積回路を別の基板（第 3 の基板 3418）上に作製することができる。

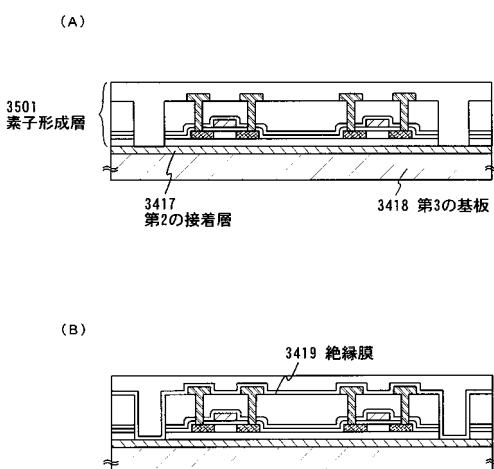

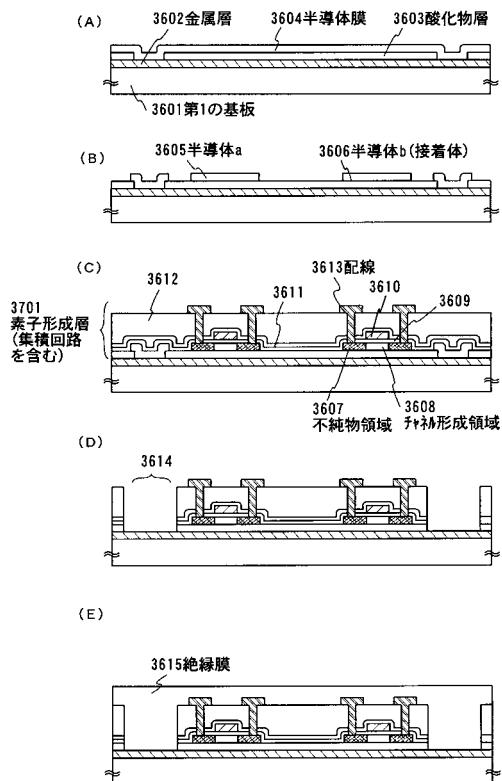

#### 【実施例 11】

#### 【0269】

本実施例では、本発明の転写工程を含む作製方法であって、実施例 9 や実施例 10 とはその一部が異なる場合について図 19、20 を用いて説明する。

#### 【0270】

図 19（A）において、第 1 の基板 3601 上に金属層 3602 が積層され、その上に酸化物層 3603 が形成される。

#### 【0271】

なお、本実施例において、第 1 の基板 3601 としては、実施例 9 と同様のガラス基板（AN100）を用いることとする。また、金属層 3602 についても実施例 9 と同様に W（タンゲステン）を主成分とする金属層 3602 を用いることとする。なお、金属層 3

10

20

30

40

50

602は、スパッタリング法により成膜し、その膜厚は10nm～200nm、好ましくは50nm～75nmとすればよい。

【0272】

金属層3602の上に形成される酸化物層3603は、酸化シリコンからなる膜を酸化シリコンターゲットを用いたスパッタリング法により、膜厚150nm～200nmで形成する。なお、酸化物層3603の膜厚は、金属層3602の膜厚の2倍以上とすることが望ましい。また、本実施例において、酸化物層3603は、パターニングにより複数の島状に分離形成される。

【0273】

次に、酸化物層3603を覆って、半導体膜3604が形成される。本実施例では、非晶質シリコン膜をプラズマCVD法により成膜することにより形成される(図19(A))。そして、この半導体膜3604をパターニングすることにより、酸化物層3603上に形成される半導体a(3605)、分離形成された2つの酸化物層3603の間に形成された半導体b(3606)が得られる。なお、ここで形成される半導体a(3605)は、後で形成されるTFTの不純物領域およびチャネル形成領域となり、半導体b(3606)が、本発明における接着体となる。

【0274】

すなわち、本発明では、TFTの一部を形成する半導体a(3605)と、接着体を形成する半導体b(3606)が同時に形成される点に特徴がある。

【0275】

次に、半導体a(3605)を一部に含む素子形成層3701が形成される(図19(C))。素子形成層3701には、集積回路を構成するTFT(pチャネル型TFT、またはnチャネル型TFT)が複数形成され、これらのTFTを接続する配線3613、絶縁膜3612等が含まれるものとする。なお、TFTを含む素子形成層の作製方法は、本発明において特に限定されるものではなく、実施例13で示すような作製方法の他、公知の作製方法を組み合わせて用いることができる。なお、TFTは、酸化物層3603上の半導体a(3605)の一部に形成された不純物領域3607およびチャネル形成領域3608、ゲート絶縁膜3609、およびゲート電極3610により構成される。

【0276】

本実施例でも実施例9の場合と同様に素子形成層3701を形成する際に、少なくとも水素を含む材料膜(半導体膜または金属膜)を形成した後、水素を含む材料膜中に含まれる水素を拡散するための熱処理を行う。なお、この熱処理を行うことにより、金属層3602と酸化物層3603との間に結晶構造を有する金属酸化物からなる層(図示せず)が形成される。

【0277】

なお、この金属酸化物からなる層(図示せず)が金属層3602と酸化物層3603との界面に形成されることにより、後の工程での第1の基板3601と素子形成層3701との剥離が容易になる。

【0278】

一方、素子形成層3701を形成する途中の熱処理により、接着体である半導体b(3606)と金属層3602との密着性を高めることができる。

【0279】

本実施例では、素子形成層3701に含まれる配線3613まで形成したところで、半導体b(3606)を除去する(図19(D))。具体的には、ドライエッチング法により絶縁膜3612の一部と半導体b(3606)とをエッチングし、開口部3614を形成する。

【0280】

例えば、絶縁膜(3609、3611、3612)および酸化物層3603をエッチングする場合であって、これらが、酸化珪素で形成されている場合には、炭化フッ素(CF<sub>4</sub>)を主成分とするエッチングガスを用いてドライエッチングを行い、また接着体である

10

20

30

40

50

半導体 b ( 3 6 0 6 ) をエッティングする場合であって、半導体 b ( 3 6 0 6 ) が珪素で形成されており、金属層 ( 例えは W ) との反応にも拘わらずその一部に珪素を主成分とする部分が残っている場合には、これを臭化水素 ( H B r ) および塩素 ( C l <sub>2</sub> ) を主成分とするエッティングガスを用いてエッティングすることができる。さらに、半導体 b ( 3 6 0 6 ) が珪素で形成されており、金属層 ( W ) との反応によってその一部がシリサイド ( W S i ) を形成している場合には、これをフッ化硫黄 ( S F <sub>6</sub> ) と臭化水素 ( H B r ) を主成分とするエッティングガスを用いてエッティングすることができる。

#### 【 0 2 8 1 】

次に、開口部 3 6 1 4 を埋め、素子形成層 3 7 0 1 の表面を平坦化するために絶縁膜 3 6 1 5 を形成する ( 図 1 9 ( E ) )。なお、本実施例では、プラズマ C V D 法により形成された膜厚 1 ~ 3 μ m の窒化酸化シリコン膜を用いる。勿論、この絶縁膜は窒化酸化シリコン膜に限定されるものでなく、窒化シリコン、窒化シリコン、酸化シリコンといった絶縁材料や、アクリル、ポリイミド、ポリアミドなどの有機絶縁材料からなる単層構造や、これらを組み合わせた積層構造としても良い。

10

#### 【 0 2 8 2 】

なお、絶縁膜 3 6 1 5 により素子形成層 3 7 0 1 の表面を平坦化した後の工程である ( 1 ) 素子形成層 3 7 0 1 の上に有機樹脂層を形成し、その上に第 1 の接着層を介して補助基板である第 2 の基板を貼り付ける工程、 ( 2 ) 素子形成層 3 7 0 1 から第 1 の基板 3 6 0 1 を物理的手段により補助基板 ( 第 2 の基板 ) が貼り付けられた素子形成層 3 7 0 1 から引き剥がす工程、 ( 3 ) 第 2 の接着層を形成し、第 2 の接着層を介して第 3 の基板と酸化物層 ( 及び素子形成層 ) とを接着する工程、および ( 4 ) 素子形成層から第 2 の基板を分離させる工程、については実施例 9 に示すものと同様の材料を用いて、同様の方法により形成することができるので説明は省略することとする。

20

#### 【 0 2 8 3 】

以上により、素子形成層 3 7 0 1 が第 2 の接着層 3 6 1 7 を介して第 3 の基板 3 6 1 8 上に転写された図 2 0 ( A ) に示す構造を得ることができる。

#### 【 0 2 8 4 】

また、本実施例では、図 1 9 ( D ) において開口部 3 6 1 4 を形成した後、絶縁膜 3 8 0 0 を形成することにより、図 2 0 ( B ) に示す構造を形成しても良い。

30

#### 【 0 2 8 5 】

以上により、第 1 の基板 3 6 0 1 上に形成され、複数の T F T で構成された集積回路を別の基板 ( 第 3 の基板 3 6 1 8 ) 上に作製することができる。

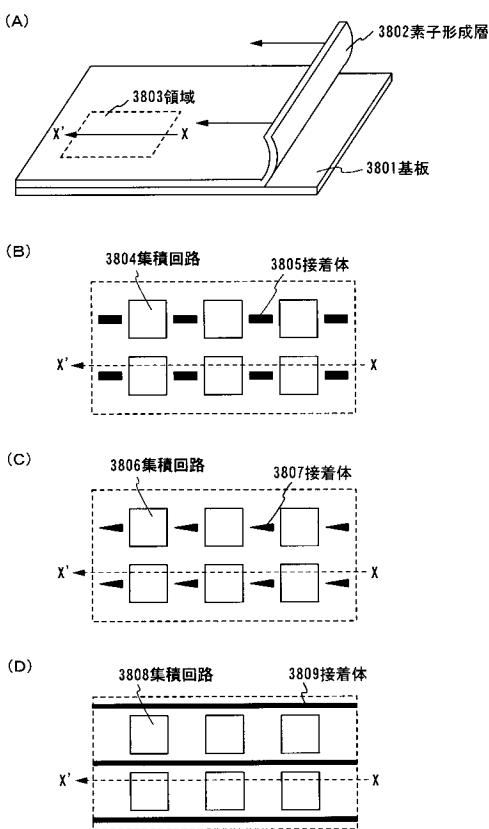

#### 【 実施例 1 2 】

#### 【 0 2 8 6 】

本実施例では、本発明における接着体の配置およびその形状について、図 2 1 を用いて説明する。

#### 【 0 2 8 7 】

本発明では、図 2 1 ( A ) に示すように基板 3 8 0 1 上に形成された素子形成層 3 8 0 2 が、物理的手段によって剥離され、別の基板上に貼付けられることにより、転写が行われる。なお、図 2 1 ( A ) の場合には、素子形成層 3 8 0 2 は、矢印の方向に剥離されるものとする。

40

#### 【 0 2 8 8 】

そこで、素子形成層 3 8 0 2 に形成される接着体の配置および形状について、素子形成層 3 8 0 2 の一部である領域 3 8 0 3 に素子形成層 3 8 0 2 の作製途中に形成され、剥離直前に除去される接着体の配置および形状の一例を図 2 1 ( B ) ~ 図 2 1 ( D ) に示す。

#### 【 0 2 8 9 】

図 2 1 ( B ) では、集積回路 3 8 0 4 が複数形成される領域 3 8 0 3 において、剥離方向 X X ' に配列される集積回路 3 8 0 4 の間に四角形状の接着体 3 8 0 5 が形成される場合について示す。なお、この場合、四角形状の接着体 3 8 0 5 が長方形を有し、剥離方向 A A ' と平行に長方形の長辺が並ぶように配置されるのがより好ましい。このように接着

50

体 3 8 0 5 を四角形状とすることにより、接着体 3 8 0 5 を除去した後、素子形成層 3 8 0 2 を基板 3 8 0 1 から容易に剥離することができる。

【 0 2 9 0 】

図 2 1 ( C ) では、集積回路 3 8 0 6 が複数形成される領域 3 8 0 3 において、剥離方向 A A ' に配列される集積回路 3 8 0 6 の間に三角形状の接着体 3 8 0 7 が形成される場合について示す。なお、この場合、三角形状の接着体 3 8 0 7 の底辺が、剥離方向 X X ' と垂直になるように配置されるのがより好ましい。このように接着体 3 8 0 7 を三角形状とした場合にも、接着体 3 8 0 7 を除去した後、素子形成層 3 8 0 2 を基板 3 8 0 1 から容易に剥離することができる。

【 0 2 9 1 】

図 2 1 ( D ) では、集積回路 3 8 0 8 が複数形成される領域 3 8 0 3 において、剥離方向 X X ' に複数配列される集積回路 3 8 0 8 の列と列との間にライン状の接着体 3 8 0 9 が形成される場合について示す。なお、この場合、ライン状の接着体 3 8 0 9 は、剥離方向 X X ' に複数の集積回路 3 8 0 8 が配列されるのと同じ長さで形成しても良いが、集積回路 3 8 0 8 1 つ分の長さで形成しても良い。このように接着体 3 8 0 9 をライン状とした場合にも、接着体 3 8 0 7 を除去した後、素子形成層 3 8 0 2 を基板 3 8 0 1 から容易に剥離することができる。

【 0 2 9 2 】

なお、本実施例で示した接着体の配置および形状は、本発明における好ましい一例に過ぎず、本発明の接着体の形状を何ら限定するものではない。

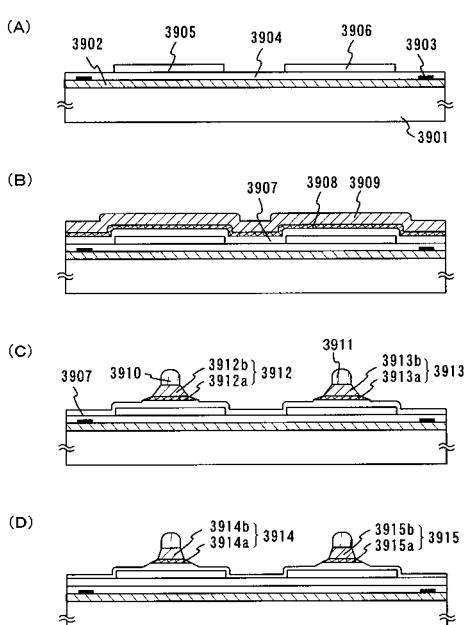

【 実施例 1 3 】

【 0 2 9 3 】

本実施例では、同一基板上に n チャネル型 TFT 及び p チャネル型 TFT を同時に作製する方法について、図 2 2 、図 2 3 を用いて説明する。

【 0 2 9 4 】

基板 3 9 0 1 上に金属層 3 9 0 2 が形成され、その上に接着体 3 9 0 3 が形成される。

【 0 2 9 5 】

本実施例では、基板 3 9 0 1 として、ガラス基板 ( # 1 7 3 7 ) を用い、金属層 3 9 0 2 には、実施例 9 と同様にタンゲステン ( W ) を主成分とする金属材料を用いる。なお、接着体 3 9 0 3 は、後で形成される集積回路 ( 複数の TFT を含む ) の間に配置されるよう所望の形状にパターニングされ、形成される。

【 0 2 9 6 】

次に金属層 3 9 0 2 および接着体 3 9 0 3 上に下地絶縁膜としても機能する酸化物層 3 9 0 4 を形成する。本実施例では、プラズマ CVD 法で成膜温度 3 0 0 °C 、原料ガス SiH<sub>4</sub> 、 N<sub>2</sub>O から作製される酸化窒化シリコン膜 ( 組成比 Si = 3 2 % 、 O = 5 9 % 、 N = 7 % 、 H = 2 % ) を 1 0 0 nm の厚さに成膜することにより、酸化物層 3 9 0 4 を形成する。

【 0 2 9 7 】

さらに、大気解放せず連続的にプラズマ CVD 法で成膜温度 3 0 0 °C 、成膜ガス SiH<sub>4</sub> で非晶質構造を有する半導体層 ( ここでは非晶質シリコン層 ) を 5 4 nm の厚さで形成する。この非晶質シリコン層は水素を含んでおり、後の熱処理によって水素を拡散させ、物理的手段で酸化物層の層内、あるいは界面において剥離することができる。

【 0 2 9 8 】

次に、重量換算で 1 0 ppm のニッケルを含む酢酸ニッケル塩溶液をスピナーで塗布する。塗布に代えてスパッタ法でニッケル元素を全面に散布する方法を用いてもよい。次いで、加熱処理を行い結晶化させて結晶構造を有する半導体膜 ( ここではポリシリコン層 ) を形成する。ここでは脱水素化のための熱処理 ( 5 0 0 °C 、 1 時間 ) の後、結晶化のための熱処理 ( 5 5 0 °C 、 4 時間 ) を行って結晶構造を有するシリコン膜を得る。また、この脱水素化のための熱処理 ( 5 0 0 °C 、 1 時間 ) は、非晶質シリコン膜に含まれる水素を金属層 3 9 0 2 と酸化物層 3 9 0 4 との界面に拡散する熱処理を兼ねている。なお、ここで

10

20

30

40

50

はシリコンの結晶化を助長する金属元素としてニッケルを用いた結晶化技術を用いるが、他の公知の結晶化技術、例えば固相成長法やレーザー結晶化法を用いてもよい。

#### 【0299】

次に、結晶構造を有するシリコン膜表面の酸化膜を希フッ酸等で除去した後、結晶化率を高め、結晶粒内に残される欠陥を補修するためのレーザー光 (XeCl: 波長 308 nm) の照射を大気中、または酸素雰囲気中で行う。レーザー光には波長 400 nm 以下のエキシマレーザー光や、YAG レーザーの第 2 高調波、第 3 高調波を用いる。ここでは、繰り返し周波数 10 ~ 1000 Hz 程度のパルスレーザー光を用い、当該レーザー光を光学系にて 100 ~ 500 mJ / cm<sup>2</sup> に集光し、90 ~ 95 % のオーバーラップ率をもつて照射し、シリコン膜表面を走査させればよい。ここでは、繰り返し周波数 30 Hz、エネルギー密度 470 mJ / cm<sup>2</sup> でレーザー光の照射を大気中で行う。 10

#### 【0300】

なお、大気中、または酸素雰囲気中で行うため、レーザー光の照射により表面に酸化膜が形成される。なお、ここではパルスレーザーを用いる例を示したが、連続発振のレーザーを用いてもよく、非晶質半導体膜の結晶化に際し、大粒径に結晶を得るためにには、連続発振が可能な固体レーザーを用い、基本波の第 2 高調波 ~ 第 4 高調波を適用するのが好ましい。代表的には、Nd:YVO<sub>4</sub> レーザー (基本波 1064 nm) の第 2 高調波 (532 nm) や第 3 高調波 (355 nm) を適用すればよい。連続発振のレーザーを用いる場合には、出力 10 W の連続発振の YVO<sub>4</sub> レーザーから射出されたレーザー光を非線形光学素子により高調波に変換する。また、共振器の中に YVO<sub>4</sub> 結晶と非線形光学素子を入れて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または橢円形状のレーザー光に成形して、被処理体に照射する。このときのエネルギー密度は 0.01 ~ 100 MW / cm<sup>2</sup> 程度 (好ましくは 0.1 ~ 10 MW / cm<sup>2</sup> ) が必要である。そして、10 ~ 2000 cm / s 程度の速度でレーザー光に対して相対的に半導体膜を移動させて照射すればよい。 20

#### 【0301】

次に、上記レーザー光の照射により形成された酸化膜に加え、オゾン水で表面を 120 秒処理して合計 1 ~ 5 nm の酸化膜からなるバリア層を形成する。本実施の形態ではオゾン水を用いてバリア層を形成するが、酸素雰囲気下の紫外線の照射で結晶構造を有する半導体膜の表面を酸化する方法や酸素プラズマ処理により結晶構造を有する半導体膜の表面を酸化する方法やプラズマ CVD 法やスパッタ法や蒸着法などで 1 ~ 10 nm 程度の酸化膜を堆積してバリア層を形成してもよい。また、バリア層を形成する前にレーザー光の照射により形成された酸化膜を除去してもよい。 30

#### 【0302】

次に、バリア層上にスパッタリング法にてゲッタリングサイトとなるアルゴン元素を含む非晶質シリコン膜を 10 nm ~ 400 nm、ここでは膜厚 100 nm で成膜する。本実施例では、アルゴン元素を含む非晶質シリコン膜は、シリコンターゲットを用いてアルゴンを含む雰囲気下で形成する。プラズマ CVD 法を用いてアルゴン元素を含む非晶質シリコン膜を形成する場合、成膜条件は、モノシリランとアルゴンの流量比 (SiH<sub>4</sub> : Ar) を 1 : 99 とし、成膜圧力を 6.665 Pa (0.05 Torr) とし、RF パワー密度を 0.087 W / cm<sup>2</sup> とし、成膜温度を 350 とする。 40

#### 【0303】

その後、650 に加熱された炉に入れて 3 分の熱処理を行いゲッタリングして、結晶構造を有する半導体膜中のニッケル濃度を低減する。炉に代えてランプアニール装置を用いてもよい。

#### 【0304】

次に、バリア層をエッチングストッパーとして、ゲッタリングサイトであるアルゴン元素を含む非晶質シリコン膜を選択的に除去した後、バリア層を希フッ酸で選択的に除去する。なお、ゲッタリングの際、ニッケルは酸素濃度の高い領域に移動しやすい傾向があるため、酸化膜からなるバリア層をゲッタリング後に除去することが望ましい。 50

## 【0305】

次いで、得られた結晶構造を有するシリコン膜（ポリシリコン膜とも呼ばれる）の表面にオゾン水で薄い酸化膜を形成した後、レジストからなるマスクを形成し、所望の形状にエッチング処理して島状に分離された半導体層3905、3906を形成する。半導体層3905、3906を形成した後、レジストからなるマスクを除去する（図22（A））。

## 【0306】

次に、フッ酸を含むエッチャントで酸化膜を除去すると同時にシリコン膜（半導体層3905、3906）の表面を洗浄した後、ゲート絶縁膜3907となるシリコンを主成分とする絶縁膜を形成する。本実施例では、プラズマCVD法により115nmの厚さで酸化シリコン膜を形成する（図22（B））。

10

## 【0307】

さらに、ゲート絶縁膜3907上に膜厚20～100nmの第1の導電膜3908と、膜厚100～400nmの第2の導電膜3909とを積層形成する。本実施例では、ゲート絶縁膜3907上に第1の導電膜3908となる膜厚50nmの窒化タンタル膜、第2の導電膜3909となる膜厚370nmのタンゲステン膜を順次積層する。

## 【0308】

なお、第1の導電膜3908及び第2の導電膜3909を形成する導電性材料としてはTa、W、Ti、Mo、Al、Cuから選ばれた元素、または前記元素を主成分とする合金材料もしくは化合物材料を用いることができる。また、第1の導電膜3908及び第2の導電膜3909としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜や、AgPdCu合金を用いてもよい。また、2層構造に限定されず、例えば、膜厚50nmのタンゲステン膜、膜厚500nmのアルミニウムとシリコンの合金（Al-Si）膜、膜厚30nmの窒化チタン膜を順次積層した3層構造としてもよい。また、3層構造とする場合、第1の導電膜のタンゲステンに代えて窒化タンゲステンを用いてもよいし、第2の導電膜のアルミニウムとシリコンの合金（Al-Si）膜に代えてアルミニウムとチタンの合金膜（Al-Ti）を用いてもよいし、第3の導電膜の窒化チタン膜に代えてチタン膜を用いてもよい。また、単層構造であってもよい。

20

## 【0309】

次に、図22（C）に示すように光露光工程によりレジストからなるマスク3910、3911を形成し、ゲート電極及び配線を形成するための第1のエッチング処理を行う。第1のエッチング処理では第1及び第2のエッチング条件で行う。エッチングにはICP（Inductively Coupled Plasma：誘導結合型プラズマ）エッチング法を用いると良い。ICPエッチング法を用い、エッチング条件（コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等）を適宜調節することによって所望のテーパー形状に膜をエッチングすることができる。なお、エッチング用ガスとしては、Cl<sub>2</sub>、BCl<sub>3</sub>、SiCl<sub>4</sub>、CCl<sub>4</sub>などを代表とする塩素系ガスまたはCF<sub>4</sub>、SF<sub>6</sub>、NF<sub>3</sub>などを代表とするフッ素系ガス、またはO<sub>2</sub>を適宜用いることができる。

30

## 【0310】

本実施例では、基板側（試料ステージ）にも150WのRF（13.56MHz）電力を投入し、実質的に負の自己バイアス電圧を印加する。なお、基板側の電極面積サイズは、12.5cm×12.5cmであり、コイル型の電極面積サイズ（ここではコイルの設けられた石英円板）は、直径25cmの円板である。この第1のエッチング条件によりW膜をエッチングして第1の導電層の端部をテーパー形状とする。第1のエッチング条件でのWに対するエッチング速度は200.39nm/min、TaNに対するエッチング速度は80.32nm/minであり、TaNに対するWの選択比は約2.5である。また、この第1のエッチング条件によって、Wのテーパー角は、約26°となる。この後、レジストからなるマスク3910、3911を除去せずに第2のエッチング条件に変え、エッチング用ガスにCF<sub>4</sub>とCl<sub>2</sub>とを用い、それぞれのガス流量比を30/30（sccm）とし、1Paの圧力でコイル型の電極に500WのRF（13.56MHz）電力を投

40

50

入してプラズマを生成して約30秒程度のエッティングを行った。基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。CF<sub>4</sub>とCl<sub>2</sub>を混合した第2のエッティング条件ではW膜及びTaN膜とも同程度にエッティングされる。第2のエッティング条件でのWに対するエッティング速度は58.97nm/min、TaNに対するエッティング速度は66.43nm/minである。なお、ゲート絶縁膜上に残渣を残すことなくエッティングするためには、10~20%程度の割合でエッティング時間を増加させると良い。

#### 【0311】

上記第1のエッティング処理では、レジストからなるマスクの形状を適したものとすることにより、基板側に印加するバイアス電圧の効果により第1の導電層及び第2の導電層の端部がテーパー形状となる。このテーパー部の角度は15~45°とすればよい。

10

#### 【0312】

こうして、第1のエッティング処理により第1の導電層と第2の導電層からなる第1の形状の導電層3912、3913(第1の導電層3912a、3913aと第2の導電層3912b、3913b)を形成する。ゲート絶縁膜となる絶縁膜3907は、10~20nm程度エッティングされ、第1の形状の導電層3912、3913で覆われない領域が薄くなつたゲート絶縁膜3907となる。

#### 【0313】

次に、レジストからなるマスクを除去せずに第2のエッティング処理を行う。ここでは、エッティング用ガスにSF<sub>6</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、それぞれのガス流量比を24/12/24(ccm)とし、1.3Paの圧力でコイル型の電極に700WのRF(13.56MHz)電力を投入してプラズマを生成してエッティングを25秒行う。基板側(試料ステージ)にも10WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。第2のエッティング処理でのWに対するエッティング速度は227.3nm/min、TaNに対するエッティング速度は32.1nm/minであり、TaNに対するWの選択比は7.1であり、ゲート絶縁膜3911であるSiONに対するエッティング速度は33.7nm/minであり、SiONに対するWの選択比は6.83である。このようにエッティングガス用ガスにSF<sub>6</sub>を用いた場合、ゲート絶縁膜3911との選択比が高いので膜減りを抑えることができる。本実施例におけるゲート絶縁膜3907の膜減りは8nm程度である。

20

#### 【0314】

この第2のエッティング処理によりWのテーパー角を70°とすることができます。この第2のエッティング処理により第2の導電層3914b、3915bを形成する。このとき、第1の導電層は、ほとんどエッティングされず、第1の導電層3914a、3915aとなる。なお、第1の導電層3914a、3915aは、第1の導電層3912a、3913aとほぼ同一サイズである。実際には、第1の導電層の幅は、第2のエッティング処理前に比べて約0.3μm程度、即ち線幅全体で0.6μm程度後退する場合もあるがほとんどサイズに変化がない。

30

#### 【0315】

また、2層構造に代えて、膜厚50nmのタンゲステン膜、膜厚500nmのアルミニウムとシリコンの合金(AL-Si)膜、膜厚30nmの窒化チタン膜を順次積層した3層構造とした場合、第1のエッティング処理における第1のエッティング条件としては、BCl<sub>3</sub>とCl<sub>2</sub>とO<sub>2</sub>とを原料ガスに用い、それぞれのガス流量比を65/10/5(ccm)とし、基板側(試料ステージ)に300WのRF(13.56MHz)電力を投入し、1.2Paの圧力でコイル型の電極に450WのRF(13.56MHz)電力を投入してプラズマを生成して117秒のエッティングを行えばよく、第1のエッティング処理における第2のエッティング条件としては、CF<sub>4</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、それぞれのガス流量比を25/25/10(ccm)とし、基板側(試料ステージ)にも20WのRF(13.56MHz)電力を投入し、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して約30秒程度のエッティングを行えばよ

40

50

く、第2のエッティング処理としてはB C 1<sub>3</sub>とC 1<sub>2</sub>を用い、それぞれのガス流量比を20/60(sccm)とし、基板側(試料ステージ)には100WのRF(13.56MHz)電力を投入し、1.2Paの圧力でコイル型の電極に600WのRF(13.56MHz)電力を投入してプラズマを生成してエッティングを行えばよい。

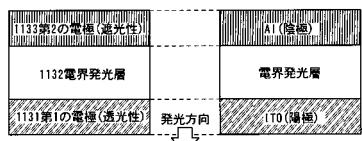

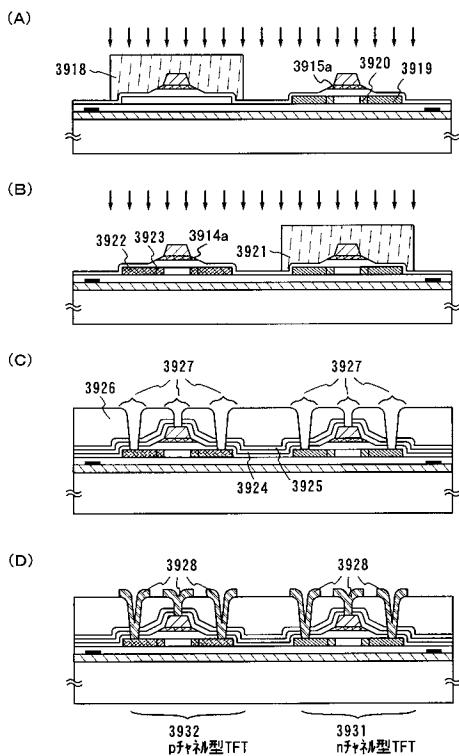

## 【0316】

次に、レジストからなるマスク3910を除去した後、次に、図23(A)に示すようにレジストからなるマスク3918を形成し第1のドーピング処理を行う。ドーピング処理はイオンドープ法、もしくはイオン注入法で行えばよい。なお、マスク3918はpチャネル型TFTを形成する半導体膜及びその周辺の領域を保護するマスクである。

## 【0317】

第1のドーピング処理におけるイオンドープ法の条件はドーザ量を $1.5 \times 10^{15}$ atoms/cm<sup>2</sup>とし、加速電圧を60~100keVとしてリン(P)をドーピングする。なお、n型を付与する不純物元素として、典型的にはリン(P)または砒素(As)を用いることができる。ここでは、第2の導電層3914b、3915bをマスクとして各半導体層に不純物領域が自己整合的に形成される。勿論、マスク3918で覆われた領域には添加されない。こうして、第1の不純物領域3919と、第2の不純物領域3920が形成される。第1の不純物領域3919には $1 \times 10^{20} \sim 1 \times 10^{21}$ /cm<sup>3</sup>の濃度範囲でn型を付与する不純物元素が添加されている。ここでは、第1の不純物領域と同じ濃度範囲の領域をn<sup>+</sup>領域とも呼ぶ。

## 【0318】

また、第2の不純物領域3920は第1の導電層3915aにより第1の不純物領域3919よりも低濃度に形成され、 $1 \times 10^{18} \sim 1 \times 10^{19}$ /cm<sup>3</sup>の濃度範囲でn型を付与する不純物元素が添加されることになる。なお、第2の不純物領域3920は、テーパー形状である第1の導電層3915aの部分を通過させてドーピングを行うため、テーパー部の端部に向かって不純物濃度が増加する濃度勾配を有している。ここでは、第2の不純物領域3920と同じ濃度範囲の領域をn<sup>-</sup>領域とも呼ぶ。

## 【0319】

次いで、レジストからなるマスク3918を除去した後、新たにレジストからなるマスク3921を形成して図23(B)に示すように第2のドーピング処理を行う。ドーピング処理はイオンドープ法、もしくはイオン注入法で行えばよい。なお、マスク3921は、nチャネル型TFTを形成する半導体膜及びその周辺の領域を保護するマスクである。

## 【0320】

第2のドーピング処理におけるイオンドープ法の条件は、ドーザ量を $1 \times 10^{15} \sim 2 \times 10^{16}$ atoms/cm<sup>2</sup>とし、加速電圧を50~100keVとしてボロン(B)をドーピングする。ここでは、第2の導電層3914b、3915bをマスクとして、各半導体層に不純物領域が自己整合的に形成される。勿論、マスク3921で覆われた領域にはボロンは添加されない。上記第2のドーピング処理により、pチャネル型TFTを形成する半導体層にp型の導電型を付与する不純物元素が添加された第3の不純物領域3922及び第4の不純物領域3923を形成する。

## 【0321】

また、第3の不純物領域3922には $1 \times 10^{20} \sim 1 \times 10^{21}$ /cm<sup>3</sup>の濃度範囲でp型を付与する不純物元素が添加されるようとする。

## 【0322】

また、第4の不純物領域3923は第1の導電層3914aのテーパー部と重なる領域に形成されるものであり、 $1 \times 10^{18} \sim 1 \times 10^{20}$ /cm<sup>3</sup>の濃度範囲でp型を付与する不純物元素が添加されるようとする。なお、第4の不純物領域3923は、テーパー形状である第1の導電層3914aの部分を通過させてドーピングを行うため、テーパー部の端部に向かって不純物濃度が増加する濃度勾配を有している。ここでは、第4の不純物領域3923と同じ濃度範囲の領域をp<sup>-</sup>領域とも呼ぶ。

## 【0323】

10

20

30

40

50

以上の工程により、それぞれの半導体層にn型またはp型の導電型を有する不純物領域が形成される。第1の形状の導電層3914、3915はTFTのゲート電極となる。

【0324】

次に、それぞれの半導体層に添加された不純物元素を活性化処理する工程を行う。この活性化工程は、ランプ光源を用いたラピッドサーマルアニール法(RTA法)、或いはYAGレーザーまたはエキシマレーザーを裏面から照射する方法、或いは炉を用いた熱処理、或いはこれらの方のうち、いずれかと組み合わせた方法によって行う。

【0325】

次に、第1の絶縁膜3924を形成する。なお、本実施例では、プラズマCVD法により形成された膜厚50nmの窒化酸化シリコン膜を用いる。勿論、この絶縁膜は窒化酸化シリコン膜に限定されるものでなく、窒化シリコン、窒化シリコン、酸化シリコンといった絶縁膜を単層または積層構造として用いても良い。

10

【0326】

次に、第1の絶縁膜3924上に第2の絶縁膜3925を形成する。ここで形成される第2の絶縁膜3925には、窒化シリコン、窒化酸化シリコン、酸化シリコンなどの絶縁膜を用いることができるが、本実施例では、プラズマCVD法により形成された膜厚50nmの窒化シリコン膜を用いることとする。

【0327】

次に、窒化シリコン膜からなる第2の絶縁膜3925を形成した後、熱処理(300～550で1～12時間の熱処理)を行い、半導体層を水素化する工程を行う(図23(C))。この工程は第2の絶縁膜3925に含まれる水素により半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、水素雰囲気下で350程度の熱処理や、プラズマ水素化(プラズマにより励起された水素を用いる)を行うこともできる。

20

【0328】

次に、第2の絶縁膜3925上に有機絶縁物材料からなる第3の絶縁膜3926を形成する。ここでは、膜厚1.6μmのアクリル樹脂膜を形成する。次に、各不純物領域に達するコンタクトホール3927を形成する。

【0329】

なお、本実施例で用いるアクリル樹脂は感光性アクリルであるため、露光して現像することにより所望の位置を開孔することができる。また、第1の絶縁膜3924および第2の絶縁膜3925の一部のエッティングには、ドライエッティング法を用い、第1の絶縁膜3924をエッティングストッパーとして第2の絶縁膜3925のエッティングを行ってから、第1の絶縁膜3924のエッティングを行う。これによりコンタクトホール3927を得る。

30

【0330】

なお、本実施例では、有機樹脂膜で形成された第3の絶縁膜3926を形成した後でコンタクトホールを形成する場合について説明したが、第3の絶縁膜3926を形成する前に第2の絶縁膜3925および第1の絶縁膜3924をドライエッティングすることもできる。なお、この場合には、エッティング処理後、第3の絶縁膜3926を形成する前に基板を熱処理(300～550で1～12時間の熱処理)するのが好ましい。

40

【0331】

そして、図23(D)に示すようにA1、Ti、Mo、W等を用いて配線3928を形成することにより、nチャネル型TFT3931、pチャネル型TFT3932を同一基板上に形成することができる。

【実施例14】

【0332】

本実施例では、本発明により形成された集積回路が、CPUである場合の機能および構成について図24を用いて説明する。

【0333】

50

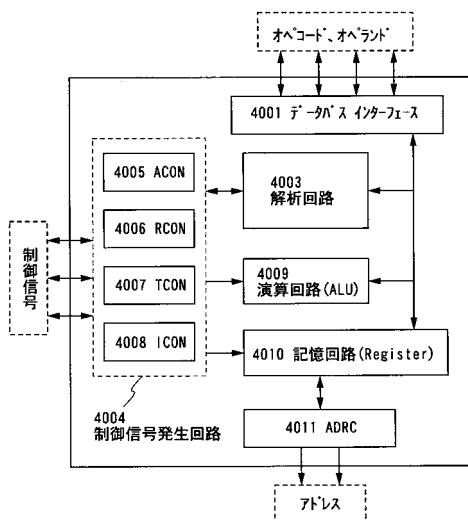

まず、オペコードがインターフェース 4001 に入力されると、解析回路 4003 (Instruction Decoderともいう)においてコードが解読され、信号が制御信号発生回路 4004 (CPU Timing Control) に入力される。信号が入力されると、制御信号発生回路 4004 から、演算回路 4009 (以下、ALUと示す)、および記憶回路 4010 (以下、Registerと示す) に制御信号が出力される。

【0334】

なお、制御信号発生回路 4004 には、ALU 4009 を制御する ALU コントローラ 4005 (以下、ACONと示す)、Register 4010 を制御する回路 4006 (以下、RCONと示す)、タイミングを制御するタイミングコントローラ 4007 (以下、TCONと示す)、および割り込みを制御する割り込みコントローラ 4008 (以下、ICONと示す) を含むものとする。 10

【0335】

一方、オペラントがインターフェース 4001 に入力されると、ALU 4009、および Register 4010 に出力される。そして、制御信号発生回路 4004 から入力された制御信号に基づく処理 (例えば、メモリリードサイクル、メモリライトサイクル、あるいは I/O リードサイクル、I/O ライトサイクル等) がなされる。

【0336】

なお、Register 4010 は、汎用レジスタ、スタックポインタ (SP)、プログラムカウンタ (PC) 等により構成される。

【0337】

また、アドレスコントローラー 4011 (以下、ADRCと示す) は、16 ビットのアドレスを出力する。 20

【0338】

なお、本実施例に示した CPU の構成は、本発明の作製方法を用いて形成される CPU の一例であり、本発明の構成を限定するものではない。従って、本実施例に示す構成以外の公知の CPU の構成を用いることも可能である。

【実施例 15】

【0339】

本実施例では、本発明の集積回路が、モジュールに組み込まれ、実際に電子機器に組み込まれる様子について、携帯電話の場合を例に挙げ、図 25 を用いて説明する。 30

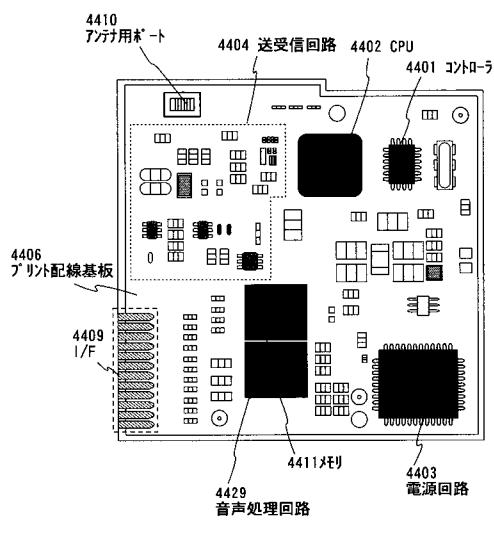

【0340】

図 25 に示す携帯電話のモジュールは、プリント配線基板 4406 に、コントローラ 4401、CPU 4402、メモリ 4411、電源回路 4403、音声処理回路 4429 及び送受信回路 4404 や、その他、抵抗、バッファ、容量素子等の素子が実装されている。なお、本発明により作製される集積回路は、コントローラ 4401、CPU 4402、メモリ 4411、電源回路 4403、音声処理回路 4429 等に用いることができる。また、ここでは、図示しないがパネルは、FPC によってプリント配線基板 4406 に実装されている。

【0341】

プリント配線基板 4406 への電源電圧及びキーボードなどから入力された各種信号は、複数の入力端子が配置されたプリント配線基板用のインターフェース (I/F) 部 4409 を介して供給される。また、アンテナとの間の信号の送受信を行うためのアンテナ用ポート 4410 が、プリント配線基板 4406 に設けられている。 40

【0342】

なお、メモリ 4411 には、VRAM、DRAM、フラッシュメモリなどが含まれている。VRAM にはパネルに表示する画像のデータが、DRAM には画像データまたは音声データが、フラッシュメモリには各種プログラムが記憶されている。

【0343】

また、電源回路 4403 では、コントローラ 4401、CPU 4402、音声処理回路 4429、メモリ 4411、送受信回路 4404 への電源電圧が生成される。またパネル 50

の仕様によっては、電源回路 4403 に電流源が備えられている場合もある。

【0344】

CPU4402 の構成については、実施例 14 で説明したので省略するが、入力された信号に基づき、各種命令を含む信号をメモリ 4411、送受信回路 4404、音声処理回路 4429、コントローラ 4401 などに送る。

【0345】