(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5100489号

(P5100489)

(45) 発行日 平成24年12月19日(2012.12.19)

(24) 登録日 平成24年10月5日(2012.10.5)

(51) Int.Cl.

HO4N 5/335 (2011.01)

F 1

HO4N 5/335

請求項の数 10 (全 18 頁)

(21) 出願番号 特願2008-117625 (P2008-117625)

(22) 出願日 平成20年4月28日 (2008.4.28)

(65) 公開番号 特開2009-267969 (P2009-267969A)

(43) 公開日 平成21年11月12日 (2009.11.12)

審査請求日 平成23年4月28日 (2011.4.28)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】撮像装置及び当該装置における信号処理方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基準クロックを発生する発振器と、

前記基準クロックに同期して水平及び垂直同期信号を発生する同期信号発生手段と、

前記基準クロック及び前記水平及び垂直同期信号に同期して第1のクロック信号と、駆動信号を含むタイミング信号とを発生するタイミング信号発生手段と、

前記駆動信号により駆動され、撮像した画像を表す画像信号を複数の第1のパラレル画素信号として出力する撮像素子と、

前記複数の第1のパラレル画素信号のそれぞれに、前記水平同期信号に同期した同期コードを付加する同期コード付加手段と、

前記同期コード付加手段により前記同期コードが付加された前記複数の第1のパラレル画素信号のそれぞれに対応して設けられ、前記第1のクロック信号に同期して前記複数の第1のパラレル画素信号のそれぞれをシリアル画素信号に変換する複数のパラレルシリアル変換手段と、

前記複数のパラレルシリアル変換手段のそれぞれから出力される前記シリアル画素信号から前記同期コードを検出したタイミングを通知する複数の検出手段と、

前記複数のパラレルシリアル変換手段のそれぞれに対応して設けられ、前記複数のパラレルシリアル変換手段のそれぞれから出力される前記シリアル画素信号を第2のパラレル画素信号に変換する複数のシリアルパラレル変換手段と、

前記複数のシリアルパラレル変換手段から出力される複数の前記第2のパラレル画素信

号について、それに対応する前記検出手段が前記同期コードを検出したタイミングに基づいて当該複数の第2のパラレル画素信号の同期を調整して、前記画像信号に対応する多値画像データを出力する調整手段と、を有することを特徴とする撮像装置。

【請求項2】

前記撮像素子から出力される前記複数の第1のパラレル画素信号のそれぞれはアナログ信号であり、

前記複数の画素信号のそれぞれに対応して設けられ、前記タイミング信号に同期して前記第1のパラレル画素信号をデジタル信号に変換する複数のA/D変換手段を更に有し、

前記同期コード付加手段は、前記複数のA/D変換手段でデジタル信号に変換された複数の前記第1のパラレル画素信号のそれぞれに前記同期コードを付加することを特徴とする請求項1に記載の撮像装置。10

【請求項3】

前記複数のシリアルパラレル変換手段のそれぞれは、対応する前記検出手段が前記同期コードを検出した後の最初の前記第2のパラレル画素信号に同期して同期フラグを出力し、

前記調整手段は、前記複数のシリアルパラレル変換手段のうちの所定のシリアルパラレル変換手段から出力される前記同期フラグのタイミングに合わせて、前記複数の第2のパラレル画素信号の同期を取ることを特徴とする請求項1又は2に記載の撮像装置。

【請求項4】

有効画像領域を示す領域情報を記憶する記憶手段と、

前記記憶手段に記憶された前記領域情報を応じて、前記調整手段から出力される前記多値画像データから有効画像領域のデータを切り出すトリミング手段を更に有することを特徴とする請求項1乃至3のいずれか1項に記載の撮像装置。20

【請求項5】

前記基準クロックの周波数よりも高い周波数の第2のクロック信号を発生するクロック発生器を更に有し、

前記調整手段は、前記第2のクロック信号に同期して前記複数の第2のパラレル画素信号の同期を調整し、前記多値画像データを出力することを特徴とする請求項1に記載の撮像装置。30

【請求項6】

基準クロックを発生する発振器と、前記基準クロックに同期して水平及び垂直同期信号を発生する同期信号発生器と、前記基準クロック及び前記水平及び垂直同期信号に同期して第1のクロック信号と、駆動信号を含むタイミング信号とを発生するタイミング信号発生器と、前記駆動信号により駆動され、撮像した画像を表す画像信号を複数の第1のパラレル画素信号として出力する撮像素子とを具備する撮像装置における信号処理方法であって、

同期コード付加器が、前記複数の第1のパラレル画素信号のそれぞれに、前記水平同期信号に同期した同期コードを付加する同期コード付加工程と、

前記同期コード付加工程において前記同期コードが付加された前記複数の第1のパラレル画素信号のそれぞれに対応して設けられた複数のパラレルシリアル変換器が、前記第1のクロック信号に同期して前記複数の第1のパラレル画素信号のそれぞれをシリアル画素信号に変換するパラレルシリアル変換工程と、40

複数の検出器が、前記複数のパラレルシリアル変換器のそれぞれから出力される前記シリアル画素信号から前記同期コードを検出したタイミングを通知する検出工程と、

前記複数のパラレルシリアル変換器のそれぞれに対応して設けられた複数のシリアルパラレル変換器が、前記複数のパラレルシリアル変換器のそれぞれから出力される前記シリアル画素信号を第2のパラレル画素信号に変換するシリアルパラレル変換工程と、

調整手段が、前記複数のシリアルパラレル変換器から出力される複数の前記第2のパラレル画素信号について、それぞれに対応する前記検出器が前記同期コードを検出したタイミングに基づいて当該複数の第2のパラレル画素信号の同期を調整して、前記画像信号に50

対応する多値画像データを出力する調整工程と、

を有することを特徴とする撮像装置における信号処理方法。

【請求項 7】

前記撮像素子から出力される前記複数の第1のパラレル画素信号のそれぞれはアナログ信号であり、

前記複数の画素信号のそれぞれに対応して設けられた複数のA/D変換器のそれぞれが、前記タイミング信号に同期して前記第1のパラレル画素信号をデジタル信号に変換するA/D変換工程を更に有し、

前記同期コード付加工工程において前記同期コード付加器は、前記複数のA/D変換器でデジタル信号に変換された複数の前記第1のパラレル画素信号のそれぞれに前記同期コードを付加することを特徴とする請求項6に記載の撮像装置における信号処理方法。

10

【請求項 8】

前記複数のシリアルパラレル変換器のそれぞれは、対応する前記検出器が前記同期コードを検出した後の最初の前記第2のパラレル画素信号に同期して同期フラグを出力し、

前記調整工程は、前記複数のシリアルパラレル変換器のうちの所定のシリアルパラレル変換器から出力される前記同期フラグのタイミングに合わせて、前記複数の第2のパラレル画素信号の同期を取ることを特徴とする請求項6又は7に記載の撮像装置における信号処理方法。

【請求項 9】

トリミング手段が、有効画像領域を示す領域情報に応じて、前記調整工程で出力される前記多値画像データから有効画像領域のデータを切り出すトリミング工程を更に有することを特徴とする請求項6乃至8のいずれか1項に記載の撮像装置における信号処理方法。

20

【請求項 10】

前記撮像装置は前記基準クロックの周波数よりも高い周波数の第2のクロック信号を発生するクロック発生器を更に有し、

前記調整工程において前記調整手段は、前記第2のクロック信号に同期して前記複数の第2のパラレル画素信号の同期を調整し、前記多値画像データを出力することを特徴とする請求項6に記載の撮像装置における信号処理方法。

【発明の詳細な説明】

【技術分野】

30

【0001】

本発明は、撮像素子から並列に出力される複数の画素信号を並行して処理する技術に関するものである。

【背景技術】

【0002】

近年、デジタルスチルカメラで撮影される画像の解像度が急速に高まり、これに伴って撮像素子（イメージセンサ）から画素データの高速な読み出しが求められている。このような高速の画素データの読み出しに対応できるセンサとして、複数のアナログデータを並行して出力できる撮像素子が使用されている。

【0003】

40

また、このアナログデータをA/D変換したデジタルデータの転送方法として、パラレルシリアル変換によりデータをシリアル化して高速に伝送する方法が知られている。このようなデータ転送方法を採用して、上述の撮像素子から出力される複数のアナログデータのそれぞれをA/D変換し、そのデジタルデータをパラレルシリアル変換して複数のシリアルデータとして伝送することが考えられる。その場合、複数のシリアルデータが並行して送信されるとため、各シリアルデータ毎の同期を取ることが重要となる。

【0004】

この同期に関する方法が特許文献1に記載されている。この文献1によれば、パラレルシリアル変換器から出力されるシリアルデータに同期コードを付加して転送する。受信側では、その同期コードを検出し、異なる系統間で検出した同期コードの検出タイミングを

50

基に、各シリアルデータの同期を取っている。

【特許文献1】特開平10-112706号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

上述した従来の方法は、パラレルシリアル変換器で変換されたシリアルデータを一旦バッファに蓄え、これを2系統の間で同期を取って読み出して伝送している。しかしながら、パラレルシリアル変換器では、シリアルクロックの周波数を安定化させるためPLL回路を用い、各系統のパラレルシリアル変換器で使用されるシリアルクロックの周波数が同じになるようにしている。そのため、複数のパラレルシリアル変換器を使用する場合にはPLL回路が異なるため各シリアルクロックは周波数が同じでも、その同期関係がなくなる。また時間軸でみると、局所的にはPLL回路のジッタの影響により、全く同一の周波数でない可能性がある。また、複数のパラレルシリアル変換器で1つのPLLを共有する構成にした場合は、PLL回路の出力クロックの周波数が高くなると複数のパラレルシリアル変換器が物理的に異なるチップの場合にクロック信号のタイミング制約を満たすのが困難となり、基板上の複数チップの配置等の制約が厳しくなる。

【0006】

本発明の目的は、このような従来の問題点を解決することにある。

【0007】

本願発明の一態様に係る撮像装置よれば、複数のパラレルシリアル変換器の各出力を受け取ってシリアルパラレル変換した多値データの同期を確実に取ることができる技術を提供できる。

【課題を解決するための手段】

【0008】

上記目的を達成するために本発明の一態様に係る撮像装置は以下のような構成を備える。即ち、

基準クロックを発生する発振器と、

前記基準クロックに同期して水平及び垂直同期信号を発生する同期信号発生手段と、

前記基準クロック及び前記水平及び垂直同期信号に同期して第1のクロック信号と、駆動信号を含むタイミング信号とを発生するタイミング信号発生手段と、

前記駆動信号により駆動され、撮像した画像を表す画像信号を複数の第1のパラレル画素信号として出力する画像素子と、

前記複数の第1のパラレル画素信号のそれぞれに、前記水平同期信号に同期した同期コードを付加する同期コード付加手段と、

前記同期コード付加手段により前記同期コードが付加された前記複数の第1のパラレル画素信号のそれぞれに対応して設けられ、前記第1のクロック信号に同期して前記複数の第1のパラレル画素信号のそれぞれをシリアル画素信号に変換する複数のパラレルシリアル変換手段と、

前記複数のパラレルシリアル変換手段のそれぞれから出力される前記シリアル画素信号から前記同期コードを検出したタイミングを通知する複数の検出手段と、

前記複数のパラレルシリアル変換手段のそれぞれに対応して設けられ、前記複数のパラレルシリアル変換手段のそれぞれから出力される前記シリアル画素信号を第2のパラレル画素信号に変換する複数のシリアルパラレル変換手段と、

前記複数のシリアルパラレル変換手段から出力される複数の前記第2のパラレル画素信号について、それに対応する前記検出手段が前記同期コードを検出したタイミングに基づいて当該複数の第2のパラレル画素信号の同期を調整して、前記画像信号に対応する多値画像データを出力する調整手段と、を有することを特徴とする。

【0009】

上記目的を達成するために本発明の一態様に係る撮像装置における信号処理方法は以下のようない工程を備える。即ち、

10

20

30

40

50

基準クロックを発生する発振器と、前記基準クロックに同期して水平及び垂直同期信号を発生する同期信号発生器と、前記基準クロック及び前記水平及び垂直同期信号に同期して第1のクロック信号と、駆動信号を含むタイミング信号とを発生するタイミング信号発生器と、前記駆動信号により駆動され、撮像した画像を表す画像信号を複数の第1のパラレル画素信号として出力する撮像素子とを具備する撮像装置における信号処理方法であつて、

同期コード付加器が、前記複数の第1のパラレル画素信号のそれぞれに、前記水平同期信号に同期した同期コードを付加する同期コード付加工程と、

前記同期コード付加工程において前記同期コードが付加された前記複数の第1のパラレル画素信号のそれぞれに対応して設けられた複数のパラレルシリアル変換器が、前記第1のクロック信号に同期して前記複数の第1のパラレル画素信号のそれぞれをシリアル画素信号に変換するパラレルシリアル変換工程と、

複数の検出器が、前記複数のパラレルシリアル変換器のそれぞれから出力される前記シリアルの画素信号から前記同期コードを検出したタイミングを通知する検出工程と、

前記複数のパラレルシリアル変換器のそれぞれに対応して設けられた複数のシリアルパラレル変換器が、前記複数のパラレルシリアル変換器のそれぞれから出力される前記シリアル画素信号を第2のパラレル画素信号に変換するシリアルパラレル変換工程と、

調整手段が、前記複数のシリアルパラレル変換器から出力される複数の前記第2のパラレル画素信号について、それぞれに対応する前記検出器が前記同期コードを検出したタイミングに基づいて当該複数の第2のパラレル画素信号の同期を調整して、前記画像信号に 20 対応する多値画像データを出力する調整工程と、

を有することを特徴とする。

#### 【発明の効果】

#### 【0010】

本発明によれば、複数のパラレルシリアル変換器の各出力を受け取ってシリアルパラレル変換した多値データの同期を確実に取ることができるという効果がある。

#### 【発明を実施するための最良の形態】

#### 【0011】

以下、添付図面を参照して本発明の好適な実施の形態を詳しく説明する。尚、以下の実施の形態は特許請求の範囲に係る本発明を限定するものでなく、また本実施の形態で説明されている特徴の組み合わせの全てが本発明の解決手段に必須のものとは限らない。

#### 【0012】

##### 【実施の形態1】

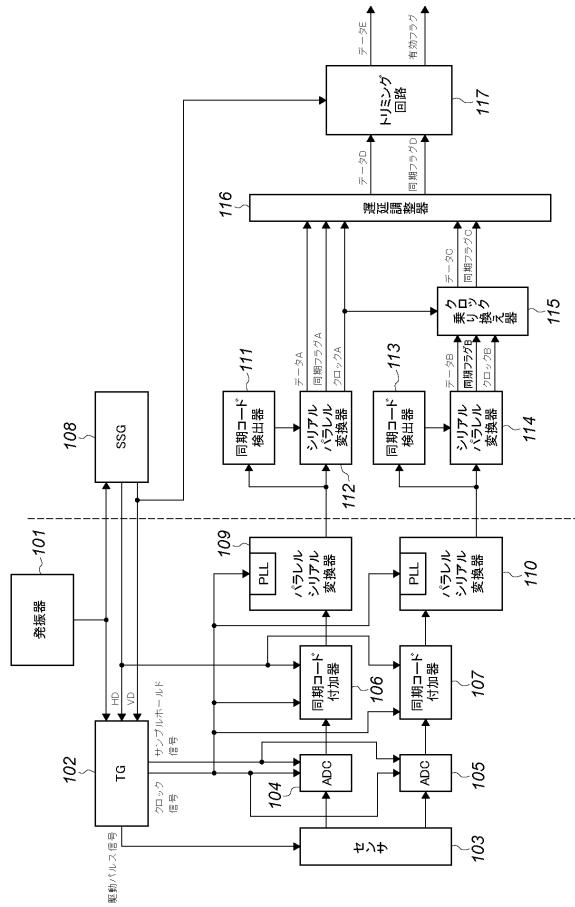

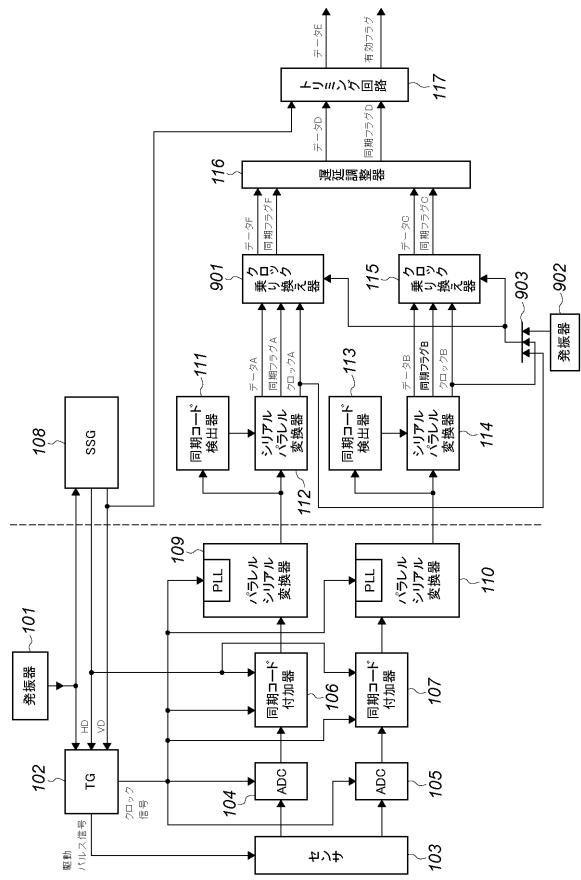

図1は、本発明の実施の形態に係る撮像装置において、撮像センサから出力される画像データの同期を取って転送するデータ転送回路の構成を説明するブロック図である。

#### 【0013】

図1において、発振器101は、動作の基準となる基準クロックを出力する。この発振器101から出力される基準クロックに基づいて、後述する各部が動作する。同期信号発生器(S SG)108は、基準クロックに同期して水平同期信号H D及び垂直同期信号V Dを出力する。タイミング信号発生器(T G)102は、S SG108から供給される同期信号H D, V Dに基づいて、センサ(撮像素子)103を駆動するための駆動パルス信号を発生する。またT G102は、A / D変換器(ADC)104, 105、同期コード付加器106, 107、パラレルシリアル変換器109, 110が動作するためのクロック信号(第1のクロック信号)を出力する。このクロック信号は、発振器101から出力される基準クロックを遅延させたクロックである。この遅延は、センサ103の出力をA / D変換器104, 105でデジタル信号に変換する際に良好なサンプリング・タイミングを得るために行われる。

#### 【0014】

センサ103は、例えばCCDやCMOSから構成される撮像素子である。このセンサ103は、その内部に、光電変換を行うフォトダイオード等の受光素子と、この受光素子

10

20

30

40

50

で得られた画素信号を T G 1 0 2 から供給される駆動パルス（駆動信号）に従って順次出力する転送路と、画素信号を増幅するアンプ等を有している。

【 0 0 1 5 】

本実施の形態に係るセンサ 1 0 3 は、撮像した画像情報をアナログ信号で出力する複数の系統を備えたセンサで、図 1 では、2 つのアナログ信号を出力しているが、このアナログ信号を出力する系統の数は、2 つに限定されるものではない。

【 0 0 1 6 】

A / D 変換器 1 0 4 , 1 0 5 はそれぞれ、T G 1 0 2 から供給されるサンプルホールドタイミング信号に従って、センサ 1 0 3 から出力されるアナログ信号をサンプリングし、それをデジタル信号に変換して出力する。ここで A / D 変換器 1 0 4 、 1 0 5 はそれぞれ 14 ビットのデジタル信号に変換する。

【 0 0 1 7 】

同期コード付加器 1 0 6 , 1 0 7 はそれぞれ、各対応する A / D 変換器 1 0 4 , 1 0 5 から出力されるデジタル信号に同期コードを付加する。この同期コードの付加は、水平同期信号 H D が出力される度に行う。パラレルシリアル変換器 1 0 9 , 1 1 0 はそれぞれ、各対応する同期コード付加器 1 0 6 , 1 0 7 から出力されるパラレルデータをシリアルデータに変換する。これらパラレルシリアル変換器 1 0 9 , 1 1 0 の各出力は、基板やケーブルを経由して同期コード検出器 1 1 1 , 1 1 3 、及びシリアルパラレル変換器 1 1 2 , 1 1 4 に供給される。ここではパラレルシリアル変換器 1 0 9 から出力されるシリアルデータは同期コード検出器 1 1 1 とシリアルパラレル変換器 1 1 2 に供給される。また、パラレルシリアル変換器 1 1 0 から出力されるシリアルデータは同期コード検出器 1 1 3 とシリアルパラレル変換器 1 1 4 に供給される。

【 0 0 1 8 】

同期コード検出器 1 1 1 , 1 1 3 はそれぞれ、入力されるシリアルデータに含まれる同期コードを検出する。そして同期コードを検出すると、各対応するシリアルパラレル変換器 1 1 2 , 1 1 4 に対して、シリアルパラレル変換したパラレルデータを出力するタイミングを知らせるタイミング信号を出力する。シリアルパラレル変換器 1 1 2 , 1 1 4 はそれぞれ、シリアルデータを入力して内部のシフトレジスタに蓄える。こうして蓄えられたシリアルデータは、各対応する同期コード検出器 1 1 1 , 1 1 3 から供給されるタイミング信号に従って、予め決められた語長毎に、パラレルデータとして出力する。こうしてシリアルパラレル変換器 1 1 2 から出力されるデータをデータ A 、シリアルパラレル変換器 1 1 4 から出力されるデータをデータ B で示している。またこのとき、同期コードに該当する部分のデータを出力する際には、その出力データが同期コードであることを示す同期フラグ（同期フラグ A , B ）も出力する。更に、シリアルデータから復元したクロック（クロック A , B ）も出力する。

【 0 0 1 9 】

クロック乗換器 1 1 5 は、シリアルパラレル変換器 1 1 4 から出力されるデータ B 及び同期フラグ B を、シリアルパラレル変換器 1 1 2 から出力されるクロック A に乗り換えて、それぞれデータ C 及び同期フラグ C として出力する。ここでは、クロック乗換器 1 1 5 は、クロック A を基準にしているが本発明はこれに限らない。例えば 2 つよりも多くの信号系統がある場合には、その中の所定のクロックを基準にしても良い。遅延調整器 1 1 6 は、シリアルパラレル変換器 1 1 2 から出力される同期フラグ A と、クロック乗換器 1 1 5 から出力される同期フラグ C とを基に 2 系統のデータ間で、クロック単位で位相を調整する。こうして遅延調整器 1 1 6 により 2 系統のデータ A , C の位相が調整されて同時化されたデータ D （多値画像データ）として同期フラグ D とともにトリミング回路 1 1 7 に出力される。トリミング回路 1 1 7 は、S S G 1 0 8 から出力される水平同期信号 V D と同期フラグ D を入力し、水平同期信号 H D , 垂直同期信号 V D に対するデータの位置を特定する。そして後段の画像信号処理部（不図示）に必要な画像領域を取り出してデータ E と、その有効領域を示す有効フラグとを出力する。

【 0 0 2 0 】

10

20

30

40

50

以上説明した図1の構成に基づいて、1フレームの画像データを取得する際の動作を説明する。

【0021】

センサ103から出力される2系統のアナログ信号は、それぞれA/D変換器104, 105でデジタル信号に変換される。次に、同期コード付加器106, 107により、このデジタル信号に対して、水平同期信号HD毎に同期コードを付加する。パラレルシリアル変換器109, 110は、こうして同期コードが付加されたデータをパラレルシリアル変換して出力する。同期コード検出器111, 113は、各対応するパラレルシリアル変換器109, 110から出力されるシリアルデータに含まれる同期コード検出してシリアルパラレル変換するタイミング信号を発生する。これによりシリアルパラレル変換器112, 114は、各対応するパラレルシリアル変換器109, 110から出力されたシリアルデータを受取ってシリアルパラレル変換するとともに、その同期フラグ及びシリアルデータから復元したクロックを出力する。クロック乗換器115は、シリアルパラレル変換器114から出力されるシリアルデータをシリアルパラレル変換器112の出力クロックに乗せ換えたデータCとして遅延調整器116に出力する。これにより、遅延調整器116の入力信号は単一のクロックに同期した信号となる。遅延調整器116は、2系統間の同期フラグのずれを基に、出力データの遅延量を調整する。こうして遅延調整器116から出力されるデータDでは、A/D変換器104, 105から出力されたデジタルデータにおける同期関係が復元されている。タイミング回路117は、垂直同期信号VDと、遅延調整器116から出力される同期フラグとをもとに、水平及び垂直同期信号HD, VDに対するデータの位置関係を復元し、後段での処理に必要な部分に有効フラグを付して出力する。10

【0022】

以上の動作により、SSG108から出力される水平及び垂直同期信号HD, VDに同期した1フレームの画像データを取り出すことができる。

【0023】

次に本実施の形態に特有の各部の動作の詳細を説明する。

【0024】

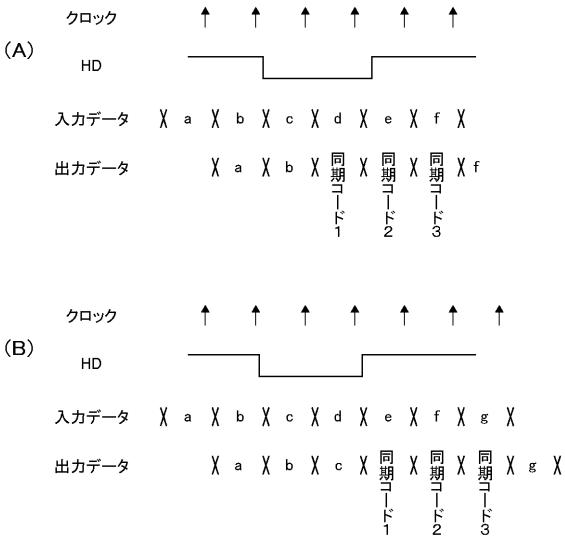

【同期コード付加器106, 107】

図2は、本実施の形態に係る同期コード付加器における同期コードの付与タイミングを説明する図である。図2において、クロックはA/D変換器104, 105のサンプリングタイミングを規定するクロック信号である。30

【0025】

図2(A)は、SSG108から出力される水平同期信号HDが立下りエッジで水平同期タイミングを示している場合の同期コードの付加例を示す。HD信号の立下りを検出すると同期コードの付加を開始し、それ以外のタイミングでは入力データを1サイクル遅延して出力データとして出力する。ここで同期コードは、同期コード1~3で構成されている。これについては詳しく後述する。

【0026】

図2(B)は、HD同期信号の立下りタイミングで有効な映像信号(図2(B)ではXc)が出力されている場合での図2(A)とは異なるタイミングでの同期コードの付加例を示す。この図2(B)では、HD同期信号の立下りから1サイクル遅れて同期コードの付加を開始している。尚、それ以外のタイミングで、入力データを1サイクル遅延して出力データとして出力している点は図2(A)と同じである。尚、図2(B)における遅延量は、有効な映像信号(Xc)と同期コードとが重ならないように複数サイクル分であってもよい。40

【0027】

ここで重要なことは、水平同期信号HDの立下りと、同期コードを付加するタイミングとの間に固定した遅延関係があることである。同期コードを付加するタイミングでは映像信号を送ることができない。このため同期コードの付加は水平ブランкиング期間等で映像50

信号が有効でない期間に付加されるように、適時 H D 同期信号の立下りから固定期間遅延したタイミング行なう。

【 0 0 2 8 】

また図 2 において、同期コードは 3 つのサイクルで付与されるものとした。これは同期コードによって、シリアルパラレル変換時のデータの位相を検出できるようにするためである。

【 0 0 2 9 】

次に、同期コードについて説明する。

【 0 0 3 0 】

例えば、16ビットのパラレルデータをパラレルシリアル変換する場合、有効画像信号領域では、データ「0x0000」「0xFFFF」を禁止にする。「0x0000」は16進コードで全て「0」の16ビットデータを示し、「0xFFFF」は16進コードで、全て「1」の16ビットデータを示している。そして { 同期コード 1 、同期コード 2 、同期コード 3 } を、{ 0x0000 , 0x0000 , 0xFFFF } といったデータの並びからなるコードとする。これにより有効画像信号領域では、「0x0000 , 0x0000」のように 32 ビット「0」が連続することはないので「0x0000 , 0x0000」によって同期コードが検出できる。またこれに引き続く「0xFFFF」によって、シリアルデータにおける同期コードの位相を検出できる。

10

【 0 0 3 1 】

また、A / D 変換器 104 , 105 が、12ビットのデジタルデータを発生する場合、同期コード付加器 106 , 107 は、12ビットのデジタルデータに4ビットのデータを付加してシリアルパラレル変換を行う16ビットの語長に拡張する。

20

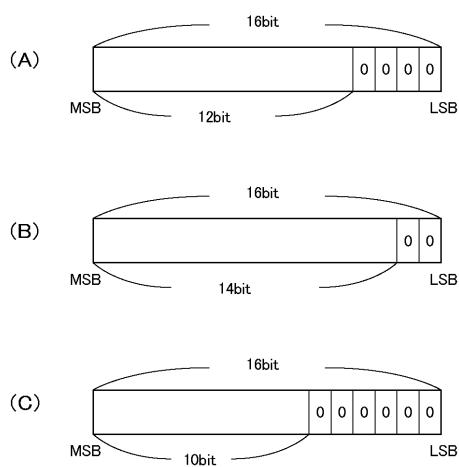

【 0 0 3 2 】

図 3 ( A ) ~ 図 3 ( C ) は、シリアルパラレル変換されたデータに含まれる有効データ部分の配置を説明する図である。

【 0 0 3 3 】

図 3 ( A ) は、シリアルパラレル変換を行う語長が 16 ビットの場合に、A / D 変換器 104 , 105 から 12 ビットのデータが出力される場合の例を示す。図 3 ( A ) では、下位の 4 ビットに「0」が付加されている。

【 0 0 3 4 】

図 3 ( B ) は、シリアルパラレル変換を行う語長が 16 ビットで、A / D 変換器 104 , 105 から出力されるデータの語長が 14 ビットの場合を示している。この場合には、下位の 2 ビットに「0」が付加されている。

30

【 0 0 3 5 】

また図 3 ( C ) は、シリアルパラレル変換を行う語長が 16 ビットで、A / D 変換器 104 , 105 から出力されるデータの語長が 10 ビットの場合を示している。この場合には、下位の 6 ビットに「0」が付加されている。

【 0 0 3 6 】

このようにして、シリアルパラレル変換する際、A / D 変換器から入力するデータのビット長と、シリアルパラレル変換するビット長とが異なる場合でも、それらの差分を調整することができる。

40

【 0 0 3 7 】

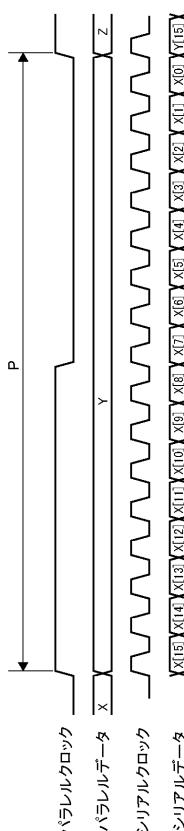

[ パラレルシリアル変換器 109 , 110 ]

本実施の形態に係るパラレルシリアル変換器 109 , 110 は、例えば 16 ビットのパラレルデータを入力し、シリアルデータに変換して出力する。

【 0 0 3 8 】

図 4 は、実施の形態に係るパラレルシリアル変換器 109 , 110 によるパラレルシリアル変換のタイミングを説明するタイミング図である。

【 0 0 3 9 】

ここでシリアルクロックは、パラレルデータの 1 クロック ( パラレルクロック ) の周期 P の 1 / 16 倍の周期を有している。即ち、シリアルクロックは、パラレルクロックの 1

50

6倍の周波数を有している。ここでは16ビットのパラレルデータXを入力した後、次のパラレルデータYを入力する周期Pで、そのパラレルデータXを16ビットのシリアルデータ(X[0], X[1], ..., X[14], X[15])に変換して出力している。

#### 【0040】

パラレルシリアル変換器109, 110のそれに含まれるPLL(Phase Locked Loop)回路は、このパラレルクロックを入力し、それを16倍して、このシリアルクロックを生成している。ここで2つの異なるPLL回路によってシリアルクロックが生成されている。従って、パラレルシリアル変換器109とパラレルシリアル変換器110のパラレルシリアル変換で使用されるシリアルクロックは周波数が同じであるが、その同期関係がなくなる。また時間軸でみると、局所的にはPLL回路のジッタの影響により、全く同一の周波数でない可能性がある。そこでパラレルシリアル変換器109, 110は、シリアルデータと、そのシリアルクロックとを対にして出力する。

#### 【0041】

##### [同期コード検出器111, 113]

同期コード検出器111, 113はそれぞれ、各対応するパラレルシリアル変換器109, 110から出力されるシリアルクロックを基に動作して、前述の同期コードの検出を行う。ここで検出する同期コードは、例えば{同期コード1、同期コード2、同期コード3} = {0x0000, 0x0000, 0xFFFF}といったデータの並びである。よって「0x0000, 0x0000」というように32ビット「0」が連続することを検出し、これに引き続いで「0xFFFF」を確認すると、シリアルデータに含まれる同期コードとその位相を検出できる。こうして同期コードを検出すると、同期コード検出器111, 113はそれぞれ、各対応するシリアルパラレル変換器112, 114に通知する。

#### 【0042】

##### [シリアルパラレル変換器112, 114]

シリアルパラレル変換器112, 114はそれぞれ、各対応するパラレルシリアル変換器109, 110から出力されるシリアルクロックとシリアルデータを入力する。そして、そのシリアルデータを、各シリアルパラレル変換器112, 114のシフトレジスタ(不図示)に格納する。そして対応する同期コード検出器111, 113が同期コードを検出したことを通知したタイミングに応じて、シフトレジスタからパラレルデータを取り出す位相を決定する。このパラレルデータの取り出しは、シリアルクロックの16周期毎に行われる。このためシリアルクロックを16分周したクロックをパラレルデータのクロック(パラレルクロック)として利用でき、シリアルパラレル変換したパラレルデータをこのパラレルクロックでラッチして出力する。

#### 【0043】

これらシリアルパラレル変換器112, 114が出力する語長は有効な語長である。例えば16ビットのデータの中に12ビットの有効な画像データが含まれている場合は、この12ビットの部分のみを出力する。即ち、前述の図3(A)の場合には、下位4ビットの「0」を除く処理を行う。また図3(B)の場合には下位2ビットを除くといった処理を実行する。

#### 【0044】

また、シリアルパラレル変換器112, 114は、各対応する同期コード検出器111, 113が同期コードを検出したことを通知した後、最初に出力するパラレルデータに同期して同期フラグとして「1」を出力する。それ以外の場合は、同期フラグとして「0」を出力する。シリアルパラレル変換器112の出力データをデータA、同期フラグを同期フラグA、出力パラレルクロックをクロックAとして図1に示す。またシリアルパラレル変換器114の出力パラレルデータをデータB、出力同期フラグを同期フラグB、出力パラレルクロックをクロックBとして図1に示す。

#### 【0045】

##### [クロック乗り換え器115]

シリアルパラレル変換器112, 114から出力されるクロックA、クロックBはそれ

10

20

30

40

50

それ、各対応するパラレルシリアル変換器 109, 110 から入力したシリアルクロックの 16 周期に相当するパラレルクロックである。前述したように、各パラレルシリアル変換器 109, 110 は、それぞれの PLL 回路でシリアルクロックを生成している。このためクロック A、クロック B はともに周波数が同じであるが同期が取れていない。また時間軸でみると局所的には、PLL 回路のジッタの影響により全く同一の周波数でない可能性がある。従って、このクロック乗り換え器 115 により、これら 2 つのパラレルクロックのズレを吸収している。

#### 【0046】

このクロック乗り換え器 115 の構成は、例えば書き込みクロックと読み出しクロックが別々に入力される FIFO で構成され、特開 2001-222407 号公報の図 2 に開示されているようにデュアルポートメモリを使用して構成することが可能である。よって、このクロック乗り換え器 115 は、データ B 及び同期フラグ B をクロック B に同期して入力し、シリアルパラレル変換器 112 から入力されるクロック A に同期してデータ C、同期フラグ C として出力する。

#### 【0047】

尚、クロック乗り換え器 115 に入力される、或はそこから出力されるデータは、データと同期フラグとで示しているが、これら両者を区別することなく連結したデータとして入出力する。つまり本実施の形態では、データ 16 ビットに同期フラグの 1 ビットが追加された 17 ビットのデータとして扱っている。

#### 【0048】

##### 【遅延調整器 116】

本実施の形態に係る遅延調整器 116 に入力されるデータ（データ A、同期フラグ A、データ C、同期フラグ C）は全てクロック A に同期して入力される。

#### 【0049】

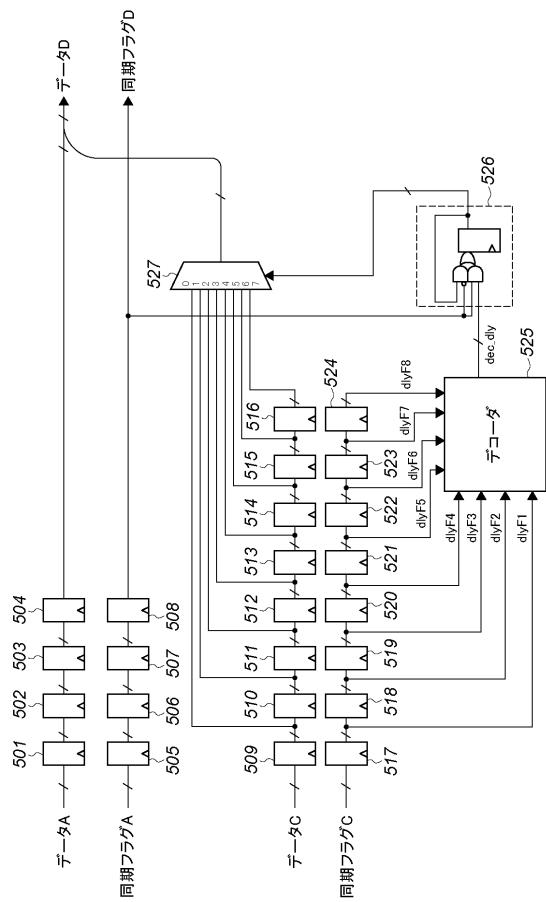

図 5 は、本実施の形態に係る遅延調整器 116 の構造を示すブロック図である。

#### 【0050】

図 5において、501～504 は入力データ A を遅延するための遅延素子である。また 505～508 は、入力した同期フラグ A を遅延するための遅延素子である。509～516 は、入力したデータ C を遅延するための遅延素子である。また 517～524 は、同期フラグ C を遅延するための遅延素子である。ここでこれら遅延素子は、フリップフロップで構成されており、それぞれパラレルクロックに同期して、入力したデータを右（出力）方向にシフトする。

#### 【0051】

デコーダ 525 は、遅延素子 517～524 の各出力入力してデコードする。ロード付き DFF（D タイプのフリップフロップ）526 は、デコーダ 525 の出力（3 ビットデータ）を遅延素子 508 の出力がハイレベルになったときにラッチする。セレクタ 527 は、ロード付き DFF 526 から出力される 3 ビットデータに応じて、遅延素子 509～516 の何れかの出力を選択する。こうしてセレクタ 527 から出力されるデータ C と、遅延素子 504 から出力されるデータ A とが連結されて 32 ビットのデータ D となり、遅延素子 508 の出力が同期フラグ D の出力となる。

#### 【0052】

図 6 は、本実施の形態に係るデコーダ 525 によるデコード例を説明する図である。

#### 【0053】

図 6において、dlyF1 から dlyF8 は、それぞれ遅延素子 517 から遅延素子 524 の出力を示している。このデコード条件は、パラレルクロックの 8 サイクルの間に 2 回、同期フラグを検出しないことを前提にしている。実際は、図 2 を参照して説明したように、同期フラグは水平同期信号 HD 毎に付加されるので、撮像センサ 103 の画素数を考えた場合に十分成り立つ条件である。

#### 【0054】

このデコード条件は、言い換えると同期フラグ C が有効、つまり「1」の同期フラグと

10

20

30

40

50

同時に入力されたデータCを保持している遅延素子509～516のいずれかの出力をセレクタ527により選択するものである。図6において、「-」は、意味のないデータであることを示している。

#### 【0055】

遅延調整器116の動作例として、有効な同期フラグAに遅れて、パラレルクロックの3クロック後に有効な同期フラグCが入力された場合を考える。この場合は、遅延素子508に有効フラグがシフトされて格納されると、ロード付きDFF526はデコーダ525の出力をラッチする。このときデコーダ525の出力は、遅延素子517の出力(dlyF1)がハイレベル「1」であるため、図6の論理表から、その出力(dec-dly)は「0」となる。これによりセレクタ527は、データCを遅延した遅延素子509にラッチされているデータを選択する。こうして選択されてセレクタ527から出力される16ビットデータと、遅延素子504から出力される16ビットデータとを連結し、データDとして出力する。

#### 【0056】

##### [トリミング回路117]

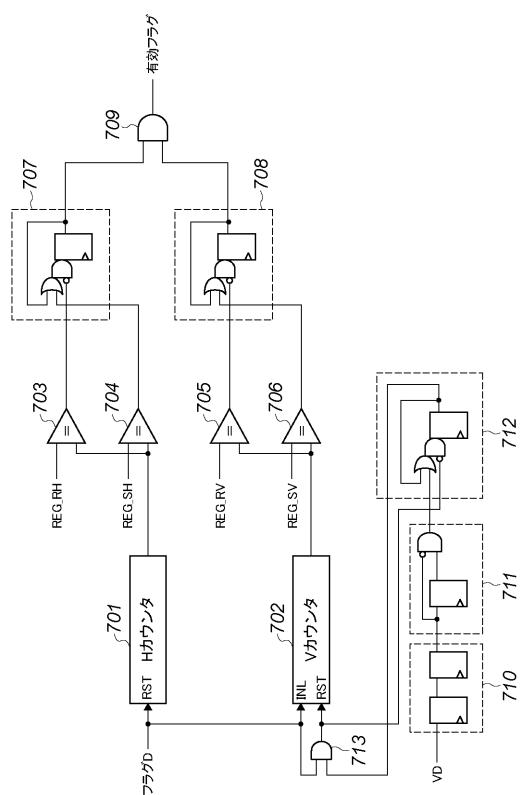

図7は、本実施の形態に係るトリミング回路117の内部構成を示すブロック図である。尚、有効画像領域を示す領域情報REG\_RH, REG\_SH, REG\_RV, REG\_SVは、レジスタ或はメモリなどに記憶されているものとする。

#### 【0057】

このトリミング回路117は、Hカウンタ701、Vカウンタ702を有し、これらカウンタ701, 702の出力をデコードすることによって図8に示す領域を有効画像領域801として取り出す。この有効画像領域801の取り出しが、データに有効フラグをつけることによって行われる。

#### 【0058】

Hカウンタ701の出力のデコードは、比較器703, 704と、リセット優先セット/リセットDFF707で行われる。またVカウンタ702の出力のデコードは、比較器705, 706とリセット優先セット/リセットDFF708で行われる。

#### 【0059】

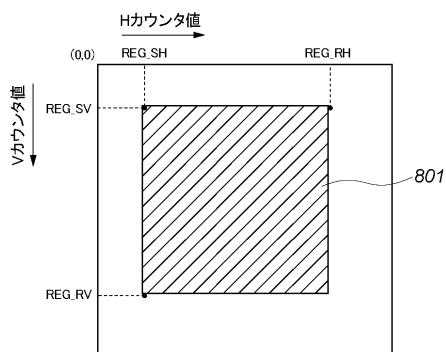

このHカウンタ701の出力のデコード結果と、Vカウンタ702の出力のデコード結果をANDゲート709で論理積をとったものが有効フラグである。尚、図7の領域情報REG\_RH, REG\_SH, REG\_RV, REG\_SVと有効画像領域801との関係は図8に示すとおりである。

#### 【0060】

図8は、画像内の有効画像領域を説明する図である。

#### 【0061】

図において、REG\_SHは有効画像領域801の左端、REG\_RHは有効画像領域801の右端に相当するHカウンタ701の値を示す。またREG\_SVは、有効画像領域801の上端に相当するVカウンタ702の値を示し、REG\_RVは、有効画像領域801の下端に相当するVカウンタ702の値を示している。

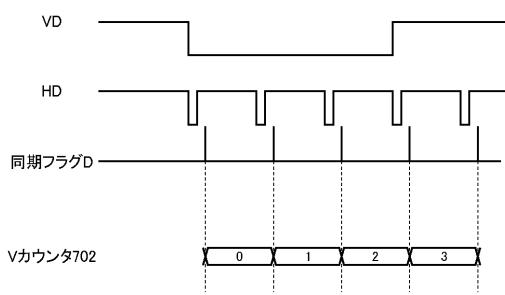

#### 【0062】

Hカウンタ701は、クロックAを入力する度にカウントアップし、同期フラグDが「1」で入力される度に「0」にリセットされる。またVカウンタ702は、クロックAで駆動され、同期フラグDが「1」のサイクルでカウントアップする。そして、垂直同期信号VDの立下りに同期フラグDが「1」になると「0」にリセットされる。ここで垂直同期信号VDは、クロックAとは非同期である。このため2段のクロックAのDFFが連なった同期化器710を通り、同期化器710の出力の立下りエッジ検出回路711の出力パルスでリセット優先セット/リセットDFF712をセットする。そして、このDFF712の出力と同期フラグDとをANDゲート713で論理積を取った信号によってVカウンタ702を「0」にリセットする。またANDゲート713の出力でDFF712をクリアする。

## 【0063】

このような動作により図9に示すように、Vカウンタ702は、垂直同期信号VDの立下りに同期して、水平同期信号HDが入力される度に1だけ増加する。

## 【0064】

図9は、本実施の形態に係るVカウンタの動作を説明するタイミング図である。

## 【0065】

上記説明はセンサ103の出力が2系統のアナログ信号である場合で説明したが、3つ以上の出力系統を有する撮像センサの場合にも同様に対応できる。

## 【0066】

以上説明したように本実施の形態1によれば、撮像センサから出力される複数系統の画像信号の同期を確実に取ることができる。 10

## 【0067】

また撮像センサから出力される複数系統の画像信号をそれぞれをシリアルデータとして出力する場合でも、複数系統の画像信号の同期を確立することができる撮像装置を提供できる。

## 【0068】

## [実施の形態2]

図10は、本発明の実施の形態2に係る撮像装置の信号処理回路を示したブロック図で、前述の図1と共に通する部分は同じ記号で示し、それらの説明を省略する。 20

## 【0069】

この実施の形態2においては、シリアルパラレル変換器112と遅延調整器116の間にクロック乗り換え器901を設け、また発振器902及びクロック選択回路903を設ける点が前述の実施の形態1の構成(図1)と異なっている。

## 【0070】

クロック選択回路903は、クロックA、クロックB、発振器902から出力されるクロックの何れかのクロックを選択する。クロック選択回路903でクロックAが選択された場合は、クロック乗り換え器901はクロックAからクロックAへの乗り換えを行い、クロック乗り換え器115はクロックBからクロックAへの乗り換えを行う。従って、前述の実施の形態1と全く同様の動作が行われる。 30

## 【0071】

次にクロック選択回路903でクロックBが選択された場合は、クロック乗り換え器901はクロックAからクロックBへの乗り換えを行い、クロック乗り換え器115はクロックBからクロックBへの乗り換えを行う。従って、前述の実施の形態1において、上下の信号系を入れ替えたに過ぎない。即ち、A/D変換器104からシリアルパラレル変換器112に至る系と、A/D変換器105からシリアルパラレル変換器114に至る系とを入れ替えたに過ぎない、よって、この場合も、前述の実施の形態1と同様の動作が行われる。

## 【0072】

次にクロック選択回路903で発振器(クロック発生器)902のクロック信号(第2のクロック信号)が選択された場合は、クロック乗り換え器901、クロック乗り換え器115は、発振器902の出力クロックへの乗り換えを行う。よって、これ以降の回路である遅延調整器116、トリミング回路117及びトリミング回路117の出力を受けて動作する信号処理回路は、発振器902の出力クロックに同期して動作する。従って、発振器902の周波数を、基準クロックの周波数の2倍以上の周波数にすることにより、トリミング回路117以降で、2つの画素が同時に入力される画像データを1サイクルで一つの画素に直列化して信号処理を行うことが可能となる。 40

## 【0073】

以上説明したように、2つのクロック乗り換え器901、115を設けることによって、トリミング回路117以降で処理するクロックの周波数を任意の周波数に設定できる。そして、その任意の周波数を例えば、基準クロックの周波数の整数倍の周波数とすること 50

により、それら整数倍の画素データを1サイクルで処理できるようになるため、その回路規模を削減することができる。

#### 【0074】

また本実施の形態2によれば、複数のパラレルシリアル変換器の間のクロックのスキュー やジッタによるずれを吸収できるので、複数のパラレルシリアル変換器間でPLLを共有する必要がなくなり、パラレルシリアル変換器の数を容易に増やすことができる。

#### 【0075】

また本実施の形態2によれば、遅延調整器の以降の処理回路のクロック周波数を任意の周波数に設定できる。これにより、例えば、撮像センサから出力される信号の系統が2つある場合、その任意の周波数を、それまでの基準クロックの周波数の2倍の周波数にすることによって、その任意の周波数の1サイクルで2つの画素データを処理できることになる。これにより、1系統の信号処理系統で複数の画素データを並行して多値データとして出力できるため、その回路規模を削減できる。

#### 【0076】

##### (他の実施形態)

以上、本発明の実施形態について詳述したが、本発明は、複数の機器から構成されるシステムに適用しても良いし、また一つの機器からなる装置に適用しても良い。

#### 【0077】

なお、本発明は、前述した実施形態に係る信号処理方法を実現するソフトウェアのプログラムを、システム或いは装置に直接或いは遠隔から供給し、そのシステム或いは装置のコンピュータが該供給されたプログラムを読み出して実行することによっても達成され得る。その場合、プログラムの機能を有していれば、形態は、プログラムである必要はない。

#### 【0078】

従って、本発明の機能処理をコンピュータで実現するために、該コンピュータにインストールされるプログラムコード自体も本発明を実現するものである。つまり、本発明のクレームでは、本発明の機能処理を実現するためのコンピュータプログラム自体も含まれる。その場合、プログラムの機能を有していれば、オブジェクトコード、インタプリタにより実行されるプログラム、OSに供給するスクリプトデータ等、プログラムの形態を問わない。

#### 【0079】

プログラムを供給するための記録媒体としては、様々なものが使用できる。例えば、フロッピー(登録商標)ディスク、ハードディスク、光ディスク、光磁気ディスク、MO、CD-ROM、CD-R、CD-RW、磁気テープ、不揮発性のメモリカード、ROM、DVD(DVD-ROM, DVD-R)などである。

#### 【0080】

その他、プログラムの供給方法としては、クライアントコンピュータのブラウザを用いてインターネットのホームページに接続し、該ホームページからハードディスク等の記録媒体にダウンロードすることによっても供給できる。その場合、ダウンロードされるのは、本発明のコンピュータプログラムそのもの、もしくは圧縮され自動インストール機能を含むファイルであってもよい。また、本発明のプログラムを構成するプログラムコードを複数のファイルに分割し、それぞれのファイルを異なるホームページからダウンロードすることによっても実現可能である。つまり、本発明の機能処理をコンピュータで実現するためのプログラムファイルを複数のユーザに対してダウンロードさせるWWWサーバも、本発明のクレームに含まれるものである。

#### 【0081】

また、本発明のプログラムを暗号化してCD-ROM等の記憶媒体に格納してユーザに配布する形態としても良い。その場合、所定の条件をクリアしたユーザに対し、インターネットを介してホームページから暗号化を解く鍵情報をダウンロードさせ、その鍵情報を使用することにより暗号化されたプログラムが実行可能な形式でコンピュータにインスト

10

20

30

40

50

ールされるようとする。

【0082】

また、コンピュータが、読み出したプログラムを実行することによって、前述した実施形態の機能が実現される形態以外の形態でも実現可能である。例えば、そのプログラムの指示に基づき、コンピュータ上で稼動しているOSなどが、実際の処理の一部または全部を行ない、その処理によっても前述した実施形態の機能が実現され得る。

【0083】

更に、記録媒体から読み出されたプログラムが、コンピュータに挿入された機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに書き込まれるようにしてもよい。この場合、その後で、そのプログラムの指示に基づき、その機能拡張ボードや機能拡張ユニットに備わるCPUなどが実際の処理の一部または全部を行ない、その処理によって前述した実施形態の機能が実現される。

【図面の簡単な説明】

【0084】

【図1】本発明の実施の形態に係る撮像装置において、撮像センサから出力される画像データの同期を取って転送するデータ転送回路の構成を説明するブロック図である。

【図2】本実施の形態に係る同期コード付加器における同期コードの付与タイミングを説明する図である。

【図3】シリアルパラレル変換されたデータに含まれる有効データ部分の配置を説明する図である。

【図4】実施の形態に係るパラレルシリアル変換器によるパラレルシリアル変換のタイミングを説明するタイミング図である。

【図5】本実施の形態に係る遅延調整器の構造を示すブロック図である。

【図6】本実施の形態に係るデコーダによるデコード例を説明する図である。

【図7】本実施の形態に係るトリミング回路の内部構成を示すブロック図である。

【図8】画像内の有効領域を説明する図である。

【図9】本実施の形態に係るVカウンタの動作を説明するタイミング図である。

【図10】本発明の実施の形態2に係る撮像装置の信号処理回路を示したブロック図である。

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

| dlyF1 | dlyF2 | dlyF3 | dlyF4 | dlyF5 | dlyF6 | dlyF7 | dlyF8 | dec_dly |

|-------|-------|-------|-------|-------|-------|-------|-------|---------|

| 1     | -     | -     | -     | -     | -     | -     | -     | 0       |

| 0     | 1     | -     | -     | -     | -     | -     | -     | 1       |

| 0     | 0     | 1     | -     | -     | -     | -     | -     | 2       |

| 0     | 0     | 0     | 1     | -     | -     | -     | -     | 3       |

| 0     | 0     | 0     | 0     | 1     | -     | -     | -     | 4       |

| 0     | 0     | 0     | 0     | 0     | 1     | -     | -     | 5       |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | -     | 6       |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 7       |

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 蓮覚寺 秀行

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 木方 庸輔

(56)参考文献 特開2006-352426 (JP, A)

特開2005-244709 (JP, A)

特開平10-112706 (JP, A)

特開平05-095566 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/335