### (19) United States

# (12) Patent Application Publication

Furukawa et al.

(10) Pub. No.: US 2008/0102566 A1 May 1, 2008 (43) Pub. Date:

### (54) MULTIPLE LAYER AND CRYSTAL PLANE ORIENTATION SEMICONDUCTOR **SUBSTRATE**

Inventors: Toshiharu Furukawa, Essex Junction, VT (US); David V. Horak, Essex Junction, VT (US); Charles W. Koburger III, Delmar, NY (US);

Leathen Shi, Yorktown Heights, NY

(US)

Correspondence Address: SCHMEISER, OLSEN & WATTS 22 CENTURY HILL DRIVE **SUITE 302 LATHAM, NY 12110 (US)**

(21) Appl. No.: 11/969,279

(22) Filed: Jan. 4, 2008

### Related U.S. Application Data

(62) Division of application No. 10/906,557, filed on Feb. 24, 2005.

### **Publication Classification**

(51) Int. Cl. H01L 21/336 (2006.01)H01L 21/84 (2006.01)

(52)U.S. Cl. .... ......... 438/150; 438/459; 257/E21; 257/E21

#### (57)ABSTRACT

A semiconductor on insulator substrate and a method of fabricating the substrate. The substrate including: a first crystalline semiconductor layer and a second crystalline semiconductor layer; and an insulating layer bonding a bottom surface of the first crystalline semiconductor layer to a top surface of the second crystalline semiconductor layer, a first crystal direction of the first crystalline semiconductor layer aligned relative to a second crystal direction of the second crystalline semiconductor layer, the first crystal direction different from the second crystal direction.

**FIG.** 1

*FIG. 2*

*FIG. 3E*

**FIG.** 4

*FIG.* 5

## MULTIPLE LAYER AND CRYSTAL PLANE ORIENTATION SEMICONDUCTOR SUBSTRATE

[0001] This application is a Division of and claims priority of copending U.S. patent application Ser. No. 10/906,557 filed on Feb. 24, 2005.

#### FIELD OF THE INVENTION

[0002] The present invention relates to the field of semiconductor substrates; more specifically, it relates a method of fabricating a semiconductor substrate having multiple crystalline layers with different crystal plane orientations.

#### BACKGROUND OF THE INVENTION

[0003] In advanced semiconductor devices, individual devices such as transistors are positioned on semiconductor substrates relative to the crystal orientation of the substrate in order to take advantage of the fact that certain device parameters change based on the alignment of device structures relative to the crystal planes of the substrate. However, this often leads to integrated circuit chip edges that are no longer aligned to preferred crystal cleavage planes of the substrate, making dicing of the substrate into individual integrated circuit chips difficult and often resulting in wafer breakage. What is needed is a semiconductor substrate and a method of fabricating the substrate that allows device structures that take advantage of particular crystal plane alignments that at the same time can be easily diced into individual integrated circuit chips.

### SUMMARY OF THE INVENTION

[0004] A semiconductor substrate of the present invention comprises an insulating layer between an upper semiconductor layer and a lower semiconductor layer. A first crystal direction in the upper layer is rotationally displaced from a second crystal direction in the lower semiconductor layer. The edges of integrated circuit chips formed in the upper semiconductor layer are aligned to the second crystal direction to enhance dicing while some or all of devices formed in the integrated circuit chips have structures aligned to the first crystal direction.

[0005] A first aspect of the present invention is a substrate, comprising: a first crystalline semiconductor layer and a second crystalline semiconductor layer; and an insulating layer bonding a bottom surface of the first crystalline semiconductor layer to a top surface of the second crystalline semiconductor layer, a first crystal direction of the first crystalline semiconductor layer aligned relative to a second crystal direction of the second crystalline semiconductor layer, the first crystal direction different from the second crystal direction.

[0006] A second aspect of the present invention is a method of fabricating a substrate, comprising: providing a first crystalline semiconductor substrate, providing a second crystalline semiconductor substrate; aligning a first crystal direction of the first crystalline semiconductor substrate to a second crystal direction of the second crystalline semiconductor substrate, the first crystal direction different from the second crystal direction; and forming an insulating layer between a bottom surface of the first crystalline semiconductor substrate and a top surface of the second crystalline semiconductor substrate, the insulating layer bonding the

first crystalline semiconductor substrate to the second crystalline semiconductor substrate,

[0007] A third aspect of the present invention is an integrated circuit chip, comprising: a first crystalline semiconductor layer and a second crystalline semiconductor layer; an insulating layer bonding a bottom surface of the first crystalline semiconductor layer to a top surface of the second crystalline semiconductor layer, a first crystal direction of the first crystalline semiconductor layer aligned relative to a second crystal direction of the second crystalline semiconductor layer, the first crystal direction different from the second crystal direction; a field effect transistor comprising a source region, a drain region and a channel region separating the source and drain regions, the source, drain and a channel regions formed in the first crystalline semiconductor layer, a lengthwise direction of the channel extending between the source and drain regions aligned with both the first and the second directions; and at least one edge of the integrated circuit chip aligned with the second direc-

[0008] A fourth aspect of the present invention is a method of fabricating an integrated circuit chip, comprising: providing a semiconductor-on-insulator substrate comprising a first crystalline semiconductor layer and a second crystalline semiconductor layer, a first crystal direction of the first crystalline semiconductor substrate aligned relative to a second crystal direction of the second crystalline semiconductor substrate, the first crystal direction different from the second crystal direction, an insulating layer formed between a bottom surface of the first crystalline semiconductor substrate and a top surface of the second crystalline semiconductor substrate, the insulating layer bonding the first crystalline semiconductor substrate to the second crystalline semiconductor; forming a field effect transistor comprising a source region, a drain region and a channel region separating the source and drain regions, the source, drain and a channel regions formed in the first crystalline semiconductor layer, a lengthwise direction of the channel extending between the source and drain regions aligned with both the first and the second directions; and dicing the semiconductor-on-insulator substrate along the second direction to form at least one edge of the integrated circuit chip.

### BRIEF DESCRIPTION OF DRAWINGS

[0009] The features of the invention are set forth in the appended claims. The invention itself, however, will be best understood by reference to the following detailed description of an illustrative embodiment when read in conjunction with the accompanying drawings, wherein:

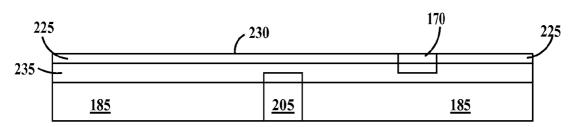

[0010] FIG. 1 is a top view of an exemplary  $\{100\}$  surfaced semiconductor substrate;

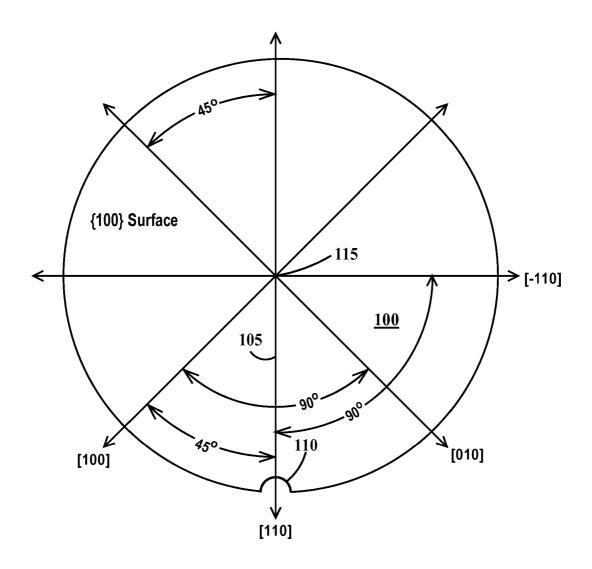

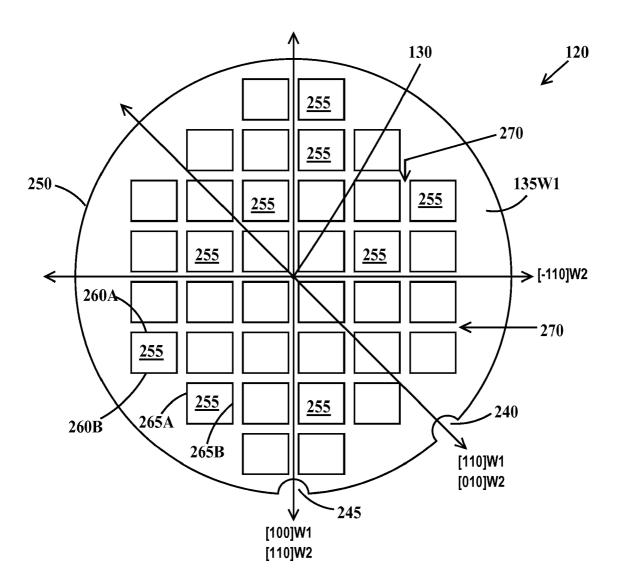

[0011] FIG. 2 illustrates an exemplary semiconductor substrate according to the present invention;

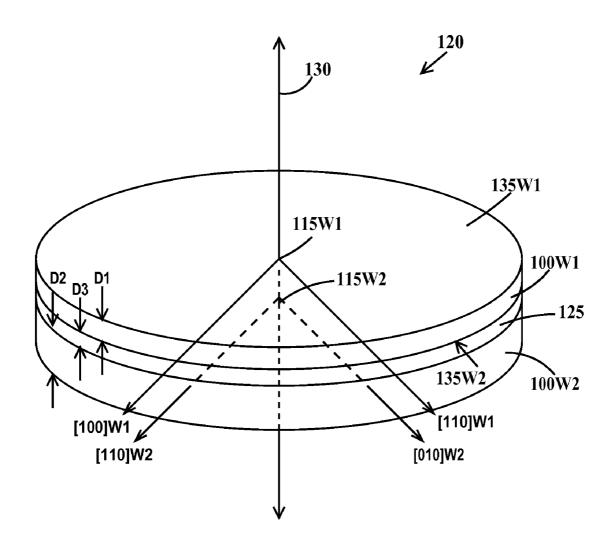

[0012] FIGS. 3A through 3E are side views of the fabrication of an exemplary semiconductor substrate according to the present invention;

[0013] FIG. 4 is a top view illustrating alignment of integrated circuit chips on the semiconductor substrate of FIG. 2; and

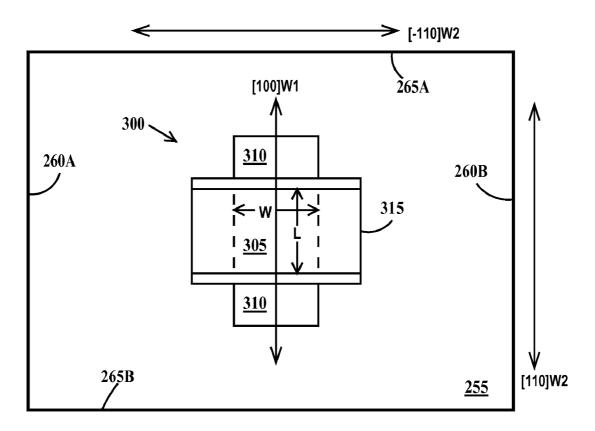

[0014] FIG. 5 is a top view illustrating alignment of a first type of device to an integrated circuit chip fabricated on a semiconductor substrate according to the present invention; and

## DETAILED DESCRIPTION OF THE INVENTION

[0015] For the purposes of the present invention, the term wafer should be considered as and exemplary version of the more general term substrate.

[0016] In crystalline solids, the atoms which make up the solid are spatially arranged in a periodic fashion called a lattice. A crystal lattice contains a volume, which is representative of the entire lattice and is regularly repeated throughout the crystal. In describing crystalline semiconductor materials in the present disclosure, the following conventions will be used:

[0017] The directions in a lattice are expressed as a set of three integers with the same relationship as the components of a vector in that direction. For example, in cubic lattices, such as silicon, that has a diamond crystal lattice, a body diagonal exists along the [111] direction with the [] brackets denoting a specific direction. Many directions in a crystal lattice are equivalent by a symmetry transformation, depending upon the arbitrary choice of orientation axes. For example, crystal directions in the cubic lattice [100], [010] and [001] are all crystallographically equivalent. A direction and all its equivalent directions are denoted by <> brackets. Thus, the designation of the <100> direction includes the equivalent [100], [010] and [001] positive directions as well as the equivalent negative directions [-100], [0-10] and [00-1].

[0018] Planes in a crystal may also be identified with a set of three integers. They are used to define a set of parallel planes and each set of integers enclosed in ( ) parentheses identifies a specific plane. For example the proper designation for a crystal plane perpendicular to the [100] direction is (100). Thus, if either a direction or a plane of a cubic lattice is known, its perpendicular counterpart may be quickly determined without calculation. Many planes in a crystal lattice are equivalent by a symmetry transformation, depending upon the arbitrary choice of orientation axes. For example, the (100), (010) and (001) planes are all crystallographically equivalent. A plane and all its equivalent planes are denoted by {} parentheses. Thus, the designation of the {100} plane includes the equivalent (100), (010) and (001) positive planes as well as the equivalent planes (-100), (0-10) and (00-1).

[0019] FIG. 1 is a top view of an exemplary {100} surfaced semiconductor substrate. In FIG. 1, a [100] direction of a {100} silicon substrate 100 is seen to be rotated 45° from a

[0020] crystal direction. A [010] crystal direction is seen to be rotated 90° from the [100] crystal direction and 45° from the [110] crystal direction. A [-110] crystal direction is seen to be rotated 90° from the [110] crystal direction. A line 105 passing through a notch 110 in the edge of substrate 100 and a center 115 of the substrate marks the [110] direction. Inversion carrier flow is affected by the crystal orientation of the channel of a field effect transistor (FET). For {100} surfaced substrates the mobility of the electrons (inversion carriers) in the channels of NFETs is relatively unaffected by choice of channel direction between the <100> crystal directions and the <110> crystal directions.

[0021] The mobility of holes (inversion carriers) in the channels of PFETs is highest in <100> crystal directions and significantly lower in <110> directions.

[0022] In one method of dicing silicon wafers, a dicing saw is used to scribe a line into the silicon wafer between integrated chips and then the wafer cleaved along these scribed lines. In another method, the dicing saw is used to cut completely through the silicon wafer. However, crystalline silicon wafers have a preferred cleavage planes and are most easily and cleanly broken or cut along {110} crystal planes.

[0023] FIG. 2 illustrates an exemplary semiconductor substrate 120 according to the present invention. In FIG. 2, a {110} crystalline silicon layer 100W1 is bonded to a {100} crystalline silicon layer 100W2 by an insulating layer 125. A central vertical axis 130 is perpendicular to top surfaces 135W1 and 135W2 of silicon layers 100W1 and 100W2 respectively. Top surface 135W1 is also the top surface of semiconductor substrate 120. Semiconductor devices, such as transistors, are intended to be formed in silicon layer 100W1 and/or on top surface 135W1.

[0024] Vertical axis 130 passes through centers 115W1 and 115W2 of respective silicon layers 100W1 and 100W2. The [100] and [110] crystal directions of silicon layer 100W1 are designated as [100]W1 and [110]W1 respectively. The [010] and [110] crystal directions of silicon layer 100W2 are designated as [100]W2 and [110]W2 respectively. Crystal direction [100]W1 is aligned to crystal direction [110]W2 and crystal direction [110]W1 is aligned to crystal direction [010] W2 Another way of stating the relation ship between the crystal directions of silicon layers 100W1 and 100W2 is that (a first) crystal direction [100]W1 is rotated 45° about axis 130 relative to (a second) crystal direction [100]W2.

[0025] The particular crystal plane alignment illustrated in FIG. 2 and described supra, should be considered exemplary and many variations are possible. For example, instead of two different crystal directions (for example, the [100] and [110] crystal directions) in two different silicon layers being aligned, the same crystal directions (for example, the [100] and [100] crystal directions) in the two different silicon layers may be rotationally offset from one another by a pre-selected angle of rotation about a vertical axis running through the centers of both wafers. Additionally, different orientation silicon layers may be used. For example silicon layer 100W1 may be a {111} crystalline silicon layer and silicon layer 100W2 may be a {100} crystalline silicon layer. Further, one or both of silicon layers 100W1 and 100W2 may be replaced with a layer comprising a group III-V semiconductor material such as GaAs, GaP, GaSb, InP, In As, InSb

[0026] First silicon layer 100W1 has a thickness D1, second silicon layer 100W2 has a thickness D2 and insulating layer 125 has a thickness D3. In one example, D1 is between about 10 nm and about 100 nm, D2 is greater than about 700 microns and D3 is between about 5 nm and about 1000 nm, preferably between 50 nm and 250 nm. In one example, insulating layer 125 comprises silicon oxide.

[0027] FIGS. 3A through 3E are side views of the fabrication of an exemplary semiconductor substrate according to the present invention. In FIG. 3A, a first silicon wafer 150 has a top surface 155, a bottom surface 160 and an edge 165. A notch 170 is formed in wafer 150. A silicon dioxide layer 175 having a thickness between about 0.5 nm to about 200

nm is formed on top surface 155 of wafer 150. A hydrogen ion implantation performed to form a hydrogen rich layer 180 in wafer 150.

[0028] In FIG. 3B, a second silicon wafer 185 has a top surface 190, a bottom surface 195 and an edge 200. A notch 205 is formed in wafer 185. A silicon dioxide layer 210 having a thickness between about 0.5 nm to about 200 nm is formed on top surface 190 of wafer 185. Oxide layers 175 and 210 are cleaned, edges 165 and 200 are aligned oxide layers 175 and 200 are brought into contact. Notches 170 and 205 serve to locate particular crystal planes in respective wafers 150 and 185.

[0029] In FIG. 3C, wafers 150 and 185 (while in contact) are heated to a temperature of about 400° C. or greater. Hydrogen rich layer 180 (see FIG. 3B) is brittle and an upper layer of wafer 150 is cleaved off leaving a silicon layer 215, having a rough top surface 220.

[0030] For many applications the remainder of wafer 150 still attached to wafer 185 is too thick and/or has too rough a surface and needs to be planarized and/or thinned. In FIG. 3D, a chemical mechanical polishing (CMP) process is performed to form a thin silicon layer 225 having a planer top surface 230. In one example, silicon layer 225 has a thickness between about 5 nm to about 100 nm

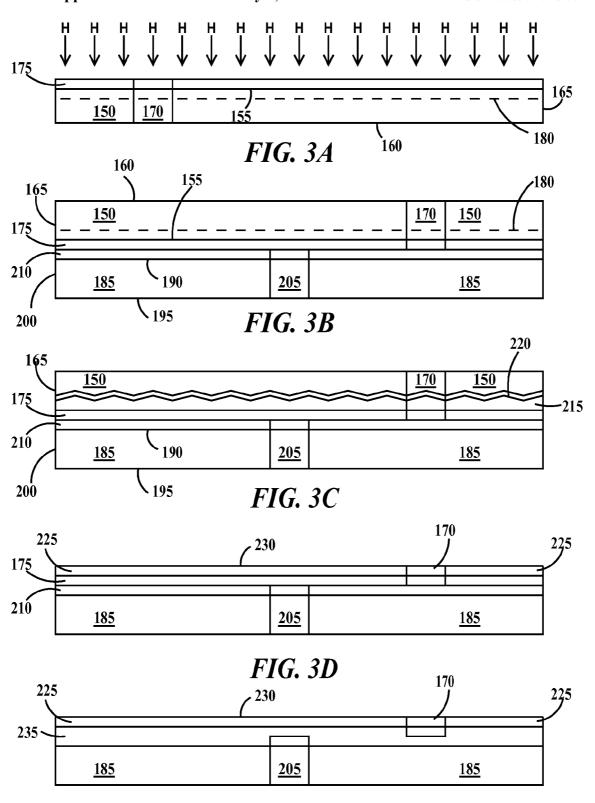

[0031] In FIG. 3E, wafers 150 and 185 are heated, for example to about 1000° C. in hydrogen in order to merge oxide layers 175 and 210 (see FIG. 3D) into a silicon dioxide layer 235 which bonds the wafers together. In one example, silicon dioxide layer 235 has thickness between about 5 nm to about 500 nm. The structure illustrated in FIG. 3E is a silicon on insulator (SOI) substrate.

[0032] FIG. 4 is a top view illustrating alignment of integrated circuit chips on semiconductor substrate 120 of FIG. 2. In FIG. 4, substrate 120 has notches 240 and 245 formed in an edge 250 of the substrate. A line passing through central axis 130 and notch 240 locates the [110]W1 and [010]W2 crystal directions which are co-aligned. A line passing through central axis 130 and notch 245 locates the [100]W1 and [110]W2 crystal directions which are coaligned. A multiplicity of integrated circuit chips 255 are formed on top surface 135W1. A first set of parallel edges 260A and 260B of integrated circuit chips 255 are parallel to crystal direction [-110]W2, a second set of parallel edges 265A and 265B of integrated circuit chips 255 are parallel to crystal direction [110]W2 (and crystal direction [100]W1). Spaces 270 between integrated circuit chips 255 form a dicing kerf where a dicing saw will cut substrate 120 to separate individual integrated circuit chips.

[0033] It should be noted that the dicing kerf is aligned with lower silicon layer 100W2 (see FIG. 2) which is the thicker layer of substrate 120 (see description supra) and the preferred cleavage planes of the lower silicon layer, while critical structures of devices formed in integrated circuit chips 255 may be printed aligned to crystal direction [100] W1 and still be aligned with edges 260A and 260B as illustrated in FIG. 5 described infra.

[0034] FIG. 5 is a top view illustrating alignment of a first type of device to an integrated circuit chip fabricated on a semiconductor substrate according to the present invention. In FIG. 5, a complementary metal oxide silicon (CMOS) PFET 300 comprises a silicon channel region 305 and

source/drain regions 310 formed in silicon layer 100W1 (see FIG. 2) and a gate 315 formed over channel region 305. A gate dielectric (not shown) is formed under gate 315. Channel region 305 has a length "L" measured between source/drain regions 310 and a width "W" perpendicular to the channel length. Edges 265A and 265B are aligned with the [-110]W2 crystal direction and edges 270A and 270B are aligned with the [110]W2 crystal direction providing improved dicing characteristics. The length "L" of channel region 305 is aligned with the [100]W1 crystal direction, which provides maximum inversion carrier mobility for a PFET as well as with edges 260A and 260B. Improved printability of images during fabrication of PFET 300 and maximum device density of devices result as well.

[0035] The description of the embodiments of the present invention is given above for the understanding of the present invention. It will be understood that the invention is not limited to the particular embodiments described herein, but is capable of various modifications, rearrangements and substitutions as will now become apparent to those skilled in the art without departing from the scope of the invention. For example, locating flats instead of locating notches or combinations of locating notches and locating flats may be used to locate the crystal directions. Therefore, it is intended that the following claims cover all such modifications and changes as fall within the true spirit and scope of the invention.

What is claimed is:

1. A method of fabricating a substrate, comprising: providing a first crystalline semiconductor substrate,

providing a second crystalline semiconductor substrate;

aligning a first crystal direction of said first crystalline semiconductor substrate to a second crystal direction of said second crystalline semiconductor substrate, said first crystal direction different from said second crystal direction; and

forming an insulating layer between a bottom surface of said first crystalline semiconductor substrate and a top surface of said second crystalline semiconductor substrate, said insulating layer bonding said first crystalline semiconductor substrate to said second crystalline semiconductor substrate.

- 2. The method of claim 1, wherein said first and second s crystalline semiconductor substrates each comprise silicon.

- 3. The method of claim 1, wherein said first and second crystal directions are co-aligned.

- **4**. The method of claim 3, wherein first and second crystalline semiconductors each comprise {100} silicon and said first crystal direction is a [100] direction and said second crystal direction is a [110] direction.

- 5. The method of claim 1, wherein inversion carriers have a higher mobility in said first crystal direction than any other direction in said first crystalline semiconductor substrate and a crystal plane perpendicular to said second crystal direction is more easily cleaved than any other crystal plane perpendicular to any other crystal direction in said second crystalline semiconductor substrate.

- **6**. The method of claim 1, wherein said insulating layer comprises silicon oxide.

- 7. The method of claim 1, further including thinning said first crystalline semiconductor substrate.

- **8**. The method of claim 6, wherein said first crystalline semiconductor substrate has a thickness of between about 10 nm to about 100 nm and said insulating layer has a thickness of between about 5 nm to about 500 nm.

- **9.** A method of fabricating an integrated circuit chip, comprising:

providing a semiconductor-on-insulator substrate comprising a first crystalline semiconductor layer and a second crystalline semiconductor layer, a first crystal direction of said first crystalline semiconductor substrate aligned relative to a second crystal direction of said second crystalline semiconductor substrate, said first crystal direction different from said second crystal direction, an insulating layer formed between a bottom surface of said first crystalline semiconductor substrate and a top surface of said second crystalline semiconductor substrate, said insulating layer bonding said first crystalline semiconductor substrate to said second crystalline semiconductor;

forming a field effect transistor comprising a source region, a drain region and a channel region separating said source and drain regions, said source, drain and a channel regions formed in said first crystalline semiconductor layer, a lengthwise direction of said channel extending between said source and drain regions aligned with both said first and said second directions; and

- dicing said semiconductor-on-insulator substrate along said second direction to form at least one edge of said integrated circuit chip.

- 10. The method of claim 9, wherein said first and second crystalline semiconductor layers each comprise silicon.

- 11. The method of claim 9, wherein said first and second crystal directions are co-aligned.

- 12. The method of claim 11, wherein first and second crystalline semiconductors each comprise {100} silicon and said first crystal direction is a [110] direction and said second crystal direction is a [100] direction.

- 13. The method of claim 11, wherein inversion carriers in said channel region have a higher mobility in said first crystal direction than any other direction in said first crystalline semiconductor layer and a crystal plane perpendicular to said second crystal direction is more easily cleaved than any other crystal plane perpendicular to any other crystal direction in said second crystalline semiconductor layer.

- **14**. The method of claim 11, wherein said insulating layer comprises silicon oxide.

- 15. The method of claim 11, wherein said first crystalline semiconductor layer has a thickness of between about 10 nm to about 100 nm and said insulating layer has a thickness of between about 5 nm to about 500 nm.

\* \* \* \* \*