(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4565700号

(P4565700)

(45) 発行日 平成22年10月20日(2010.10.20)

(24) 登録日 平成22年8月13日(2010.8.13)

(51) Int.Cl.

F 1

H01L 21/8244 (2006.01)

H01L 27/10 381

H01L 27/11 (2006.01)

H01L 27/10 471

H01L 27/10 (2006.01)

請求項の数 16 (全 18 頁)

(21) 出願番号 特願2000-132848 (P2000-132848)

(22) 出願日 平成12年4月27日 (2000.4.27)

(65) 公開番号 特開2001-28401 (P2001-28401A)

(43) 公開日 平成13年1月30日 (2001.1.30)

審査請求日 平成19年4月25日 (2007.4.25)

(31) 優先権主張番号 特願平11-130945

(32) 優先日 平成11年5月12日 (1999.5.12)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100080001

弁理士 筒井 大和

(74) 代理人 100075096

弁理士 作田 康夫

(72) 発明者 長田 健一

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者 南 正隆

東京都小平市上水本町五丁目20番1号

株式会社日立製作所半導体グループ内

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1および第2ビット線と、

複数のワード線と、

複数のメモリセルと、

前記第1および第2ビット線と並んで配置される第1Pウエル領域と、

前記第1および第2ビット線と並んで配置される第2Pウエル領域と、

前記第1Pウエル領域と前記第2Pウエル領域との間に配置されるNウエル領域と、

前記第1および第2Pウエル領域に第1電位を供給する第1配線と、

前記Nウエル領域に第2電位を供給する第2配線とを有し、

前記複数のメモリセルの各々は、第1Nチャネル型MOSトランジスタおよび第1Pチャネル型MOSトランジスタを含む第1インバータと、第2Nチャネル型MOSトランジスタおよび第2Pチャネル型MOSトランジスタを含み、その入力端子が前記第1インバータの出力端子に接続され、その出力端子が前記第1インバータの入力端子に接続された第2インバータと、ソース・ドレイン経路を前記第1インバータの出力端子と前記第1ビット線との間に有する第3Nチャネル型MOSトランジスタと、ソース・ドレイン経路を前記第2インバータの出力端子と前記第2ビット線との間に有する第4Nチャネル型MOSトランジスタとを有し、前記第3および第4Nチャネル型MOSトランジスタのゲートは前記複数のワード線のいずれか一つに接続されており、

前記第1Pウエル領域には、前記複数のメモリセルの前記第1および第3Nチャネル型

10

20

MOSトランジスタが形成され、

前記第2Pウエル領域には、前記複数のメモリセルの前記第2および第4Nチャネル型MOSトランジスタが形成され、

前記Nウエル領域には、前記複数のメモリセルの前記第1および第2Pチャネル型MOSトランジスタが形成され、

前記第1配線と前記第1および第2Pウエル領域とのコンタクトが設けられる領域は、前記複数のメモリセルがアレイ状に配列されるメモリアレイ領域から分けて前記第1および第2ビット線が延びる方向に配置され、

前記第2配線と前記Nウエル領域とのコンタクトが設けられる領域は、前記メモリアレイ領域から分けて前記第1および第2ビット線が延びる方向に配置される半導体装置。 10

【請求項2】

請求項1において、

前記第1および第2配線は、前記複数のワード線と並ぶように配置される半導体装置。

【請求項3】

請求項1または2において、

電源電位線および接地電位線の各々は、前記第1および第2ビット線と並ぶように配置される半導体装置。

【請求項4】

請求項1乃至3のいずれかにおいて、

前記第1および第2配線は、前記第1および第2ビット線が形成される層とは異なる層に形成される半導体装置。 20

【請求項5】

請求項1乃至4のいずれかにおいて、

前記第1および第2配線は、前記複数のワード線が形成される層に形成される半導体装置。

【請求項6】

請求項1乃至5のいずれかにおいて、

前記複数のメモリセルの前記第1、第2、第3および第4Nチャネル型MOSトランジスタは、前記第1Pウエル領域と前記Nウエル領域との境界線と並ぶように配置される半導体装置。 30

【請求項7】

請求項1乃至6のいずれかにおいて、

前記第1Pウエル領域は拡散層を含み、

前記拡散層の形状は、前記拡散層上に規定され、前記第1Pウエル領域と前記Nウエル領域との境界線に平行となる線に対して線対称である半導体装置。

【請求項8】

請求項7において、

前記拡散層の形状は、長方形である半導体装置。

【請求項9】

請求項7において、

前記拡散層の形状は、互いに幅の異なる複数の長方形の組み合わせである半導体装置。 40

【請求項10】

請求項1において、

前記ワード線に平行な方向に配置された2つの隣接するメモリセルの一方は、前記第1Pウエル領域に第1の拡散層を有し、

前記2つの隣接するメモリセルの他方は、前記第1Pウエル領域に第2の拡散層を有し、

前記第1の拡散層と前記第2の拡散層とは分離されている半導体装置。

【請求項11】

請求項1において、

50

前記第1電位は接地電位であり、前記第2電位は電源電位である半導体装置。

【請求項12】

第1、第2、第3および第4ビット線と、

第1Nチャネル型MOSトランジスタおよび第1Pチャネル型MOSトランジスタを有する第1インバータと、第2Nチャネル型MOSトランジスタおよび第2Pチャネル型MOSトランジスタを有し、その入力が前記第1インバータの出力に接続され、その出力が前記第1インバータの入力に接続される第2インバータと、そのソース・ドレイン経路が前記第1ビット線と前記第1インバータの出力との間に接続される第3Nチャネル型MOSトランジスタと、そのソース・ドレイン経路が前記第2ビット線と前記第2インバータの出力との間に接続される第4Nチャネル型MOSトランジスタとを含む第1メモリセルと、

第5Nチャネル型MOSトランジスタおよび第3Pチャネル型MOSトランジスタを有する第3インバータと、第6Nチャネル型MOSトランジスタおよび第4Pチャネル型MOSトランジスタを有し、その入力が前記第3インバータの出力に接続され、その出力が前記第3インバータの入力に接続される第4インバータと、そのソース・ドレイン経路が前記第3ビット線と前記第3インバータの出力との間に接続される第7Nチャネル型MOSトランジスタと、そのソース・ドレイン経路が前記第4ビット線と前記第4インバータの出力との間に接続される第8Nチャネル型MOSトランジスタとを有する第2メモリセルと、

第9Nチャネル型MOSトランジスタおよび第5Pチャネル型MOSトランジスタを有する第5インバータと、第10Nチャネル型MOSトランジスタおよび第6Pチャネル型MOSトランジスタを有し、その入力が前記第5インバータの出力に接続され、その出力が前記第5インバータの入力に接続される第6インバータと、そのソース・ドレイン経路が前記第1ビット線と前記第5インバータの出力との間に接続される第11Nチャネル型MOSトランジスタと、そのソース・ドレイン経路が前記第2ビット線と前記第6インバータの出力との間に接続される第12Nチャネル型MOSトランジスタとを有する第3メモリセルと、

第13Nチャネル型MOSトランジスタおよび第7Pチャネル型MOSトランジスタを有する第7インバータと、第14Nチャネル型MOSトランジスタおよび第8Pチャネル型MOSトランジスタを有し、その入力が前記第7インバータの出力に接続され、その出力が前記第7インバータの入力に接続される第8インバータと、そのソース・ドレイン経路が前記第3ビット線と前記第7インバータの出力との間に接続される第15Nチャネル型MOSトランジスタと、そのソース・ドレイン経路が前記第4ビット線と前記第8インバータの出力との間に接続される第16Nチャネル型MOSトランジスタとを有する第4メモリセルと、

前記第1、第3、第9および第11Nチャネル型MOSトランジスタの基板電極に第1電位を供給するための第1コンタクトと、

前記第1、第2、第5および第6Pチャネル型MOSトランジスタの基板電極に第2電位を供給するための第2コンタクトと、

前記第2、第4、第5、第7、第10、第12、第13および第15Nチャネル型MOSトランジスタの基板電極に前記第1電位を供給するための第3コンタクトと、

前記第3、第4、第7および第8Pチャネル型MOSトランジスタの基板電極に前記第2電位を供給するための第4コンタクトと、

前記第6、第8、第14および第16Nチャネル型MOSトランジスタの基板電極に前記第1電位を供給するための第5コンタクトと、

を有し、

前記第1および第2Pチャネル型MOSトランジスタは、前記第1および第3Nチャネル型MOSトランジスタと前記第2および第4Nチャネル型MOSトランジスタとの間に形成され、

前記第3および第4Pチャネル型MOSトランジスタは、前記第5および第7Nチャネ

ル型MOSトランジスタと前記第6および第8Nチャネル型MOSトランジスタとの間に形成され、

前記第2および第4Nチャネル型MOSトランジスタと前記第5および第7Nチャネル型MOSトランジスタは隣り合って形成され、

前記第5および第6Pチャネル型MOSトランジスタは、前記第9および第11Nチャネル型MOSトランジスタと前記第10および第12Nチャネル型MOSトランジスタとの間に形成され、

前記第7および第8Pチャネル型MOSトランジスタは、前記第13および第15Nチャネル型MOSトランジスタと前記第14および第16Nチャネル型MOSトランジスタとの間に形成され、

前記第10および第12Nチャネル型MOSトランジスタと前記第13および第15Nチャネル型MOSトランジスタは隣り合って形成され、

前記第1、第2、第3、第4および第5コンタクトは、前記第1、第2、第3および第4メモリセルがアレイ状に配置されるメモリアレイ領域である第1領域外の第2領域に形成されており、前記第1領域内には、前記第1から第16Nチャネル型MOSトランジスタの基板電極に前記第1電位を供給するためのコンタクトおよび前記第1から第8Pチャネル型MOSトランジスタの基板電極に前記第2電位を供給するためのコンタクトは設けられておらず、

前記第1メモリセルと前記第2メモリセルは線対称に配置され、

前記第3メモリセルと前記第4メモリセルは線対称に配置され、

前記第1メモリセルと前記第3メモリセルは線対称に配置され、

前記第2メモリセルと前記第4メモリセルは線対称に配置されることを特徴とする半導体装置。

#### 【請求項13】

請求項12において、

前記第1から第4ビット線と交差する複数の第1ワード線を有し、

前記第3、第4、第7、第8、第11、第12、第15および第16Nチャネル型MOSトランジスタのそれぞれのゲートは、前記複数の第1ワード線のうち、対応する一つに接続されていることを特徴とする半導体装置。

#### 【請求項14】

請求項13において、

前記第3、第4、第7および第8Nチャネル型MOSトランジスタのゲートは、前記複数の第1ワード線のうち、同じ一つのワード線に接続され、

前記第11、第12、第15および第16Nチャネル型MOSトランジスタのそれぞれのゲートは、前記複数の第1ワード線のうち、同じ他の一つのワード線に接続されていることを特徴とする半導体装置。

#### 【請求項15】

請求項13または14において、

前記第1、第3、第9および第11Nチャネル型MOSトランジスタが形成される第1Pウエル領域と、

前記第1、第2、第5および第6Pチャネル型MOSトランジスタが形成される第1Nウエル領域と、

前記第2、第4、第5、第7、第10、第12、第13および第15Nチャネル型MOSトランジスタが形成される第2Pウエル領域と、

前記第3、第4、第7および第8Pチャネル型MOSトランジスタが形成される第2Nウエル領域と、

前記第6、第8、第14および第16Nチャネル型MOSトランジスタが形成される第3Pウエル領域と、

を有し、

前記第1コンタクトは、前記第1Pウエル領域と接続され、

10

20

30

40

50

前記第2コンタクトは、前記第1Nウエル領域と接続され、

前記第3コンタクトは、前記第2Pウエル領域と接続され、

前記第4コンタクトは、前記第2Nウエル領域と接続され、

前記第5コンタクトは、前記第3Pウエル領域と接続されることを特徴とする半導体装置。

【請求項16】

請求項15において、

前記第1および第2ビット線に接続される複数の第5メモリセルと、

前記第3および第4ビット線に接続される複数の第6メモリセルと、

を有し、

前記複数の第5メモリセルおよび前記複数の第6メモリセルは、前記第1および第2領域外の第3領域に形成され、

前記第2領域は、前記第1領域と前記第3領域との間に形成され、

前記第1から第3Pウエル領域は、前記第1から第3領域に渡って連続して形成され、

前記第1および第2Nウエル領域は、前記第1から第3領域に渡って連続して形成されることを特徴とする半導体装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、半導体集積回路装置に関わり、特にS R A M (static random access memory) セルのレイアウトおよびこのセルを用いて構成したメモリに関するものである。

【0002】

【従来の技術】

C M O S構成の1ポートS R A Mセルは、通常6個のトランジスタで構成されており、従来の公知のレイアウトとして特開平10-178110が知られている。

【0003】

従来のS R A Mセルのレイアウトでは、S R A Mセルを構成するインバータが形成されたPウエル領域が2つに分割されてNウエル領域の両側に配置され、ウエル境界線がビット線に平行に走るように形成されている。

【0004】

【発明が解決しようとする課題】

微細化が進むにつれ、露光装置の波長をG線からI線さらにエキシマレーザへと短くして対応してきた。しかし、微細化の要求は装置の短波長化の進歩よりも早く、近年では波長以下のパターン寸法を加工する必要に迫られている。パターン寸法が波長以下になると鍵状に曲がったような複雑なパターンではレイアウトに忠実にパターンを形成できなくなり、メモリセルの対称性を崩す原因となる。

【0005】

しかし、従来の公知例では、Pウエル領域の基板へのコンタクトをとるために、拡散層の形を鍵状に曲げる必要があった。このため、対称性が悪く微細化が困難であるという問題があった。

【0006】

【課題を解決するための手段】

そこで、本発明では、第1のNチャネル型M O Sトランジスタと第1のPチャネル型M O Sトランジスタとを含む第1のインバータと、第2のNチャネル型M O Sトランジスタと、第2のPチャネル型M O Sトランジスタとを含み、前記第1のインバータの出力端子に入力端子が接続され、前記第1のインバータの入力端子に出力端子が接続された第2のインバータと、前記第1のインバータの出力端子にソースが接続され、第1のビット線にドレインが接続され、ワード線にゲートが接続された第3のNチャネル型M O Sトランジスタと、前記第2のインバータの出力端子にソースが接続され、第2のビット線にドレインが接続され、ワード線にゲートが接続された第4のNチャネル型M O Sトランジスタとを

備え、前記第1および第3のNチャネル型MOSトランジスタは第1のPウエル領域に形成され、その拡散層は曲がりがなく、配置方向が、第1および第2のPチャネル型MOSトランジスタが形成される第1のnウエル領域との境界に対して、平行であり、前記第2および第4のNチャネル型MOSトランジスタは第2のPウエル領域に形成され、その拡散層が曲がりがなく、配置方向が、第1および第2のPチャネル型MOSトランジスタが形成される第1のnウエル領域との境界に対して、平行であることを特徴としている。

【0007】

拡散層の形状としては、また、その外形を直線を主体として構成し、最も長い直線部分が、第1および第2のPチャネル型MOSトランジスタが形成される第1のnウエル領域との境界に対して、平行であり、かつ、その境界に平行な中心線となる直線を規定した場合、その中心線に対して線対称であり、第2および第4のNチャネル型MOSトランジスタは第2のPウエル領域に形成され、その拡散層の外形は直線を主体として構成され、最も長い直線部分が、第1および第2のPチャネル型MOSトランジスタが形成される第1のnウエル領域との境界に対して、平行であり、かつ、その境界に平行な中心線となる直線を規定した場合、その中心線に対して線対称であることとしてもよい。このとき、線対称と言った場合、完全に線対称でなくとも、例えば中心線の左右で拡散層の面積が同じ程度の形状として、若干の非対称も場合により許容するものである。

10

【0008】

また、前記第3のNチャネル型MOSトランジスタのゲートに用いられる第1の多結晶シリコン配線層と、前記第1のNチャネル型MOSトランジスタのゲートと前記第1のPチャネル型MOSトランジスタのゲートとに用いられる第2の多結晶シリコン配線層とが平行に配置され、前記第4のNチャネル型MOSトランジスタのゲートに用いられる第3の多結晶シリコン配線層と、前記第2のNチャネル型MOSトランジスタのゲートと前記第2のPチャネル型MOSトランジスタのゲートに用いられる第4の多結晶シリコン配線層とが平行に配置され、第1および第3の多結晶シリコン配線層は、ワード線を構成する第2層の金属配線層とコンタクトを介して接続される。

20

【0009】

また、前記第1のインバータの入力端子と前記第2のインバータの出力端子がコンタクトで電気的に接続され、前記第2のインバータの入力端子と前記第1のインバータの出力端子がコンタクトで電気的に接続されてもよい。

30

【0010】

また、前記第1、第2のビット線と、前記第1、第2のPチャネル型MOSトランジスタのソースに接続された電源線と、前記第1、第2のNチャネル型MOSトランジスタのソースに接続された接地線とが、第3層の金属配線層で、拡散層と平行に形成されてもよい。

【0011】

また、前記第3層の金属配線層で形成された第1のビット線が前記第3層の金属配線層で形成された電源線と、前記第3層の金属配線層で形成された第1のNチャネル型MOSトランジスタのソースに接続された接地線とに挟まれ、前記第3層の金属配線層で形成された第2のビット線が前記第3層の金属配線層で形成された電源線と、前記第3層の金属配線層で形成された第2のNチャネル型MOSトランジスタのソースに接続された接地線とに挟まれてもいい。

40

【0012】

あるいは、前記第1、第2のビット線と、前記第1、第2のPチャネル型MOSトランジスタのソースに接続された電源線とが第3層の金属配線層で形成され、ワード線が第3層の金属層で形成され、前記第1、第2のNチャネル型MOSトランジスタのソースに接続された接地線が、第3層および第2層の金属配線層で形成されてもよい。

【0013】

また、前記メモリセルがアレイ状に並べられ、アレイ中およびアレイの上下に、Pウエル領域の基板へのコンタクトおよびNウエル領域の基板へのコンタクトがワード線と平行に

50

直線的に配置されている。以上では n ウエル領域の両側に 2 つの p ウエル領域を配置した例であるが、p ウエル領域の両側に 2 つの n ウエル領域を配置することもできる。

【 0 0 1 4 】

また、本願発明を適用した半導体記憶装置の他の例においては、少なくとも 1 対の N ウエル領域と P ウエル領域とからなるメモリセルをアレイ状に配置したメモリアレイを複数備え、そのメモリアレイの間に少なくとも一つの中間領域を有し、N ウエル領域と P ウエル領域との境界は少なくとも一つの直線部分を有し、N ウエル領域と P ウエル領域にそれぞれ形成された拡散層の平面形状は、

( 1 ) 直線部分と平行な長辺を有する長方形の形状、または、( 2 ) 直線部分と平行な長辺を有する複数の長方形をそれぞれの短辺を介して組み合わせた形状であり、あるいは、

( 1 ) 直線部分と平行な長辺を有する長方形の形状、または、( 2 ) 直線部分と平行な長辺を有する複数の長方形を上記直線部分の方向に延びるように組み合わせた形状であることを特徴とする。

【 0 0 1 5 】

少なくともメモリアレイの領域においては、直線部分に平行にビット線が配置され、直線部分に垂直な方向にワード線が配置される。好ましくは、中間領域においては、直線部分に垂直な方向に少なくとも一種類の配線が配置され、かつ、電源配線と N ウエル領域または P ウエル領域に形成された拡散層との電気的接触を行う配線( 例えはコンタクト ) が形成されている。この配線としては電源配線、接地配線、その他の電位の配線が考えられる。

【 0 0 1 6 】

本願発明は特に 6 つのトランジスタから構成されるスタティック RAM のメモリセルを有する半導体記憶装置に好適である。

【 0 0 1 7 】

【発明の実施の形態】

以下、本発明に係わる半導体記憶装置の好適ないくつかの事例につき、図面を用いて説明する。

【 0 0 1 8 】

実施例 1

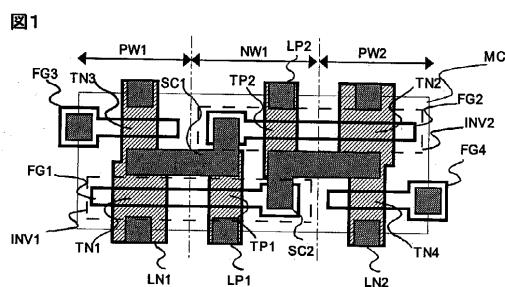

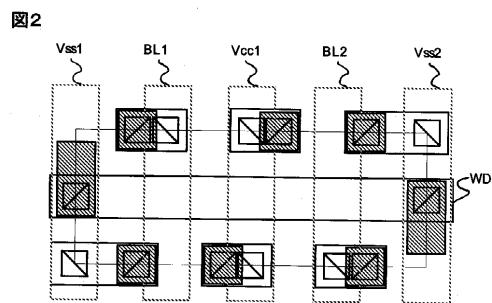

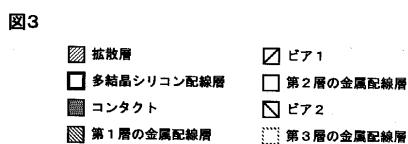

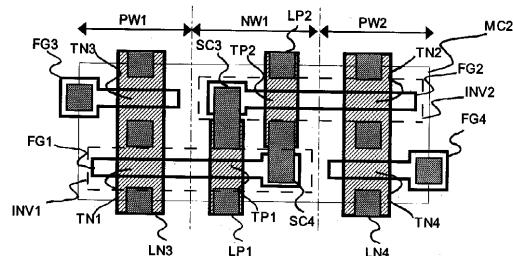

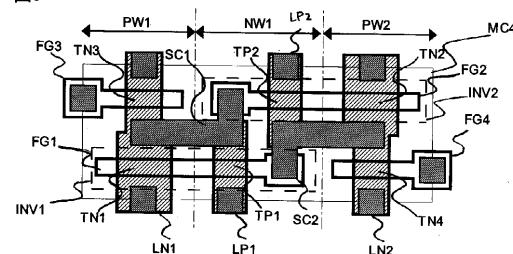

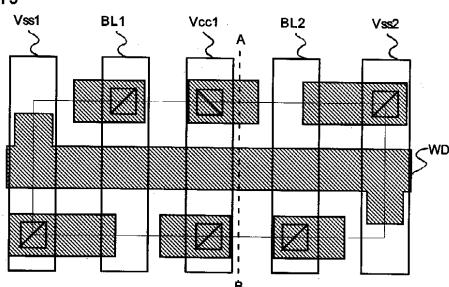

図 1 および図 2 に本発明の S R A M セルのレイアウト M C を示す。図 1 は、半導体基板に形成された、ウエル領域、拡散層、多結晶シリコン配線層およびコンタクトが示されており、図 2 には、第 1 層の金属配線層、ビアホール 1 、第 2 層の金属配線層、ビアホール 2 および第 3 層の金属配線層が示されている。図 3 は、図 1 および図 2 で使用される記号の説明である。

【 0 0 1 9 】

P ウエル領域 P W 1 に形成される N チャネル型 M O S トランジスタ T N 1 と N ウエル領域 N W 1 に形成される P チャネル型 M O S トランジスタ T P 1 によってインバータ I N V 1 が構成される。また、N ウエル領域 P W 1 に形成される N チャネル型 M O S トランジスタ T N 2 と N ウエル領域 N W 1 に形成される P チャネル型 M O S トランジスタ T P 2 によってインバータ I N V 2 が構成される。

【 0 0 2 0 】

インバータ I N V 1 の出力は、コンタクト S C 1 によってインバータ I N V 2 の入力と電気的に接続されている。また、インバータ I N V 2 の出力は、コンタクト S C 2 によってインバータ I N V 1 の入力と電気的に接続されている。

【 0 0 2 1 】

N チャネル型 M O S トランジスタ T N 3 は、ドレイン電極がビット線 B L 1 に接続され、ソース電極が、N チャネル型 M O S トランジスタ T N 1 のドレインに接続され、ゲート電極は、ワード線 W D に接続される。同様に、N チャネル型 M O S トランジスタ T N 4 は、ドレイン電極がビット線 B L 2 に接続され、ソース電極が、N チャネル型 M O S トランジスタ T N 2 のドレインに接続され、ゲート電極は、ワード線 W D に接続される。

10

20

30

40

50

## 【0022】

Nチャネル型MOSトランジスタTN1およびNチャネル型MOSトランジスタTN3は、拡散層LN1上に形成され、Nチャネル型MOSトランジスタTN2およびNチャネル型MOSトランジスタTN4は、拡散層LN2上に形成される。

## 【0023】

Pチャネル型MOSトランジスタTP1は、拡散層LP1上に形成され、Pチャネル型MOSトランジスタTP2は、拡散層LP2上に形成される。

## 【0024】

拡散層(LN1、LN2、LP1、LP2)は、曲がりなく直線であるため、折れ曲がり部でのパターン補正が必要なく、ノード間のバランスが良くなる。メモリセルをアレイ上に並べた場合、拡散層は、ビット線(BL1、BL2)に平行な4本の直線となる。

10

## 【0025】

また、Nチャネル型MOSトランジスタTN3のゲート電極に用いられる多結晶シリコン配線層FG3および、Nチャネル型MOSトランジスタTN4のゲート電極に用いられる多結晶シリコン配線層FG4は、ビット線(BL1、BL2)と垂直方向に第2の金属配線層を用いて形成されるワード線WLに接続されている。Nチャネル型MOSトランジスタTN1およびPチャネル型MOSトランジスタTP1のゲート電極に用いられる多結晶シリコン配線層FG1、Nチャネル型MOSトランジスタTN2およびPチャネル型MOSトランジスタTP2のゲート電極に用いられる多結晶シリコン配線層FG2および多結晶シリコン配線層(FG3、FG4)は、ワード線と平行に配置されている。

20

## 【0026】

Nチャネル型MOSトランジスタTN1のソース電極は、第3層の金属配線層で形成された接地電位線Vss1に接続され、Nチャネル型MOSトランジスタTN2のソース電極は、第3層の金属配線層で形成された接地電位線Vss2に接続される。また、Pチャネル型MOSトランジスタ(TP1、TP2)のソース電極は、第3層の金属配線層で形成された電源電位線Vcc1に接続されている。

## 【0027】

ビット線BL1は、電源電位Vcc1と接地電位Vss1に挟まれており、ビット線BL2は電源電位Vcc1と接地電位Vss2に挟まれている。この構造は、ビット線どうしのクロスカップルノイズを低減でき、低電圧、高速動作に効果がある。

30

## 【0028】

また、コンタクトホールのエッチ時にサイドスペーサーを削って $n^-$ 層上にコンタクトが形成された場合、コンタクトから $n^-$ を通して基板に流れ込むことが考えられる。多結晶シリコン配線層と拡散層をつなぐコンタクトを形成する場合、拡散層TP2と多結晶シリコン配線層FG1の間隔をサイドスペーサーの長さよりも長くすることにより、拡散層に $n^-$ が形成されずリーク電流を防ぐことができる。

## 【0029】

## 実施例2

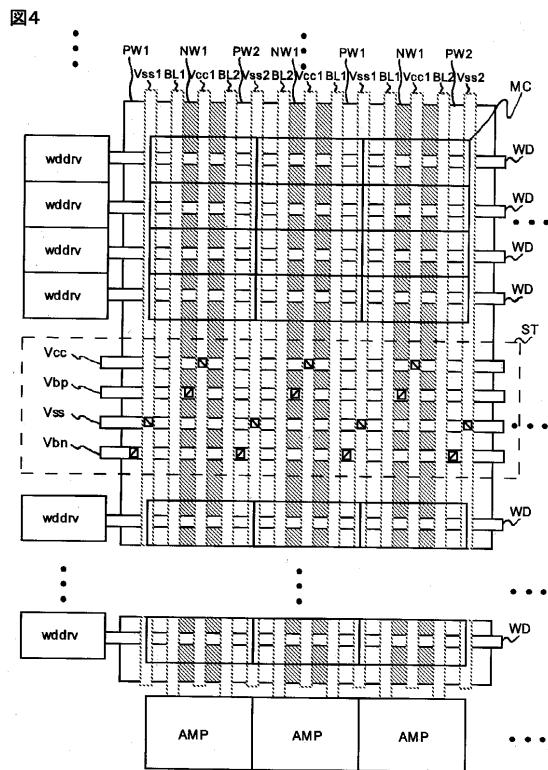

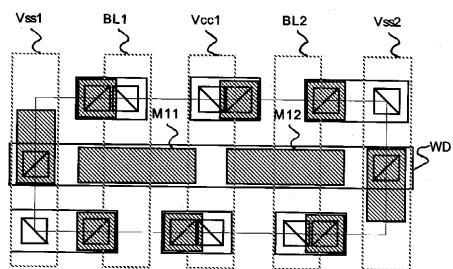

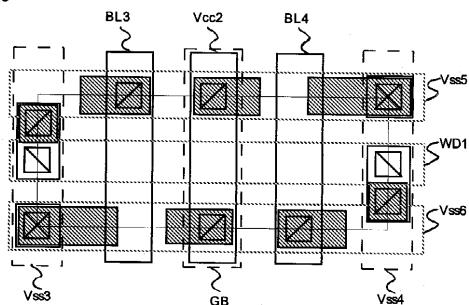

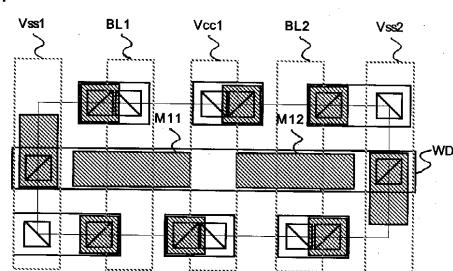

図4に実施例1のメモリセルMCをアレイ状に配列した場合の例を示す。図中の記号は、図3に説明されている。

40

## 【0030】

メモリセルMCは例えば、256口-×128カラム並べられる。実施例1のメモリセルは、ビット線方向の高さが低いため、256口のメモリセルを並べても、ビット線の長さが従来に比べて短くなるので、高速化できる。隣合うメモリセルMCは、y軸に対して線対称に配置され、上下のメモリセルMCは、x軸に対して線対称に配置される。また、アレイの途中には、基板への電源を供給するための領域STが、ワード線WDと平行に形成される。領域STは、例えば、メモリセル32口あるいは、64口毎に配置される。

## 【0031】

Pウエル領域(PW1、PW2)に電位を供給する配線VbnおよびNウエル領域NW1

50

に電位を供給する配線  $V_{b\,p}$  がワード線と平行に形成される。配線  $V_{b\,n}$  は、接地電位  $V_{ss}$  と接続してもいいし、 $V_{ss}$  とは異なる電位を供給することができる。また、配線  $V_{b\,p}$  は、電源電位  $V_{cc}$  と接続してもいいし、 $V_{cc}$  とは異なる電位を供給することもできる。

【0032】

また、領域  $S\,T$  では、電源電位線  $V_{cc\,1}$  を補強するための電源電位線  $V_{cc}$  がワード線と平行に形成され、接地電位 ( $V_{ss\,1}$ 、 $V_{ss\,2}$ ) を補強するための接地電位線  $V_{ss}$  がワード線と平行に形成される。

【0033】

また、接地電位線 ( $V_{ss\,1}$ 、 $V_{ss\,2}$ ) が、ワード線  $W\,D$  と垂直方向に配置されるので 10 、1つのワード線を選択した場合に、このワード線に沿った各メモリセルに対して、1対の接地電位線から電位が供給されるので、電位線のノイズが小さく、アクセスの高速化、低電圧化に効果がある。

【0034】

また、メモリセル  $M\,C$  は、ワード線方向の幅が広いため、センスアンプ  $A\,M\,P$  のレイアウトが容易であり、従来行われていた、メモリセル 2 カラムで1つのセンスアンプをレイアウトする必要がなく、1カラムに1つのセンスアンプがレイアウトできる。また、ワードドライバ回路  $W\,D\,D\,R\,V$  は従来に比べて偏平なレイアウトとなる。

【0035】

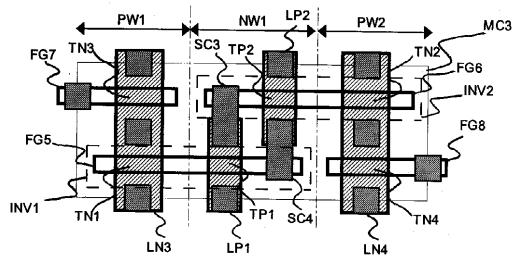

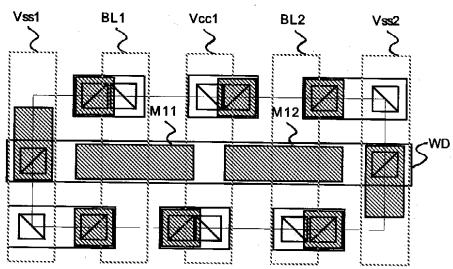

実施例 3

20

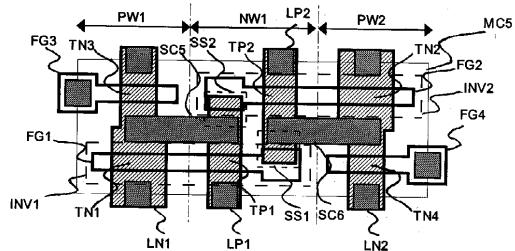

図 5 および図 6 に実施例 3 の  $S\,R\,A\,M$  セルのレイアウト  $M\,C\,2$  を示す。図 5 および図 6 で使用される記号の説明を図 3 に示した。実施例 3 のメモリセル  $M\,C\,2$  は実施例 1 のメモリセル  $M\,C$  と比べて、実施例 1 では、拡散層 ( $L\,N\,1$ 、 $L\,N\,1$ ) の形が羽子板状であるのに対し、実施例 3 の拡散層 ( $L\,N\,3$ 、 $L\,N\,4$ ) が長方形であると点と、コンタクト ( $S\,C\,1$ 、 $S\,C\,2$ ) が、コンタクト ( $S\,C\,3$ 、 $S\,C\,4$ ) と第 1 層の金属配線層 ( $M\,1\,1$ 、 $M\,1\,2$ ) で置き換えられている点を除いて同一である。

【0036】

通常メモリセルでは、安定性を確保するために、N チャネル型  $M\,O\,S$  トランジスタ ( $T\,N\,1$ 、 $T\,N\,2$ ) のゲート幅は、N チャネル型  $M\,O\,S$  トランジスタ ( $T\,N\,3$ 、 $T\,N\,4$ ) のゲート幅の 1.5 倍に設計される。しかし、この場合は、実施例 1 で示したように、拡散層の形が羽子板状になり、パターン補正 ( $O\,P\,C$ ) などの技術が必要となる。また、このために、トランジスタどうしのバランスも悪くなる。これに対して、実施例 3 では、拡散層 ( $L\,N\,3$ 、 $L\,N\,4$ ) が長方形なので、加工が容易で、また、この結果トランジスタのバランスも良くすることができる。ただし、ゲート幅の比が 1.0 倍になってしまふため、N チャネル型  $M\,O\,S$  トランジスタ ( $T\,N\,1$ 、 $T\,N\,2$ ) に比べて、N チャネル型  $M\,O\,S$  トランジスタ ( $T\,N\,3$ 、 $T\,N\,4$ ) の酸化膜厚を厚くするか、ゲート長を長くするか、しきい値を高くなるか、あるいは電界緩和のための低濃度ドレイン領域の不純物濃度を低くするなどにより駆動力に差をつけていわゆるセルレシオを大きくする必要がある。また、実施例 3 では、実施例 1 でインバータ  $I\,N\,V\,1$  の出力とインバータ  $I\,N\,V\,2$  の入力を接続していたコンタクト  $S\,C\,1$  の代わりに、コンタクト  $S\,C\,3$  と第 1 層の金属配線層  $M\,1\,1$  を用いている。このようにすることにより折れ曲がったコンタクトが必要なくなり、パターン補正 ( $O\,P\,C$ ) 等が必要なくなる。

【0037】

実施例 4

30

図 7 および図 8 に実施例 4 の  $S\,R\,A\,M$  セルのレイアウト  $M\,C\,3$  を示す。図 7 および図 8 で使用される記号の説明を図 3 に示した。実施例 4 のメモリセル  $M\,C\,3$  は実施例 3 のメモリセル  $M\,C\,2$  と比べて、多結晶シリコン配線層 ( $F\,G\,5$ 、 $F\,G\,6$ 、 $F\,G\,7$ 、 $F\,G\,8$ ) の形が長方形である点が異なる。このセルでは、折れ曲がりがなく、パターン補正 ( $O\,C\,P$ ) が不要なく、トランジスタどうしのバランスがよくなる。

【0038】

40

50

## 実施例 5

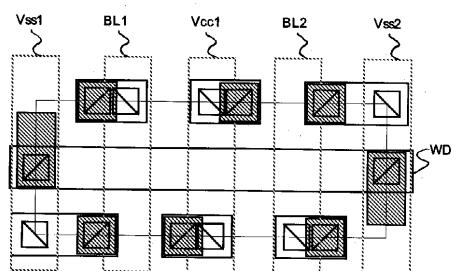

図 9 および図 10 に実施例 5 の S R A M セルのレイアウト M C 4 を示す。図 9 および図 10 で使用される記号の説明を図 11 に示した。実施例 5 のメモリセル M C 4 は実施例 1 のメモリセル M C と比べて、配線構造が異なる。

## 【 0 0 3 9 】

ビット線 ( B L 3 、 B L 4 ) および、電源電位線 V c c 2 は、第 2 層の金属配線層を用いて形成される。ワード線 W D 1 および接地電位線 ( V s s 5 、 V s s 6 ) は、第 3 層の金属配線層を用いてビット線と垂直に形成される。接地電位線 ( V s s 3 、 V s s 4 ) は、第 4 層の金属配線層を用いてビット線と平行に形成される。

## 【 0 0 4 0 】

グローバルビット線 G B は、ビット線を階層化した場合に使用される配線である。グローバルビット線 G B とビット線 ( B L 3 、 B L 4 ) とは、第 3 層の金属配線層でシールドされているので、クロスカップルノイズを防ぐことができる。また、接地電位線 ( V s s 3 、 V s s 4 ) によって、グローバルビット線 G B どうしのクロスカップルノイズを防ぐことができる。

## 【 0 0 4 1 】

## 実施例 6

図 12 および図 13 に実施例 6 の S R A M セルのレイアウト M C 5 を示す。図 12 および図 13 で使用される記号の説明を図 14 に示した。実施例 6 のメモリセル M C 5 は実施例 1 のメモリセル M C と比べて、ゲート電極と拡散層接続するいわゆる 3 層コンタクトの構造が異なる。

## 【 0 0 4 2 】

実施例 1 では L 字状のコンタクト S C 1 、 S C 2 でゲート電極と拡散層を接続しているが、実施例 6 ではゲート電極と拡散層接続領域 S S 1 、 S S 2 でシリサイドにより接続している。そのためゲート電極と拡散層を接続するためにコンタクトを L 字状に曲げる必要がなく I 字状の長方形のコンタクト S C 5 、 S C 6 にできる。コンタクトに折れ曲がりがなく、パターン補正 ( O C P ) が必要ない。

## 【 0 0 4 3 】

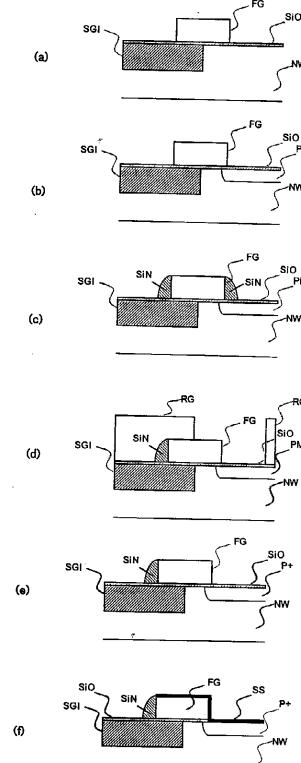

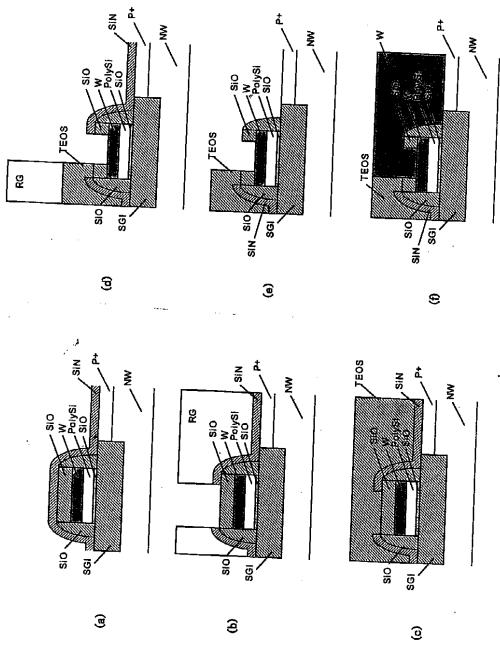

ゲート電極と拡散層接続領域 S S 1 、 S S 2 でシリサイドにより接続する具体的なプロセスフローを図 15 に示す。

## 【 0 0 4 4 】

ゲート電極 F G を多結晶シリコンで形成する ( 図 15 ( a ) ) 。

## 【 0 0 4 5 】

ゲート電極 F G の側壁にサイドスペーサ S i N を C V D シリコン窒化膜により形成する ( 図 15 ( b ) ) 。

## 【 0 0 4 6 】

アクティブ領域側のサイドスペーサ S i N をシリコン窒化膜と酸化膜を高選択でエッティングできる条件でエッティングし取り除く ( 図 15 ( c ) ) 。

## 【 0 0 4 7 】

P 型高濃度拡散層  $P^+$  を形成する ( 図 15 ( d ) ) 。

## 【 0 0 4 8 】

C o などの高融点金属をスパッタにより堆積し、アニールすることで多結晶シリコンゲート電極と拡散層に選択的にシリサイドを形成する ( 図 15 ( e ) ) 。このときゲート電極の側壁と拡散層とがシリサイドにより接続される。

## 【 0 0 4 9 】

## 実施例 7

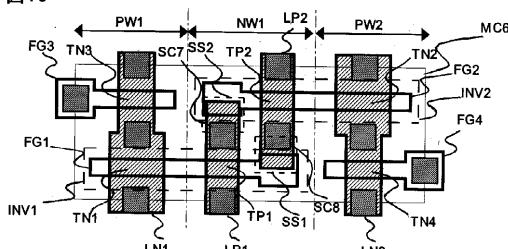

図 16 および図 17 に実施例 7 の S R A M セルのレイアウト M C 6 を示す。図 16 および図 17 で使用される記号の説明を図 14 に示した。実施例 7 のメモリセル M C 6 は実施例 6 のメモリセル M C 5 と比べて、コンタクト ( S C 5 、 S C 6 ) が、コンタクト ( S C 7 、 S C 8 ) と第 1 層の金属配線層 ( M 1 1 、 M 1 2 ) で置き換えられている点を除いて

10

20

30

40

50

同一である。

【0050】

実施例7ではすべてのコンタクトを正方形コンタクトにでき、パターン補正(OCP)が必要ない。

【0051】

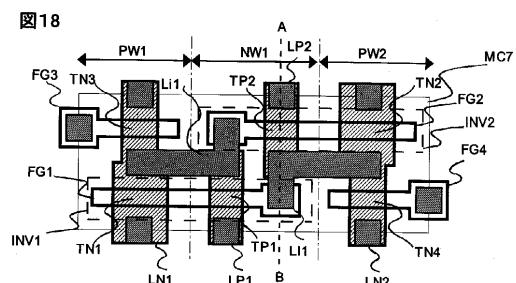

実施例8

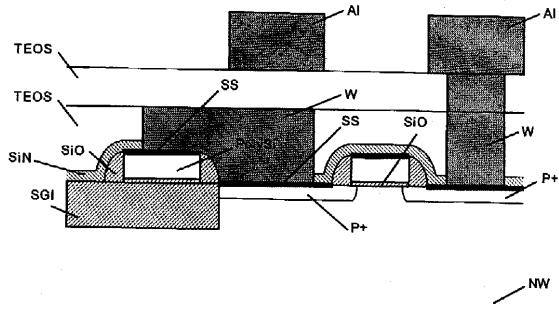

図18および図19に実施例8のSRAMセルのレイアウトMC7を示す。図18および図19で使用される記号の説明を図20に示した。実施例8のメモリセルMC7は実施例1のメモリセルMCと比べて、コンタクト(SC1、SC2)が、ローカルインターロネクト(LI1、LI2)で置き換えられている点と、ワード線が第2層目の金属配線から第1層目の金属配線に、ビット線と電源電位線と接地電位線が第3層目の金属配線から第2層目の金属配線に変更されている点を除いて同一である。図21は図18、19のA-B線に沿った断面図である。

10

【0052】

実施例1ではコンタクトSC1、SC2は他のコンタクトと同層で形成しているために、SC1、SC2の上に第1層目の金属配線を配置できないという制約がある。実施例8ではコンタクトとは別層のローカルインターロネクトLI1、LI2で形成するために上に第1層目の金属配線を配置でき、実施例1と比較すると金属配線を1層減らす事ができる。

【0053】

20

実施例9

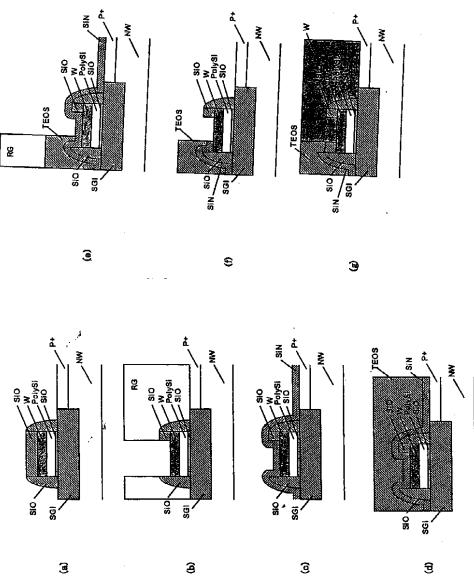

図22に実施例9の3層コンタクト部のプロセスフローを示す。実施例9は実施例1、3、4、5、8の3層コンタクト部を形成するプロセスの一例である。

【0054】

近年のLSIでは、コンタクトがホト工程の合せずれにより拡散層やゲート電極から外れてもフィールド酸化膜を削ることがないように、シリコン窒化膜などをストップとして高選択エッティングでコンタクト穴を加工するのが一般的になってきている。ゲート電極をいわゆるサリサイド技術により低抵抗化する場合は、拡散層形成後に拡散層上とゲート電極上を露出させてシリサイドを形成し、その上にエッティングストップとしてのシリコン窒化膜を堆積し、層間絶縁膜を更にその上に堆積してからコンタクト穴を形成するために、ゲート電極上のコンタクトと拡散層上のコンタクトをそのまま同時に形成しても両者共に導通を取ることができる。しかし、従来広く用いられてきたポリサイドゲート電極や、近年発表されているポリメタルゲート電極の場合、エッティングストップとしてのシリコン窒化膜堆積前にはゲート電極上に酸化膜などの絶縁膜が残りゲート電極は露出していないために、その上にシリコン窒化膜を堆積してコンタクトを形成しようとするとゲート電極上のコンタクトの底部には酸化膜が残り導通が取れない。実施例9はコンタクト穴を開ける部分のゲート電極上のシリコン窒化膜をあらかじめ取り除いておくことによりゲート電極上コンタクトの導通を確保するものである。

30

【0055】

以下、図22により実施例9のプロセスフローを説明する。

40

【0056】

ゲート電極と拡散層 $P^+$ を形成した後、エッティングストップとしてシリコン窒化膜SiNを堆積する(図22(a))。ゲート電極は多結晶シリコンPolySiとタングステンWの積層であり、さらにその上に保護膜として酸化膜SiOが積層されている。

【0057】

ゲート電極上のコンタクト穴を開ける部分のシリコン窒化膜をドライエッティングにより取り除く(図22(b))。

【0058】

プラズマCVDによるTEOS膜などを堆積し、層間絶縁膜を形成する(図22(c))。

50

## 【0059】

コンタクト開口部の酸化膜をシリコン窒化膜との高選択ドライエッチングによりエッチングする(図22(d))。高選択エッチングのためシリコン窒化膜はエッチングされずストップとなる。あらかじめゲート電極上のシリコン窒化膜を取り除いておいた部分はストップが無いためにゲート電極上までエッチングされる。そのため、ゲート電極上も導通が取れるようになる。

## 【0060】

シリコン窒化膜を高選択ドライエッチングにより取り除く(図22(e))。

## 【0061】

コンタクト穴の部分にタンゲステンなどの金属を埋め込みプラグとする(図22(f))

10

。

## 【0062】

## 実施例10

図23に実施例10の3層コンタクト部のプロセスフローを示す。実施例10は実施例1、3、4、5、8の3層コンタクト部を形成するプロセスの一例である。

## 【0063】

実施例10のプロセスフローは、実施例9のプロセスフローと比較して、エッチングストップのシリコン窒化膜の堆積前にゲート電極上のコンタクト穴を開ける部分の酸化膜を取り除いておく点が異なる。

## 【0064】

20

以下、図23により実施例10のプロセスフローを説明する。

## 【0065】

ゲート電極と拡散層 $P^+$ を形成する(図23(a))。ゲート電極は多結晶シリコン $P_{0.1}ySi$ とタンゲステンWの積層であり、さらにその上に保護膜として酸化膜 $SiO$ が積層されている。

## 【0066】

ゲート電極上のコンタクト穴を開ける部分の酸化膜をドライエッチングにより取り除き、ゲート電極上を露出させる(図23(b))。

## 【0067】

エッチングストップとしてシリコン窒化膜 $SiN$ を堆積する(図23(c))。

30

プラズマCVDによるTEOS膜などを堆積し、層間絶縁膜を形成する(図23(d))

。

## 【0068】

コンタクト開口部の酸化膜をシリコン窒化膜との高選択ドライエッチングによりエッチングする(図23(e))。高選択エッチングのためシリコン窒化膜はエッチングされずストップとなる。

## 【0069】

シリコン窒化膜を高選択ドライエッチングにより取り除く(図23(f))。シリコン窒化膜堆積前にゲート電極上の酸化膜を取り除いた部分はこのときに露出するために、ゲート電極上も導通が取れるようになる。

40

## 【0070】

コンタクト穴の部分にタンゲステンなどの金属を埋め込みプラグとする(図23(g))

。

## 【0071】

## 【発明の効果】

本発明によれば、拡散層が必要以上に複雑な形状とならないため、微細化が容易である

。

## 【図面の簡単な説明】

【図1】実施例1に係わる半導体装置のレイアウト図。

【図2】実施例1に係わる半導体装置のレイアウト図。

50

|                                                |    |

|------------------------------------------------|----|

| 【図3】実施例1、2、3、4で使用される記号の説明図。                    |    |

| 【図4】実施例2に係わる半導体装置のレイアウト図。                      |    |

| 【図5】実施例3に係わる半導体装置のレイアウト図。                      |    |

| 【図6】実施例3に係わる半導体装置のレイアウト図。                      |    |

| 【図7】実施例4に係わる半導体装置のレイアウト図。                      |    |

| 【図8】実施例4に係わる半導体装置のレイアウト図。                      |    |

| 【図9】実施例5に係わる半導体装置のレイアウト図。                      |    |

| 【図10】実施例5に係わる半導体装置のレイアウト図。                     | 10 |

| 【図11】実施例5で使用される記号の説明図。                         |    |

| 【図12】実施例6に係わる半導体装置のレイアウト図。                     |    |

| 【図13】実施例6に係わる半導体装置のレイアウト図。                     |    |

| 【図14】実施例6で使用される記号の説明図。                         |    |

| 【図15】実施例6に係わる半導体装置のプロセスフロー断面図。                 |    |

| 【図16】実施例7に係わる半導体装置のレイアウト図。                     |    |

| 【図17】実施例7に係わる半導体装置のレイアウト図。                     |    |

| 【図18】実施例8に係わる半導体装置のレイアウト図。                     |    |

| 【図19】実施例8に係わる半導体装置のレイアウト図。                     |    |

| 【図20】実施例8で使用される記号の説明図。                         |    |

| 【図21】実施例8に係わる半導体装置の断面図。                        |    |

| 【図22】実施例9に係わる半導体装置のプロセスフロー断面図。                 | 20 |

| 【図23】実施例10に係わる半導体装置のプロセスフロー断面図。                |    |

| 【符号の説明】                                        |    |

| MC、MC2、MC3、MC4、MC5、MC6、MC7……S R A Mメモリセル       |    |

| TN1、TN2、TN3、TN4……Nチャネル型MOSトランジスタ               |    |

| TP1、TP2……Pチャネル型MOSトランジスタ                       |    |

| PW1、PW2……Pウエル領域                                |    |

| NW1、NW……Nウエル領域                                 |    |

| FG1、FG2、FG3、FG4、FG5、FG6、FG7、FG8、FG……多結晶シリコン配線層 |    |

| LN1、LN2、LN3、LN4、LP1、LP2……拡散層                   | 30 |

| SC1、SC2、SC3、SC4、SC5、SC6、SC7、SC8……コンタクト         |    |

| INV1、INV2……インバータ回路                             |    |

| WD、WD1……ワード線                                   |    |

| BL1、BL2、BL3、BL4……ピット線                          |    |

| Vss、Vss1、Vss2、Vss3、Vss4、Vss5、Vss6……接地電位線       |    |

| Vcc、Vcc1、Vcc2……電源電位線                           |    |

| Vbp……Nウエル領域へ電位を供給する線                           |    |

| Vbn……Pウエル領域へ電位を供給する線                           |    |

| Wddrv……ワードドライバ回路                               |    |

| AMP……センスアンプ回路                                  | 40 |

| M11、M12……第1層の金属配線層                             |    |

| GB……グローバルピット線                                  |    |

| S GI……フィールド領域                                  |    |

| PolySi……多結晶シリコン                                |    |

| SiN……シリコン窒化膜                                   |    |

| SiO……シリコン酸化膜                                   |    |

| SS……シリサイド層                                     |    |

| TEOS……プラズマCVD TEOS膜                            |    |

| W……タンゲステン                                      |    |

| A1……アルミニウム配線層                                  | 50 |

P + ..... P 型高濃度拡散層。

【図1】

【図2】

【図3】

【図4】

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

図11

|            |             |

|------------|-------------|

| 拡散層        | ピア1         |

| 多結晶シリコン配線層 | ピア2         |

| コンタクト      | ピア3         |

| 第1層の金属配線層  | ピア1、ピア2、ピア3 |

| 第3層の金属配線層  | ピア4         |

| 第4層の金属配線層  | ピア5         |

【図12】

図12

【図13】

図13

【図14】

図14

|                 |           |

|-----------------|-----------|

| 拡散層             | ピア1       |

| 多結晶シリコン配線層      | 第2層の金属配線層 |

| コンタクト           | ピア2       |

| 第1層の金属配線層       | 第3層の金属配線層 |

| ゲート電極と拡散層との接続領域 |           |

【図15】

【図15】

図15

【図16】

図16

【図17】

図17

【図18】

図18

【図19】

図19

【図20】

図20

|              |           |

|--------------|-----------|

| 拡散層          | ピア1       |

| 多結晶シリコン配線層   | 第2層の金属配線層 |

| コンタクト        |           |

| ローカルインターポネクト |           |

| 第1層の金属配線層    |           |

【図21】

図21

【図22】

図22

【図23】

---

フロントページの続き

(72)発明者 池田 修二

東京都小平市上水本町五丁目20番1号

株式会社日立製作所半導体グループ内

(72)発明者 石橋 孝一郎

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

審査官 小森 重樹

(56)参考文献 特開平07-106438 (JP, A)

特開平05-235300 (JP, A)

特開平09-027552 (JP, A)

特開平07-130877 (JP, A)

特開平10-178110 (JP, A)

特開平09-270468 (JP, A)

特開平10-032263 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8244

H01L 27/10