# (19) **日本国特許庁(JP)**

G06F

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2013-58207 (P2013-58207A)

(43) 公開日 平成25年3月28日(2013.3.28)

(51) Int. Cl. FLテーマコード (参考) GO6F 11/28 (2006, 01) GO6F 11/28 5BO42 315A G06F 9/48 (2006, 01) GO6F 9/46 310K

9/46

GO6F

#### 審査請求 有 請求項の数 1 OL 外国語出願 (全 25 頁)

(21) 出願番号 特願2012-209762 (P2012-209762) (22) 出願日 平成24年9月24日 (2012.9.24) (62) 分割の表示 特願2009-537298 (P2009-537298) の分割 原出願日 平成19年11月12日 (2007.11.12) (31) 優先権主張番号 11/560, 217 (32) 優先日 平成18年11月15日(2006.11.15)

(2006.01)

(33) 優先権主張国 米国(US)

9/46

(71) 出願人 595020643

410

クゥアルコム・インコーポレイテッド QUALCOMM INCORPORAT EDアメリカ合衆国、カリフォルニア州 92 121-1714、サン・ディエゴ、モア ハウス・ドライブ 5775

(74)代理人 100108855

弁理士 蔵田 昌俊

(74)代理人 100109830

弁理士 福原 淑弘

(74)代理人 100088683

弁理士 中村 誠

(74)代理人 100103034

弁理士 野河 信久

最終頁に続く

(54) 【発明の名称】マルチスレッド化デジタル信号プロセッサに関する非侵入型、スレッド選択式デバッギング方法 及びシステム

#### (57)【要約】 (修正有)

【課題】マルチスレッド化DSPにおけるリアルタイム の挙動に対して非侵入的にデバッグを行う。

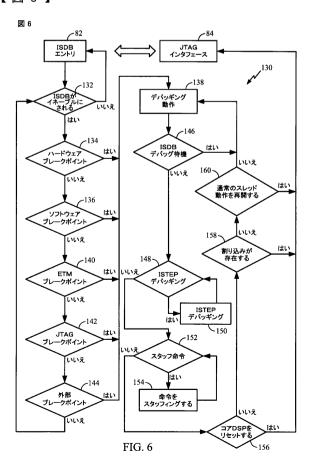

【解決手段】ISDBがDSP動作に関してイネーブル にされ(132)、ハードウェアブレークポイント13 4、ソフトウェアブレークポイント136、ETMブレ ークポイント140、JTAGブレークポイント142 、または、外部ブレークポイント144が存在すると、 デバッギング動作138に進む。ISTEPデバッギン グが有効である場合は、ISTEPデバッギング150 を行う。命令スタッフィング動作が有効である場合は、 命令スタッフィング動作154を行う。コアDSPリセ ット命令がデバッギング動作によって生成されている場 合は、コアDSPデジタル信号プロセッサをリセットす る(156)。

【選択図】図6

#### 【特許請求の範囲】

# 【請求項1】

マルチスレッド化デジタル信号プロセッサをデバッグするための非侵入型方法であって

前記マルチスレッド化デジタル信号プロセッサの少なくとも 1 つ以上のスレッドを用いて複数の処理命令をマルチスレッド化プロセスにおいて実行することと、

少なくとも 1 つのデバッギングイベントを生成するための 1 つ以上のブレークポイント命令を識別することと、

前記ブレークポイント命令のうちの少なくとも1つを実行することに応じて前記少なく とも1つのデバッギングイベントを生成することと、

前記少なくとも1つのデバッギングイベントに応じて複数のデバッギング命令を実行することであって、前記デバッギング命令は、前記マルチスレッド化デジタル信号プロセッサの少なくとも1つ以上のスレッドをデバッギングモードに移行させることによって前記マルチスレッド化デジタル信号プロセッサにおいて前記複数の処理命令を前記実行することを非侵入方式でデバッグするためのデバッギング命令であることと、

前記複数のデバッギング命令を前記実行することを報告するために前記複数のデバッギング命令を前記実行することからの少なくとも 1 つのデバッギングリターンを生成すること、とを備える、非侵入型方法。

# 【請求項2】

前記少なくとも 1 つのデバッギングイベントは、前記マルチスレッド化デジタル信号プロセッサ内において内部生成されたインスタンスに応じて発生する請求項 1 に記載の方法

#### 【請求項3】

前記少なくとも 1 つのデバッギングイベントは、前記マルチスレッド化デジタル信号プロセッサ内において外部生成されたインスタンスに応じて発生する請求項 1 に記載の方法

### 【請求項4】

前記少なくとも 1 つのデバッギングイベントは、前記マルチスレッド化デジタル信号プロセッサ内においてプログラムカウンタが予め決められたカウントに達することに応じて発生する請求項 1 に記載の方法。

### 【請求項5】

前記マルチスレッド化デジタル信号プロセッサの前記少なくとも1つ以上のスレッドは、前記デバッギングモードから出る請求項1に記載の方法。

# 【請求項6】

少なくとも 1 つ以上の命令スタッフィング命令は、前記マルチスレッド化デジタル信号 プロセッサの動作に関連する予め決められたデバッギングアルゴリズムを実行する請求項 1 に記載の方法。

## 【請求項7】

前記マルチスレッド化デジタル信号プロセッサ内の前記少なくとも1つ以上のデバッギング命令は、前記複数のデバッギング命令を前記実行することと前記複数の処理命令を前記実行することとの間においてJTAGインタフェースインタフェースを用いる請求項1に記載の方法。

# 【請求項8】

マルチスレッド化デジタル信号プロセッサを非侵入方式でデバッグするための動作に関 するシステムであって、

デジタル信号マルチスレッド化プロセスにおいて複数の処理命令を実行するための前記 マルチスレッド化デジタル信号プロセッサの1つ以上のスレッドと、

少なくとも 1 つのデバッギングイベントを生成するための一組のブレークポイント命令と、

前記ブレークポイント命令のうちの少なくとも1つを実行することに応じて少なくとも

10

20

30

40

1つのデバッギングイベントを生成するためのデバッギングイベント生成命令と、

前記少なくとも1つのデバッギングイベントに応じて前記複数のデバッギング命令を実行するための前記スレッドのうちの1つ以上であって、前記複数のデバッギング命令は、前記マルチスレッド化デジタル信号プロセッサの少なくとも1つ以上のスレッドをデバッギングモードに移行させることによって前記マルチスレッド化デジタル信号プロセッサにおいて前記複数の処理命令を前記実行することを非侵入方式でデバッギングするためのデバッギング命令である前記スレッドのうちの1つ以上と、

前記マルチスレッド化デジタル信号プロセッサの前記少なくとも1つ以上のスレッドにおいて前記複数のデバッギング命令を前記実行することを報告するために前記複数のデバッギング命令を前記実行することからの少なくとも1つのデバッギングリターンを生成するためのデバッギングリターン命令と、を備える、システム。

【請求項9】

前記マルチスレッド化デジタル信号プロセッサ内においてプログラムカウンタが予め決められたカウントに達することに応じて前記デバッギングイベントが発生するための回路と命令とをさらに備える請求項8に記載のシステム。

【請求項10】

前記マルチスレッド化デジタル信号プロセッサの前記少なくとも 1 つ以上のスレッドを前記デバッギングモードから出すための回路と命令とをさらに備える請求項 8 に記載のシステム。

【請求項11】

前記マルチスレッド化デジタル信号プロセッサの動作に関連する予め決められたデバッギングアルゴリズムを実行するための一組の命令スタッフィング命令をさらに備える請求項8に記載のシステム。

【請求項12】

JTAGインタフェースを用いて前記マルチスレッド化デジタル信号プロセッサを非侵 入方式でデバッグするための回路と命令とをさらに備える請求項8に記載のシステム。

【請求頃13】

パーソナル電子デバイスをサポートするための動作に関するマルチスレッド化デジタル信号プロセッサであって、マルチスレッド化処理中にデバッグするための非侵入型手段を備え、

前記マルチスレッド化デジタル信号プロセッサの少なくとも 1 つ以上のスレッドを用いてマルチスレッド化プロセスにおいて複数の処理命令を実行するための手段と、

少なくとも 1 つのデバッギングイベントを生成するための 1 つ以上のブレークポイント 命令を識別するための手段と、

前記ブレークポイント命令のうちの少なくとも 1 つを実行することに応じて少なくとも 1 つのデバッギングイベントを生成するための手段と、

前記少なくとも 1 つのデバッギングイベントに応じて前記複数のデバッギング命令を実行するための手段であって、前記デバッギング命令は、前記マルチスレッド化デジタル信号プロセッサの少なくとも 1 つ以上のスレッドをデバッギングモードに移行させることによって前記マルチスレッド化デジタル信号プロセッサにおいて前記複数の処理命令を前記実行することを非侵入方式でデバッグするためのデバッギング命令である手段と、

前記マルチスレッド化デジタル信号プロセッサの前記少なくとも1つ以上のスレッドにおいて前記複数のデバッギング命令を前記実行することを報告するために前記複数のデバッギング命令を前記実行することからの少なくとも1つのデバッギングリターンを生成するための手段と、を備える、マルチスレッド化デジタル信号プロセッサ。

【請求項14】

前記マルチスレッド化デジタル信号プロセッサ内において内部生成されたインスタンスに応じて前記デバッギングイベントが発生するための手段をさらに備える請求項 1 3 に記載のデジタル信号プロセッサシステム。

【請求項15】

10

20

30

40

前記マルチスレッド化デジタル信号プロセッサ内において外部生成されたインスタンスに応じて前記デバッギングイベントが発生するための手段をさらに備える請求項13に記載のマルチスレッド化デジタル信号プロセッサ。

# 【請求項16】

前記マルチスレッド化デジタル信号プロセッサ内においてプログラムカウンタが予め決められたカウントに達することに応じて前記デバッギングイベントが発生するための手段をさらに備える請求項13に記載のマルチスレッド化デジタル信号プロセッサ。

## 【請求項17】

前記マルチスレッド化デジタル信号プロセッサの前記少なくとも 1 つ以上のスレッドを前記デバッギングモードから出すための手段をさらに備える請求項 1 3 に記載のマルチスレッド化デジタル信号プロセッサ。

### 【請求項18】

前記マルチスレッド化デジタル信号プロセッサの動作に関連する予め決められたデバッギングアルゴリズムを実行するための命令をスタッフィングするための手段をさらに備える請求項13に記載のマルチスレッド化デジタル信号プロセッサ。

#### 【請求項19】

前記複数のデバッギング命令を前記実行することと前記複数の処理命令を前記実行することとの間においてJTAGインタフェースを用いるための手段をさらに備える請求項13に記載のマルチスレッド化デジタル信号プロセッサ。

# 【請求項20】

マルチスレッド化デジタル信号プロセッサを非侵入方式でデバッグするための前記マルチスレッド化デジタル信号プロセッサにおける処理命令に関してここにおいて具現化されたコンピュータによって読み取り可能なプログラムコード手段を有するコンピュータによって使用可能な媒体であって、

前記マルチスレッド化デジタル信号プロセッサの少なくとも1つ以上のスレッドを用いてマルチスレッド化プロセスにおいて複数の処理命令を実行するためのコンピュータによって読み取り可能なプログラムコード手段と、

少なくとも 1 つのデバッギングイベントを生成するために 1 つ以上のブレークポイント 命令を識別するためのコンピュータによって読み取り可能なプログラムコード手段と、

前記ブレークポイント命令のうちの少なくとも1つを実行することに応じて少なくとも 1つのデバッギングイベントを生成するためのコンピュータによって読み取り可能なプログラムコード手段と、

前記少なくとも1つのデバッギングイベントに応じて前記複数のデバッギング命令を実行するためのコンピュータによって読み取り可能なプログラムコード手段であって、前記デバッギング命令は、前記マルチスレッド化デジタル信号プロセッサの少なくとも1つ以上のスレッドをデバッギングモードに移行させることによって前記マルチスレッド化デジタル信号プロセッサにおいて前記複数の処理命令を前記実行することを非侵入方式でデバッグするためのデバッギング命令であるコンピュータによって読み取り可能なプログラムコード手段と、

前記マルチスレッド化デジタル信号プロセッサの前記少なくとも1つ以上のスレッドにおいて前記複数のデバッギング命令を前記実行することを報告するために前記複数のデバッギング命令を前記実行することからの少なくとも1つのデバッギングリターンを生成するためのコンピュータによって読み取り可能なプログラムコード手段と、を備える、コンピュータによって使用可能な媒体。

#### 【請求項21】

前記少なくとも 1 つのデバッギングイベントであって、前記マルチスレッド化デジタル信号プロセッサ内において内部生成されたインスタンスに応じて発生するデバッギングイベント、に応じて前記複数のデバッギング命令を実行するためのコンピュータによって読み取り可能なプログラムコード手段をさらに備える請求項 2 0 に記載のコンピュータによって使用可能な媒体。

20

10

30

40

#### 【発明の詳細な説明】

# 【技術分野】

### [00001]

開示される主題は、データ通信に関するものである。本開示は、より具体的には、マルチスレッド化デジタル信号プロセッサに関する斬新な及び改良された非侵入型、スレッド選択式デバッギング方法及びシステムに関するものである。

#### 【背景技術】

# [0002]

電気通信及びその他の種類の電子装置とそれをサポートする映像、複雑な音声、テレビ会議及びその他のリッチソフトウェアアプリケーションでは、信号処理を含むことがます多くなっている。信号処理は、複雑であるが反復的なアルゴリズムにおいて高速な学計算及びデータ生成を行うことが要求される。多くのアプリケーションは、リアルタイムでの演算が要求され、すなわち、信号は時間の連続関数であり、数値処理のためにサンプしてデジタル信号に変換しなければならない。プロセッサは、到着したサンプに関する個別の演算を行うアルゴリズムを実行しなければならない。デジタル信号プロセッサ(DSP)のアーキテクチャは、該アルゴリズムを処理するように最適化される。優れた信号処理エンジンの特徴は、高速で柔軟な算術演算ユニットと、演算ユニットへの又は演算ユニットからの制限されないデータフローと、演算ユニット内における拡張された精密な動的範囲と、デュアルアドレス生成器と、効率的なプログラムシーケンシングと、プログラミングの容易さと、を含む。

#### [0003]

DSP技術の1つの有望な用途は、通信システム、例えば、衛星又は地上リンクを通じてのユーザー間における音声とデータの通信をサポートする符号分割多元接続(CDMA)システム、を含む。多元接続通信システムにおけるCDMA技術の使用は、"SPREAD SPECTRUM MULTIPLE ACCESS COMMUNICATION SYSTEM USING SATELLITE OR TERRESTRIAL REPEATERS"(衛星又は地上中継器を用いた拡散スペクトル多元接続通信システム)という題名を有する米国特許番号 4 , 9 0 1 , 3 0 7 及び"SYSTEM AND METHOD FOR GENERATING WAVEFORMS IN A CDMA CELLULAR TELEHANDSET SYSTEM"(CDMAセルラーテレハンドセットシステムにおいて波形を生成するためのシステム及び方法)という題名を有する米国特許番号 5 , 1 0 3 , 4 5 9 において開示されており、両特許とも、請求される主題の譲受人に譲渡されている。

# [0004]

CDMAシステムは、典型的には、1つ以上の基準に準拠するように設計される。1つの該第1世代の基準は、"二重モード広帯域拡散スペクトルセルラーシステムに関するTIA/EIA/IS-95端末-基地局互換性基準"であり、以下ではIS-95基準と呼ばれる。IS-95CDMAシステムは、音声データ及びパケットデータを送信することができる。第1世代よりも効率的にパケットデータを送信することができるより新しい世代の基準が、"第3世代パートナーシッププロジェクト"(3GPP)と呼ばれるコンソーシアムによって提供され、一般人が簡単に入手可能である一組の文書、例えば、文書番号3G TS 25.211、3G TS 25.213、及び3G TS 25.214、において具体化されている。3GPP基準は、以下ではW-CDMA基準と呼ばれる。

# [0005]

例えばW-DCMA基準を採用する複雑なDSP運用ソフトウェアは、強固な開発ツールが要求される。該開発ツールは、符号の生成、インテグレーション、試験、デバッギング、及びアプリケーション性能の評価のための開発ツールを含むことができる。ソフトウェア又は複雑なDSPアプリケーション、例えば高度な電気通信アプリケーション、を開発及び運用する際には、精巧であるがその一方で非侵入型のデバッギングソフトウェアが必要である。すなわち、デバッギングソフトウェアアプリケーションは、ソフトウェアの欠陥及び運用上の問題の訂正をモニタリング、試験、及びサポートする上で十分に強固で

10

20

30

40

なければならないだけでなく、デバッギング動作中にコアプロセッサソフトウェアと干渉 しないように動作できなければならない。さもないと、コア処理ソフトウェア内のいずれ の問題も、該デバッギングソフトウェアを使用中に検出することができず又は適切に検出 することができない。

# [0006]

例えば、リアルタイム映像ソフトウェアを最適化及びデバッグするためには、サイクルが正確なプロファイリング及び非侵入型のデバッギングという特長が極めて重要である。さらに、開発ボードは、広範なリアルタイムの試験を可能にするために大量の試験データをプロセッサ内に又はプロセッサから移動させるためのサポートが必要である。これらの及びその他の状況は、非侵入型のコアプロセッサソフトウェアデバッギングを要求する。従って、マルチスレッド化デジタル信号プロセッサにおいては、マルチスレッド化オペレーティングソフトウェアを非侵入的にデバッグする必要がある。さらに、リアルタイムオペレーティングソフトウェアが存在する環境においては、侵入型デバッギングプログラムが引き起こすことがあるソフトウェアの変更は、プロセッサ内において起きることを明らかに変更させ、必要なデバッギング動作に加えてソフトウェアの運用上の問題の決定に対しても悪影響を及ぼす可能性がある。

# [0007]

上記により、対話形式でかつマルチスレッド化デジタル信号プロセッサのリアルタイムの挙動に対して非侵入的に動作することができるDSPデバッギングプロセスが必要であることが明確になる。

#### [ 0 0 0 8 ]

マルチスレッド化されたDSPにおいては、1つ以上のスレッド間における対話もコアプロセッサの誤動作を引き起こすことがある。このことは、個々のスレッドがプログラミングされたとおりに及び希望されるとおりに個々に動作できるにもかかわらず当てはまることがある。さらに、動作中のスレッドの異なる組合せも、デバッギングソフトウェアによる解析を行うのが有益である異なる種類のプログラミング上の問題を引き起こす可能性がある。

# [0009]

さらに、マルチスレッド化DSPにおいては、デバッギング動作を行うことが望まれる数多くのポイント、すなわちブレークポイントが存在することができる。該ブレークポイントは、コアプロセッサのアプリケーションに影響を及ぼすハードウェアの状態、ソフトウェアの状態、外部の状態、及びその他の状態に起因して生じることができる。好ましいことに、柔軟な型のマルチスレッド化DSPデバッギングソフトウェアアプリケーションは、コアプロセッサアプリケーションのデバッギングを要求する非常に様々な状態に対処する。実際、柔軟であるためには、デバッギングソフトウェアがデバッギングソフトウェアの動作を必要とする状態に従って動的に変化することが要求される。

# [0010]

これらの考慮事項を念頭に置き、個々のスレッドのデバッギングをサポートするマルチスレッド化DSPデバッギングプロセスが必要であることは明確である。

## [0011]

コア処理アプリケーションのニーズに従って1つ、2つ、又はそれよりも多いスレッドのスレッド選択式デバッギング動作を許可するマルチスレッド化DSPデバッギングプロセスの必要性も存在する。

# [0012]

マルチスレッド化DSPがDSPの動作に影響を及ぼす非常に様々な状態、例えば、デバッギングブレークポイントを確立することができるハードウェア状態、ソフトウェア状態、外部状態、及びその他の状態、を有するデバッギングプロセスに従事することを許可する方法及びシステムの必要性も存在する。

#### 【発明の概要】

# [0013]

20

10

30

40

マルチスレッド化デジタル信号プロセッサに関する非侵入型スレッド選択式デバッギング方法及びシステムを提供するための技法が開示され、該技法は、デジタル信号プロセッサの動作と、パソコン、パーソナルデジタルアシスタント、ワイヤレスハンドセット、及び同様の電子デバイスにおいて動作するアプリケーションを含むますます強力になるソフトウェアアプリケーションに関するデジタル信号プロセッサ命令の効率的な使用と、の両方を向上させ、さらに関連するデジタルプロセッサの速度及びサービス品質を向上させる

# [0014]

開示される主題の一側面により、マルチスレッド化デジタル信号プロセッサの非侵入型 デ バ ッ ギ ン グ に 関 す る 方 法 及 び シ ス テ ム が 提 供 さ れ る 。 前 記 方 法 及 び シ ス テ ム は 、 デ バ ッ ギング命令を第 1 の組のレジスタ内に格納し、処理命令を第 2 の組のレジスタ内に格納す ることを許容する。前記第2の組のレジスタは、前記第1の組のレジスタと異なる。前記 方法及びシステムは、前記マルチスレッド化デジタル信号プロセッサの少なくとも1つ以 上のスレッドを用いてマルチスレッド化プロセスにおいて処理命令をさらに実行する。前 記処理命令の部分組は、少なくとも1つのデバッギングイベントを生成するためのブレー クポイント命令である。前記プロセスは、前記ブレークポイント命令のうちの少なくとも 1つの前記実行に応じて少なくとも1つのデバッギングイベントを生成し、前記デバッギ ングイベントに応じてデバッギング命令を実行し、前記デバッギング命令は、前記マルチ ス レッ ド 化 デ ジ タ ル 信 号 プ ロ セ ッ サ の 少 な く と も 1 つ 以 上 の ス レ ッ ド を デ バ ッ ギ ン グ 動 作 モードに移行させることによって前記マルチスレッド化デジタル信号プロセッサ内におけ る処理命令の前記実行を非侵入方式でデバッグすることを許容する。本開示は、前記マル チ ス レ ッ ド 化 デ ジ タ ル 信 号 プ ロ セ ッ サ の ス レ ッ ド の 前 記 部 分 組 に お け る デ バ ッ ギ ン グ 命 令 の前記実行を報告するために前記複数のデバッギング命令の前記実行からのデバッギング リターンを生成する。

#### [0015]

開示される主題のこれらの利点とその他の利点、及び追加の斬新な特長は、ここにおいて提供される説明から明確になるであろう。この発明の概要の意図は、請求される主題に関する包括的な説明を提供することではなく、主題の機能の一部について簡単に概説することである。ここにおいて提供されるその他のシステム、方法、特長及び利点は、以下の図及び発明を実施するための形態を検討し次第当業者に明確になるであろう。これらのすべての追加のシステム、方法、特長及び利点は、この説明の中に含められ、さらに添付される請求項の適用範囲内に含められることが意図される。

【図面の簡単な説明】

# [0016]

開示される主題の特長、性質、及び利点は、以下の発明を実施するための形態を図面と 併読することでより明確になるであろう。なお、図面全体において同様の参照文字は同様 の要素を識別する。

【 図 1 】本実施形態を実装することができる通信システムの単純化されたブロック図である。

【図2】本実施形態の教示を実行するためのDSPアーキテクチャを示す。

【図3】開示される主題の技術的利点を提供するデジタル信号プロセッサの一実施形態の アーキテクチャブロック図を提供する。

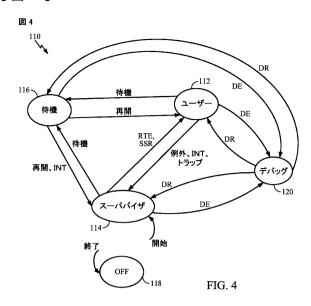

【図4】非侵入型デバッギング動作モードにおける動作を含む本開示のモード制御に関する側面の機能ブロック図である。

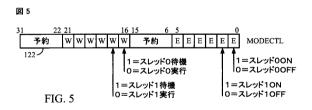

【 図 5 】 本 開 示 の デ バ ッ ギ ン グ 動 作 を 達 成 す る た め の モ ー ド 制 御 レ ジ ス タ を 示 し た 図 で あ る 。

【 図 6 】 本 開 示 の 非 侵 入 型 デ バ ッ ギ ン グ ア ル ゴ リ ズ ム の 様 々 な 側 面 に 関 す る 流 れ 図 で あ る

【発明を実施するための形態】

[ 0 0 1 7 ]

10

20

30

20

30

40

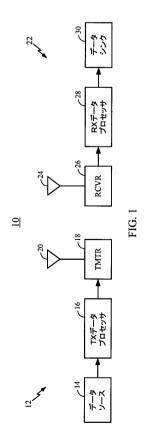

50

マルチスレッド化デジタル信号プロセッサに関する非侵入型スレッド選択式デバッギング方法及びシステムに関する開示される主題は、ここにおいて提示される利益が有利であることができるあらゆる型のマルチスレッド化処理に関して用途を有する。 1 つの該用は、電気通信において現れ、特に、 1 つ以上のデジタル信号処理回路を採用するワイヤレスハンドセットにおいて現れる。該ワイヤレスハンドセットをどのようにして用いることができるかについて説明するために、図1は、開示される割り込み処理方法及びブロスの提示される実施形態を実装することができる通信システム10の単純化たブロ以上のので提供する。送信機ユニット12において、データは、データ源14から、1つのアナログ信号を生成するとでではブロックで送信される。次に、アナログ信号を変調、フィルタリング、増幅、及びアップコンバージョンして変調された信号を生成する送信機(TMTR)18に提供される。変調された信号は、アンテナ20を介して1つ以上の受信機ユニットに送信される。

[0018]

受信機ユニット22においては、送信された信号は、アンテナ24によって受信されて受信機(RCVR)26に提供される。受信機26内において、受信された信号が増幅、フィルタリング、ダウンコンバージョン、復調、及びデジタル化されて同相の(I)及び(Q)サンプルが生成される。これらのサンプルは、受信(RX)データプロセッサ28によって復号及び処理されて送信されたデータが復元される。受信機ユニット22における復号及び処理は、送信機ユニット12において実行される符号化及び処理を補完する形で実行される。復元されたデータは、データシンク30に提供される。

[ 0 0 1 9 ]

上述される信号処理は、音声、映像、パケットデータ、メッセージ送信、及びその他の種類の通信を一方向に送信することをサポートする。双方向通信システムは、2方向データ送信をサポートする。しかしながら、説明を単純化するため、図1には他方の方向に関する信号処理は示されていない。通信システム10は、地上リンクを通じてのユーザー間における音声及びデータ通信をサポートする符号分割多元接続(CDMA)システム、時分割多元接続(TDMA)通信システム(例えば、GSM(登録商標)システム)、周波数分割多元接続(FDMA)通信システム、又はその他の多元接続通信システムであることができる。1つの特定の実施形態においては、通信システム10は、W-CDMA基準に準拠するCDMAシステムである。

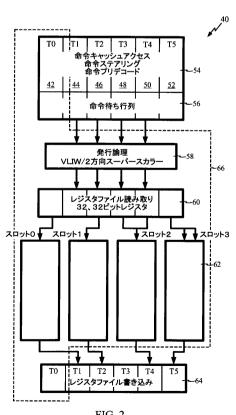

[0020]

図2は、図1の送信データプロセッサ16及び受信データプロセッサ28として働くことができるDSP40アーキテクチャを示す。DSP40は、ここにおいて提示されっかまたび概念を実効的に用いることができる非常に数多くの可能なデジタル信号プロセッサにおいては、スレッドエ0:エ5(参照番号42乃至52)は、異なるスレッドからのにおいては、スレッドエ0:エ5(参照番号42乃至52)は、エ0:エ5に関する命令の組を含む。回路54は、命令アクセス機構を表し、スレッドエ0に関する命令をフェッチするために用いられる。回路54に関する命令は、プロセッサパイプライに発行する。本のである。命令待ち行列56内の命令は、プロセッサパイプライに発行するを発行があるがあるである。とができる。選択されたスレッド面のスタファイル60が読まれ、読み取られたデータがSLOT0:SLOT3に関するを形態において採用されるパケットグループの結合に関するものである。

[0021]

実行データ経路62からの出力は、DSP40の動作からの結果を戻すために、同じく個々のスレッドT0:T5を受け入れるように構成されたレジスタファイル書き込み回路64に向かう。従って、回路54及びそれよりも前からレジスタファイル書き込み回路64までのデータ経路は、処理パイプライン66を形成する。本実施形態は、最大で6つの

20

30

40

50

スレッドT0:T5を有する単一のプロセッサを採用することができる。プロセッサパイプライン66は、6つのステージを有し、これは、回路54からレジスタ60及び64にデータ項目をフェッチするために必要な最低限のプロセッササイクル数と一致する。DSP40は、プロセッサパイプライン66内の異なるスレッドT0:T5の命令を同時並行して実行する。すなわち、DSP40は、6つの独立したプログラムカウンタ、プロセッサパイプライン66内のスレッドT0:T5の命令を区別するための内部タギング機構、及びスレッドスイッチをトリガーする機構を提供する。

# [0022]

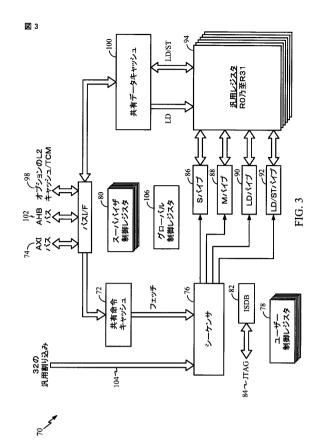

従ってDSP40は、非常に様々な信号、画像、及び映像処理用途において高性能及び 低電力であるように設計された汎用デジタル信号プロセッサを提供する。図3は、開示さ れ る 主 題 の 1 つ の 表 示 に 関 す る 関 連 づ け ら れ た 命 令 セ ッ ト ア ー キ テ ク チ ャ の 幾 つ か の 側 面 を含むDSP40アーキテクチャの概要を示す。DSP40アーキテクチャの実装は、イ ン タ ー リ ー ビン グ さ れ た マ ル チ ス レ ッ ド 化 ( I M T ) を サ ポ ー ト す る 。 こ の 実 行 モ デ ル に おいては、ハードウェアは、パイプライン内の異なるスレッドからの命令をインターリー ビングすることによって複数のハードウェアスレッドT0:T5の同時並行実行をサポー トする。この特長は、DSP40がコアとメモリの高い利用を依然として維持しながら積 極的なクロック周波数を含むことを許容する。IMTは、アウトオブオーダー実行、広範 な転送ネットワーク、等の高コストの補償機構を必要とせずに高スループットを提供する 。さらに、DSP40は、IMTの変形、例えば、M.アーメド、等による、"Variable Interleaved Multithreaded Processor Method and System" (可変のインターリービン グされたマルチスレッド化プロセッサに関する方法及びシステム)及び "Method and Sys tem for Variable Thread Allocation and Switching in a Multithreaded Processor" (マルチスレッド化されたプロセッサにおける可変スレッド割り当て及び切り換えに関す る方法及びシステム)という題名を有する共通譲渡米国特許出願において開示される変形 及び斬新な手法、を含むことができる。

## [0023]

図3は、特に、開示される主題の教示を採用することができる単一のスレッドに対して適用されるDSP40に関するコア処理アーキテクチャ70ブロック図を提供する。ブロック図70は、AXIバス74からバスインタフェース(I/F)73を介して命令を受け取る共有命令キャッシュ72を描き、これらの命令は、混合された16ビットと32ビットの命令を含む。これらの命令は、スレッドT0:T5のシーケンサ76、ユーザー制御レジスタ78、及びスーパバイザ制御レジスタ80に届く。開示される主題のコアレベルシステムアーキテクチャは、JTAGインタフェース84を介してコアプロセッサ70をインタフェースするインシリコンデバッギングシステム(ISDB)82も含み、以下ではこれらの両方がさらに詳細に説明される。

# [0024]

シーケンサ76は、ハイブリッド2方向スーパースカラー命令及び4方向VLIW命令をS‐パイプユニット86、M‐パイプユニット88、LD[Load]‐パイプ90、及びLD/ST[Store]‐パイプユニット92に提供し、これらの全ユニットは、汎用レジスタ94と通信する。AXIバス74は、バスI/F73を介して、スレッドT0:T5への共有データキャッシュ96LD/ST命令とも通信する。オプションのL2キャッシュ/TCM98信号は、共有データTCM100を有するLD/ST命令を含み、LD/ST命令は、さらにスレッド汎用レジスタ94に流れる。AHB周辺バス102から、MSM専用コントローラ104は、T0:T5と割り込みを通信し、割り込みコントローラ命令と、デバッギング命令と、タイミング命令と、を含む。グローバル制御レジスタ106は、スレッドT0:T5と制御レジスタ命令を通信する。

# [0025]

従って、DSP40は、6つの仮想DSPコアを含み、各仮想DSPコアは、グローバル制御レジスタ106と、プライベートスーパバイザ制御レジスタ80と、を含む。グローバル制御レジスタ106は、全スレッド間で共有される。各スレッドは、共通データキ

20

30

40

50

ャッシュ及び共通命令キャッシュを共有する。ロード、ストア、及びフェッチの各動作は、共通のバスインタフェースによって対処される。高性能AXIバス74及びそれよりも低性能のAHBバス102は、データ及び命令トラフィックをオフコアメモリ及び周辺装置に接続するために用いられる。統合されたレベル2メモリ(キャッシュ及び/又はTCM)入力98はオプションである。周辺装置のアクセスは、メモリによってマッピングされるロード及びストアを通じて行うことができる。AHBとAXIとの間における物理アドレスパーティションは、MSMレベルで構成することができる。

# [0026]

明確なことであるが、DSP40に関する提示されるアーキテクチャは、経時で発展及び変化することができる。例えば、DSP40が用いることができる命令キャッシュ数は、6から1に、又はその他のキャッシュ数に変更することができる。TCM100におけるスーパースカラーディスパッチL1データ、及びその他のアーキテクチャ上の側面は、変更することができる。しかしながら、本主題は、非常に様々なコンフィギュレーションにおいて及びDSP40の修正の大規模な系統に関して継続的な関連性を有することができる。

#### [0027]

ISDB82は、JTAGインタフェース84を介して、DSP40に関するハードウェアデバッガを提供する。ISDB82は、システム又はスーパバイザ専用レジスタを共有することによってJTAGインタフェース84を通じてソフトウェアデバッグ機能を提供し、これらのレジスタは、1つのスレッドベースのスーパバイザ制御レジスタ80、及び全スレッド間におけるグローバル制御レジスタ106に分割される。システム制御レジスタは、1つのスレッドごとの割り込みと例外制御及び1つのスレッドごとのメモリ管理活動に関して用いられる。グローバルレジスタは、デバッギング動作のためにISDB82と対話することを許容する。

#### [0028]

ISDB82は、DSP40が動作する間にソフトウェア開発者が自己のソフトウェアをデバッグするのを可能にする。ISDB82ハードウェアは、ISDB82において動作中のソフトウェアデバッガプログラムと組み合わせることで、DSP40オペレーティングシステムソフトウェアをデバッグするために用いることができる。ISDB82は、デバッギングハードウェアスレッドを個々にサポートする。ユーザーは、スレッド実行を中断すること、スレッドレジスタを閲覧及び変更すること、命令とデータメモリ、単一ステップスレッド、を閲覧及び変更すること、スレッドに命令をスタッフィングすること、及びスレッド実行を再開することができる。信頼されるユーザーは、すべてのISDB82の特長にアクセス可能であり、信頼されないユーザーは、1つ以上の特長にアクセス可能である。

# [0029]

ISDB82は、プログラムカウンタ上に常駐するISDB82デバッギングソフトウェアと通信するためにデバッガインタフェースカードと通信することができ、すべてJTAGインタフェース84を通じて行うことができる。ホストデバッガソフトウェアは、ISDB制御レジスタを読み取る及び書き込むことによってISDB82と対話することができる。通信は、例えば、読み取り/書き込みの対象となるISDBレジスタを識別する40ビットパケット、及び32ビットデータペイロードを通じて行うことができる。この動作をサポートするパケットフォーマットは、各々の幅が32ビットであることができる最大で64の制御レジスタであることができる。

#### [0030]

ISDB82は、デバッギング動作中にセキュリティを制御するための信頼されるレジスタを含む。ISDB82trustedがセットされた場合は、すべてのISDB82レジスタがデバッガソフトウェアにとって可視であり、すべてのISDBコマンドを使用可能である。ISDB82trustedがクリアされた場合は、ISDB82は、制限された一組の動作のみを許可する。

20

30

40

50

#### [ 0 0 3 1 ]

一定のISDB82レジスタがコアソフトウェアにとって可視であるようにすることができる。これらのレジスタは、スーパバイザ(SUPERVISOR)モード制御レジスタ転送命令を介してアクセス可能である。コア命令は、ブレークポイント命令を含む。ISDBtrustedがセットされたときには、この命令は、実行中のスレッドにデバッグ動作モード120に入らせる。この移行は、スレッド制御をISDB82に移行させる。ブレークポイントを実行したスレッドに加えて、その他のスレッドは、ISDB82プログラミングに従って選択的にデバッグ(DEBUG)モード120に入ることができる。ISDB82が信頼されないか又はイネーブルにされない場合は、この命令はNOPとして処理される。好ましいことに、ブレークポイント命令は、パケット内における唯一の命令である。

[0032]

図4は、デバッギングプロセス中におけるISDB82の動作を含むDSP40の様々なモード制御側面に関する処理モード図110を示す。図5は、本開示のデバッギング動作を達成させるためのモード制御レジスタ122を示す。一実施形態においては、モード制御レジスタ122は、開示される動作モードへの / からの移行を援助し、ビット31乃至22を占有する予約セクションと、待機ビット21乃至16と、予約ビット16乃至6と、エラービット5乃至0と、を含む。モード制御レジスタ122は、数多くの異なる方法で実装できるが、図5の例示される実施形態は、ISDB82が所有する様々な性質及びISDB82が可能にする動作を含むISDB82に関する以下の説明を理解するのに役立つことができる。

[0033]

次に、図4に関して、DSP40は、全スレッドに対してグローバルであり個々のスレ ッドに対してローカルである処理モードをサポートする。各DSP40ハードウェアスレ ッドは、すべて図4において示されるように、2つの実行モード、ユーザー(USER) モード112とスーパバイザモード114、及び3つの非処理モードすなわち待機(WA IT)モード116、OFFモード118、及びデバッグモード120、を個々にサポー トする。スレッドのモードは、その他のスレッドと独立しており、例えば、1つのスレッ ドは待機モード116であることができ、他のスレッドは、ユーザーモード112であり 、以下同様である。図4の1つのスレッドごとのモード状態図は、様々な命令又はイベン トによってサポートされる。これらは、"例外"すなわち内部例外イベントと、"Int " すなわち外部割り込みイベントと、" RTE " すなわち例外モードからのソフトウェア リターン命令と、"SSR"すなわちSSRレジスタ命令の更新と、あらゆるモードから 入力することができる " 停止 " すなわちソフトウェア停止命令と、同じくあらゆるモード から入力することができる"開始"すなわちソフトウェア開始命令と、"トラップ"すな わちソフトウェアトラップ命令と、"待機"すなわちソフトウェア待機命令と、"再開" すなわちソフトウェア再開命令と、"DE"すなわちデバッグイベントと、"DR"すな わちデバッグ命令と、を含む。請求される主題の異なる実装における機能は、ここにおい て提示される機能とわずかに異なることができる一方で、 " 開始 " 、 " 待機 " 、 " 再開 " 、 " DE " 、及び / 又は " DR " の意味は、請求される主題の適用範囲と一致する最も広 義の解釈を行うことができる。

[0034]

レジスタは、DSP40においてユーザーモード112及びスーパバイザモード114の両方において利用可能である。ユーザーモードレジスタは、一組の汎用レジスタ及び一組の制御レジスタに分割される。汎用レジスタは、アドレス生成、スカラー及びベクトル算術を含むすべての汎用演算に関して用いられる。制御レジスタは、ハードウェアループ、プレディケート、等の特殊目的の機能をサポートする。

#### [0035]

汎用レジスタは、幅が32ビットであり、単一レジスタとして又は2つのレジスタの整列された対としてアクセスすることができる。汎用レジスタファイルは、命令に関する全

20

30

40

50

オペランドを提供し、ロード/ストアに関するアドレスと、数値命令に関するデータオペランドと、ベクトル命令に関するベクトルオペランドと、を含む。

# [0036]

DSP40レジスタ及び命令は、標準的なC言語規約を採用するソフトウェアスタックの効率的な使用をサポートする。スタックは、高アドレスから低アドレスに向かって増大する。スタックポインタレジスタは、スタック最上部における最後の有効要素を指す。プッシュ動作は、最初にスタックポインタの数を減らし次にスタックにデータを書き込み、ポップ動作は、スタックから読み取ってスタックポインタの数を増やす。

# [0037]

スタック上の手順フレームは、関数呼び出しに関するリターンアドレス及び手順によって必要とされるすべてのローカル変数とデータを含む。さらに、フレームポインタがリターンアドレスの後に格納される。このフレームポインタは、スタック上における前手順フレームのアドレスを含む。この目的は、デバッガがメモリ内のスタックを検討して呼び出しシーケンス、関数パラメータ、等を簡単に決定するのを可能にすることによってデバッグを容易にすることである。

#### [0038]

デバッグモード120は、スレッドがISDB82からのコマンドを待っている特別な状態である。例えばソフトウェアブレークポイント命令の実行、ISDB82からのブレークポイントの発生によって、ISDBデバッグイベントが生じるごとに、示されたスレッドがデバッグモード120に入ることができる。デバッグモード120においては、コアは、JTAGインタフェース84からのコマンドを介してISDB82によって制御される。ISDB82が再開コマンドの実行に起因してスレッドをリリースすると、スレッドは、現在のモード設定に従って動作を再開することができる。スレッドがデバッグモード120にあるときには、ISDB82によって制御することはできない。デバッグモード120におるスレッドをターゲットにした、実行中のスレッドからの待機命令、再開命令、開始命令、又は停止命令は、無視することができる。同様に、マスク不可割り込み(NMI)は、デバッグモード120にあるスレッドは無視することができる。

# [0039]

ハードウェアリセット(HARDWARE RESET)モード(示されていない)及びデバッグモード120は、全スレッドに対してグローバルである。ハードウェアリセットピンがアサートされるごとに、あらゆるスレッドがどのような処理状態であるかにかかわらず、DSP40は、ハードウェアリセットモードになることができる。リセットモードにおいては、全レジスタが各々のリセット値に設定される。どのような処理も、ハードウェアリセットピンがデアサートされるまで行うことができない。リセットピンがアサートされた時点で、プロセッサは、リセットモードに移行することができ、全レジスタットである。リセットピンがデアサートされた後は、スレッドでリセット値にリセットすることができる。このことは、スレッドエードバイザモード114に入らせてリセットされたベクトル位置での実行を開始させることができる。その他の全スレッドは、オフ状態であることができる。この時点においては、ソフトウェアは、各スレッドに関するモード移行を個々に自由に制御することができる。

#### [0040]

各スレッドは、そのスレッドに関してOFFモード118への及びOFFモード118からの移行を制御する1つの移行ビットをモード制御レジスタ122において有することができる。停止命令を介して移行ビットに書き込むことは、関連づけられたスレッドをOFFにする。開始命令を介して移行ビットに書き込むことは、スレッドをオンにし、ソフトリセット割り込みをトリガーする。各スレッドは、待機モード116への及び待機モード116からの移行を制御するための1つの待機ビットをモード制御レジスタ122に含むことができる。待機命令を介して待機ビットに書き込むことは、関連づけられたスレッドをアイドル状態にすることができ、他方、再開命令を介しての書き込みは、待機モード

20

30

40

50

1 1 6 が設定される前に行っていたあらゆることをスレッドに再開させることができる。 【 0 0 4 1 】

ブレークポイントを用いることで、DSP40の6つのスレッドは、個々にデバッグモ ー ド 1 2 0 に入ること及びデバッグモード 1 2 0 から出ることができる。ブレークポイン トトリガーは、ISDB82においてサポートされる5つの異なる種類のブレークポイン トに対応する5つのソースから来ることができる。これらのブレークポイントは、ハード ウェアブレークポイントと、ソフトウェアブレークポイントと、 E T M ブレークポイント と、JTAGインタフェースブレークポイントと、外部ブレークポイントと、を含む。ス レッドは、ブレークポイントをヒットした時点で、現行モード(例えば、待機/実行(R UN))からデバッグモード120に移行する。デバッグモード120において、スレッ ドは、ISDB82からのコマンドを待つ。OFFモード118にあるスレッドはパワー ダウンされ、ISDB82からのコマンドを受け入れることができない。デバッグモード 120に入るレーテンシーは、実装によって定義される。例えば、本開示においては、イ ベント電力崩壊に関連するとして定義される。例えば、一実装は、デバッグモード120 に入る前に、所定の動作を完了させる、例えば未解決のロード要求を終了させる、ことを 選択することができる。一実施形態においては、スレッド識別子レジスタは、8ビットの 読 み 取 り / 書 き 込 み フ ィ ー ル ド を 含 み 、 ソ フ ト ウ ェ ア ス レ ッ ド 識 別 子 を 保 持 す る た め に 用 いられる。このフィールドは、ブレークポイントとマッチさせるためにハードウェアデバ ッガによって用いられる。

# [0042]

ブレークポイントプロセスに入る方法は、幾つかの異なる方法が存在する。例えば、2つのハードウェアブレークポイントが存在する。レジスタが予め決められた値と等しい場合は、プログラムカウンタ(PC)が予め決められた値にマッチするときに、プロセスがデバッグモード120になる。PCに加えて、その他の修飾子、例えば、アドレス翻訳(物理アドレス又は仮想アドレス)等のスレッドID、が存在することができる。ASIDは、プロセスにおけるプロセスID又はマルチスレッド化プロセスにおける特定のスレッドと類似のタグである。このため、物理アドレス、仮想アドレス、ASID、PC、又はその他の修飾子を用いて、プロセス空間内のプログラムの位置のフィックスを随意に入手することができる。

# [ 0 0 4 3 ]

ISDB82は、2つの出力割り込みピンも定義する。これらの信号は、ISDB82を出てMSM104内に入り、MSMレベルでストラップされる。これらの2つの信号は、ブレークイベント及びJTAGインタフェース84コマンドである。ブレークイベントコマンド時においては、ISDB82は、示されたスレッド番号においてブレークポイントが生じるごとにこの割り込みを呼び出すようにプログラミングすることができる。JTAGインタフェース84は、この割り込みを呼び出すためのコマンドを送る。

### [0044]

ハードウェアブレークポイントは、スレッドプログラムカウンタ、ASID(アドレス空間識別子)、及びスレッド識別子レジスタのうちの1以上をISDBによってプログラミングされた値とマッチさせる。マッチ条件が満たされているときには、スレッドは、デバッグモード120に入る。ブレークポイントをヒットしたスレッドに加えて、その他のスレッドもデバッグモード120に入るように構成することができる。このことは、例えばブレークポイントコンフィギュレーションレジスタプログラミングを通じて達成させることができる。

# [0045]

ハードウェアブレークポイントは、様々な特長、例えば、物理的又は仮想であることができる32ビットプログラムカウンタ値をマッチさせる、6ビットASID値をマッチさせる、8ビットスレッド識別子値をマッチさせる、及び/又はブレークポイントをヒットした時点で強制的にその他のスレッドをデバッグモード120に入らせる、等、をサポー

20

30

40

50

トすることができる。ハードウェアブレークポイントを設定するために、ブレークポイントプログラムカウンタ及びブレークポイントコンフィギュレーションレジスタは、JTAGインタフェース84を通じて、そして次にISDB82コンフィギュレーションレジスタを介してイネーブル及び構成されたブレークポイントを用いて設定することができる。

開示される主題は、一定のソフトウェアブレークポイントも提供する。例えば、ユーザーレベルブレークポイント命令を用いてハードウェアデバッグモード120に入ることができる。この命令が実行されると、コアは、システムコンフィギュレーションISDBtrustedビットがセットされた場合は、スレッドはデバッグモード120に入ることができる。ISDBtrustedがクリアされるか又はISDBがディスエーブルにされたときには、ブレークポイント命令の実行はNOPとして処理することができる。ブレークポイント命令のプログラムカウンタアドレスに対する制限は存在しない。しかしながら、ブレークポイント命令は、その他の命令とパケット化することができない。

# [0047]

[0046]

# [ 0 0 4 8 ]

従って、開示される主題は、デバッグモード120に入らせるブレークポイントの場合にデバッグモード120に移行するための経路を提供する。開示される主題は、マルチスレッド化デジタル信号プロセッサ内のいずれのスレッド又はスレッドの組がデバッグ120に入るかを制御する。ETMブレークポイントデバッギングは、プロセッサデバッギングに関して用いることができる性能プロファイリング等の動作行う。そのブロックは、デバッギングプロセスに入るためのブレークポイントを提供することができる。

# [0049]

この状況においては、ハードウェアブレークポイント及びETMブレークポイントスレッド番号MASKの両方が、マッチしているスレッドに関してイネーブルにされる。この例においては、DSP40は、ハードウェアブレークポイントがETMブレークポイントに引き続いてトリガーされるときのみにデバッグモード120に切り換わることができる。ETMブレークポイントが生じる前に生じるハードウェアブレークポイントトリガーは、無視することができる。ブレークポイントコンフィギュレーションが"0"に設定されるか又は設定されないときには、ハードウェアブレークポイント及びETMブレークポイントスレッド番号MASは通常どおりに挙動する。すなわち、イネーブルにされたときに、対応するブレークポイントトリガーは、スレッドを直ちにデバッグモード120に切り換えさせることができる。

# [0050]

$oxed{\mathsf{J}}\ \mathsf{T}\ \mathsf{A}\ \mathsf{G}\ \mathsf{T}\ \mathsf{V}\ \mathsf{P}\ \mathsf{D}\ \mathsf{F}\ \mathsf{T}\ \mathsf{V}$   $oxed{\mathsf{D}}\ \mathsf{F}\ \mathsf{V}$   $oxed{\mathsf{D}}\ \mathsf{F}\ \mathsf{V}$   $oxed{\mathsf{D}}\ \mathsf{F}\ \mathsf{V}$

20

30

40

50

に入ることができる。ISDB82は、外部ブレークポイントを通じてマルチコアデバッグもサポートする。該ブレークポイントは、外部デバッグ要求信号において立ち上がりエッジが検出されたときにトリガーされる。このイベント時において、外部ブレークポイントスレッド番号マスクにおいて示される全スレッドがデバッグモード120に入ることができる。

# [0051]

開示される主題の他の特長は、"命令スタッフィング"と呼ばれる。命令スタッフィングは、ホストデバッギングプロセスがコアの状態を検査しようとするときに生じる。従って、ブレークポイントが生じたときには、プロセスは、コアを検討してコアにおいて動作が発生しているかどうかを決定することを試みる。この決定を行う仕組みは、デバッグ動作モード120に入りつつあるスレッドにおいてプロセッサ命令を実行することを目的としてそのプロセッサ命令を送ることである。

# [0052]

命令スタッフィング動作においては、命令は、デバッグモード120時にすべての影響 を受けているレジスタ全部又は一部分を読み取るようにプロセッサに指示することができ る。さらに、デバッグモード120は、予め決められた組の又は型の命令をロードするよ うにプロセッサに指示することができる。状態を読み取る又は書き込むことに加えて、基 本的にはいずれの命令も、このプロセスにおいて読み取ること又はコアに書き込むことが できる。例えば、何らかのアルゴリズム又はプロセスをプロセスコアにおいて実行するの が望ましい場合は、開示される主題は、一組のオプションを許容する。命令スタッフィン グプロセスにおいては、記憶場所に分岐し、プロセスは、動作のために符号をリリースす ることができる。該符号は、例えば、規定された一組の理由で一定の関数を実行するため の符号を含むことが可能である。1つの該理由は、複雑なデータ構造を処理するためであ ることができる。命令が、所定のデータ構造の全要素を読み出すことである場合は、プロ セスは、そのデータ構造を再構築することであることができる。該プロセスは、極端に難 しい可能性がある。データ構造を読み出すための一組の命令を備えることで、プロセスは 、その命令の組を呼び出して特定の命令を入手することであることができ、特定の命令は 、希望される要素(例えば、要素12)に従って実行することが可能である。このことは 、多くの型のデータ取り出し及び同様の動作を有意に単純化する。

# [ 0 0 5 3 ]

命令スタッフィングは、ISDB82がコアにおいて命令を実行する方法である。命令は、様々な理由で、例えば、コアレジスタ及びメモリを読み取る及び書き込むために、ユーザーに関して要約されたデバッガ動作のために、及びユーザーによって入力された命令に関して、スタッフィングされる。命令をスタッフィングするためには、ユーザーは、最初に、実行対象となる32ビット命令を用いてスタッフ命令レジスタをプログラミングはなければならない。命令スタッフィングに関して、ISDBコマンドレジスタは、最初にコマンドフィールドをスタッフィングに関定し、次にスレッド番号フィールドを命令をはいるスレッドに設定することによって書き込むことができる。選択されたスレッドができるスタッフィングできるようになる前にデバッグモード120であることができる。スレッド番号内の2つ以上のビットが設定されるか又は選択されたスレッドがデバッグモード120にない場合は、結果は未定義である。次に、スタッフィングされた命令(ユーザー又はスーパバイザ)の特権レベルの設定を含む段階が生じる。

# [0054]

スタッフコマンドを発行後は、選択された特権レベルを有する選択されたスレッドにおいて命令を実行することができる。命令スタッフィング中には、プログラムカウンタは数字が増えない。プログラムカウンタを用いるスタッフィングされた命令(分岐、又は例外を生じさせる命令)は、スレッドの現在のプログラムカウンタ値を用いることができる。スタッフィングされた命令が例外を生じさせる場合は、ISDB状態レジスタは、例外が発生したことを示すことができる。スレッドは、デバッグモード120にとどまることができる。スレッドの設計されたレジスタは、例外状態を反映させることができる。好まし

20

30

40

50

いことに、ISDB82デバッギングソフトウェアは、例外を発生させることができた命令をスタッフィング後にISDB状態レジスタに問い合わせて例外が発生したかどうかを確認する。

[0055]

例外が認識された時点においては、ここにおいて開示されるプロセスは、状況をどのように取り扱うかに関する幾つかの選択肢を含む。例えば、デバッガソフトウェアは、例外リターンポイントにおいてソフトウェア又はハードウェアブレークポイントをプログラミングすることを選択し、ハンドラーを実行するためにスレッドを再開することができる。次に、デバッガは、OS"helper"関数にスレッドをリダイレクションすることができる。次に、単一ステップを用いてハンドラーを実行することおよび手作業で問題を解決する(例えば、TLBを再ロードする)ことを行うことができる。しかしながら、具体的な戦略は、OS及び/又はソフトウェアデバッガの実装により異なることができる。

[0056]

レジスタ、キャッシュ、及びメモリは、適切な命令シーケンスをスタッフィングすることによってアクセスすることができる。命令に関するステップのシーケンスは、ISDBデバッギングアルゴリズムを用いてレジスタ及びキャッシュを読み取る/書き込むことを含むことができる。デバッガソフトウェアは、コアレジスタとISDBメールボックスとの間でデータを移動させるための適切な制御レジスタ転送命令をスタッフィングすることによってスレッドレジスタを読み取る/書き込むことができる。この命令は、例外が発生しないようにするためにスーパバイザ特権レベルを用いてスタッフィングすることができる。

[0057]

再開コマンドは、デバッグからコアモード制御レジスタにおいてプログラミングされたモードにスレッドを移行させるために用いられる。再開方法は、JTAGインタフェース84コマンド又は外部信号のいずれかから再開させる2つの方法がある。JTAGインタフェース84コマンドからの再開である場合は、コマンドマスクにおいて示された、デバッグモード120にあるスレッドが終了し、モード制御レジスタにおいて示されるモードになる。外部信号からの再開である場合は、外部再開スレッド番号MASKにおいて示され、デバッグモード120にあるスレッドが、モード制御レジスタにおいて示されるモードに移行する。

[0058]

ISDBリセットコマンドを実行することは、ハードウェアリセットを強制し、DSP全体(全スレッド)にリセットさせる。このことは、全レジスタを初期値、例えば電力オフスレッド1乃至5に設定し、リセット割り込みをスレッドTOに送る。一定のスレッドのみをリセットすることが希望される場合は、適切なマスク設定を用いて最初に開始命令をスタッフィングする手順で行うことができる。このことは、示されたスレッドに対してリセット割り込みを保留状態にすることができる。次に、プロセスは、希望されるスレッドにおいてISDB再開命令を実行することを含む。

[0059]

他の型のブレークポイントは、ホストがプロセッサにコマンドを送ってブレークを指示する」TAGインタフェース84ブレークポイントである。基本的に入り外部ピンが存在する。この実施形態においては、ISDB82制御レジスタは、JTAGインタフェース84を介してデバッガホストソフトウェアによってアクセスすることができる。ISDB82は、異なるデバッグタスクを実行し、DSP40コアプロセッサと通信するようにISDB82を構成するためにホストシステムによって用いることができる様々な制御レジスタを提供する。例えば、ISDB82状態レジスタは、ISDB82の現在の状態を示す。ISDB82状態レジスタのビットは、いずれのスレッドが"待機"対実行モードにあるかを示し、その他は、いずれのスレッドが"OFF"モードであるかを示す。これらは、コアモード制御レジスタのEビットフィールドを反映したものである。例えばOFFであるスレッドは、一般的にはデバッグできない。従って、ISDBコマンドがオフであ

20

30

40

50

るスレッドに送られる場合は、結果は未定義である。その他のデバッグモード 1 2 0 状態ビットは、いずれのスレッドがデバッグモード 1 2 0 であるかを示す。スレッドがデバッグモード 1 2 0 にあることをこれらのビットが示す場合は、待機/実行モードビットは、デバッグモード 1 2 0 に入る前にモードを示す。

# [0060]

さらにその他のビットは、スタッフコマンド状態、すなわちスタッフ命令プロセスが成功しているかどうか又はスタッフ命令が例外を発生させたかどうか、を示す。ISDBコマンド状態ビットは、ISDBコマンドが成功又は失敗であったかを表す。他の組のビットは、いずれかのスレッドがデバッグ120モードにあるときにグローバル割り込みディスエーブルを提供し、従って、デバッグモード120にあるスレッドに関しては割り込みがディスエーブルにされ、その他のスレッドに関してはイネーブルにされる。いずれかのスレッドがデバッグモード120にあるときには全スレッドに関して割り込みがディスエーブルにされる。

# [0061]

その他のビットは、外部再開信号に基づいていずれのスレッドが再開すべきかを示すフィールドを形成することができる。外部再開信号に基づき、マスクビットが設定されているスレッドに関して、そのスレッドがデバッグモード120にある場合は、前モードを再開することができ、その他の場合は影響がない。他のフィールドは、外部ブレークポイント要求時にいずれのスレッドがブレークすべきかを示す。マスクビットが設定されているスレッドに関して、ISDB82において外部ブレークポイント信号を受信した時点で、そのスレッドがデバッグモード120ない場合は、デバッグモードに入ることができ、その他の場合は影響がない。

## [0062]

さらに、ISDBコンフィギュレーション命令は、ISDB82の様々な特長をイネーブル又はディスエーブルにすることができる。いずれかのスレッドがデバッグモード120にあるときにグローバル割り込みディスエーブルが発生し、それによりデバッグモード120にあるスレッドに関する割り込みをディスエーブルにする。ISDBコンフィギュレーションレジスタ内の他のフィールドは、外部再開信号に基づいていずれのスレッドが再開すべきかを示すことができる。外部再開信号に基づき、マスクビットが設定されているスレッドに関して、該スレッドがデバッグモード120にある場合は、該スレッドは前モードを再開する。その他の場合は影響がない。

# [0063]

ISDBレジスタ内のさらに他のフィールドは、ISDB82が外部ブレークポイント要求を受け取った時点でいずれのスレッドがブレークすべきかを示すことができる。外部ブレークポイント信号を受け取った時点で、マスクビットが設定されているスレッドに関して、スレッドがデバッグモード120にない場合は、デバッグモード120に入ることができる。その他の場合は影響がない。

## [0064]

ブレークポイント情報レジスタは、デバッグモード120にあるスレッドに関して、いずれのトリガーがブレークポイントを発生させたかを示す。これは、ブレークポイント命令実行時にいずれの追加のスレッドがブレークすべきかを示す6ビットフィールドであることができる。最下位ビットは、スレッド番号0に関するビットであることができ、次のビットはスレッド番号1に関するビットであり、以下同様である。ブレークポイント命令実行時において、ブレークポイントを実行したスレッドは、デバッグモード120に入ることができる。さらに、このマスクにおいてビットが設定されているスレッドは、デバッグモード120に入ることができる。

#### [0065]

ISDB82からMSMに進む割り込み信号ブレークイベントが存在する。このマスクにおいて示されるスレッド番号がデバッグモード120に入るごとに、ブレークイベント割り込みが呼び出される。一実施形態においては、ビット0は、スレッド番号0に関する

20

30

40

50

ビットであり、ビット1はスレッド番号1に関するビットであり、以下同様である。デバッグモード120にあるスレッドに関して、これらのビットは、何がデバッグモード120への移行を生じさせたかを示す。デバッグモード120にないスレッドに関しては、これらのビットは未定義である。従って、ビットは、ハードウェアブレークポイント、ブレークポイント命令実行、ETMブレークポイント、JTAGインタフェース84ブレークポイント、外部ブレークポイントの存在を示す。さらに、その他のビットは、ブレークポイントソースを示すことができる。ブレークポイントプログラムカウンタは、ブレークポイントプログラムカウンタと同一のレジスタを含み、これらは、ハードウェアブレークポイントを制御することを除く。ブレークポイントコンフィギュレーションレジスタは、スレッドのプログラムカウンタレジスタと比較するために用いられる。

[0066]

ISDB82コマンドレジスタは、いずれのスレッドがデバッグモード120に移行できるかを示すためのブレークコマンドを含むことができる。再開コマンドに関して、いずれのスレッドが再開すべきかを示す。ISTEPコマンドは、いずれのスレッドがステップ・バイ・ステッププロセスにおいてステップすべきかを示す。スタッフ命令コマンドは、いずれのスレッドが命令スタッフィング動作を行うためのスタッフ命令を受け取ることができるかを示す。スタッフ命令特権は、幾つかのスタッフィングされた命令がユーザーモードにおいて実行するのを許容し、その他は、スーパバイザモードにおいて実行することができる。

[0067]

ブレークコマンドに基づき、DSP40は、スレッド番号マスクにおいて示される全スレッドをデバッグモード120に移行させることができる。再開コマンドは、スレッド番号マスクにおいて示される全スレッドを実行モードに移行させることをプロセッサに行わせる。ステップコマンドは、デジタル信号プロセッサが1つのパケットに関するスレッド番号マスク内において示される全スレッドをステップさせることを許容する。示されたスレッドがデバッグモード120にない場合は影響がない。

[0068]

スタッフコマンドは、スレッド番号マスクにおいて示されるスレッドにおけるスタッフ命令レジスタ内に含まれる 3 2 ビット命令を実行することをデジタル信号プロセッサに行わせる。マスク内の 1 つのビットのみをセットすることができる。示されるスレッドがデバッグモード 1 2 0 にない場合は、挙動は未定義である。リセットコマンドは、DSPへのハードウェアリセットを開始する。レジスタは、初期値に設定され、スレッド 1 乃至 5 がオフにされ、スレッド T 0 は、リセット割り込みが与えられる。割り込みコマンドに基づき、ISDB82は、JTAGインタフェース84コマンド割り込みを呼び出す。この信号は、ISDB82は、JTAGインタフェース84コマンド割り込みを呼び出す。この信号は、ISDB82イネーブルレジスタは、ISDB82の動作をイネーブルにし、さらに、"セキュリティ"ISDB82イネーブルビット及びISDB82クロックの状態を検査する

[0069]

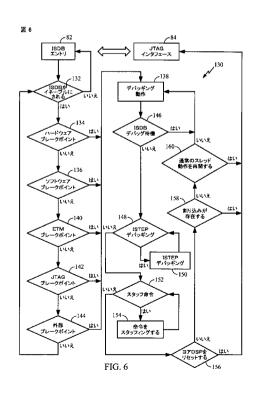

ISDB82の動作をサポートする様々なコマンドについて説明したが、ISDB82 デバッギング動作の典型的プロセスは、さらに有益であることができる。従って、図6は、本開示の様々な非侵入型デバッギングアルゴリズムの側面に関するISDB82流れ図を示す。図6のISDB82プロセスの流れは、様々な手法を用いて実行することができるが、提示される開示主題の基本的な流れは、希望される非侵入型デバッギング動作を達成する。従って、図6に関して、JTAGインタフェース84から、ISDB入口ステップ130において、プロセスの流れが開始することができる。

[0070]

ISDB入口ステップ130から、非侵入型デバッギングプロセスの流れは、ISDBがDSP40動作に関してイネーブルにされているかどうかを試験する、ISDBによってイネーブルにされるクエリ132に進む。ISDBがDSP40動作に関してイネーブ

20

30

40

50

ルにされている場合は、プロセスの流れは、ハードウェアブレークポイントクエリ134 に進む。ハードウェアブレークポイントクエリ134は、ハードウェアブレークポイント に遭遇しているかどうかを試験する。遭遇していない場合は、プロセスの流れは、ソフト ウェアブレークポイントクエリ136まで続くことができる。その他の場合は、プロセス の流れは、デバッギング動作が開始するデバッギング動作ステップ138に進む。ソフト ウェアブレークポイント136は、ソフトウェアブレークポイントの存在の有無を試験し - ソフトウェアブレークポイントが存在する場合はISDB82プロセスをデバッギング 動作ステップ138に向ける。ソフトウェアブレークポイントが存在しない場合は、プロ セスの流れは、ETMブレークポイントクエリ140まで続く。ETMブレークポイント ク エ リ 1 4 0 は 、 E T M ブ レ ー ク ポ イ ン ト の 存 在 の 有 無 を 試 験 し 、 E T M ブ レ ー ク ポ イ ン トが存在する場合はISDB82プロセスをデバッギング動作ステップ138に向ける。 ETMブレークポイントが存在しない場合は、プロセスの流れは、JTAGインタフェー ス 8 4 ブレークポイントクエリ 1 4 2 まで続く。JTAGインタフェース 8 4 ブレークポ イント142は、JTAG84ブレークポイントの存在の有無を試験し、JTABブレー クポイントが存在する場合は、ISDB82プロセスをデバッギング動作ステップ138 に向かわせる。JTABブレークポイントが存在しない場合は、プロセスの流れは、外部 ブレークポイントクエリ144まで続く。外部ブレークポイント144は、外部ブレーク ポイントの存在の有無を試験し、外部ブレークポイントの存在する場合は、ISDB82 プ ロ セ ス を デ バ ッ ギ ン グ 動 作 ス テ ッ プ 1 3 8 に 向 か わ せ る 。 外 部 ブ レ ー ク ポ イ ン ト が 存 在 しない場合は、プロセスの流れは、ISDBによってイネーブルにされるクエリ132に 戻る。このタイプのサイクルは、DSP40の動作中に繰り返すことができる。

[ 0 0 7 1 ]

ISDB82プロセスの流れがデバッギング動作ステップ138に進んだ時点で、"デバッグ待機"クエリ146は、待機モード116が有効かどうか試験する。有効である場合は、待機116モードが終了するまでデバッギング動作は行われない。待機モード116が有効でない場合は、プロセスの流れは、ISTEPデバッギングクエリ148に進む。ISTEPデバッギングクエリ148は、個々のステップデバッギングがISDB82動作に関して有効であるかどうかを試験する。有効である場合は、プロセスの流れは、スタッフ命令クエリ152に進む。スタッフ命令クエリ152は、命令スタッフィング動作がISDB82日に関して有効であるかどうかを試験する。有効である場合は、プロセスの流れは、クエリ156において説明される命令スタッフィング動作を表すスタッフ命令ステップ156に進む。

[0072]

クエリ156において、コアDSP40リセット命令がデバッギング動作によいてはなっては、コアDSP40リセット命令がデバッギング動作によび生たって成立に関する試験が実施される。コアDSP40リセッサリセットが生まれている場合は、プロセスの流れは、コアDSP40プロセットコマンドが生まれていない場合は、プロセスの流れは、割り込みが存在クエリ158に進む。割り込みが存在するかとうかとまれ、プロセスの流れは、可以込みが存在するかとうがであまれ、プロを表でできる場合は、デバッギング動作に割り込まれていることを示す信号をDSP40に引き、プロできるがに、通常のスレッド動作が開始することができるができるができるができる場合は、プロセスの流れは、通常のスレッド動作が開始することができる場合は、プロセスの流れは、J T A G インタフェース84に進み、DSP40は、対象スレッドをデバッが開始することができる場合は、プロセスがが継続する場合は、プロセード120から通常動作モードに移行させる。デバッギングが継続する場合は、プロセード120から通常動作モードに移行させる。デバッギングが継続する場合は、プロマースのよりに関いては、アロッドの対象スレッドを通常している。デバッギングが継続する場合は、プロマースのよりに関いては、アロッドでは、アロッドでは、アロッドに移行させる。デバッギングが手には、アロッドでは、アロッドに移行させる。デバッギングが継続する場合は、アロッドでは、アロッドでは、アロッドでは、アロッドでは、アロッドでは、アロッドでは、アロッドでは、アロッドでは、アロッドでは、アロッドでは、アロッドでは、アロッドでは、アロッドでは、アロッドでは、アロッドを引きるには、アロッドを対象には、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを対象がでは、アロッドを表がでは、アロッドを表がでは、アロッドを表がでは、アロッドを表がでは、アロッドを表がでは、アロッドを表がでは、アロッドを表がでは、アロッドを表がでは、アロッドを表がでは、アロッドを表がでは、アロッドを表がでは、アロッドを表がでは、アロッドを表がでは、アロッドを表がでは、アロッドを表がでは、アロッドを表がでは、アロッドを表がでは、アロッドを表がでは、アロッとのでは、アロッドを表がでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとのでは、アロッとので

20

30

40

50

スの流れは、デバッギング動作ステップ138に戻る。

# [0073]

明確なことであるが、ISDB82プロセスの流れの動作は、非常に広範であることが可能であるが、これらの動作は開示される主題の適用範囲内であることができる。従って、図6のISDB82プロセスの流れは、本開示の1つの可能な実施形態として例示することを目的とするものである。

#### [0074]

開示される主題の他の側面は、DSP40内における電力崩壊を通じてのデバッギングを含む。ISDBコンフィギュレーションレジスタは、デバッガソフトウェア(JTAGインタフェース84を介する)及びスーパバイザコアソフトウェア(CR転送命令を介する)の両方によって読み取り可能及び書き込み可能である。カーネルソフトウェアは、この特長を用いて電力崩壊時におけるISDBコンフィギュレーションをセーブ及びリストアすることができる。これらの共有レジスタを書き込むマスターが多数存在するため、これらのレジスタは首尾一貫した、相互に排他的な形でのみ書き込むことが重要である。

### [0075]

本明細書の方針は、コアがパワーダウン又はパワーアップ中のときには、JTAGインタフェース84はこれらのレジスタを読み取る/書き込むことを許容されないといってある。同様に、JTAG84がこれらのレジスタを修正中であるときには、コアは、ワーダウンすることが許容されない。この方針は、ハードウェアとソフトウェアの組合した関しても強制される。システムコンフィギュレーションにおける1つのビット、エアスーパバイザソフトウェアのみによって書き込むできる。このビットは、ロSP40のハードウェアリセット時にクリアされるこのビットがクリアされているときには、すべてのJTAGインタフェース84読み取りといったがクリアされているときには、すべてのJTAGインタフェース84読み取りにファップシーケンスを完了していてエSDBと対話する準備が整っているかをホストソフトウェアに示すことができる。このことは、セーブされたエSDB82コンフィギュレーションをウォームブートパワーアップ(リストア)シーケンスにおいてリストアさせる機会をコアに与える。

# [0076]

電力崩壊時におけるデバッギングの一例は、電力を意識する必要がある携帯電話において見つけることができる。 D S P 4 0 は、依然としてデバッギングを行う必要がある間にオフになるか又はアイドル状態になることができる。従って、開示される主題は、電力崩壊インスタンスのみにおいて現れることができるブレークポイントを設定する能力を提供する。このことは、コアが動作中でない又は"オン"状態でないときでさえもデバッグする能力を提供する。

# [0077]

開示される実施形態における、電力崩壊時のデバッギングは、DSPが電力を降下させることに関連づけられたコンフィギュレーションに関する一組のブレークポイントを設定することを含む。DSPが電力を降下させる前に、DSPは、コンフィギュレーションを特定のレジスタ内にセーブする。これらの特定のレジスタ及びコンフィギュレーションは、RAMプロセスの中断を可能にする。従って、DSPが戻ったときに、コンフィギュレーションは、次のデバッグ動作を実行できる状態にある。

# [0078]

ここにおいて、マルチスレッド化デジタル信号デジタル信号プロセッサにおける非侵入型、スレッド選択式デバッギングに関して説明される処理上の特長及び機能は、様々な方法で実装することができる。例えば、DSP40が上述される動作を実行できるだけでなく、本明細書の実施形態は、ここにおいて説明される機能を果たすように設計された特定用途向け集積回路(ASIC)、マイクロコントローラ、デジタル信号プロセッサ、又はその他の電子回路において実装することもできる。さらに、ここにおいて説明されるプロセス及び特長は、該様々な信号及び命令処理システムによる読み取り及び実行のために磁

気媒体、光学媒体、又はその他の記録媒体に格納することができる。従って、好まれる実 施形態に関する上記の説明は、当業者が請求される主題を製造または使用するのを可能に することを目的とするものである。これらの実施形態に対する様々な修正が当業者にとっ て容易に明確になるであろう。さらに、ここにおいて定義される一般原理は、革新的な能 力を用いずにその他の実施形態にも適用可能である。以上のように、請求される主題は、 ここにおいて示される実施形態に限定されることが意図されるものではなく、ここにおい て開示される原理及び斬新な特長に一致する限りにおいて最も広範な適用範囲が認められ るべきである。

# 【図1】

図 1

# 【図2】

図 2

FIG. 2

# 【図3】

# 【図4】

# 【図5】

# 【図6】

#### 【手続補正書】

【提出日】平成24年10月24日(2012.10.24)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

マルチスレッド化デジタル信号プロセッサをデバッグするための非侵入型方法であって

前記マルチスレッド化デジタル信号プロセッサの少なくとも 1 つ以上のスレッドを用いて複数の処理命令をマルチスレッド化プロセスにおいて実行することと、

少なくとも 1 つのデバッギングイベントを生成するための 1 つ以上のブレークポイント命令を識別することと、

前記ブレークポイント命令のうちの少なくとも1つを実行することに応じて前記少なく とも1つのデバッギングイベントを生成することと、

前記少なくとも1つのデバッギングイベントに応じて複数のデバッギング命令を実行することであって、前記デバッギング命令は、前記マルチスレッド化デジタル信号プロセッサの少なくとも1つ以上のスレッドをデバッギングモードに移行させることによって前記マルチスレッド化デジタル信号プロセッサにおいて前記複数の処理命令を前記実行することを非侵入方式でデバッグするためのデバッギング命令であることと、

前記複数のデバッギング命令を前記実行することを報告するために前記複数のデバッギング命令を前記実行することからの少なくとも 1 つのデバッギングリターンを生成すること、とを備える、非侵入型方法。

## フロントページの続き

| (74)代理人 | 100095441 |

|---------|-----------|

|---------|-----------|

弁理士 白根 俊郎

(74)代理人 100075672

弁理士 峰 隆司

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100158805

弁理士 井関 守三

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(72)発明者 ルシアン・コドレスキュ

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

(72)発明者 ウィリアム・シー.・アンダーソン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

7 5

(72)発明者 スレッシュ・ベンクマハンティ

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

7 5

(72)発明者 ルイス・アチレ・ジアンニニ

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

7 5

(72)発明者 マノジクマー・パイラ

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

7 5

(72)発明者 スーフェン・チェン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

7 5

F ターム(参考) 5B042 GA23 HH25 HH50 LA10

【外国語明細書】 2013058207000001.pdf