(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6534677号

(P6534677)

(45) 発行日 令和1年6月26日(2019.6.26)

(24) 登録日 令和1年6月7日(2019.6.7)

(51) Int.Cl.

F 1

|             |           |

|-------------|-----------|

| HO1L 25/065 | (2006.01) |

| HO1L 25/07  | (2006.01) |

| HO1L 25/18  | (2006.01) |

| HO1L 23/50  | (2006.01) |

| HO2M 3/00   | (2006.01) |

|      |       |

|------|-------|

| HO1L | 25/08 |

| HO1L | 23/50 |

| HO2M | 3/00  |

|   |

|---|

| Y |

| W |

| Y |

請求項の数 11 (全 13 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2016-553573 (P2016-553573)  |

| (86) (22) 出願日 | 平成27年2月20日 (2015.2.20)        |

| (65) 公表番号     | 特表2017-511976 (P2017-511976A) |

| (43) 公表日      | 平成29年4月27日 (2017.4.27)        |

| (86) 國際出願番号   | PCT/US2015/016739             |

| (87) 國際公開番号   | W02015/127159                 |

| (87) 國際公開日    | 平成27年8月27日 (2015.8.27)        |

| 審査請求日         | 平成30年2月19日 (2018.2.19)        |

| (31) 優先権主張番号  | 14/185,502                    |

| (32) 優先日      | 平成26年2月20日 (2014.2.20)        |

| (33) 優先権主張国   | 米国(US)                        |

|               |                                                                                                                       |

|---------------|-----------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者     | 390020248<br>日本テキサス・インスツルメンツ合同会社<br>東京都新宿区西新宿六丁目24番1号                                                                 |

| (73) 特許権者     | 507107291<br>テキサス インスツルメンツ インコーポ<br>レイテッド<br>アメリカ合衆国 テキサス州 75265<br>-5474 ダラス メイル ステイショ<br>ン 3999 ピーオーボックス 655<br>474 |

| (74) 上記1名の代理人 | 100098497<br>弁理士 片寄 恒三                                                                                                |

最終頁に続く

(54) 【発明の名称】スタックされたチップ及びインターポーラを備えた部分的に薄化されたリードフレームを有するコンバータ

## (57) 【特許請求の範囲】

## 【請求項1】

電力供給システムであって、

QFNリードフレームと、対向する側にFET端子を備える第1のチップと、平坦なインターポーラと、一方の側にFET端子を備える第2のチップを順次に含む、垂直にアセンブルされるスタックを含み、

前記リードフレームが、リードと、前記スタックから離れて面する第1の表面と前記スタックに面する第2の表面とを備えるパッドとを有し、前記第2の表面がポケットとして窪んだ部分を有し、前記ポケットが前記ポケットにおいて半導体チップを取り付けるために適した深さとアウトライントとを有し、前記パッドが前記電力供給システムの接地された出力端子に連結され、

前記第1のチップが、前記ポケットに取り付けられるFETソース及びゲート端子と、前記第2の表面の窪んでいない部分と共に面するFETドレイン端子とを有し、

前記インターポーラが、前記第1のチップに面する平坦な第3の表面と、前記第2のチップに面する反対の平坦な第4の表面と、前記第3及び第4の表面の間の均一な第1の高さとを有し、前記インターポーラが、ギャップにより分離され、前記第1の高さの金属と前記第1の高さより小さい第2の高さの金属とを含む複数のトレースと、前記ギャップと前記第1及び第2の高さの間の差とを充填する絶縁性材料とを含み、

前記複数のトレースの第1のトレースが、前記電力供給システムの入力端子に連結され、前記第2のチップのFETドレイン端子に取り付けられる前記第4の表面を有し、

10

20

前記複数のトレースの第2のトレースが、前記電力供給システムのスイッチノード端子に連結され、前記第1のチップのFETドレイン端子に取り付けられる前記第3の表面と前記第2のチップのFETソース端子に取り付けられる前記第4の表面とを有する、電力供給システム。

【請求項2】

請求項1に記載の電力供給システムであって、

前記パッドの第1の表面と前記リードとを封止されないまま残すパッケージを更に含む、電力供給システム。

【請求項3】

請求項2に記載の電力供給システムであって、

前記FET端子と反対の前記第2のチップの側が封止されない、電力供給システム。

【請求項4】

請求項2に記載の電力供給システムであって、

前記パッドの封止されない第1の表面が熱エネルギーを拡散するために適している、電力供給システム。

【請求項5】

請求項3に記載の電力供給システムであって、

前記第2のチップの前記封止されない側が熱エネルギーを拡散するために適している、電力供給システム。

【請求項6】

請求項1に記載の電力供給システムであって、

前記第1及び第2のチップのゲートが前記複数のトレースの第3のトレースに連結される、電力供給システム。

【請求項7】

請求項6に記載の電力供給システムであって、

前記第2のチップが前記電力供給システムのドライバ・コントローラ回路要素と更に統合され、前記ドライバ・コントローラ回路の端子が前記複数のトレースの第4のトレースに連結される、電力供給システム。

【請求項8】

電力供給システムを製造する方法であって、

リードと第1及び第2の表面を備えるパッドとを有するリードフレームを提供することであって、前記第2の表面がポケットのために窪んだ部分を有し、前記ポケットが半導体チップを取り付けるために適した深さとアウトラインとを有する、前記提供することと、一方の側にFETソース端子とFETゲート端子とを備え、反対の側にFETドレイン端子を備える第1のチップを提供することと、

前記第1のチップの前記FETソース端子を前記パッドの前記第2の表面の前記窪んだ部分に取り付けることと、

絶縁性ゾーンを備えて交互に並ぶ金属性トレースのネットワークを備える第3及び第4の表面を有する平坦なインターポーラを提供することと、

それぞれのトレースを前記パッドとリードと前記第1のチップのFETドレイン端子とに接続することにより前記パッドの前記第2の表面上にその第3の表面を備える前記インターポーラを置くことと、

同じ側に、第2のFETのソース端子とドレイン端子とゲート端子と、集積されたドライバ・コントローラ回路要素の端子とを有する第2のチップを提供することと、

前記第2のFETの前記ソース端子とドレイン端子とゲート端子と、前記ドライバ・コントローラ回路要素の前記端子とをそれぞれのトレースに接続することにより、前記インターポーラの前記第4の表面上に前記第2のチップを置き、垂直にスタックされた電力供給システムを完成することと、

を含む、方法。

【請求項9】

10

20

30

40

50

請求項 8 に記載の方法であって、

前記インターポーザを提供する前に、

第 1 の高さと第 1 の平面における第 1 の表面と平行な第 2 の平面における第 2 の表面と

を有する金属の平坦なシートを提供することと、

前記平坦なシートをギャップにより分離される複数のトレースにパターニングすることと、

或るトレースの部分を前記第 1 の高さより小さい第 2 の高さまで薄化することと、

絶縁性ゾーンを備えて交互に並ぶ金属性トレースのネットワークを備える第 3 及び第 4

の表面を有する平坦なインターポーザをつくるために、前記第 1 及び前記第 2 の平面により

限定される絶縁性材料で前記ギャップと前記薄化されたトレース部分とを充填すること

と、

を更に含む、方法。

【請求項 10】

請求項 8 に記載の方法であって、

前記第 2 のチップを置いた後に、前記リードフレームの前記第 1 の表面を封止されない

まま残して、前記垂直にスタックされたシステムをパッケージング化合物に封止すること

を更に含む、方法。

【請求項 11】

請求項 8 に記載の方法であって、

前記第 2 のチップを置いた後に、前記パッドの前記第 1 の表面と、前記端子と反対の前

記第 2 のチップの側とを封止されないまま残して、前記垂直にスタックされたシステムを

パッケージング化合物に封止することを更に含む、方法。

【発明の詳細な説明】

【技術分野】

【0001】

本願は、概して半導体デバイス及びプロセスに関し、更に特定して言えば、スタックされたチップとインターポーザとを備えた部分的に薄化されたリードフレームを有し、配線及びクリップのない、D C / D C コンバータの構造及び製造方法に関連する。

【背景技術】

【0002】

電力供給回路の中でも広く広まっているファミリは、D C 電圧を別のD C 電圧に変換するためのパワースイッチングデバイスである。特に、増大しつつある電力搬送要件に適しているのが、直列に接続され、共通スイッチノードにより共に結合される、2つのパワーM O S 電界効果トランジスタ(F E T)を備えた電力ブロックである。このようなアッセンブリは、ハーフブリッジと呼ぶこともある。レギュレートドライバ及びコントローラが付加される場合、こういったアッセンブリは、パワー段と称され、又は、より一般的には同期バックコンバータと称される。同期バックコンバータにおいて、(a)ハイサイドスイッチと呼ぶこともある制御F E Tチップは、供給電圧V<sub>I N</sub>とL C 出力フィルタとの間に接続され、(b)ローサイドスイッチと呼ぶもある同期(s y n c)F E Tチップは、L C 出力フィルタと接地電位との間に接続される。制御F E Tチップ及び同期F E Tチップのゲートは、コンバータ及びコントローラのドライバのための回路要素を含む半導体チップに接続される。半導体チップは接地電位にも接続される。

【0003】

今日のパワースイッチングデバイスの多くでは、パワーM O S F E Tのチップとドライバ及びコントローラI Cのチップとは、個別の構成要素として水平に隣り合ってアセンブルされる。各チップは、典型的に、金属性リードフレームの矩形又は方形のパッドに取り付けられる。パッドは、入力 / 出力端子としてリードにより囲まれる。他のパワースイッチングデバイスにおいて、パワーM O S F E Tチップ及びドライバ・コントローラI Cは、単一のリードフレームパッド上に水平に隣り合ってアセンブルされ、単一のリードフレームパッドは、全ての4面でデバイス出力端子として働くリードにより囲まれる。リード

10

20

30

40

50

は、カンチレバーエクステンションなしに共通に整形され、クワッドフラットノーリード (QFN) 又はスマートアウトライノーリード (SON) デバイスの方式で配される。チップからリードへの電気的接続は、ボンディングワイヤによって提供され得、ボンディングワイヤは、(それらの長さ及び抵抗のため)著しい寄生インダクタンスをパワー回路に導入する。

【0004】

幾つかの最近導入されたアドバンストアッセンブリにおいて、クリップが、多くの接続配線の代わりとなる。これらのクリップは、幅が広く、厚い金属でつくられ、そのため、クリップにより導入される寄生インダクタンスが最小である。各アセンブリは典型的にプラスチック封止にパッケージングされ、パッケージングされた構成要素は、電力供給システムの基板アッセンブリのためのディスクリート構成ブロックとして用いられる。

【0005】

他の最近導入された方式において、制御FETチップ及び同期FETチップは、リードフレームパッドの上のスタックとして互いの頂部上に垂直にアセンブルされる。これら2つのうち物理的に面積が一層大きなチップがリードフレームパッドに取り付けられ、クリップが、スイッチノード及びスタック頂部への接続を提供する。物理的サイズとは関係なく、同期FETチップは、デューティサイクル及び導通損失の考慮に起因して、制御FETチップの能動エリアより大きな能動エリアを必要とする。同期チップ及び制御チップの両方がソースダウンアセンブルされるとき、(物理的に且つ能動エリアが)一層大きな同期チップがリードフレームパッド上にアセンブルされ、(物理的に且つ能動エリアが)一層小さな制御チップが、同期チップのドレインに連結されるソースを有して、スイッチノードを形成し、そのドレインが入力サプライ $V_{IN}$ に接続される。第1のクリップが、2つのチップ間のスイッチノードに接続される。スタック頂部の伸長された第2のクリップが、入力サプライ $V_{IN}$ に連結される。パッドは、接地電位にあり、動作において生成される熱のスプレッダとして機能する。ドライバ・制御ICチップは、チップ及びクリップのスタック近くに水平に隣り合ってアセンブルされ、ボンディングワイヤによってFETゲート及びリードフレームリードと接続される。それらの形状及び材料のため、クリップ及びワイヤボンドは抵抗及びインダクタンスを有し、これらはシステムの寄生容量に寄与する。

【0006】

更に別の最近導入された電力システムにおいて、ドライバ・制御チップが、第2のクリップの頂部上の垂直スタックに含まれる。このアセンブリ構造は、リードフレームパッド及び同様に印刷回路基板の占有面積を節約するが、非常に長い下方ボンディングワイヤのリスク、及び、ワイヤ流れのリスク、及びその後の封止プロセスの間の電気的短絡のリスクがある。

【発明の概要】

【0007】

記載される例において、電力供給システム (DC/DCコンバータなど) が、垂直にアセンブルされたスタックを有し、垂直にアセンブルされたスタックは、QFNリードフレーム、対向する側にFET端子を備えた第1の(ローサイド)チップ、平坦なインターポーラ、及び一つの側にFET端子を備えた第2の(ハイサイド)チップを順次含む。第2のチップは、ドライバ・コントローラ回路要素と統合される。リードフレームは、リード、及び、スタックから離れて面する第1の表面とスタックに面する第2の表面とを備えたパッドを有する。第1の表面は、PC基板への取り付けのためである。第2のパッド表面はポケットとして窪んだ部分を有し、ポケットは、ポケットにおいて半導体チップを取り付けるために適した深さ及びアウトラインを備える。パッドは、システムの接地された出力端子に連結される。第1のチップは、窪んだポケットに取り付けられるFETソース端子、及び窪んでいない第2のパッド表面と共に面である、FETドレイン及びゲート端子を有する。

【0008】

10

20

30

40

50

インターポーザは、第1のチップに面する平坦な第3の表面、第2のチップに面する反対の平坦な第4の表面、及びこれらの表面間の均一な第1の高さを有する。インターポーザ金属は、ギャップにより分離されるトレースにパターニングされ、トレースは、第1の高さの金属、及び第1の高さより小さい第2の高さの金属を含む。絶縁性材料が、ギャップ及び第1及び第2の高さ間の差を充填する。システムのスイッチノード端子に連結された一つのトレースが、ローサイドFETのドレイン端子に取り付けられた第3の表面を備え、及びハイサイドFETのソース端子に取り付けられた第4の表面を備える。システムの入力端子に連結された別のトレースが、ハイサイドFETのドレイン端子に取り付けられた第4の表面を有する。

【図面の簡単な説明】

10

【0009】

【図1】垂直にスタックされたチップ及びインターポーザを備えた電力供給システムの例示の実施例の斜視図であって、このシステムにはボンディングワイヤ及びクリップがない。

【0010】

【図2】パッドを備えたリードフレームの上面図であり、これは、半導体FETチップをアセンブルするために適した部分的に薄化された又は窪んだ部分を有する。

【0011】

【図3】リードフレームパッドの窪んだ部分に取り付けられた半導体FETチップを備えた図2のリードフレームの図であり、チップは、垂直にスタックされたシステムの第1のチップであり、取り付けられていないチップ端子が、リードフレームパッドの窪んでいない部分と共に面である。

20

【0012】

【図4】システムの半導体チップを相互接続するための金属のシートに形成されるインターポーザの上面図である。

【0013】

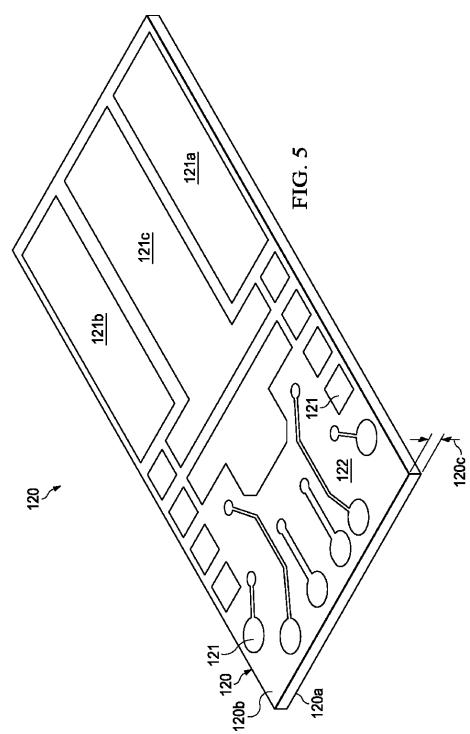

【図5】図4のインターポーザの底部図である。

【0014】

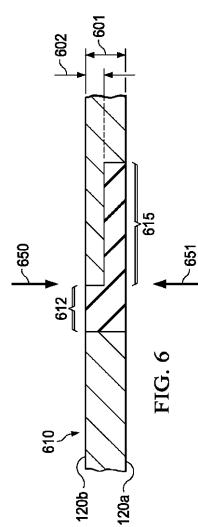

【図6】平坦なシート金属が、パターニング、部分的薄化、及び金属トレース間のギャップを絶縁性材料で充填する工程を介して処理された後の、図4及び図5のインターポーザの一部の断面である。

30

【0015】

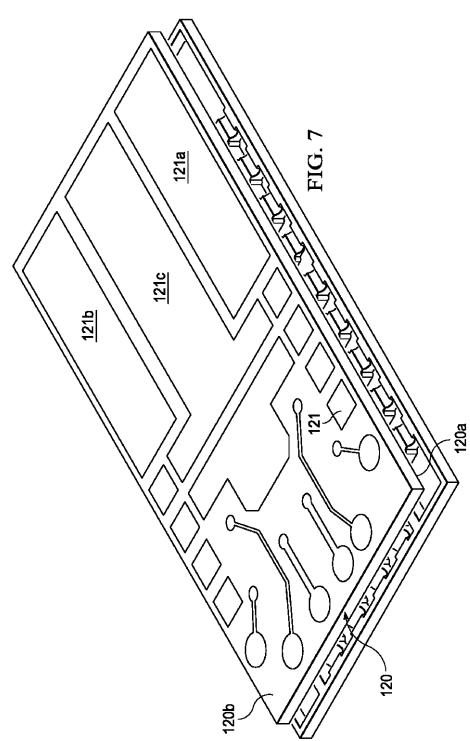

【図7】リードフレーム及び第1のチップに取り付けられたインターポーザを備えた垂直スタックの斜視図である。

【0016】

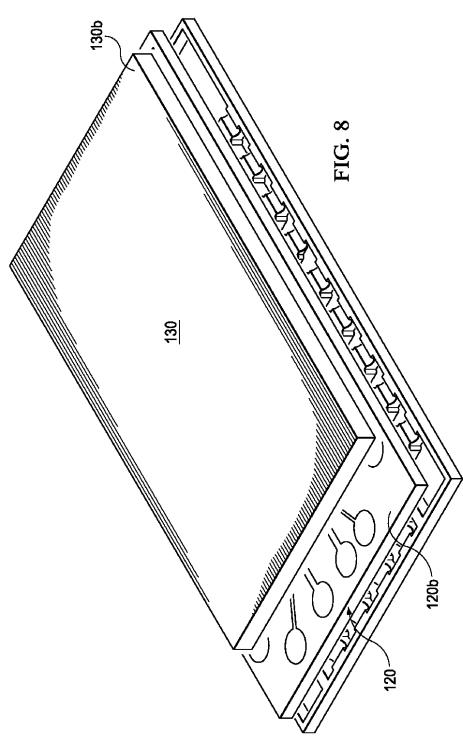

【図8】インターポーザにクリップ取り付けされた第2のFETチップを備えた垂直スタックの斜視図である。

【発明を実施するための形態】

【0017】

DC/DCパワーコンバータでは、小型化に対する絶え間ない市場トレンドにより、アセンブルされたシステムにより消費される基板エリアの低減、及び低減された高さが要求されている。これらの目標は、システム性能の改善及びコスト低減と同時に達成されることが好ましい。

40

【0018】

リードフレームパッド上に垂直にアセンブルされるチップ及びクリップのシステムの高さは、ローサイドFETチップがリードフレームパッドに埋め込まれる場合に低減され得、リードフレームパッドは、チップの挿入を可能にするために薄化されたポケットを有する。挿入後、チップの一つの端子がパッドに電気的に取り付けられ、チップの露出された他の端子が、薄化されていないパッド部分及びリードの表面と共に面となる。

【0019】

50

要素をそれらの機能を犠牲にすることなく排除するために、システム高さを著しく低減する方法が、両方のクリップを単一のインターポーザで置き換えることによって、及びその回路要素をハイサイドFETのチップに統合することによりディスクリートのドライバ・コントローラチップを排除することによって達成される。平坦なインターポーザが、金属のシートから、高電流を搬送すること及び熱を拡散することが可能な、部分的に薄化された低抵抗トレースのネットワークへと金属性リードフレームをスタンピング及びコイニング(coining)することによって、及びその後、ギャップ及び部分的に薄化された金属部分を絶縁及び補強モールディング化合物で充填することによって事前作製される。リードフレームパッド上にスタックされるインターポーザは、パッドポケットに挿入されたローサイドチップの端子に取り付けられた一つのトレース、及びリードに取り付けられた他のトレースを有する。他のインターポーザトレースが、ハイサイドFETの端子及び集積されたドライバ・制御回路要素の端子を備えたインターポーザの頂部上にスタックされたハイサイドチップに取り付けられる。リードフレーム、インターポーザ、及びチップのスタックは、パッケージング化合物に封止され得るが、ハイサイドチップの取り付けられない表面が封止されないままであるとき、それをヒートシンクを取り付けるために利用し得ることは技術的利点である。このヒートシンクは、基板シンクに接続されるリードフレームパッドと共に、システムの二重の冷却を可能とする。

#### 【0020】

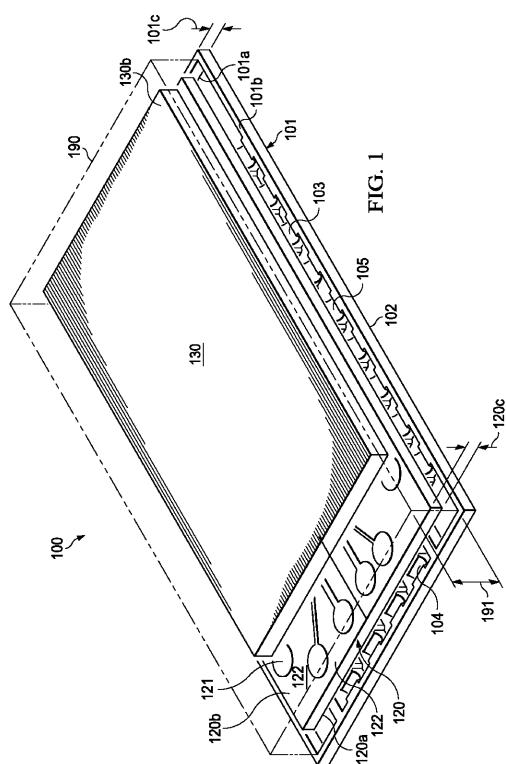

図1は、概して、例示の実施例の100で示す、DC/DCコンバータなどの電力供給システムを示し、リードフレーム101のレール102をトリミングする工程の前のシステムが示されている。明確にするため、システム100は、透明の封止190を備えて示されている。好ましい実際の封止は、トランスファモールド技術に適した黒色エポキシ配合を用いる。図1の例示のシステムは、1mm未満の厚み191(例えば、約0.6~約0.8mm)と、約5mmのシステム長さ192及び約6mmの幅193を備えた矩形のフットプリントとを有する。他のシステムは正方形であってよく、幾つかは3mm×3mmの小ささである。

#### 【0021】

透明の封止を介して見ることができるのは、垂直にアセンブルされたスタックであり、これは、順次、リードフレーム101、対向する側のFET端子(図1では見ることはできない)を備えた第1のチップ、平坦なインターポーザ120、及び一つの側の(この側は図1では見ることはできない)FET端子を備えた第2のチップ130を含む。図1は、第2のチップ130のベアシリコン表面を示す。金属リードフレーム101は概して、クワッドラットノーリード(QFN)及びスマートアウトライノーリード(SON)タイプのモジュールに適している。リードフレームは、パッド(図1では見ることができない)、及び複数のリード103、104、105、及び106を含む。リードフレームは、銅又は銅合金でつくられることが好ましく、代替の金属選択肢には、アルミニウム、鉄ニッケル合金、及びKovar(商標)が含まれる。リードフレームの両方の表面は、ニッケル、パラジウム、及び金のめっきされた層のシーケンスなどにより、はんだ取り付けを促進するように準備され得る。また、少なくとも一つの表面は、銀のめっきされる層などにより、熱伝導率を高めるように堆積された金属層を有し得る。図1に示す例示の実施例のためのリードフレーム金属の好ましい厚み101cは、0.2mmから0.3mmまでの範囲にあり、他の実施例が、一層厚い又は一層薄いリードフレーム金属を用い得る。低コスト及びバッチ処理のため、シート金属で開始し、スタンピング又はエッティングによりストリップとしてリードフレームを製造し、及び、封止プロセスの後ストリップをトリミングすることによるモジュールのためにリードフレームをシンギュレートすることが好ましい。電気的に、パッドは、電力供給システムの接地された出力端子に連結される。

#### 【0022】

リードフレーム101は、スタックから離れた方向に面し、図10においてより詳細に示す(a)第1の表面101aと、スタックへの方向に面し、図2において更に詳細に説明する(b)第2の表面101bとを有する。インターポーザ120は、リードフレーム

10

20

30

40

50

に面する平坦な表面 120a を有し、表面 120a は本明細書において第 3 の表面と称する。反対の平坦な表面 120b は、リードフレームから離れて面し、本明細書において第 4 の表面と称し、これは図 1 において見ることができる。平坦な表面 120a 及び 120b の間で、インターポーザ 120 は、本明細書において第 1 の高さと称する均一の高さ 120c を有する。図 1 の例示の実施例において、高さ 120c は、約 0.2 mm ~ 約 0.3 mm あり得、他の実施例において、インターポーザは一層薄く又は一層厚くし得る。

#### 【0023】

図 4、図 5、及び図 6 において更に詳細に記載されるように、インターポーザ 120 は、平坦な金属のシートでつくられ、平坦な金属のシートは、ギャップにより分離される複数のトレースにパターニングされる。複数のトレースの幾つかを図 1 において見ることができ、それらは概して 121 で示される。121a と示され、本明細書において第 1 のトレースと称される、複数のトレースの一つが、システムの入力端子に連結される。幾つかのトレースは、部分エッチング又はコイニングにより構成され得、そのため、それらは、第 1 の高さの金属と、第 1 の高さより小さい第 2 の高さの金属とを含む。モールディングプロセスによって提供される重合体の化合物などの絶縁性材料が、ギャップ 122 と、第 1 及び第 2 の高さ間の差とを充填するために用いられる。従って、インターポーザ 120 は、表面 120a 及び 120b 上に異なる取り付けパッドを提供し得、更に、取り付けパッド間の相互接続トレースを提供する。高い電気的及び熱的伝導性を提供するベース金属が選択される場合、相互接続は、低い電気抵抗及び良好な熱拡散特性を示す。

#### 【0024】

図 1 は更に、本明細書において第 2 の FET チップ又はシステムのハイサイドと称する、FET チップ 130 の側 130b を示す。端子は、側 130b とは反対のチップ側にある（そのため、図 1 において見ることができない）ため、チップ 130 の側 130b には FET 端子がない。チップ 130 は、全てのその端子でインターポーザの第 4 の表面 120b にフリップ取り付けされる。図 1 において見るのはインターポーザトレースエリア 122 であり、インターポーザトレースエリア 122 上に第 2 の FET のソース端子が取り付けられ、これが電気的にシステムのスイッチノードとして働く。システム 100 がパッケージング化合物 190 に封止されるとき、チップ 130 の表面 130b は封止されないままであり得、そのため、それをヒートシンク取り付けのために利用することができ、システムの熱的特性が改善される。

#### 【0025】

チップ 130 は、第 2 の FET を含み、ドライバ・制御回路要素と統合される。従って、側 130b とは反対のチップ表面は、第 2 の FET の端子と、ドライバ・コントローラ回路要素の端子とを含む。図 5 に関連して述べるように、第 2 の FET の端子とドライバ・コントローラ回路要素の端子は、インターポーザに面し、マッチング (matching) インターポーザ金属コンタクトに取り付けられる。

#### 【0026】

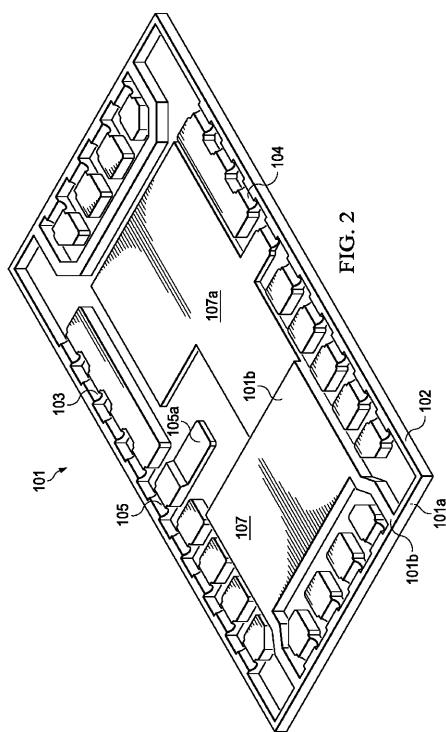

図 2 は、レール 102 によりフレーミングされ、共に保持される、例示のリードフレーム 101 を示す。図 2 の斜視図は、第 2 の表面と称される第 2 のリードフレーム表面 101b を実際に示し、その上に半導体チップのシーケンスがスタックされる（第 1 の表面 101a は図 2 には示していない）。例示の実施例において、パッド 107 はほぼ矩形の形状を有し、他のシステムでは、パッドは、正方形形状、又は、半導体チップを取り付けるために適した任意の構成を有し得る。第 2 のパッド表面 101b の部分 107a が、パッド 107 の元の表面 101b の平面に対して窪んでいる。図 2 において破線で記される部分 107a は、ポケットとして形作られ、半導体チップ（図 3 における 110）を取り付けるために適した深さ及びアウトラインを有し、ポケットに底部端子を備える。この取り付けは、チップの頂部端子が元の表面 101b の平面と共に面となるように成される。窪みは、化学的又はイオンボンバードエッチング及び機械的コイニングを含む幾つかの手法の一つによって実現され得る。図 2 の例示のリードフレームにおいて、窪みは、リード 105 の部分 105a を含み、これは、FET チップのアッセンブリにおける FET チップ 1

10

20

30

40

50

10のゲート端子のためのコンタクトとして機能する。

【0027】

少なくとも幾つかのリードフレーム部分が、冶金学的組成を備えた表面を有する場合、金の薄い層、又は、ニッケル、パラジウム、及び金などの層のシーケンスなどの、はんだ取り付けが促進される。

【0028】

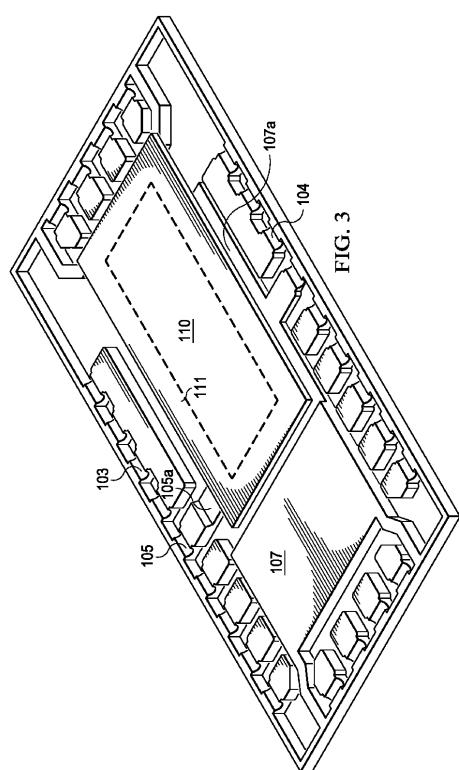

図3は、リードフレームパッドの窪んだポケット107aにおける第1のFETチップ110の取り付け後のリードフレーム101を示す。第1のFETチップ110は、システムのローサイド(LS)トランジスタとして機能する。これは、それが両方のチップ表面上に端子を有するため、いわゆる垂直FETである。LS FETのソース端子は、窪んだパッド部(図2における107a)に取り付けられ、これは、システムの接地された出力端子V<sub>out</sub>に接続される。また、LS FETのゲート端子は、窪んだリード部(図2における105a)に取り付けられ、これはLSゲートリードとして機能する。FETチップ110のドレイン端子は、それが上向きであるので図3において見ることができ、このドレイン端子は、破線111により示されるおおよそのアウトライン内に配置され得る。チップ110の取り付けは、ドレイン端子が、窪んでいないパッド部分107の第2の表面101bと共に面となるように成される。

【0029】

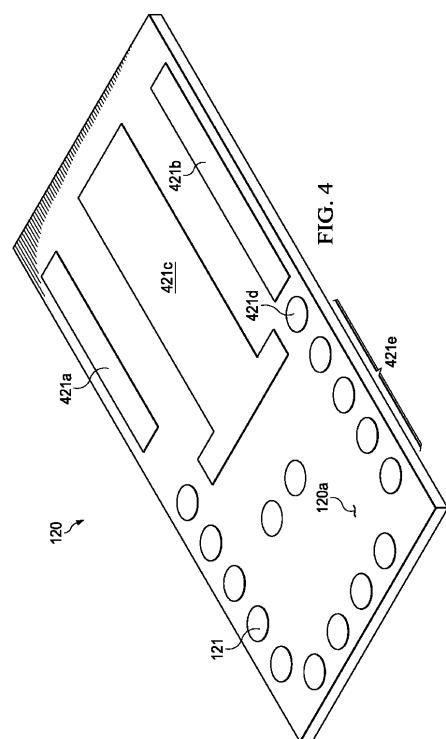

図4、図5、及び図6はインターポーラ120を指す。図4は、第1のチップ110及びリードフレームパッドに面する平坦なインターポーラ表面120aを示し、表面120aはここでは第3の表面と称される。図5は、リードフレームから離れて面する反対の平坦なインターポーラ表面120bを示し、表面120bはここでは第4の表面と称される。表面120a及び120b間で、インターポーラ120は均一の高さ120cを有し、そのため、インターポーラ120はシート状の特徴を有する。図4、図5、及び図6の例において、高さ120cは0.2mm~0.4mmであり得、好ましくは約0.3mmである。図4及び図5が示すように、インターポーラ120のシートは、ギャップ122により分離される金属属性トレース121にパターニングされる。ギャップは、電気的に絶縁性の材料、好ましくは、トランスファモールディングプロセスにおいて用いられるエポキシベース化合物を備えた絶縁性材料、で充填される。薄くされた部分がないトレースは、低い電気的及び熱抵抗を有し、大電流を搬送するため及び熱エネルギーを放散するために特に適している。

【0030】

従って、図4及び図5に示されるインターポーラは、インターポーラ表面に取り付けられる半導体デバイスのための、平坦なシート状の相互接続(interconnector)であり、インターポーラは、絶縁性ゾーンを備えて互いに組み合わされた(interdigitated)金属属性トレースのネットワークを有する。異なる金属対絶縁体高さ比に起因して、図4及び図5のインターポーラ表面は、異なる金属属性コンタクトエリアを示す。図4に示すインターポーラ表面が、(図3において図示するような)リードフレームパッドのポケットに挿入された第1のチップ110を備えたリードフレームに取り付けられるべきであるため、図4のインターポーラ金属トレースは、パッド、リード、及びFET端子の分布に合致し、また、複数の他のトレースは、ドライバ・コントローラ回路要素の端子として機能する。金属トレースは、システムの入力端子V<sub>IN</sub>に連結されるべきトレース421a、システムのスイッチノード端子V<sub>SW</sub>に連結されるべきトレース421b、及び接地電位に接続されるべきトレース421cを含む。複数の他のトレースは、ドライバ・コントローラ回路要素の端子として機能する。他のトレース(図4におけるトレース421dなど、本明細書において第3のトレースと称される)は、第1及び第2のFETのゲートのための取り付けコンタクトとして機能する。

【0031】

図5に示すインターポーラ表面はチップ130の端子に取り付けられ得るため、これは、第2のFETの端子と、集積されたドライバ・コントローラ回路要素の端子とを含み、

10

20

30

40

50

図5のインターポーザ金属コンタクトは、これらの端子の分布に合致する。金属トレースは、(a)システムの入力端子V<sub>IN</sub>に連結されるべき第1のトレース121a、(b)システムのスイッチノード端子V<sub>SW</sub>に連結されるべき第2のトレース121b、(c)接地電位に接続されるべきトレース121c、及び(d)トランジスタゲートに連結されるべき第3のトレース421dを含む。複数の他のトレースは、ドライバ・コントローラ回路要素の端子として機能し、それらは、図4において421eで示す複数のトレースなど、本明細書において第4のトレースと称する。

#### 【0032】

図6におけるインターポーザ部の垂直断面が示すように、矢印651の方向に底部からインターポーザの第3の表面を見ると、矢印650の方向で頂部からインターポーザの第4の表面を見るのに比べて、ずっと大きなエリアが絶縁性材料で充填されることが分かる。或る金属性トレースの部分は、高さ601に対して低減された高さ602のトレース部分をつくるために、部分的に薄化されるか又はハーフエッチングされる。トレースの薄化された部分は、その後、好ましくは重合体のモールディング化合物である、絶縁性材料615で充填される。従って、インターポーザの底部図651は、上面図650に比べて一層大きな絶縁エリア及び低減された金属性エリアを示す。

#### 【0033】

図7は、パッド窪みに埋め込まれた、リードフレームリード、パッド、及び第1のチップに取り付けられた第3の表面120aを備えたインターポーザ120を示す。第4の表面120bは、リードフレームから離れて面し、(例示のコンタクトとして)V<sub>IN</sub>に連結されるべきトレース121a、V<sub>SW</sub>に連結されるべきトレース121b、及び接地されるべきトレース121cを示す。

#### 【0034】

図8は、インターポーザ120の第4の表面120b上の金属トレースにフリップ取り付けされた第2のチップ130を示す。チップ130は、一つのチップ側の全ての3つの端子を備えたFET、及び同じチップ側の端子を備えた電力コンバータシステムのためのドライバ及びコントローラとして働く集積回路を一つの半導体チップに組み合わせる。全ての端子がチップ側(これは、インターポーザに取り付けられる)にあるため、インターポーザ120から離れて面する反対のチップ側130bには端子がないままであり、特に、端子のないチップ側130bにヒートシンクが取り付けられ得るとき、熱エネルギーをシステムから離れて搬送するために利用可能である。

#### 【0035】

図7及び図8の例において、第2のFET130のドレイン端子は、システムの入力端子に連結されるべき、インターポーザのトレース121aに取り付けられる。第2のFET130のソース端子は、システムのスイッチノード端子に連結されるべき、インターポーザのトレース121bに取り付けられる。更に、トレース121bが、第1のFET110のドレイン端子に取り付けられる。

#### 【0036】

図8が示すように、既存の電力供給システムとは対照的に、電力供給システムのアッセンブリにおいて関与する金属クリップ又は金属性ボンディングワイヤがない。従来は、クリップが厚い金属でつくられ、ボンディングワイヤが、必要とされるループ高さを形成するための空間を必要とする。これらの要素を(それらの機能をなくすことなく)排除することは、システム高さの実質的な節約につながる。従って、図8の電力供給システムをパッケージング材料(トランスマルティングプロセスにおいて用いられる重合体の化合物など)に封止した後、封止されたコンバータは1mm未満の高さを有し得る。図1に関連して述べたように、約0.6~約0.8mmの高さを備えたパッケージングされたコンバータが製造され得る。封止プロセスにおいて、リードフレームパッドの第1の表面101a及びリード(図2)が封止されないまま残され、更に、幾つかの実施例では、システムの熱的特性を高めるために第2のFETの表面130bが封止されないまま残され得る。

10

20

30

40

50

## 【0037】

別の実施例において、電力供給システム（DC/DCコンバータなど）を製造する方法が、リードと、第1及び第2の表面を備えたパッドとを備えたリードフレームを提供することにより開始し、第2の表面は、半導体チップを取り付けるために適した深さ及びアウトラインを備えたポケットのために窪んだ部分を有し、この窪みをつくるための適切な手法は、化学的エッチング、機械的コイニング、プラニッシュ加工、及びイオンミリングを含む。次に、第1の半導体チップが提供され、これは、一つのチップ側にソース及びゲート端子を備え、反対のチップ側にFETドレイン端子を備えたFETを有する。その後、第1のFETチップのソース端子は、リードフレームパッドの窪んだ第2の表面上に取り付けられる。

10

## 【0038】

次の処理工程において、平坦なインターポーラが提供され、これは、絶縁性ゾーンを備えて交互に並ぶ金属属性トレースのネットワークを備えた、第3及び第4の表面を有する。インターポーラは、それぞれのトレースをパッド及びリード及び第1のFETのドレイン端子に接続することにより、その第3の表面がリードフレームの第2の表面上に置かれる。

## 【0039】

次に、第2のチップが、同じ側に、第2のFETのソース、ドレイン、及びゲート端子と、集積されたドライバ・コントローラ回路要素の端子とを有する。第2のチップは、第2のFETのソース、ドレイン、及びゲート端子とドライバ・コントローラ回路要素の端子を、それぞれのインターポーラトレースに接続することにより、インターポーラの第4の表面上に置かれる。従って、金属属性クリップ及びボンディングワイヤの助けなしに、チップ及びインターポーラの垂直スタックがつくられる。この垂直スタックはパッケージング化合物に封止され得、パッケージング化合物は、リードフレームの少なくとも第1の表面を、及び幾つかのシステムにおいてFET端子とは反対の第2のチップの表面も、封止されないまま残し得る。最終的に、パッケージから突出する如何なる接続リードフレームレールも、トリミングプロセスにおいて取り除かれ得る。

20

## 【0040】

インターポーラの製造は、金属の平坦なシートを提供することで開始し、金属の平坦なシートは、第1の高さ、第1の平面における第1の表面、及び平行な第2の平面における第2の表面を有する。金属のシートは、ギャップにより分離される複数のトレースに（エッチング手法などにより）パターニングされる。その後、或るトレースの部分が、第1の高さより小さい第2の高さまで薄化される。適切な薄化手法には、エッチング、プラニッシュ加工、及びイオンミリングが含まれる。最終的に、ギャップ及び薄化されたトレース部分は、絶縁性材料（重合体のモールディング化合物など）で充填され、これは、第1及び第2の平面により限定される。従って、平坦なインターポーラは、絶縁性ゾーンを備えて交互に並ぶ金属属性トレースのネットワークを備えた第3及び第4の表面を有し、金属属性トレースのネットワークは、第3及び第4の表面で異なり得る。

30

## 【0041】

本発明の特許請求の範囲内で、説明した例示の実施例に改変が成され得、他の実施例が可能である。少なくとも一つのバージョンにおいて、例示の実施例を電界効果トランジスタに及び他の適切なパワートランジスタに適用する。

40

## 【0042】

別の例として、FET端子とは反対の第2のチップの表面を封止されないまま残し、そのためこの表面が、好ましくははんだ付けにより、ヒートシンクに接続され得るようにすることにより、電力供給モジュールの高電流能力は更に拡張され得、効率が更に高められる。この構成において、モジュールは、リードフレームにより及び第2のFETの外向きに面する表面により二重に冷却され、そのため、熱を両方の大きな表面からヒートシンクへ放散することができる。

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 ラジェヴ ディンカー ジヨシ

アメリカ合衆国 95014 カリフォルニア州 クバチーノ, コルビー アヴェニュー 10

168

審査官 庄司 一隆

(56)参考文献 国際公開第2012/109265 (WO, A1)

米国特許出願公開第2012/0326287 (US, A1)

米国特許出願公開第2012/0248539 (US, A1)

特開2001-274312 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12 - 23/15

H01L 23/50

H01L 25/00 - 25/18

H02M 3/00