(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-129499

(P2006-129499A)

(43) 公開日 平成18年5月18日(2006.5.18)

(51) Int.CI.

H03M 1/12

(2006.01)

F 1

H03M 1/12

テーマコード(参考)

C

5 J O 2 2

審査請求 未請求 請求項の数 10 O L (全 13 頁)

(21) 出願番号 特願2005-316280 (P2005-316280)

(22) 出願日 平成17年10月31日 (2005.10.31)

(31) 優先権主張番号 10/977833

(32) 優先日 平成16年10月29日 (2004.10.29)

(33) 優先権主張国 米国(US)

(71) 出願人 399117121

アジレント・テクノロジーズ・インク

AGILENT TECHNOLOGIE

S, INC.

アメリカ合衆国カリフォルニア州パロアル

ト ページ・ミル・ロード 395

395 Page Mill Road

Palo Alto, California

U. S. A.

(74) 代理人 100099623

弁理士 奥山 尚一

(74) 代理人 100096769

弁理士 有原 幸一

(74) 代理人 100107319

弁理士 松島 鉄男

最終頁に続く

(54) 【発明の名称】 交互ADCを利用したサンプル・レートの倍加方法およびシステム

## (57) 【要約】

【課題】高精度で高サンプル・レートのアナログ・ディジタル変換方法およびシステムを提供する。

【解決手段】本発明の一実施態様によれば、アナログ・ベースバンド信号入力120、アナログ・ベースバンド信号を受信するよう動作可能なN個のアナログ・ディジタル変換器(ADC)104、105を有する変換回路110、及び、N個のADCの出力106を受信して、N個のADCにおける不整合が補正されたアナログ・ベースバンド信号のデジタル表現107を生成するよう動作可能な有限インパルス応答(FIR)フィルタ130を具備するシステムを含む。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

アナログ・ベースバンド信号をデジタル化するための方法であって、

N個のアナログ・デジタル変換器（A D C）を有する変換回路にアナログ・ベースバンド信号を受信するステップと、

前記A D Cの出力に有限インパルス応答（F I R）フィルタを適用することによって、

前記N個のA D Cにおける不整合を補正するステップと、

を含み、前記F I Rフィルタが複数のN×Nマトリックス・フィルタ・タップを含む、方法。

**【請求項 2】**

前記変換回路の伝達関数を求めて、サンプリングを行うステップと、

所望の周波数応答を選択して、サンプリングを行うステップと、

前記伝達関数のサンプルの行列アレイ及び前記所望の周波数応答のサンプルの行列アレイを形成するステップと、

前記アレイについてフーリエ変換を実施するステップと、

行列毎に、前記所望の周波数応答のサンプルの変換行列アレイに、前記伝達関数のサンプルの逆行列アレイを乗算するステップと、

前記乗算ステップの結果得られた行列アレイに関して逆フーリエ変換を実施するステップと、

前記F I Rフィルタにおいて前記逆フーリエ変換の結果を用いるステップと、

を含む、請求項 1 に記載の方法。 20

**【請求項 3】**

前記変換回路の伝達関数を求めて、サンプリングを行うステップが、

前記回路に既知信号を入力し、その出力を記録するステップと、

前記出力及び前記既知入力から前記伝達関数を求めるステップと、

前記伝達関数の離散的サンプルを生成するステップと、

を含む、請求項 2 に記載の方法。

**【請求項 4】**

前記所望の周波数応答が、遷移帯域が急速にロール・オフする、前記アナログ・ベースバンド信号の第1のナイキスト間隔に関するフラットな通過帯域である、請求項 2 に記載の方法。 30

**【請求項 5】**

前記アナログ・ベースバンド信号の表現であるデジタル信号を出力するステップをさらに含む、請求項 1 に記載の方法。

**【請求項 6】**

前記アナログ・ベースバンド信号を変換回路に受信するステップが、該アナログ・ベースバンド信号をN個の相補経路に分割するステップを含み、各経路は、異なる時間遅延素子と前記N個のA D Cのうちの1つとを含む、請求項 1 に記載の方法。

**【請求項 7】**

アナログ・ベースバンド信号入力と、

前記アナログ・ベースバンド信号を受信するよう動作可能な、N個のアナログ・デジタル変換器（A D C）を有する変換回路と、

前記N個のA D Cの出力を受信し、該N個のA D Cにおける不整合が補正された前記アナログ・ベースバンド信号のデジタル表現を生成するよう動作可能な有限インパルス応答（F I R）フィルタと、

を具備する、変換回路。

**【請求項 8】**

前記変換回路が、2つのA D Cを含み、前記F I Rフィルタが、2×2マトリックス・フィルタ・タップを含む、請求項 1 に記載の方法または請求項 7 に記載のシステム。

**【請求項 9】**

10

20

30

40

50

前記変換回路が、3つのA D Cを含み、前記F I R フィルタが、 $3 \times 3$ マトリックス・フィルタ・タップを含む、請求項1に記載の方法または請求項7に記載のシステム。

#### 【請求項10】

前記アナログ・ベースバンド入力信号の帯域幅が、前記個別A D CのうちのどのA D Cのナイキスト帯域幅よりも広い、請求項7に記載のシステム。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、一般に、アナログ・ディジタル変換に関し、特に、アナログ・ディジタル変換におけるサンプリング・レートの向上に関する。 10

##### 【背景技術】

##### 【0002】

信号受信機の分野において、広帯域及びベースバンド・アナログ信号をデジタル信号に変換するには、アナログ・ディジタル変換器(A D C)のサンプル・レートと精度の間で固有のトレードオフを伴うことになる。設計者は、精度の高さが十分ではない可能性のある高速A D Cを利用するか、あるいは、より高精度の低サンプル・レートA D Cを利用するかの選択に直面する。受信信号 $F_{\text{signal}}$ の周波数によって、エイリアシングを回避するために利用しなければならない最低サンプル・レート $F_{\text{sample}}$ が決まるので、この選択は設計者が行う場合が多い。一般に、これは $2 F_{\text{signal}} = F_{\text{sample}}$ になるであろう。

中間周波数(I F)信号の変換においてある程度の成功を収めたアプローチの1つは、それぞれが所望のサンプル・レートの1/2でサンプリングする(I F信号の帯域幅が各A D Cの第1のナイキスト間隔の2倍以下であると仮定して)、交互A D Cを利用することである。まず、I F信号は、1つの同相(I)信号と1つの直交信号(Q)(すなわち、I / Qベースバンド信号)に変換される。次に、I及びQ信号は、 $F_{\text{sample}}$ の1/2でサンプリングする1対の交互A D Cの一方によって、それぞれデジタル化される。2つのA D Cの周波数応答が非理想的で不整合のため、信号には歪が加えられる。実際、2つのA D Cの周波数応答の不整合によって、単一A D Cシステムに対する2つのA D Cによるシステムの利点が大部分なくなる可能性がある。 20

##### 【0003】

解決法の1つでは、I及びQ信号が、Iデジタル化信号に数列[1, -1, 1, ...]を掛け、Qデジタル化信号に数列[j, -j, j, ...]を掛ける局部発振器によって処理される。この結果、後続処理のための実数経路と虚数経路の間ににおけるIサンプルとQサンプルの完全な概念的分離が得られる。各A D Cの周波数応答の乱れは、従って、実数データ・ストリームまたは虚数データ・ストリームに関連する可能性がある。単一有限インパルス応答(F I R)フィルタを用いて、データ経路の汚染が除去され、フィルタの出力が、もとのアナログ信号の情報の全てを含む1つのデジタル信号に再構築される。 30

##### 【0004】

歪を実数成分及び虚数成分に概念的に分離することによって、単一F I Rフィルタを用いて2つのA D Cの周波数応答の不整合を補正できるという点を理解する手掛かりが得られる。しかし、I F信号解決法によって、必ずしも、單一アナログ・ベースバンド入力信号をデジタル化するシステムにおける2つのA D C間の周波数応答の不整合を補正するための解決が得られるとは限らない。これは、單一アナログ・ベースバンド入力信号を実数成分と虚数成分に分離することができないからである。 40

##### 【発明の開示】

##### 【0005】

本発明の実施態様の1つには、アナログ・ベースバンド信号入力、アナログ・ベースバンド信号を受信するよう動作可能なN個のアナログ・ディジタル変換器(A D C)を有する変換回路、及び、N個のA D Cの出力を受信して、N個のA D Cにおける不整合が補正されたアナログ・ベースバンド信号のデジタル表現を生成するよう動作可能な有限イン

パルス応答( F I R )フィルタを具備するシステムが含まれている。

#### 【 0 0 0 6 】

本発明のもう1つの実施態様において、二重ADCシステムにおける周波数応答不整合の補正は、信号を偶数経路と奇数経路に分割することによって実施され、奇数経路の信号には時間遅延が施される。2つの経路は、独立したADCによってデジタル化され、もとのアナログ・ベースバンド入力信号の偶数及び奇数デジタル表現成分が得られる。偶数成分及び奇数成分には、2つのADC間における周波数応答の不整合による歪が含まれている。次に、この不整合を補正するため、これらの成分は、 $2 \times 2$ マトリックス・フィルタ・タップを用いる単一FIRフィルタに入力される。この結果、もとのアナログ・ベースバンド入力信号の情報の全てを含む單一デジタル信号に再構築することが可能な、10補正された偶数成分及び奇数成分が得られる。

#### 【 発明を実施するための最良の形態 】

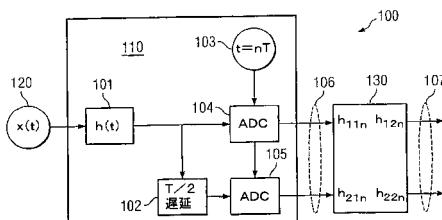

#### 【 0 0 0 7 】

図1は、交互アナログ・デジタル変換器(ADC)を利用して、サンプル・レートの倍加を実施するためのシステム100を示す、本発明の実施態様の1つの例示である。この例では、入力120は、デジタル変換のため回路110に供給されるアナログ・ベースバンド信号である。いかなる回路とも同様に、回路110には、 $h(t)_{101}$ で例示のインパルス応答が含まれる。インパルス応答101は、ADC104及び105、遅延素子102、及び、不図示の追加回路コンポーネントに関する応答である。インパルス応答101は、回路110の各種コンポーネントの特性によって決まるが、単純化のため、20回路110の個別コンポーネントの1つとして例示されている。

#### 【 0 0 0 8 】

入力120は、回路110に供給され、2つの経路に分割される。上部経路はADC104に通じている。下部経路は、遅延素子102及びADC105に通じている。この実施態様の場合、ADC104及び105は、両方とも、クロック103によって動作する。従って、両方の経路において、信号120はデジタル信号に変換されるが、下部経路では、入力120に時間遅延が施される。概念上、ADC104及び105は、ある特定のクロック・サイクルにおいて、共に、1つのゼロの遅延と1つのT/2の遅延に対応する1組のサンプルを生じるように、交互に動作する。この結果、ADC104及び105は、それぞれ、アナログ入力信号120の偶数(番目の)及び奇数(番目の)デジタル表現成分106を生じるよう動作する。ADC104及び105は、それぞれ、アンダーサンプリングを実施するので、どちらの成分も、それ自体は、アナログ・ベースバンド信号入力120に含まれる情報の全てを表わすものではない。しかし、総合すると、各ADC104及び105が、所望のサンプリング周波数の少なくとも1/2で入力120のサンプリングを行う限りにおいて、成分106は、アナログ・ベースバンド信号入力120における情報の全てを表わすことになる。30

#### 【 0 0 0 9 】

ADC104及び105は、ちょうど同じ時間にアナログ・ベースバンド信号入力120のサンプリングを行い、全く同じパラメータを扱うのが理想である。しかし、実際の実施態様では、ある程度の周波数応答の不整合が示される。周波数応答の不整合の結果として、成分106が單一デジタル信号に構築されると、ある程度情報の歪が生じることになる。従って、デジタル表現の精度が低下することになる。40

#### 【 0 0 1 0 】

インパルス応答101には、ADC104と105の間の周波数応答不整合が含まれており、インパルス応答101を利用して、不整合を有効に補正するフィルタ130を設計することが可能である。システム100には、ADC104及び105の出力106を受信して、ADC104と105との間の不整合が補正されたアナログ・ベースバンド信号入力120のデジタル表現107を生成するよう動作可能な、有限インパルス応答(FIR)フィルタ130が含まれている。

#### 【 0 0 1 1 】

交互 A D C 間の周波数応答不整合の補正において遭遇する問題の 1 つは、デジタル表現成分 1 0 6 のそれぞれがアナログ・ベースバンド信号入力 1 2 0 の完全な表現ではないという事実を考慮に入れることができ、F I R フィルタ 1 3 0 のようなフィルタを設計する方法である。それは、各 A D C 1 0 4 及び 1 0 5 の後に、単一フィルタを配置するほど単純ではない。組み合わせることにより、その成分に見受けられるのと同じシーケンスのサンプルを生成することが可能な第 1 及び第 2 のナイキスト間隔信号の組み合わせは無限に存在するので、奇数または偶数成分だけしか受信しない単一フィルタでは、成分に正しいフィルタリングを施すのに十分な情報は得られない。従って、必要とされるフィルタは、偶数及び奇数サンプル値成分の両方を受信して、調整するフィルタである。換言すれば、フィルタは、奇数成分と偶数成分の両方を相互結合して、全サンプルの線形結合を計算し、正しい偶数サンプルと全サンプルの線形結合とを生成して、正しい奇数サンプルを生成する。F I R フィルタ 1 3 0 では、それぞれ、システム・インパルス応答 1 0 1 の偶数及び奇数成分を用いて計算され、それぞれ、表現 1 0 6 の偶数及び奇数成分に適用される一連の  $2 \times 2$  マトリックス・フィルタ・タップを組み込むことによって、こうした解決法が得られる。

10

20

## 【 0 0 1 2 】

次に、正しい F I R フィルタ・タップの計算プロセスについて検討することにする。以下の方程式では、偶数及び奇数デジタル表現成分 1 0 6 の各対が 2 要素ベクトルとして取り扱われる。システム 1 0 0 では、交互 A D C 1 0 4 及び 1 0 5 が利用されるので、ベクトル及び行列を用いた計算が、表記の便宜上行われる。当該技術者には明らかなように、この計算は、A D C 1 0 4 及び 1 0 5 の交互動作を表す時変段階的関数 ( piecemeal functions ) を用いて実施することも可能である。

30

40

## 【 0 0 1 3 】

アナログ・ベースバンド入力信号 1 2 0 の所望の信号処理  $\times (t)$  が、方程式 1 に示されている。

## 【 0 0 1 4 】

## 【 数 1 】

$$y_n = \begin{bmatrix} x(t) \otimes g(t) \\ x(t + T/2) \otimes g(t) \end{bmatrix}_{t=nT} \quad (1)$$

## 【 0 0 1 5 】

ここで、T は、各 A D C 1 0 4 及び 1 0 5 のサンプリング周期であり、 $g(t)$  は信号に施される所望のフィルタリングのインパルス応答である。この応答  $g(t)$  の帯域幅は、合成サンプル・レートによってエイリアシングを除去するため、1/T 未満である。これは、例えば、第 2 のナイキスト間隔の周波数をフィルタで除去するために遷移帯域が急速にロール・オフしている、 $\times(t)$  の第 1 のナイキスト間隔に対する平坦な通過帯域として実施可能である。 $g(t)$  で表わされるフィルタリングは、アナログ・ベースバンド入力信号 1 2 0 の、ユーザの理想的なアナログ・デジタル変換であり、通常、ユーザによって選択される。

40

## 【 0 0 1 6 】

しかし、回路 1 1 0 (二重 A D C フロント・エンド) からの実際の出力信号 1 0 6 は、方程式 2 によって表わされる。

## 【 0 0 1 7 】

## 【数2】

$$x_n = \begin{bmatrix} x(t) \otimes h_1(t) \\ x(t) \otimes h_2(t) \end{bmatrix}_{t=nT} \quad (2)$$

## 【0018】

ここで、 $h_1(t)$ は、偶数サンプルADC104を介した入力コネクタからのインパルス応答であり、 $h_2(t)$ は、奇数サンプルADC105を介した入力コネクタからのインパルス応答である。インパルス応答101を $h_1(t)$ 及び $h_2(t)$ に分割するのは、本明細書で用いられるベクトル表記にインパルス応答101を適応させる方法の1つである。それはまた、2つの経路のそれぞれに、個別インパルス応答が生じることを表わしてもいる。留意すべきは、方程式1と同様、右辺は離散的サンプル値のアレイを表わしているという点である。さらに、 $h_1(t)$ 及び $h_2(t)$ の帯域幅は、1/T未満であると仮定される。

## 【0019】

目標は、フィルタ130の適正な較正フィルタ応答 $q_n$ を決定することにある。方程式3は、 $q_n$ 、 $y_n$ 、及び $x_n$ の関係を表している。以下に示すように、方程式3を操作して、 $q_n$ を計算することが可能である。

## 【0020】

## 【数3】

$$y_n = q_n \otimes x_n \quad (3)$$

## 【0021】

方程式3は、畳み込み積分を明示的に書き出すことによって、方程式4として書き直すことが可能である。

## 【0022】

## 【数4】

$$\begin{bmatrix} \int_{-\infty}^{\infty} x(\tau) g(nT - \tau) d\tau \\ \int_{-\infty}^{\infty} x(\tau + T/2) g(nT - \tau) d\tau \end{bmatrix} = q_n \otimes \begin{bmatrix} \int_{-\infty}^{\infty} x(\tau) h_1(nT - \tau) d\tau \\ \int_{-\infty}^{\infty} x(\tau) h_2(nT - \tau) d\tau \end{bmatrix} \quad (4)$$

## 【0023】

ここで、新たなダミー積分変数 $\tau = \tau' + 1/2$ 。これは、無限限界のため、積分結果を変化させることはない。同様に、離散的サンプル・データ畳み込み総和は、方程式5におけるように、明示的に書き出すことが可能である。

## 【0024】

10

20

30

40

【数5】

$$\begin{bmatrix} \int_{\tau=-\infty}^{\infty} x(\tau)g(nT-\tau)d\tau \\ \int_{\tau=-\infty}^{\infty} x(\tau)g(nT+T/2-\tau)d\tau \end{bmatrix} = \sum_{\tau=-\infty}^{\infty} q_m \begin{bmatrix} \int_{\tau=-\infty}^{\infty} x(\tau)h_1((n-m)T-\tau)d\tau \\ \int_{\tau=-\infty}^{\infty} x(\tau)h_2((n-m)T-\tau)d\tau \end{bmatrix} \quad (5)$$

【0025】

10

次に、積分及び総和は記録することが可能である。また、ダミー積分変数は、各ベクトルの両方の要素に対して同じであるので、方程式6におけるように、スカラである被積分関数にベクトルを掛けて、積分を実施することが可能である。

【0026】

【数6】

$$\int_{\tau=-\infty}^{\infty} x(\tau) \begin{bmatrix} g(nT-\tau) \\ g(nT+T/2-\tau) \end{bmatrix} d\tau = \int_{\tau=-\infty}^{\infty} x(\tau) \sum_{\tau=-\infty}^{\infty} q_m \begin{bmatrix} h_1((n-m)T-\tau) \\ h_2((n-m)T-\tau) \end{bmatrix} d\tau \quad (6)$$

20

【0027】

方程式6が、あらゆる任意の入力信号x(t)、及び、全てのn及びt値について当てはまるようになることが望ましい。従って、この関係は、方程式7として表わされる。

【0028】

【数7】

$$\begin{bmatrix} g(nT-\tau) \\ g(nT+T/2-\tau) \end{bmatrix} = \sum_{\tau=-\infty}^{\infty} q_m \begin{bmatrix} h_1((n-m)T-\tau) \\ h_2((n-m)T-\tau) \end{bmatrix} \quad (7)$$

30

【0029】

フィルタの帯域幅制限のため、インパルス応答g、h<sub>1</sub>、及び、h<sub>2</sub>は、全て、T/2の間隔があいた時間サンプルによって完全に指定される。従って、上記制約は、離散的時点t=0及びt=T/2において評価しさえすればよい。これらの時点の両方における制約は、方程式8におけるように、單一行列方程式をなすように書くことが可能である。

【0030】

【数8】

$$\begin{bmatrix} g(nT) & g(nT-T/2) \\ g(nT+T/2) & g(nT) \end{bmatrix} = \sum_{\tau=-\infty}^{\infty} q_m \begin{bmatrix} h_1((n-m)T) & h_1((n-m)T-T/2) \\ h_2((n-m)T) & h_2((n-m)T-T/2) \end{bmatrix} \quad (8)$$

40

【0031】

従って、方程式9及び10における下記行列を定義するのが役に立つ。

【0032】

【数9】

$$\mathbf{h}_n = \begin{bmatrix} h_1(nT) & h_1(nT - T/2) \\ h_2(nT) & h_2(nT - T/2) \end{bmatrix} \quad (9)$$

$$\mathbf{g}_n = \begin{bmatrix} g(nT) & g(nT - T/2) \\ g(nT + T/2) & g(nT) \end{bmatrix} \quad (10)$$

【0033】

10

所望の係数行列集合  $\mathbf{q}_m$  は、方程式 1.1 におけるように、行列置き込み方程式を解くことによって求められる。

【0034】

【数10】

$$g_n = \sum_{m=-\infty}^{\infty} q_m h_{n-m} \quad (11)$$

【0035】

20

置き込みの実施を回避するため、行列を周波数領域に変換することによって、この解に近づくことが可能である。変換の長さ  $N$  は、完全なインパルス応答  $\mathbf{g}$ 、 $\mathbf{h}_1$ 、及び、 $\mathbf{h}_2$  を包含するのに十分な長さでなければならない。

【0036】

【数11】

$$\sum_{n=0}^{N-1} e^{\frac{-j2\pi kn}{N}} g_n = \sum_{m=-\infty}^{\infty} q_m e^{\frac{-j2\pi km}{N}} \sum_{n=0}^{N-1} e^{\frac{-j2\pi k(n-m)}{N}} h_{n-m} \quad (12)$$

【0037】

30

$p = n - m$  を代入する。これによって、最も右側の総和に対する制限が変化する。

【0038】

【数12】

$$\sum_{n=0}^{N-1} e^{\frac{-j2\pi kn}{N}} g_n = \sum_{m=-\infty}^{\infty} q_m e^{\frac{-j2\pi km}{N}} \sum_{p=-m}^{N-1-m} e^{\frac{-j2\pi kp}{N}} h_p \quad (13)$$

【0039】

40

総和される値が  $N$  において周期的であれば、最も右側の総和に対する制限は、 $m$  から独立するように調整することが可能である。これは、 $\mathbf{h}$  を、方程式 1.4 に表わされるように、有限持続時間インパルス応答の循環バージョンである  $\mathbf{h}_p$  に置き換えることによって実施される。

$$h_p = h_{p \bmod N} \quad (14)$$

【0040】

この置換を実施し、フィルタ・タップ数を制限することによって、方程式 1.5 が得られる。フィルタ・タップが、 $0 \sim N - 1$  の範囲においてのみ非ゼロであり、この非ゼロ範囲は、方程式 1.5 において循環的に用いられるという点に留意されたい。従って、 $N$  は、完全な補償フィルタ・インパルス応答  $\mathbf{q}_m$  を包含するのに十分なほど大きくなるように選択しなければならない。一般に、これは、 $\mathbf{g}$  及び  $\mathbf{h}$  応答よりも多少長い。 $N$  を小さくしそう

50

ると、良好な較正応答をもたらすのに必要な自由度が制限されることになる。

【0041】

【数13】

$$\sum_{n=0}^{N-1} e^{\frac{-j2\pi kn}{N}} g_n = \sum_{m=0}^{N-1} e^{\frac{-j2\pi km}{N}} q_m \sum_{p=0}^{N-1} e^{\frac{-j2\pi kp}{N}} h'_p \quad (15)$$

【0042】

方程式15における総和のそれぞれは、フーリエ変換に相当する。大文字を用いて変換を表わすと、方程式16が得られる。

10

$$G_k = Q_k H_k \quad (16)$$

【0043】

方程式16を操作して、方程式17におけるように、所望の較正フィルタの周波数応答について解くことが可能である。変換された行列要素は、複素数であり、従って、表示の乗算には、複素数演算が必要とされるという点に留意されたい。また、もとの時間領域行列は実数であるので、変換行列は、Nを法として添字kに関して共役対称をなすという点にも留意されたい。この事実を利用して、可変記憶及び計算時間を短縮することも可能である。

$$Q_k = G_k H_k^{-1} \quad (17)$$

【0044】

従って、インパルス応答を得るには、方程式18におけるような、逆フーリエ変換を行うことが必要になる。

【0045】

【数14】

$$q_m = \sum_{k=0}^{N-1} e^{\frac{-j2\pi km}{N}} Q_k \quad (18)$$

20

30

【0046】

出力 $q_m$ は、FIRフィルタ130によって連続的に繰り返されるN個の $2 \times 2$ マトリックスのシーケンスである。個々のマトリックスは、それぞれ、ADC104及び105の不整合を補正するためにFIRフィルタ130によって利用されるフィルタ・タップである。方程式6に関して上述のように、 $q_m$ はナイキスト周波数 $1/T$ を超えない他の信号にも有効である。

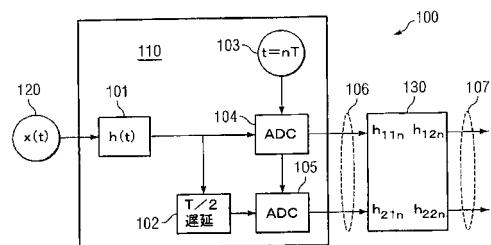

【0047】

図2は、ADC不整合を補正するための方法200を示すフローチャート実施態様である。プロセス201では、 $h_1(t)$ 及び $h_2(t)$ が決定される。 $h_1(t)$ 及び $h_2(t)$ を決定するためのさまざまな方法が存在する。例えば、回路110(図1)のアナログ・ベースバンド信号入力として、うまく制御された既知のテスト入力を利用することが可能である。ADC104及び105の出力は、 $T/2$ の間隔でサンプリングし、記録される。これらの値を上記方程式2に代入すると、 $h_1(t)$ 及び $h_2(t)$ の離散的値を解くために操作可能な関係式が得られることになる。インパルス応答 $h_1(t)$ 及び $h_2(t)$ は、回路110のインパルス応答だけではなく、ADC104と105との間の時間オフセット・エラーも表わしている。

40

【0048】

プロセス202では、所望の周波数応答 $g(t)$ が選択される。所望の周波数応答は、ADCに周波数応答の不整合がほとんどないか、または、全くない応答であり、数学的にも理想的であり、理論的には、不整合を完全に除去することが可能である。

40

50

## 【0049】

プロセス203では、 $T/2$ の間隔で所望の周波数応答がサンプリングされ、記録される。このステップにおいて、周波数応答は、上記方程式4～18に用いることが可能な離散的形式にされる。

## 【0050】

プロセス204では、ブロック201及び203からサンプリングされ記録された応答を利用して、方程式9及び10で定義された行列のアレイが形成される。

## 【0051】

プロセス205では、方程式9及び10の行列に関して方程式13のフーリエ変換が実施され、個別行列要素の配列は、実数データ列として処理される。この結果、方程式16の周波数領域行列が得られる。10

## 【0052】

プロセス206では、アレイ内の各H行列アレイの逆数を取り、方程式17の乗算が実施される。このステップは、行列のアレイ全体にわたって各行列毎に実施される。

## 【0053】

プロセス207では、ブロック206のステップの結果に関して方程式18の逆フーリエ変換が実施される。個別行列要素のアレイは、逆フーリエ変換の複素数データ列として処理される。このステップでは、ベクトル・アレイ $q_m$ が得られる。

## 【0054】

プロセス208では、 $q_m$ をFIRフィルタ130において用い、ADC104と105（図1の全て）の間における周波数応答の不整合を補正する。従って、 $1/T$ のナイキスト周波数を超えないアナログ・ベースバンド入力信号120が、回路110に入力され、フィルタ130による調整を受け、もとのアナログ入力信号120の正確なデジタル表現107として出力される。20

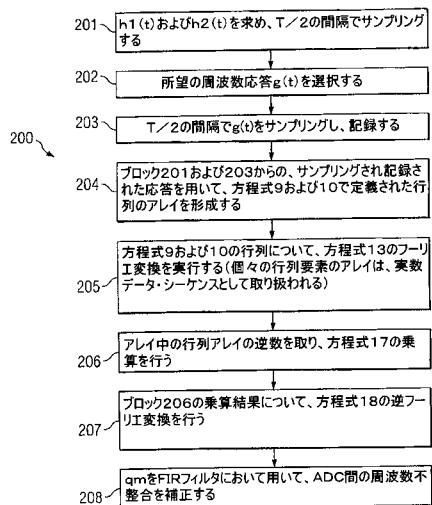

## 【0055】

図3は、交互ADCを用いてサンプル・レートの倍加を実施するためのシステム300に関する実施態様の1つである。システム300は、システム100と同様であるが、遅延素子（図1の遅延素子102のような）を用いる代わりに、進めた（あるいはまた、遅らせた）クロック301を利用する。その結果は、システム100の場合と同じになり、ADC104及び105の出力に、偶数及び奇数デジタル表現成分106が生じることになる。本発明は、入力アナログ・ベースバンド信号の偶数及び奇数デジタル表現成分を生成するいかなる特定のプロセスに制限されるものではなく、他の代替実施態様も本発明の範囲内である。偶数及び奇数デジタル表現成分は、ちょうど2つのサンプル値デジタル成分が存在する場合の、サンプル値デジタル成分間における、より一般的な補完関係の一例である。以下で解説するように、この補完関係は、3つ以上のサンプル値デジタル成分を含む実施態様を包含するように一般化することが可能である。30

## 【0056】

上記実施態様例では、 $2 \times 2$ マトリックス・タップを備えたFIRフィルタが利用される。しかし、本発明は、フィルタにおいてより大規模なマトリックス・タップが用いられる実施態様を扱うように拡張することが可能である。40

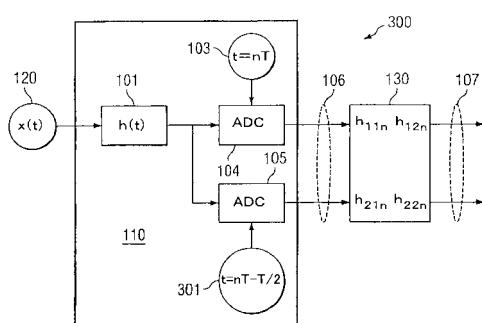

## 【0057】

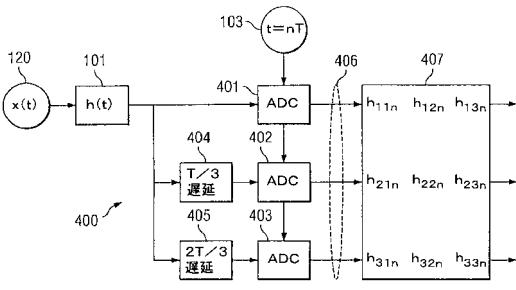

図4は、3つのADC401～403を利用して、サンプル・レートを3倍にするためのシステム400に関する実施態様の1つである。2つのADCを用いて、回路のサンプリング・レートが倍加される最後の例とちょうど同じように、図示構成をなすように3つのADCを用いることによって、サンプリング・レートを3倍にすることが可能である。ADC401は、その入力における遅延がゼロであり、一方、ADC402は、その入力に $T/3$ の遅延404を生じ、ADC403は、その入力に $2T/3$ の遅延405を生じる。ADC401～403は、概念上、循環的であり、従って、ある特定のクロック・サイクルにおいて、共に、遅延がゼロのサンプル、遅延が $T/3$ のサンプル、及び、遅延が $2T/3$ のサンプルを含む、1組のサンプルを生じることになる。50

## 【0058】

システム400では、偶数及び奇数ディジタル表現成分（図1の成分106のような）を利用するのではなく、上記2つのADCによる実施態様における遅延に類似したやり方で遅延させられる、3つの相補成分406が利用される。この場合、FIRフィルタ407は、 $3 \times 3$  フィルタである。マトリックス・フィルタ・タップの計算は、 $2 \times 2$  マトリックス・タップの計算と同様であり、従って、方程式3、11、及び、16～18は、当てはまるが、中間計算の方程式は、3要素ベクトル及び $3 \times 3$  行列の利用に適応させなければならない。

## 【0059】

他の複数ADCの実施態様は、可能であり、本発明の範囲内である。実際のところ、ADC数はNまで増加させることが可能であり（「N」は、必ずしも、上記方程式14で利用されているのと同じではない）、この場合、FIRフィルタは、相補的ディジタル表現成分に $N \times N$  マトリックス・タップを適用して、ADCの不整合を補正する。

## 【0060】

留意すべきは、フィルタ130のタップの計算が、行列及びベクトルを用いて実施されるので、偶数及び奇数サンプルが同時に採取された対として、また、フィルタ係数が同時に適用される4つの係数からなる集合として有効に表現されるという点である。別の観点からすると、ADC104及び105（図1の）は時間期間Tの交互時間にサンプルを採取し、フィルタ130（図1の）が交互時間に偶数及び奇数サンプルに係数を適用するとみなすことが可能である。これは、時変段階的方程式として表わすことが可能であり、この場合、フィルタ130は、ある時間にはある係数集合を偶数成分に適用し、別の時間には別の係数集合を奇数成分に適用する。いずれの見解を用いる適用例も、各種実施態様の範囲内であり、当該技術者には明らかなように、2つのアプローチは数学的に同等である。

## 【0061】

本発明及びその利点について詳述してきたが、もちろん、付属の請求項によって定義の本発明から逸脱することなく、さまざまな変更、代替、及び、改変を施すことが可能である。さらに、本出願の範囲は、本明細書に解説のプロセス、機械、製造、合成物、手段、方法、及び、ステップに限定されることを意図したものではない。開示から容易に明らかになるように、本明細書に解説の対応する実施態様とほぼ同じ機能を実施するか、または、ほぼ同じ結果を実現する、現存するか、または、開発されることになるプロセス、機械、製造、合成物、手段、方法、及び、ステップを利用することが可能である。従って、付属の請求項は、こうしたプロセス、機械、製造、合成物、手段、方法、及び、ステップを含むことを意図したものである。

## 【図面の簡単な説明】

## 【0062】

【図1】交互ADCを用いてサンプル・レートの倍加を実施するための本発明の実施態様の1つを例示した図である。

## 【図2】ADCの不整合を補正するための本発明の実施態様の1つに関するフローチャートである。

【図3】交互ADCを用いてサンプル・レートの倍加を実施するための本発明の実施態様の1つを例示した図である。

【図4】3つのADCを利用して、サンプル・レートを3倍にするための本発明の実施態様の1つを例示した図である。

## 【符号の説明】

## 【0063】

100：変換システム

101：インパルス応答

102：遅延素子

103：クロック

10

20

30

40

50

104、105：アナログ・デジタル変換器

110：変換回路

120：アナログ・ベースバンド信号

130：有限インパルス応答フィルタ

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(72)発明者 ハワード・イー・ヒルトン

アメリカ合衆国ワシントン州98290,スノホミッシュ,セヴァンティーンシックス・ストリート

・サウスイースト 15419

F ターム(参考) 5J022 AA01 BA05 BA10 CA07 CA10 CC03 CD01 CE01 CE04