(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3647642号

(P3647642)

(45) 発行日 平成17年5月18日(2005.5.18)

(24) 登録日 平成17年2月18日(2005.2.18)

(51) Int.C1.<sup>7</sup>

F 1

H01L 21/82

H01L 21/82

L

G06F 17/50

G06F 17/50

658K

H01L 21/822

H01L 27/04

D

H01L 27/04

請求項の数 7 (全 13 頁)

(21) 出願番号

特願平10-106507

(22) 出願日

平成10年4月16日(1998.4.16)

(65) 公開番号

特開平11-307639

(43) 公開日

平成11年11月5日(1999.11.5)

審査請求日

平成15年12月18日(2003.12.18)

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 山本 弘幸

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 大嶋 洋一

(56) 参考文献 特開昭62-001244 (JP, A)

最終頁に続く

(54) 【発明の名称】半導体集積回路の電源回路及び電源配線方法並びに電源配線手順を実行するプログラムを記録した記録媒体

## (57) 【特許請求の範囲】

## 【請求項 1】

第1及び第2の電源線をそれぞれ有する第1の電源領域及び第2の電源領域と、

前記第1の電源領域と前記第2の電源領域の間の領域に配置され、前記第1の電源領域

の第1の電源線が接続された第1の中継電源線と、

前記第1の電源領域と前記第2の電源領域の間の領域に配置され、前記第2の電源領域

の第2の電源線が接続された第2の中継電源線と、を有し、

前記第1の中継電源線と前記第2の中継電源線は所定の複数箇所において相互に接続

されている半導体集積回路の電源回路であって、

前記第1の電源領域は複数の前記第1の電源線を有し、

10

前記第2の電源領域は複数の前記第2の電源線を有し、

前記第1の電源線と前記第2の電源線とはピッチが互いに異なる、

ことを特徴とする半導体集積回路の電源回路。

## 【請求項 2】

前記第1の電源線と前記第1の中継電源線とは直交して接続され、

前記第2の電源線と前記第2の中継電源線とは直交して接続されていることを特徴とする

請求項1記載の半導体集積回路の電源回路。

## 【請求項 3】

前記第2の電源領域は前記第1の電源領域を取り囲むように配置され、

前記第1及び第2の中継電源線は、前記第1の電源領域と前記第2の電源領域の間の領

20

域に前記第1の電源領域の外周に沿って配置されていることを特徴とする請求項1記載の半導体集積回路の電源回路。

**【請求項4】**

前記第1の電源領域は前記第1の電源線と電位が異なる第3の電源線を有し、

前記第2の電源領域は前記第2の電源線と電位が異なる第4の電源線を有し、

前記第1の電源領域と前記第2の電源領域の間の領域に配置され、前記第1の電源領域の第3の電源線が接続された第3の中継電源線と、

前記第1の電源領域と前記第2の電源領域の間の領域に配置され、前記第2の電源領域の第4の電源線が接続された第4の中継電源線とを更に有する半導体集積回路の電源回路であって、

前記第3の電源線と前記第4の電源線とは電位が互いに異なり、前記第3の中継電源線と前記第4の中継電源線は電気的に分離されていることを特徴とする請求項1記載の半導体集積回路の電源回路。

**【請求項5】**

ピッチの異なる複数の電源線、電位の異なる複数の電源線又はピッチの異なる複数の電源線及び電位の異なる複数の電源線を半導体集積回路に配線する電源回路配線方法において、電位毎に中継電源線を設け、前記電源線を電位毎に該中継電源線に接続し、前記電源線には、該中継電源線を介して電源を供給することを特徴とする半導体集積回路の電源配線方法。

**【請求項6】**

a . セルに電源を供給する電源線を配線する半導体チップの外周に入出力セルを配置し、このセルの配置情報をレイアウトデータベースに記憶する工程と、

b . 前記半導体チップ内部に電源線の配線に影響を与えるセルを配置し、このセルの配置情報を前記レイアウトデータベースに記憶する工程と、

c . 前記半導体チップ内部に標準の電源の電位と異なる電位の電源線を配置する場合、異なる電位の電源線を配置する領域を設定し、この設定された領域の情報を前記レイアウトデータベースに記憶する工程と、

d . 前記半導体チップ内部に標準の電源線のピッチと異なるピッチの電源線を配置する場合、異なるピッチの電源線を配置する領域を設定し、この設定された領域の情報を前記レイアウトデータベースに記憶する工程と、

e . 前記セルの配置された領域又は電源線の配置される領域の領域間に、中継電源線を配線する工程と、

f . 前記中継電源線のうち、隣接する領域の中継電源線であって、かつ、同じ電位の中継電源線を相互に接続し、更に、前記セルの配置された領域又は電源線の配置される領域内における電源線を配線する工程とよりなることを特徴とする電源配線方法。

**【請求項7】**

コンピュータに、

a . セルに電源を供給する電源線を配線する半導体チップの外周に入出力セルを配置し、このセルの配置情報をレイアウトデータベースに記憶する手順と、

b . 前記半導体チップ内部に電源線の配線に影響を与えるセルを配置し、このセルの配置情報を前記レイアウトデータベースに記憶する手順と、

c . 前記半導体チップ内部に標準の電源の電位と異なる電位の電源線を配置する場合、異なる電位の電源線を配置する領域を設定し、この設定された領域の情報を前記レイアウトデータベースに記憶する手順と、

d . 前記半導体チップ内部に標準の電源線のピッチと異なるピッチの電源線を配置する場合、異なるピッチの電源線を配置する領域を設定し、この設定された領域の情報を前記レイアウトデータベースに記憶する手順と、

e . 前記セルの配置された領域又は電源線の配置される領域の領域間に、中継電源線を配線する手順と、

f . 前記中継電源線のうち、隣接する領域の中継電源線であって、かつ、同じ電位の中継電源線を相互に接続し、更に、前記セルの配置された領域又は電源線の配置される領域内における電源線を配線する手順を実行させることを特徴とするプログラムを記録した記録媒体。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

10

20

30

40

50

半導体集積回路の電源回路及び電源配線方法並びに電源配線手順を実行するプログラムを記録した記録媒体に関する。

#### 【0002】

##### 【従来の技術】

大規模集積回路（以下、「LSI」という。）の規模が大きくなるに従い、一つのLSI内部に標準（スタンダードセル、標準的なゲートアレイ等）とは異なる電位の電源又は標準とは異なるピッチの電源線（電源線は、セルに直接電源を供給する電源用配線をいい、ピッチが異なるとは、電源線の間隔又は電源線自体の線幅が異なることを言う。）を配線する必要が生じる。

#### 【0003】

従来は、電源線のピッチや電源線の電位の異なる領域間に電位の種類の合計分だけの垂直な同電位線分を挿入し双方の領域から、垂直な線分に接続する配線の配線層を変えたり、片方の配線を折り曲げて電源線のピッチを変えることで接続を行ってきた。

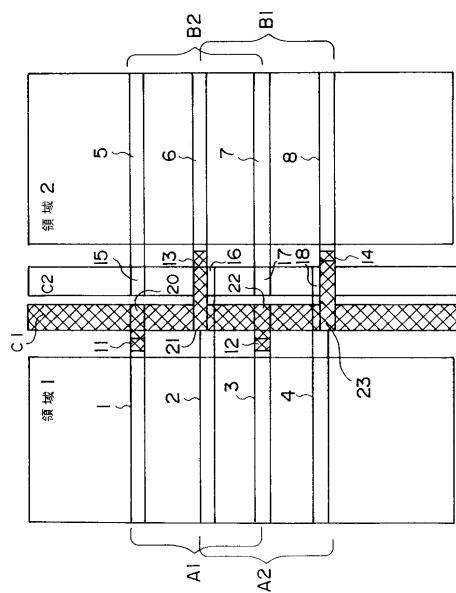

図1は、配線層を変えることにより、異なる電位を接続する従来例の方法である。電源領域1には、電源線1～4が配線され、電源領域2には、電源線5～8が配線されている。電源領域1の電源線1、3と電源領域2の電源線6、8が同電位の電源であり、また、電源領域1の電源線2、4と電源領域2の電源線5、7が同電位の電源である場合を示す。

#### 【0004】

本方法では、電源線1～8は2層配線であり、電源領域1と電源領域2の間に設けた電源C1は1層配線、同じく電源C2は2層配線である。電源領域1の電源線1、3及び電源領域2の電源線6、8と電源C1は同電位であり、電源領域1の電源線2、4及び電源領域2の電源線5、7と電源C2は同電位である。

電源領域1の電源線2、4及び電源領域2の電源線5、7は2層にあり、また、これらと同電位の電源C2も2層にあるので、そのまま、接点部15～18において接続される。また、電源領域1の電源線1、3及び電源領域2の電源線6、8は、2層にあり、これと同電位の電源C1は1層にあるので、電源線1、3、6、8は、層変換部11～14で、2層から1層に変換され、1層の電源C1と接点部20～23で接続される。

#### 【0005】

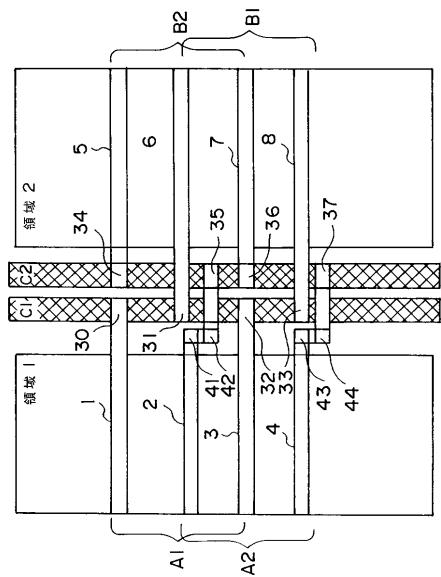

図2は、電源線を折り曲げることにより接続する方法である。この場合は、電源線1～8は、2層配線であり、電源C1、C2は、1層配線である。電源線1～8と電源C1、C2とは、層を異にするが、スルーホール等で接点部30～37で接続される。電源線2、4は、方向変換部41～44で折り曲げられて、電源線6、8との重ならないようにされて、電源C2と接続される。

#### 【0006】

##### 【発明が解決しようとする課題】

図1の方式では、予め電源線1～8の配線層が確定していなければならず、また、電源領域間に電源C1、C2の2層の配線層を使用するため、電源領域間の信号配線の接続の自由度が減少し、信号の配線が困難となることもある。

図2の方式は、電源線1～8の間隔が、電源線の太さに対して、十分に広いことが必要で、電源線1～8の間隔が狭いと、電源線をいくら曲げても、電源線との重なりを避けることができないという問題がある。

#### 【0007】

また、これら的方式は、電源配線層や電源線のピッチに依存していることから、半導体集積回路の電源の配線における、電源配線層又は電源線のピッチの自由度を低下させることにもつながる。

そこで、本発明は、上記問題に鑑みなされたものであり、電源配線のための手数を削減し、信号配線又は電源配線の自由度を損なうことなく、複数の異電位又は異電源ピッチを有する電源線を配線する半導体集積回路の電源回路を提供することを目的とするものである。

#### 【0008】

10

20

30

40

50

## 【課題を解決するための手段】

請求項 1 に記載された発明は、第 1 及び第 2 の電源線をそれぞれ有する第 1 の電源領域及び第 2 の電源領域と、第 1 の電源領域と第 2 の電源領域の間の領域に配置され、第 1 の電源領域の第 1 の電源線が接続された第 1 の中継電源線と、第 1 の電源領域と第 2 の電源領域の間の領域に配置され、第 2 の電源領域の第 2 の電源線が接続された第 2 の中継電源線と、を有し、第 1 の中継電源線と前記第 2 の中継電源線は所定の複数箇所において相互に接続されている半導体集積回路の電源回路であって、第 1 の電源領域は複数の前記第 1 の電源線を有し、第 2 の電源領域は複数の前記第 2 の電源線を有し、第 1 の電源線と前記第 2 の電源線とはピッチが互いに異なる、ことを特徴とする半導体集積回路の電源回路である。

10

## 【0010】

請求項 2 に記載された発明は、請求項 1 記載の半導体集積回路の電源回路において、前記第 1 の電源線と前記第 1 の中継電源線とは直交して接続され、前記第 2 の電源線と前記第 2 の中継電源線とは直交して接続されていることを特徴とする。

## 【0012】

請求項 3 に記載された発明は、請求項 1 記載の半導体集積回路の電源回路において、前記第 2 の電源領域は前記第 1 の電源領域を取り囲むように配置され、前記第 1 及び第 2 の中継電源線は、前記第 1 の電源領域と前記第 2 の電源領域の間の領域に前記第 1 の電源領域の外周に沿って配置されていることを特徴とする。

## 【0013】

請求項 4 に記載された発明は、請求項 1 記載の半導体集積回路の電源回路において、前記第 1 の電源領域は前記第 1 の電源線と電位が異なる第 3 の電源線を有し、前記第 2 の電源領域は前記第 2 の電源線と電位が異なる第 4 の電源線を有し、前記第 1 の電源領域と前記第 2 の電源領域の間の領域に配置され、前記第 1 の電源領域の第 3 の電源線が接続された第 3 の中継電源線と、前記第 1 の電源領域と前記第 2 の電源領域の間の領域に配置され、前記第 2 の電源領域の第 4 の電源線が接続された第 4 の中継電源線とを更に有する半導体集積回路の電源回路であって、前記第 3 の電源線と前記第 4 の電源線とは電位が互いに異なり、前記第 3 の中継電源線と前記第 4 の中継電源線は電気的に分離されていることを特徴とする。

## 【0016】

請求項 5 に記載された発明は、ピッチの異なる複数の電源線、電位の異なる複数の電源線又はピッチの異なる複数の電源線及び電位の異なる複数の電源線を半導体集積回路に配線する電源回路配線方法において、電位毎に中継電源線を設け、前記電源線を電位毎に該中継電源線に接続し、前記電源線には、該中継電源線を介して電源を供給することを特徴とする半導体集積回路の電源配線方法である。

## 【0018】

請求項 6 に記載された発明は、a. 電源線を配線する半導体チップの外周に入出力セルを配置し、このセルの配置情報をレイアウトデータベースに記憶する工程と、b. 前記半導体チップ内部に電源線の配線に影響を与えるセルを配置し、このセルの配置情報を前記レイアウトデータベースに記憶する工程と、c. 前記半導体チップ内部に標準の電源の電位と異なる電位の電源線を配置する場合、異なる電位の電源線を配置する領域を設定し、この設定された領域の情報を前記レイアウトデータベースに記憶する工程と、d. 前記半導体チップ内部に標準の電源線のピッチと異なるピッチの電源線を配置する場合、異なるピッチの電源線を配置する領域を設定し、この設定された領域の情報を前記レイアウトデータベースに記憶する工程と、e. 前記セルの配置された領域又は電源線の配置される領域の領域間に、中継電源線を配線する工程と、f. 前記中継電源線のうち、隣接する領域の中継電源線であって、かつ、同じ電位の中継電源線を相互に接続し、更に、前記セルの配置された領域又は電源線の配置される領域内における電源線を配線する工程とよりなることを特徴とする電源配線方法である。

## 【0020】

20

30

40

50

請求項 7 に記載された発明は、コンピュータに、 a . セルに電源を供給する電源線を配線する半導体チップの外周に入出力セルを配置し、このセルの配置情報をレイアウトデータベースに記憶する手順と、 b . 前記半導体チップ内部に電源線の配線に影響を与えるセルを配置し、このセルの配置情報を前記レイアウトデータベースに記憶する手順と、 c . 前記半導体チップ内部に標準の電源の電位と異なる電位の電源線を配置する場合、異なる電位の電源線を配置する領域を設定し、この設定された領域の情報を前記レイアウトデータベースに記憶する手順と、 d . 前記半導体チップ内部に標準の電源線のピッチと異なるピッチの電源線を配置する場合、異なるピッチの電源線を配置する領域を設定し、この設定された領域の情報を前記レイアウトデータベースに記憶する手順と、 e . 前記セルの配置された領域又は電源線の配置される領域の領域間に、中継電源線を配線する手順と、 f . 前記中継電源線のうち、隣接する領域の中継電源線であって、かつ、同じ電位の中継電源線を接続し、更に、前記セルの配置された領域又は電源線の配置される領域内における電源線を配線する手順を実行させることを特徴とするプログラムを記録した記録媒体である。10

#### 【 0 0 2 2 】

#### 【発明の実施の形態】

次に、本発明の実施の形態について図面と共に説明する。

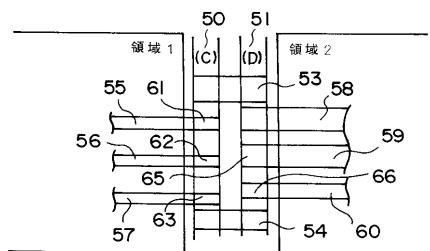

図 3 は、本発明の配線の基本を説明するための図である。電源領域 1 の電源線と電源領域 2 の電源線の電位が同じ場合である。電源領域 1 には、電源線 5 5 ~ 5 7 が配線され、電源領域 2 には、電源線 5 8 ~ 6 0 が配線されている。20

#### 【 0 0 2 3 】

本発明においては、各電源領域毎に、隣接する領域の間に、中継電源線を設ける。つまり、電源領域 1 の中継電源線 C と電源領域 2 の中継電源線 D を、隣接する電源領域 1 、 2 の間に設けている。更に、各電源線は中継電源線と直交する。つまり、電源領域 1 の電源線 5 5 ~ 5 7 は、中継電源線 C と電源線 5 5 ~ 5 7 との交点 6 1 ~ 6 3 で接続される。同じく、電源領域 2 の電源線 5 8 ~ 6 0 は、電源線 5 8 ~ 6 0 と中継電源線 D との交点 6 4 ~ 6 6 で接続される。また、中継電源線 C と中継電源線 D とは、任意の複数箇所において相互に接続される。図 3 では、接続回線 5 3 、 5 4 により、 2 箇所で接続されている。

#### 【 0 0 2 4 】

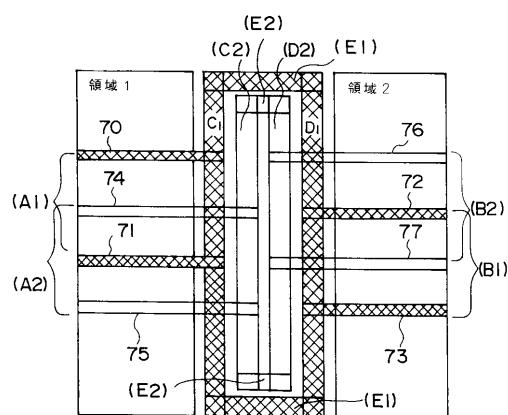

図 4 は、本発明の第 1 の実施の形態を説明するための図で、二つの電源領域が、夫々、同じ二つの電位の電源線を有する場合である。なお、以降の説明において、電源線及び中継電源線は、横線の場合は、 2 層に配線され、縦線の場合は、 1 層に配線される。電源線及び中継電源線の 1 層と 2 層は、必要に応じ、コントクトホール等で接続される。30

#### 【 0 0 2 5 】

電源領域 1 は、電源線 7 0 、 7 1 、 7 4 、 7 5 を有し、更に、電源領域 1 の中継電源線 C 1 及び中継電源線 C 2 を設ける。また、電源領域 2 は、電源線 7 2 、 7 3 、 7 6 、 7 7 を有し、更に、電源領域 2 の中継電源線 D 1 及び中継電源線 D 2 を設ける。ここで、電源線 7 0 ~ 7 3 、中継電源線 C 1 及び中継電源線 D 1 の電位が同じであり、電源線 7 4 ~ 7 7 、中継電源線 C 2 及び中継電源線 D 2 の電位が同じであるとする。

#### 【 0 0 2 6 】

電源領域 1 の電源線 7 0 、 7 1 は、中継電源線 C 1 と接続し、電源領域 1 の電源線 7 4 、 7 5 は、中継電源線 C 2 と接続する。また、電源領域 2 の電源線 7 2 、 7 3 は、中継電源線 D 1 と接続し、電源領域 2 の電源線 7 6 、 7 7 は、中継電源線 D 2 に接続する。中継電源線 C 1 と中継電源線 D 1 は、接続回線 E 1 で接続され、中継電源線 C 2 と中継電源線 D 2 は、接続回線 E 2 で接続される。中継電源線同士を密接に結合する（多くの点で接続する）ことにより、中継電源線を細くすることができる。つまり、中継電源線同士を多点で接続すると、電源経路が多くとれて、特定の中継電源線を経由する割合が減少するから、その電源線を細くすることが可能となる。40

#### 【 0 0 2 7 】

このように接続した結果、電源線 7 0 ~ 7 3 は、中継電源線 C 1 及び中継電源線 D 1 を介50

して外部電源に接続され、また、電源線 74～77 は、中継電源線 C2 及び中継電源線 D2 を介して外部電源に接続される。

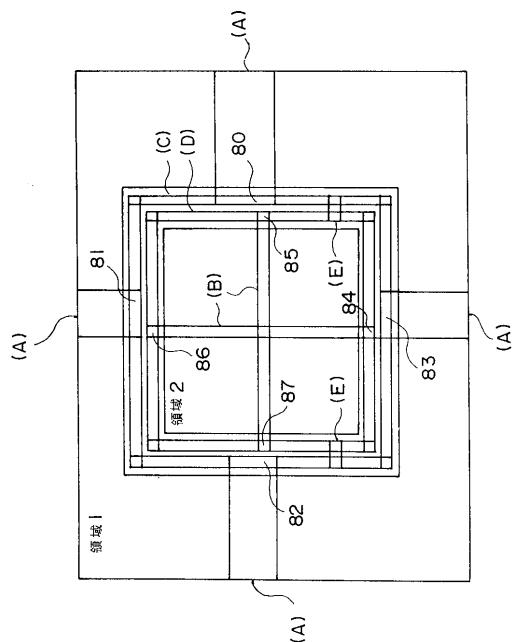

図 5 は、本発明の第 2 の実施の形態を説明するための図で、隣接する電源領域の一方の電源領域が他方の電源領域の外周に位置する場合である。中継電源線は、一方の電源領域及び他方の電源領域の間に設ける。

#### 【0028】

電源領域 1 が電源領域 2 の外周に位置し、電源領域 1 の電源線 A と電源領域 2 の電源線 B とが同電位の場合を説明する。電源領域 1 の中継電源線 C 及び電源領域 2 の中継電源線 D を、電源領域 1 及び電源領域 2 の間にループ状に設ける。電源領域 1 の電源線 A は、電源領域 1 の中継電源線 C と交点 80～83 で接続される。また、電源領域 2 の電源線 B は、電源領域 2 の中継電源線 D と交点 84～87 で接続される。二つの中継電源線 C、D は、任意の点で接続回線 E により接続される。

#### 【0029】

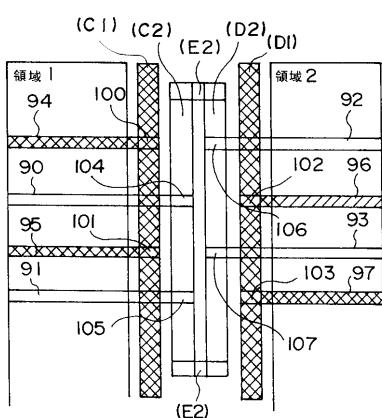

図 6 は、本発明の第 3 の実施の形態を説明するための図で、二つの電源領域が、夫々、二つの電位の電源線を有し、そのうちの一つの電位が、隣接する領域の電源線と同じ場合である。

電源領域 1 の同じ電位の電源線 90 及び電源線 91 と電源領域 2 の同じ電位の電源線 92 及び電源線 93 とが同電位で、電源領域 1 の同じ電位の電源線 94 及び電源線 95 と電源領域 2 の同じ電位の電源線 96 及び電源線 97 とが異なる電位を有する場合である。

#### 【0030】

電源領域 1 の電源線 90、91 を電源領域 1 の中継電源線 C2 に接続し、電源領域 2 の電源線 92、93 を電源領域 2 の中継電源線 D2 に接続する。そして、中継電源線 C2、D2 の電位は同じであるから、中継電源線 C2 と中継電源線 D2 を接続回線 E2 で接続する。

更に、電源領域 1 の電源線 94、95 は、電源領域 1 の中継電源線 C1 に交点 100、101 で接続される。また、電源領域 2 の電源線 96、97 は、電源領域 2 の中継電源線 D1 に交点 102、103 で接続される。中継電源線 C1 と中継電源線 D1 とは、電位が異なるので、分離したままである。

#### 【0031】

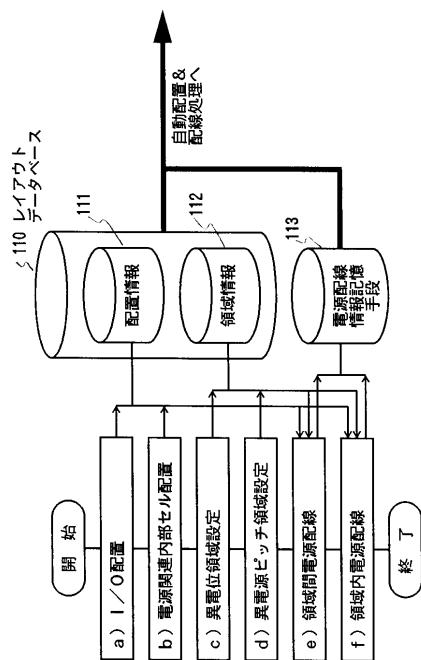

図 7 は、コンピュータを用いて、LSI の電源配線のレイアウト設計を行うフローである。次の段階よりなる。

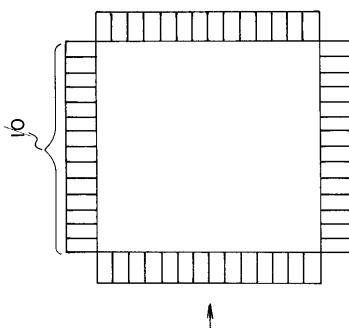

a. 図 8 に示すように、セルに電源を供給するための電源線を配線する半導体チップの外周に I/O セル（入出力セル）を配置し、このセルの配置情報をレイアウトデータベース 110 の配置情報領域 111 に記憶する段階。

#### 【0032】

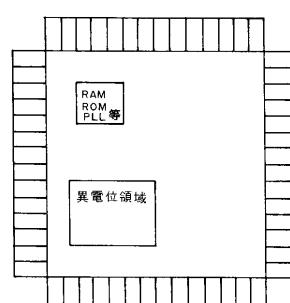

b. 図 9 に示すように、前記半導体チップ内部に、例えば、ROM、RAM、PLL（Phase Locked Loop）等のような電源線の配線に影響を与えるセルを配置し、このセルの配置情報を前記レイアウトデータベース 110 の配置情報 111 に記憶する段階。

c. 図 10 に示すように、前記半導体チップ内部に標準の電源の電位（スタンダードセル、標準的なゲートアレイ等における電位）と異なる電位の電源線を配置する場合、異なる電位の電源線を配置する領域を設定し、この設定された領域の情報を前記レイアウトデータベース 110 の領域情報 112 に記憶する段階。

#### 【0033】

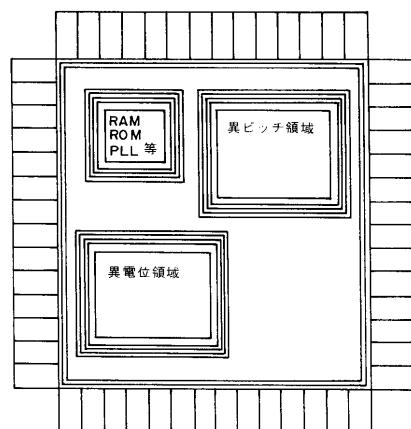

d. 図 11 に示すように、前記半導体チップ内部に標準の電源線のピッチと異なるピッチの電源線を配置する場合、異なるピッチの電源線を配置する領域を設定し、この設定された領域の情報を前記レイアウトデータベース 110 の領域情報 112 に記憶する段階。

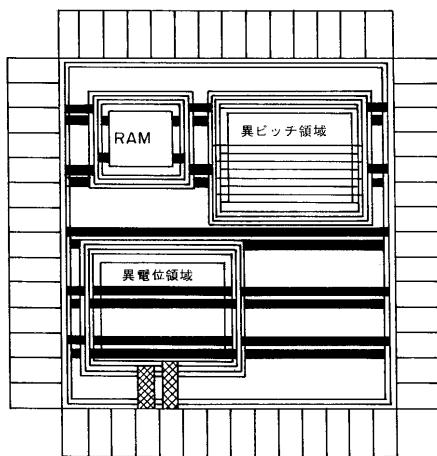

e. 図 12 に示すように、前記 b の段階で設定されたセルの配置された領域又は前記 c、d の段階で設定された電源線の配置される領域の領域間に、各領域毎に、かつ電位毎に中継電源線を配線し、この情報を電源配線情報記憶手段 113 に記憶する段階。

#### 【0034】

10

20

30

40

50

f. 図13に示すように、前記中継電源線のうち、隣接する領域の中継電源線であって、かつ、同じ電位の中継電源線を接続し、更に、前記bの段階で設定されたセルの配置された領域又は前記c、dの段階で設定された電源線の配置される領域内に電源線を配線する段階。

この、配線レイアウト後に、電源線に合わせてセルを配置する処理が行われ、その後、このレイアウトデータベース110内の配置情報111と領域情報112と電源配線情報113とに基づいて自動配置、自動配線処理を行うことが可能となる。

#### 【0035】

なお、前記bの段階で設定されたセルの配置された領域又は前記c、dの段階で設定された電源線の配置される領域の領域間の中継電源線は、図12のように各領域の周囲を中継電源線で囲むことにより、結果として、中継電源線が領域間に設けるようにしてもよい。

#### 【0036】

上述の如く本発明の実施の形態によれば、次に述べる種々の効果を実現することができる。

電源供給の中継を行う中継電源線を設け、半導体上のセルに電源を供給する電源線には中継電源線を介して電源を供給することにより、効率の良い配線を行い、I/Oセルとの接続回線数を減少させ、その結果、信号配線又は電源配線の自由度を上げた複数の異電位、異電源ピッチ又は異電位及び異電源ピッチを有する電源線を配線する半導体集積回路の電源回路を提供することができる。

また、電源線と中継電源線とを直交して接続することにより、各電源線及び各中継電源線を、夫々平行に配線し、電源線と中継電源線を効率よく整然と配線することができる。

また、半導体集積回路に複数の電源領域を設け、更に電源領域に対して、電位毎に一又は複数の中継電源線を設けることにより、領域を単位として配線を行い、設置するセルに応じて、柔軟に電源配線を行うことができる。

また、中継電源線を電源領域の外周又は隣接する電源領域の間に設けたことにより、中継電源線の配線による、信号配線又は電源配線の自由度を上げることができる。

また、隣接する電源領域の一方の電源領域が他方の電源領域の外周に位置する場合であっても、信号配線又は電源配線の自由度を上げ、複数の異電位、異電源ピッチ又は異電位及び異電源ピッチを有する電源線を配線する半導体集積回路の電源回路を提供することができる。

また、同じ電位の中継電源線を相互に接続することにより、I/Oセルとの接続回線を少なくでき、信号配線又は電源配線の自由度を損なうことを最小にすることができる。

また、隣接する電源領域の中継電源線を複数箇所において接続することにより、電源供給の経路を複数とし、その結果、個々の電源線に流れる電流を少なくし、電源線の幅を狭くすることができる。

また、半導体集積回路に配線する電源回路配線方法において、電位毎に中継電源線を設け、前記電源線を電位毎に該中継電源線に接続し、前記電源線には、該中継電源線を介して電源を供給することにより、効率の良い配線を行い、I/Oセルとの接続回線数を減少させ、その結果、半導体集積回路の配線において、信号配線又は電源配線の自由度を上げることができる。

また、半導体チップ内部に標準の電源の電位と異なる電位の電源線を配置する場合、異なる電位の電源線を配置する領域を設定し、この設定された領域の情報をレイアウトデータベースに記憶する工程と、半導体チップ内部に標準の電源線のピッチと異なるピッチの電源線を配置する場合、異なるピッチの電源線を配置する領域を設定し、この設定された領域の情報をレイアウトデータベースに記憶する工程を設けることにより、特に、半導体集積回路の電源回路における電源の配線方法において、電源配線のための手数を削減し、信号配線又は電源配線の自由度を上げた複数の異電位、異電源ピッチ又は異電位及び異電源ピッチを有する電源線を配線することができる。

また、前記半導体チップ内部に標準の電源の電位と異なる電位の電源線を配置する場合、異なる電位の電源線を配置する領域を設定し、この設定された領域の情報をレイアウト

10

20

30

40

50

データベースに記憶する手順と、前記半導体チップ内部に標準の電源線のピッチと異なるピッチの電源線を配置する場合、異なるピッチの電源線を配置する領域を設定し、この設定された領域の情報をレイアウトデータベースに記憶する手順を設けることにより、半導体集積回路の電源回路における電源の配線において、電源配線のための手数を削減し、信号配線又は電源配線の自由度を上げた複数の異電位、異電源ピッチ又は異電位及び異電源ピッチを有する電源線を配線することができる電源配線方法の手順が記録されたプログラムを記録した記憶媒体を提供することができる。

**【発明の効果】**

上述の如く本発明によれば、電源配線のための手数を削減し、信号配線又は電源配線の自由度を損なうことなく、複数の異電位又は異電源ピッチを有する電源線を配線する半導体集積回路の電源回路を提供することができる。

10

**【0037】**

請求項 2 記載の発明によれば、電源線と中継電源線とが、直交して接続することにより、各電源線及び各中継電源線を、夫々平行に配線し、電源線と中継電源線を効率よく整然と配線することができる。

請求項 3 記載の発明によれば、半導体集積回路に複数の電源領域を設け、更に電源領域に対して、電位毎に一又は複数の中継電源線を設けることにより、領域を単位として配線を行い、設置するセルに応じて、柔軟に電源配線を行うことができる。

**【0038】**

請求項 4 記載の発明によれば、中継電源線を電源領域の外周又は隣接する前記電源領域の間に設けたことにより、中継電源線の配線による、信号配線又は電源配線の自由度を上げることができる。

20

請求項 5 記載の発明によれば、隣接する電源領域の一方の電源領域が他方の電源領域の外周に位置する場合であっても、請求項 4 に係る発明と同様に、信号配線又は電源配線の自由度を上げ、複数の異電位、異電源ピッチ又は異電位及び異電源ピッチを有する電源線を配線する半導体集積回路の電源回路を提供することができる。

**【0039】**

請求項 6 記載の発明によれば、同じ電位の中継電源線を相互に接続することにより、I/Oセルとの接続回線を少なくでき、信号配線又は電源配線の自由度を損なうことを最小にすることができる。

30

請求項 7 記載の発明によれば、隣接する電源領域の中継電源線を複数箇所において接続することにより、電源供給の経路を複数とし、その結果、個々の電源線に流れる電流を少なくし、電源線の幅を狭くすることができる。

**【0040】**

請求項 8 記載の発明によれば、半導体集積回路に配線する電源回路配線方法において、電位毎に中継電源線を設け、前記電源線を電位毎に該中継電源線に接続し、前記電源線には、該中継電源線を介して電源を供給することにより、効率の良い配線を行い、I/Oセルとの接続回線数を減少させ、その結果、半導体集積回路の配線において、信号配線又は電源配線の自由度を上げることができる。

**【0041】**

請求項 9 記載の発明によれば、半導体チップ内部に標準の電源の電位と異なる電位の電源線を配置する場合、異なる電位の電源線を配置する領域を設定し、この設定された領域の情報をレイアウトデータベースに記憶する工程と、半導体チップ内部に標準の電源線のピッチと異なるピッチの電源線を配置する場合、異なるピッチの電源線を配置する領域を設定し、この設定された領域の情報をレイアウトデータベースに記憶する工程を設けることにより、特に、半導体集積回路の電源回路における電源の配線方法において、電源配線のための手数を削減し、信号配線又は電源配線の自由度を上げた複数の異電位、異電源ピッチ又は異電位及び異電源ピッチを有する電源線を配線することができる。

40

**【0042】**

請求項 10 記載の発明によれば、前記半導体チップ内部に標準の電源の電位と異なる電位

50

の電源線を配置する場合、異なる電位の電源線を配置する領域を設定し、この設定された領域の情報をレイアウトデータベースに記憶する手順と、前記半導体チップ内部に標準の電源線のピッチと異なるピッチの電源線を配置する場合、異なるピッチの電源線を配置する領域を設定し、この設定された領域の情報をレイアウトデータベースに記憶する手順を設けることにより、半導体集積回路の電源回路における電源の配線において、電源配線のための手数を削減し、信号配線又は電源配線の自由度を上げた複数の異電位、異電源ピッチ又は異電位及び異電源ピッチを有する電源線を配線することができる電源配線方法の手順が記録されたプログラムを記録した記憶媒体を提供することができる。

【図面の簡単な説明】

- 【図 1】従来の配線層を変えることによる接続方法 10

- 【図 2】従来の電源線を折り曲げることにより接続する方法である。

- 【図 3】本発明の配線の基本を説明するための図である。

- 【図 4】本発明の第 1 の実施の形態を説明するための図である。

- 【図 5】本発明の第 2 の実施の形態を説明するための図である。

- 【図 6】本発明の第 3 の実施の形態を説明するための図である。

- 【図 7】コンピュータを用いて、LSI の電源配線のレイアウト設計を行うフローである。

- 。

- 【図 8】半導体チップの外周に I/O セルを配置する図である。

- 【図 9】電源線の配線に影響を与えるセルを配置する図である。

- 【図 10】異なる電位の電源線を配置する領域を設定する図である。 20

- 【図 11】異なるピッチの電源線を配置する領域を設定する図である。

- 【図 12】各領域毎に中継電源線を配線する図である。

- 【図 13】同じ電位の中継電源線を接続し、領域内の電源線を配線する図である。

【符号の説明】

- |                    |               |    |

|--------------------|---------------|----|

| 1 1、 1 2、 1 3、 1 4 | 層変換部          |    |

| 2 0、 2 1、 2 2、 2 3 | 接点部           |    |

| 3 0、 3 1、 3 2、 3 3 | 接点部           |    |

| 4 1、 4 2、 4 3、 4 4 | 方向変換部         |    |

| 5 5 ~ 6 0          | 電源線           |    |

| 5 0、 5 1           | 中継電源線         | 30 |

| 5 3、 5 4           | 接続回線          |    |

| 1 1 0              | レイアウトデータベース   |    |

| 1 1 1              | 配置情報          |    |

| 1 1 2              | 領域情報          |    |

| 1 1 3              | 電源配線情報記憶手段    |    |

| A                  | 電源領域 1 の電源線   |    |

| B                  | 電源領域 2 の電源線   |    |

| C                  | 電源領域 1 の中継電源線 |    |

| D                  | 電源領域 2 の中継電源線 |    |

| E                  | 接続回線          | 40 |

【図1】

従来の配線層を変えることによる接続方法

【図2】

従来の電源線を折り曲げることにより接続する方法

【図3】

本発明の配線の基本を説明するための図

【図4】

本発明の第1の実施の形態を説明するための図

【図5】

本発明の第2の実施の形態を説明するための図

【図6】

本発明の第3の実施の形態を説明するための図

【図7】

コンピュータを用いてLSIの電源配線の

レイアウト設計を行うフロー

【図8】

半導体チップの外周にI/Oセルを配置する図

【図9】

電源線の配線に影響を与えるセルを配置する図

【図10】

異なる電位の電源線を配置する領域を設定する図

【図 1 1】

異なるピッチの電源線を配置する領域を設定する図

【図 1 2】

各領域毎に中継電源線を配線する図

【図 1 3】

同じ電位の中継電源線を接続し、領域内の電源線を配線する図

---

フロントページの続き

(58)調査した分野(Int.Cl.<sup>7</sup> , DB名)

H01L 21/82

H01L 21/822

H01L 27/04

G06F 17/50