(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2005-501313

(P2005-501313A)

(43) 公表日 平成17年1月13日(2005.1.13)

(51) Int.C1.<sup>7</sup>

F 1

テーマコード(参考)

**G06F 12/14**

G06F 12/14

510C

5B017

**G06F 9/30**

G06F 9/30

380Z

5B033

**G06F 11/22**

G06F 11/22

310D

5B048

審査請求 未請求 予備審査請求 有 (全 42 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2002-589946 (P2002-589946) |

| (86) (22) 出願日 | 平成14年4月17日 (2002.4.17)       |

| (85) 翻訳文提出日   | 平成15年11月10日 (2003.11.10)     |

| (86) 國際出願番号   | PCT/US2002/011935            |

| (87) 國際公開番号   | W02002/093336                |

| (87) 國際公開日    | 平成14年11月21日 (2002.11.21)     |

| (31) 優先権主張番号  | 09/852,942                   |

| (32) 優先日      | 平成13年5月10日 (2001.5.10)       |

| (33) 優先権主張国   | 米国(US)                       |

| (31) 優先権主張番号  | 09/852,372                   |

| (32) 優先日      | 平成13年5月10日 (2001.5.10)       |

| (33) 優先権主張国   | 米国(US)                       |

| (31) 優先権主張番号  | 09/853,226                   |

| (32) 優先日      | 平成13年5月11日 (2001.5.11)       |

| (33) 優先権主張国   | 米国(US)                       |

|          |                                                                                                                                                                                             |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (71) 出願人 | 591016172<br>アドバンスト・マイクロ・ディバイシズ・<br>インコーポレイテッド<br>ADVANCED MICRO DEVICES INCORPORATED<br>アメリカ合衆国、94088-3453<br>カリフォルニア州、サンノゼ、ピイ・<br>オウ・ボックス・3453、ワン・エイ・<br>エム・ディ・プレイス、メイル・ストップ<br>・68(番地なし) |

| (74) 代理人 | 100099324<br>弁理士 鈴木 正剛                                                                                                                                                                      |

| (74) 代理人 | 100111615<br>弁理士 佐野 良太                                                                                                                                                                      |

最終頁に続く

(54) 【発明の名称】パーソナルコンピュータシステムにおいて裏口アクセス機構を閉鎖するための機構

## (57) 【要約】

裏口アクセス機構を閉鎖するための方法、デバイスおよびシステム。1以上のハードウェアデバッグテスト(HDT)イネーブルビットを格納するように構成された第1のレジスタと、複数のHDT入力信号を受信すべく接続された第1の制御ロジックと、第1のレジスタに接続された第2の制御ロジックとが、プロセッサに含まれる。第1の制御ロジックは第1のレジスタにアクセスすべく接続されている。第2の制御ロジックはプロセッサのリセットに応答して1以上のデフォルト値を第1のレジスタに格納するように構成されている。もうひとつのプロセッサには、複数のマイクロコード入力を受信すべく接続された第1の制御ロジックと、第1の制御ロジックに接続された第1のレジスタと、第1のレジスタに接続された第2の制御ロジックとが含まれる。第1のレジスタは、1以上のマイクロコードローダーイネーブルビットを格納するように構成されている。第2の制御ロジックは、プロセッサのリセットに応答して1以上のデフォルト値を第1のレジスタに格納するように構成されている。

**【特許請求の範囲】****【請求項 1】**

1以上のハードウェアデバッグテスト(HDT)イネーブルビットを格納するように構成された第1のレジスタと、

複数のHDT入力信号を受信すべく接続された第1の制御ロジックであって、第1のレジスタにアクセスすべく接続された第1の制御ロジックと、

第1のレジスタに接続され、プロセッサのリセットに応答して1以上のデフォルト値を第1のレジスタに格納するように構成された第2の制御ロジックと、を含むプロセッサ。

**【請求項 2】**

第1の制御ロジックがさらに、HDTモードに入る要求を受信するように構成され、第1の制御ロジックがさらに、HDTモードに入る要求に応答して、第1のレジスタに格納された1以上のHDTイネーブルビットの選択されたエントリを読み出すように構成され、第1の制御ロジックがさらに、1以上のHDTイネーブルビットの選択されたエントリに基づいて、HDTモードに入る要求を受け入れるまたは拒否するように構成されている、請求項1に記載のプロセッサ。 10

**【請求項 3】**

1以上のHDTイネーブルビットの1以上のデフォルト値を格納するように構成された1以上の不揮発性メモリセルをさらに含み、第2の制御ロジックがさらに、プロセッサのリセットに応答して、1以上のHDTイネーブルビットの1以上のデフォルト値を1以上の不揮発性メモリセルから読み出し、かつ、1以上のHDTイネーブルビットの1以上のデフォルト値を第1のレジスタに書き込むべく接続されている、請求項1に記載のプロセッサ。 20

**【請求項 4】**

第2の制御ロジックがさらに、プロセッサのリセットに応答して、1以上のHDTイネーブルビットの1以上のデフォルト値を示す信号を受信し、かつ、1以上のHDTイネーブルビットの1以上のデフォルト値を第1のレジスタに書き込みすべく接続されている、請求項1に記載のプロセッサ。

**【請求項 5】**

1以上のマイクロコードローダーイネーブルビットを格納するように構成された第3のレジスタと、

複数のマイクロコード入力を受信すべく接続された第3の制御ロジックであって、第3のレジスタにアクセスすべく接続されている第3の制御ロジックと、 30

第3のレジスタに接続され、プロセッサのリセットに応答して1以上のデフォルト値を第3のレジスタに格納するように構成された第4の制御ロジックと、をさらに含む、請求項1に記載のプロセッサ。

**【請求項 6】**

第3の制御ロジックがさらに、マイクロコード修正要求を受信するように構成され、第3の制御ロジックがさらに、マイクロコード修正要求に応答して、第3のレジスタに格納された1以上のマイクロコードローダーイネーブルビットの選択されたエントリを読み出すように構成され、第3の制御ロジックがさらに、1以上のマイクロコードローダーイネーブルビットの選択されたエントリに基づいて、マイクロコード修正要求を受け入れるまたは拒否するように構成されている、請求項5に記載のプロセッサ。 40

**【請求項 7】**

第1の制御ロジックに接続された第2のレジスタをさらに含み、第2のレジスタが1以上のHDTイネーブルロックビットを格納するように構成されている、請求項1に記載のプロセッサ。

**【請求項 8】**

第1の制御ロジックがさらに、HDTモードのステータスの修正要求を受信するように構成され、第1の制御ロジックがさらに、HDTモードのステータスの修正要求に応答して、第2のレジスタに格納された1以上のHDTイネーブルロックビットの選択されたエントリを読み出すように構成され、第1の制御ロジックがさらに、1以上のHDTイネーブルロック 50

ビットの選択されたエントリに基づいて、HDTモード修正要求を受け入れるまたは拒否するように構成されている、請求項7に記載のプロセッサ。

【請求項9】

複数のマイクロコード入力を受信すべく接続された第1の制御ロジックと、

第1の制御ロジックに接続され、1以上のマイクロコードローダーイネーブルビットを格納するように構成された第1のレジスタと、

第1のレジスタに接続され、プロセッサのリセットに応答して1以上のデフォルト値を第1のレジスタに格納するように構成された第2の制御ロジックと、を含むプロセッサ。

【請求項10】

第1の制御ロジックがさらに、マイクロコード修正要求を受信するように構成され、第1の制御ロジックがさらに、マイクロコード修正要求に応答して、第1のレジスタに格納された1以上のマイクロコードローダーイネーブルビットの選択されたエントリを読み出すように構成され、第1の制御ロジックがさらに、1以上のマイクロコードローダーイネーブルビットの選択されたエントリに基づいて、マイクロコード修正要求を受け入れるまたは拒否するように構成されている、請求項9に記載のプロセッサ。 10

【請求項11】

1以上のマイクロコードローダーイネーブルビットの1以上のデフォルト値を格納するように構成された1以上の不揮発性メモリセルをさらに含み、第2の制御ロジックがさらに、プロセッサのリセットに応答して、1以上のマイクロコードローダーイネーブルビットの1以上のデフォルト値を1以上の不揮発性メモリセルから読み出し、かつ、1以上のマイクロコードローダーイネーブルビットの1以上のデフォルト値をマイクロコードローダーのレジスタに書き込むべく接続されている、請求項9に記載のプロセッサ。 20

【請求項12】

第2の制御ロジックがさらに、プロセッサのリセットに応答して、1以上のマイクロコードローダーイネーブルビットの1以上のデフォルト値を示す信号を受信し、かつ、1以上のマイクロコードローダーイネーブルビットの1以上のデフォルト値を第1のレジスタに書き込みすべく接続されている、請求項9に記載のプロセッサ。

【請求項13】

第1の制御ロジックに接続された第2のレジスタをさらに含み、第2のレジスタが1以上のマイクロコードローダーイネーブルロックビットを格納するように構成されている、請求項9に記載のプロセッサ。 30

【請求項14】

第1の制御ロジックがさらに、マイクロコードローダーのロックステータス修正要求を受信するように構成され、第1の制御ロジックがさらに、マイクロコードローダーのロックステータス修正要求に応答して、第2のレジスタに格納された1以上のマイクロコードローダーイネーブルロックビットの選択されたエントリを読み出すように構成され、第1の制御ロジックがさらに、1以上のマイクロコードローダーイネーブルロックビットの選択されたエントリに基づいて、マイクロコードローダーのロックステータス修正要求を受け入れるまたは拒否するように構成されている、請求項13に記載のプロセッサ。

【請求項15】

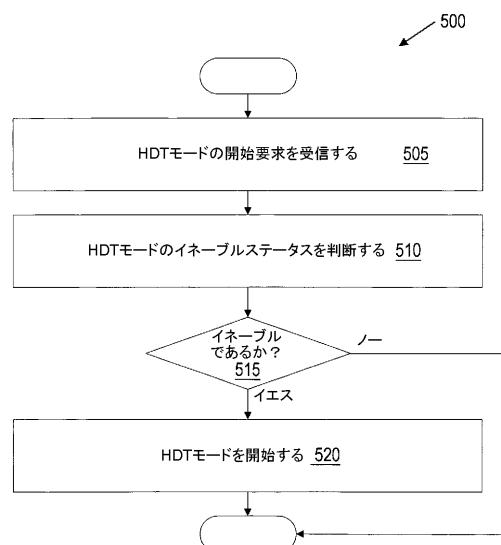

HDTモードの開始要求を受信し、

HDTモードのイネーブルステータスを判断し、

HDTモードのイネーブルステータスがイネーブルに設定されている場合にHDTモードを開始することを含む、HDTモードのイネーブルステータスを判断するための方法。 40

【請求項16】

HDTモードのイネーブルステータスを判断することが、1以上のHDTイネーブルビットに対応する1以上のエントリをレジスタから読み出すことを含む、請求項15に記載の方法。

【請求項17】

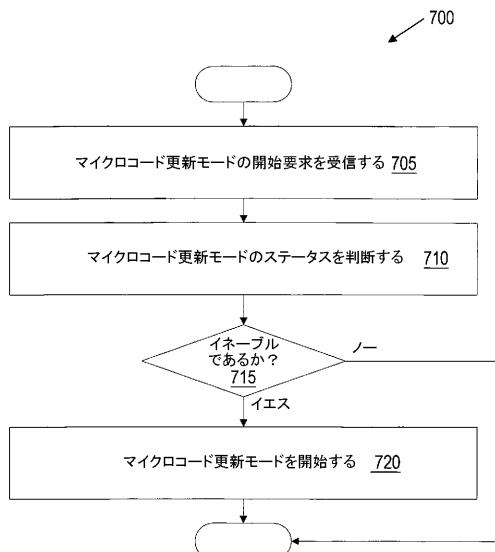

マイクロコード修正要求を受信し、

マイクロコードローダーのイネーブルステータスを判断し、 50

マイクロコードローダーのイネーブルステータスがイネーブルに設定されている場合にマイクロコードを修正することを含む、マイクロコードを修正するための方法。

【請求項 18】

マイクロコードローダーのイネーブルステータスを判断することが、1以上のマイクロコードローダーイネーブルビットに対応する1以上のエントリをレジスタから読み出すことを含む、請求項17に記載の方法。

【請求項 19】

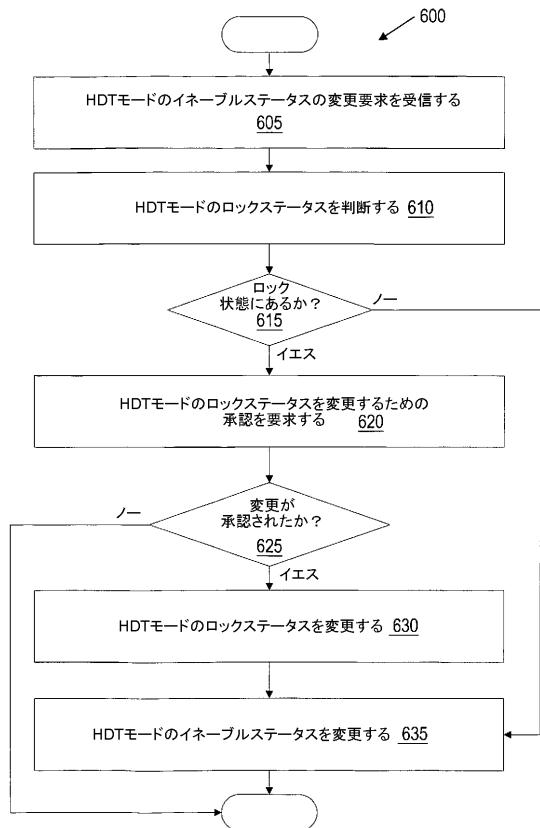

HDTモードのステータスの変更要求を受信し、

HDTモードのイネーブルロックステータスを判断し、

HDTモードのイネーブルロックステータスがアンロックに設定されている場合にHDTモードのステータスを修正することを含む、HDTモードのステータスの変更方法。 10

【請求項 20】

HDTモードのイネーブルロックステータスを判断することが、1以上のHDTイネーブルロックビットに対応する1以上のエントリをレジスタから読み出すことを含む、請求項19に記載の方法。

【請求項 21】

HDTモードのステータスを修正することが、1以上のHDTイネーブルビットに対応する1以上のエントリをレジスタに書き込むことを含む、請求項19に記載の方法。

【請求項 22】

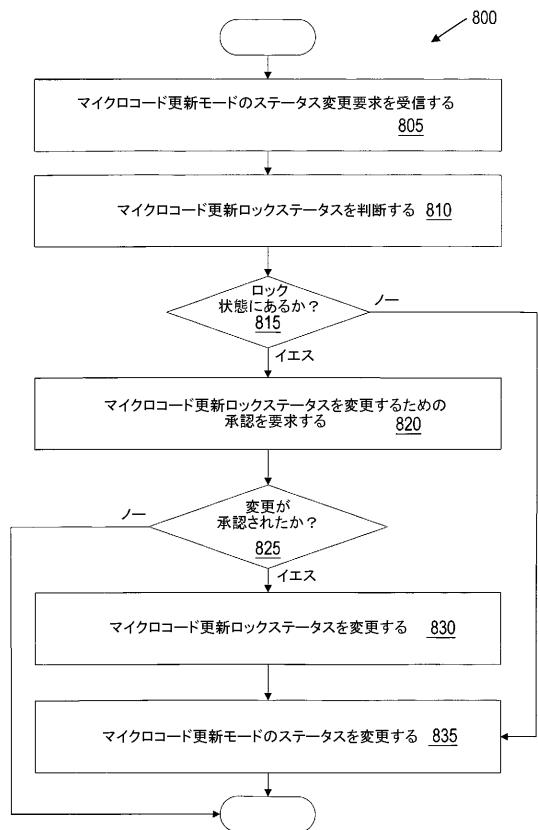

マイクロコードローダーのイネーブルステータスの変更要求を受信し、

マイクロコードローダーのイネーブルロックステータスを判断し、

マイクロコードローダーのイネーブルロックステータスがアンロックに設定されている場合にマイクロコードローダーのイネーブルステータスを修正することを含む、マイクロコードローダーのイネーブルステータスの変更方法。 20

【請求項 23】

マイクロコードローダーのイネーブルロックステータスを判断することが、1以上のマイクロコードローダーイネーブルロックビットに対応する1以上のエントリをレジスタから読み出すことを含む、請求項22に記載の方法。

【請求項 24】

マイクロコードローダーのイネーブルステータスを修正することが、1以上のマイクロコードローダーイネーブルビットに対応する1以上のエントリをレジスタに書き込むことを含む、請求項22に記載の方法。 30

【請求項 25】

1以上の不揮発性メモリセルから1以上のデフォルト値を読み出すことと、プルアップレジスタまたはプルダウンレジスタによって1以上のデフォルト値をストラップされた値として受信することと、からなる群から選択される、1以上のデフォルト値を取得することと、

プロセッサのリセットに応答して、1以上のデフォルト値を1以上のさまざまなエントリとして1以上のレジスタに書き込むことと、を含み、1以上のさまざまなエントリは、

1以上のHDTイネーブルビットと、

1以上のHDTイネーブルロックビットと、

マイクロコードローダーの1以上のイネーブルビットと、

マイクロコードローダーの1以上のイネーブルロックビットと、からなる群から選択される、プロセッサを動作させる方法。 40

【発明の詳細な説明】

【関連出願の表示】

【0001】

本件出願は、発明者デール・イー・ギューリック (Dale E. Gulick) およびジェフリー・エス・ストロンギン (Geoffrey S. Strongin)、発明の名称「Secure Execution Box and Method (セキュア実行ボックスおよび方法)」である、2001年5月10日に 50

出願の係属中の米国特許出願第09/852,372号の一部継続出願である。また、本件出願は、発明者ジェフリー・エス・ストロンギンおよびデール・イー・ギューリック、2001年5月10日に出願の発明の名称「Computer System Architecture for Enhanced Security and Manageability(セキュリティを高め、かつ管理の容易性を高めるためのコンピュータシステムアーキテクチャ)」である、係属中の米国特許出願第09/852,942号の一部継続出願でもある。

【技術分野】

【0002】

本発明は、広義にはコンピュータシステムに関し、特に、パーソナルコンピュータシステムを不正な裏口アクセスから保護するための方法および装置に関する。

10

【背景技術】

【0003】

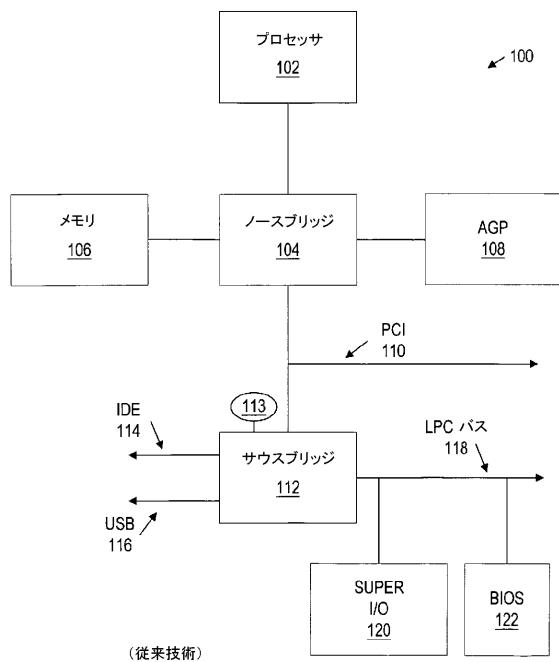

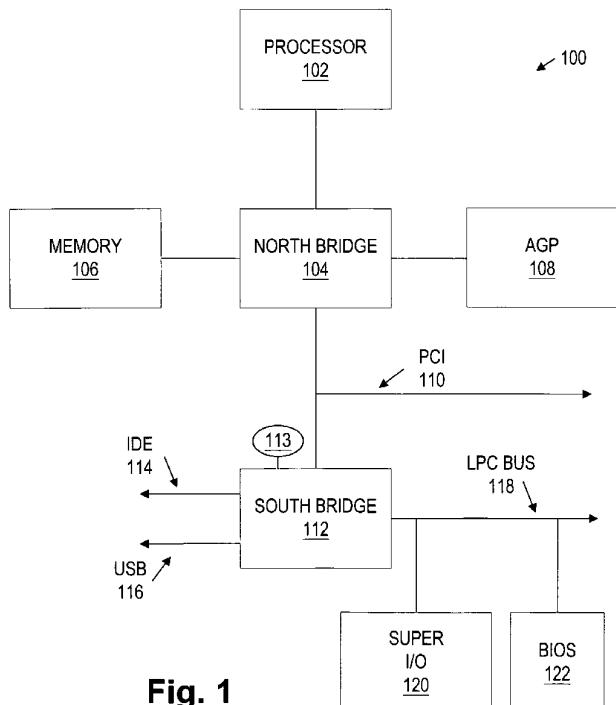

代表的なコンピュータシステム100を図1に示す。このコンピュータシステム100は、プロセッサ102と、ノースブリッジ104と、メモリ106と、AGP(Advanced Graphics Port)メモリ108と、PCI(Peripheral Component Interconnect)バス110と、サウスブリッジ112と、バッテリと、ATアタッチメント(ATA)インターフェース114[より一般的にはIDE(Integrated Drive Electronics)インターフェースとして知られる]と、ユニバーサルシリアルバス(USB)インターフェース116と、Low Pin Count(LPC)バス118と、入出力コントローラチップ(Super I/O<sup>TM</sup>)120と、BIOSメモリ122とを含む。ノースブリッジ104およびサウスブリッジ112は、チップをひとつしか含まないものであってもよいし、全体を総称して「チップセット」と呼ぶ複数のチップを含むものであってもよい点に注意されたい。また、コンピュータシステム100には、キャッシュ、モデム、パラレルインターフェースまたはシリアルインターフェース、SCSIインターフェース、ネットワークインターフェースカード[「Super I/O」はカリフォルニア州サンタクララのナショナルセミコンダクターコーポレーションの商標である]など、必要に応じて他のバス、デバイスおよび/またはサブシステムを含み得る点にも注意されたい。

【0004】

プロセッサ102はノースブリッジ104に接続されている。ノースブリッジ104は、プロセッサ102、メモリ106、AGPメモリ108、PCIバス110それぞれの相互インターフェースを提供する。サウスブリッジ112は、PCIバス110、IDEインターフェース114やUSBインターフェース116、LPCバス118に接続された周辺機器やデバイス、サブシステムそれぞれの相互インターフェースを提供する。バッテリ113はサウスブリッジ112に接続された状態で示されている。Super I/O<sup>TM</sup>チップ120はLPCバス118に接続されている。

【0005】

ノースブリッジ104は、プロセッサ102、メモリ106、AGPメモリ108、PCIバス110に接続されたデバイス、サウスブリッジ112に接続されたデバイスおよびサブシステム同士および/またはこれらの間での通信アクセスを提供する。一般に、コンピュータシステム100への接続用のPCIバス110とつながるPCI「スロット」(図示せず)に、着脱自在の周辺デバイスが挿入される。あるいは、マザーボード上にあるデバイスをPCIバス110に直接接続してもよい。

【0006】

サウスブリッジ112は、PCIバス110と、LPCバス118(あるいはX-バスまたはISAバスなどの旧世代のバス)を介してコンピュータシステム100に接続されているのが普通であるモデムやプリンタ、キーボード、マウスなどのさまざまなデバイスやサブシステムとの間のインターフェースを提供する。サウスブリッジ112には、デバイスとコンピュータシステム100の残りの部分とを、IDEインターフェース114、USBインターフェース116、LPCバス118を介してインターフェースするロジックが含まれる。

【発明の開示】

50

**【発明が解決しようとする課題】****【0007】**

ハードウェア的な観点からみると、x86の動作環境では、ユーザプライバシーの保護、企業秘密および法人資産に対するセキュリティの提供、あるいはコンテンツプロバイダの所有者の権利の保護という点ではほとんど何もしていない。これらの目標すなわちプライバシー、セキュリティ、所有権(Privacy、Security、Ownership:以下、PSOと総称する)はいずれもコンピュータがインターネットに接続される時代にあって次第に重要なものとなりつつあるが、初期のパーソナルコンピュータはPSOの需要を見越して設計されたものではなかった。

**【0008】**

ソフトウェア的な観点からみても、x86の動作環境がPSOの点で粗末なことに変わりはない。ソフトウェア経由あるいは単にパーソナルコンピュータのカバーを開けるだけでハードウェアを直接いじることが容易であるため、セキュリティソフトウェアおよびデバイスの大半が侵入者または泥棒による危機にさらされる。パーソナルコンピュータはものの見事に使いやすいものであるが、この点はPSOの問題を大きくするにすぎないのである。

**【課題を解決するための手段】****【0009】****発明の開示**

本発明によれば、プロセッサが得られる。このプロセッサは、1以上のハードウェアデバッグテスト(HDT)イネーブルビットを格納するように構成された第1のレジスタと、複数のHDT入力信号を受信すべく接続された第1の制御ロジックと、第1のレジスタに接続された第2の制御ロジックと、を含む。第1の制御ロジックは第1のレジスタにアクセスすべく接続されている。第2の制御ロジックは、プロセッサのリセットに応答して1以上のデフォルト値を第1のレジスタに格納するように構成されている。

**【0010】**

本発明によれば、HDTモードのイネーブルステータスを判断するための方法が得られる。この方法は、HDTモードの開始要求を受信し、HDTモードのイネーブルステータスを判断し、HDTモードのイネーブルステータスがイネーブルに設定されている場合にHDTモードを開始することを含む。

**【0011】**

本発明によれば、マイクロコードを修正するための方法が得られる。この方法は、マイクロコード修正要求を受信し、マイクロコードローダーのイネーブルステータスを判断し、マイクロコードローダーのイネーブルステータスがイネーブルに設定されている場合にマイクロコードを修正することを含む。

**【0012】**

本発明によれば、HDTモードのステータスの変更方法が得られる。この方法は、HDTモードのステータスの変更要求を受信し、HDTモードのイネーブルロックステータスを判断し、HDTモードのイネーブルロックステータスがアンロックに設定されている場合にHDTモードのステータスを修正することを含む。

**【0013】**

本発明によれば、マイクロコードローダーのイネーブルステータスの変更方法が得られる。この方法は、マイクロコードローダーのイネーブルステータスの変更要求を受信し、マイクロコードローダーのイネーブルロックステータスを判断し、マイクロコードローダーのイネーブルロックステータスがアンロックに設定されている場合にマイクロコードローダーのイネーブルステータスを修正することを含む。

**【0014】**

本発明によれば、プロセッサを動作させる方法が得られる。この方法は、1以上の不揮発性メモリセルから1以上のデフォルト値を読み出すことと、プルアップレジスタまたはプルダウンレジスタによって1以上のデフォルト値をストラップされた値(strapped value)として受信することと、からなる群から選択される、1以上のデフォルト値を得ること

10

20

30

40

50

とを含む。この方法は、プロセッサのリセットに応答して、1以上のデフォルト値を1以上のさまざまなエントリとして1以上のレジスタに書き込むことを含む。1以上のさまざまなエントリは、1以上のHDTイネーブルビットと、1以上のHDTイネーブルロックビットと、マイクロコードローダーの1以上のイネーブルビットと、マイクロコードローダーの1以上のイネーブルロックビットと、からなる群から選択される。

#### 【0015】

添付の図面を参照しての以下の説明を参照することで、本発明を理解することができよう。図中、同様の構成要素には同様の参照符号を付してある。

#### 【0016】

本発明はさまざまな改変や別の形態が可能なものであるが、その具体的な実施形態を一例として図示し、本願明細書中にて詳細に説明する。しかしながら、本願明細書に記載の具体的な実施形態についての説明は、ここに開示の特定の形態に本発明を限定することを意図したものではなく、添付の特許請求の範囲に定義した本発明の範囲に含まれる改変例、等価物および別の形をすべて包含することを意図している点を理解されたい。10

#### 【発明を実施するための最良の形態】

#### 【0017】

以下、実例としての本発明の実施形態について説明する。説明を明確にするため、本願明細書では実際の実施例における特徴をすべて説明したわけではない。もちろん、このような実際の実施形態を開発するにあたっては、いずれの場合もシステム関連の制約やビジネス関連の制約を踏まえるなど、実施例ごとにさまざまな判断を行って開発者らの意図する目的を達成していく必要があり、これは実施例ごとに異なるものであることは理解できよう。さらに、このような開発作業は複雑かつ時間を要するものになる場合があるが、それでも本願の開示内容を利用できる当業者らにとっては日常業務の一環であろうことも理解できよう。参照符号にアルファベットも加えてあるのは、それぞれの参照符号を付した項目の別の実施形態または例を示すためである。20

#### 【0018】

低消費電力設計されたコンピュータシステムの動作モードのひとつにシステム管理モード(system management mode:SMM)がある。SMMは第四世代のx86プロセッサ用に作られたものである。新しい世代のx86プロセッサが登場するにつれて、SMMはオペレーティングシステムにとって相対的にトランスペアレン特なものとなつていった。すなわち、コンピュータシステムはオペレーティングシステムに対してほとんどまたは全く影響を与えることなくSMMに入ったりこのモードから抜けたりするのである。30

#### 【0019】

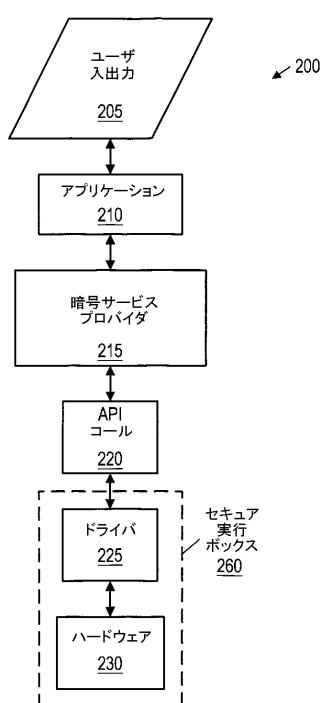

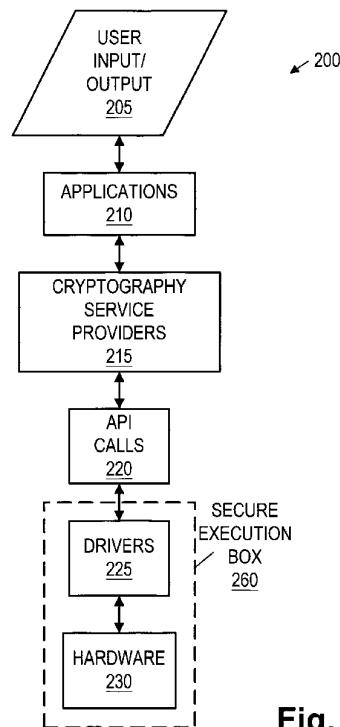

本発明の一態様による、セキュア実行ボックス260を有するコンピュータシステムにおけるデータ・コマンドフローのフローチャートの実施形態のブロック図を図2に示す。ユーザ入出力(1/0)データおよび/またはコマンド205が1以上のアプリケーション210との間で受け渡しされる。アプリケーション210は、コンピュータシステム100または他の何らかのコンピュータシステムなどのコンピュータシステム内の暗号サービスプロバイダ215とデータやコマンドをやり取りする。暗号サービスプロバイダ215は、ハードウェア230に対するアクセスを提供するドライバ225と、API(アプリケーションプログラミングインターフェース)コール220を使って通信するものであつてもよい。40

#### 【0020】

本発明の一態様によれば、ドライバ225およびハードウェア230は、セキュア実行モード(SEM)260で動作するように構成されたセキュア実行ボックスの一部である。単にセキュリティ動作とも呼ぶ、プライバシー、セキュリティ、所有権(PSO)についての信頼された動作を、コンピュータシステムがSEM260にある間に実行することができる。ユーザ1/0205および/またはアプリケーション210からのソフトウェアコールについてはSMM260にあるセキュア実行ボックスに対して行うことができる。また、ソフトウェアコールによってSEM260にあるセキュア実行ボックスに対してアクセスし、詳50

細については後述するものなどのさまざまなセキュリティハードウェア資源を利用できる。

#### 【0021】

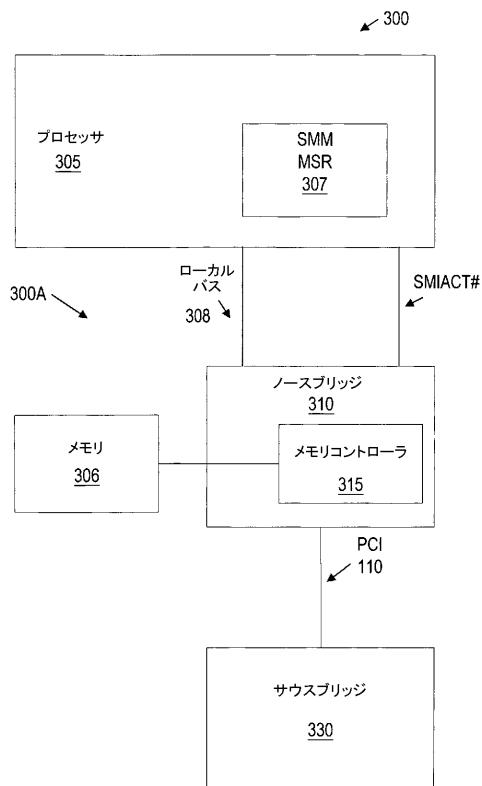

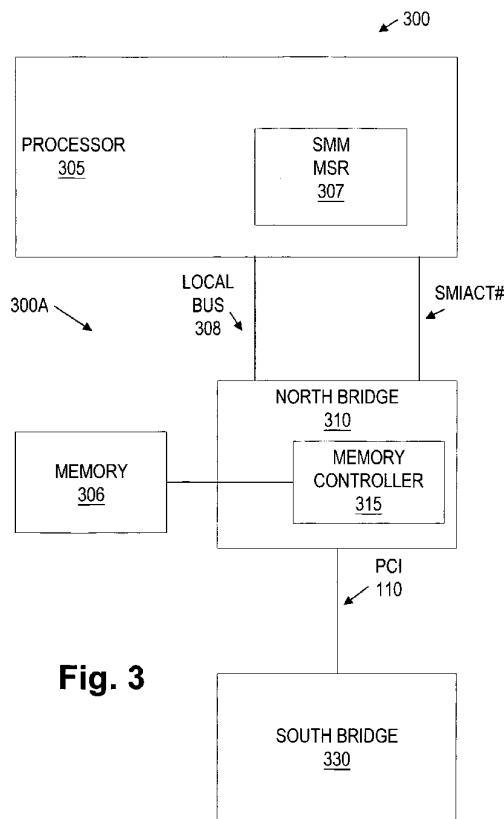

本発明のさまざまな態様による、SMM MSRを有するコンピュータシステム300の実施形態をブロック図の形で図3に示す。図3は、プロセッサ305と、ノースブリッジ310と、メモリ306と、サウスブリッジ330とを含む。プロセッサは1以上のSMM MSR(マシン固有レジスタ)307を含む。ノースブリッジ310はメモリコントローラ315を含む。ノースブリッジ310は、プロセッサ305とサウスブリッジ330との間で、ローカルバス308を介してプロセッサ305に接続され、PCIバス110を介してサウスブリッジ330に接続されている。ノースブリッジ310はプロセッサ305からSMIA CT#信号を受信すべく接続されている。10

#### 【0022】

図3の実施形態では、コンピュータシステム300は、標準的なプロセッサ信号(ノースブリッジ310へのSMIACT#など)および/またはローカルバス308およびPCIバス110でのバスサイクルを利用して、プロセッサ305がSMMにある旨を伝達する。

#### 【0023】

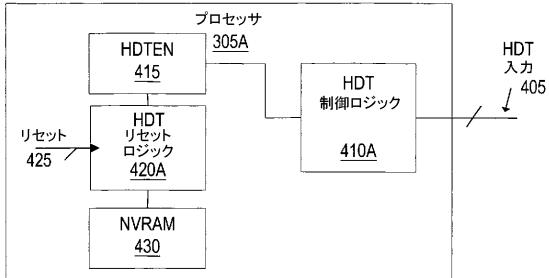

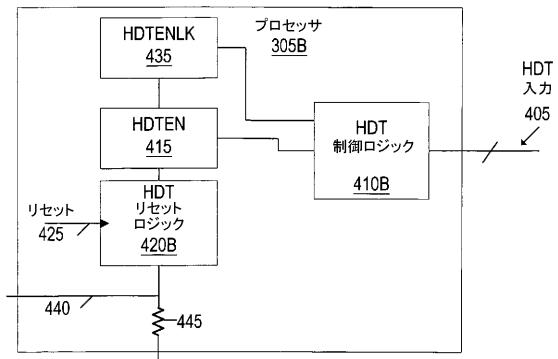

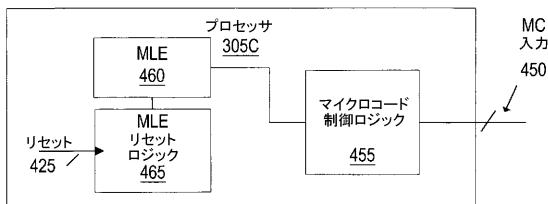

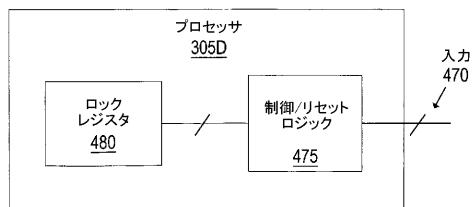

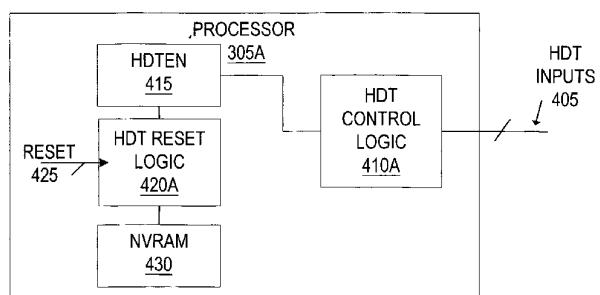

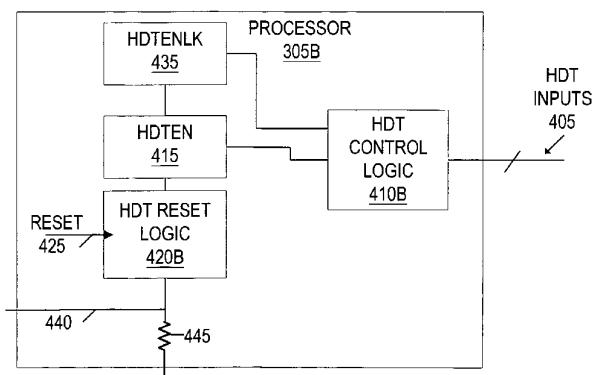

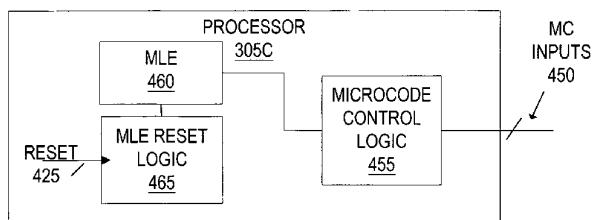

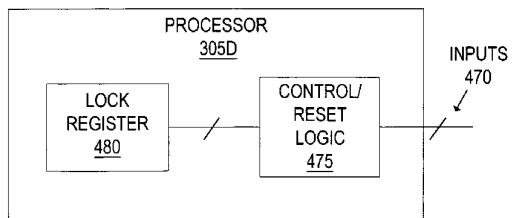

本発明のさまざまな実施形態では、SMMのセキュリティが前提である。弱点を突かれてSMMのセキュリティを危うくする可能性のある1以上のいわゆる「裏口」が存在し得る点に注意されたい。企図される問題としては、プロセッサ305のハードウェアデバッグテスト(HDT)モードの誤用ならびにプロセッサ305がマイクロコードをロードして差し替える機能があげられる。図4A~図4Dに示されているのは、プロセッサ305のさまざまな実施形態305A、305B、305C、305Dであり、その各々が1以上の裏口からの攻撃に対するさまざまなセキュリティプロテクションを含む。20

#### 【0024】

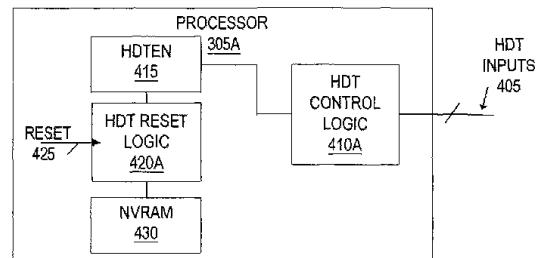

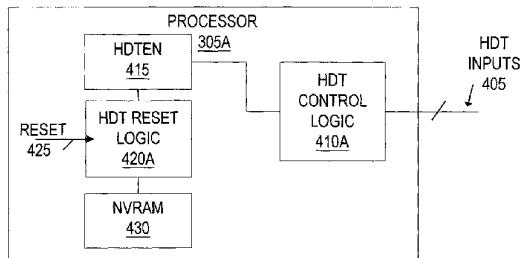

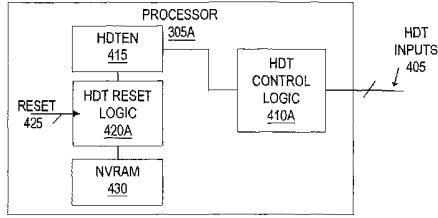

図4Aでは、プロセッサ305Aに、HDT制御ロジック410Aと、HDTリセットロジック420Aと、HDTイネーブルレジスタ415および不揮発性ランダムアクセスメモリ(NVRAM)430を含む1以上のレジスタとが含まれる。図示のように、HDT制御ロジック410Aは、複数のHDTピン405を介して複数の入力信号を受信すべく接続されている。HDT制御ロジック410Aはさらに、HDTイネーブルレジスタ415に接続されている。HDTリセットロジック420Aは、ライン425でRESET信号を受信し、HDTイネーブルレジスタ415およびNVRAM430にアクセス(すなわち読み出しおよび書き込み)すべく接続されている。30

#### 【0025】

図4Bでは、図4Bのプロセッサ305Bに、HDT制御ロジック410Bと、HDTリセットロジック420Bと、HDTイネーブルレジスタ415およびHDTイネーブルロックレジスタ435を含む2つのレジスタと、が含まれる。図示のように、HDT制御ロジック410Bは、複数のHDTピン405を介して複数の入力信号を受信すべく接続されている。HDT制御ロジック410Bはさらに、HDTイネーブルレジスタ415およびHDTイネーブルロックレジスタ435に接続されている。HDTリセットロジック420Bは、プルアップ(またはプルダウン)抵抗器445を介して、ライン425でRESET信号を受信し、ライン440などで信号を受信すべく接続されている。40

#### 【0026】

図4Cでは、プロセッサ305Cに、マイクロコード制御ロジック455と、マイクロコードローダーのイネーブルリセットロジック465と、マイクロコードローダーのイネーブルレジスタ460を含む1以上のレジスタと、が含まれる。図示のように、マイクロコード制御ロジック455は、複数のマイクロコード入力ピン450を介して複数の入力信号を受信すべく接続されている。マイクロコード制御ロジック455はさらに、マイクロコードローダーのイネーブルレジスタ460に接続されている。マイクロコードローダーのイネーブルリセットロジック465は、RESET信号を受信し、マイクロコードローダーのイネーブルレジスタ460にアクセスすべく接続されている。50

## 【 0 0 2 7 】

図 4 Dでは、プロセッサ 3 0 5 Dに、マイクロコード制御ロジック 4 5 5 と統合されたHDT制御ロジック 4 1 0 と、HDTリセットロジック 4 2 0 と、制御 / リセットロジック 4 7 5 を形成するためのMLEリセットロジック 4 6 5 とが含まれる。HDTイネーブルレジスタ 4 1 5 およびマイクロコードローダーのイネーブルレジスタ 4 6 0 は、マルチビットロックレジスタ 4 8 0 に統合されている。制御 / リセットロジック 4 7 5 への複数の入力 4 7 0 が図示されている。これらの複数の入力 4 7 0 には、HDT入力 4 0 5 、マイクロコード入力 4 5 0 および / またはリセット信号伝達手段を含み得る。他の実施形態（図示せず）では、HDT制御ロジック 4 1 0 およびマイクロコード制御ロジック 4 5 5 のみを統合するか、あるいはHDTリセットロジック 4 2 0 およびMLEリセットロジック 4 6 5 だけを統合する。

10

## 【 0 0 2 8 】

本発明のさまざまな実施形態によれば、レジスタ 4 1 5 、 4 3 5 および 4 6 0 ならびにNVRAM 4 3 0 に、1 以上のビット用の格納空間が含まれる。一実施形態では、各レジスタが 1 ビットを格納するように構成されている。イネーブルレジスタ 4 1 5 および 4 6 0 を単一のロックレジスタに統合してもよく、HDTイネーブルロックレジスタ 4 3 5 をマイクロコードのイネーブルロックレジスタとして利用してもよい点に注意されたい。レジスタ 4 1 5 、 4 3 5 、 4 6 0 および / または 4 8 0 をSMM MSR 3 0 7 に含み得る点も企図される。

## 【 0 0 2 9 】

さまざまな実施形態において、HDTイネーブルレジスタ 4 1 5 は、HDTモードがイネーブルであるかデセーブルであるかを示す1 以上のHDTイネーブルビットを格納するように構成されている。HDTリセットロジック 4 2 0 は、プロセッサ 3 0 5 のリセット時に1 以上のHDTイネーブルビットをデフォルトの状態に設定するように構成されている。

20

## 【 0 0 3 0 】

図 4 A および図 4 B に示すものなどのHDTモードを制御するための複数の実施形態が企図される。一実施形態では、エンジニアリングと試験とに用いられる、量産ではないプロセッサ 3 0 5 では、HDTモードがデフォルトでイネーブルである。このHDTモードについては、量産される標準的なプロセッサ 3 0 5 のデフォルトでデセーブルにしてもよい。図 4 A に示すもうひとつの実施形態では、デフォルトの状態をNVRAM 4 3 0 に格納し、ここから読み出すようにすることができる。この実施形態ではデフォルトの状態を変更可能にしてもよいが、図示の実施形態ではデフォルトの状態はデセーブルに設定されている。図 4 B に示すさらに他の実施形態では、ストラッピングオプションを使ってデフォルトの状態を設定する。このデフォルト値がプルアップ（またはプルダウン）抵抗器 4 4 5 を介してHDTリセットロジック 4 2 0 B に提供される。

30

## 【 0 0 3 1 】

図 4 C および図 4 D に示すものなどのマイクロコードローダーのモードを制御するための複数の実施形態も企図される。図示しない一実施形態では、マイクロコード更新モードを、エンジニアリングと試験とに用いられる量産ではないプロセッサ 3 0 5 上のデフォルトとしてイネーブルにする。このマイクロコード更新モードについては、量産される標準的なプロセッサ 3 0 5 のデフォルトとしてデセーブルにすることができる。図 4 A に示す実施形態に類似の別の実施形態では、デフォルトの状態をNVRAM 4 3 0 に格納し、ここから読み出すようにすることができる。この実施形態ではデフォルトの状態を変更可能にしてもよいが、図示の実施形態ではデフォルトの状態はデセーブルに設定されている。図 4 B に示すさらに他の実施形態では、ストラッピングオプションを使うことがデフォルトの状態である。このデフォルト値がプルアップ（またはプルダウン）抵抗器 4 4 5 を介してMLEリセットロジック 4 6 5 に提供される。

40

## 【 0 0 3 2 】

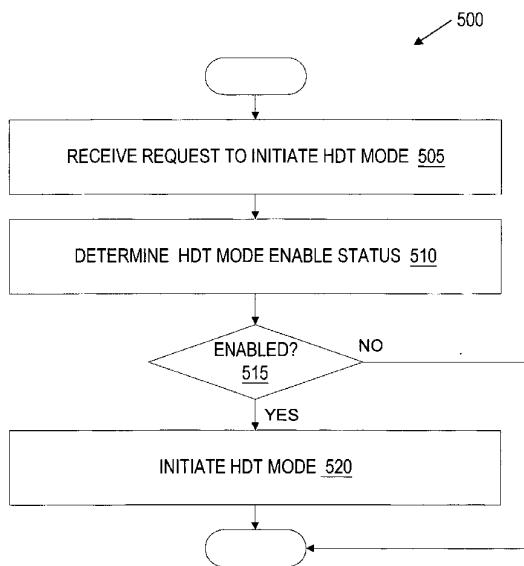

ここで図 5 に移ると、HDTモードを開始するための方法 5 0 0 が図示されている。HDTモードに入る要求を受信（ステップ 5 0 5 ）したことに応答して、HDT制御ロジック 4 1 0 が1 以上のHDTイネーブルビットのステータスをチェックし、HDTモードがイネーブルである

50

かデセーブルであるかを確認する（ステップ 510）。HDTモードがイネーブルである（ステップ 515）場合、HDT制御ロジック 410 は HDTモードを開始する（ステップ 520）。HDTモードがデセーブルである（ステップ 515）場合、HDT制御ロジック 410 が HDTモードを開始することはない。

#### 【0033】

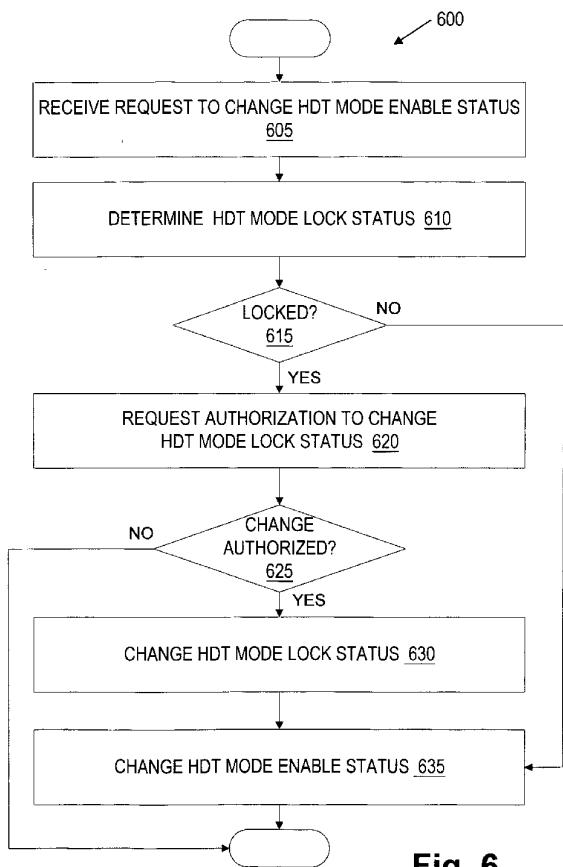

ここで図 6 に移ると、HDTモードのロックを含むHDTモードのイネーブルステータスを変更するための方法 600 が図示されている。HDTモードに入る要求を受信（ステップ 605）したことに応答して、HDT制御ロジック 410 が 1 以上のHDTイネーブルロックビットのステータスをチェックし、HDTロックモードがロック状態にあるかアンロック状態にあるかを判断する（ステップ 610）。HDTロックモードがアンロック状態にある（ステップ 615）場合、HDT制御ロジック 410 は HDTモードを開始する（ステップ 635）。HDTロックモードがロック状態にある（ステップ 615）場合、HDT制御ロジック 410 は HDTロックモードのステータスを変更するための承認を要求する（ステップ 620）。変更が承認された（ステップ 625）場合、HDT制御ロジック 410 が HDTモードのロックビットを変更してアンロック状態にする（ステップ 630）。変更が承認されなかった（ステップ 625）場合、HDT制御ロジック 410 によって HDTモードのロックビットが変更されることはない。

#### 【0034】

さまざまな実施形態において、HDTイネーブルステータスの変更には 1 以上のHDTイネーブルステータスピットを設定またはリセットすればよい。たとえば、HDTモードをデセーブルにすることができるが、SMM内では、HDT制御ロジック 410 へのあらかじめ定められた入力によって HDT制御ロジック 410 に HDTモードのステータスを変更してイネーブルにするように伝えることができる。図 4A の実施形態では、たとえば、一旦信号を受けると、HDT制御ロジック 410 は HDTイネーブルビットのステータスをデセーブルからイネーブルに変更する。

#### 【0035】

図 4B の実施形態に戻ると、たとえば、HDTモードのステータス変更の要求を受信したことに対応して、HDT制御ロジック 410 が 1 以上のHDTイネーブルロックビットのステータスをチェックし、HDTロックモードがイネーブルであるかデセーブルであるかを確認する。HDTロックモードがデセーブルである場合、HDT制御ロジック 410 は HDTモードのステータスを変更することができる。HDTロックモードがイネーブルである場合、HDT制御ロジック 410 が HDTモードのステータスを変更することはない。

#### 【0036】

HDTロックモードがロック状態にある（ステップ 615）場合に、HDTロックモードのステータスを変更するための承認を要求する（ステップ 620）のではなく方法 600 を終了させてよい点に注意されたい。方法 600 には、方法 600 で承認を要求する（ステップ 620）前に HDTロックモードのステータス変更の要求を受け取る（図示せず）ことも含み得る。

#### 【0037】

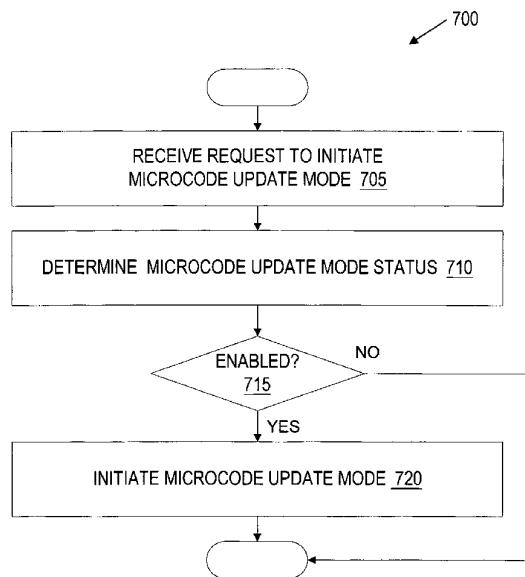

ここで図 7 に移ると、マイクロコードローダーを開始するための方法 700 が図示されている。マイクロコード更新モードの開始要求を受信（ステップ 705）したことに応答して、マイクロコード制御ロジック 455 が 1 以上のマイクロコードイネーブルビットのステータスをチェックし、マイクロコード更新モードがイネーブルであるかデセーブルであるかを確認する（ステップ 710）。マイクロコード更新モードがイネーブルである（ステップ 715）場合、マイクロコード制御ロジック 455 がマイクロコード更新モードを開始する（ステップ 720）。マイクロコード更新モードがデセーブルである（ステップ 715）場合、マイクロコード制御ロジック 455 がマイクロコード更新モードを開始することはない。

#### 【0038】

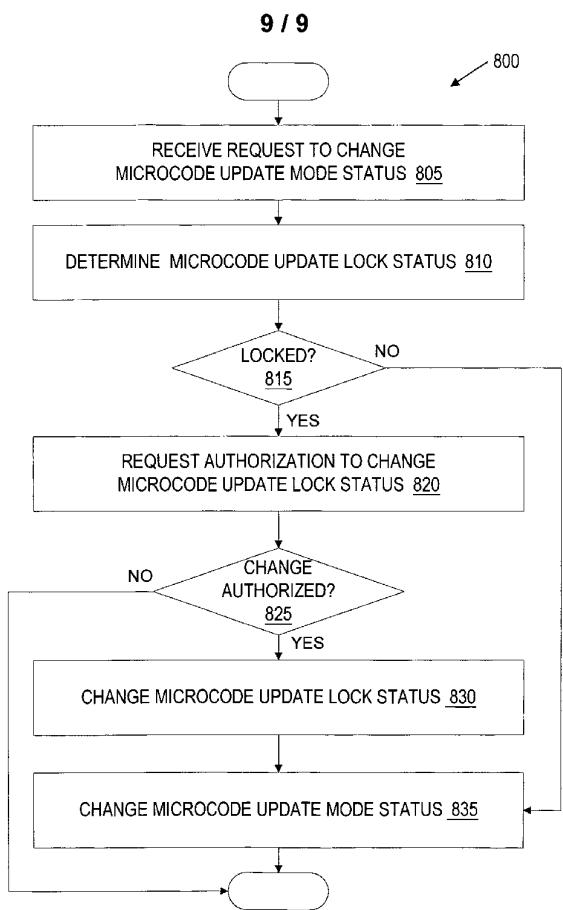

ここで図 8 に移ると、マイクロコードモードのロックを含むマイクロコード更新モードの

10

20

30

40

50

イネーブルステータスを変更するための方法 800 が図示されている。マイクロコードモードに入る要求を受信（ステップ 805）したことに応答して、マイクロコード制御ロジック 455 が 1 以上のマイクロコードイネーブルロックビットのステータスをチェックし、マイクロコードモードがロック状態であるかアンロック状態であるかを確認する（ステップ 810）。マイクロコードロックモードがアンロック状態にある（ステップ 815）場合、マイクロコード制御ロジック 455 がマイクロコードモードを開始する（ステップ 835）。マイクロコードロックモードがロック状態にある（ステップ 815）場合は、マイクロコード制御ロジック 455 がマイクロコードモードのロックステータスを変更するための承認を要求する（ステップ 820）。変更が承認された（ステップ 825）場合、マイクロコード制御ロジック 455 がマイクロコードモードのロックビットを変更してアンロック状態にする（ステップ 830）。変更が承認されなかった（ステップ 825）場合、マイクロコード制御ロジック 455 によってマイクロコードモードのロックビットが変更されることはない。

10

#### 【0039】

さまざまな実施形態において、マイクロコードイネーブルステータスの変更には 1 以上のマイクロコードイネーブルステータスピットを設定またはリセットすればよい。たとえば、マイクロコードモードをデセーブルにすることができるが、SMM 内では、マイクロコード制御ロジック 455 へのあらかじめ定められた入力によってマイクロコード制御ロジック 455 にマイクロコードモードのステータスを変更してイネーブルにするように伝えることができる。図 4C の実施形態では、たとえば、一旦信号を受けると、マイクロコード制御ロジック 455 は 1 以上のマイクロコードイネーブルビットのステータスをデセーブルからイネーブルに変更する。

20

#### 【0040】

マイクロコードモードのステータス変更の要求を受信したことに応答して、マイクロコード制御ロジック 455 が 1 以上のマイクロコードイネーブルロックビットのステータスをチェックし、マイクロコードロックモードがイネーブルであるかデセーブルであるかを判断することができる。マイクロコードロックモードがデセーブルである場合、マイクロコード制御ロジック 455 はマイクロコードモードのステータスを変更することができる。マイクロコードロックモードがイネーブルである場合、マイクロコード制御ロジック 455 がマイクロコードモードのステータスを変更することはない。

30

#### 【0041】

マイクロコード更新ロックステータスがロック状態にある（ステップ 815）場合に、マイクロコード更新ロックのステータスを変更するための承認を要求する（ステップ 820）のではなく方法 800 を終了させてもよい点に注意されたい。方法 800 には、方法 3500 で承認を要求する（ステップ 820）前にマイクロコード更新ロックステータス変更の要求を受け取る（図示せず）ことも含み得る。

#### 【0042】

本願開示の目的において、ROMについて説明した内容は、フラッシュメモリや他の実質的に不揮発性のメモリタイプにも適用されるものとする。以上、本願明細書に開示の本発明の方法をフローチャートの形で説明してきたが、さまざまな実施形態においてこれらのフローチャートのさまざまな要素を省略または異なる順序で実行してもよい点に注意されたい。また、本願に開示の本発明の方法では実施例のバリエーションを認めている点にも注意されたい。

40

#### 【0043】

上記に開示したような本発明のいくつかの態様は、ハードウェアまたはソフトウェアでインプリメントできるものである。したがって、結果として本願明細書に記載の詳細な説明の内容については、ハードウェアで実現できるプロセスに関するものもあれば、コンピュータシステムまたはコンピューティングデバイスのメモリ内のデータビットについての動作を記号的に表現した内容に關係のある、ソフトウェアで実現できるプロセスに関するものもある。これらの説明および表現は、当業者らが自分たちの行っている作業の内容を、

50

ハードウェアとソフトウェアの両方を使用している他の当業者に最も効率よく伝達するのに使用する手段である。両方のプロセスおよび動作には物理的な量を物理的に操作する必要がある。ソフトウェアでは、必ずしも必要というわけではないが、これらの量は格納や転送、結合、比較、あるいは操作が可能な電気信号や磁気信号、あるいは光信号の形態をとるのが普通である。主に一般利用の観点から、場合によってはこれらの信号をビットや値、エレメント、シンボル、文字、項、数などで参照すると都合がよいことが明らかになっている。

#### 【0044】

しかしながら、上記の用語および同様の用語はすべてしかるべき物理的な量に関連付けられるものであり、これらの量に付される都合のよいうラベルにすぎない点に留意すべきである。特に明記する場合または自明であろうと思われる場合を除き、本願開示全体を通して、これらの説明は、いくつかの電子デバイスのストレージ内で物理的な（電子的、磁気的または光学的）量として表されるデータを操作し、ストレージ内あるいは送信デバイスまたはディスプレイデバイスで同様に物理的な量として表される他のデータに変換する電子デバイスの行為およびプロセスについてのものである。このような説明を示す代表的な用語としては、「processing（処理する／処理／プロセッシング）」、「computing（コンピューティング）」、「calculating（計算する／計算）」、「determining（判断する／判定する／判断／判定）」、「displaying（表示する／表示）」などの用語があるが、これに限定されるものではない。

#### 【0045】

また、ソフトウェアで実現される本発明の態様は一般に、何らかの形のプログラム格納媒体でエンコードされるか、何らかのタイプの送信媒体を使って実現される点に注意されたい。プログラム格納媒体としては、磁気（フロッピーディスクまたはハードドライブなど）または光（コンパクトディスク読み出し専用メモリすなわち「CD ROM」など）があげられ、読み出し専用メモリであってもランダムアクセスメモリであってもよい。同様に、送信媒体はツイストペア線であってもよいし、同軸ケーブル、光ファイバまたは従来技術において周知の他の何らかの好適な送信媒体であってもよい。本発明は特定の実施例のいずれの態様にも限定されるものではない。

#### 【0046】

本発明は本願明細書の教示内容の利益を享受する当業者らに自明の上記とは異なるが等価な方法で改変および実施することのできるものであるため、上記にて開示した個々の実施形態は一例にすぎない。さらに、添付の請求の範囲に記載したものを受け、本願明細書に図示した構成または設計の詳細に対する限定を何ら意図するものではない。したがって、上記にて開示した個々の実施形態を変更または改変してもよく、そのような変形例はいずれも本発明の範囲に包含されるとみなせることは明白である。よって、本願明細書で求められる保護は添付の請求の範囲に記載のとおりである。

#### 【図面の簡単な説明】

#### 【0047】

【図1】従来技術のコンピュータシステムのブロック図を示す。

【図2】本発明の一態様による、セキュア実行ボックスを有するコンピュータシステムにおけるデータ・コマンドフローの実施形態のフローチャートを示す。

【図3】本発明の一態様による、SMM MSRを有するコンピュータシステムの実施形態のブロック図を示す。

【図4A】本発明のさまざまな態様による、ロックレジスタとロジックとを含むプロセッサの実施形態のブロック図を示す。

【図4B】本発明のさまざまな態様による、ロックレジスタとロジックとを含むプロセッサの実施形態のブロック図を示す。

【図4C】本発明のさまざまな態様による、ロックレジスタとロジックとを含むプロセッサの実施形態のブロック図を示す。

【図4D】本発明のさまざまな態様による、ロックレジスタとロジックとを含むプロセッサの実施形態のブロック図を示す。

10

20

30

40

50

サの実施形態のブロック図を示す。

【図5】本発明の一態様による、HDTモードを開始するための方法の実施形態のフロー チャートを示す。

【図6】本発明の一態様による、HDTイネーブルステータスを変更するための方法の実施形態のフロー チャートを示す。

【図7】本発明の一態様による、マイクロコードローダーを開始するための方法の実施形態のフロー チャートを示す。

【図8】本発明の一態様による、マイクロコードローダーのイネーブルステータスを変更するための方法の実施形態のフロー チャートを示す。

【図1】

【図2】

【図3】

【図4 A】

【図4 B】

【図4 C】

【図4 D】

【図5】

【図6】

【図7】

【図8】

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

21 November 2002 (21.11.2002)

PCT

(10) International Publication Number

WO 02/093336 A2

- (51) International Patent Classification': G06F 1/00 (51) Designated States (national): AL, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GR, GI, GM, IIR, IHU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PI, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZM, ZW.

- (21) International Application Number: PCT/US02/11935 (52) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SI, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IL, LU, MC, NL, PL, SE, TR), OAPI patent (BJ, BJ, CH, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

- (22) International Filing Date: 17 April 2002 (17.04.2002)

- (25) Filing Language: English (53) Published:

- (26) Publication Language: English — without international search report and to be republished upon receipt of that report

- (30) Priority Data:

09/852,942 10 May 2001 (10.05.2001) US

09/852,372 10 May 2001 (10.05.2001) US

09/853,226 11 May 2001 (11.05.2001) US

- (71) Applicant: ADVANCED MICRO DEVICES, INC. [US/US]; One AMD Place, P.O. Box 9453, Sunnyvale, CA 94088-3453 (US).

- (72) Inventor: STRONGIN, Geoffrey, S.; 7210 Montana Norte, Austin, TX 78731 (US).

- (74) Agent: DRAKE, Paul, S.; Advanced Micro Devices, Inc., 5204 East Ben White Boulevard, M/S 562, Austin, TX 78741 (US).

*[Continued on next page]*

(54) Title: MECHANISM FOR CLOSING BACK DOOR ACCESS MECHANISMS IN PERSONAL COMPUTER SYSTEMS

WO 02/093336 A2

(57) Abstract: Methods, devices, and systems for closing back door access mechanisms. A processor includes a first register configured to store one or more hardware-debug-test (HDT) enable bits, a first control logic coupled to receive a plurality of HDT input signals, and a second control logic coupled to the first register. The first control logic is coupled to access the first register. The second control logic is configured to store one or more default values in the first register in response to a reset of the processor. Another processor includes a first control logic configured to receive a plurality of microcode inputs, a first register coupled to the first control logic, and a second control logic coupled to the first register. The first register is configured to store one or more microcode loader enable bits. The second control logic is configured to store one or more default values in the first register in response to a reset of the processor.

---

**WO 02/093336 A2**

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

WO 02/093336

PCT/US02/11935

**MECHANISM FOR CLOSING BACK DOOR ACCESS

MECHANISMS IN PERSONAL COMPUTER SYSTEMS**

This Application is a continuation-in-part of co-pending U.S. Patent Application No. 09/852,372, 5 entitled, "Secure Execution Box and Method," filed on May 10, 2001, whose inventors are Dale E. Gulick and Geoffrey S. Strongin. This Application is also a continuation-in-part of co-pending U.S. Patent Application No. 09/852,942, entitled, "Computer System Architecture for Enhanced Security and Manageability," filed on May 10, 2001, whose inventors are Geoffrey S. Strongin and Dale E. Gulick.

**TECHNICAL FIELD**

10 This invention relates generally to computing systems, and, more particularly, to a method and apparatus for protecting personal computer systems from unauthorized back door accesses.

**BACKGROUND ART**

Fig. 1 illustrates an exemplary computer system 100. The computer system 100 includes a processor 102, a north bridge 104, memory 106, Advanced Graphics Port (AGP) memory 108, a Peripheral Component Interconnect (PCI) bus 110, a south bridge 112, a battery, an AT Attachment (ATA) interface 114 (more commonly known as an Integrated Drive Electronics (IDE) interface), a universal serial bus (USB) interface 116, a Low Pin Count (LPC) bus 118, an input/output controller chip (SuperI/O™) 120, and BIOS memory 122. It is noted that the north bridge 104 and the south bridge 112 may include only a single chip or a plurality of chips, leading to the collective term "chipset." It is also noted that other buses, devices, and/or subsystems may be included in the computer system 100 as desired, e.g. caches, modems, parallel or serial interfaces, SCSI interfaces, network interface cards, etc. ("SuperI/O" is a trademark of National Semiconductor Corporation of Santa Clara, Calif.)

The processor 102 is coupled to the north bridge 104. The north bridge 104 provides an interface between the processor 102, the memory 106, the AGP memory 108, and the PCI bus 110. The south bridge 112 provides an interface between the PCI bus 110 and the peripherals, devices, and subsystems coupled to the IDE interface 114, the USB interface 116, and the LPC bus 118. The battery 113 is shown coupled to the south bridge 112. The Super I/O™ chip 120 is coupled to the LPC bus 118.

The north bridge 104 provides communications access between and/or among the processor 102, memory 106, the AGP memory 108, devices coupled to the PCI bus 110, and devices and subsystems coupled to the south bridge 112. Typically, removable peripheral devices are inserted into PCI "slots" (not shown) that connect to the PCI bus 110 to couple to the computer system 100. Alternatively, devices located on a motherboard may be directly connected to the PCI bus 110.

The south bridge 112 provides an interface between the PCI bus 110 and various devices and subsystems, such as a modem, a printer, keyboard, mouse, etc., which are generally coupled to the computer system 100 through the LPC bus 118 (or its predecessors, such as an X-bus or an ISA bus). The south bridge 112 includes the logic used to interface the devices to the rest of computer system 100 through the IDE interface 114, the USB interface 116, and the LPC bus 118.

From a hardware point of view, an x86 operating environment provides little for protecting user privacy, providing security for corporate secrets and assets, or protecting the ownership rights of content providers. All of these goals, privacy, security, and ownership (collectively, PSO) are becoming critical in an

WO 02/093336

PCT/US02/11935

age of Internet-connected computers. The original personal computers were not designed in anticipation of PSO needs.

From a software point of view, the x86 operating environment is equally poor for PSO. The ease of direct access to the hardware through software or simply by opening the cover of the personal computer allows 5 an intruder or thief to compromise most security software and devices. The personal computer's exemplary ease of use only adds to the problems for PSO.

#### DISCLOSURE OF INVENTION

In accordance with the present invention, a processor is provided. The processor includes a first register configured to store one or more hardware-debug-test (HDT) enable bits, a first control logic coupled to 10 receive a plurality of HDT input signals, and a second control logic coupled to the first register. The first control logic is coupled to access the first register. The second control logic is configured to store one or more default values in the first register in response to a reset of the processor.

In accordance with the present invention, a method for determining an HDT mode enable status is provided. The method includes receiving a request to initiate the HDT mode, determining HDT mode enable 15 status, and initiating the HDT mode if the HDT mode enable status is set to enabled.

In accordance with the present invention, a method for modifying microcode is provided. The method includes receiving a request to modify microcode, determining microcode loader enable status, and modifying microcode if the microcode loader enable status is set to enabled.

In accordance with the present invention, a method of changing HDT mode status is provided. The 20 method includes receiving a request to change HDT mode status, determining HDT mode enable lock status, modifying HDT mode status if the HDT mode enable lock status is set to unlocked.

In accordance with the present invention, a method of changing microcode loader enable status is provided. The method includes receiving a request to change microcode loader enable status, determining 25 microcode loader enable lock status, and modifying microcode loader enable status if the microcode loader enable lock status is set to unlocked.

In accordance with the present invention, a method of operating a processor is provided. The method includes obtaining one or more default values selected from the group consisting of reading the one or more default values from one or more non-volatile memory cells and receiving the one or more default values as a strapped value through a pull-up or pull-down resistor. The method includes writing the one or more default 30 values as one or more various entries in one or more registers in response to a reset of the processor. The one or more various entries are selected from the group consisting of one or more HDT enable bits, one or more HDT enable lock bits, one or more microcode loader enable bits, and one or more microcode loader enable lock bits.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The invention may be understood by reference to the following description taken in conjunction with 35 the accompanying drawings, in which like reference numerals identify similar elements, and in which:

Fig. 1 illustrates a block diagram of a prior art computer system;

Fig. 2 illustrates a flowchart of an embodiment of data and command flow in a computer system having a secure execution box, according to one aspect of the present invention;

Fig. 3 illustrates a block diagram of an embodiment of a computer system having SMM MSRs, 40 according to one aspect of the present invention;

WO 02/093336

PCT/US02/11935

Figs. 4A-4D illustrate block diagrams of embodiments of processors including lock registers and logic, according to various aspects of the present invention;

Fig. 5 illustrates a flowchart of an embodiment of a method for initiating HDT mode, according to one aspect of the present invention;

5 Fig. 6 illustrates a flowchart of an embodiment of a method for changing the HDT enable status, according to one aspect of the present invention;

Fig. 7 illustrates a flowchart of an embodiment of a method for initiating the microcode loader, according to one aspect of the present invention; and

10 Fig. 8 illustrates a flowchart of an embodiment of a method for changing the microcode loader enable status, according to one aspect of the present invention.

While the invention is susceptible to various modifications and alternative forms, specific embodiments thereof have been shown by way of example in the drawings and are herein described in detail. It should be understood, however, that the description herein of specific embodiments is not intended to limit the invention to the particular forms disclosed, but on the contrary, the intention is to cover all modifications, equivalents, and alternatives falling within the scope of the invention as defined by the appended claims.

#### MODE(S) FOR CARRYING OUT THE INVENTION

Illustrative embodiments of the invention are described below. In the interest of clarity, not all features of an actual implementation are described in this specification. It will, of course, be appreciated that in the development of any such actual embodiment, numerous implementation-specific decisions must be made to achieve the developers' specific goals, such as compliance with system-related and business-related constraints, which will vary from one implementation to another. Moreover, it will be appreciated that such a development effort might be complex and time-consuming, but would nevertheless be a routine undertaking for those of ordinary skill in the art having the benefit of this disclosure. The use of a letter in association with a reference number is intended to show alternative embodiments or examples of the item to which the reference number is connected.

System Management Mode (SMM) is a mode of operation in the computer system that was implemented to conserve power. The SMM was created for the fourth generation x86 processors. As newer x86 generation processors have appeared, the SMM has become relatively transparent to the operating system. That is, computer systems enter and leave the SMM with little or no impact on the operating system.

30 Fig. 2 illustrates a block diagram of an embodiment of a flowchart showing data and command flow in a computer system having a secure execution box 260, according to one aspect of the present invention. User input and output (I/O) data and/or commands 205 are provided to and received from one or more applications 210. The applications 210 exchange data and commands with cryptography service providers 215 within the computer system, such as the computer system 100 or any other computer system. The cryptography service providers 215 may use API (Application Programming Interface) calls 220 to interact with drivers 225 that provide access to hardware 230.

According to one aspect of the present invention, the drivers 225 and the hardware 230 are part of a secure execution box configured to operate in a secure execution mode (SEM) 260. Trusted privacy, security and ownership (PSO) operations, also referred to simply as security operations, may take place while the computer system is in SEM 260. Software calls propagated from the user I/O 205 and/or the applications 210

WO 02/093336

PCT/US02/11935

may be placed into the secure execution box in SMM 260. The software calls have access to the secure execution box in SEM 260 to various security hardware resources.

Fig. 3 illustrates a block diagram of an embodiment of a computer system 300 with SMM MSRs, according to various aspects of the present invention. Fig. 3 includes a processor 305, a north bridge 310, memory 306, and a south bridge 330. The processor includes one or more SMM MSRs (machine specific registers) 307. The north bridge 310 includes a memory controller 315. The north bridge 310 is coupled between the processor 305 and the south bridge 330, to the processor 305 through a local bus 308 and to the south bridge 330 through the PCI bus 110. The north bridge 310 is coupled to receive the SMI ACT# signal from the processor 305.

In the embodiment of Fig. 3, the computer system 300 signals that the processor 305 is in SMM using standard processor signals (e.g. SMI ACT# to the north bridge 310) and/or bus cycles on the local bus 308 and PCI bus 110.

In various embodiments of the present invention, the security of SMM is assumed. It is noted that one or more so-called "backdoors" may exist that could be exploited to compromise the security of SMM. The issues contemplated include misuse of the hardware debug test (HDT) mode of the processor 305 as well as the ability of the processor 305 to load and replace microcode. Illustrated in Figs. 4A-D are various embodiments 305A, 305B, 305C, 305D of the processor 305, each of which includes various security protections against one or more backdoor attacks.

In Fig. 4A, the processor 305A includes HDT control logic 410A, HDT reset logic 420A, and one or more registers, including an HDT enable register 415 and non-volatile random access memory (NVRAM) 430. As shown, the HDT control logic 410A is coupled to receive a plurality of input signals through a plurality of HDT pins 405. The HDT control logic 410A is further coupled to the HDT enable register 415. The HDT reset logic 420A is coupled to receive a RESET signal over a line 425 and to access (i.e. read and write) the HDT enable register 415 and the NVRAM 430.

In Fig. 4B, the processor 305B of Fig. 4B includes HDT control logic 410B, HDT reset logic 420B, and two registers, including the HDT enable register 415 and an HDT enable lock register 435. As shown, the HDT control logic 410B is coupled to receive a plurality of input signals through the plurality of HDT pins 405. The HDT control logic 410B is further coupled to the HDT enable register 415 and the HDT enable lock register 435. The HDT reset logic 420B is coupled to receive the RESET signal over the line 425 and a signal, such as over a line 440, through a pull-up (or pull-down) resistor 445.

In Fig. 4C, the processor 305C includes microcode control logic 455, microcode loader enable reset logic 465, and one or more registers, including a microcode loader enable register 460. As shown, the microcode control logic 455 is coupled to receive a plurality of input signals through a plurality of microcode input pins 450. The microcode control logic 455 is further coupled to the microcode loader enable register 460. The microcode loader enable reset logic 465 is coupled to receive the RESET signal and to access the microcode loader enable register 460.

In Fig. 4D, the processor 305D includes HDT control logic 410 integrated with the microcode control logic 455, the HDT reset logic 420, and the MLE reset logic 465 to form control/reset logic 475. The HDT enable register 415 and the microcode loader enable register 460 are integrated into a multibit lock register 480.

A plurality of inputs 470 are shown to the control/reset logic 475. The plurality of inputs 470 may include the

WO 02/093336

PCT/US02/11935

HDT inputs 405, the microcode inputs 450, and/or the reset signaling means. Other embodiments (not shown) integrate only the HDT control logic 410 and the microcode control logic 455, or just the HDT reset logic 420 and the MLE reset logic 465.

According to various embodiments of the present invention, the registers 415, 435, and 460, as well as the NVRAM 430 include storage space for one or more bits. In one embodiment, each register is configured to store a single bit. It is noted that the enable registers 415 and 460 may also be integrated into a single lock register, and the HDT enable lock register 435 may be used as a microcode enable lock register. It is contemplated that the registers 415, 435, 460, and/or 480 could be included in the SMM MSRs 307.

In various embodiments, the HDT enable register 415 is configured to store one or more HDT enable bits signifying whether HDT mode is enabled or disabled. The HDT reset logic 420 is configured to set the one or more HDT enable bits to a default state upon a reset of the processor 305.

Multiple embodiments for controlling the HDT modes are contemplated, such as those illustrated in Figs. 4A and 4B. In one embodiment, the HDT mode is enabled as the default on non-production processors 305 used for engineering and testing. The HDT mode may be disabled as the default in standard production processors 305. In another embodiment, illustrated in Fig. 4A, the default state may be stored in and read from the NVRAM 430. In this embodiment, the default state may be changeable, but in the illustrated embodiment, the default state is set to disabled. In still another embodiment, illustrated in Fig. 4B, the default state is set using a strapping option. The default value is provided to the HDT reset logic 420B through the pull-up (or pull-down) resistor 445.

Multiple embodiments for controlling the microcode loader modes are also contemplated, such as those illustrated in Figs. 4C and 4D. In one embodiment, not illustrated, the microcode update mode is enabled as the default on non-production processors 305 used for engineering and testing. The microcode update mode may be disabled as the default in standard production processors 305. In another embodiment, similar to that illustrated in Fig. 4A, the default state may be stored in and read from the NVRAM 430. In this embodiment, the default state may be changeable, but in the illustrated embodiment the default state is set to disabled. In still another embodiment, illustrated in Fig. 4B, the default state is using a strapping option. The default value is provided to the MLE reset logic 465 through the pull-up (or pull-down) resistor 445.

Turning now to Fig. 5, a method 500 for initiating the HDT mode is shown. In response to receiving a request to enter the HDT mode (step 505), the HDT control logic 410 checks the status of the one or more HDT enable bits to see if the HDT mode is enabled or disabled (step 510). If the HDT mode is enabled (step 515), then the HDT control logic 410 initiates the HDT mode (step 520). If the HDT mode is disabled (step 515), then the HDT control logic 410 will not initiate the HDT mode.

Turning now to Fig. 6, a method 600 for changing the HDT mode enable status, which includes an HDT mode lock, is shown. In response to receiving a request to enter the HDT mode (step 605), the HDT control logic 410 checks the status of the one or more HDT enable lock bits to determine if the HDT lock mode is locked or unlocked (step 610). If the HDT lock mode is unlocked (step 615), then the HDT control logic 410 initiates HDT mode (step 635). If the HDT lock mode is locked (step 615), then the HDT control logic 410 requests authorization to change the HDT lock mode status (step 620). If the change is authorized (step 625), then the HDT control logic 410 changes the HDT mode lock bit to unlocked (step 630). If the change is not authorized (step 625), then the HDT control logic 410 does not change the HDT mode lock bit.

WO 02/093336

PCT/US02/11935

In various embodiments, the HDT enable status may be changed by setting or resetting the one or more HDT enable status bits. For example, the HDT mode may be disabled, but inside SMM, a predetermined input to the HDT control logic 410 may signal the HDT control logic 410 to change the HDT mode status to enabled. In the embodiment of Fig. 4A, for example, once signaled, the HDT control logic 410 would change the status of the HDT enable bit from disabled to enabled.

Referring back to the embodiment of Fig. 4B, for example, in response to receiving a request to change the HDT mode status, the HDT control logic 410 checks the status of the one or more HDT enable lock bits to see if the HDT lock mode is enabled or disabled. If the HDT lock mode is disabled, then the HDT control logic 410 may change the HDT mode status. If the HDT lock mode is enabled, then the HDT control logic 410 will not change the HDT mode status.

It is noted that the method 600 may alternatively terminate if the HDT lock mode is locked (step 615), instead of requesting authorization to change the HDT lock mode status (step 620). The method 600 may also include receiving a request to change the HDT lock mode status (not shown) prior to the method 600 requesting authorization (step 620).

Turning now to Fig. 7, a method 700 for initiating the microcode loader is shown. In response to receiving a request to initiate the microcode update mode (step 705), the microcode control logic 455 checks the status of the one or more microcode enable bits to see if microcode update mode is enabled or disabled (step 710). If the microcode update mode is enabled (step 715), then the microcode control logic 455 initiates the microcode update mode (step 720). If the microcode update mode is disabled (step 715), then the microcode control logic 455 will not initiate the microcode update mode.

Turning now to Fig. 8, a method 800 for changing the microcode update mode enable status, which includes a microcode mode lock, is shown. In response to receiving a request to enter the microcode mode (step 805), the microcode control logic 455 checks the status of the one or more microcode enable lock bits to see if the microcode mode is locked or unlocked (step 810). If the microcode lock mode is unlocked (step 815), then the microcode control logic 455 initiates the microcode mode (step 835). If the microcode lock mode is locked (step 815), then the microcode control logic 455 requests authorization to change the microcode mode lock status (step 820). If the change is authorized (step 825), then the microcode control logic 455 changes the microcode mode lock bit to unlocked (step 830). If the change is not authorized (step 825), then the microcode control logic 455 does not change the microcode mode lock bit.

In various embodiments, the microcode enable status may be changed by setting or resetting the one or more microcode enable status bits. For example, the microcode mode may be disabled, but inside SMM, a predetermined input to the microcode control logic 455 may signal the microcode control logic 455 to change the microcode mode status to enabled. In the embodiment of Fig. 4C, for example, once signaled, the microcode control logic 455 will change the status of the one or more microcode enable bits from disabled to enabled.

In response to receiving a request to change the microcode mode status, the microcode control logic 455 may check the status of the one or more microcode enable lock bits to determine if the microcode lock mode is enabled or disabled. If the microcode lock mode is disabled, then the microcode control logic 455 may change the microcode mode status. If the microcode lock mode is enabled, then the microcode control logic 455 will not change the microcode mode status.

WO 02/093336

PCT/US02/11935

It is noted that the method 800 may alternatively terminate if the microcode update lock status is locked (step 815), instead of requesting authorization to change the microcode update lock status (step 820). The method 800 may also include receiving a request to change the microcode update lock status (not shown) prior to the method 3500 requesting authorization (step 820).

5 For the purposes of this disclosure, references to ROM are to be construed as also applying to flash memory and other substantially non-volatile memory types. Note that while the methods of the present invention disclosed herein have been illustrated as flowcharts, various elements of the flowcharts may be omitted or performed in different order in various embodiments. Note also that the methods of the present invention disclosed herein admit to variations in implementation.

10 Some aspects of the invention as disclosed above may be implemented in hardware or software. Thus, some portions of the detailed descriptions herein are consequently presented in terms of a hardware implemented process and some portions of the detailed descriptions herein are consequently presented in terms of a software-implemented process involving symbolic representations of operations on data bits within a memory of a computing system or computing device. These descriptions and representations are the means

15 used by those in the art to convey most effectively the substance of their work to others skilled in the art using both hardware and software. The process and operation of both require physical manipulations of physical quantities. In software, usually, though not necessarily, these quantities take the form of electrical, magnetic, or optical signals capable of being stored, transferred, combined, compared, and otherwise manipulated. It has proven convenient at times, principally for reasons of common usage, to refer to these signals as bits, values,

20 elements, symbols, characters, terms, numbers, or the like.

It should be borne in mind, however, that all of these and similar terms are to be associated with the appropriate physical quantities and are merely convenient labels applied to these quantities. Unless specifically stated or otherwise as may be apparent, throughout the present disclosure, these descriptions refer to the action and processes of an electronic device, that manipulates and transforms data represented as physical (electronic, magnetic, or optical) quantities within some electronic device's storage into other data similarly represented as physical quantities within the storage, or in transmission display devices. Exemplary of the terms denoting such a description are, without limitation, the terms "processing," "computing," "calculating," "determining," "displaying," and the like.

Note also that the software-implemented aspects of the invention are typically encoded on some form

30 of program storage medium or implemented over some type of transmission medium. The program storage medium may be magnetic (e.g., a floppy disk or a hard drive) or optical (e.g., a compact disk read only memory, or "CD ROM"), and may be read only or random access. Similarly, the transmission medium may be twisted wire pairs, coaxial cable, optical fiber, or some other suitable transmission medium known to the art. The invention is not limited by these aspects of any given implementation.

35 The particular embodiments disclosed above are illustrative only, as the invention may be modified and practiced in different but equivalent manners apparent to those skilled in the art having the benefit of the teachings herein. Furthermore, no limitations are intended to the details of construction or design herein shown, other than as described in the claims below. It is therefore evident that the particular embodiments disclosed above may be altered or modified and all such variations are considered within the scope of the invention.

40 Accordingly, the protection sought herein is as set forth in the claims below.

WO 02/093336

PCT/US02/11935

**CLAIMS**

1. A processor, comprising:

- a first register configured to store one or more hardware-debug-test (HDT) enable bits;

- a first control logic coupled to receive a plurality of HDT input signals, wherein the first control logic is coupled to access the first register; and

- a second control logic coupled to the first register, wherein the second control logic is configured to store one or more default values in the first register in response to a reset of the processor.

2. The processor of claim 1, wherein the first control logic is further configured to receive a request to enter an HDT mode, wherein the first control logic is further configured to read selected entries of the one or more HDT enable bits stored in the first register in response to the request to enter HDT mode, and wherein the first control logic is further configured to grant or deny the request to enter HDT mode based on the selected entries of the one or more HDT enable bits.

- 15 3. The processor of claim 1, further comprising:

- one or more non-volatile memory cells configured to store the one or more default values for the one or more HDT enable bits, wherein the second control logic is further coupled to read the one or more default values for the one or more HDT enable bits from the one or more non-volatile memory cells and to write the one or more default values for the one or more HDT enable bits into the first register in response to the reset of the processor.

4. The processor of claim 1, wherein the second control logic is further coupled to receive a signal indicative of the one or more default values for the one or more HDT enable bits and to write the one or more default values for the one or more HDT enable bits into the first register in response to the reset of the processor.

- 20 5. The processor of claim 1, further comprising:

- a third register configured to store one or more microcode loader enable bits;

- a third control logic coupled to receive a plurality of microcode inputs, wherein the third control logic is coupled to access the third register; and

- a fourth control logic coupled to the third register, wherein the fourth control logic is configured to store one or more default values in the third register in response to a reset of the processor.

- 25 6. The processor of claim 5, wherein the third control logic is further configured to receive a request to modify microcode, wherein the third control logic is further configured to read selected entries of the one or more microcode loader enable bits stored in the third register in response to the request to modify microcode, and wherein the third control logic is further configured to grant or deny the request to modify microcode based on the selected entries of the one or more microcode loader enable bits.

- 40 7. The processor of claim 1, further comprising:

WO 02/093336

PCT/US02/11935

a second register coupled to the first control logic, wherein the second register is configured to store one or more HDT enable lock bits.

8. The processor of claim 7, wherein the first control logic is further configured to receive a request to modify HDT mode status, wherein the first control logic is further configured to read selected entries in the one or more HDT enable lock bits stored in the second register in response to the request to modify HDT mode status, and wherein the first control logic is further configured to grant or deny the request to modify HDT mode based on the selected entries in the one or more HDT enable lock bits.

10 9. A processor, comprising:

a first control logic coupled to receive a plurality of microcode inputs;

a first register coupled to the first control logic, wherein the first register is configured to store one or more microcode loader enable bits; and

a second control logic coupled to the first register, wherein the second control logic is configured to store one or 15 more default values in the first register in response to a reset of the processor.

10. The processor of claim 9, wherein the first control logic is further configured to receive a request to modify microcode, wherein the first control logic is further configured to read selected entries of the one or more microcode loader enable bits stored in the first register in response to the request to modify microcode, and wherein the first control logic is further configured to grant or deny the request to modify microcode based on the selected entries of the one or more microcode loader enable bits.

11. The processor of claim 9, further comprising:

one or more non-volatile memory cells configured to store the one or more default values for the one or more 25 microcode loader enable bits, wherein the second control logic is further coupled to read the one or more default values for the one or more microcode loader enable bits from the one or more non-volatile memory cells and to write the one or more default values for the one or more microcode loader enable bits into the microcode loader register in response to the reset of the processor.

30 12. The processor of claim 9, wherein the second control logic is further coupled to receive a signal indicative of the one or more default values for the one or more microcode loader enable bits and to write the one or more default values for the one or more microcode loader enable bits into the first register in response to the reset of the processor.

35 13. The processor of claim 9, further comprising:

a second register coupled to the first control logic, wherein the second register is configured to store one or more microcode loader enable lock bits.

40 14. The processor of claim 13, wherein the first control logic is further configured to receive a request to modify microcode loader lock status, wherein the first control logic is further configured to read

WO 02/093336

PCT/US02/11935

selected entries in the one or more microcode loader enable lock bits stored in the second register in response to the request to modify microcode loader lock status, and wherein the first control logic is further configured to grant or deny the request to modify microcode loader lock status based on the selected entries in the one or more microcode loader enable lock bits.

5

15. A method for determining an HDT mode enable status, the method comprising:

receiving a request to initiate the HDT mode;

determining HDT mode enable status;

initiating the HDT mode if the HDT mode enable status is set to enabled.

10

16. The method of claim 15, wherein determining HDT mode enable status comprises reading one or more entries corresponding to one or more HDT enable bits from a register.

15

17. A method for modifying microcode, the method comprising:

receiving a request to modify microcode;

determining microcode loader enable status;

modifying microcode if the microcode loader enable status is set to enabled.

20

18. The method of claim 17, wherein determining microcode loader enable status comprises reading one or more entries corresponding to one or more microcode loader enable bits from a register.

25

19. A method of changing HDT mode status, the method comprising:

receiving a request to change HDT mode status;

determining HDT mode enable lock status; and

25 modifying HDT mode status if the HDT mode enable lock status is set to unlocked.

20. The method of claim 19, wherein determining HDT mode enable lock status comprises reading one or more entries corresponding to one or more HDT enable lock bits from a register.

30

21. The method of claim 19, wherein modifying HDT mode status comprises writing one or more entries corresponding to one or more HDT enable bits to a register.

22. A method of changing microcode loader enable status, the method comprising:

receiving a request to change microcode loader enable status;

35 23. The method of claim 22, wherein determining microcode loader enable lock status comprises reading one or more entries corresponding to one or more microcode loader enable lock bits from a register.

40

WO 02/093336

PCT/US02/11935

24. The method of claim 22, wherein modifying microcode loader enable status comprises writing one or more entries corresponding to one or more microcode loader enable bits to a register.

25. A method of operating a processor, the method comprising:

- 5 obtaining one or more default values, wherein obtaining the one or more default values is selected from the group consisting of:

- reading the one or more default values from one or more non-volatile memory cells, and

receiving the one or more default values as a strapped value through a pull-up or pull-down resistor; and

- 10 writing the one or more default values as one or more various entries in one or more registers in response to a reset of the processor, wherein the one or more various entries are selected from the group consisting of:

one or more HDT enable bits,

one or more HDT enable lock bits,

15 one or more microcode loader enable bits, and

one or more microcode loader enable lock bits.

**Fig. 1**

**(Prior Art)**

**2 / 9****Fig. 2**

WO 02/093336

PCT/US02/11935

**3 / 9**

**4 / 9****Fig. 4A****Fig. 4B**

**5 / 9****Fig. 4C****Fig. 4D**

**6 / 9****Fig. 5**

WO 02/093336

PCT/US02/11935

7 / 9

Fig. 6

WO 02/093336

PCT/US02/11935

**8 / 9****Fig. 7**

WO 02/093336

PCT/US02/11935

**Fig. 8**

## 【国際公開パンフレット（コレクトバージョン）】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

21 November 2002 (21.11.2002)

PCT

(10) International Publication Number

WO 2002/093336 A3(51) International Patent Classification<sup>7</sup>: G06F 1/00 (81) Designated States (national): AE, AG, AL, AM, AT, AU,

AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU,

CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH,

GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC,

LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW,

MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SE, SG,

SI, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VN,

YU, ZA, ZM, ZW.

(21) International Application Number:

PCT/US2002/011935

(22) International Filing Date: 17 April 2002 (17.04.2002)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

09/852,942 10 May 2001 (10.05.2001) US

09/852,372 10 May 2001 (10.05.2001) US

09/853,226 11 May 2001 (11.05.2001) US

(81) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

(71) Applicant: ADVANCED MICRO DEVICES, INC.

[US/US]; One AMD Place, P.O. Box 9453, Sunnyvale, CA

94088-3453 (US).(84) Designated States (regional): Published:

— with international search report(72) Inventor: STRONGIN, Geoffrey, S., 7210 Montana

Norte, Austin, TX 78731 (US).(88) Date of publication of the international search report:

12 February 2004(74) Agent: DRAKE, Paul, S.; Advanced Micro Devices, Inc.,

5204 East Ben White Boulevard, M/S 562, Austin, TX

78741 (US).

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: PROCESSOR WITH PROTECTED TEST AND DEBUG MODE

(57) **Abstract:** Methods, devices, and systems for closing back door access mechanisms. A processor includes a first register configured to store one or more hardware-debug-test (HDT) enable bits, a first control logic coupled to receive a plurality of HDT input signals, and a second control logic coupled to the first register. The first control logic is coupled to access the first register. The second control logic is configured to store one or more default values in the first register in response to a reset of the processor. Another processor includes a first control logic coupled to receive a plurality of microcode inputs, a first register coupled to the first control logic, and a second control logic coupled to the first register. The first register is configured to store one or more microcode loader enable bits. The second control logic is configured to store one or more default values in the first register in response to a reset of the processor.

WO 2002/093336 A3

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                          | International Application No.<br>PCT/US 02/11935                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| A. CLASSIFICATION OF SUBJECT MATTER<br>IPC 7 G06F1/00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      |

| B. FIELDS SEARCHED<br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 G06F G11C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      |

| Electronic data base consulted during the International search (name of data base and, where practical, search terms used)<br>EPO-Internal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                      |