OFICINA ESPAÑOLA DE

PATENTES Y MARCAS

ESPAÑA

⑪ Número de publicación: **2 883 349**

⑮ Int. Cl.:

**H03K 19/003** (2006.01)

**H03K 19/0185** (2006.01)

⑫

TRADUCCIÓN DE PATENTE EUROPEA

T3

⑥ Fecha de presentación y número de la solicitud internacional: **25.01.2017 PCT/US2017/014949**

⑦ Fecha y número de publicación internacional: **05.10.2017 WO17172002**

⑨ Fecha de presentación y número de la solicitud europea: **25.01.2017 E 17704366 (8)**

⑩ Fecha y número de publicación de la concesión europea: **28.07.2021 EP 3437193**

---

④ Título: **Circuitos de entrada/salida aislados de descarga electrostática y método para proteger dichos circuitos**

⑩ Prioridad:

**31.03.2016 US 201615088035**

④ Fecha de publicación y mención en BOPI de la traducción de la patente:

**07.12.2021**

⑦ Titular/es:

**QUALCOMM INCORPORATED (100.0%)

Attn: International IP Administration, 5775

Morehouse Drive

San Diego, CA 92121-1714, US**

⑦ Inventor/es:

**WORLEY, EUGENE ROBERT;

JALILIZENALI, REZA;

DUNDIGAL, SREEKER;

CHEN, WEN-YI;

CHILLARA, KRISHNA CHAITANYA y

KANG, TAEHYUN**

⑦ Agente/Representante:

**ISERN JARA, Jorge**

**ES 2 883 349 T3**

---

Aviso: En el plazo de nueve meses a contar desde la fecha de publicación en el Boletín Europeo de Patentes, de la mención de concesión de la patente europea, cualquier persona podrá oponerse ante la Oficina Europea de Patentes a la patente concedida. La oposición deberá formularse por escrito y estar motivada; sólo se considerará como formulada una vez que se haya realizado el pago de la tasa de oposición (art. 99.1 del Convenio sobre Concesión de Patentes Europeas).

## DESCRIPCIÓN

Circuitos de entrada/salida aislados de descarga electrostática y método para proteger dichos circuitos

## 5 Campo técnico

La presente divulgación se refiere en general a circuitos integrados (CIs). Más específicamente, la presente divulgación se refiere a circuitos de entrada/salida (E/S) aislados de descarga electrostática (ESD).

## 10 Antecedentes

La protección contra descargas electrostáticas (ESD) en dispositivos electrónicos se realiza en general mediante circuitos de sujeción. Estos circuitos de sujeción se pueden utilizar para fijar o "sujetar" las variaciones máximas positivas o negativas de una señal de voltaje a un valor definido mediante la derivación de la corriente ESD. Los 15 elementos de temporización de los circuitos de sujeción transitorios se pueden implementar mediante el uso de resistencias y condensadores (RC). Dichos circuitos de sujeción se denominan sujeciones RC. Las sujeciones RC pueden usar el modelo de cuerpo humano (HBM) y el modelo de dispositivo cargado (CDM) para determinar sus 20 valores de constante de tiempo RC. Además, las sujeciones RC tienen una serie de ventajas sobre otros tipos de sujeciones, que incluye la portabilidad del proceso, la facilidad de simulación con modelos de transistores de efecto de campo semiconductivo de óxido metálico estándar (MOSFET), tiempos de respuesta más rápidos y voltajes de compensación conductivos más bajos.

Sin embargo, a medida que la tecnología de proceso continúa disminuyendo, el voltaje de falla de ESD también se 25 reduce. Por ejemplo, los voltajes de falla que utilizan la prueba CDM del modelo de dispositivo cargado para estrés ESD pueden resultar en voltajes de falla tan bajos como 3 voltios para la mayoría de los procesos avanzados. Un método común para la protección ESD es usar un diodo en combinación con una sujeción RC. Este enfoque muestra un voltaje de compensación de conducción relativamente bajo de aproximadamente 1.6 voltios, el cual es la suma de los voltajes de compensación del diodo y la sujeción RC.

30 Desafortunadamente, el voltaje de compensación total se reduce muy lentamente ya que aproximadamente 1.1 voltios del voltaje de compensación total está controlado por la física del diodo, el cual no se aumenta, a la vez que el voltaje de compensación de la sujeción RC aumenta muy lentamente ya que depende del voltaje de umbral del MOSFET. Cuando un MOSFET protegido falla a 3 voltios, esto da como resultado una sobrecarga de voltaje muy 35 pequeña para caídas de voltaje (IR) de solo 1.4 voltios. Si la corriente máxima del CDM es de 5 amperios (A), entonces la resistencia total máxima para este caso es de 0.28 ohmios ( $\Omega$ ). Por lo tanto, la suma de una resistencia de diodo "encendido", una resistencia de bus, y una resistencia de sujeción RC debe sumar menos de 0.28 ohmios. Los expertos en la técnica reconocerán que lograr la suma de resistencia indicada es muy desafiante.

40 El documento EP 0482336 A1 describe un dispositivo de interfaz de línea que se puede conmutar entre modos de operación de un solo extremo y diferencial. El documento US 6624992 B1 describe sistemas y métodos para proteger circuitos y sistemas eléctricos y electrónicos de descargas electrostáticas. El documento US 2013/335099 A1 describe circuitos integrados para controladores lógicos en modo de corriente para mejorar la protección contra descargas electrostáticas.

## 45 Resumen

De acuerdo con un aspecto de la invención, en la reivindicación 1 se expone un circuito controlador diferencial de convertidor de paralelo a serie/convertidor de serie a paralelo (SERDES) protegido contra descarga electrostática (ESD).

50 De acuerdo con otro aspecto de la invención, en la reivindicación 8 se expone un método para proteger un circuito de entrada/salida diferencial (E/S) convertidor de paralelo a serie/convertidor de serie a paralelo (SERDES).

55 Esto ha resumido, de manera bastante amplia, las características y ventajas técnicas de la presente divulgación con el fin de que la descripción detallada que sigue pueda entenderse mejor. Las características y ventajas adicionales de la divulgación se describirán a continuación. Los expertos en la técnica deben apreciar que esta divulgación puede utilizarse fácilmente como una base para modificar o diseñar otras estructuras para llevar a cabo los mismos propósitos de la presente divulgación. Los expertos en la técnica también deberían darse cuenta de que dichas construcciones equivalentes no se apartan de las enseñanzas de la invención como se define en las reivindicaciones adjuntas. Las características novedosas, las cuales se cree que son características de la invención, tanto en cuanto a su organización y método de operación, junto con otros objetos y ventajas, se entenderán mejor a partir de la siguiente descripción cuando se consideren en relación con las figuras adjuntas. Debe entenderse expresamente, sin embargo, que cada una de las figuras se proporciona con el propósito de ilustración y descripción únicamente y no pretende ser una definición de los límites de la presente invención.

## Breve descripción de los dibujos

Para una comprensión más completa de la presente divulgación, se hace ahora referencia a la siguiente descripción tomada junto con los dibujos adjuntos.

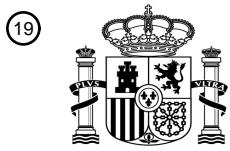

- 5 La Figura 1 es un diagrama esquemático de un sistema de circuito de entrada/salida (E/S) protegido contra ESD de acuerdo con un aspecto de la presente divulgación.

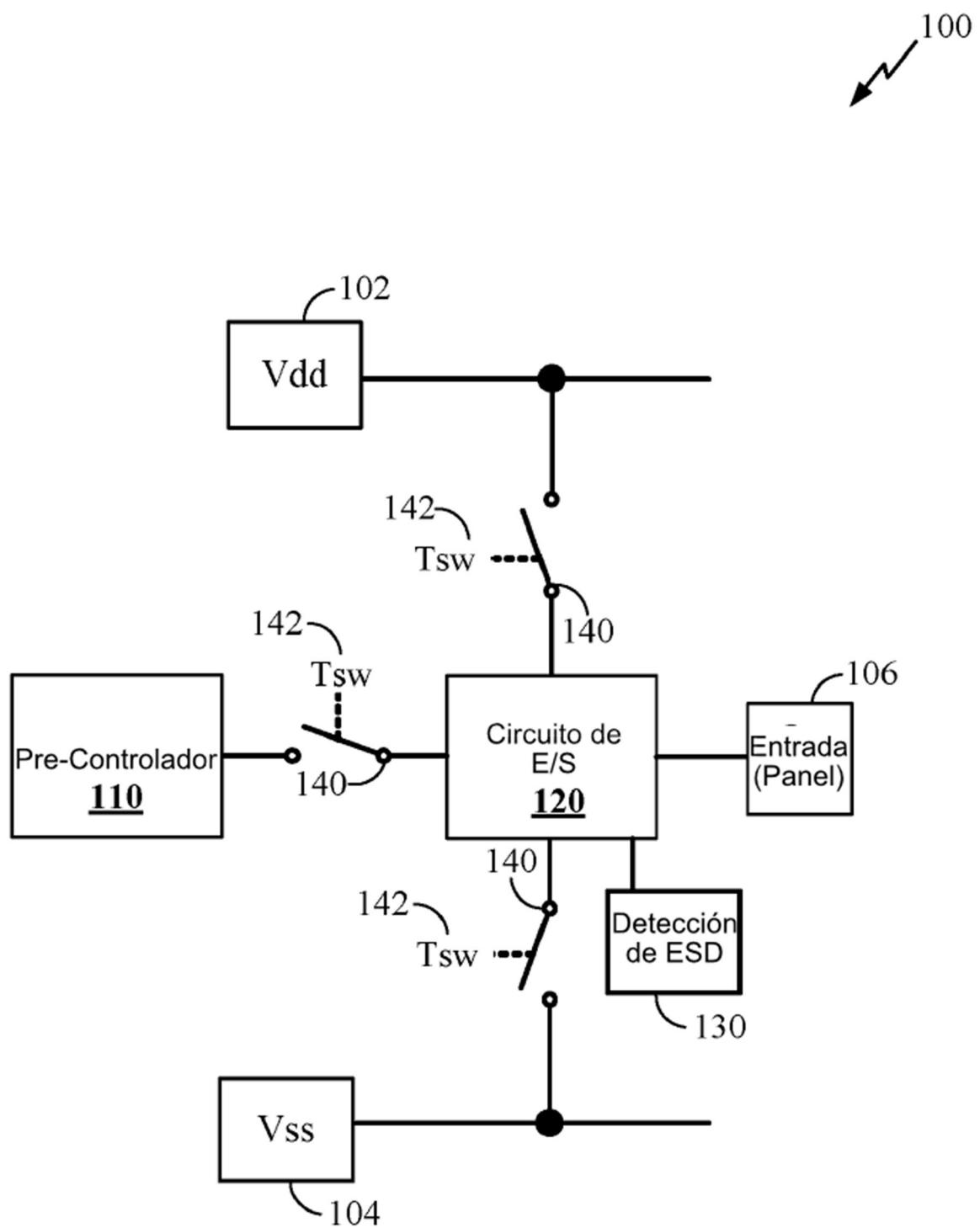

La Figura 2 ilustra un circuito de E/S de bajo voltaje (LV) protegido contra ESD de acuerdo con aspectos de la 10 presente divulgación no cubiertos por la invención.

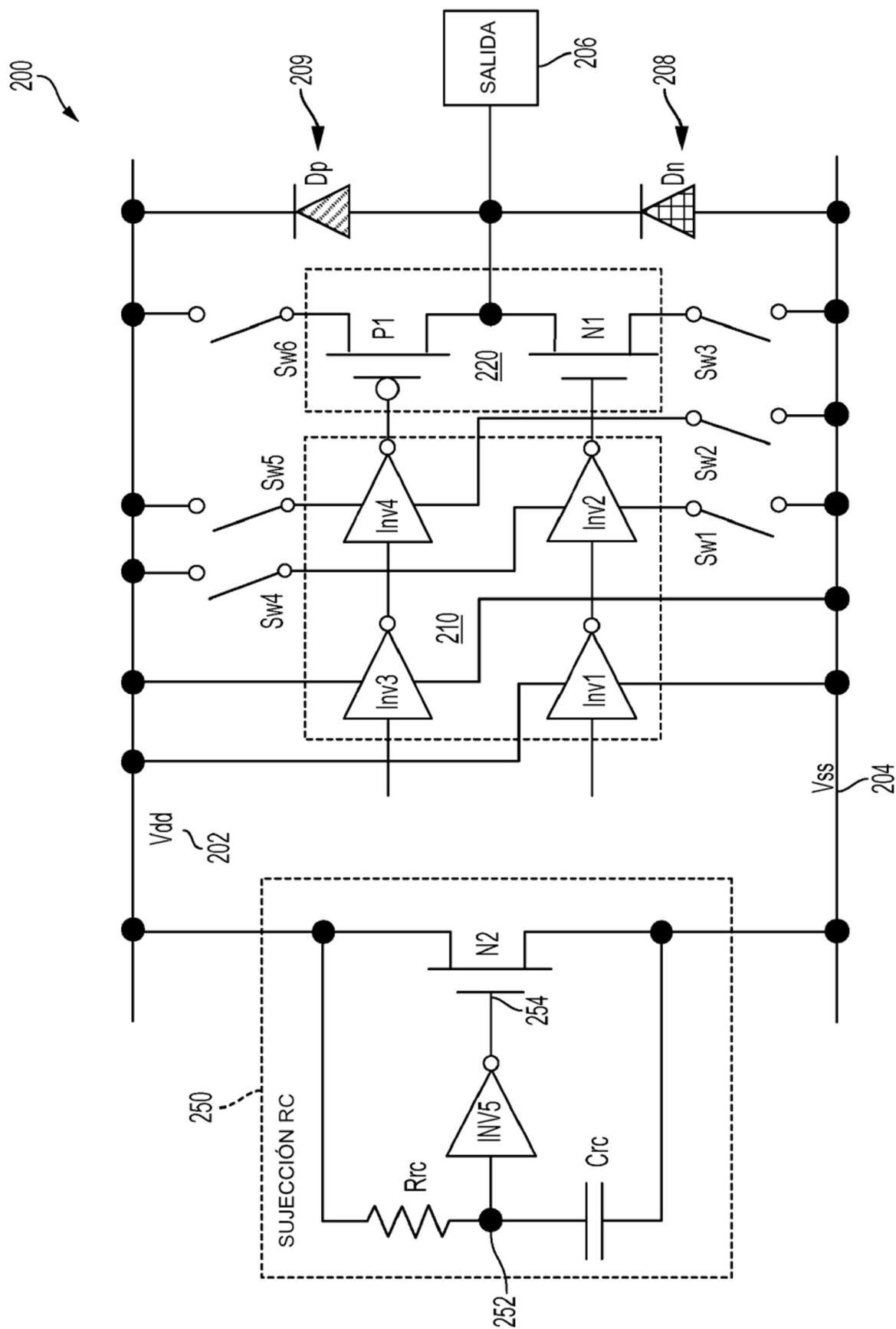

- 10 La Figura 3 es un diagrama de disposición de un circuito detector de descarga electrostática (ESD) transitorio de acuerdo con un aspecto de la presente divulgación.

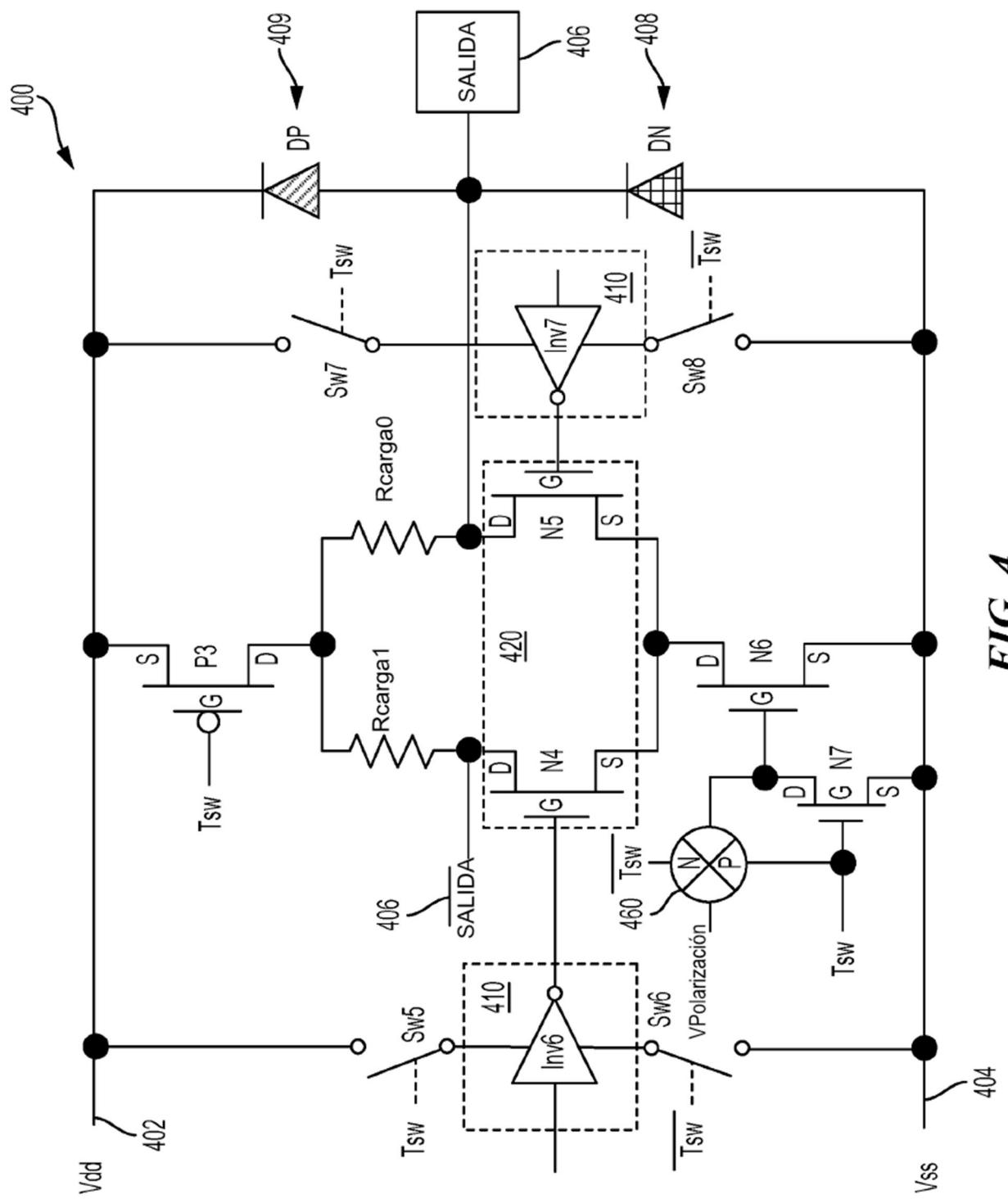

- 15 La Figura 4 es un diagrama esquemático de un circuito controlador diferencial de convertidor de paralelo a serie/convertidor de serie a paralelo (SERDES) protegido contra descarga electrostática (ESD), de acuerdo con un aspecto de la presente divulgación.

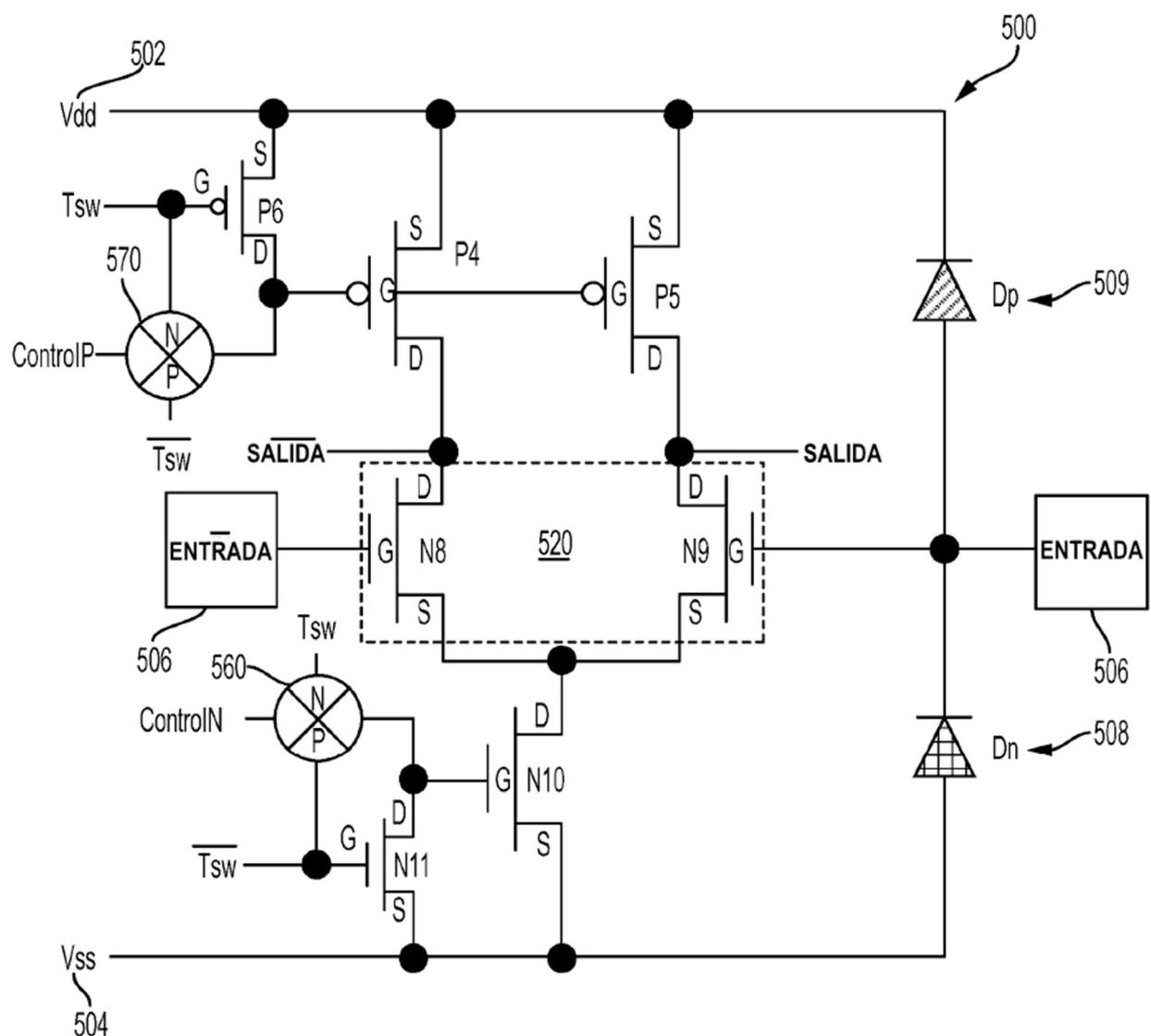

- 20 La Figura 5 es un diagrama esquemático de un circuito receptor diferencial de convertidor de paralelo a serie/convertidor de serie a paralelo (SERDES) protegido contra descarga electrostática (ESD), de acuerdo con un aspecto de la presente divulgación.

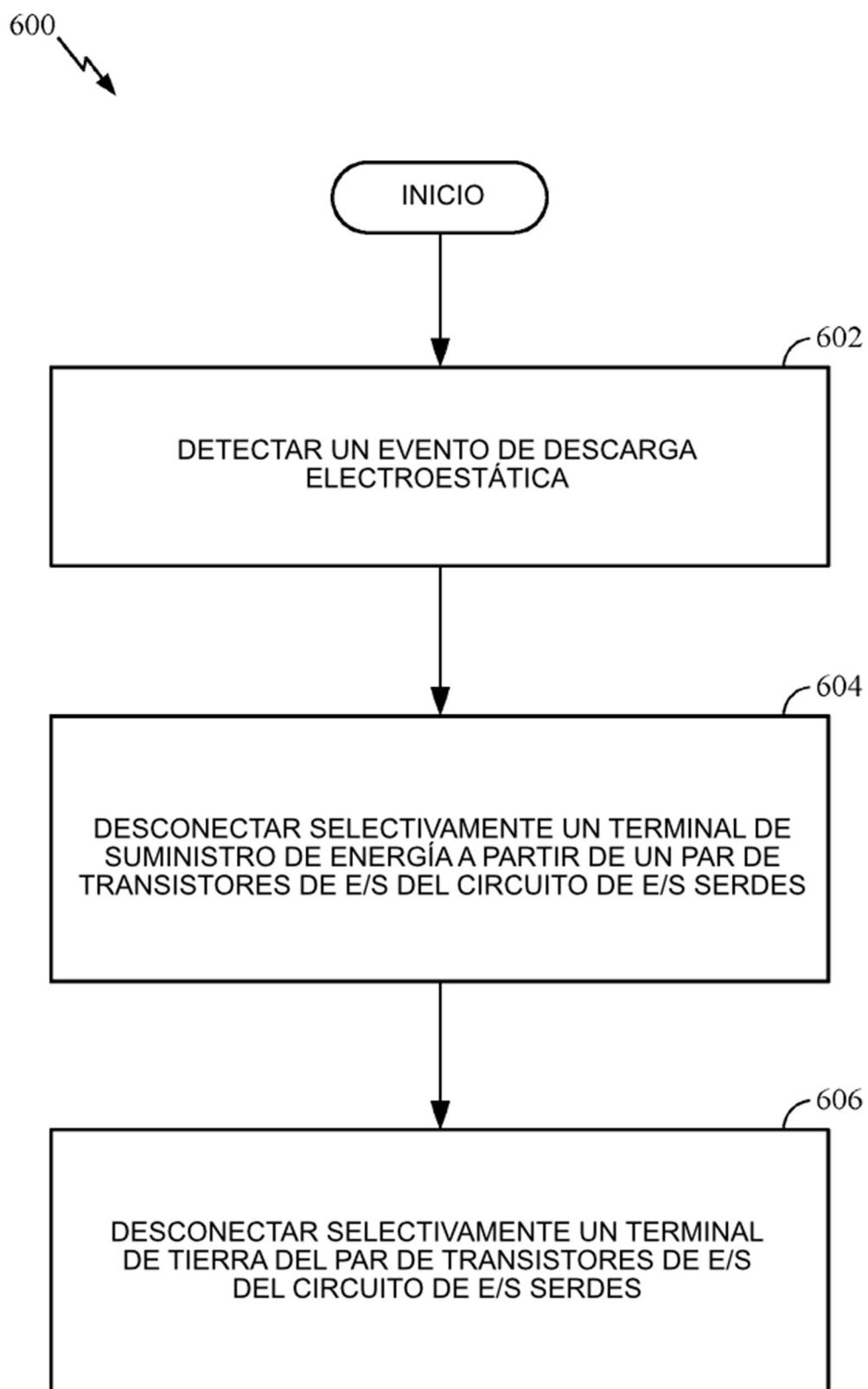

25 La Figura 6 es un diagrama de flujo del proceso que ilustra un método para proteger un circuito de entrada/salida diferencial (E/S) de convertidor de paralelo a serie/convertidor de serie a paralelo (SERDES) de acuerdo con un aspecto de la presente divulgación.

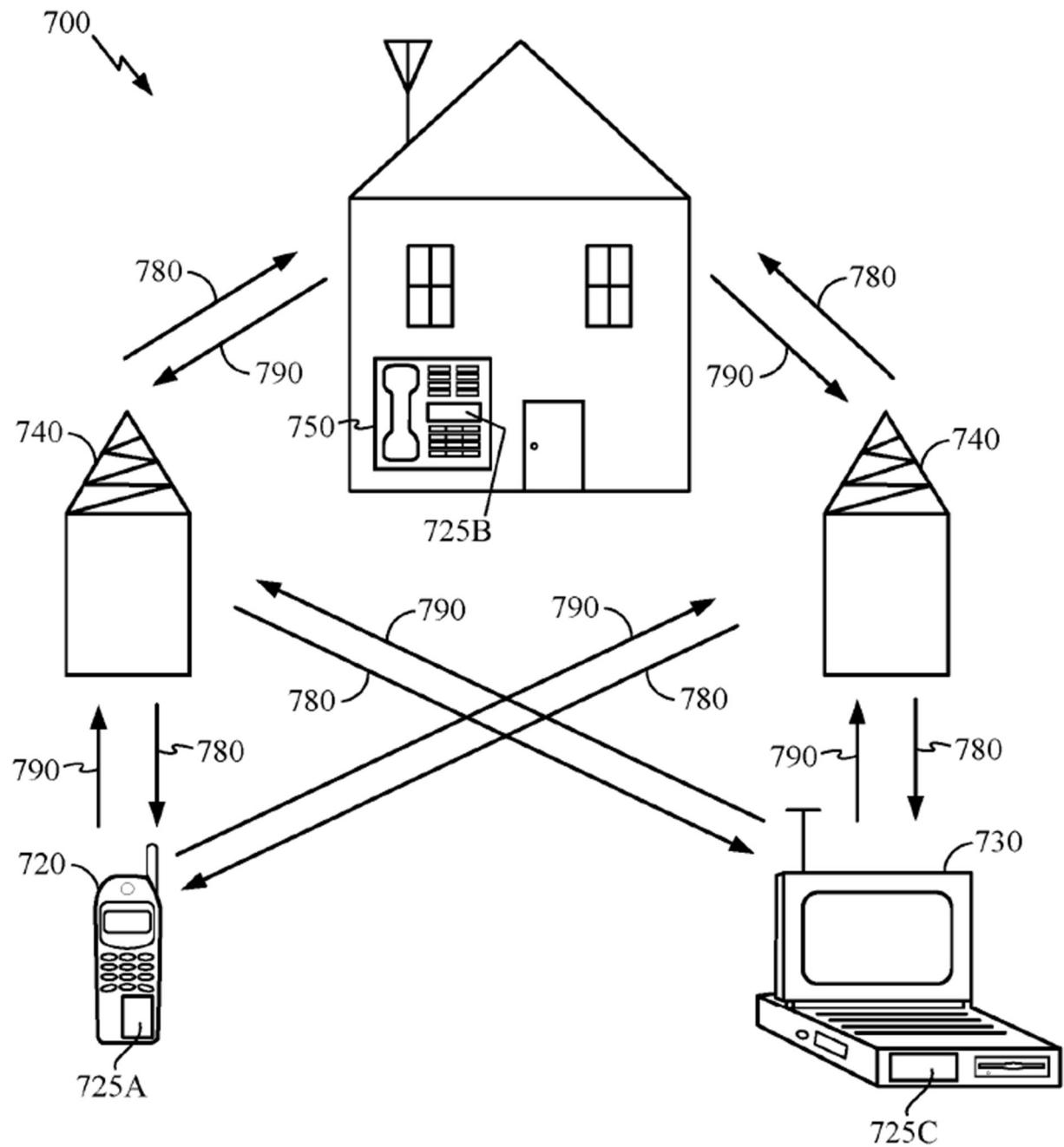

- 30 La Figura 7 es un diagrama de bloques que muestra un ejemplo de sistema de comunicación inalámbrica en el cual se puede emplear ventajosamente una configuración de la divulgación.

- 35 La Figura 8 es un diagrama de bloques que ilustra una estación de trabajo de diseño utilizada para la disposición de circuitos, y, diseño lógico de un componente semiconductivo de acuerdo con una configuración.

## Descripción detallada

- 35 La descripción detallada que se expone a continuación, en relación con los dibujos adjuntos, pretende ser una descripción de diversas configuraciones y no pretende representar las únicas configuraciones en las cuales se pueden practicar los conceptos descritos en el presente documento. La descripción detallada incluye detalles específicos con el fin de proporcionar una comprensión profunda de los diversos conceptos. Sin embargo, será evidente para los expertos en la técnica que estos conceptos se pueden practicar sin estos detalles específicos. En 40 algunos casos, las estructuras y componentes bien conocidos se muestran en forma de diagrama de bloques con el fin de impedir oscurecer dichos conceptos. Como se describe en el presente documento, el uso del término "y/o" pretende representar un "O inclusivo", y el uso del término "o" pretende representar un "O exclusivo".

- 45 La protección contra descargas electrostáticas (ESD) en dispositivos electrónicos se puede realizar utilizando circuitos de sujeción. Estos circuitos de sujeción se utilizan para derivar la corriente ESD fijando o "sujetando" las variaciones máximas positivas o negativas de una señal de voltaje a un valor definido. Las resistencias y los condensadores (RC) se utilizan en general para implementar los elementos de temporización de los circuitos de sujeción transitorios. Dichos circuitos de sujeción se denominan sujeciones RC. Las sujeciones RC pueden usar el modelo de cuerpo humano (HBM) o el modelo de dispositivo cargado (CDM) para determinar sus valores de constante de tiempo RC. Estas sujeciones RC también tienen una serie de ventajas sobre otros tipos de sujeciones, 50 que incluyen la portabilidad del proceso, la facilidad de simulación con modelos de transistores de efecto de campo semiconductivo de óxido metálico estándar (MOSFET), tiempos de respuesta más rápidos, y voltajes de compensación de conducción más bajos.

- 55 Los transistores de núcleo de bajo voltaje (LV) se usan comúnmente en circuitos de entrada/salida (E/S) para proporcionar tanto potencia como velocidades de datos elevadas. Sin embargo, a medida que la tecnología de proceso continúa reduciendo la escala de los transistores de núcleo de bajo voltaje, el voltaje de falla de descarga electrostática también se reduce. Por ejemplo, los voltajes de falla que utilizan la prueba CDM del modelo de dispositivo cargado para estrés por descarga electrostática pueden resultar en voltajes de falla tan bajos como 3 voltios para la mayoría de los procesos avanzados. Un método común para la protección ESD de los circuitos de E/S 60 es usar un diodo en combinación con una sujeción RC. Este enfoque muestra un voltaje de compensación de conducción relativamente bajo de aproximadamente 1.6 voltios, el cual es la suma de los voltajes de compensación del diodo y la sujeción RC.

- 65 Desafortunadamente, el voltaje de compensación total se reduce muy lentamente ya que aproximadamente 1.1 voltios del voltaje de compensación total está controlado por la física del diodo, la cual no se aumenta, a la vez que el voltaje de compensación de la sujeción RC aumenta muy lentamente ya que depende del voltaje de umbral del

MOSFET. Cuando un MOSFET protegido falla a 3 voltios, una sobrecarga de voltaje muy pequeña da como resultado caídas de voltaje (IR) de solo 1.4 voltios. Si la corriente máxima del CDM es de 5 amperios (A), entonces la resistencia total máxima para este caso es de 0.28 ohmios ( $\Omega$ ). Por lo tanto, la suma de una resistencia de diodo "encendido", una resistencia de bus, y una resistencia de sujeción RC debe sumar menos de 0.28 ohmios. Los expertos en la técnica reconocerán que lograr la suma de resistencia indicada es muy desafiante.

En un aspecto de la divulgación, se describe un circuito de entrada/salida (E/S) convertidor de paralelo a serie/convertidor de serie a paralelo (SERDES) protegido contra ESD en el cual los voltajes de falla se aumentan para superar la sobrecarga de voltaje de compensación reducida indicada. Es decir, debido a que no existe una forma obvia de reducir el voltaje de compensación, el cual está limitado por las propiedades físicas indicadas, una solución, de acuerdo con los aspectos de la presente divulgación, se basa en aumentar el voltaje de falla de los circuitos de E/S SERDES. Por ejemplo, si el voltaje de falla de E/S se puede aumentar a 5 voltios, entonces la resistencia máxima permitida asociada con la caída de IR de descarga pasa de 0.28 ohmios a 0.68 ohmios de acuerdo con el ejemplo proporcionado anteriormente.

La Figura 1 es un diagrama esquemático de un sistema 100 de circuito de entrada/salida (E/S) protegido contra ESD de acuerdo con un aspecto de la presente divulgación. De manera representativa, un circuito 120 controlador de entrada/salida (E/S) se acopla selectivamente a un circuito 110 pre-controlador para activar un panel 106 de entrada. En este aspecto de la presente divulgación, los commutadores 140 están dispuestos entre el circuito 120 controlador de E/S, un terminal 102 (Vdd) de suministro de energía, un terminal 104 (Vss) de tierra, y el circuito 110 de pre-controlador del sistema 100 de circuito de E/S protegido contra ESD. En operación, un circuito 130 detector de ESD (por ejemplo, un detector transitorio) monitoriza la operación normal del sistema 100 de circuito de E/S protegido contra ESD. El circuito 130 detector de ESD está configurado para detectar un evento de descarga electrostática e impedir que el evento de descarga electrostática dañe el circuito 120 controlador de E/S. En un aspecto de la presente divulgación, el circuito 130 detector de ESD puede configurarse como se muestra en la Figura 3.

En este aspecto de la presente divulgación, durante un evento de descarga electrostática detectado, el circuito 130 detector de ESD abre los commutadores 140 usando señales 142 de control de commutador (Tsw) para hacer flotar los nodos que se acoplan al circuito 120 controlador de E/S para el resto del sistema 100 de circuito de E/S protegido contra ESD. Las señales 142 de control del commutador pueden ser un '0' lógico durante un evento de descarga electrostática detectado y un 1 lógico durante la operación normal. Por tanto, durante la operación normal, los commutadores 140 se cierran, lo que permite que el circuito 120 controlador de E/S funcione normalmente. Aunque esta disposición supone que el '1' lógico para las señales 142 de control del commutador cierra los commutadores 140 y el '0' lógico abre los commutadores 140, también son posibles otras configuraciones de las señales 142 de control del commutador. Un circuito detector de ESD, por ejemplo, como se muestra en la Figura 3, puede afirmar una señal de control de commutador Tsw a un estado lógico '1' en respuesta a un evento de descarga electrostática detectado, y mantener la señal de control de commutador Tsw en un estado '0' lógico durante la operación normal.

Este aspecto de la presente divulgación aísla el circuito 120 controlador de E/S durante un evento de descarga electrostática utilizando los commutadores 140. Esto permite que los transistores (por ejemplo, transistores de efecto de campo semiconductivo de óxido metálico (MOSFET)) del circuito 120 controlador de E/S "floten", eliminando así una ruta de descarga del circuito de E/S hasta el límite del voltaje de falla del cuerpo de drenaje de los MOSFETs del circuito de E/S. El voltaje de falla del cuerpo de drenaje de un MOSFET se puede aumentar usando ataduras de cuerpo débiles, pero el uso de ataduras de cuerpo débiles debe atenuarse con la susceptibilidad de enganche. Los aspectos de la presente divulgación previenen el voltaje de falla del cuerpo de drenaje de los transistores del circuito controlador de E/S al proporcionar detección de descarga electrostática para circuitos de E/S de bajo voltaje (LV), por ejemplo, como se muestra en la Figura 2, así como el convertidor de paralelo a serie/convertidor de serie a paralelo (SERDES) y los circuitos controladores de entrada y salida, por ejemplo, como se muestra en las Figuras 4 y 5.

La Figura 2 ilustra un sistema 200 de circuito de E/S de bajo voltaje (LV) protegido contra ESD de acuerdo con aspectos de la presente divulgación no cubiertos por la presente invención. De manera representativa, el sistema 200 de circuito de E/S protegido incluye un circuito 220 controlador de E/S acoplado a un circuito 210 pre-controlador. El circuito 220 controlador de E/S incluye un transistor de efecto de campo de tipo p de bajo voltaje (PFET) y controladores FET de tipo n (NFET) que son controlados por inversores pre-controlador (Inv) del circuito 210 pre-controlador. En esta disposición, el controlador N1 de transistor de tipo n y el controlador P1 de transistor de tipo p del circuito 220 controlador de E/S se utilizan para controlar un panel 206 de salida (Salida).

En este aspecto de la presente divulgación, los commutadores se utilizan para hacer flotar el circuito 220 controlador de E/S y una porción del circuito 210 pre-controlador para proporcionar protección ESD para el sistema 200 de circuito de E/S protegido. En esta disposición, se puede usar un commutador de encendido Sw6 para encender/apagar una conexión del controlador P1 de transistor de tipo p a un terminal 202 de suministro de energía (Vdd) del sistema 200 de circuito de E/S protegido. De manera similar, un commutador de tierra Sw3 hace o interrumpe una conexión del controlador N1 de transistor de tipo n a un terminal 204 de tierra (Vss) del sistema 200 de circuito de E/S protegido. Además, un inversor de pre-controlador Inv2 del circuito 210 pre-controlador incluye un

5 comutador de encendido Sw4 y un comutador de tierra Sw1 para proporcionar protección ESD. De forma similar, un inversor de pre-controlador Inv4 del circuito 210 de pre-controlador incluye un comutador de encendido Sw5 y un comutador de tierra Sw2. En esta disposición, un inversor de pre-controlador Inv3, acoplado al inversor de pre-controlador Inv4, y un inversor de pre-controlador Inv1, acoplado al pre-controlador Inv2 del circuito 210 pre-controlador, están directamente acoplados entre el terminal 204 de tierra y el terminal 202 de suministro de energía.

10 Como se ilustra adicionalmente en la Figura 2, una sujeción 250 de capacitancia de resistencia (RC) está acoplada al terminal 202 de suministro de energía y al terminal 204 de tierra del sistema 200 de circuito de E/S protegido. En esta disposición, la sujeción 250 RC está habilitada por un detector de transitorios ESD, que incluye una resistencia Rrc, un condensador Crc, y un inversor Inv5. Durante un evento de descarga electrostática, los transistores de controlador (por ejemplo, el controlador N1 de transistor de tipo n y el controlador P1 de transistor de tipo p) "flotan" con respecto a los rieles de encendido (por ejemplo, 202, 204) y las entradas (por ejemplo, 210). El voltaje de falla del controlador N1 de transistor de tipo n ahora está determinado por la unión del cuerpo de drenaje del controlador N1 de transistor de tipo n. En un aspecto de la presente divulgación, una atadura de cuerpo más débil puede aumentar el voltaje de falla del controlador N1 de transistor de tipo n mediante el uso de un anillo de N pozos.

15 Durante la operación normal, la resistencia Rrc mantiene un nodo 252 interno cerca del nivel de voltaje del terminal 202 de suministro de energía (por ejemplo, Vdd). El nodo 252 interno activa las acciones del inversor Inv5. Esto también mantiene un nodo 254 de puerta de un transistor N2 de derivación al nivel de voltaje del terminal 204 de tierra, el cual mantiene el transistor N2 apagado (por ejemplo, no conductor). A medida que pasa el tiempo, la resistencia Rrc eleva el voltaje a través (también conocido como "elevación") de un condensador Crc hasta el nivel de voltaje del terminal 202 de suministro de energía. En esta configuración, el voltaje de activación del suministro de energía es mucho mayor que la constante de tiempo RC de Rrc y Crc. Como resultado, N2 permanece apagado durante la fase de encendido. La elevación del condensador Crc al nivel de voltaje Vdd del terminal 202 de suministro de energía cambia el voltaje del nodo 252 interno a un voltaje alto, lo cual enciende el inversor Inv5. Una vez que se enciende el inversor Inv5, el voltaje del terminal 204 de tierra se alimenta al nodo 254 de puerta del transistor N2 de derivación. Esto apaga el transistor N2 de derivación.

20 30 Antes de un evento de descarga electrostática, la sujeción RC 250 se desconecta de modo que la carga en el condensador Crc es cero. Durante el evento de descarga electrostática, aparecen transitorios de descarga electrostática en el terminal 202 de suministro de energía, lo que hace que el voltaje entre el terminal 202 de suministro de energía y el terminal 204 de tierra aumente rápidamente (por ejemplo, en unos pocos nanosegundos o menos). El condensador Crc mantiene el voltaje del nodo 252 interno a cero voltios, de manera momentánea. El inversor Inv5 emite un voltaje en el nodo 254 de puerta al nivel de voltaje del terminal 202 de suministro de energía, lo cual enciende el transistor N2 de derivación.

25 35 40 El transistor N2 de derivación está diseñado para absorber el flujo de corriente durante la descarga electrostática, lo cual mantiene un rango de voltaje reducido entre el terminal 202 de suministro de energía y el terminal 204 de tierra. El transistor N2 de derivación también se conoce como transistor de derivación de corriente de descarga electrostática debido a que desvía la corriente causada por una descarga electrostática que fluye a partir del terminal 202 de suministro de energía al terminal 204 de tierra. El transistor N2 de derivación opera en conjunto con la ruta de derivación proporcionada por un diodo Dp 209 y un diodo Dn 208 acoplados entre el terminal 202 de suministro de energía, el terminal 204 de tierra y los transistores de controlador (por ejemplo, el controlador N1 de transistor de tipo n y el controlador P1 de transistor de tipo p). En una implementación, la resistencia Rrc puede ser una resistencia de polisilicio. En otra implementación, la resistencia Rrc puede ser un transistor (tal como un MOSFET) polarizado como una resistencia.

45 50 55 Dependiendo de la tolerancia a fallas del controlador de transistor protegido (por ejemplo, el controlador N1 de transistor de tipo n y el controlador P1 de transistor de tipo p) y la condición de tensión, no todos los comutadores (por ejemplo, Sw1, Sw2, Sw5 y Sw6) tienen que implementarse. Por ejemplo, el peor caso de descarga para el modelo de dispositivo cargado (CDM) es típicamente cuando la corriente fluye hacia el panel 206 de salida, a través del diodo Dp 209 y a través del transistor N2 de derivación de la sujeción RC 250. Esta polaridad de descarga tensiona el controlador N1 de transistor de tipo n más que el controlador P1 de transistor de tipo p. Además, los transistores de canal P, tal como el controlador P1 de transistor de tipo p, tienen una tolerancia de voltaje más alta que los transistores de canal N, tal como el controlador N1 de transistor de tipo n. Por lo tanto, el comutador de tierra Sw3, el comutador de tierra Sw1, y el comutador de encendido Sw4 pueden ser suficientes, a la vez que agregar el comutador de tierra Sw2, el comutador de encendido Sw5, y el comutador de encendido Sw6 puede no mejorar la tolerancia de voltaje general en el panel 206 de salida.

60 65 En un aspecto de la presente divulgación, los comutadores de encendido y de tierra (Sw1, Sw2, Sw3, Sw4, Sw5 y Sw6) se implementan usando transistores de efecto de campo semiconductivo de óxido metálico (MOSFETs). El tamaño de los transistores de comutación puede determinar un aumento en la cantidad de resistencia del controlador de salida del sistema 200 de circuito de E/S protegido. Sin embargo, el tamaño de los transistores de comutación puede aumentar ya que los comutadores de transistores grandes no afectan negativamente el rendimiento del sistema 200 de circuito de E/S protegido, que no sea el aumento del área de disposición.

La Figura 3 es un diagrama de disposición de un circuito 300 detector de descarga electrostática transitorio (ESD) de acuerdo con un aspecto de la presente divulgación. De manera representativa, el circuito 300 detector de ESD transitorio incluye una resistencia R y un condensador C. Estos elementos RC, junto con un inversor Inv6, controlan un estado lógico '1' en una señal de control de conmutador Tsw cuando se produce un rápido aumento de voltaje en un terminal 302 de suministro (Vdd). El rápido aumento en el terminal 302 de suministro se identifica como un evento de descarga electrostática (ESD), en lugar de una condición de encendido mucho más lenta durante la operación normal.

El circuito 300 detector de ESD transitorio también incluye un conmutador N3 de transistor de tipo n, acoplado a un inversor Inv7, y un conmutador P2 de transistor de tipo p, acoplado a un inversor Inv6, los cuales se "apagan" durante un evento de descarga electrostática, pero están en un estado "encendido" durante la operación normal para controlar las señales de control del conmutador (Tsw y Tsw). Alternativamente, la señal transitoria puede retirarse de la salida del inversor Inv5 de la sujeción RC 250 de la Figura 2. Debe tenerse en cuenta que los conmutadores N3 de transistor de tipo n y un conmutador P2 de transistor de tipo p pueden ser transistores de efecto de campo semiconductivo de óxido metálico (MOSFETs) de bajo voltaje o de alto voltaje. En este aspecto de la presente divulgación, el circuito 300 detector de ESD transitorio define la señal de control del conmutador Tsw a un estado lógico '1' en respuesta a un evento de descarga electrostática detectado, y mantiene la señal de control del conmutador Tsw en un estado lógico '0' durante la operación normal para proporcionar protección ESD para los circuitos de controlador de entrada y salida de convertidor de paralelo a serie/convertidor de serie a paralelo (SERDES), por ejemplo, como se muestra en la Figura 4.

Cada sujeción RC (tal como la sujeción RC 250 y el circuito 300 detector de ESD transitorio de las Figuras 2 y 3, respectivamente) tiene una constante de tiempo RC correspondiente. La sujeción RC 250 y el circuito 300 detector de ESD transitorio pueden configurarse para un modelo de cuerpo humano o un modelo de dispositivo cargado. A continuación, se utiliza el modelo de cuerpo humano o el modelo de dispositivo cargado para calcular la constante de tiempo RC de la sujeción RC. El cálculo de la constante de tiempo RC para la sujeción RC puede implicar la multiplicación de las resistencias (Rrc y R) con los condensadores de temporización (Crc y C) para derivar un producto que se convierte en el valor de la constante de tiempo RC. Por lo general, el modelo de cuerpo humano calcula un valor de constante de tiempo RC más alto para una sujeción RC, el cual puede usar valores de resistencia y capacitancia mayores. El modelo de dispositivo cargado define un valor de constante de tiempo RC que es más corto y más rápido que la constante de tiempo RC definida por el modelo de cuerpo humano.

Por ejemplo, una constante de tiempo RC asociada con la descarga del modelo de dispositivo cargado es menor o alrededor de un nanosegundo, a la vez que otra constante de tiempo RC asociada con la descarga del modelo del cuerpo humano puede ser de alrededor de ciento cincuenta (150) nanosegundos o más. El modelo de dispositivo cargado también suele tener una amplitud de corriente mucho mayor que el modelo de cuerpo humano. El modelo de cuerpo humano también puede disipar más energía que el modelo de dispositivo cargado.

El daño a los dispositivos MOSFET se produce a menudo en los dieléctricos de óxido de puerta, ya que estas áreas de los dispositivos tienen mucho voltaje. El dieléctrico de la puerta se rompe a voltajes elevados. El diseño de la sujeción RC tiende a favorecer el mantenimiento de un voltaje general bajo. Por lo tanto, se evalúa un intercambio entre el tiempo, el nivel de voltaje y el nivel de corriente para obtener un diseño de sujeción RC eficaz. De acuerdo con aspectos de la presente divulgación, se proporciona la prevención de daños a los dispositivos MOSFET para los circuitos de controlador de entrada y salida del convertidor de paralelo a serie/convertidor de serie a paralelo (SERDES), por ejemplo, como se muestra en las Figuras 4 y 5.

La Figura 4 es un diagrama esquemático de un controlador 400 de salida de convertidor de paralelo a serie/convertidor de serie a paralelo (SERDES) protegido contra ESD, de acuerdo con un aspecto de la presente divulgación. De manera representativa, el controlador 400 de salida diferencial SERDES incluye un circuito 420 controlador de E/S acoplado a un circuito 410 previo al controlador para controlar un panel 406 de salida diferencial. En este aspecto de la presente divulgación, el circuito 420 controlador de E/S incluye un par de controladores de transistor de efecto de campo tipo n (NFET) controlados por inversores pre-controladores (Inv) del circuito 410 pre-controlador. Además, un par de cargas (por ejemplo, Rcarga0 y Rcarga1) representa la impedancia característica (por ejemplo, 100 Ohmios) de una línea de transmisión acoplada al panel 406 de salida diferencial.

Durante un evento de descarga electrostática, una ruta de derivación proporcionada por un diodo Dp 409 y un diodo Dn 408 puede ser insuficiente para proteger los dieléctricos de óxido de puerta del par de controladores NFET del circuito 420 controlador de E/S. De acuerdo con aspectos de la presente divulgación, el controlador 400 de salida diferencial SERDES está configurado para "flotar" el par de controladores NFET del circuito 420 controlador de E/S usando conmutadores de encendido y de tierra, como se describe con más detalle a continuación. Como se describe en el presente documento, el término "flotar" puede referirse a la desconexión del par de controladores NFET del circuito 420 controlador de E/S de los rieles de encendido y las entradas al circuito controlador de E/S.

En esta disposición, se utiliza un controlador N4 de transistor de tipo n (por ejemplo, el primer controlador de transistor) para controlar una salida complementaria (Salida) del panel 406 de salida diferencial. Además, un controlador N5 de transistor de tipo n (por ejemplo, segundo controlador de transistor) del circuito 420 controlador de

E/S se usa para controlar una salida (Salida) del panel 406 de salida diferencial. Un inversor de pre-controlador Inv6 (por ejemplo, el primer inversor de pre-controlador) está acoplado a una puerta G del controlador N4 de transistor de tipo n para controlar la operación del controlador N4 de transistor de tipo n. El inversor de pre-controlador Inv6 también se acopla selectivamente entre un terminal 402 de suministro de energía (Vdd) y un terminal 404 de tierra (Vss) a través de un conmutador de encendido Sw5 (por ejemplo, el primer conmutador de transistor de efecto de campo tipo p (PFET)) y un conmutador de tierra Sw6 (por ejemplo, primer conmutador de transistor de efecto de campo tipo n (NFET)) para proteger el controlador N4 de transistor de tipo n durante un evento de descarga electrostática. De manera similar, un inversor de pre-controlador Inv7 (por ejemplo, un segundo inversor de pre-controlador) está acoplado a una puerta del controlador N5 de transistor de tipo n para controlar la operación del controlador N5 de transistor de tipo n. El inversor de pre-controlador Inv7 también está acoplado selectivamente entre el terminal 402 de suministro de energía y el terminal 404 de tierra a través de un conmutador de encendido Sw7 (por ejemplo, segundo conmutador PFET) y un conmutador de tierra Sw8 (por ejemplo, segundo conmutador NFET) para proteger el controlador N5 de transistor de tipo n durante un evento de descarga electrostática.

- 5 En esta implementación, el conmutador de encendido Sw5 y el conmutador de encendido Sw7, así como el conmutador de tierra Sw6 y el conmutador de tierra Sw8 están configurados para deshabilitar el inversor de pre-controlador Inv6 y el inversor de pre-controlador Inv7 en respuesta a la señal de control de conmutador Tsw y una señal de control de conmutador complementaria  $\bar{T}_{sw}$ , respectivamente. Además, se usa un transistor P3 conmutador de tipo p para desconectar el terminal 402 de suministro de energía del controlador N4 de transistor de tipo n y el controlador N5 de transistor de tipo n del circuito 420 controlador de E/S durante un evento de descarga electrostática detectado. De manera similar, el transistor N6 de tipo n de polarización de modo común se usa para desconectar el terminal 404 de tierra del receptor N4 de transistor de tipo n y el receptor N5 de transistor de tipo n del circuito 420 controlador de E/S durante un evento de descarga electrostática detectado. En esta configuración, la señal de control del conmutador Tsw se define en un estado lógico '1' en respuesta a un evento de descarga electrostática detectado. Sin embargo, durante la operación normal, la señal de control del conmutador Tsw se mantiene en el estado lógico '0'.

- 10

- 15

- 20

- 25

Para desconectar el terminal 404 de tierra, un transistor N6 de tipo n de polarización de modo común se apaga o se comuta al nodo de voltaje de polarización (Vpolarización) de acuerdo con una puerta 460 de transmisión. Durante la operación normal, la puerta de transmisión alimenta el voltaje de nodo Vpolarización a la puerta G del transistor N6 de tipo n de polarización de modo común. La alimentación del voltaje del nodo Vpolarización al transistor N6 de tipo n de polarización de modo común pre-polariza el transistor N6 de tipo n de polarización de modo común para acelerar un tiempo de respuesta si se detecta un evento de descarga electrostática. Además, un conmutador de tipo n N7 está apagado en respuesta a la desinscripción (por ejemplo, '0' lógico) de la señal de control del conmutador Tsw durante la operación normal.

- 30

- 35

- 40

- 45

- 50

- 55

- 60

- 65

Durante un evento de descarga electrostática, la puerta 460 de transmisión suministra la señal de control de conmutador complementaria  $\bar{T}_{sw}$  (por ejemplo, '0' lógico) para apagar el transistor N6 de tipo n de polarización de modo común. Además, un conmutador N7 de tipo n se enciende en respuesta a la afirmación de la señal de control del conmutador Tsw durante el evento de descarga electrostática. En esta configuración, el conmutador N7 de tipo n tiene un drenaje D acoplado a una puerta G del transistor N6 de tipo n de polarización de modo común, una fuente S acoplada al terminal 404 de tierra, y una puerta G acoplada a la señal de control del conmutador Tsw. Durante el evento de descarga electrostática, el conmutador N7 de tipo n se enciende para conectar a tierra la puerta G del transistor N6 de tipo n de polarización de modo común para desconectar el terminal 404 de tierra. Debido a que el transistor N6 de tipo n de polarización de modo común está pre-polarizado, el transistor N6 de tipo n de polarización de modo común responde rápidamente para desconectar el terminal 404 de tierra.

En esta configuración, los conmutadores de encendido (por ejemplo, Sw5 y Sw7) corresponden a PFETs, y los conmutadores de tierra (por ejemplo, Sw6 y Sw8) corresponden a NFETs. Como resultado, los conmutadores de encendido (por ejemplo, Sw5 y Sw7) están abiertos en respuesta a la afirmación de la señal de control del conmutador Tsw (por ejemplo, '1' lógico); a la vez que los conmutadores de tierra (por ejemplo, Sw6 y Sw8) están abiertos en respuesta a la señal de control del conmutador complementaria  $\bar{T}_{sw}$  (por ejemplo, '0' lógico) durante un evento de descarga electrostática. Con esta configuración, los conmutadores de tierra (por ejemplo, Sw6 y Sw8) se pueden implementar con poca sobrecarga del circuito, especialmente si la señal de control del conmutador Tsw y la señal de control del conmutador complementaria  $\bar{T}_{sw}$  se derivan del circuito 300 detector de ESD transitorio, como se muestra en la Figura 3. En esta configuración, el transistor P3 conmutador tipo p es opcional con base en la polaridad de descarga del peor caso y las resistencias de carga diferencial Rcarga1 y Rcarga2, las cuales pueden estar en el rango de aproximadamente 100 ohmios.

La Figura 5 es un diagrama esquemático de un receptor 500 diferencial de convertidor de paralelo a serie/convertidor de serie a paralelo (SERDES) protegido contra ESD, de acuerdo con un aspecto de la presente divulgación. De manera representativa, el receptor 500 diferencial SERDES incluye un circuito 520 receptor de E/S acoplado a un panel 506 de entrada diferencial. En este aspecto de la presente divulgación, el circuito 520 receptor de E/S incluye un par de receptores de transistores de efecto de campo de tipo n (NFETs). Durante un evento de descarga electrostática, una ruta de derivación proporcionada por un diodo Dp 509 y un diodo Dn 508 es insuficiente para proteger los dieléctricos de óxido de puerta del par de receptores NFET del circuito 520 receptor de E/S.

De acuerdo con aspectos de la presente divulgación, el receptor 500 diferencial SERDES está configurado para 'flotar' el par de receptores NFET del circuito 520 receptor de E/S, como se describe con más detalle a continuación. Como se describe en el presente documento, el término 'flotar' puede referirse a la desconexión del par de receptores NFET del circuito 520 receptor de E/S de los rieles de encendido y tierra del receptor 500 diferencial SERDES.

En esta disposición, se utiliza un receptor N8 de transistor de tipo n (por ejemplo, el primer receptor de transistor) para recibir una entrada complementaria (Entrada) del panel 506 de entrada diferencial. Además, un receptor N9 de transistor de tipo n (por ejemplo, segundo receptor de transistor) del circuito 520 receptor de E/S se usa para recibir una entrada (Entrada) del panel 506 de entrada diferencial. Una salida diferencial complementaria (Salida) está acoplada a un drenaje D del receptor N8 de transistor de tipo n para suministrar la entrada complementaria recibida (Entrada) del panel 506 de entrada diferencial. Además, una salida diferencial (Salida) está acoplada a un drenaje del receptor N9 de transistor de tipo n para suministrar la entrada recibida (Entrada) del panel 506 de entrada diferencial.

En este aspecto de la presente divulgación, un transistor P4 de carga de tipo p está acoplado entre el drenaje D del receptor N8 de transistor de tipo n y un terminal 502 de suministro de energía (Vdd). Además, un transistor P5 de encendido de tipo p está acoplado entre el drenaje D del receptor N9 de transistor de tipo n y el terminal 502 de suministro de energía. Un transistor N11 de tipo n de modo común también está acoplado entre una fuente S tanto del receptor N8 de transistor de tipo n como del receptor N9 de transistor de tipo n, y un terminal 504 de tierra (Vss). En esta disposición, el transistor N11 de tipo n de modo común puede operar como un espejo de corriente para el circuito 520 receptor de E/S manteniendo una corriente de salida constante.

En esta implementación, el transistor P4 de carga de tipo p (primer transistor de carga) se usa para desconectar el terminal 502 de suministro de energía del receptor N8 de transistor de tipo n del circuito 520 receptor de E/S durante un evento de descarga electrostática. Además, el transistor P5 de carga de tipo p (segundo transistor de carga) se usa para desconectar el terminal 502 de suministro de energía del receptor N9 de transistor de tipo n del circuito 520 receptor de E/S durante un evento de descarga electrostática. De manera similar, el transistor N10 de tipo n de modo común se usa para desconectar el terminal 504 de tierra del receptor N8 de transistor de tipo n y el receptor N9 de transistor de tipo n del circuito 520 receptor de E/S durante un evento de descarga electrostática detectado. En esta configuración, la señal de control del conmutador Tsw se anula a un estado lógico '0' en respuesta a un evento de descarga electrostática detectado. Sin embargo, durante la operación normal, la señal de control del conmutador Tsw se mantiene en un estado lógico '1'.

Para desconectar el terminal 504 de tierra, el transistor N10 de tipo n de modo común se apaga o se conmuta a una señal de control de tipo n (ControlN) de acuerdo con una puerta 560 de transmisión. Durante la operación normal, la puerta 560 de transmisión alimenta la señal de control de tipo n ControlN a la puerta del transistor N10 de tipo n de modo común. Durante un evento de descarga electrostática, la puerta 560 de transmisión alimenta la señal de control del conmutador Tsw (por ejemplo, '0' lógico) para apagar el transistor N10 de modo común. Además, un conmutador N11 de tipo n se enciende en respuesta a la señal de control del conmutador complementaria  $\bar{T}_{sw}$  (por ejemplo, '1' lógico). En esta configuración, el conmutador N11 de tipo n tiene un drenaje D acoplado a una puerta G del transistor N10 de tipo n de modo común, una fuente S acoplada al terminal 504 de tierra, y una puerta G acoplada a la señal de control del conmutador complementaria  $\bar{T}_{sw}$ . En esta disposición, el conmutador N11 de tipo n conecta a tierra el transistor N10 de tipo n de modo común en respuesta a la señal de control de conmutador complementaria  $\bar{T}_{sw}$  (por ejemplo, '1' lógico) mediante el cortocircuito de la puerta G del transistor N10 de tipo n de modo común al terminal 504 de tierra durante un evento de descarga electrostática detectado.

Para desconectar el terminal 502 de suministro de energía, el transistor P4 de tipo p de carga y el transistor P5 de tipo p de carga se apagan o se conmutan a una señal de control de tipo p (ControlP) de acuerdo con una puerta 570 de transmisión. Durante la operación normal, la puerta 570 de transmisión alimenta la señal de control de tipo p ControlP a una puerta G del transistor P4 de tipo p de carga y una puerta G del transistor P5 de tipo p de carga. Por ejemplo, alimentar ControlP al transistor P4 de tipo p de carga y al transistor tipo p de carga puede hacer que estos transistores floten durante la operación normal.

Durante un evento de descarga electrostática, la puerta 570 de transmisión alimenta la señal de control del conmutador complementaria  $\bar{T}_{sw}$  (por ejemplo, '1' lógico) al transistor P4 de tipo p de carga y al transistor P5 de tipo p de carga para apagar los transistores de carga tipo p. Además, un conmutador P6 de tipo p se enciende en respuesta a la señal de control del conmutador Tsw (por ejemplo, '0' lógico). En esta configuración, el conmutador P6 de tipo p tiene un drenaje D acoplado a las puertas del transistor P4 de tipo p de carga y el transistor P5 de tipo p de carga, una fuente S acoplada al terminal 502 de suministro de energía, y una puerta G acoplada a la señal de control del conmutador Tsw. En esta disposición, el conmutador N8 de tipo n conecta a tierra el transistor P4 de tipo p de carga y el transistor P5 de tipo p de carga en respuesta a la desactivación de la señal de control del conmutador Tsw mediante el cortocircuito de las puertas del transistor P4 de carga de tipo p y el transistor P5 de tipo p de carga al terminal 502 de suministro de energía durante el evento de descarga electrostática detectado.

La Figura 6 es un diagrama de flujo del proceso que ilustra un método 600 para proteger un circuito de entrada/salida diferencial (E/S) de convertidor de paralelo a serie/convertidor de serie a paralelo (SERDES) de acuerdo con un aspecto de la presente divulgación. En el bloque 602, se detecta un evento de descarga electrostática. Por ejemplo, como se muestra en la Figura 3, el circuito 300 detector de ESD transitorio puede detectar un evento de descarga electrostática cuando ocurre un rápido aumento de voltaje en un terminal 302 de suministro (Vdd). El rápido aumento en el terminal 302 de suministro se identifica como un evento de descarga electrostática (ESD), en lugar de una condición de encendido mucho más lenta durante la operación normal.

- 5 10 Con referencia nuevamente en la Figura 6, en el bloque 604, un terminal de suministro de energía se desconecta selectivamente de un par de transistores de E/S del circuito de E/S SERDES. Por ejemplo, como se muestra en la Figura 4, se utiliza un transistor P3 conmutador de tipo p para desconectar el terminal 402 de suministro de energía del controlador N4 de transistor de tipo n y el controlador N5 de transistor de tipo n del circuito 420 controlador de E/S durante un evento de descarga electrostática detectado. Como se muestra en la Figura 5, el transistor P4 de carga de tipo p se usa para desconectar el terminal 502 de suministro de energía del receptor N8 de transistor de tipo n del circuito 520 receptor de E/S durante un evento de descarga electrostática. Además, el transistor P5 de carga de tipo p se usa para desconectar el terminal 502 de suministro de energía del receptor N9 de transistor de tipo n del circuito 520 receptor de E/S durante un evento de descarga electrostática.

- 15 20 Con referencia de nuevo en la Figura 6, en el bloque 606, un terminal de tierra se desconecta selectivamente del par de transistores de E/S del circuito controlador de E/S SERDES. Por ejemplo, como se muestra en la Figura 4, el transistor N6 de tipo n de polarización de modo común se usa para desconectar el terminal 404 de tierra del receptor N4 de transistor de tipo n y el receptor N5 de transistor de tipo n del circuito 420 controlador de E/S durante un evento de descarga electrostática detectado. Como se muestra en la Figura 5, el transistor N10 de tipo n de modo común se usa para desconectar el terminal 504 de tierra del receptor N8 de transistor de tipo n y el receptor N9 de transistor de tipo n del circuito 520 receptor de E/S durante un evento de descarga electrostática detectado.

25 30 De acuerdo con un aspecto adicional de la presente divulgación, se describe el circuito de entrada/salida diferencial (E/S) de convertidor de paralelo a serie/convertidor de serie a paralelo (SERDES). El circuito de E/S diferencial SERDES incluye medios para desconectar selectivamente el terminal de suministro de energía del primer controlador de transistor y el segundo controlador de transistor del circuito controlador de E/S. Los medios de desconexión selectiva pueden ser el circuito 300 detector de ESD de la Figura 3. El circuito de E/S diferencial SERDES incluye además medios para desconectar selectivamente el terminal de tierra del primer controlador de transistor y el segundo controlador de transistor del circuito controlador de E/S. Por ejemplo, los medios de desconexión selectiva pueden ser el circuito 300 detector de ESD de la Figura 3. En otro aspecto, los medios anteriormente mencionados pueden ser cualquier circuito, módulo, o cualquier aparato configurado para realizar las funciones enumeradas por los medios anteriormente mencionados.

35 40 La Figura 7 es un diagrama de bloques que muestra un ejemplo de sistema 700 de comunicación inalámbrica en el cual se puede emplear ventajosamente un aspecto de la divulgación. Con fines ilustrativos, la Figura 7 muestra tres unidades 720, 730, y 750 remotas y dos estaciones 740 base. Se reconocerá que los sistemas de comunicación inalámbrica pueden tener muchas más unidades remotas y estaciones base. Las unidades 720, 730, y 750 remotas incluyen dispositivos IC 725A, 725C, y 725B que incluyen los circuitos de E/S SERDES protegidos contra ESD divulgados. Se reconocerá que otros dispositivos también pueden incluir los circuitos de E/S SERDES protegidos contra ESD divulgados, tales como las estaciones base, los dispositivos de conmutación, y el equipo de red. La Figura 7 muestra señales 780 de enlace directo a partir de la estación 740 base a las unidades 720, 730, y 750 remotas y señales 790 de enlace inverso a partir de las unidades 720, 730, y 750 remotas a las estaciones 740 base.

45 50 En la Figura 7, la unidad 720 remota se muestra como un teléfono móvil, la unidad 730 remota se muestra como un ordenador portátil, y la unidad 750 remota se muestra como una unidad remota de ubicación fija en un sistema de bucle local inalámbrico. Por ejemplo, una unidad remota puede ser un teléfono móvil, una unidad de sistemas de comunicación personal (PCS) de mano, una unidad de datos portátil tal como un asistente de datos personales, un dispositivo con GPS, un dispositivo de navegación, un decodificador, un reproductor de música, un reproductor de vídeo, una unidad de entretenimiento, una unidad de datos de ubicación fija tal como un equipo de lectura de medidores, un componente de la unidad remota, tal como un controlador de pantalla, un módem, u otro dispositivo que almacena o recupera datos o instrucciones de ordenador, o combinaciones de los mismos. Aunque la Figura 7 ilustra unidades remotas de acuerdo con los aspectos de la divulgación, la divulgación no se limita a estas unidades ilustradas de ejemplo. Los aspectos de la divulgación pueden emplearse adecuadamente en diversos dispositivos, los cuales incluyen los circuitos de E/S SERDES protegidos contra ESD divulgados.

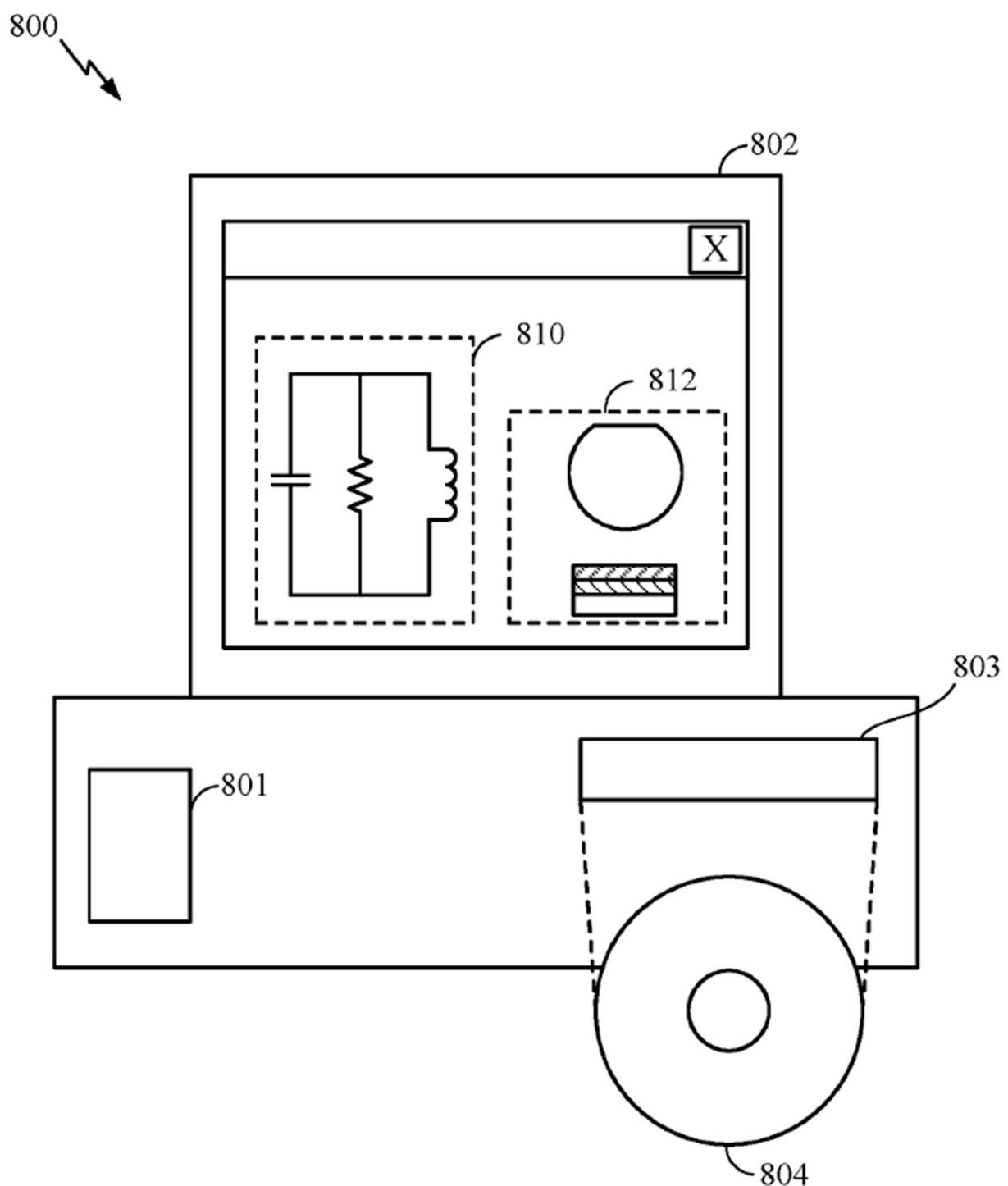

55 60 La Figura 8 es un diagrama de bloques que ilustra una estación de trabajo de diseño utilizada para el diseño de circuitos, disposición, y lógica de un componente semiconductivo, tal como los circuitos de E/S SERDES protegidos contra ESD divulgados anteriormente. Una estación 800 de trabajo de diseño incluye un disco 801 duro que contiene el software del sistema operativo, archivos de soporte, y software de diseño tal como Cadence u OrCAD. La estación 800 de trabajo de diseño también incluye una pantalla 802 para facilitar el diseño de un circuito 810 o un

componente 812 semiconductivo tal como un circuito controlador de E/S protegido contra ESD. Se proporciona un medio 804 de almacenamiento para almacenar tangiblemente el diseño 810 de circuito o el componente 812 semiconductivo. El diseño 810 de circuito o el componente 812 semiconductivo pueden almacenarse en el medio 804 de almacenamiento en un formato de archivo tal como GDSII o GERBER. El medio 804 de almacenamiento

5 puede ser un CDROM, DVD, disco duro, memoria flash, u otro dispositivo apropiado. Además, la estación 800 de trabajo de diseño incluye un aparato 803 de controlador para aceptar entradas a partir de o escribir salidas en el medio 804 de almacenamiento.

10 Los datos registrados en el medio 804 de almacenamiento pueden especificar configuraciones de circuito lógico, datos de patrón para máscaras de fotolitografía, o datos de patrón de máscara para herramientas de escritura en serie tales como litografía por haz de electrones. Los datos pueden incluir además datos de verificación lógica tales como diagramas de tiempo o circuitos de red asociados con simulaciones lógicas. Proporcionar datos en el medio 804 de almacenamiento facilita el diseño del diseño 810 de circuito o el componente 812 semiconductivo al disminuir el número de procesos para diseñar tabletas semiconductivas.

15 Para una implementación de firmware y/o software, las metodologías pueden implementarse con módulos (por ejemplo, procedimientos, funciones, etc.) que realizan las funciones descritas en el presente documento. Se puede utilizar un medio legible por máquina que incorpore de forma tangible instrucciones para implementar las metodologías descritas en el presente documento. Por ejemplo, los códigos de software pueden almacenarse en una memoria y ejecutarse mediante una unidad de procesador. La memoria puede implementarse dentro de la unidad de procesador o externamente a la unidad de procesador. Como se usa en el presente documento, el término "memoria" se refiere a tipos de memoria a largo plazo, a corto plazo, volátil, no volátil, u otra y no se limita a un tipo particular de memoria o número de memorias, o tipo de medio sobre la cual está almacenada la memoria.

20 25 Si se implementa en firmware y/o software, las funciones pueden almacenarse como una o más instrucciones o código en un medio legible por ordenador. Los ejemplos incluyen medios legibles por ordenador codificados con una estructura de datos y medios legibles por ordenador codificados con un programa de ordenador. Los medios legibles por ordenador incluyen medios físicos de almacenamiento de ordenador. Un medio de almacenamiento puede ser un medio disponible al que se puede acceder mediante un ordenador. A modo de ejemplo, y sin limitarse a ello, dichos medios legibles por ordenador pueden incluir RAM, ROM, EEPROM, CD-ROM u otro almacenamiento en disco óptico, almacenamiento en disco magnético, u otros dispositivos de almacenamiento magnético, u otro medio que se pueda utilizar para almacenar el código de programa deseado en la forma de instrucciones o estructuras de datos y al que se puede acceder mediante un ordenador; disco magnético y disco, como se usa en el presente documento, incluye disco compacto (CD), disco láser, disco óptico, disco versátil digital (DVD), disquete y disco Blu-ray donde los discos en general reproducen datos magnéticamente, a la vez que los discos reproducen datos ópticamente con láser. Las combinaciones de los anteriores también deben incluirse dentro del alcance de los medios legibles por ordenador.

30 35 40 Además del almacenamiento en un medio legible por ordenador, se pueden proporcionar instrucciones y/o datos como señales en medios de transmisión incluidos en un aparato de comunicación. Por ejemplo, un aparato de comunicación puede incluir un transceptor que tenga señales indicativas de instrucciones y datos. Las instrucciones y los datos están configurados para hacer que uno o más procesadores implementen las funciones descritas en las reivindicaciones.

45 50 55 Aunque la presente divulgación y sus ventajas se han descrito en detalle, debe entenderse que se pueden realizar aquí diversos cambios, sustituciones y alteraciones sin apartarse de la tecnología de la divulgación tal como se define en las reivindicaciones adjuntas. Por ejemplo, los términos relativos, tales como "arriba" y "abajo" se utilizan con respecto a un sustrato o dispositivo electrónico. Por supuesto, si el sustrato o dispositivo electrónico está invertido, arriba se convierte en abajo y viceversa. Además, si se orienta hacia los lados, arriba y abajo pueden referirse a los lados de un sustrato o dispositivo electrónico. Además, el alcance de la presente solicitud no está destinado a limitarse a las configuraciones particulares del proceso, la máquina, la fabricación, la composición de la materia, los medios, los métodos y las etapas descritas en la especificación. Como un experto en la técnica apreciará fácilmente a partir de la divulgación, los procesos, las máquinas, la fabricación, las composiciones de materia, los medios, los métodos o las etapas, que existen actualmente o que se desarrollarán posteriormente, que realizan sustancialmente la misma función o logran sustancialmente el mismo resultado como las configuraciones correspondientes descritas en el presente documento pueden utilizarse de acuerdo con la presente divulgación.

## REIVINDICACIONES

1. Un circuito (400) controlador diferencial de convertidor de paralelo a serie/convertidor de serie a paralelo protegido, SERDES de descarga electrostática, ESD, que comprende:

- 5        un circuito (420) controlador de entrada/salida, E/S, que incluye un primer controlador (N4) de transistor y un segundo controlador (N5) de transistor, cada uno de los cuales tiene un drenaje acoplado a un panel (406) de salida diferencial;

- 10      un circuito (410) pre-controlador que incluye un primer inversor de pre-controlador (Inv6) acoplado a una puerta del primer controlador de transistor, y un segundo inversor de pre-controlador (Inv7) acoplado a una puerta del segundo controlador de transistor, en el cual el circuito de pre-controlador está acoplado selectivamente entre un terminal (402) de suministro de energía y un terminal (404) de tierra;

- 15      un transistor (P2, P3) conmutador acoplado entre el terminal de suministro de energía, el primer controlador de transistor, y el segundo controlador de transistor del circuito controlador de E/S;

- 20      un transistor (N6) de modo común acoplado entre el terminal de tierra, el primer controlador de transistor y el segundo controlador de transistor del circuito controlador de E/S; y

- 25      un circuito (300) detector de ESD configurado para desconectar selectivamente el terminal de suministro de energía del primer controlador de transistor y el segundo controlador de transistor del circuito controlador de E/S apagando el transistor (P2, P3) conmutador, y configurado para desconectar selectivamente el terminal de tierra del primer controlador de transistor y el segundo controlador de transistor del circuito controlador de E/S apagando el transistor (N6) de modo común, comprendiendo el circuito detector de ESD:

- 30      un conmutador (N7) transistor de efecto de campo tipo n, NFET, que tiene un drenaje acoplado a una puerta del transistor (N6) de modo común, una fuente acoplada al terminal de tierra y una puerta acoplada a una señal de control de conmutador (Tsw) del circuito detector de ESD; y una puerta (460) de transmisión operable de acuerdo con la señal de control de conmutador (Tsw) para alimentar un voltaje de polarización (Vpolarización) al transistor (N6) de modo común durante la operación normal y para alimentar una señal de control de conmutador complementaria (/Tsw) al transistor de modo común durante un evento de descarga electrostática

- 35      2. El circuito controlador diferencial SERDES protegido contra ESD de la reivindicación 1, comprendiendo además:

- 35      un primer conmutador (Sw5) de transistor de efecto de campo tipo p, PFET, que acopla selectivamente el primer inversor pre-controlador (Inv6) al terminal de suministro de energía; y un segundo conmutador PFET (Sw7) que acopla selectivamente el segundo inversor pre-controlador (Inv7) al terminal de suministro de energía, en el cual el primer conmutador PFET y el segundo conmutador PFET pueden abrirse en respuesta a la señal de control del conmutador (Tsw) del circuito detector de ESD.

- 40      3. El circuito controlador diferencial SERDES protegido contra ESD de la reivindicación 1, comprendiendo además:

- 45      un segundo conmutador (Sw6) de transistor de efecto de campo de tipo n, NFET, que acopla selectivamente el primer inversor pre-controlador (Inv6) al terminal de tierra; y un tercer conmutador NFET (Sw8) que acopla selectivamente el segundo inversor pre-controlador (Inv7) al terminal de tierra, en el cual el tercer conmutador NFET y el segundo conmutador NFET pueden abrirse en respuesta a la señal de control del conmutador complementaria (/Tsw) del circuito detector de ESD.

- 50      4. El circuito controlador diferencial SERDES protegido contra ESD de la reivindicación 1, en el cual el primer controlador de transistor y el segundo controlador de transistor comprenden transistores de efecto de campo de tipo n, NFETs.

- 55      5. El circuito controlador diferencial SERDES protegido contra ESD de la reivindicación 1, integrado en un sistema de circuito de E/S para un módem.

- 60      6. El circuito controlador diferencial SERDES protegido contra ESD de la reivindicación 1 integrado en un sistema de circuito de E/S para un controlador de pantalla.

- 65      7. El circuito controlador diferencial SERDES protegido contra ESD de la reivindicación 1, integrado en un teléfono móvil, un decodificador, un reproductor de música, un reproductor de vídeo, una unidad de entretenimiento, un dispositivo de navegación, un ordenador, sistemas de comunicación personales de mano, PCS, unidad, una unidad de datos portátil, y/o una unidad de datos de ubicación fija.

- 65      8. Un método para proteger un circuito de entrada/salida diferencial, E/S de convertidor de paralelo a serie/convertidor de serie a paralelo, SERDES, que comprende:

detectar (602) un evento de descarga electrostática; desconectar (604) selectivamente un terminal (402) de suministro de energía de un par de transistores (N4, N5) de E/S del circuito de E/S diferencial SERDES en respuesta al evento de descarga electrostática detectado;

- 5 desconectar (606) selectivamente un terminal (404) de tierra del par de transistores (N4, N5) de E/S del circuito de E/S diferencial SERDES en respuesta al evento de descarga electrostática detectado al apagar un transistor (N6) de modo común; y controlar el par de transistores de E/S del circuito de E/S diferencial SERDES mediante un circuito (410) pre-controlador que incluye un primer inversor de pre-controlador (Inv6) y un segundo inversor de pre-controlador (Inv7), en el cual el circuito pre-controlador está acoplado selectivamente entre el terminal de suministro de energía y el terminal de tierra; en donde la desconexión selectiva del terminal de tierra del par de transistores de E/S se realiza controlando una puerta (460) de transmisión, a través de una señal de control de comutador (Tsw), para alimentar un voltaje de polarización (Vpolarización) al transistor (N6) de modo común durante la operación normal y para alimentar una señal de control de comutador complementaria (/Tsw) al transistor de modo común para apagarlo durante el evento de descarga electrostática, en donde el transistor (N6) de modo común está acoplado entre el terminal de tierra y el par de transistores I/O.

- 10 15 20 9. El método de la reivindicación 8, que comprende además integrar el circuito de E/S diferencial SERDES en un teléfono móvil, un decodificador, un reproductor de música, un reproductor de vídeo, una unidad de entretenimiento, un dispositivo de navegación, un ordenador, sistemas de comunicación personales de mano, PCS, una unidad, una unidad de datos portátil, y/o una unidad de datos de ubicación fija.

**FIG. 1**

FIG. 2

**FIG. 3**

FIG. 4

**FIG. 5**

**FIG. 6**

**FIG. 7**

**FIG. 8**