(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4945999号

(P4945999)

(45) 発行日 平成24年6月6日(2012.6.6)

(24) 登録日 平成24年3月16日(2012.3.16)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 27/04   | (2006.01) | HO1L 27/04 | H    |

| HO1L 21/822  | (2006.01) | HO1L 27/06 | 311B |

| HO1L 27/06   | (2006.01) | HO1L 27/08 | 102F |

| HO1L 27/088  | (2006.01) | HO1L 27/08 | 331D |

| HO1L 21/8234 | (2006.01) | HO1L 21/76 | M    |

請求項の数 16 (全 31 頁) 最終頁に続く

(21) 出願番号

特願2005-308704 (P2005-308704)

(22) 出願日

平成17年10月24日 (2005.10.24)

(65) 公開番号

特開2007-116053 (P2007-116053A)

(43) 公開日

平成19年5月10日 (2007.5.10)

審査請求日

平成20年10月20日 (2008.10.20)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100104710

弁理士 竹腰 昇

(74) 代理人 100124682

弁理士 黒田 泰

(74) 代理人 100090479

弁理士 井上 一

(74) 代理人 100090387

弁理士 布施 行夫

(74) 代理人 100090398

弁理士 大渕 美千栄

最終頁に続く

(54) 【発明の名称】集積回路装置及び電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の電源ノードと中間ノード及び第2の電源ノードとの間に設けられる第1の保護回路と、

前記第2の電源ノードと前記中間ノードとの間に設けられる第2の保護回路とを含み、前記第1の保護回路は、

前記第1の電源ノードと前記中間ノードとの間に設けられ、前記第1の電源ノードから前記中間ノードへの方向を順方向とする第1のダイオードと、

前記第1の電源ノードと前記中間ノードとの間に設けられ、前記中間ノードから前記第1の電源ノードへの方向を順方向とする第2のダイオードと、

前記第2の電源ノードと前記中間ノードとの間に設けられ、前記第2の電源ノードから前記中間ノードへの方向を順方向とし、第2導電型基板と前記第2導電型基板の上の第1の第1導電型ウェルがトリブルウェル構造を構成する場合に、前記第2導電型基板と前記第1の第1導電型ウェルとの間の接合面に形成される第1の寄生ダイオードとを含み、

前記第2の保護回路は、

前記第2の電源ノードと前記中間ノードとの間に設けられ、前記第2の電源ノードから前記中間ノードへの方向を順方向とする第3のダイオードと、

前記第2の電源ノードと前記中間ノードとの間に設けられ、前記中間ノードから前記第2の電源ノードへの方向を順方向とする第4のダイオードと、

前記第2の電源ノードと前記中間ノードとの間に設けられ、前記第2の電源ノードから

10

前記第2の電源ノードと前記中間ノードとの間に設けられ、前記第2の電源ノードから

20

前記中間ノードへの方向を順方向とし、前記第2導電型基板と前記第2導電型基板の上の第2の第1導電型ウェルがトリプルウェル構造を構成する場合に、前記第2導電型基板と前記第2の第1導電型ウェルとの間の接合面に形成される第2の寄生ダイオードとを含むことを特徴とする集積回路装置。

**【請求項2】**

請求項1において、

前記第1のダイオードは、第1の第2導電型拡散領域とその下の第1の第1導電型ウェルとの間の接合面に形成され、

前記第2のダイオードは、第1の第1導電型拡散領域とその下の第1の第2導電型ウェルとの間の接合面に形成され、

前記第3のダイオードは、第2の第2導電型拡散領域とその下の第2の第1導電型ウェルとの間の接合面に形成され、

前記第4のダイオードは、第2の第1導電型拡散領域とその下の第2の第2導電型ウェルとの間の接合面に形成されることを特徴とする集積回路装置。

**【請求項3】**

請求項1又は2において、

第3の電源ノードと前記中間ノード及び前記第2の電源ノードとの間に設けられる第3の保護回路を含み、

前記第3の保護回路は、

前記第3の電源ノードと前記中間ノードとの間に設けられ、前記第3の電源ノードから前記中間ノードへの方向を順方向とする第5のダイオードと、

前記第3の電源ノードと前記中間ノードとの間に設けられ、前記中間ノードから前記第3の電源ノードへの方向を順方向とする第6のダイオードと、

前記第2の電源ノードと前記中間ノードとの間に設けられ、前記第2の電源ノードから前記中間ノードへの方向を順方向とし、トリプルウェル構造を構成する第2導電型基板とその上の第3の第1導電型ウェルとの間の接合面に形成される第3の寄生ダイオードとを含むことを特徴とする集積回路装置。

**【請求項4】**

請求項3において、

前記第5のダイオードは、第3の第2導電型拡散領域とその下の第3の第1導電型ウェルとの間の接合面に形成され、

前記第6のダイオードは、第3の第1導電型拡散領域とその下の第3の第2導電型ウェルとの間の接合面に形成されることを特徴とする集積回路装置。

**【請求項5】**

請求項3又は4において、

シリアルバスを介してデータ転送を行う物理層回路を含む高速インターフェース回路ブロックと、少なくとも1つの他の回路ブロックとを含み、

前記高速インターフェース回路ブロックは、

第1、第2の保護回路ブロックを含み、

前記第1、第2の保護回路ブロックの各々は、前記高速インターフェース回路ブロックの電源と前記他の回路ブロックの電源との間に設けられる少なくとも1つの保護回路を含み、

前記第1の保護回路ブロックは、前記第1の保護回路と、前記第2の保護回路と、前記第3の保護回路を含み、

前記第2の保護回路ブロックは、前記第1の保護回路と同じ回路構成の第4の保護回路と、前記第2の保護回路と同じ回路構成の第5の保護回路と、前記第3の保護回路と同じ回路構成の第6の保護回路を含み、

前記第1の保護回路ブロックは、前記高速インターフェース回路ブロックの短辺を第1の辺とした場合に、前記第2の保護回路ブロックよりも前記第1の辺側に配置され、

前記第2の保護回路ブロックは、前記高速インターフェース回路ブロックの前記第1の

10

20

30

40

50

辺に対向する辺を第3の辺とした場合に、前記第1の保護回路ブロックよりも前記第3の辺側に配置されることを特徴とする集積回路装置。

**【請求項6】**

請求項5において、

前記物理層回路は、前記第1、第2の保護回路ブロックの間に配置されることを特徴とする集積回路装置。

**【請求項7】**

請求項5又は6において、

前記第1の辺から前記第3の辺へと向かう方向を第1の方向とし、前記第1の方向の反対方向を第3の方向とした場合に、前記物理層回路の前記第3の方向側に前記第1の保護回路ブロックが配置され、前記物理層回路の前記第1の方向側に前記第2の保護回路ブロックが配置されることを特徴とする集積回路装置。

10

**【請求項8】**

請求項5乃至7のいずれかにおいて、

前記高速インターフェース回路ブロックは、前記物理層回路と、ロジック回路を含み、

前記高速インターフェース回路ブロックの前記第1の辺から前記第3の辺へと向かう方向を第1の方向とし、前記高速インターフェース回路ブロックの長辺である第2の辺から対向する第4の辺へと向かう方向を第2の方向とした場合に、前記ロジック回路は、前記物理層回路の前記第2の方向側に配置されることを特徴とする集積回路装置。

20

**【請求項9】**

請求項8において、

前記他の回路ブロックとして、表示制御信号を生成するドライバ用ロジック回路ブロックを含み、

前記ドライバ用ロジック回路ブロックは、前記ロジック回路の前記第2の方向側に配置されることを特徴とする集積回路装置。

**【請求項10】**

請求項8又は9において、

前記物理層回路の前記第1の方向での長さをL1とし、前記ロジック回路の前記第1の方向での長さをL2とした場合に、L2 > L1であることを特徴とする集積回路装置。

30

**【請求項11】**

請求項1又は0において、

前記第1の方向の反対方向を第3の方向とした場合に、前記物理層回路の前記第3の方向側の第1の領域に前記第1の保護回路ブロックが配置され、前記物理層回路の前記第1の方向側の第2の領域に前記第2の保護回路ブロックが配置されることを特徴とする集積回路装置。

**【請求項12】**

請求項1又は1において、

前記第1、第2の領域に、前記高速インターフェース回路ブロックの高電位側電源と低電位側電源の間に設けられるキャパシタが形成されるキャパシタ領域が配置されることを特徴とする集積回路装置。

40

**【請求項13】**

請求項5乃至1又は2のいずれかにおいて、

前記高速インターフェース回路ブロックは、前記物理層回路と、ロジック回路と、共用電源の電源線を含み、

前記第1の保護回路ブロックは、

前記第1の電源ノードである前記物理層回路の電源と、前記中間ノードである前記共用電源との間に設けられる前記第1の保護回路と、

前記第3の電源ノードである前記ロジック回路の電源と、前記共用電源との間に設けられる前記第2の保護回路と、

前記第2の電源ノードである前記他の回路ブロックの電源と、前記共用電源との間に設

50

けられる前記第3の保護回路を含み、

前記第2の保護回路ブロックは、

前記物理層回路の電源と前記共用電源との間に設けられる前記第4の保護回路と、

前記ロジック回路の電源と前記共用電源との間に設けられる前記第5の保護回路と、

前記他の回路ブロックの電源と前記共用電源との間に設けられる前記第6の保護回路を含むことを特徴とする集積回路装置。

【請求項14】

請求項13において、

前記高速インターフェース回路ブロックの前記第1の辺から前記第3の辺へと向かう方向を第1の方向とし、前記第1の方向の反対方向を第3の方向とした場合に、

10

前記第1の保護回路の前記第3の方向側に前記第2の保護回路が配置され、

前記第4の保護回路の前記第1の方向側に前記第5の保護回路が配置されることを特徴とする集積回路装置。

【請求項15】

請求項14において、

前記第1の保護回路と前記物理層回路を接続する第1の電源線の前記第3の方向側に、前記第2の保護回路と前記ロジック回路を接続する第2の電源線が配線され、

前記第4の保護回路と前記物理層回路を接続する第4の電源線の前記第1の方向側に、前記第5の保護回路と前記ロジック回路を接続する第5の電源線が配線されることを特徴とする集積回路装置。

20

【請求項16】

請求項1乃至15のいずれかに記載の集積回路装置と、

前記集積回路装置により駆動される表示パネルと、

を含むことを特徴とする電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、集積回路装置及び電子機器に関する。

【背景技術】

【0002】

30

アナログ回路とデジタル回路とが混在し、複数の電源系を有する集積回路装置では、1つの電源系で生じたサージ、ノイズ等が他の電源系に及ぼす影響（素子の破壊、ノイズの伝搬等）を、できる限り低減することが望ましい。このため、従来よりこのような電源系間の影響を低減するための技術が知られている。

【0003】

しかしながら、上記従来技術等では、トリプルウェル構造の回路におけるサージ、ノイズ等の悪影響の低減については考慮されていなかった。

【特許文献1】特開平9-172146号公報

【発明の開示】

【発明が解決しようとする課題】

40

【0004】

本発明は、以上のような技術的課題に鑑みてなされたものであり、その目的とするところは、サージ、ノイズ等の悪影響を低減できる集積回路装置及びこれを含む電子機器を提供することにある。

【課題を解決するための手段】

【0005】

本発明は、第1の電源ノードと中間ノードとの間に設けられる第Jの保護回路と、第2の電源ノードと前記中間ノードとの間に設けられる第Kの保護回路とを含み、前記第Jの保護回路は、前記第1の電源ノードと前記中間ノードとの間に設けられ、前記第1の電源ノードから前記中間ノードへの方向を順方向とする第1のダイオードと、前記第1の電源

50

ノードと前記中間ノードとの間に設けられ、前記中間ノードから前記第1の電源ノードへの方向を順方向とする第2のダイオードと、前記第2の電源ノードと前記中間ノードとの間に設けられ、前記第2の電源ノードから前記中間ノードへの方向を順方向とし、トリプルウェル構造を構成する第2導電型基板とその上の第1の第1導電型ウェルとの間の接合面に形成される第1の寄生ダイオードとを含み、前記第Kの保護回路は、前記第2の電源ノードと前記中間ノードとの間に設けられ、前記第2の電源ノードから前記中間ノードへの方向を順方向とする第3のダイオードと、前記第2の電源ノードと前記中間ノードとの間に設けられ、前記中間ノードから前記第2の電源ノードへの方向を順方向とする第4のダイオードと、前記第2の電源ノードと前記中間ノードとの間に設けられ、前記第2の電源ノードから前記中間ノードへの方向を順方向とし、トリプルウェル構造を構成する第2導電型基板とその上の第2の第1導電型ウェルとの間の接合面に形成される第2の寄生ダイオードとを含む集積回路装置に関する。 10

#### 【0006】

本発明によれば、第1の電源ノードと中間ノードの間に第Jの保護回路が設けられ、第2の電源ノードと中間ノードの間に第Kの保護回路が設けられる。また第Jの保護回路は、双方向ダイオードを構成する第1、第2のダイオードと、第1の寄生ダイオードを含み、第Kの保護回路は、双方向ダイオードを構成する第3、第4のダイオードと、第2の寄生ダイオードを含む。この場合に、第1の寄生ダイオードは、トリプルウェル構造を構成する第2導電型基板とその上の第1の第1導電型ウェルとの間の接合面に形成され、第2の寄生ダイオードは、トリプルウェル構造を構成する第2導電型基板とその上の第2の第1導電型ウェルとの間の接合面に形成される。 20

#### 【0007】

そして本発明では、第J、第Kの保護回路の接続ノードである中間ノードに、第1、第2の寄生ダイオードの両方が寄生するように、第J、第Kの保護回路が接続される。従って、寄生ダイオードの経路が伝搬経路になった場合と伝送経路にならない場合とで、第1、第2の電源ノード間でのダイオードの段数を同じ段数にすることができる、寄生ダイオードがノイズ伝搬経路になる事態を防止できる。従って、トリプルウェル構造の回路において、サージ、ノイズ等の悪影響を効果的に低減できる

また本発明では、前記第1のダイオードは、第1の第2導電型拡散領域とその下の第1の第1導電型ウェルとの間の接合面に形成され、前記第2のダイオードは、第1の第1導電型拡散領域とその下の第1の第2導電型ウェルとの間の接合面に形成され、前記第3のダイオードは、第2の第2導電型拡散領域とその下の第2の第1導電型ウェルとの間の接合面に形成され、前記第4のダイオードは、第2の第1導電型拡散領域とその下の第2の第2導電型ウェルとの間の接合面に形成されるようにしてもよい。 30

#### 【0008】

このようにすれば、トリプルウェル構造の回路に好適な第J、第Kの保護回路を実現できる。

#### 【0009】

また本発明では、第3の電源ノードと前記中間ノードとの間に設けられる第Lの保護回路を含み、前記第Lの保護回路は、前記第3の電源ノードと前記中間ノードとの間に設けられ、前記第3の電源ノードから前記中間ノードへの方向を順方向とする第5のダイオードと、前記第3の電源ノードと前記中間ノードとの間に設けられ、前記中間ノードから前記第3の電源ノードへの方向を順方向とする第6のダイオードと、前記第2の電源ノードと前記中間ノードとの間に設けられ、前記第2の電源ノードから前記中間ノードへの方向を順方向とし、トリプルウェル構造を構成する第2導電型基板とその上の第3の第1導電型ウェルとの間の接合面に形成される第3の寄生ダイオードとを含むようにしてもよい。 40

#### 【0010】

このようにすれば、第J、第K、第Lの保護回路の接続ノードである中間ノードに、第1、第2、第3の寄生ダイオードの全てが寄生するように、第J、第K、第Lの保護回路が接続されるようになる。従って、寄生ダイオードの経路が伝搬経路になった場合と伝送

経路にならない場合とで、第1、第2、第3の電源ノード間でのダイオードの段数を同じ段数にすることができる、寄生ダイオードがノイズ伝搬経路になる事態を防止できる。

**【0011】**

また本発明では、前記第5のダイオードは、第3の第2導電型拡散領域とその下の第3の第1導電型ウェルとの間の接合面に形成され、前記第6のダイオードは、第3の第1導電型拡散領域とその下の第3の第2導電型ウェルとの間の接合面に形成されるようにしてもよい。

**【0012】**

このようにすれば、トリプルウェル構造の回路に好適な第J、第K、第Lの保護回路を実現できる。

10

**【0013】**

また本発明では、シリアルバスを介してデータ転送を行う物理層回路を含む高速インターフェース回路ブロックと、少なくとも1つの他の回路ブロックとを含み、前記高速インターフェース回路ブロックは、前記高速インターフェース回路ブロックの電源と前記他の回路ブロックの電源との間に設けられる保護回路を含む第1、第2の保護回路ブロックを含み、前記第1の保護回路ブロックは、前記第Jの保護回路である第1の保護回路と、前記第Lの保護回路である第2の保護回路と、前記第Kの保護回路である第3の保護回路を含み、前記第2の保護回路ブロックは、前記第Jの保護回路である第4の保護回路と、前記第Lの保護回路である第5の保護回路と、前記第Kの保護回路である第6の保護回路を含み、前記第1の保護回路ブロックは、前記高速インターフェース回路ブロックの短辺である第1の辺側に配置され、前記第2の保護回路ブロックは、前記高速インターフェース回路ブロックの前記第1の辺に対向する第3の辺側に配置されるようにしてもよい。

20

**【0014】**

本発明によれば、高速インターフェース回路ブロックの第1の辺側に第1の保護回路ブロックが配置され、第2の辺側に第2の保護回路ブロックが配置される。従って、他の回路ブロックの電源からの静電気が第1の辺側から到来した場合には、第1の保護回路ブロックにより静電気破壊等を防止でき、他の回路ブロックの電源からの静電気が第2の辺側から到来した場合には、第2の保護回路ブロックにより静電気破壊等を防止できる。従って、高速インターフェース回路を組み込んだ場合にも静電気破壊等を効果的に防止でき、集積回路装置の信頼性を向上できる。

30

**【0015】**

また本発明では、前記物理層回路は、前記第1、第2の保護回路ブロックの間に配置されるようにしてもよい。

**【0016】**

このようにすれば、物理層回路のトランジスタ等が破壊されるのを、物理層回路の両サイドに配置された第1、第2の保護回路ブロックにより効果的に防止できる。

**【0017】**

また本発明では、前記高速インターフェース回路ブロックは、前記物理層回路と、ロジック回路を含み、前記高速インターフェース回路ブロックの前記第1の辺から前記第3の辺へと向かう方向を第1の方向とし、前記高速インターフェース回路ブロックの長辺である第2の辺から対向する第4の辺へと向かう方向を第2の方向とした場合に、前記ロジック回路は、前記物理層回路の前記第2の方向側に配置されるようにしてもよい。

40

**【0018】**

このようにすれば、信号の流れに沿った効率的なレイアウトが可能になる。

**【0019】**

また本発明では、前記他の回路ブロックとして、表示制御信号を生成するドライバ用ロジック回路ブロックを含み、前記ドライバ用ロジック回路ブロックは、前記ロジック回路の前記第2の方向側に配置されるようにしてもよい。

**【0020】**

このようにすれば、ロジック回路、ドライバ用ロジック回路ブロック間の配線をショート

50

トパスで接続できるようになり、レイアウト効率を向上できる。

【0021】

また本発明では、前記物理層回路の前記第1の方向での長さをL1とし、前記ロジック回路の前記第1の方向での長さをL2とした場合に、L2 > L1であってもよい。

【0022】

このようにすればロジック回路、ドライバ用ロジック回路ブロック間の信号配線領域の幅を広くすることができ、配線をショートパスで接続できるようになる。

【0023】

また本発明では、前記第1の方向の反対方向を第3の方向とした場合に、前記物理層回路の前記第3の方向側の第1の領域に前記第1の保護回路ブロックが配置され、前記物理層回路の前記第1の方向側の第2の領域に前記第2の保護回路ブロックが配置されるよう 10 にしてもよい。

【0024】

このようにすれば、物理層回路の第3の方向側の空き領域である第1の領域や第1の方向側の空き領域である第2の領域を有効活用できる。

【0025】

また本発明では、前記第1、第2の領域に、前記高速インターフェース回路ブロックの高電位側電源と低電位側電源の間に設けられるキャパシタが形成されるキャパシタ領域が配置されるようにしてよい。

【0026】

このようにすれば、第1、第2の領域を有効活用して電源の安定化を図れる。

【0027】

また本発明では、前記高速インターフェース回路ブロックは、前記物理層回路と、ロジック回路と、共用電源の電源線を含み、前記第1の保護回路ブロックは、前記第1の電源ノードである前記物理層回路の電源と、前記中間ノードである前記共用電源との間に設けられる前記第1の保護回路と、前記第3の電源ノードである前記ロジック回路の電源と、前記共用電源との間に設けられる前記第2の保護回路と、前記第2の電源ノードである前記他の回路ブロックの電源と、前記共用電源との間に設けられる前記第3の保護回路を含み、前記第2の保護回路ブロックは、前記物理層回路の電源と前記共用電源との間に設けられる前記第4の保護回路と、前記ロジック回路の電源と前記共用電源との間に設けられる前記第5の保護回路と、前記他の回路ブロックの電源と前記共用電源との間に設けられる前記第6の保護回路を含むようにしてよい。 30

【0028】

このようにすれば、物理層回路の電源、ロジック回路の電源、他の回路ブロックの電源と、共用電源との間に、1段の保護回路が配置されるようになる。従って、一部の経路においてのみ静電気耐圧やノイズ耐性が低下してしまう事態を防止できる。

【0029】

また本発明では、前記高速インターフェース回路ブロックの前記第1の辺から前記第3の辺へと向かう方向を第1の方向とし、前記第1の方向の反対方向を第3の方向とした場合に、前記第1の保護回路の前記第3の方向側に前記第2の保護回路が配置され、前記第4の保護回路の前記第1の方向側に前記第5の保護回路が配置されるようにしてよい。 40

【0030】

このようにすれば、物理層回路やロジック回路に供給する電源の電源線の効率的な配線が可能になる。

【0031】

また本発明では、前記第1の保護回路と前記物理層回路を接続する第1の電源線の前記第3の方向側に、前記第2の保護回路と前記ロジック回路を接続する第2の電源線が配線され、前記第4の保護回路と前記物理層回路を接続する第4の電源線の前記第1の方向側に、前記第5の保護回路と前記ロジック回路を接続する第5の電源線が配線されるようにしてよい。

10

20

30

40

50

**【0032】**

このようにすれば、第1、第2の電源線が交差して配線されたり、第4、第5の電源線が交差して配線される事態を防止でき、レイアウト効率を向上できる。

**【0033】**

また本発明は、上記のいずれかに記載の集積回路装置と、前記集積回路装置により駆動される表示パネルとを含む電子機器に関するもの。

**【発明を実施するための最良の形態】****【0034】**

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。10

**【0035】****1. 保護回路**

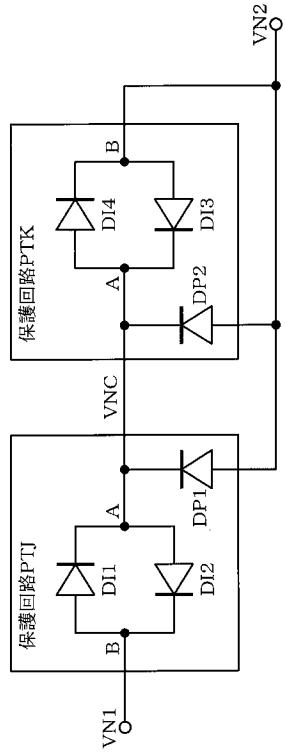

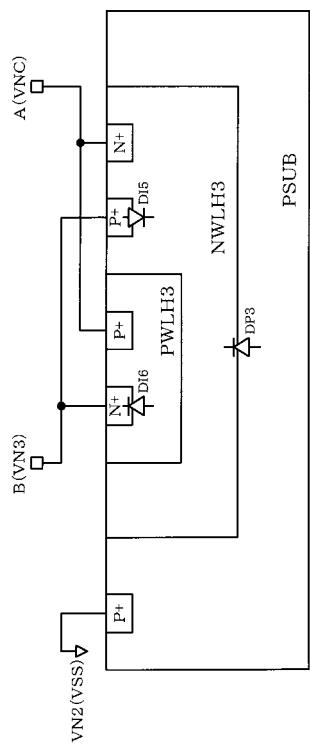

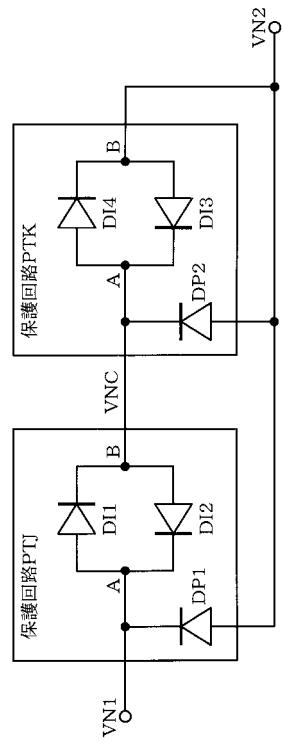

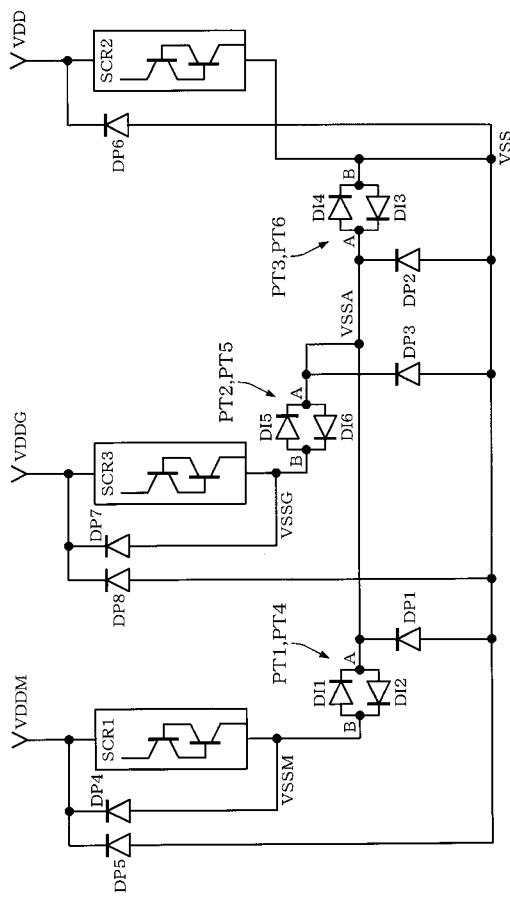

図1に、本実施形態の集積回路装置（半導体装置）が含む保護回路の構成例を示す。なお本実施形態の保護回路は図1の構成に限定されず、図1に示されるもの以外の構成要素を設けるなどの種々の変形実施が可能である。

**【0036】**

本実施形態の集積回路装置は、第1の電源ノードVN1と中間ノードVNC（共用電源ノード、ダミー電源ノード）との間に設けられる第Jの保護回路PTJと、第2の電源ノードVN2と中間ノードVNCとの間に設けられる第Kの保護回路PTKを含む。なおJ、Kは異なる自然数である。20

**【0037】**

保護回路PTJは、ダイオードDI1、DI2により構成される双方向ダイオードを含む。具体的には、電源ノードVN1（B端子）と中間ノードVNC（A端子）との間に設けられ、VN1からVNCへの方向を順方向とする第1のダイオードDI1を含む。また電源ノードVN1と中間ノードVNCとの間に設けられ、VNCからVN1への方向を順方向とする第2のダイオードDI2を含む。更に、電源ノードVN2と中間ノードVNCとの間に設けられ、VN2からVNCへの方向を順方向とする第1の寄生ダイオードDP1を含む。この寄生ダイオードDP1は、トリプルウェル構造を構成するP型基板（広義には第2導電型基板）とその上のN型ウェル（広義には第1の第1導電型ウェル）との間の接合面に形成される。30

**【0038】**

保護回路PTKは、ダイオードDI3、DI4により構成される双方向ダイオードを含む。具体的には、電源ノードVN2（B端子）と中間ノードVNC（A端子）との間に設けられ、VN2からVNCへの方向を順方向とする第3のダイオードDI3を含む。またVN2とVNCとの間に設けられ、VNCからVN2への方向を順方向とする第4のダイオードDI4を含む。更に、VN2とVNCとの間に設けられ、VN2からVNCへの方向を順方向とする第2の寄生ダイオードDP2を含む。この寄生ダイオードDP2は、トリプルウェル構造を構成するP型基板（第2導電型基板）とその上のN型ウェル（広義には第2の第1導電型ウェル）との間の接合面に形成される。40

**【0039】**

このような双方向ダイオードにより保護回路を形成すれば、静電保護の機能とノイズ除去の機能を保護回路に持たせることができる。例えば電源ノードVN1とVN2の間に正極性又は負極性の静電気電圧が印加された場合にも、保護回路PTJ、PTKの双方向ダイオードが放電経路になって静電気が放電されるため、トランジスタの静電気破壊が防止される。また電源ノードVN2にノイズが乗った場合にも、保護回路PTJ、PTKの双方向ダイオードによりノイズが除去されて、電源ノードVN1にノイズが伝わらないようになる。同様に電源ノードVN1にノイズが乗った場合にも、保護回路PTJ、PTKの双方向ダイオードによりノイズが除去されて、電源ノードVN2にノイズが伝わらないようになる。例えばダイオードの順方向電圧が0.6Vである場合には、1.50

2 V 以下のノイズは伝わらないようになる。

#### 【0040】

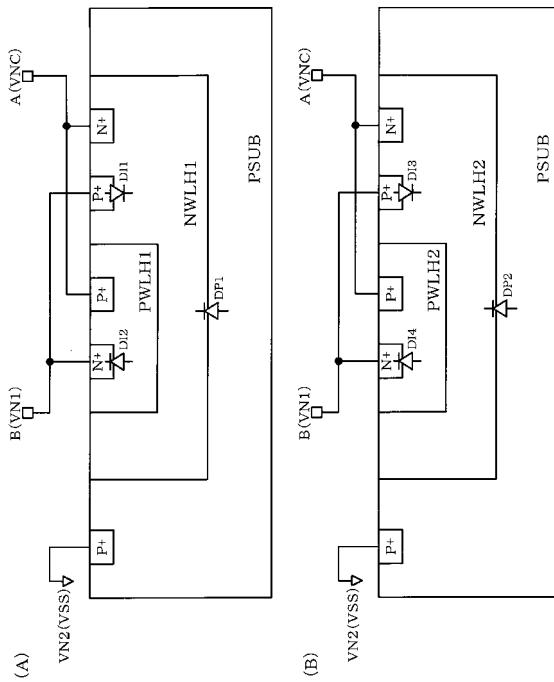

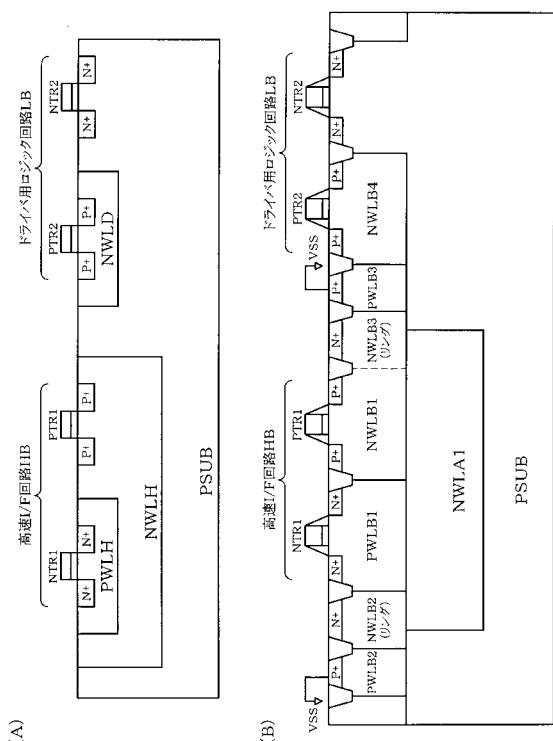

図2(A)(B)は、保護回路PTJ、PTKを構成するダイオードの縦構造を模式的に示す断面図である。図2(A)では、P型基板PSUB(第2導電型基板)に、P型ウェルPWLH1を囲むようにN型ウェルNWLH1が形成される。そしてダイオードDI1は、P+領域(広義には第1の第2導電型拡散領域)とその下のN型ウェルNWLH1(広義には第1の第1導電型ウェル)との間の接合面(PN接合)に形成される。またダイオードDI2は、N+領域(広義には第1の第1導電型拡散領域)とその下のP型ウェルPWLH1(広義には第1の第2導電型ウェル)との間の接合面に形成される。そして寄生ダイオードDP1は、P型基板PSUBとその上のN型ウェルNWLH1との間の接合面に形成される。

10

#### 【0041】

図2(B)では、P型基板PSUBに、P型ウェルPWLH2を囲むようにN型ウェルNWLH2が形成されている。そしてダイオードDI3は、P+領域(広義には第2の第2導電型拡散領域)とその下のN型ウェルNWLH2(広義には第2の第1導電型ウェル)との間の接合面に形成される。またダイオードDI4は、N+領域(広義には第2の第1導電型拡散領域)とその下のP型ウェルPWLH2(広義には第2の第2導電型ウェル)との間の接合面に形成される。このようにダイオードDI3は、ダイオードDI1が形成されるN型ウェルNWLH1とは分離形成されたN型ウェルNWLH2に形成される。またダイオードDI4は、ダイオードDI2が形成されるP型ウェルPWLH1とは分離形成されたP型ウェルPWLH2に形成される。そして寄生ダイオードDP2は、P型基板PSUBとその上のN型ウェルNWLH2との間の接合面に形成される。

20

#### 【0042】

なお図3に、ダイオードが形成されるトリプルウェル構造の詳細例を示す。図3のPWLB1は図2(A)のPWLH1に相当し、図3のNWLB1は図2(A)のNWLH1に相当する。

#### 【0043】

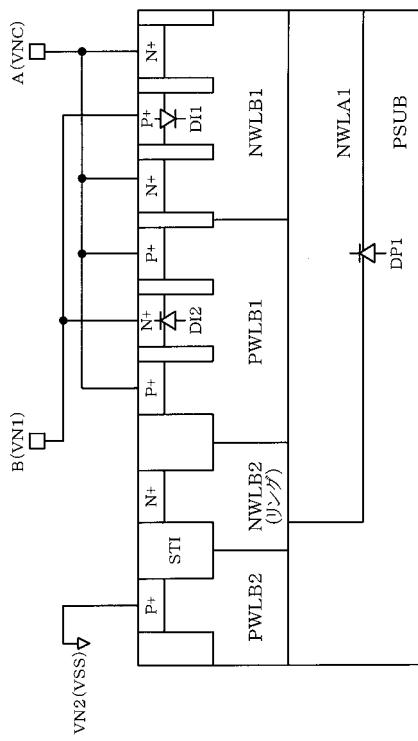

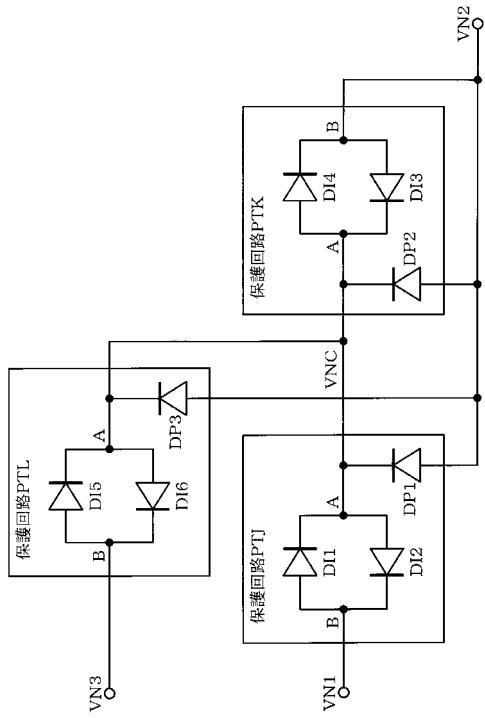

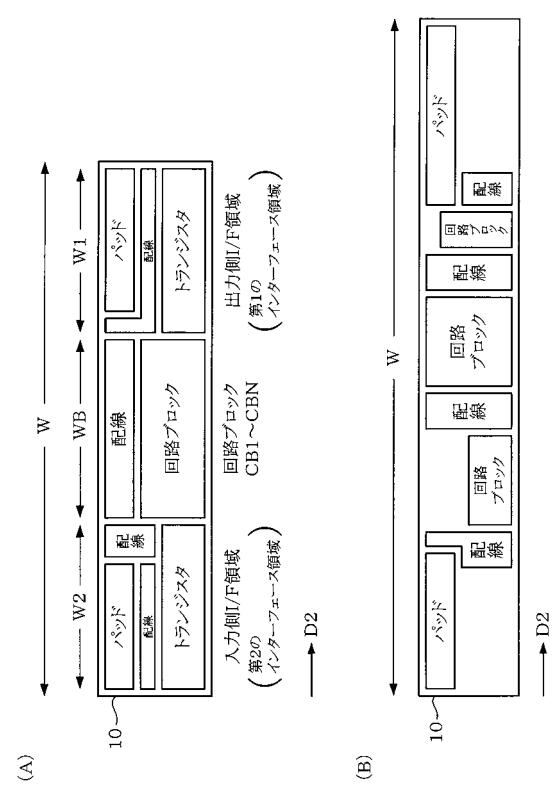

図4に電源の数が更に増えた場合の構成例を示す。図4では集積回路装置は、第3の電源ノードVN3と中間ノードVNCとの間に設けられる第Lの保護回路PTLを含む。なお、LはJ、Kとは異なる自然数である。

30

#### 【0044】

保護回路PTLは、ダイオードDI5、DI6により構成される双方向ダイオードを含む。具体的には、電源ノードVN3(B端子)と中間ノードVNC(A端子)との間に設けられ、VN3からVNCへの方向を順方向とする第5のダイオードDI5を含む。またVN3とVNCとの間に設けられ、VNCからVN3への方向を順方向とする第6のダイオードDI6を含む。更に、VN2とVNCとの間に設けられ、VN2からVNCへの方向を順方向とする第3の寄生ダイオードDP3を含む。この寄生ダイオードDP3は、トリプルウェル構造を構成するP型基板(第2導電型基板)とその上のN型ウェル(広義には第3の第1導電型ウェル)との間の接合面に形成される。なお図4には、3つの保護回路を設けた場合を示しているが、4つ以上の保護回路を設けるようにしてもよい。

40

#### 【0045】

図5に、保護回路PTLを構成するダイオードの断面図を示す。図5では、P型基板PSUBに、P型ウェルPWLH3を囲むようにN型ウェルNWLH6が形成されている。そしてダイオードDI5は、P+領域(広義には第3の第2導電型拡散領域)とその下のN型ウェルNWLH3(広義には第3の第1導電型ウェル)との間の接合面に形成される。またダイオードDI6は、N+領域(広義には第3の第1導電型拡散領域)とその下のP型ウェルPWLH3(広義には第3の第2導電型ウェル)との間の接合面に形成される。このようにダイオードDI5は、ダイオードDI1、DI3が形成されるN型ウェルNWLH1、NWLH2とは分離形成されたN型ウェルNWLH3に形成される。またダイオードDI6は、ダイオードDI2、DI4が形成されるP型ウェルPWLH1、PWL

50

H 2 とは分離形成された P 型ウェル P W L H 3 に形成される。そして寄生ダイオード D P 3 は、P 型基板 P S U B とその上の N 型ウェル N W L H 3 との間の接合面に形成される。

#### 【 0 0 4 6 】

図 2 ( A ) ( B )、図 5 に示すように、保護回路 P T J、P T K、P T L の A 端子には、各々、寄生ダイオード D P 1、D P 2、D P 3 が寄生する。そして図 1、図 4 では、このような寄生ダイオードが形成される保護回路 P T J、P T K、P T L の A 端子同士を接続するようにしている。具体的には図 1 では、保護回路 P T J、P T K の A 端子同士を、中間ノード V N C を介して接続している。また図 4 では、保護回路 P T J、P T K、P T L の A 端子同士を、中間ノード V N C を介して接続している。

#### 【 0 0 4 7 】

このように接続すれば、寄生ダイオード D P 1、D P 2、D P 3 は、A 端子である中間ノード V N C にだけ寄生するようになる。従って、寄生ダイオードの経路が伝搬経路になつた場合と伝送経路にならない場合とで、電源ノード V N 1、V N 2 間のダイオードの段数、V N 2、V N 3 間のダイオードの段数、V N 3、V N 1 間のダイオードの段数を、同じ段数（例えば 2 段）にすることができ、寄生ダイオードがノイズ伝搬経路になつてしまふ事態を防止できる。

#### 【 0 0 4 8 】

例えば図 6 に本実施形態の比較例を示す。図 6 では、保護回路 P T J の B 端子と保護回路 P T K の A 端子が接続される。従って、この比較例では図 6 に示すように、寄生ダイオード D P 1 が、電源ノード V N 1、V N 2 間に形成されてしまう。従って、寄生ダイオード D P 1 の順方向電圧が 0.6 V であったとすると、0.6 V より大きいノイズは除去されずに、電源ノード V N 1、V N 2 間で伝搬してしまう。

#### 【 0 0 4 9 】

これに対して図 1 では、保護回路 P T J、P T K の A 端子同士が接続される。従って、寄生ダイオード D P 1 は V N C、V N 2 間に形成され、V N 1、V N 2 間には形成されない。従って、ダイオード D I 2、D I 3 の経路でのダイオードの段数のみならず、ダイオード D I 2、寄生ダイオード D P 1 の経路でのダイオードの段数や、ダイオード D I 2、寄生ダイオード D P 2 の経路でのダイオードの段数も、2 段になる。従って、ダイオードの順方向電圧が 0.6 V である場合に、1.2 V 以下のノイズが電源ノード V N 1、V N 2 間で伝搬してしまう事態を効果的に防止できる。

#### 【 0 0 5 0 】

### 2 . 集積回路装置の回路構成

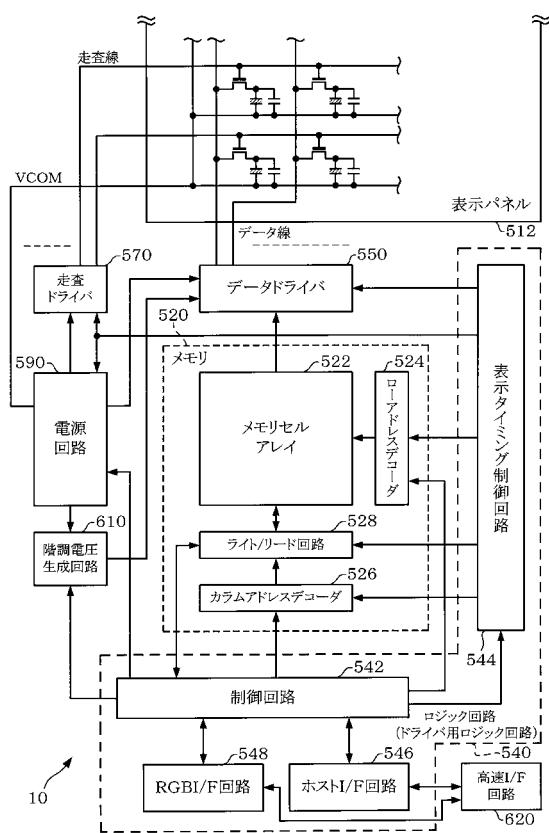

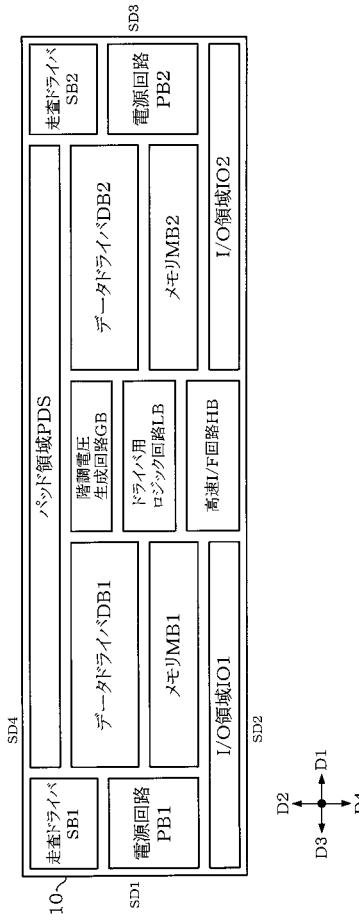

図 7 に本実施形態の集積回路装置 10 が表示ドライバである場合の回路構成例を示す。なお集積回路装置 10 の回路構成は図 7 に限定されず、種々の変形実施が可能である。例えば図 7 の構成要素の一部を省略したり、図 7 に示されるもの以外の構成要素を含んでいてもよい。また本実施形態の集積回路装置は、表示ドライバには限定されず、ベースバンドエンジン、アプリケーションプロセッサ、画像処理コントローラなどのホストデバイスなどであつてもよい。

#### 【 0 0 5 1 】

表示パネル 512 は、複数のデータ線（ソース線）と、複数の走査線（ゲート線）と、データ線及び走査線により特定される複数の画素を有する。そして各画素領域における電気光学素子（狭義には、液晶素子）の光学特性を変化させることで、表示動作を実現する。この表示パネル 512 は、TFT、TFT などのスイッチング素子を用いたアクティブマトリクス方式のパネルにより構成できる。なお表示パネル 512 は、アクティブマトリクス方式以外のパネルであつてもよいし、液晶パネル以外のパネル（有機ELパネル等）であつてもよい。

#### 【 0 0 5 2 】

メモリ 520 (RAM) は画像データを記憶する。メモリセルアレイ 522 は複数のメモリセルを含み、少なくとも 1 フレーム（1 画面）分の画像データ（表示データ）を記憶する。このメモリ 520 は、ロードアドレスデコーダ 524 (MPU/LCD ロードアドレス

10

20

30

40

50

デコーダ)、カラムアドレスデコーダ526(MPUカラムアドレスデコーダ)、ライト/リード回路528(MPUライト/リード回路)を含む。

#### 【0053】

ロジック回路540(ドライバ用ロジック回路)は、表示タイミングやデータ処理タイミングを制御するための表示制御信号を生成する。このロジック回路540は例えばゲートアレイ(G/A)などの自動配置配線により形成できる。制御回路542は各種制御信号を生成したり、装置全体の制御を行う。表示タイミング制御回路544は表示タイミングの制御信号を生成し、メモリ520から表示パネル512側への画像データの読み出しを制御する。ホストI/F(インターフェース)回路546は、ホスト(MPU)からのアクセス毎に内部パルスを発生してメモリ520にアクセスするホストインターフェースを実現する。RGBI/F回路548は、ドットクロックにより動画のRGBデータをメモリ520に書き込むRGBインターフェースを実現する。高速I/F回路620はシリアルバスを介した高速シリアル転送を実現する。

#### 【0054】

データドライバ550は、表示パネル512のデータ線を駆動するためのデータ信号を生成する。具体的にはデータドライバ550は、メモリ520から画像データである階調データを受け、階調電圧生成回路610から複数(例えば64段階)の階調電圧(基準電圧)を受ける。そして、これらの複数の階調電圧の中から、階調データに対応する電圧を選択して、データ信号(データ電圧)として表示パネル512の各データ線に出力する。

#### 【0055】

走査ドライバ570は表示パネルの走査線を駆動するための走査信号を生成する。電源回路590は各種の電源電圧を生成し、データドライバ550、走査ドライバ570、階調電圧生成回路610等に供給する。階調電圧生成回路610(補正回路)は階調電圧を生成し、データドライバ550に出力する。

#### 【0056】

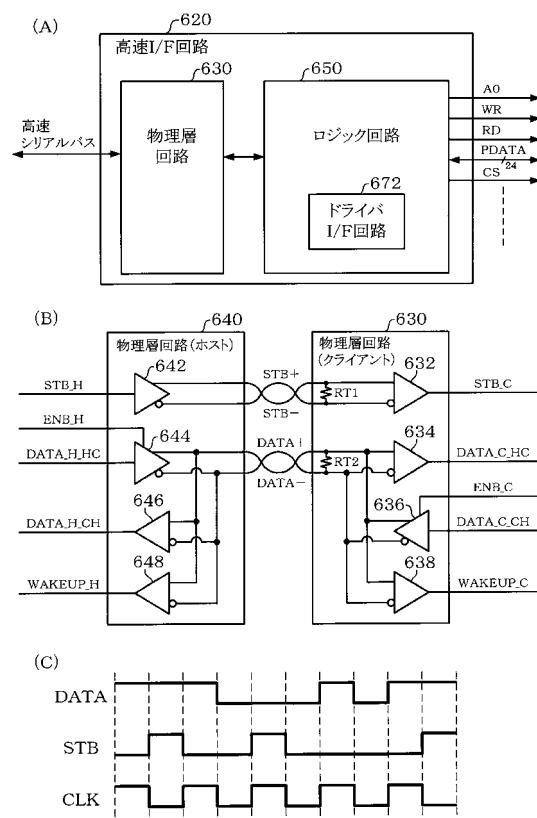

##### 3. 高速I/F回路の構成

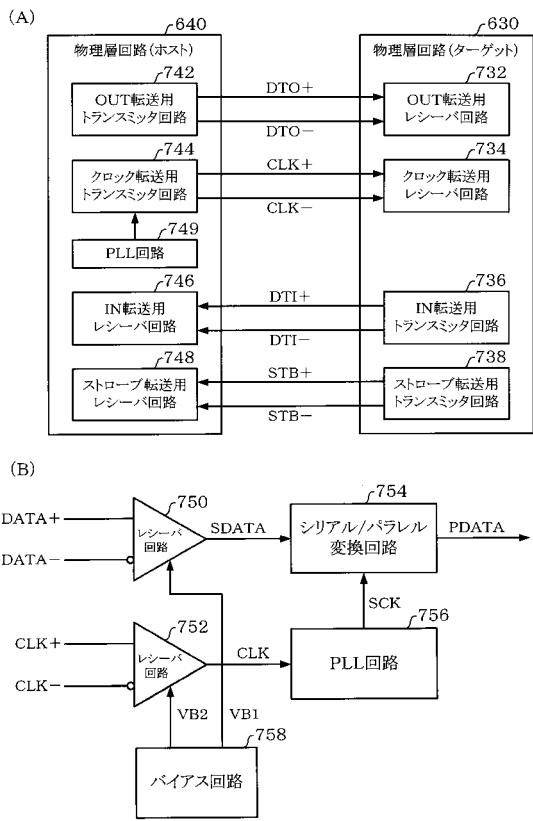

図8(A)に高速I/F(インターフェース)回路620の構成例を示す。物理層回路630(アナログフロントエンド回路、トランシーバ)は、差動信号(差動データ信号、差動ストローブ信号、差動クロック信号)等を用いたシリアルバスを介してデータ(パケット)を受信したり、送信するための回路である。具体的にはシリアルバスの差動信号線を電流駆動又は電圧駆動することによりデータの送受信が行われる。この物理層回路630は、シリアルバスを介してデータを受信するレシーバ回路及びシリアルバスを介してデータを送信するトランスミッタ回路の少なくとも一方を含むことができる。

#### 【0057】

なおシリアルバスは多チャンネル構成のものであってもよい。またシングルエンド転送でシリアル転送を行ってもよい。また物理層回路630は高速ロジック回路を含むことができる。この高速ロジック回路は、シリアルバスの転送クロックに相当する高速クロックで動作する回路である。具体的には物理層回路630は、シリアルバスを介して受信したシリアルデータをパラレルデータに変換するシリアル/パラレル変換回路、シリアルバスを介して送信するシリアルデータにパラレルデータを変換するパラレル/シリアル変換回路、 FIFO、エラスティシティバッファ、或いは分周回路などを含むことができる。

#### 【0058】

ロジック回路650は高速I/F回路620が内蔵するロジック回路であり、物理層の上層であるリンク層やトランザクション層の処理を行う。例えばシリアルバスを介して物理層回路630が受信したパケットを解析し、パケットのヘッダとデータを分離して、ヘッダを抽出する。また、シリアルバスを介してパケットを送信する場合には、そのパケットの生成処理を行う。このロジック回路650は例えばゲートアレイ(G/A)などの自動配置配線により形成できる。

#### 【0059】

ロジック回路650はドライバI/F回路672を含む。ドライバI/F回路672は

10

20

30

40

50

、高速 I / F 回路 620 と表示ドライバの内部回路（図 7 のドライバ用ロジック回路 540、ホスト I / F 回路 546）との間のインターフェース処理を行う。具体的にはドライバ I / F 回路 672 は、アドレス 0 信号 A0（コマンド / データ識別信号）、ライト信号 W R、リード信号 R D、パラレルデータ信号 P D A T A、チップセレクト信号 C Sなどを含むインターフェース信号を生成して、表示ドライバの内部回路（他の回路ブロック）に出力する。

#### 【0060】

図 8 (B) に物理層回路の構成例を示す。図 8 (B) において、物理層回路 640 はホストデバイスに内蔵され、物理層回路 630 は表示ドライバに内蔵される。また 636、642、644 はトランスミッタ回路であり、632、634、646 はレシーバ回路である。また 638、648 はウェイクアップ検出回路である。ホスト側のトランスミッタ回路 642 は S T B + / - を駆動する。そしてクライアント側のレシーバ回路 632 は、駆動により抵抗 R T 1 の両端に発生した電圧を増幅し、ストローブ信号 S T B \_ C を後段の回路に出力する。またホスト側のトランスミッタ回路 644 は D A T A + / - を駆動する。そしてクライアント側のレシーバ回路 634 は、駆動により抵抗 R T 2 の両端に発生した電圧を増幅し、データ信号 D A T A \_ C \_ H C を後段の回路に出力する。

#### 【0061】

図 8 (C) に示すように送信側は、データ信号 D A T A とクロック信号 C L K の排他的論理和をとることで、ストローブ信号 S T B を生成し、この S T B を高速シリアルバスを介して受信側に送信する。そして受信側は、受信したデータ信号 D A T A とストローブ信号 S T B の排他的論理和をとることで、クロック信号 C L K を再生する。

#### 【0062】

なお物理層回路の構成は図 8 (B) に限定されず、例えば図 9 (A) (B) に示すような種々の変形実施が可能である。

#### 【0063】

例えば図 9 (A) の第 1 の変形例において、ホスト側は差動クロック信号 C L K + / - のエッジに同期して差動データ信号 (OUT データ) D T O + / - を出力する。従ってターゲット側は、C L K + / - を用いて D T O + / - をサンプリングして取り込むことができる。またターゲット側はホスト側から供給された差動クロック信号 C L K + / - に基づいて差動ストローブ信号 S T B + / - を生成して出力する。そしてターゲット側は S T B + / - のエッジに同期して差動データ信号 (IN データ) D T I + / - を出力する。従ってホスト側は、S T B + / - を用いて D T I + / - をサンプリングして取り込むことができる。

#### 【0064】

また図 9 (B) の第 2 の変形例において、データ用のレシーバ回路 750 は差動データ信号 D A T A + / - を受信し、得られたシリアルデータ S D A T A をシリアル / パラレル変換回路 754 に出力する。クロック用のレシーバ回路 752 は差動クロック信号 C L K + / - を受信し、得られたクロック C L K を後段の P L L (Phase Locked Loop) 回路 756 に出力する。P L L 回路 756 は、クロック C L K に基づいてサンプリングクロック S C K (周波数が同一で位相が互いに異なる多相のサンプリングクロック) を生成し、シリアル / パラレル変換回路 754 に出力する。シリアル / パラレル変換回路 754 は、サンプリングクロック S C K を用いて、シリアルデータ S D A T A をサンプリングし、パラレルデータ P D A T A を出力する。

#### 【0065】

例えば携帯電話機などでは、M P U、B B E / A P P、画像処理コントローラなどのホストデバイスは、電話番号入力や文字入力のためのボタンが設けられる携帯電話機の第 1 の機器部分の第 1 の回路基板に実装される。また表示ドライバは、表示パネル (L C D) やカメラデバイスが設けられる携帯電話機の第 2 の機器部分の第 2 の回路基板に実装される。

#### 【0066】

10

20

30

40

50

そして従来は、ホストデバイス、表示ドライバの間でのデータ転送は、C M O S電圧レベルのパラレル転送により実現していた。このため、第1、第2の機器部分を接続するヒンジなどの接続部分を通る配線の本数が多くなって、設計の自由度を妨げたり、E M Iノイズが発生するなどの問題があった。

#### 【0067】

これに対して図8(A)～図9(B)では、ホストデバイス、表示ドライバ間でのデータ転送は小振幅のシリアル転送により実現される。従って第1、第2の機器部部分の接続部分を通る配線の本数を減らすことができると共にE M Iノイズの発生を低減できる。

#### 【0068】

##### 4. 保護回路ブロック

10

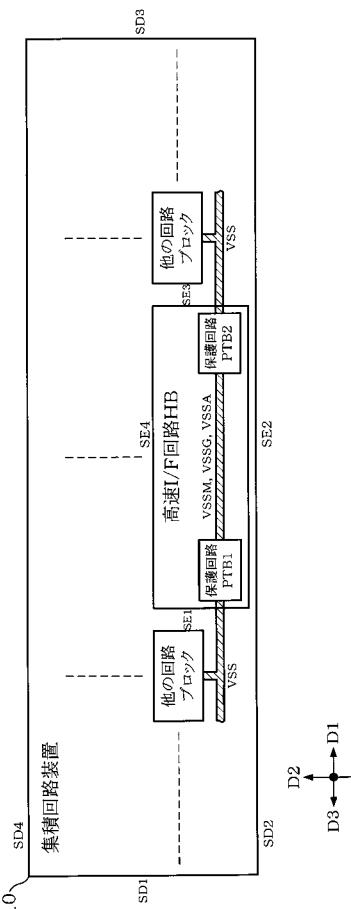

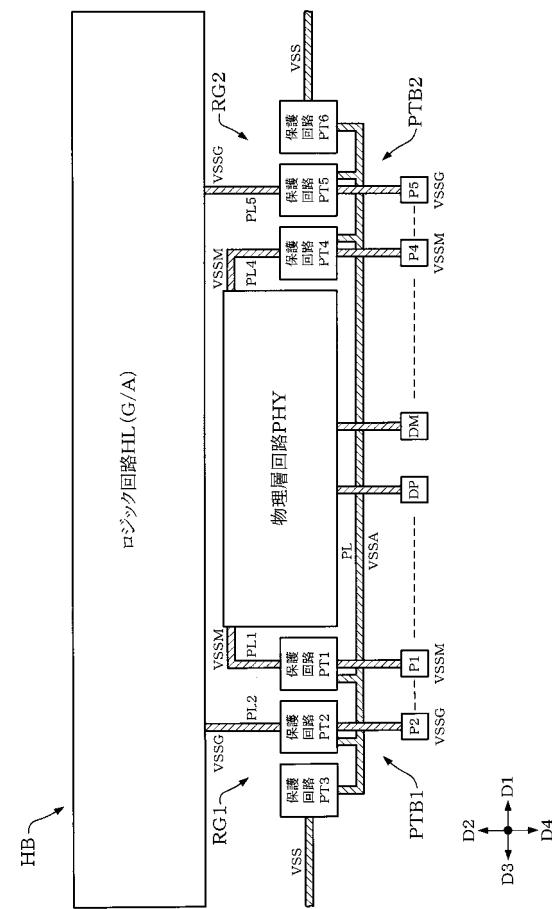

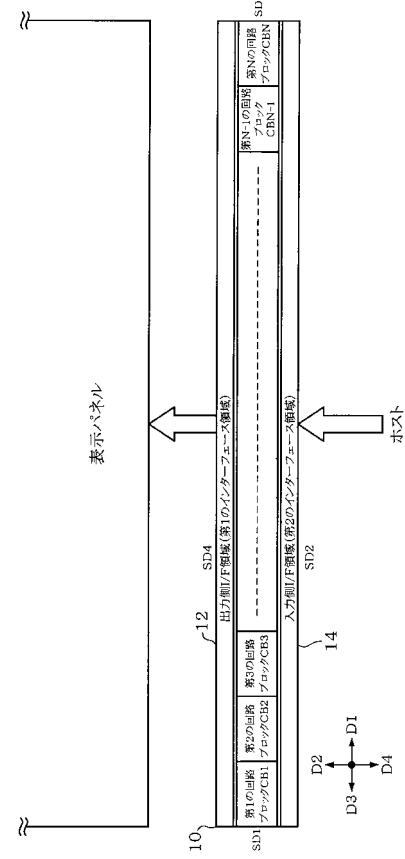

図10に集積回路装置10のレイアウト例を示す。集積回路装置10は、高速I/F回路ブロックHBと、少なくとも1つの他の回路ブロック(HB以外の回路ブロック)を含む。ここで他の回路ブロックとは、データドライバブロックである。或いはドライバ(表示ドライバ)用ロジック回路ブロックや電源回路ブロックや階調電圧生成回路ブロックである。或いはメモリ内蔵の場合にはメモリブロックであり、アモルファスTFT用の場合には走査ドライバブロックである。

#### 【0069】

高速I/F回路ブロックHBは第1、第2の保護回路ブロック(保護回路領域)PTB1、PTB2を含む。この保護回路ブロックPTB1、PTB2の各々は、高速I/F回路ブロックHBの電源(低電位電源)VSSM、VSSG又はVSSAと、他の回路ブロックの電源(低電位電源)VSSとの間に設けられる少なくとも1つの保護回路を含む。

20

#### 【0070】

そして保護回路ブロックPTB1は、高速I/F回路ブロックHBの第1の辺SE1側に配置され、保護回路ブロックPTB2は、HBの辺SE1に対向する第3の辺SE3側に配置される。即ちHBの両サイドにPTB1、PTB2が配置される。例えば図10において、高速I/F回路ブロックHBの短辺である第1の辺SE1から対向する第3の辺SE3へと向かう方向を第1の方向D1とし、D1の反対方向を第3の方向D3としたとする。またHBの長辺である第2の辺SE2から対向する第4の辺SE4へと向かう方向を第2の方向D2とし、D2の反対方向を第4の方向D4としたとする。そして高速I/F回路ブロックHBのD2方向に沿った中心線を想定すると、保護回路ブロックPTB1はこの中心線のD3方向側に配置され、保護回路ブロックPTB2はこの中心線のD1方向側に配置される。なお図10ではHBの左辺が第1の辺SE1で、右辺が第3の辺SE3になっているが、左辺が第3の辺SE3で、右辺が第1の辺SE1であってもよい。

30

#### 【0071】

図10の配置によれば異種電源間に静電気電圧が印加された場合に、高速I/F回路ブロックHB内のトランジスタ等の静電気破壊を効果的に防止できる。例えばドライバ用電源VSSとHB用の電源VSSM又はVSSG等の間に静電気電圧が印加された場合に、PTB1、PTB2の保護回路(双方向ダイオード等)が静電気の放電経路になることで、トランジスタの静電気破壊が防止される。

#### 【0072】

40

特に、高速I/F回路ブロックHBは、D1方向での長さが長い細長のブロックになっている。従って、保護回路ブロックをHBの中央付近に配置すると、保護回路により静電気放電が行われる前に、HB内のトランジスタが破壊されてしまうおそれがある。

#### 【0073】

この点、図10では、保護回路ブロックPTB1、PTB2が高速I/F回路ブロックHBの両サイドに配置されている。従ってVSSからの静電気を、HBの両サイドの位置である入り口部分で放電することが可能になるため、HB内のトランジスタが静電気破壊される事態を効果的に防止できる。

#### 【0074】

なお保護回路ブロックPTB1、PTB2の各々は、異種電源(VSSM、VSSG、

50

VSSA、VSS) 間の保護回路を少なくとも 1 つを含めばよい。またこれらの保護回路は近くの場所に配置してもよいし、離れた場所に配置してもよい。

#### 【0075】

また高速 I / F 回路では、信号の反射を防止するために送信側と受信側とでインピーダンス整合をとっている。ところが、集積回路装置をガラス基板に COG (Chip On Glass) 実装すると、集積回路装置の両端部のバンプでの接触抵抗が上昇してしまう。即ち集積回路装置とガラス基板の熱膨張係数は異なる。従って、熱膨張係数の差によって生じる応力(熱ストレス)は、集積回路装置の両端部の方が中央部よりも大きくなる。このため、両端部では、バンプでの接触抵抗が時間経過につれて上昇してしまう。従って高速 I / F 回路の受信用パッド又は送信用パッド (DATA+/-等) として、集積回路装置の両端部のバンプに接続されるパッドを使用すると、バンプでの接触抵抗の上昇によって、インピーダンス整合が崩れてしまい、高速シリアル転送の信号品質が劣化する。10

#### 【0076】

この点、図 10 では、高速 I / F 回路ブロック HB が、集積回路装置 10 の両端を除く中央付近に配置される。具体的には集積回路装置 10 の辺 S D 1 と高速 I / F 回路ブロック HB (HB の辺 S E 1)との間に、HB 以外の他の回路ブロックが配置される。また集積回路装置 10 の辺 S D 3 と HB (HB の辺 S E 3)との間に、HB 以外の他の回路ブロックが配置される。このようにすれば、高速 I / F 回路ブロック HB は、集積回路装置 10 の両端に配置されないようになる。従って、接触抵抗の上昇を原因とするインピーダンス不整合を低減でき、高速シリアル転送の信号品質の劣化を低減できる。20

#### 【0077】

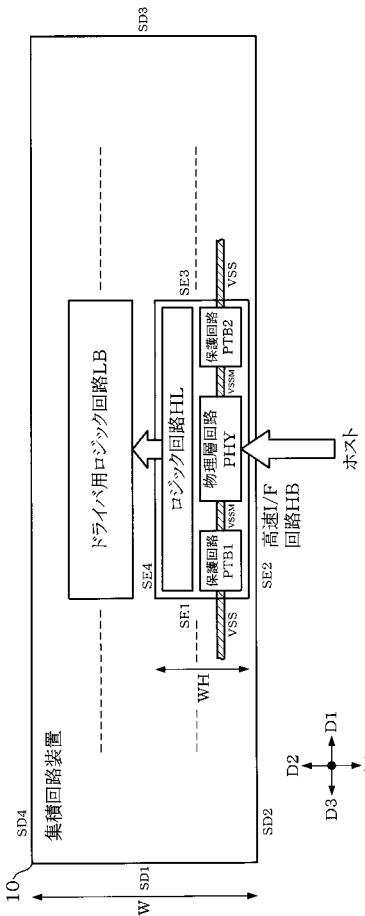

##### 5. 集積回路装置、高速 I / F 回路ブロック詳細なレイアウト例

図 11 に集積回路装置 10、高速 I / F 回路ブロック HB の詳細なレイアウト例を示す。図 11 では、HB が含む物理層回路 PHY が、保護回路ブロック PTB 1、PTB 2 の間に配置される。即ち PHY の D 3 方向側に PTB 1 が配置され、PHY の D 1 方向側に PTB 2 が配置される。このようにすれば、電源 VSS からの静電気が、HB の両サイドの PTB 1、PTB 2 の保護回路で放電され、PTB 1、PTB 2 の間の物理層回路 PHY のトランジスタが破壊されるのを効果的に防止できる。また電源 VSS からのノイズが物理層回路 PHY に伝達されるのも効果的に防止できる。なお、PTB 1、PTB 2 を物理層回路 PHY の両サイドに配置しない変形実施も可能である。例えば PTB 1、PTB 2 をロジック回路 HL の両サイドに配置してもよい。30

#### 【0078】

また図 11 に示すように、高速 I / F 回路ブロック HB は、物理層回路 PHY とロジック回路 HL (図 8 (A) の 650) を含む。このロジック回路 HL は、リンク層やトランザクション層の処理を行ったり、ドライバ回路とのインターフェース処理を行う回路である。そしてロジック回路 HL が物理層回路 PHY の D 2 方向側 (辺 S E 2 から S E 4 へと向かう方向側) に配置される。更に集積回路装置 10 が、高速 I / F 回路ブロック HB 以外の他の回路ブロックとして、表示制御信号を生成するドライバ用ロジック回路ブロック LB (図 7 の 540) を含む。そしてドライバ用ロジック回路ブロック LB がロジック回路 HL の D 2 方向側に配置される。40

#### 【0079】

図 11において物理層回路 PHY はホストデバイスからのシリアルのデータ(画像データ)を受け、パラレルのデータに変換してロジック回路 HL に出力する。そしてロジック回路 HL は、図 8 (A) に示すようなホストインターフェース信号 (A0、WR、RD、PDATA 等) を生成してドライバ用ロジック回路ブロック LB に出力する。このように信号の流れは D 2 方向になる。このため図 11 では、この信号の流れに合わせて、物理層回路 PHY の D 2 方向側にロジック回路 HL を配置すると共に HL の D 2 方向側にドライバ用ロジック回路ブロック LB を配置している。このようにすることで、入力と出力の間がショートパスになり、信号遅延を最適化でき、効率の良い信号伝達が可能になる。

#### 【0080】

10

20

30

40

50

また図11のように配置すれば、高速I/F回路ブロックHBのD1方向の長さを長くすることで、D2方向でのHBの幅WHを小さくできる。そしてHBの幅WHが小さくなると、集積回路装置10のD2方向での幅Wも小さくでき、チップのスリム化を図れる。これにより実装を容易化できる。

#### 【0081】

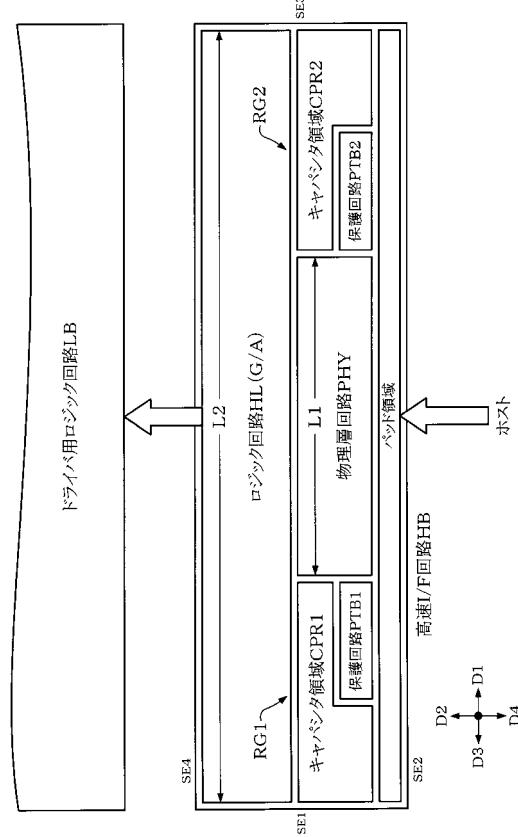

図12に高速I/F回路ブロックHBの更に詳細なレイアウト例を示す。図12において、物理層回路PHYのD1方向での長さをL1とし、ロジック回路HLのD1方向での長さをL2とすると、 $L_2 > L_1$ の関係が成り立つ。即ち長辺方向の長さは、物理層回路PHYよりもロジック回路HLの方が長い。そして図12では、物理層回路PHYのD3方向側の空き領域である第1の領域RG1に保護回路ブロックPTB1が配置され、PHYのD1方向側の空き領域である第2の領域RG2に保護回路ブロックPTB2が配置される。更に領域RG1、RG2にはキャパシタ領域CPR1、CPR2が配置される。このキャパシタ領域CPR1、CPR2には、高速I/F回路ブロックHBの電源を安定化するためのキャパシタが形成される。即ち高速I/F回路ブロックHBの高電位側電源(VDD)と低電位側電源(VSS)の間に設けられるキャパシタが形成される。このキャパシタは、ゲートアレイ(G/A)のベーシックセルのゲート容量などをを利用して形成できる。

#### 【0082】

ロジック回路HLとドライバ用ロジック回路LBの間には、データ信号、制御信号などの多数の信号が配線される。従って、HL、LB間の信号配線領域(インターフェース領域)はなるべく広いことが望ましい。

#### 【0083】

この点、図12では、ロジック回路HLのD2方向側にドライバ用ロジック回路ブロックLBが配置されると共に、HLのD1方向での長さL2が長くなっている。従ってロジック回路HLとドライバ用ロジック回路ブロックLBとの間の信号配線領域のD1方向の長さも広くできる。即ち信号配線領域のD1方向での長さをL2にできる。従って例えば信号線の配線ピッチをPTHとした場合には、HLとLBの間で(L2/PTH)本の信号線を配線できる。またHLとLBの間の配線をショートパスで接続できるようになり、信号配線領域のD2方向での幅を小さくできる。この結果、集積回路装置10のD2方向での幅Wも小さくでき、チップのスリム化を図れ、実装を容易化できる。

#### 【0084】

また物理層回路PHYの長さL1よりもロジック回路HLの長さL2を長くすると、PHYの両サイドに空き領域RG1、RG2ができる。

#### 【0085】

この点、図12では、この空き領域RG1、RG2に保護回路ブロックPTB1、PTB2やキャパシタ領域CPR1、CPR2を配置している。従って、 $L_2 > L_1$ としたことで形成された空き領域RG1、RG2を有効利用して、保護回路ブロックPTB1、PTB2等を配置できる。即ち、HL、LB間の効率的な配線によるD2方向での幅W、WHの縮小と、PHYの両サイドにPTB1、PTB2を配置することによる静電気耐圧、ノイズ耐性の向上を両立できる。また空き領域RG1、RG2にはキャパシタ領域CPR1、CPR2が形成されるため、電源を安定化でき、ノイズ耐性等を更に向上できる。

#### 【0086】

図13に集積回路装置10の詳細なレイアウト例を示す。集積回路装置10は、高速I/F回路ブロックHB、ドライバ用ロジック回路ブロックLBを含む。また階調電圧を生成する階調電圧生成回路ブロックGBと、生成された階調電圧に基づいて表示パネルのデータ線を駆動するデータドライバブロックDB1、DB2を含む。また階調データである画像データを記憶するメモリブロックMB1、MB2と、表示パネルの走査線を駆動する走査ドライバブロックSB1、SB2と、電源を生成する電源回路ブロックPB1、PB2を含む。更にI/O領域IO1、IO2、パッド領域PDS(データ線、走査線のパッドの領域)を含む。

10

20

30

40

50

**【 0 0 8 7 】**

図13に示すように高速I/F回路ブロックHBとドライバ用ロジック回路ブロックLBは隣接して配置される。具体的には、辺SD2から辺SD4に向かう方向をD2方向とした場合に、D2方向に沿ってHB、LBが隣接して配置される。またLBと階調電圧生成回路ブロックGBも隣接して配置される。具体的にはLBとGBもD2方向に沿って隣接して配置される。

**【 0 0 8 8 】**

また図13では、階調電圧生成回路ブロックGBとデータドライバブロックDB1、DB2が隣接して配置される。具体的には、辺SD1から辺SD3に向かう方向をD1方向とした場合に、GBとDB1、DB2はD1方向に沿って隣接して配置される。

10

**【 0 0 8 9 】**

例えば階調電圧生成回路ブロックGBは図示しない調整レジスタを含む。そしてこの調整レジスタには、階調電圧の振幅調整、階調特性の傾き調整、階調特性の微調整などを行うための調整データが、ドライバ用ロジック回路ブロックLBにより設定される。このような調整データを設定することで、表示パネルの種類に応じた最適な階調特性（特性）を得ることができ、表示品質を向上できる。

**【 0 0 9 0 】**

しかしながら、このような調整を行うための調整データのビット数は非常に多い。このため、ドライバ用ロジック回路ブロックLBから階調電圧生成回路ブロックGBへの調整データの信号線の本数も多い。従ってLBとGBを隣接して配置しないと、調整データの信号線のための配線領域が原因となってチップ面積が増加するおそれがある。

20

**【 0 0 9 1 】**

この点、図13では、ドライバ用ロジック回路ブロックLBと階調電圧生成回路ブロックGBはD2方向に沿って隣接して配置される。従って、LBからの調整データの信号線をショートパスでGBに接続できるため、配線領域を原因とするチップ面積の増加を防止できる。

**【 0 0 9 2 】**

またデータドライバブロックDB1、DB2は図示しないD/A変換回路を含む。そしてこのD/A変換回路は、階調電圧生成回路ブロックGBからの複数の階調電圧を受ける。そしてこれらの階調電圧の中から階調データに対応した電圧を選択することで、階調データのD/A変換を行う。従って、階調電圧生成回路ブロックGBからデータドライバブロックDB1、DB2への階調電圧の信号線の本数も多い。従ってGBとDB1、DB2とを隣接して配置しないと、階調電圧の信号線のための配線領域が原因となってチップ面積が増加するおそれがある。

30

**【 0 0 9 3 】**

この点、図13では、階調電圧生成回路ブロックGBとデータドライバブロックDB1、DB2はD1方向に沿って隣接して配置される。従って、GBからの階調電圧の信号線をショートパスでDB1、DB2に接続できるため、配線領域を原因とするチップ面積の増加を防止できる。

**【 0 0 9 4 】**

40

**6 . 保護回路の配置**

図14に保護回路ブロックPTB1、PTB2が含む保護回路のレイアウト例を示す。図14に示すように高速I/F回路ブロックHBは、物理層回路PHYと、ロジック回路HLと、共用電源VSSA(ESSD用ダミー電源)の電源線PLを含む。この電源線PLは、高速I/F回路ブロックHB内において例えばD1方向に沿って配線される。

**【 0 0 9 5 】**

そして保護回路ブロックPTB1は、物理層回路PHYの電源VSSMと共に電源VSSAとの間に設けられる保護回路PT1を含む。またロジック回路HLの電源VSSGと共に電源VSSAとの間に設けられる保護回路PT2や、他の回路ブロック(ドライバ用ロジック回路ブロック等)の電源VSSと共に電源VSSAとの間に設けられる保護回路

50

P T 3 を含む。

**【 0 0 9 6 】**

また保護回路ブロック P T B 2 は、電源 V S S M と共に電源 V S S A との間に設けられる保護回路 P T 4 を含む。また電源 V S S G と共に電源 V S S A との間に設けられる保護回路 P T 5 や、電源 V S S と共に電源 V S S A との間に設けられる保護回路 P T 6 を含む。

**【 0 0 9 7 】**

ここで、図 14 の V S S M 、 V S S 、 V S S G は、各々、図 4 の第 1 、第 2 、第 3 の電源ノード V N 1 、 V N 2 、 V N 3 に相当する。また図 14 の V S S A は図 4 の中間ノード V N C に相当する。また図 14 の第 1 、第 4 の保護回路 P T 1 、 P T 4 は図 4 の第 J の保護回路 P T J に相当し、第 2 、第 5 の保護回路 P T 2 、 P T 5 は第 L の保護回路 P T L に相当し、第 3 、第 6 の保護回路 P T 3 、 P T 6 は第 K の保護回路 P T K に相当する。

10

**【 0 0 9 8 】**

なお図 14において物理層回路 P H Y がシリアル / パラレル変換回路などの高速ロジック回路を含む場合には、この高速ロジック回路用の電源を設けてもよい。この場合には、保護回路ブロック P T B 1 、 P T B 2 の各々に、高速ロジック回路用の電源と電源 V S S A との間に設けられる保護回路を更に含ませればよい。

**【 0 0 9 9 】**

図 14 では、保護回路 P T 1 の D 3 方向側に保護回路 P T 2 が配置され、保護回路 P T 4 の D 1 方向側に保護回路 P T 5 が配置される。また、保護回路 P T 2 の D 3 方向側に保護回路 P T 3 が配置され、保護回路 P T 5 の D 1 方向側に保護回路 P T 6 が配置される。

20

**【 0 1 0 0 】**

また図 14 では、保護回路 P T 1 と物理層回路 P H Y を接続する第 1 の電源線 P L 1 の D 3 方向側に、保護回路 P T 2 とロジック回路 H L を接続する第 2 の電源線 P L 2 が配線される。同様に、保護回路 P T 4 と物理層回路 P H Y を接続する第 4 の電源線 P L 4 の D 1 方向側に、保護回路 P T 5 とロジック回路 H L を接続する第 5 の電源線 P L 5 が配線される。

**【 0 1 0 1 】**

具体的には電源線 P L 1 、 P L 4 は、物理層回路 P H Y に接続するために、保護回路 P T 1 、 P T 4 から D 2 方向に沿って配線された後、 D 1 方向又は D 3 方向に屈曲されて配線される。これらの P L 1 、 P L 4 は、パッド ( 電極 ) P 1 、 P 4 からの電源 V S S M を物理層回路 P H Y に供給するための電源線である。

30

**【 0 1 0 2 】**

また電源線 P L 2 、 P L 5 は、ロジック回路 H L に接続するために、保護回路 P T 2 、 P T 5 から D 2 方向に沿って配線される。これらの P L 2 、 P L 5 は、パッド P 2 、 P 5 からの電源 V S S G をロジック回路 H L に供給するための電源線である。

**【 0 1 0 3 】**

また図 14 では、電源線 P L 1 が接続されるパッド P 1 が、保護回路 P T 1 の D 4 方向側に配置され、電源線 P L 2 が接続されるパッド P 2 が、保護回路 P T 2 の D 4 方向側に配置される。即ちパッド P 2 がパッド P 1 の D 3 方向側に配置される。同様に電源線 P L 4 が接続されるパッド P 4 が、保護回路 P T 4 の D 4 方向側に配置され、電源線 P L 5 が接続されるパッド P 5 が、保護回路 P T 5 の D 4 方向側に配置される。即ちパッド P 5 がパッド P 4 の D 1 方向側に配置される。

40

**【 0 1 0 4 】**

また図 14 では物理層回路 P H Y の受信用のパッド D P 、 D M ( 或いは送信用パッドであってもよい ) が設けられる。これらの D P 、 D M は、図 8 ( A ) ~ 図 9 ( B ) で説明した差動データ信号 ( DATA + / - 、 DTO + / - ) 用のパッドである。そして図 14 では、これらのパッド D P 、 D M がパッド P 1 とパッド P 4 の間に配置される。

**【 0 1 0 5 】**

図 14 の配置によれば、外部の他の回路ブロックの電源 V S S からの静電気を、物理層

50

回路 P H Y の両サイドに配置された保護回路により効率的に放電できる。従って物理層回路 P H Y 等のトランジスタが破壊される事態を効果的に防止できる。

#### 【0106】

また図14では、電源VSSAの電源線PLがD1方向に沿って配線され、電源VSSM、VSSGの電源線PL1、PL2、PL4、PL5がD2方向に沿って配線される。従って、電源線PL1、PL2、PL4、PL5の各々と電源線PLとの交差位置付近に、保護回路PT1、PT2、PT4、PT5を配置できるようになり、効率的なレイアウトを実現できる。

#### 【0107】

また図14では電源線PL1とPL2を交差させずに配線でき、電源線PL4とPL5も交差させずに配線できる。従って、空き領域RG1、RG2を利用して、十分な太さの電源線PL1、PL2、PL4、PL5を配線できるようになり、物理層回路PHY、ロジック回路HLに供給される電源VSSM、VSSGの安定化を図れる。更に、領域RG1、RG2にキャパシタ領域CPR1、CPR2を形成し、そのキャパシタの一端を電源線に接続するようにすれば、電源の更なる安定化を図れる。

#### 【0108】

##### 7. トリプルウェル構造

本実施形態では、以下に説明するように、トリプルウェル構造を有効活用してノイズの悪影響を低減している。

#### 【0109】

即ち図15(A)に示すように、高速I/F回路ブロックHBが含むN型トランジスタ(広義には第1導電型トランジスタ)NTR1は、P型ウェル(広義には第2導電型ウェル)PWLHに形成される。また高速I/F回路ブロックHBが含むP型トランジスタ(広義には第2導電型トランジスタ)PTR1は、P型ウェルPWLHを囲むようにP型基板PSUBに形成されたN型ウェルNWLHに形成される。

#### 【0110】

一方、ドライバ用ロジック回路ブロックLB(ドライバ回路)が含むN型トランジスタNTR2、P型トランジスタPTR2は、高速I/F回路ブロックHB用のN型ウェルNWLHには形成されず、NWLHの領域以外の領域に形成される。具体的にはP型トランジスタPTR2は、HB用のNWLHとは分離されたN型ウェルNWLDに形成され、N型トランジスタNTR2は、P型基板PSUBに形成される。このようにすれば、高速I/F回路ブロックHBを構成するトランジスタNTR1、PTR1と、ドライバ用ロジック回路ブロックLBを構成するトランジスタNTR2、PTR2とを、トリプルウェル構造のN型ウェルNWLHにより分離できる。これにより、N型ウェルNWLHを障壁にして、HB、LB間でのノイズ伝達を防止できる。従って、LBが発生するノイズの悪影響をHB(PHY)が受けにくくなり、シリアル転送の伝送品質を維持できる。またHBが発生するノイズの悪影響をLB等が受けにくくなり、誤動作の発生等を防止できる。なおLBのトランジスタNTR2、PTR2をトリプルウェル構造で実現してもよい。

#### 【0111】

図15(B)にトリプルウェル構造の詳細例を示す。図15(B)のN型ウェルNWLA1、NWLB1、NWLB2、NWLB3が、図15(A)のN型ウェルNWLHに相当する。また図15(B)のP型ウェルPWLB1が、図15(A)のP型ウェルPWLHに相当する。また図15(B)のN型ウェルNWLB4が、図15(A)のN型ウェルNWLDに相当する。

#### 【0112】

図15(B)においてNWLA1は深いウェルになっており、NWLB1、NWLB2、NWLB3、NWLB4は浅いウェルになっている。またNWLB2、NWLB3はリング状に形成されている。これにより、P型ウェルPWLB1を囲むようにN型ウェルを形成できる。またP型ウェルPWLB2、PWLB3には、VSSの電源線に電気的に接続されるP+領域(広義には第2導電型拡散領域)が形成されている。このようなP型ウ

10

20

30

40

50

エルPWL B 2、PWL B 3やP+領域を設けることで、P型基板PSUBの電位を安定化でき、ノイズ耐性を向上できる。

#### 【0113】

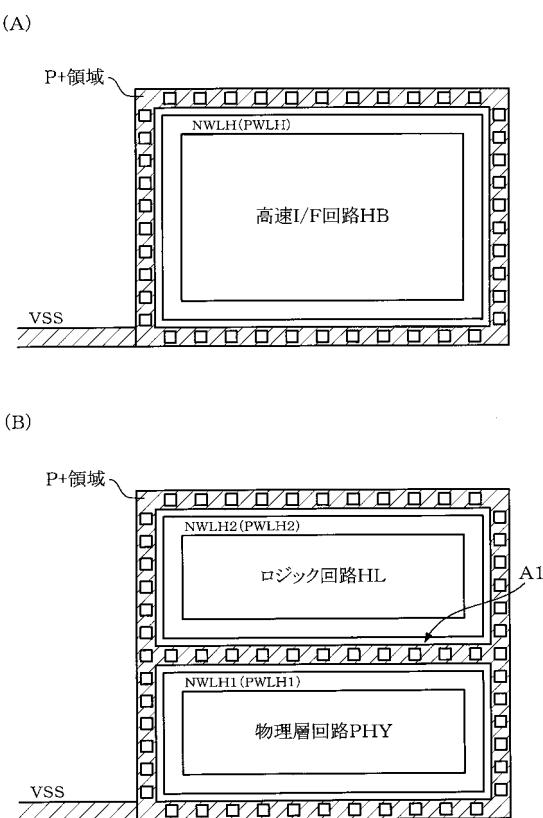

基板電位安定化用のP+領域(第2導電型拡散領域)は、例えば図16(A)(B)で説明する手法により形成できる。

#### 【0114】

図16(A)では、ドライバ用ロジック回路ブロックLBの電源VSSに電気的に接続される基板電位安定化用のP+領域が、高速I/F回路ブロックHBを囲むようにリング状にP型基板PSUBに形成されている。即ちコンタクトによりVSSの電源線に電気的に接続されたP+領域のガードリングが、HBが形成されるN型ウェルNWLHの周囲を囲むように形成されている。このようにすれば、N型ウェルNWLHの周縁のP型基板PSUBの電位が安定化されるため、HBで発生したノイズがLB等に伝達するのを効果的に防止できる。10

#### 【0115】

また図16(B)では、HBが含む物理層回路PHYは、トリプルウェル構造のN型ウェルNWLH1に形成され、ロジック回路HLは、NWLH1と分離して形成されたトリプルウェル構造のN型ウェルNWLH2に形成される。具体的にはPHYを構成するN型トランジスタは、P型ウェルPWLH1に形成される。またPHYを構成するP型トランジスタは、PWLH1を囲むようにPSUBに形成されたN型ウェルNWLH1に形成される。20

#### 【0116】

一方、ロジック回路HLを構成するN型トランジスタは、P型ウェルPWLH2に形成される。またHLを構成するP型トランジスタは、PWLH2を囲むようにPSUBに形成されたN型ウェルNWLH2に形成される。

#### 【0117】

図16(B)のようにすれば、物理層回路PHYとロジック回路HLが、トリプルウェル構造の別ウェルに形成される。従ってHLで発生したノイズの悪影響をPHYが受けにくくなり、シリアル転送の伝送品質を維持できる。またPHYで発生したノイズの悪影響もHLが受けにくくなり、誤動作の発生等を防止できる。またHLが形成されるN型ウェルNWLH2が障壁となって、物理層回路PHYとドライバ用ロジック回路ブロックLBとの間でのノイズ伝達も低減できる。30

#### 【0118】

また図16(B)では、VSSの電源線が、高速I/F回路ブロックHB内に配線される。即ち、HBの周縁のみならず、図16(B)のA1に示すようにHBの内部にもVSSの電源線が配線される。そして、このように配線されたVSSに接続されるP+領域が、N型ウェルNWLH1とNWLH2の間のP型基板PSUBに形成される。

#### 【0119】

このようにすれば、N型ウェルNWLH1、NWLH2の間に介在するP型基板PSUBについても、そこに形成されるP+領域によりその電位が安定化される。従って、HLで発生したノイズがPHYに伝達しにくくなると共に、PHYで発生したノイズもHLに伝達しにくくなる。また、このようにVSSの電源線を配線すれば、HB用の電源VSSM、VSSG等とVSSとの間の保護回路についても効率良くレイアウトできるようになり、レイアウトの効率化と信頼性の向上を両立できる。40

#### 【0120】

なおHB内のN型ウェルやP+領域の形成手法は図16(A)(B)に限定されない。例えばPHYのアナログ回路が形成されるN型ウェルと、PHYの高速ロジック回路が形成されるN型ウェルとを別ウェルにしてもよい。このようにすれば、ノイズ耐性を更に向上できる。

#### 【0121】

8 . 双方向ダイオード

10

20

30

40

50

図17に示すように、保護回路PT1～PT6は双方向ダイオード(整流素子)などにより構成できる。例えば保護回路PT1、PT4は、各々、ダイオードDI1、DI2により構成される双方向ダイオードを含む。具体的には、VSSMの電源ノード(第1の電源ノード)とVSSAの電源ノード(中間ノード)との間に設けられ、VSSMからVSSAへの方向を順方向とする第1のダイオードDI1を含む。またVSSMの電源ノードとVSSAの電源ノードとの間に設けられ、VSSAからVSSMへの方向を順方向とする第2のダイオードDI2を含む。更に、VSSの電源ノード(第2の電源ノード)とVSSAの電源ノードとの間に設けられ、VSSからVSSAへの方向を順方向とする第1の寄生ダイオードDP1を含む。

## 【0122】

10

保護回路PT3、PT6は、各々、VSSとVSSAの間に設けられ、VSSからVSSAへの方向を順方向とする第3のダイオードDI3と、VSSとVSSAの間に設けられ、VSSAからのVSSへの方向を順方向とする第4のダイオードDI4を含む。更に、VSSとVSSAの間に設けられ、VSSからVSSAへの方向を順方向とする第2の寄生ダイオードDP2を含む。

## 【0123】

保護回路PT2、PT5は、各々、VSSGとVSSAの間に設けられ、VSSGからVSSAへの方向を順方向とする第5のダイオードDI5を含む。またVSSGとVSSAの間に設けられ、VSSAからのVSSGへの方向を順方向とする第6のダイオードDI6を含む。更に、VSSとVSSAの間に設けられ、VSSからVSSAへの方向を順方向とする第3の寄生ダイオードDP3を含む。

20

## 【0124】

なお図17に示すように、VDDMとVSSMの間、VDDとVSSの間、VDDGとVSSGの間には、各々、サイリスタSCR1、SCR2、SCR3が設けられている。またVDDMとVSSMの間、VDDGとVSSGの間には、各々、寄生ダイオードDP4、DP7が形成される。更にVDDM、VDD、VDDGとVSSとの間には、寄生ダイオードDP5、DP6、DP8が形成される。

## 【0125】

## 9. 細長の集積回路装置

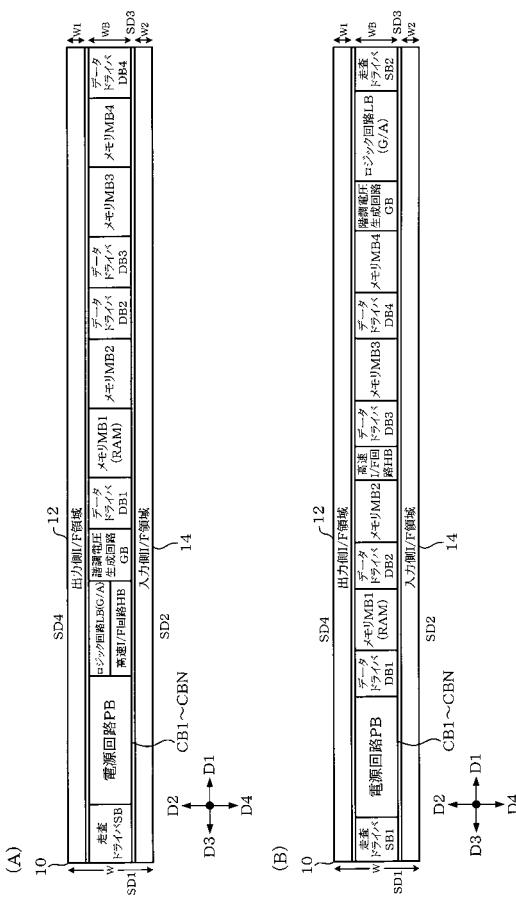

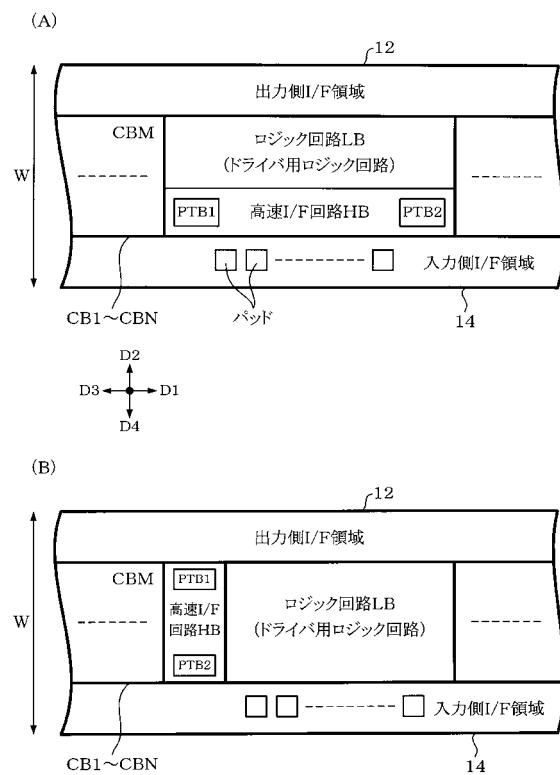

図18に集積回路装置10のレイアウトの変形例を示す。この集積回路装置10は、D1方向に沿って配置される第1～第Nの回路ブロックCB1～CBN(Nは2以上の整数)を含む。また集積回路装置10は、第1～第Nの回路ブロックCB1～CBNのD2方向側に辺SD4に沿って設けられる出力側I/F領域12(広義には第1のインターフェース領域)を含む。また第1～第Nの回路ブロックCB1～CBNのD4方向側に辺SD2に沿って設けられる入力側I/F領域14(広義には第2のインターフェース領域)を含む。より具体的には、出力側I/F領域12(第1のI/O領域)は、回路ブロックCB1～CBNのD2方向側に、例えば他の回路ブロック等を介さずに配置される。また入力側I/F領域14(第2のI/O領域)は、回路ブロックCB1～CBNのD4方向側に、例えば他の回路ブロック等を介さずに配置される。

30

## 【0126】

40

出力側(表示パネル側)I/F領域12は、表示パネルとのインターフェースとなる領域であり、パッドや、パッドに接続される出力用トランジスタ、保護素子などの種々の素子を含む。具体的には、データ線へのデータ信号や走査線への走査信号を出力するための出力用トランジスタなどを含む。なお表示パネルがタッチパネルである場合等には、入力用トランジスタを含んでもよい。

## 【0127】

入力側(ホスト側)I/F領域14は、ホストとのインターフェースとなる領域であり、パッドや、パッドに接続される入力用(入出力用)トランジスタ、出力用トランジスタ、保護素子などの種々の素子を含むことができる。具体的には、ホストからの信号(デジタル信号)を入力するための入力用トランジスタやホストへの信号を出力するための出力

50

用トランジスタなどを含む。

**【0128】**

なお、短辺である辺 S D 1、S D 3 に沿った出力側又は入力側 I / F 領域を設けるようにしてもよい。また外部接続端子となるバンプ等は、I / F (インターフェース) 領域 12、14 に設けてもよいし、それ以外の領域 (第 1 ~ 第 N の回路ブロック C B 1 ~ C B N ) に設けてもよい。I / F 領域 12、14 以外の領域に設ける場合には、金バンプ以外の小型バンプ技術 (樹脂をコアとするバンプ技術など) を用いることで実現される。

**【0129】**

また第 1 ~ 第 N の回路ブロック C B 1 ~ C B N は、少なくとも 2 つ (或いは 3 つ) の異なる回路ブロック (異なる機能を持つ回路ブロック) を含むことができる。集積回路装置 10 が表示ドライバである場合を例にとれば、回路ブロック C B 1 ~ C B N は、データドライバ、メモリ、走査ドライバ、ロジック回路、階調電圧生成回路、電源回路のブロックの少なくとも 2 つを含むことができる。

**【0130】**

図 19 (A) (B) に集積回路装置 10 の平面レイアウトの詳細例を示す。図 19 (A) (B)において、第 1 ~ 第 N の回路ブロック C B 1 ~ C B N は、第 1 ~ 第 4 のメモリブロック M B 1 ~ M B 4 (広義には第 1 ~ 第 I のメモリブロック。I は 2 以上の整数) を含む。また第 1 ~ 第 4 のメモリブロック M B 1 ~ M B 4 の各々に対して、D 1 方向に沿ってその各々が隣接して配置される第 1 ~ 第 4 のデータドライバブロック D B 1 ~ D B 4 (広義には第 1 ~ 第 I のデータドライバブロック) を含む。具体的にはメモリブロック M B 1 とデータドライバブロック D B 1 が D 1 方向に沿って隣接して配置され、メモリブロック M B 2 とデータドライバブロック D B 2 が D 1 方向に沿って隣接して配置される。そしてデータドライバブロック D B 1 がデータ線を駆動するために用いる画像データ (表示データ) は、隣接するメモリブロック M B 1 が記憶し、データドライバブロック D B 2 がデータ線を駆動するために用いる画像データは、隣接するメモリブロック M B 2 が記憶する。

**【0131】**

なお本実施形態の集積回路装置 10 のレイアウト配置は図 19 (A) (B) に限定されない。例えばメモリブロックやデータドライバブロックのブロック数を 2、3 或いは 5 以上にしてもよいし、メモリブロックやデータドライバブロックをブロック分割しない構成にしてもよい。またメモリブロックとデータドライバブロックが隣接しないようにする変形実施も可能である。またメモリブロック、走査ドライバブロック、電源回路ブロック又は階調電圧生成回路ブロックなどを設けない構成としてもよい。また回路ブロック C B 1 ~ C B N と出力側 I / F 領域 12 や入力側 I / F 領域 14 の間に、D 2 方向での幅が極めて狭い回路ブロック (W B 以下の細長回路ブロック) を設けてもよい。また回路ブロック C B 1 ~ C B N が、異なる回路ブロックが D 2 方向に多段に並んだ回路ブロックを含んでもよい。例えば走査ドライバ回路と電源回路を 1 つの回路ブロックとした構成としてもよい。

**【0132】**

図 20 (A) に、集積回路装置 10 の D 2 方向に沿った断面図の例を示す。ここで W 1、W B、W 2 は、各々、出力側 I / F 領域 12、回路ブロック C B 1 ~ C B N、入力側 I / F 領域 14 の D 2 方向での幅である。この幅 W 1、W B、W 2 は、各々、出力側 I / F 領域 12、回路ブロック C B 1 ~ C B N、入力側 I / F 領域 14 のトランジスタ形成領域 (バルク領域、アクティブ領域) の幅 (最大幅) であり、バンプの形成領域は含まない。また W は集積回路装置 10 の D 2 方向での幅である。

**【0133】**

本実施形態では図 20 (A) に示すように、D 2 方向において、回路ブロック C B 1 ~ C B N と出力側、入力側 I / F 領域 12、14 との間に他の回路ブロックが介在しない構成にできる。従って、 $W_1 + W_B + W_2 = W < W_1 + 2 \times W_B + W_2$  とすることができる。或いは、 $W_1 + W_2 < W_B$  が成立立つため、 $W < 2 \times W_B$  とすることもできる。

**【0134】**

10

20

30

40

50

一方、図20(B)の配置手法では、2以上の複数の回路ブロックがD2方向に沿って配置される。具体的にはデータドライバブロックとメモリブロックがD2方向に沿って配置される。

#### 【0135】

例えば図20(B)においてホスト側からの画像データはメモリブロックに書き込まれる。そしてデータドライバブロックは、メモリブロックに書き込まれたデジタルの画像データをアナログのデータ電圧に変換して、表示パネルのデータ線を駆動する。従って画像データの信号の流れはD2方向である。このため図20(B)では、この信号の流れに合わせて、メモリブロックとデータドライバブロックをD2方向に沿って配置している。

#### 【0136】

ところが図20(B)の配置手法には以下のような課題がある。

#### 【0137】

第1に、表示ドライバなどの集積回路装置では、低コスト化のためにチップサイズの縮小が要求される。ところが、微細プロセスを採用し、集積回路装置を単純にシューリンクしてチップサイズを縮小すると、短辺方向のみならず長辺方向も縮小されてしまい、狭ピッチのために実装が困難になる。

#### 【0138】

第2に、表示ドライバでは、表示パネルの種類（アモルファス TFT、低温ポリシリコン TFT）や画素数（Q C I F、Q V G A、V G A）や製品の仕様などに応じて、メモリやデータドライバの構成が変わる。従って図20(B)の配置手法では、ある製品ではパッドピッチとメモリのセルピッチとデータドライバのセルピッチが一致していたとしても、メモリやデータドライバの構成が変わると、これらのピッチが一致しなくなる。ピッチが一致しなくなると、回路ブロック間に、ピッチの不一致を吸収するための無駄な配線領域を形成しなければならなくなる。この結果、集積回路装置のD2方向での幅が大きくなり、チップ面積が増加し、コスト増を招く。一方、このような事態を避けるために、パッドピッチとセルピッチが揃うようにメモリやデータドライバのレイアウトを変更すると、開発期間が長期化し、結局、コスト増を招く。

#### 【0139】

これに対して図18、図19(A)(B)の配置手法では複数の回路ブロックCB1～CBNがD1方向に沿って配置される。また図20(A)では、パッド（バンプ）の下にトランジスタ（回路素子）を配置できる（能動面バンプ）。また回路ブロック内の配線であるローカル配線よりも上層（パッドよりも下層）で形成されるグローバル配線により、回路ブロック間や、回路ブロックとI/F領域間等での信号線を形成できる。従って、集積回路装置10のD1方向での長さを維持したままで、D2方向での幅Wを狭くでき、スリムな細長チップを実現できる。

#### 【0140】

また図18、図19(A)(B)の配置手法では回路ブロックCB1～CBNがD1方向に沿って配置されるため、製品の仕様変更等に容易に対応できる。即ち共通のプラットフォームを用いて様々な仕様の製品を設計できるため、設計効率を向上できる。例えば図19(A)(B)において、表示パネルの画素数や階調数が増減した場合にも、メモリブロックやデータドライバブロックのブロック数や、1水平走査期間での画像データの読み出し回数等を増減するだけで対応できる。また図19(A)(B)はメモリ内蔵のアモルファス TFTパネル用の例であるが、メモリ内蔵の低温ポリシリコン TFTパネル用の製品を開発する場合には、回路ブロックCB1～CBNの中から走査ドライバブロックを取り除くだけで済む。またメモリ非内蔵の製品を開発する場合には、メモリブロックを取り除けば済む。そしてこのように仕様に合わせて回路ブロックを取り除いても、それが他の回路ブロックに及ぼす影響が最小限に抑えられるため、設計効率を向上できる。

#### 【0141】

また図18、図19(A)(B)の配置手法では、各回路ブロックCB1～CBNのD2方向での幅（高さ）を、例えばデータドライバブロックやメモリブロックの幅（高さ）

10

20

30

40

50

に統一できる。そして各回路ブロックのトランジスタ数が増減した場合には、各回路ブロックのD1方向での長さを増減することで調整できるため、設計を更に効率化できる。例えば図19(A)(B)において、階調電圧生成回路ブロックや電源回路ブロックの構成が変更になり、トランジスタ数が増減した場合にも、階調電圧生成回路ブロックや電源回路ブロックのD1方向での長さを増減することで対応できる。

#### 【0142】

そして図18、図19(A)(B)の配置手法を採用した場合にも、図21(A)に示すように、高速I/F回路ブロックHBの両サイドに保護回路ブロックPTB1、PTB2が配置される。これにより高速I/F回路ブロックHBのトランジスタの静電気破壊の防止やノイズ除去を実現できる。また高速I/F回路ブロックHBとロジック回路ブロックLBとの間の配線領域のD1方向の長さを広くでき、配線効率を向上できる。また高速I/F回路ブロックHBのD2方向での幅を小さくできるため、集積回路装置のD2方向での幅Wも小さくでき、スリムな細長チップを実現できる。10

#### 【0143】

また高速I/F回路ブロックHBを図21(B)のように配置してもよい。図21(B)では、高速I/F回路ブロックHBのD1(又はD3)方向に隣接してロジック回路ブロックLBが配置されている。図21(B)の場合でも、高速I/F回路ブロックHBの両サイドに保護回路ブロックPTB1、PTB2が配置される。従って、静電気破壊の防止、ノイズ除去を実現できると共に、HBとLBの間の配線領域のD2方向での長さを広くして配線効率を向上できる。20

#### 【0144】

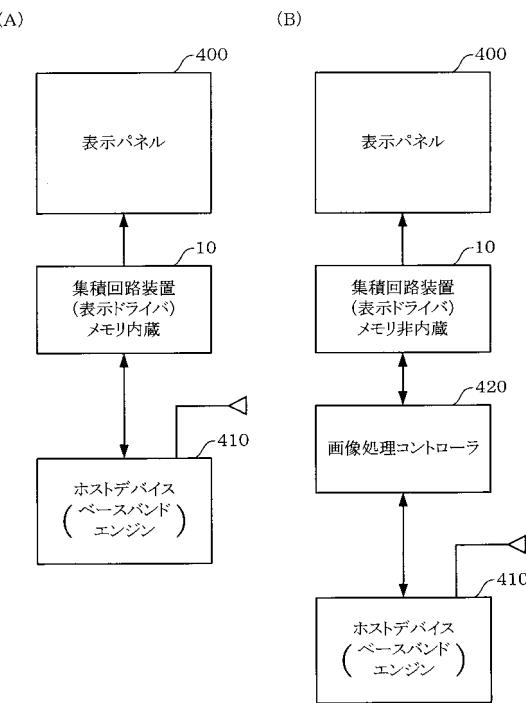

##### 10. 電子機器

図22(A)(B)に本実施形態の集積回路装置10を含む電子機器(電気光学装置)の例を示す。なお電子機器は図22(A)(B)に示されるもの以外の構成要素(例えばカメラ、操作部又は電源等)を含んでもよい。また本実施形態の電子機器は携帯電話機には限定されず、デジタルカメラ、PDA、電子手帳、電子辞書、プロジェクタ、リアプロジェクションテレビ、或いは携帯型情報端末などであってもよい。

#### 【0145】

図22(A)(B)においてホストデバイス410は、例えばMPU、ベースバンドエンジンなどである。このホストデバイス410は、表示ドライバである集積回路装置10の制御を行う。或いはアプリケーションエンジンやベースバンドエンジンとしての処理や、圧縮、伸長、サイジングなどのグラフィックエンジンとしての処理を行うこともできる。また図22(B)の画像処理コントローラ420は、ホストデバイス410に代行して、圧縮、伸長、サイジングなどのグラフィックエンジンとしての処理を行う。30

#### 【0146】

図22(A)の場合には、集積回路装置10としてメモリ内蔵のものを用いることができる。即ちこの場合には集積回路装置10は、ホストデバイス410からの画像データを、一旦内蔵メモリに書き込み、書き込まれた画像データを内蔵メモリから読み出して、表示パネルを駆動する。一方、図22(B)の場合には、集積回路装置10としてメモリ非内蔵のものを用いることができる。即ちこの場合には、ホストデバイス410からの画像データは、画像処理コントローラ420の内蔵メモリに書き込まれる。そして集積回路装置10は、画像処理コントローラ420の制御の下で、表示パネル400を駆動する。40

#### 【0147】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語(第1導電型ウェル、第2導電型ウェル、第1導電型拡散領域、第2導電型拡散領域、第1導電型トランジスタ、第2導電型トランジスタ、第2導電型基板等)と共に記載された用語(N型ウェル、P型ウェル、N+領域、P+領域、N型トランジスタ、P型トランジスタ、P

型基板等)は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また集積回路装置や電子機器の構成、配置、動作も本実施形態で説明したものに限定に限定されず、種々の変形実施が可能である。

**【図面の簡単な説明】**

**【0 1 4 8】**

【図1】保護回路の構成例。

【図2】図2(A)(B)は、ダイオードの縦構造を示す模式的な断面図。

【図3】ダイオードの縦構造を示す詳細な断面図。

【図4】保護回路の他の構成例。

【図5】ダイオードの縦構造を示す模式的な断面図。

10

【図6】本実施形態の比較例。

【図7】集積回路装置の回路構成例。

【図8】図8(A)(B)(C)は高速I/F回路、物理層回路の構成例。

【図9】図9(A)(B)は物理層回路の他の構成例。

【図10】集積回路装置のレイアウト例。

【図11】集積回路装置の詳細なレイアウト例。

【図12】高速I/F回路ブロックの詳細なレイアウト例。

【図13】集積回路装置の更に詳細なレイアウト例。

【図14】保護回路のレイアウト例。

【図15】図15(A)(B)はトリプルウェルを用いる手法の説明図。

20

【図16】図16(A)(B)はP+領域の形成手法の説明図。

【図17】双方向ダイオードの説明図。

【図18】集積回路装置のレイアウトの変形例。

【図19】図19(A)(B)は集積回路装置の平面レイアウトの詳細例。

【図20】図20(A)(B)は集積回路装置の断面図の例。

【図21】図21(A)(B)は保護回路ブロックの配置例。

【図22】図22(A)(B)は電子機器の構成例。

**【符号の説明】**

**【0 1 4 9】**

P T J 第Jの保護回路、P T K 第Kの保護回路、P T L 第Lの保護回路、

30

D I 1 ~ D I 6 第1~第6のダイオード、

D P 1 ~ D P 3 第1~第3の寄生ダイオード、H B 高速I/F回路ブロック、

L B ドライバ用ロジック回路ブロック、P H Y 物理層回路、H L ロジック回路、

P T B 1、P T B 2 第1、第2の保護回路ブロック、P T 1 ~ P T 6 保護回路、

P 1、P 2、P 4、P 5、D P、D M パッド、

P L 1、P L 2、P L 4、P L 5 電源線、R G 1、R G 2 第1、第2の領域、

C P R 1、C P R 2 第1、第2のキャパシタ領域、

10 集積回路装置、12 出力側I/F領域、14 入力側I/F領域、

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【 図 1 5 】

【 図 1 4 】

【図16】

【図17】

【図18】

【図19】

【 図 2 0 】

【図21】

【図22】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 27/08 (2006.01)

H 01 L 21/76 (2006.01)

(72)発明者 米澤 岳美

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

(72)発明者 澤田 光章

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 田代 吉成

(56)参考文献 特開平10-173134 (JP, A)

特開2002-83931 (JP, A)

特開2002-344543 (JP, A)

特開2001-94053 (JP, A)

特開2005-183513 (JP, A)

特開2003-203985 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 822

H 01 L 21 / 76

H 01 L 21 / 8234

H 01 L 27 / 04

H 01 L 27 / 06

H 01 L 27 / 08

H 01 L 27 / 088