(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-93579

(P2005-93579A)

(43) 公開日 平成17年4月7日(2005.4.7)

(51) Int.Cl.<sup>7</sup>

**H01L 21/82**

**H01L 21/3205**

**H01L 21/822**

**H01L 21/8242**

**H01L 27/04**

F 1

H01L 21/82      F

H01L 27/10      491

H01L 27/04      V

H01L 27/04      P

H01L 27/10      691

テーマコード(参考)

5FO33

5FO38

5FO64

5FO83

審査請求有 請求項の数 8 O L (全 13 頁) 最終頁に続く

(21) 出願番号

(22) 出願日

特願2003-322584 (P2003-322584)

平成15年9月16日 (2003.9.16)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100083161

弁理士 外川 英明

(72) 発明者 小松 幸生

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内

(72) 発明者 小山 啓

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】 ヒューズ領域の占める割合を小さく、安価に、しかも、再現性よく実現できるヒューズ素子を有する半導体装置を提供する。

【解決手段】 回路素子が設けられた半導体基板上に第1の導電線層からなるヒューズF1～F3と第2の導電線層からなる抵抗R1～R3とを並列接続した2組以上のヒューズ単位Fu1～Fu3を直列接続してなるヒューズ素子5を設ける。ヒューズF1～F3は、半導体基板上面から遠い側に、抵抗R1～R3は、半導体基板上面から近い側にして絶縁膜中に形成する。

【選択図】 図1

5:ヒューズ素子 10a, 10b:コンタクト 11a, 11b:コンタクトパッド

16:コンタクトプラグ F1, F2, F3:ヒューズ Fu1, Fu2, Fu3:ヒューズ単位

R1, R2, R3:抵抗

**【特許請求の範囲】****【請求項 1】**

回路素子が設けられた半導体基板と、

前記半導体基板上に設けられた絶縁膜と、

ヒューズと抵抗とを並列接続したヒューズ単位を2個以上直列接続した構造を有し、且つ

前記絶縁膜中に埋め込まれたヒューズ素子と、

を具備し、

前記抵抗を半導体基板上面側に配置し、前記ヒューズを前記抵抗の上方に配置したことを

特徴とする半導体装置。

**【請求項 2】**

回路素子が設けられた半導体基板と、

前記半導体基板上に設けられた絶縁膜と、

前記絶縁膜中に前記半導体基板上面に沿って直線状に連接され、且つ第1の導電線層で構成された2個以上の抵抗と前記絶縁膜中で前記抵抗の上方に前記半導体基板上面に沿って直線状に連接され、且つ第2の導電線層で構成された2個以上のヒューズとを有し、前記各抵抗の両端と前記各ヒューズの両端とがコンタクトプラグにより接続されたヒューズ素子と、

を具備することを特徴とする半導体装置。

**【請求項 3】**

前記直線状の抵抗と前記直線状のヒューズとは、正対配置されていることを特徴とする

請求項2に記載の半導体装置。 20

**【請求項 4】**

前記直線状のヒューズは、前記直線状の抵抗の直上から水平方向にずれた位置に配置されていることを特徴とする請求項2に記載の半導体装置。

**【請求項 5】**

前記2個以上の抵抗は、異なる抵抗値を有することを特徴とする請求項2に記載の半導体装置。

**【請求項 6】**

前記異なる抵抗値は、前記第2の導電線層の層幅を変化させて形成することを特徴とする

請求項5に記載の半導体装置。 30

**【請求項 7】**

第2の導電線層は、金属または合金であることを特徴とする請求項1乃至6のいずれか1項に記載の半導体装置。

**【請求項 8】**

第1の導電線層は、ポリシリコンであることを特徴とする請求項1乃至7のいずれか1項に記載の半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、高集積化された半導体装置に係り、特に半導体装置の不良領域を救済するレーベル溶断方式のヒューズを備えた半導体装置に関する。 40

**【背景技術】****【0002】**

近年、高集積化の進む半導体装置においては、微細化要求として回路設計ルールの縮小化が進められている。特に大規模集積化が進むD R A M等の半導体記憶装置では、その傾向が顕著である。また、微細化に伴い、故障に備えた予備回路としての冗長回路を予め設けておき、不良メモリセルを冗長回路の正常なメモリセルと置き換えることで、不良部分を救済するリダンダンシ技術が広く採用されている。

**【0003】**

現実的には、ウェーハプロセス後、全く不良メモリセルのない半導体記憶装置を製造す 50

ることは困難であり、通常の半導体記憶装置では、ダイソート検査により不良メモリセルを特定して、冗長回路の正常なメモリセルと置き換えて、動作的に良品として保証された半導体記憶装置が製品化される。

#### 【0004】

そして、不良メモリセルは、正常なメモリセルと常に置き換えて使用されねばならないので、不良メモリセルのアドレスは、不揮発性の記憶素子に記憶させておく必要がある。この記憶素子として、レーザ光を用いて切断して、切断／未切断により「1」／「0」を記録するレーザ溶断方式のヒューズが従来使用してきた。

#### 【0005】

ところで、半導体記憶装置の大容量化が進むにつれ、不良メモリセル（ビット）の数が増加し、それを救済するためのヒューズの数も増加してきている。製品歩留まりを一定に維持するには、所定数の不良まではヒューズを用いて救済することが必要である。少なくとも数100ビット程度の不良をヒューズを用いて救済することが行われている。

#### 【0006】

例えば、大容量DRAM等では、約1万個程度のヒューズを用いた記憶素子（以下、ヒューズ素子という）が半導体記憶装置中に設けられている。同じ設計ルールで記憶容量が2倍に増加すると、チップ面積は約2倍に増大し、微小な塵等の異物が付着すると、メモリセルに物理的影響を与え、不良ビット数を増やしてしまう可能性がある。また、微細化が進むと、たとえ同じ大きさの塵でも、より多くのメモリセルが覆われて不良となり、やはり、不良ビットが増大してしまう結果となる。今後、半導体記憶装置の大容量化に伴い、不良メモリセル数が増加し、ヒューズの数及び冗長回路が増加する傾向は避けられない。

#### 【0007】

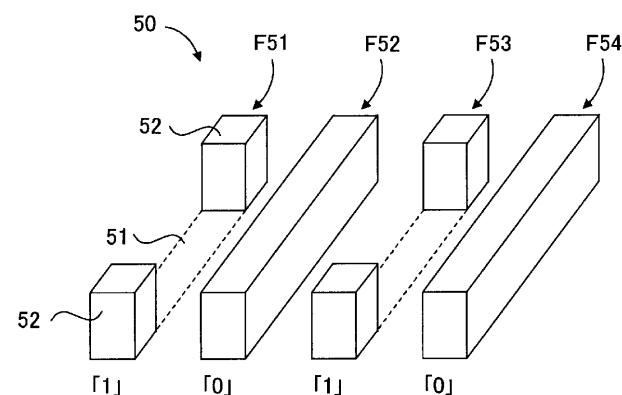

図7は、従来の半導体記憶装置におけるヒューズの構造を示す斜視図である。図7の状態では、ヒューズF51～F54の4本のヒューズが形成されており、ヒューズF51とヒューズF53はレーザを照射して切斷され、一方、ヒューズF52とヒューズF54はヒューズ形成時のまま、すなわち未切斷の状態で維持されている。

#### 【0008】

これらヒューズF51とヒューズF53の切斷された状態は、例えば「1」記憶状態として利用される。また、ヒューズF52とヒューズF54の未切斷の状態は、例えば「0」記憶状態として利用される。ここでは、4本のヒューズを用いて「1」又は「0」の状態を記憶させて合計2の4乗である16ビットの記憶が可能となる。

#### 【0009】

なお、個々のヒューズサイズを小さくすることで、ヒューズ領域の面積を縮小することも考えられるが、ヒューズを切斷する際に用いるレーザブロー装置におけるレーザ照射の焦点位置精度の限界と、レーザ光のスポット径の制約等があるために、ヒューズを一定幅よりも小さく設定することは困難であるため、今以上、ヒューズ領域の面積の割合を小さくすることは難しい。

#### 【0010】

そこで、ヒューズ領域の面積の割合を小さくした半導体記憶装置が提案されている（例えば、特許文献1参照。）。

#### 【0011】

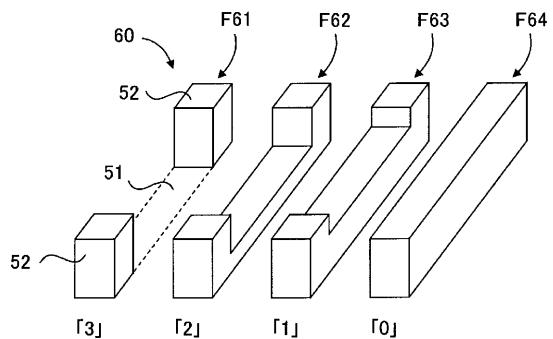

この半導体装置では、ヒューズへのレーザ照射の際、除去対象のヒューズごとに照射エネルギー、または照射時間を変化させてヒューズの厚さを段階的に調節することによってヒューズの抵抗値を変え、従来、切斷／未切斷の2ビットであった情報を、一本のヒューズから3ビット以上の多値の情報を得るようにしたものである。例えば、図8に示すように、ヒューズF61を切斷、ヒューズF62を厚く除去、ヒューズF63を薄く除去、ヒューズF64を除去しない状態の4段階の抵抗を作製することにより、一本のヒューズ当たり4ビットの情報を与えることができ、4本のヒューズを並べることにより合計4の4乗である256ビットの記憶が可能となる。これにより従来の技術に比べて、ヒューズ領

10

20

30

40

50

域の面積の割合を小さくしている。

【0012】

しかしながら、上記多値化の技術は、ヒューズのレーザ溶断量を変化させるという難易度の高い技術で、原理的には可能であるが、低コストで、しかも、再現性よくレーザ溶断を実現することは難しい。

【特許文献1】特開2002-261166号公報（第3頁、図1）

【発明の開示】

【発明が解決しようとする課題】

【0013】

上述したように、半導体記憶装置において、記憶容量の増加、微細化の進展に伴ってヒューズ領域の占める割合が大きくなっている。このヒューズ領域の占める割合を小さくするために、特許文献1において、ヒューズの多値化が提案されているが、レーザ溶断によりヒューズである導電線層厚を段階的に調整する技術では、安価に、しかも、再現性よく実現することが困難であるという問題がある。

【0014】

従って、本発明は、上記問題に鑑みなされたもので、ヒューズ領域の占める割合が小さく、安価に、しかも、再現性よく実現できるヒューズ素子を有する半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0015】

上記目的を達成するために、本発明の一態様の半導体装置は、回路素子が設けられた半導体基板と、前記半導体基板上に設けられた絶縁膜と、ヒューズと抵抗とを並列接続したヒューズ単位を2個以上直列接続した構造を有し、且つ前記絶縁膜中に埋め込まれたヒューズ素子とを具備し、前記抵抗を前記半導体基板上面側に配置し、前記ヒューズを前記抵抗の上方に配置したことを特徴とする。

【発明の効果】

【0016】

本発明によれば、ヒューズ領域の占める割合を小さく、安価で、しかも、再現性よく実現できるヒューズ素子を有する半導体装置を提供できる。

【発明を実施するための最良の形態】

【0017】

以下、本発明の実施例について、図面を参照しながら説明する。

【実施例1】

【0018】

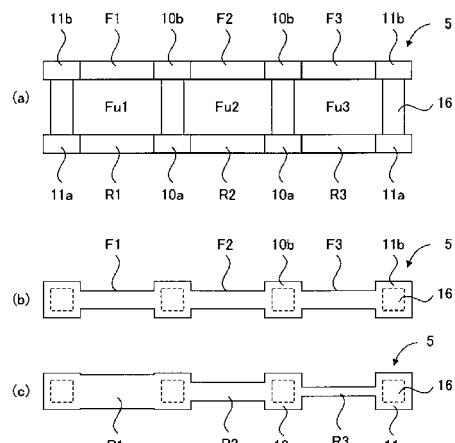

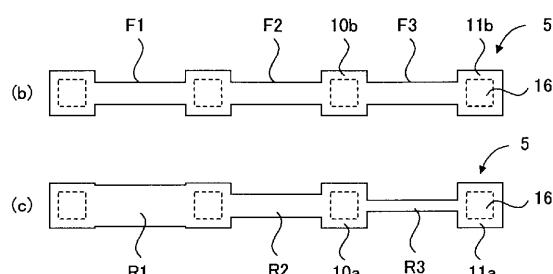

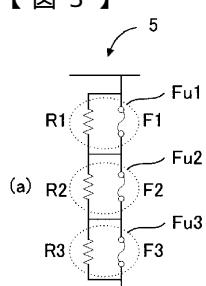

まず、実施例1に係る半導体装置について、図1を参照しながら説明する。図1(a)は、半導体装置のヒューズ素子を模式的に示す正面図、図1(b)は、図1(a)のヒューズ素子を上方から見た平面図、図1(c)は、図1(a)のヒューズ素子を下方から見た平面図である。なお、図中、同一部分には、同一符号を付して示す。

【0019】

図1(a)に示すように、本実施例の半導体装置では、ヒューズ素子5は、ヒューズF1～F3の各々と抵抗R1～R3の各々とを並列接続した3組のヒューズ単位Fu1からFu3の各々を直列接続した構造を有している。ここでは、半導体基板(図示略)の上面には、例えば、第1の導電線層からなる3個の抵抗R1～R3がコンタクト10aを介して同一平面上において直線状に接続されている。この3個の抵抗R1～R3、コンタクト10a、及び両端部のコンタクトパッド11aは、不純物がドープされたポリシリコンかなりり、同一層厚で、各抵抗R1～R3は同一長さに形成されている。

【0020】

一方、抵抗R1～R3の上部には、例えば、第2の導電線層からなる3個のヒューズF1～F3が、コンタクト10bを介して同一平面上において直線状に接続されている。この3個のヒューズF1～F3、コンタクト10b、及び、両端部のコンタクトパッド11bは、

10

20

30

40

50

b は、 AlCu を Ti / TiN 層で挟み込んだ積層構造で、同一層厚で、各ヒューズ F 1 ~ F 3 は同一長さに形成されている。また、この 3 個のヒューズ F 1 ~ F 3 及びコンタクト 10 b は、各々、3 個の抵抗 R 1 ~ R 3 及びコンタクト 10 a 上に正対して配置されている。

#### 【 0021 】

そして、下部と上部のコンタクト 10 a 及び 10 b と、コンタクトパッド 11 a 及び 11 b は、例えば、AlCu 等からなるコンタクトプラグ 16 によりそれぞれ接続されている。すなわち、ヒューズ F 1 と抵抗 R 1 、ヒューズ F 2 と抵抗 R 2 、ヒューズ F 3 と抵抗 R 3 は、各々、コンタクトプラグ 16 によりそれぞれ並列接続され、ヒューズ単位 F u 1 ~ F u 3 を構成し、この 3 組のヒューズ単位 F u 1 ~ F u 3 は、直列接続されている。なお、コンタクト 10 a 、 10 b は両端部のコンタクトパッド 11 a 、 11 b より小さく形成される。

#### 【 0022 】

そして、ヒューズ素子 5 の端部にあるコンタクトパッドは、配線層（図示略）により読み出し回路に接続されて、ヒューズ素子 5 の記憶情報を伝送するようになっている。ヒューズ F 1 ~ F 3 の抵抗は、通常、抵抗 R 1 ~ R 3 の抵抗より 2 枝以上低く設定されている。

#### 【 0023 】

また、図 1 (b) に示すように、3 個のヒューズ F 1 ~ F 3 は、同じ層幅に形成されている。

#### 【 0024 】

また、図 1 (c) に示すように、抵抗 R 1 は最も幅が広く、抵抗 R 2 は中間の幅に、そして抵抗 R 3 は最も幅が狭く形成されている。従って、抵抗 R 1 ~ R 3 は、同一材料、同一層厚で形成されているので、それぞれに対応する抵抗値 r 1 ~ r 3 は、層の幅に逆比例して、 $r_1 < r_2 < r_3$  となる。

#### 【 0025 】

そして、ヒューズ F 1 ~ F 3 が未切断の時においては、コンタクトプラグ 16 間の抵抗は、並列に接続されたヒューズ F 1 ~ F 3 の抵抗が支配的となり、ほとんどゼロに近いヒューズ F 1 ~ F 3 の抵抗を示すことになる。一方、ヒューズ F 1 ~ F 3 を切断した時においては、ヒューズ F 1 ~ F 3 の抵抗は無限大となるため、抵抗 R 1 ~ R 3 の値がコンタクトプラグ 16 間の抵抗を支配することになる。

#### 【 0026 】

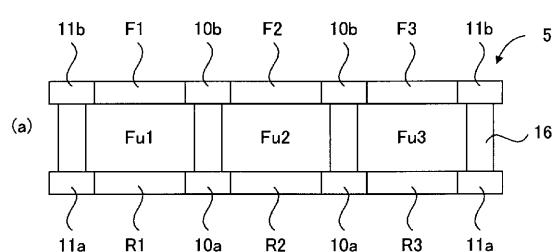

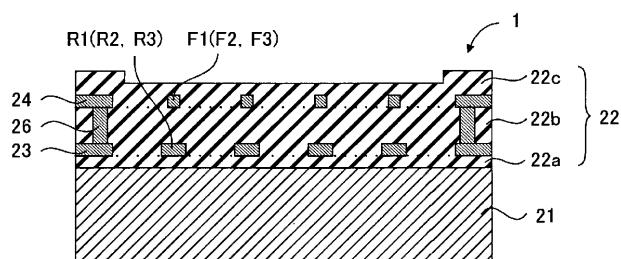

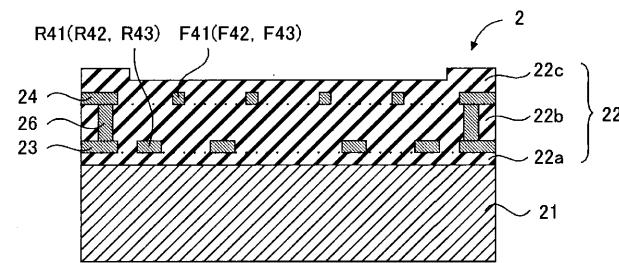

図 2 は、上記ヒューズ素子 5 を半導体基板上に組み込んだ状態を模式的に示す断面図である。この図は、図 1 に示す上記ヒューズ素子 5 を紙面表面から裏面に向かって、4 連、並置した状態を示すものである。図 2 に示すように、半導体装置 1 の半導体基板 21 上には、ヒューズ素子 5 が、4 連、並置されている。各連のヒューズ素子 5 は、図 1 に示す構造を有しており、半導体基板 21 上にあって、半導体基板 21 に近い側に、所定の厚さを有する 4 個の抵抗 R 1 (R 2 、 R 3 ) が互いに水平方向に離間して形成され、半導体基板 21 から遠い側に、所定の厚さを有する 4 個のヒューズ F 1 (F 2 、 F 3 ) が互いに水平方向に離間して形成されている。これらの抵抗 R 1 (R 2 、 R 3 ) 及びヒューズ F 1 (F 2 、 F 3 ) は、半導体基板 21 上に設けられた、例えば酸化膜からなる絶縁膜 22 中に形成されている。

#### 【 0027 】

更に詳しくは、半導体基板 21 中には、例えば、MOS パークのソース、ドレイン（図示略）等の回路素子がヒューズ回路から離れて形成されている。半導体基板 21 上には、絶縁膜 22 a を介して下部配線層、すなわち第 1 の導電線層 23 が設けられている。この第 1 の導電線層 23 を利用して、抵抗 R 1 ~ R 3 、コンタクト 10 a 、及びコンタクトパッド 11 a ( 図示略 ) を形成している。この第 1 の導電線層 23 は、絶縁膜 22 b 中に設けられたコンタクトプラグ 26 を介して、絶縁膜 22 b 上の上部配線層、すなわち第 2 の導電線層 24 に接続されている。そして、この第 2 の導電線層 24 を利用してヒューズ

10

20

30

40

50

ーズ F 1 ~ F 3、コンタクト 10 b、及びコンタクトパッド 11 b (図示略) を形成している。この第 2 の導電線層 24 上には、絶縁膜 22 c が設けられている。更に、絶縁膜 22 c 上には、ヒューズ F 1 ~ F 3 の直上部等を除いて、例えば、ポリイミド膜等 (図示略) が積層されている。ヒューズ F 1 ~ F 3 を覆う絶縁膜 22 c は、例えば、酸化膜が使われ、レーザ溶断条件に合うように膜厚が制御されている。なお、絶縁膜は、便宜上、3 種類に分類して示したが、それぞれは必ずしも単層ではなく、また、同質の絶縁膜とは限らない。

#### 【 0 0 2 8 】

次に、ヒューズ素子 5 のヒューズ F 1 ~ F 3 にレーザを照射して、ヒューズを溶断する方法を説明する。通常のヒューズ溶断装置 (図示略) を用いて、レーザのビーム径、レーザ出力、パルス幅等を調節して、フォーカスを最適にして、除去対象のヒューズ F 1 ~ F 3 にレーザを照射する。絶縁膜 22 c は、レーザをほとんど吸収しないが、保温の役目を担うとされている。ヒューズ F 1 ~ F 3 は、レーザ照射によって加熱されて溶融する。この際に、ヒューズ F 1 ~ F 3 上部の急激な温度上昇により圧力上昇が起こり、ヒューズ溶融部の上部の絶縁膜 22 c が吹き飛ばされる。これにより、圧力が大気圧程度に下がると同時に、溶融したヒューズ F 1 ~ F 3 が気化して、除去対象のヒューズ F 1 ~ F 3 が切斷される。

#### 【 0 0 2 9 】

ヒューズ F 1 ~ F 3 上部の絶縁膜 22 c が吹き飛ばされる程度の圧力上昇が起こるために、ヒューズ F 1 ~ F 3 側部及び下部へ対しても応力あるいはクラック等の伝播が起こる。従って、隣接するヒューズ F 1 ~ F 3 の水平方向に離間させる距離、及び、並列接続される抵抗 R 1 ~ R 3 の垂直方向の距離は重要である。垂直方向の距離を大きく取るために、例えば、図 2 に示すように、半導体装置の多層配線構造における最下層またはその近くにある第 1 の導電線層 23 と同じ高さに、抵抗 R 1 ~ R 3 を設けて、一方、ヒューズ F 1 ~ F 3 の位置は、多層配線構造における上部のメタル配線層である第 1 の導電線層 24 を利用することになる。離間すべき最小限の距離は、ヒューズの材質、形状等を含めたヒューズ溶断条件により異なるので、最適な条件を探して決めることになる。

#### 【 0 0 3 0 】

また、多層の絶縁膜 22 構成は、垂直方向の応力緩和に役立ち、単層膜構成とした場合より離間すべき距離を小さくすることが可能である。

#### 【 0 0 3 1 】

次に、ヒューズと抵抗で構成される一連のヒューズ素子 5 の記憶容量について、図 3 を参照しながら説明する。図 3 (a) は、図 1 に示したヒューズ素子 5 の等価回路図、図 3 (b) はヒューズ切断の有無を組合せることにより得られる抵抗値及びその抵抗値に割り当てる情報 (ビット) を示す表である。

#### 【 0 0 3 2 】

図 1 に示す一連の上記ヒューズ素子 5 は、図 3 (a) に示すように、例えばヒューズ F 1 と抵抗 R 1、ヒューズ F 2 と抵抗 R 2、ヒューズ F 3 と抵抗 R 3 とが各々、並列接続され、且つこれらの 3 組のヒューズ単位 F u 1 ~ F u 3 が直列接続された回路構成となる。ヒューズ F 1 ~ F 3 の抵抗値は、抵抗 R 1 ~ R 3 に比較して無視できる程度に低く (ここでは、仮に 0 とする)、抵抗 R 1、R 2、R 3 の抵抗値をそれぞれ r 1、r 2、r 3 として、その大きさを例えば  $r_1 < r_2 < r_3$  とする。

#### 【 0 0 3 3 】

まず、ヒューズ F 1 ~ F 3 が切断されてない状態では、ヒューズ F 1 ~ F 3 と抵抗 R 1 ~ R 3 からなるヒューズ単位 F u 1 ~ F u 3 における各々の両端の抵抗値はゼロであり、3 組が直列接続された一連のヒューズ素子 5 両端の総抵抗値もゼロである。

#### 【 0 0 3 4 】

そして、例えばヒューズ F 1 だけを切断すると、ヒューズ素子 5 両端の抵抗値は  $r_1 + 0 + 0$  となり、総抵抗値は  $r_1$  となる。また、例えば、ヒューズ F 2 だけを切断するとヒューズ素子両端の抵抗は  $0 + r_2 + 0$  となり、総抵抗値は  $r_2$  となる。また、例えば、ヒ

10

20

30

40

50

ヒューズ F 2 と F 3 だけを切断するとヒューズ素子両端の抵抗は  $0 + r_2 + r_3$  となり、総抵抗値は  $r_2 + r_3$  となり、以下同様に合計で 8 通りの総抵抗値の場合が考えられる。

#### 【0035】

これらをまとめると、図 3 ( b ) に示すように、8 通りの抵抗値が得られ、例えば、 $r_1 = 1$  、 $r_2 = 2$  、 $r_3 = 4$  とすると、0 ~ 7 まで 1 の差で 8 通りの設定が可能となる。そして、8 通りの抵抗値に 2 進数 3 衔の数を割り当てることができ、例えば、抵抗値 0 に 0 0 0 を割り当て、抵抗値  $r_1 + r_2 + r_3$  に 1 1 1 を割り当てることが可能である。すなわち、ヒューズ F 1 ~ F 3 と抵抗 R 1 ~ R 3 からなる 3 組のヒューズ単位 F u 1 ~ F u 3 を直列接続することにより、8 ビットの情報を記憶することができるヒューズ素子となる。

#### 【0036】

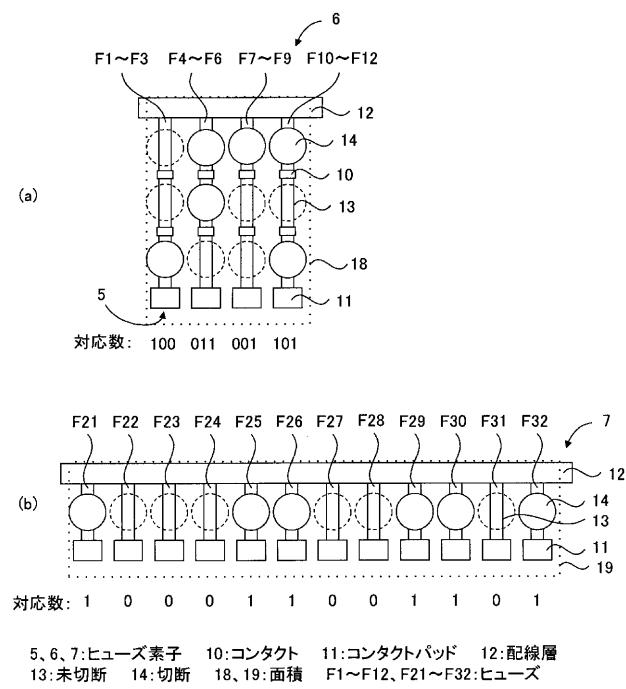

次に、3 組のヒューズと抵抗を接続した 8 ビットの情報を記憶するヒューズ素子の面積効率が向上する理由を、図 4 を参照しながら説明する。図 4 ( a ) は、図 1 に示した多値化されたヒューズ素子 ( F 1 ~ F 3 等 ) を 4 本並列に配置 ( 3 組 4 連 ) して 2 進数 12 衔を記憶できるヒューズ素子 6 の構成図である。各ヒューズ素子は、一端をコンタクトパッドを結ぶ共通の配線層 12 を介して、他端をコンタクトパッド 11 に接続される個別配線 ( 図示略 ) を介して、読み出し回路に接続される。破線の円はヒューズが未切断 13 の状態を表し、実線の円はヒューズが切断 14 の状態を表す。それぞれの円の大きさは、レーザ溶断の影響が強く及ぶ範囲を模式的に示し、従って、ヒューズ素子 6 は、マージンを見て隣接するヒューズ、コンタクト、及びコンタクトパッド等に影響が出ない程度に近接して配列された構成となっている。従って、必要最低限の面積 18 は点線で示す領域となる。

#### 【0037】

なお、本実施例によるヒューズ素子の記憶数値は、図 4 ( a ) に示すように、8 ビットのヒューズ素子 5 を 4 連並列しており、例えば、1 0 0 、 0 1 1 、 0 0 1 、 1 0 1 となり、合計で 8 の 4 乗の 4 0 9 6 通りの識別が可能となる。

#### 【0038】

一方、例えば、従来の同じ記憶容量を持つヒューズ素子は、図 4 ( b ) に示すように、ヒューズ F 21 ~ F 32 を 12 個並べて形成される。そして、ヒューズ F 1 ~ F 12 の一端は、コンタクトパッドを結ぶ共通の配線層 12 を介して、他端はコンタクトパッド 11 に各々接続される配線層 ( 図示略 ) を介して、読み出し回路に接続される。従って、隣接するヒューズ素子との離間距離を考慮したヒューズ素子の占める必要最低限の面積 19 は点線で示す領域となる。なお、従来のヒューズ素子の記憶数値は、図 4 ( b ) に示すように、1 0 0 0 1 1 0 0 1 1 0 1 となり、同様に合計で 2 の 12 乗の 4 0 9 6 通りの識別が可能となる。図 4 ( a ) に示すように、本実施例による場合には、ヒューズ素子 5 の両端部のコンタクトパッド 11 のみ配線層に接続される。中間にある 2 個のコンタクト 10 は、隣接のヒューズとの接続、及び、ヒューズと下方の抵抗との接続を行うコンタクトプラグとの接続に使われる所以、コンタクトパッド 11 に比較して小さく形成され、しかも、端部のコンタクトパッドには必要な隣接素子との間隔を省略できる。すなわち、図 4 ( b ) に示すように、3 組のヒューズと抵抗からなるヒューズ素子を、個々に分離して並べる場合に比較して短くなる。

#### 【0039】

更に、ヒューズ素子のみだけでなく、その外側にある配線層も考慮すると、本実施例によるヒューズ素子では、読み出し回路へ接続する個別の配線層本数の減少が可能である。すなわち、図 4 ( b ) に示す従来の 12 個のヒューズ素子 7 には、12 本の配線層が必要であるが、図 4 ( a ) に示す本実施例の 3 組 4 連のヒューズ素子 5 には、4 本の配線層を用意すればよく、従来のヒューズ素子に比較して配線層本数を 3 分の 1 に減少できる。以上のように、ヒューズ素子形成の面積の低減と読み出し配線層の減少により、半導体装置 1 においてヒューズ素子の占める面積を 2 / 3 から 1 / 2 程度に減少させることができる。

## 【0040】

上記した本実施例では、ヒューズには切断／未切断の2値の情報しか求めないために、通常のヒューズ溶断装置を用いて、ヒューズを切断することができる。そのためヒューズ溶断装置に特別な機能を追加する必要がなく、また、マージンの少ないヒューズ溶断条件で切断する必要がないので、スループットを落とすことなく、安価で、再現性よくヒューズ溶断が可能である。しかも、ヒューズ素子の占める面積を2/3から1/2程度に減少させることができるので、半導体装置の大容量化に対してもヒューズ領域の占める面積の割合を小さくすることが可能である。

## 【実施例2】

## 【0041】

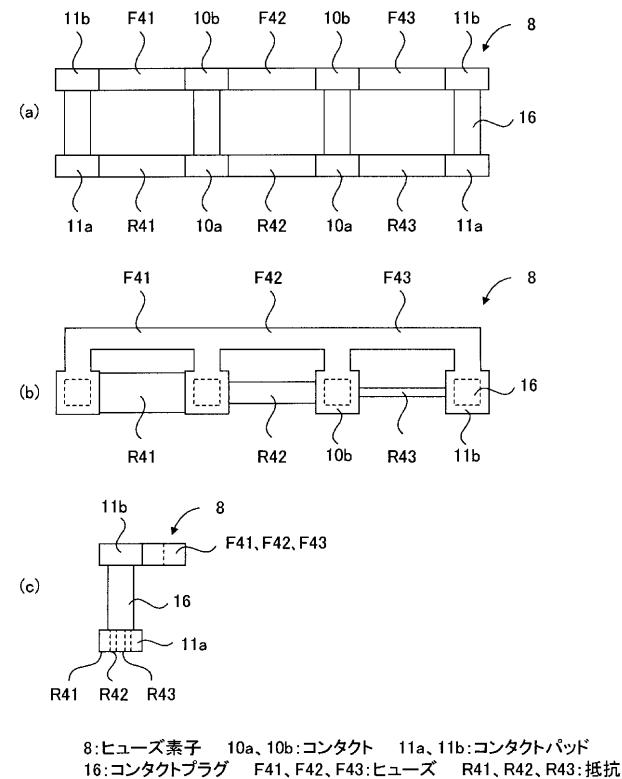

次に、本発明の実施例2に係る半導体装置について、図5を参照しながら説明する。図5(a)は、半導体装置のヒューズ素子の正面図、図5(b)は、図5(a)のヒューズ素子を上方から見た平面図、図5(c)は、図5(a)のヒューズ素子を右側方から見た側面図である。なお、実施例1と同一構成部分には同一の符号を付して、その説明は省略し、異なる構成部分について説明する。

## 【0042】

本実施例によるヒューズ素子8と実施例1におけるヒューズ素子5との違いは、ヒューズF41～F43が、抵抗R41～R43の上部において、抵抗R41～R43の直上から水平方向にずれた位置、例えば紙面上の上方に設けたことにある。そして、各ヒューズF41～F43の端部を抵抗R41～R43方向に折り曲げてコンタクトパッド11a上に延長し、且つその先端部にコンタクト10b及びコンタクトパッド11bを設け、このコンタクト10b及びコンタクトパッド11bはコンタクトプラグ16を介してコンタクト10a及びコンタクトパッド11aにそれぞれ接続している。

## 【0043】

なお、本実施例のヒューズF41～F43は、実施例1におけるヒューズに比べて抵抗は、折り曲げ部分の抵抗成分の分だけ増加するが、この増加分も含めてヒューズF41～F43の抵抗が、抵抗R41～R43に対して影響が出ないように構成されている。

## 【0044】

図6は、上記ヒューズ素子8を半導体基板上に組み込んだ状態を模式的に示す断面図である。この図は、図5に示す上記ヒューズ素子8を紙面表面から裏面に向かって、4連、並置した状態を示すものである。

## 【0045】

図6に示すように、半導体基板21のヒューズ形成領域の中心線に対して左側には、図5(c)に示す状態のヒューズ素子8を、2連、そのまま配置し、右側には、図5(c)に示す状態のヒューズ素子8を、2連、鏡面対称にして配置している。ここで、ヒューズF41の位置は、実施例1における位置と同じ位置に設けているので、左側の2連のヒューズ8における抵抗R41の位置は実施例1の抵抗の位置より左側に寄り、右側の2連のヒューズ8においては右側に寄る変位した構造となっている。

## 【0046】

なお、本実施例では、図5(c)の状態のヒューズ素子とこれと鏡面対称のヒューズ素子との2種類を並置させる構造としたが、どちらか1種類の状態のヒューズ素子を並置させても差し支えない。

## 【0047】

以上のような実施例2によれば、実施例1で得られる効果の他に、ヒューズF41と抵抗R41の距離が離れることにより、レーザ溶断条件が同じなら、ヒューズF41を溶断する時の応力あるいはクラック等の伝播を軽減できる。言い換えれば、遠く離れたので、より強力なレーザ溶断条件を取ることが可能になり、短時間で処理することができ、スループットを上げることができる。

## 【0048】

また、ヒューズを半導体基板21に近づけて形成することができるので、配線層の微細

化が可能となり、レーザ溶断が容易となる。

【0049】

更に、ヒューズとコンタクトパッドが離れるので、ヒューズをより小さく作製することが可能となり、ヒューズ素子としてより小型化が可能となり、半導体装置におけるヒューズ素子の占有面積を低減できる。

【0050】

以上、本発明の実施例を説明したが、本発明は上記実施例に限定されるものではなく、本発明の要旨を逸脱しない範囲内で種々変形して実施することができる。

【0051】

例えば、3組のヒューズ単位を有するヒューズ素子の場合を示したが、2組のヒューズ単位の場合でも、従来に比較してヒューズの占有面積効率を上げることができる。更に面積効率を上げようすると、ヒューズ素子のヒューズ単位を4組以上に増加させた構成とすればよい。ただし、この場合、各抵抗の抵抗値を明確に区別する必要があり、抵抗のより精密な作製と測定の精度向上を考慮する必要がある。

【0052】

また、上述の実施例では、多層配線構造の下層の配線層を用いて抵抗を形成し、上層の配線層を用いてヒューズを形成したが、多層配線の配線層を使わずに、別に抵抗あるいはヒューズを形成してもよい。その結果、抵抗あるいはヒューズのために、最適な抵抗率、層厚等を選択でき、制御性のよいヒューズ素子を形成することができる。

【0053】

また、抵抗は同一組成の材料の層厚を一定にして、層幅を変化させることでその抵抗値を変化させたが、層幅を一定にして、層厚を変化させてもよい。層厚と層幅の両方を変化させることでその抵抗値を変化させることもできる。

【0054】

また、抵抗の抵抗値を大きく変化させたい時には、抵抗率の比較的大きな、例えば、不純物濃度を調整したポリシリコンから、抵抗率の大きい金属または合金、そして、抵抗率の小さい金属または合金等を使い分けることができる。構造は単層でも、多層でも差し支えないし、これらの材料と層厚または層幅の変化を組合せることも差し支えない。

【0055】

更に、ヒューズはAlCuをTi/TiNで挟み込んだ構成の材料を使用したが、単層の金属、他の金属材料、あるいは、金属以外のレーザ溶断可能な導電性材料でもよい。ヒューズの抵抗値は、並列する抵抗の抵抗値に比較して、2桁以上低く、実質ゼロとして扱えるような構成にして、ヒューズ素子を形成したが、ヒューズの抵抗値を、抵抗の抵抗値に対して無視できない程度接近した値とすることも可能である。

【0056】

また、ヒューズと抵抗とをコンタクトプラグで直接、しかも直線的に接続しているが、第1の導電線層と第2の導電線層との中間の導電線層を介して、間接的に、しかも曲折して接続してもよい。

【図面の簡単な説明】

【0057】

【図1】(a)は、本発明の実施例1に係る半導体装置に用いられるヒューズ素子を模式的に示す正面図、(b)は図1(a)のヒューズ素子を上方から見た平面図、(c)は図1(a)のヒューズ素子を下方向から見た平面図。

【図2】本発明の実施例1に係る半導体装置の要部断面図。

【図3】(a)は、本発明の実施例1に係るヒューズ素子の等価回路、(b)は図3(a)のヒューズ素子の抵抗値とビット対応を示す図。

【図4】(a)は、本発明の実施例1に係るヒューズ素子の占有面積を説明するための平面図、(b)は従来のヒューズ素子の占有面積を説明するための平面図。

【図5】(a)は、本発明の実施例2に係る半導体装置に用いられるヒューズ素子を模式的に示す正面図、(b)は図5のヒューズ素子を上方から見た平面図、(c)は図5(a)

10

20

30

40

50

) のヒューズ素子を側面から見た側面図。

【図6】本発明の実施例2に係る半導体装置の要部断面図。

【図7】従来の半導体装置に用いられるヒューズ素子を模式的に示す斜視図。

【図8】従来の半導体装置に用いられる改善されたヒューズ素子を模式的に示す斜視図。

【符号の説明】

【0058】

1、2 半導体装置

5、6、7、8、50、60 ヒューズ素子

10、10a、10b コンタクト

11、11a、11b コンタクトパッド

12 配線層

13 未切断

14 切断

16、26 コンタクトプラグ

18、19 面積

21 半導体基板

22、22a、22b、22c 絶縁膜

23 第1の導電線層(下部配線層)

24 第2の導電線層(上部配線層)

51 ヒューズ切断領域

52 端部

F1 ~ F12、F21 ~ F32、F41 ~ F43、F51 ~ F54、F61 ~ F64 ヒューズ

R1 ~ R12、R41 ~ R43 抵抗

Fu1 ~ Fu3 ヒューズ単位

【図1】

5:ヒューズ素子 10a、10b:コンタクト 11a、11b:コンタクトパッド

16:コンタクトプラグ F1、F2、F3:ヒューズ Fu1、Fu2、Fu3:ヒューズ単位

R1、R2、R3:抵抗

【図2】

1:半導体装置 21:半導体基板 22、22a、22b、22c:絶縁膜

23:第1の導電線層 24:第2の導電線層 26:コンタクトプラグ

F1、F2、F3:ヒューズ R1、R2、R3:抵抗

【図3】

| 抵抗値とビット対応 |     |

|-----------|-----|

| 抵抗値       | ビット |

| 0         | 000 |

| r1        | 001 |

| r2        | 010 |

| r3        | 100 |

| r1+r2     | 011 |

| r1+r3     | 101 |

| r2+r3     | 110 |

| r1+r2+r3  | 111 |

5:ヒューズ素子 F1、F2、F3:ヒューズ Fu1、Fu2、Fu3:ヒューズ単位

R1、R2、R3:抵抗

【図4】

【図5】

【図6】

【図7】

【図8】

51:ヒューズ切断領域 52:端部 60:ヒューズ素子

F61、F62、F63、F64:ヒューズ

---

フロントページの続き

|                          |              |            |

|--------------------------|--------------|------------|

| (51)Int.Cl. <sup>7</sup> | F I          | テーマコード(参考) |

| H 01 L 27/10             | H 01 L 21/88 | Z          |

| H 01 L 27/108            | H 01 L 21/88 | P          |

|                          | H 01 L 21/88 | S          |

F ターム(参考) 5F033 HH09 HH33 JJ09 KK04 MM08 RR03 RR22 TT04 VV09 VV11

VV16 XX03 XX34

5F038 AR09 AR12 AR19 AR21 AR23 AV15 CA02 CA05 CA16 DF05

5F064 BB14 CC09 CC22 EE09 EE22 EE27 FF02 FF05 FF27 FF32

FF42

5F083 AD00 GA09 GA30 JA32 JA36 JA40 JA56 JA58 ZA10