(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6455180号

(P6455180)

(45) 発行日 平成31年1月23日(2019.1.23)

(24) 登録日 平成30年12月28日(2018.12.28)

(51) Int.Cl.

H02M 3/28 (2006.01)

F 1

H02M 3/28

H02M 3/28H

E

請求項の数 7 (全 14 頁)

(21) 出願番号 特願2015-13801 (P2015-13801)

(22) 出願日 平成27年1月28日 (2015.1.28)

(65) 公開番号 特開2016-140183 (P2016-140183A)

(43) 公開日 平成28年8月4日 (2016.8.4)

審査請求日 平成30年1月24日 (2018.1.24)

(73) 特許権者 000006220

ミツミ電機株式会社

東京都多摩市鶴牧2丁目11番地2

(74) 代理人 100090033

弁理士 荒船 博司

(74) 代理人 100093045

弁理士 荒船 良男

(72) 発明者 松田 裕樹

東京都多摩市鶴牧2丁目11番地2 ミツ

ミ電機株式会社内

審査官 赤穂 嘉紀

最終頁に続く

(54) 【発明の名称】電源制御用半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

電圧変換用のトランスの一次側巻線に間欠的に電流を流すためのスイッチング素子を、前記トランスの一次側巻線に流れる電流に比例した電圧と前記トランスの二次側からの出力検出信号とに応じてオン、オフ制御する駆動パルスを生成し出力する電源制御用半導体装置であって、

周波数可変な発振回路を備え前記スイッチング素子を周期的にオンさせるタイミングを与えるクロック信号を発生するクロック発生回路と、

前記トランスの一次側巻線に流れる電流に比例した電圧と前記トランスの二次側からの出力検出信号に基づいて前記スイッチング素子をオフさせるタイミングを与える電圧／電流制御回路と、

前記二次側からの出力検出信号に応じて前記発振回路の発振周波数を変化させる周波数制御回路と、

外部から設定情報を与えるための設定端子と、を備え、

前記周波数制御回路は、前記設定端子の状態に応じて、出力検出信号対発振周波数特性を変更可能であり、

前記出力検出信号対発振周波数特性は、第1特性と第2特性の2つであり、前記出力検出信号が所定の第1レベルよりも低い領域では第1周波数に固定され、前記出力検出信号が前記第1レベルよりも高い第2レベルよりも高い領域では第2周波数に固定され、

前記第1特性の前記第1周波数と前記第2特性の前記第1周波数は同一である一方、前

記第1特性の前記第2周波数と前記第2特性の前記第2周波数は異なる値に設定され、前記出力検出信号が前記第1レベルと第2レベルとの間にあるときは前記出力検出信号の変化に対して発振周波数が直線的に変化するように構成されていることを特徴とする電源制御用半導体装置。

【請求項2】

電圧変換用のトランスの一次側巻線に間欠的に電流を流すためのスイッチング素子を、前記トランスの一次側巻線に流れる電流に比例した電圧と前記トランスの二次側からの出力検出信号とに応じてオン、オフ制御する駆動パルスを生成し出力する電源制御用半導体装置であって、

周波数可変な発振回路を備え前記スイッチング素子を周期的にオンさせるタイミングを与えるクロック信号を発生するクロック発生回路と、 10

前記トランスの一次側巻線に流れる電流に比例した電圧と前記トランスの二次側からの出力検出信号に基づいて前記スイッチング素子をオフさせるタイミングを与える電圧／電流制御回路と、

前記二次側からの出力検出信号に応じて前記発振回路の発振周波数を変化させる周波数制御回路と、

外部から設定情報を与えるための設定端子と、を備え、

前記周波数制御回路は、

前記出力検出信号に応じた信号と所定の基準電圧とを入力とし、前記出力検出信号に応じた信号に比例した電圧を出力する非反転増幅回路と、 20

前記非反転増幅回路の出力をインピーダンス変換して前記発振回路へ供給するバッファ回路と、を備え、前記設定端子の状態に応じて、出力検出信号対発振周波数特性を変更可能であり、

前記非反転増幅回路は、前記設定端子の状態に応じて増幅率が可変に構成されていることを特徴とする電源制御用半導体装置。

【請求項3】

前記出力検出信号対発振周波数特性は、前記出力検出信号が所定の第1レベルよりも低い領域では第1周波数に固定され、前記出力検出信号が前記第1レベルより高い第2レベルよりも高い領域では第2周波数に固定されることを特徴とする請求項2に記載の電源制御用半導体装置。 30

【請求項4】

前記出力検出信号対発振周波数特性は第1特性と第2特性の2つであり、前記第1特性の前記第1周波数と前記第2特性の前記第1周波数は同一である一方、前記第1特性の前記第2周波数と前記第2特性の前記第2周波数は異なる値に設定され、前記出力検出信号が前記第1レベルと第2レベルとの間にあるときは前記出力検出信号の変化に対して発振周波数が直線的に変化することを特徴とする請求項3に記載の電源制御用半導体装置。

【請求項5】

前記周波数制御回路は、

前記非反転増幅回路の出力に応じて前記発振回路に対する周波数制御信号を生成するものであり、 40

前記周波数制御信号を、前記出力検出信号が前記第1レベルよりも低い領域では前記第1レベルに固定するとともに、前記出力検出信号が前記第2レベルよりも高い領域では前記第2レベルに固定するクランプ機能と、

前記周波数制御信号を出力する前記バッファ回路の機能と、

を備えるように構成されていることを特徴とする請求項3または4に記載の電源制御用半導体装置。

【請求項6】

前記周波数制御回路は前記クランプ機能を有するクランプ回路を備え、

前記クランプ回路は、4入力の差動増幅回路であり、前記4入力として、前記出力検出信号に対応した電圧と、前記第1レベルに対応した電圧と、前記第2レベルに対応した電 50

圧と、当該差動増幅回路の出力電圧とが入力されていることを特徴とする請求項 5 に記載の電源制御用半導体装置。

【請求項 7】

前記クランプ回路は、前記出力検出信号を入力とし、当該クランプ回路によりクランプされた信号が前記非反転増幅回路へ入力されるように構成されていることを特徴とする請求項 6 に記載の電源制御用半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電源制御用半導体装置に関し、特に電圧変換用トランスを備えた絶縁型直流電源装置を構成する制御用半導体装置を利用して有効な技術に関する。 10

【背景技術】

【0002】

直流電源装置には、交流電源を整流するダイオード・ブリッジ回路と、該回路で整流された直流電圧を降圧して所望の電位の直流電圧に変換する絶縁型 D C - D C コンバータなどで構成された A C - D C コンバータがある。かかる A C - D C コンバータとしては、例えば電圧変換用トランスの一次側巻線と直列に接続されたスイッチング素子を P W M (パルス幅変調) 制御方式や P F M (パルス周波数変調) 制御方式等でオン、オフ駆動して一次側巻線に流れる電流を制御し、二次側巻線に誘起される電圧を制御するようにしたスイッチング電源装置が知られている。 20

【0003】

また、スイッチング制御方式の A C - D C コンバータにおいては、一次側の制御動作のために、一次側のスイッチング素子と直列に電流検出用の抵抗を設けるとともに、電源制御回路 ( I C ) には該抵抗により電流 - 電圧変換された電圧が入力される端子 ( 電流検出端子 ) を設け、検出された電流値と二次側からのフィードバック電圧とに基づいて一次巻線のピーク電流を制御して二次側の出力電圧または出力電流を一定に維持するようしているものがある ( 特許文献 1 参照 ) 。

【0004】

さらに、電流検出用の抵抗で電流 - 電圧変換した電圧と二次側からのフィードバック電圧によって出力を制御するように構成した A C - D C コンバータにおいては、軽負荷時ににおけるスイッチングロスを低減し電力効率を上げるため、あるフィードバック電圧 V FB1 以下と V FB2 以上の領域ではスイッチング周波数を固定した P W M 方式で制御する一方、 V FB1 ~ V FB2 の間では周波数を変化させて制御を行うようにしているものがある。 30

【先行技術文献】

【特許文献】

【0005】

【特許文献 1】特開 2001 - 157446 号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、上記のようなフィードバック電圧 - スイッチング周波数特性 ( 以下、 F B 電圧 - 周波数特性と記す ) に従って、出力電圧制御を行うように構成した A C - D C コンバータにおいては、例えばノイズ対策でスイッチング周波数を変更したい場合や小型化のために小さなトランスを使用したいような要求がある場合に、対応することができないという課題がある。 40

【0007】

本発明は上記のような背景の下になされたもので、その目的とするところは、スイッチング周波数制御特性を外部からの設定で変更することができ、電源装置のノイズ対策や小型化への対応のためにスイッチング周波数を容易に変更することができる電源制御用半導体装置を提供することにある。 50

## 【課題を解決するための手段】

## 【0008】

上記目的を達成するため本発明は、

電圧変換用のトランスの一次側巻線に間欠的に電流を流すためのスイッチング素子を、前記トランスの一次側巻線に流れる電流に比例した電圧と前記トランスの二次側からの出力検出信号とに応じてオン、オフ制御する駆動パルスを生成し出力する電源制御用半導体装置であって、

周波数可変な発振回路を備え前記スイッチング素子を周期的にオンさせるタイミングを与えるクロック信号を発生するクロック発生回路と、

前記トランスの一次側巻線に流れる電流に比例した電圧と前記トランスの二次側からの出力検出信号に基づいて前記スイッチング素子をオフさせるタイミングを与える電圧／電流制御回路と、

前記二次側からの出力検出信号に応じて前記発振回路の発振周波数を変化させる周波数制御回路と、

外部から設定情報を与えるための設定端子と、を備え、

前記周波数制御回路は、前記設定端子の状態に応じて、出力検出信号対発振周波数特性を変更可能であり、

前記出力検出信号対発振周波数特性は、第1特性と第2特性の2つであり、前記出力検出信号が所定の第1レベルよりも低い領域では第1周波数に固定され、前記出力検出信号が前記第1レベルよりも高い第2レベルよりも高い領域では第2周波数に固定され、

前記第1特性の前記第1周波数と前記第2特性の前記第1周波数は同一である一方、前記第1特性の前記第2周波数と前記第2特性の前記第2周波数は異なる値に設定され、前記出力検出信号が前記第1レベルと第2レベルとの間にあるときは前記出力検出信号の変化に対して発振周波数が直線的に変化するように構成した。

## 【0009】

上記した構成によれば、周波数可変な発振回路と、二次側からの出力検出信号に応じて発振回路の発振周波数を変化させる周波数制御回路とを備え、周波数制御回路は設定端子の状態（外付け抵抗の抵抗値）に応じて出力検出信号対発振周波数特性を変更するので、スイッチング周波数制御特性を外部からの設定で変更することができ、電源装置のノイズ対策や小型化への対応のためにスイッチング周波数を容易に変更することができる。

## 【0010】

また、下限のスイッチング周波数と上限のスイッチング周波数が異なる任意の特性を選択し、選択した特性に従ったスイッチング制御を行わせることができる。

## 【0011】

さらに、下限のスイッチング周波数は同一で上限のスイッチング周波数が異なるいずれかの特性に従ったスイッチング制御を行うことができる。

## 【0012】

本出願の他の発明は、

電圧変換用のトランスの一次側巻線に間欠的に電流を流すためのスイッチング素子を、前記トランスの一次側巻線に流れる電流に比例した電圧と前記トランスの二次側からの出力検出信号とに応じてオン、オフ制御する駆動パルスを生成し出力する電源制御用半導体装置であって、

周波数可変な発振回路を備え前記スイッチング素子を周期的にオンさせるタイミングを与えるクロック信号を発生するクロック発生回路と、

前記トランスの一次側巻線に流れる電流に比例した電圧と前記トランスの二次側からの出力検出信号に基づいて前記スイッチング素子をオフさせるタイミングを与える電圧／電流制御回路と、

前記二次側からの出力検出信号に応じて前記発振回路の発振周波数を変化させる周波数制御回路と、

外部から設定情報を与えるための設定端子と、を備え、

10

20

30

40

50

前記周波数制御回路は、

前記出力検出信号に応じた信号と所定の基準電圧とを入力とし、前記出力検出信号に応じた信号に比例した電圧を出力する非反転增幅回路と、

前記非反転增幅回路の出力をインピーダンス変換して前記発振回路へ供給するバッファ回路と、を備え、前記設定端子の状態に応じて、出力検出信号対発振周波数特性を変更可能であり、

前記非反転增幅回路は、前記設定端子の状態に応じて増幅率が可変であるようにした。

これにより、スイッチング周波数制御特性を外部からの設定で変更することができ、電源装置のノイズ対策や小型化への対応のためにスイッチング周波数を容易に変更することができる上、既存の回路技術を組み合わせて、外部からの設定で発振回路の周波数を変更することができる周波数制御回路を容易に実現することができる。

10

**【発明の効果】**

**【0013】**

本発明によれば、電圧変換用のトランスを備え一次側巻線に流れる電流をオン、オフして出力を制御する絶縁型直流電源装置の制御用半導体装置において、電源装置のノイズ対策や小型化への対応のためにスイッチング周波数を容易に変更することができるという効果がある。

**【図面の簡単な説明】**

**【0014】**

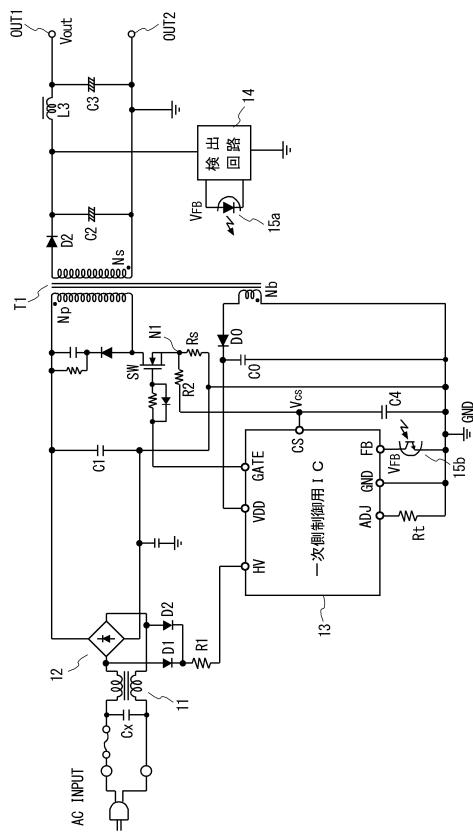

【図1】本発明に係る絶縁型直流電源装置としてのAC - DCコンバータの一実施形態を示す回路構成図である。

20

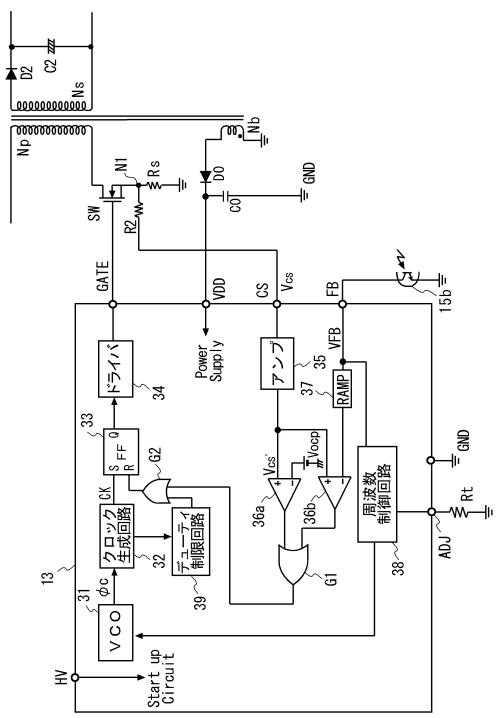

【図2】図1のAC - DCコンバータにおけるトランスの一次側スイッチング電源制御回路(電源制御用IC)の構成例を示すブロック図である。

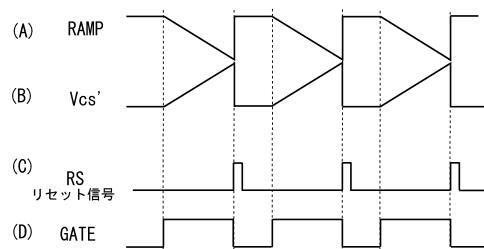

【図3】実施例の電源制御用ICにおける各部の電圧の変化の様子を示す波形図である。

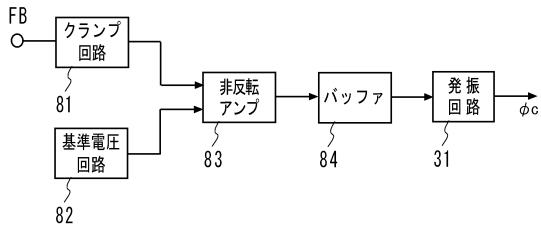

【図4】電源制御用ICにおける周波数制御回路の構成例を示すブロック図である。

【図5】周波数制御回路の具体的な回路構成例を示す回路構成図である。

【図6】周波数制御回路を構成する上下限クランプ回路の構成の変形例を示す回路構成図である。

【図7】実施例の電源制御用ICにおけるスイッチング周波数とフィードバック電圧VFBの関係を示す特性図である。

30

【図8】図5の周波数制御回路を構成するクランプ回路の具体的な回路構成例を示す回路構成図である。

**【発明を実施するための形態】**

**【0015】**

以下、本発明の好適な実施形態を図面に基づいて説明する。

図1は、本発明を適用した絶縁型直流電源装置としてのAC - DCコンバータの一実施形態を示す回路構成図である。

**【0016】**

この実施形態のAC - DCコンバータは、ノーマルモードノイズを減衰するためにAC端子間に接続されたXコンデンサCxと、コモンモードコイルなどからなるノイズ遮断用のラインフィルタ11と、交流電圧(AC)を整流するダイオード・ブリッジ回路12と、整流後の電圧を平滑する平滑用コンデンサC1と、一次側巻線Npと二次側巻線Nsおよび補助巻線Nbとを有する電圧変換用のトランスT1と、このトランスT1の一次側巻線Npと直列に接続されたNチャネルMOSFETからなるスイッチングトランジスタSWと、該スイッチングトランジスタSWを駆動する電源制御回路13を有する。この実施形態では、電源制御回路13は、単結晶シリコンのような1個の半導体チップ上に半導体集積回路(以下、電源制御用ICと称する)として形成されている。

40

**【0017】**

上記トランスT1の二次側には、二次側巻線Nsと直列に接続された整流用ダイオードD2と、このダイオードD2のカソード端子と二次側巻線Nsの他方の端子との間に接続

50

された平滑用コンデンサC2とが設けられ、一次側巻線Npに間歇的に電流を流すことで二次側巻線Nsに誘起される交流電圧を整流し平滑することによって、一次側巻線Npと二次側巻線Nsとの巻線比に応じた直流電圧Voutを出力する。

【0018】

さらに、トランジスタT1の二次側には、一次側のスイッチング動作で生じたスイッチングリップル・ノイズ等を遮断するためのフィルタを構成するコイルL3およびコンデンサC3が設けかれているとともに、出力電圧Voutを検出するための検出回路14と、該検出回路14に接続され検出電圧に応じた信号を電源制御用IC13へ伝達するフォトカプラの発光側素子としてのフォトダイオード15aが設けられている。そして、一次側には、上記電源制御用IC13のフィードバック端子FBと接地点との間に接続され上記検出回路14からの信号を受信する受光側素子としてのフォトトランジスタ15bが設けられている。

10

【0019】

また、この実施形態のAC-DCコンバータの一次側には、上記補助巻線Nbと直列に接続された整流用ダイオードD0と、このダイオードD0のカソード端子と接地点GNDとの間に接続された平滑用コンデンサC0とからなる整流平滑回路が設けられ、該整流平滑回路で整流、平滑された電圧が上記電源制御用IC13の電源電圧端子VDDに印加されている。

一方、電源制御用IC13には、ダイオード・ブリッジ回路12で整流される前の電圧がダイオードD11, D12および抵抗R1を介して印加される高圧端子HVが設けられており、電源投入時（プラグが差し込まれた直後）は、この高圧端子HVからの電圧で動作することができるよう構成されている。

20

【0020】

さらに、本実施形態においては、スイッチングトランジスタSWのソース端子と接地点GNDとの間に電流検出用の抵抗Rsが接続されているとともに、スイッチングトランジスタSWと電流検出用抵抗RsとのノードN1と電源制御用IC13の電流検出端子CSとの間に抵抗R2が接続されている。さらに、電源制御用IC13の電流検出端子CSと接地点との間にはコンデンサC4が接続され、抵抗R2とコンデンサC4によりローパスフィルタが構成されるようになっている。

【0021】

30

次に、上記電源制御用IC13の具体的な構成例について説明する。

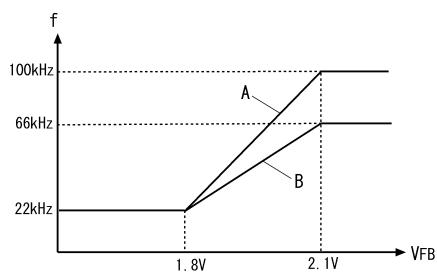

本実施形態の電源制御用IC13は、外部からスイッチング周期を設定するための外部設定端子ADJを備えるとともに、該外部設定端子ADJの設定状態に応じて、予め用意されている2つのFB電圧-周波数特性のうちいずれか一方を選択し、選択された特性に従って出力の発振周波数制御を行うように構成されている。具体的には、図7に示す2つの特性AまたはBのうちいずれか一方が選択可能である。

【0022】

上記FB電圧-周波数特性AとBは、フィードバック電圧VFBがVFB1（例えば1.8V）以下では、特性A, B共に22kHzのような同一かつ一定の周波数でPWM制御を行い、VFB2（例えば2.1V）以上では特性Aは100kHzのような一定の周波数、特性Bは66kHzのような一定の周波数でそれぞれPWM制御を行うとともに、VFB1～VFB2間ではフィードバック電圧VFBの変化に応じて周波数が直線的に変化するような制御を行う。

40

なお、制御が切り替わる上記VFB1（1.8V）, VFB2（2.1V）やVFB1以下の領域における固定周波数（22kHz）、VFB2以上の領域における固定周波数（66kHz, 100kHz）は一例であって、そのような数値に限定されるものではない。

【0023】

図2には、上記のような機能を備える本実施形態の電源制御用IC13の構成例が示されている。

図2に示すように、本実施例の電源制御用IC13は、フィードバック端子FBの電圧

50

VFBに応じた周波数で発振する発振回路31と、該発振回路31で生成された発振信号cに基づいて一次側スイッチングトランジスタSWをオンさせるタイミングを与えるクロック信号CKを生成するワンショットパルス生成回路のような回路からなるクロック生成回路32と、クロック信号CKによってセットされるRS・フリップフロップ33と、該フリップフロップ33の出力に応じてスイッチングトランジスタSWの駆動パルスGATEを生成するドライバ(駆動回路)34を備える。本明細書では、上記発振回路31とクロック生成回路32とを合わせたものをクロック発生回路と称する。

【0024】

また、電源制御用IC13は、電流検出端子CSに入力されている電圧V<sub>CS</sub>を増幅する非反転増幅回路からなるアンプ35と、該アンプ35により増幅された電位V<sub>CS'</sub>と過電流状態の監視のための比較電圧(スレッシホールド電圧)V<sub>OCP</sub>とを比較する電圧比較回路としてのコンパレータ36aと、フィードバック端子FBの電圧V<sub>FB</sub>に基づいて図3(A)に示すような所定の波形の電圧RAMPを生成する波形生成回路37と、前記アンプ35により増幅された図3(B)に示すような波形の電位V<sub>CS'</sub>と波形生成回路37により生成された波形RAMPとを比較するコンパレータ36bと、コンパレータ36aと36bの出力の論理和をとるORゲートG1を備える。本実施例の電源制御用IC13においては、図3(A)の電圧RAMPは、FB電圧からある一定の傾きをもって電圧が低下するように生成される。

【0025】

上記ORゲートG1の出力RS(図3(C)参照)が上記フリップフロップ33のリセット端子に入力されることで、スイッチングトランジスタSWをオフさせるタイミングを与えるように構成されている。なお、フィードバック端子FBと内部電源電圧端子と間にはプルアップ抵抗が設けられており、フォトトランジスタ15bに流れる電流は該抵抗によって電圧に変換される。また、波形生成回路37を設けているのは、サブハーモニック発振対策のためであり、電圧V<sub>FB</sub>を直接あるいはレベルシフトしてコンパレータ36bへ入力するように構成しても良い。

【0026】

また、本実施例の電源制御用IC13は、フィードバック端子FBの電圧V<sub>FB</sub>と外部設定端子ADJの電圧を監視して、これらの端子の電圧に応じて前記発振回路31の発振周波数すなわちスイッチング周波数を、図7に示すような特性に従って変化させる周波数制御回路38を備える。図示しないが、外部設定端子ADJと内部電源電圧端子と間にはプルアップ抵抗もしくは定電流源が設けられており、外部設定端子ADJに接続される外付け抵抗Rtに流れる電流が該抵抗によって電圧に変換され、周波数制御回路38は外部設定端子ADJの電圧に応じて制御する発振周波数の特性をAまたはBに切り替えるように構成されている。これにより、ユーザは、外部設定端子ADJに接続する外付け抵抗Rtの抵抗値を選択することで、FB電圧-周波数特性を切り替えることができる。

【0027】

さらに、本実施例の電源制御用IC13には、上記クロック生成回路32から出力されるクロック信号CKに基づいて、駆動パルスGATEのデューティ(T<sub>on</sub> / T<sub>cycle</sub>)が予め規定された最大値(例えば85%~90%)を超えないように制限をかけるための最大デューティリセット信号を生成するデューティ制限回路39が設けられており、デューティ制限回路39から出力される最大デューティリセット信号を、ORゲートG2を介して上記フリップフロップ33に供給してパルスが最大デューティに達した場合にはその時点でリセットさせることでスイッチングトランジスタSWを直ちにオフさせるように構成されている。

【0028】

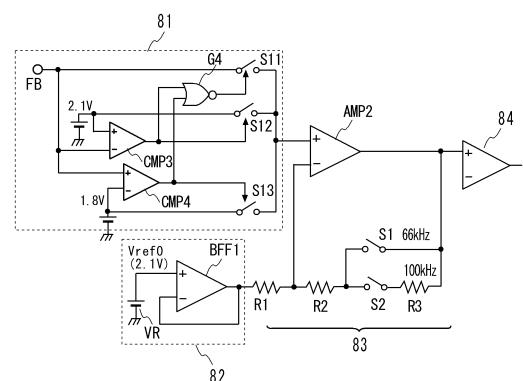

図4には、本実施形態の電源制御用IC13を構成する周波数制御回路38の構成例が示されている。

図4に示すように、周波数制御回路38は、フィードバック端子FBの電圧V<sub>FB</sub>が所定の電圧V<sub>FB1</sub>(1.8V)以下である場合にはV<sub>FB1</sub>にクランプするとともに、V<sub>FB2</sub>(2.1V)

10

20

30

40

50

) 以上である場合には VFB2 (2.1V) にクランプする上下限クランプ回路 8 1 と、図 7 に示す FB 電圧 - 周波数特性のリニアな領域 VFB1 ~ VFB2 のスタートとなるポイントに対応する基準電圧 Vref0 (例えば 2.1V) を発生する基準電圧回路 8 2 と、上下限クランプ回路 8 1 を通過した電圧 (1.8V ~ 2.1V) に比例した電圧 (0.65V ~ 2.1V / 0.45V ~ 2.1V) を生成する非反転増幅回路 8 3 と、該非反転増幅回路 8 3 の出力をインピーダンス変換して発振回路 3 1 へ供給するバッファ回路 8 4 とを備える。

#### 【0029】

一方、発振回路 3 1 は、上記バッファ回路 8 4 の出力に応じた周波数の発振信号 (クロック信号 c) を生成するように構成されている。

また、この実施例の周波数制御回路 3 8 は、外部設定端子 ADJ の電圧に応じて非反転増幅回路 8 3 の増幅率すなわち図 7 に示す FB 電圧 - 周波数特性線のリニアな領域 VFB1 ~ VFB2 での直線の傾きを切り替えることができるように構成されている。10

#### 【0030】

このように、図 7 の FB 電圧 - 周波数特性 A, B のいずれかを選択できるように構成されていることによって、ノイズ対策でスイッチング周波数を変更したい場合や小型化のために小さなトランジistorを使用したい要求がある場合に、電源装置の設計者は外部設定端子 ADJ に接続する外付け抵抗 R t の抵抗値を変えるだけで容易に対応することができるという利点がある。

なお、図 7 は、電源制御用 IC 1 3 にとっては FB 電圧 - 周波数特性を示すものであるが、二次側からのフィードバック電圧 VFB は負荷電流に対応しているので、電源としては負荷電流 - 周波数特性を示しているとみなすことができる。20

#### 【0031】

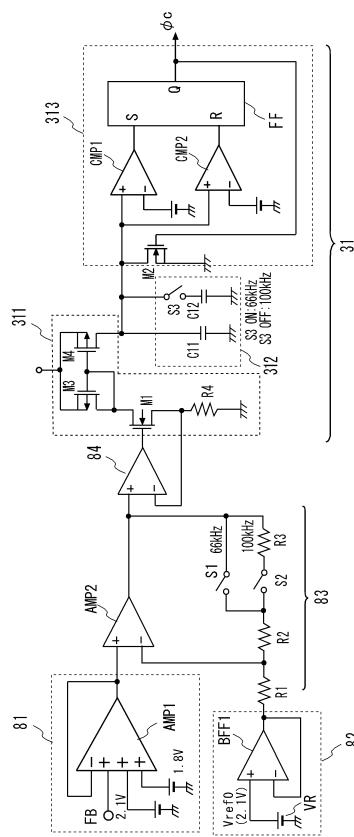

図 5 には、図 4 の周波数制御回路 3 8 の具体的な回路構成例が示されている。

図 5 において図 4 と同一の回路部分には同一の符号が付されている。すなわち、符号 8 1 は上下限クランプ回路、符号 8 2 は基準電圧回路、符号 8 3 は非反転増幅回路、符号 8 4 はバッファ回路、符号 3 1 は発振回路である。

図 5 に示すように、上下限クランプ回路 8 1 は 4 入力の差動増幅回路 AMP 1 で構成されており、反転入力端子に自身の出力電圧がフィードバックされ、電源制御用 IC のフィードバック端子 FB の電圧 VFB がクランプ電圧 VFB1 と VFB2 との間の電圧範囲 (1.8V ~ 2.1V) にあるときは、フィードバック電圧 VFB をそのまま後段の非反転増幅回路 8 3 の非反転入力端子側へ伝達するバッファ (ボルテージフォロワ) として動作し、フィードバック電圧 VFB がクランプ電圧 VFB1 (1.8V) 以下である場合には VFB1 にクランプするとともに、VFB が VFB2 (2.1V) 以上である場合には VFB2 (2.1V) にクランプした電圧を出力するように構成されている。30

#### 【0032】

基準電圧回路 8 2 は、基準電圧源 VR とバッファ (ボルテージフォロワ) BFF 1 から構成され、基準電圧源 VR が発生する基準電圧 Vref0 (2.1V) をそのまま非反転増幅回路 8 3 の反転入力端子側へ供給する。

非反転増幅回路 8 3 は、2 入力の差動増幅回路 AMP 2 と、基準電圧回路 8 2 と反転入力端子との間に接続された入力抵抗 R 1 と、出力端子と反転入力端子との間に直列に接続された帰還抵抗 R 2, R 3 と、帰還抵抗 R 3 と並列に接続されたスイッチ S 1 および帰還抵抗 R 3 と直列に接続されたスイッチ S 2 とから構成されている。スイッチ S 1 と S 2 は、外部設定端子 ADJ の電位に応じていずれか一方が選択的にオンされるように構成されており、スイッチ S 1 がオンされると R 2 のみが帰還抵抗として接続された状態 (増幅率が小さい状態) となり、スイッチ S 2 がオンされると R 2 および R 3 が帰還抵抗として接続された状態 (増幅率が大きい状態) となる。40

#### 【0033】

また、スイッチ S 1 と S 2 のいずれがオンされている場合にも、フィードバック電圧 VFB が 2.1V のときは非反転増幅回路 8 3 の出力電圧は Vref0 (2.1V) となるが、スイッチ S 1 がオンされている状態 (66kHz モード) でフィードバック電圧 VFB として 1.8V が入力50

されたときは非反転増幅回路83の出力電圧は0.65Vとなり、スイッチS2がオンされている状態(100kHzモード)でフィードバック電圧VFBとして2.1Vが入力されたときは非反転増幅回路83の出力電圧は0.45Vとなるように、抵抗R1, R2, R3の抵抗値が設定されている。なお、フィードバック電圧VFBが1.8V~2.1Vの範囲では、フィードバック電圧VFBに比例して変化する電圧が非反転増幅回路83から出力される。そして、この非反転増幅回路83の出力は、バッファ回路84を介して発振回路31へ供給される。バッファ回路84はボルテージフォロワによって構成されている。

#### 【0034】

発振回路31は、バッファ回路84によって、非反転入力端子と同電位となるように制御されたMOSトランジスタM1のソース電圧と対GNDに接続されている抵抗R4に10

流れる電流で決まる電流を流す電流源回路311と、該電流源回路311からの電流によって充電される容量C11, C12およびC12と直列に接続されたスイッチS3からなる周波数切替え部312と、上記容量C11, C12の電荷を放電するための放電用MOSトランジスタM2および2つのコンパレータCMP1, CMP2とフリップフロップFF1からなるオシレータ部313とを備えている。

#### 【0035】

そして、上記フリップフロップFF1の出力が放電用MOSトランジスタM2のゲート端子に印加され、容量C11, C12の充電と放電を繰り返すことにより、内部で三角波を生成し所定の周波数のクロック信号を出力するようになっている。なお、電流源回路311は、MOSトランジスタM3のドレイン電流を折り返すため、MOSトランジスタM3, M4からなるカレントミラー回路を備えている。20

上記説明より分かるように、電流源回路311は、フィードバック電圧VFBに応じた電流を流すこととなる。その結果、オシレータ部313で生成される発振信号cはフィードバック電圧VFBに応じた周波数となる。また、スイッチS3がオン状態にされるとC11, C12の合計容量値が増加して発振周波数は低くなり、スイッチS3がオフ状態にされるとC11, C12の合計容量値が減少して発振周波数は高くなる。C11, C12の容量比が例えば1:2に設定されることで、切替え前後の周波数比は2:3となる。この比は、上限周波数の66kHzと100kHzに対応する。

#### 【0036】

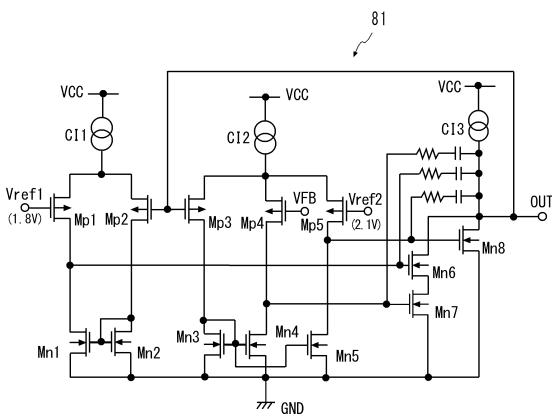

図8には、上記上下限クランプ回路81の具体的な回路の例が示されている。

30

図8の上下限クランプ回路81は、互いにソース端子が結合された2個のMOSトランジスタMp1, Mp2を有する第1差動入力段81Aと、互いにソース端子が結合された3個のMOSトランジスタMp3, Mp4, Mp5を有する第2差動入力段81Bと、直列形態に接続され第1差動入力段81Aの出力ノード(Mp1のドレイン)と第2差動入力段81Bの第1出力ノード(Mp4のドレイン)の電位がゲート端子にそれぞれ印加されたMOSトランジスタMn6, Mn7を有する出力段81Cとから構成されている。

そして、第1差動入力段81AのMOSトランジスタMp1のゲート端子に基準電圧Vref1(1.8V)が印加され、第2差動入力段81BのMOSトランジスタMp4とMp5のゲート端子にそれぞれフィードバック電圧VFBと基準電圧Vref2(2.1V)が印加されている。

40

#### 【0037】

また、出力段81Cは、内部電源端子VCCと接地点GNDとの間に直列に接続された定電流源CI3およびMOSトランジスタMn8を備え、該トランジスタMn8のゲート端子に上記第2差動入力段81Bの第2出力ノード(Mp5のドレイン)の電位が印加され、Mn8のドレイン端子が出力端子OUTに接続されるとともに、入力段81Aに対する出力トランジスタのMn6と、入力段81Bに対する出力トランジスタのMn7, Mn8が設けられており、出力段81Cの出力電圧が上記第1差動入力段81AのMOSトランジスタMp2のゲート端子と第2差動入力段81BのMOSトランジスタMp3のゲート端子にフィードバックされている。

これにより、図8の上下限クランプ回路81は、上述したように、フィードバック電圧

50

VFBをそのまま後段の回路へ伝達するバッファとして動作するとともに、VFBがクランプ電圧VFB1(1.8V)以下である場合にはVFB1にクランプし、VFBがVFB2(2.1V)以上である場合にはVFB2(2.1V)にクランプするように動作する。

さらに、出力段81Cを構成する上記MOSトランジスタMn6, Mn7, Mn8のゲート・ドレイン間には、位相補償用の抵抗および容量が各々接続されている。

#### 【0038】

なお、図8に示す周波数制御回路38の構成は一例であって上記構成に限定されるものではない。例えば、上下限クランプ回路81は、図6に示すように、フィードバック電圧VFBまたは基準電圧Vref1(1.8V)またはVref2(2.1V)のいずれかの電圧を伝達する3つのスイッチS11, S12, S13と、フィードバック電圧VFBと基準電圧Vref1またはVref2を比較する2つのコンパレータCMP3, CMP4と、CMP3とCMP4の出力の論理和をとってスイッチS13をオン、オフ制御するNORゲートG4とからロジック回路として構成することもできる。10

#### 【0039】

また、図5の周波数制御回路38における発振回路31は、容量C11, C12を切り替えることで発振周波数を切り替えるように構成されているが、容量を切り替える代わりに電流源回路311の電流値を切替え可能に構成して、電流源回路311から容量C11を充電するために流す電流値を切り替えることで発振周波数を切り替えるようにしても良い。オシレータ部313も、コンパレータとフリップフロップからなる回路の代わりに、複数のインバータを直列に接続してなるリングオシレータを用いて構成するようにしても良い。20

#### 【0040】

以上本発明者によってなされた発明を実施形態に基づき具体的に説明したが、本発明は前記実施形態に限定されるものではない。例えば、前記実施形態では、図3に示すような所定の電圧(1.8V)以下では同一の周波数に固定される2つの特性に従った周波数制御を行う周波数制御回路について説明したが、所定の電圧(1.8V)以下でそれぞれ異なる周波数に固定される2つの特性に従った周波数制御を行うように構成しても良い。また、制御可能なFB電圧-周波数特性は2つに限定されず、3以上であっても良い。

#### 【0041】

また、前記実施形態では、トランスの一次側巻線に間歇的に電流を流すスイッチングトランジスタSWを、電源制御用IC13とは別個の素子としているが、このスイッチングトランジスタSWを電源制御用IC13に取り込んで、1つの半導体集積回路として構成してもよい。30

さらに、前記実施形態では、本発明をフライバック方式のAC-DCコンバータを構成する電源制御用ICに適用した場合について説明したが、本発明はフォワード型や疑似共振型のAC-DCコンバータを構成する電源制御用ICにも適用することができる。

#### 【符号の説明】

#### 【0042】

- 1 1 ラインフィルタ

- 1 2 ダイオード・ブリッジ回路(整流回路)

- 1 3 電源制御回路(電源制御用IC)

- 1 4 二次側検出回路(検出用IC)

- 1 5 a フォトカプラの発光側ダイオード

- 1 5 b フォトカプラの受光側トランジスタ

- 3 1 発振回路

- 3 2 クロック生成回路

- 3 4 ドライバ(駆動回路)

- 3 5 アンプ(増幅回路)

- 3 6 a 過電流検出用コンパレータ(過電流検出回路)

- 3 6 b 電圧/電流制御用コンパレータ(電圧/電流制御回路)

- 3 7 波形生成回路

10

20

30

40

50

- 3 8 周波数制御回路

3 9 デューティ制限回路

8 1 クランプ回路

8 2 基準電圧回路

8 3 非反転増幅回路

8 4 バッファ回路

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(56)参考文献 特開2001-157446(JP,A)

特開2004-040856(JP,A)

特開2013-062930(JP,A)

特開2016-135036(JP,A)

(58)調査した分野(Int.Cl., DB名)

H02M 3/00 - 3/44