(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2008-519434

(P2008-519434A)

(43) 公表日 平成20年6月5日(2008.6.5)

| (51) Int.Cl.          | F 1        |     | テーマコード (参考) |

|-----------------------|------------|-----|-------------|

| HO1L 29/786 (2006.01) | HO1L 29/78 | 621 | 5FO32       |

| HO1L 21/764 (2006.01) | HO1L 21/76 | A   | 5FO48       |

| HO1L 21/762 (2006.01) | HO1L 21/76 | D   | 5F110       |

| HO1L 21/76 (2006.01)  | HO1L 27/12 | F   |             |

| HO1L 27/12 (2006.01)  | HO1L 29/78 | 620 |             |

審査請求 未請求 予備審査請求 未請求 (全 16 頁) 最終頁に続く

|               |                              |          |                                                                                                            |

|---------------|------------------------------|----------|------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2007-539143 (P2007-539143) | (71) 出願人 | 504199127<br>フリースケール セミコンダクター イン<br>コーポレイテッド<br>アメリカ合衆国 78735 テキサス州<br>オースティン ウィリアム キャノン<br>ドライブ ウエスト 6501 |

| (86) (22) 出願日 | 平成17年10月25日 (2005.10.25)     | (74) 代理人 | 100089705<br>弁理士 社本 一夫                                                                                     |

| (85) 翻訳文提出日   | 平成19年7月2日 (2007.7.2)         | (74) 代理人 | 100140109<br>弁理士 小野 新次郎                                                                                    |

| (86) 國際出願番号   | PCT/US2005/038847            | (74) 代理人 | 100075270<br>弁理士 小林 泰                                                                                      |

| (87) 國際公開番号   | W02006/050051                | (74) 代理人 | 100080137<br>弁理士 千葉 昭男                                                                                     |

| (87) 國際公開日    | 平成18年5月11日 (2006.5.11)       |          |                                                                                                            |

| (31) 優先権主張番号  | 10/977,266                   |          |                                                                                                            |

| (32) 優先日      | 平成16年10月29日 (2004.10.29)     |          |                                                                                                            |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                                            |

最終頁に続く

(54) 【発明の名称】最適化された応力効果に関する2重トレンチを備えたトランジスタ構造とその方法

## (57) 【要約】

半導体デバイス構造体の一部を形成するための方法は、半導体活性層、絶縁層、および、半導体基板を有する半導体 オン - 絶縁体基板を提供することを有する。第1の絶縁トレンチは、半導体活性層内に形成され、ストレッサー材料は、第1のトレンチの底部に堆積され、ストレッサー材料は、デュアルユース薄膜を含む。第2の絶縁トレンチは、半導体活性層内に形成され、第2の絶縁トレンチは、第2のトレンチの底部にストレッサー材料がない。第1および第2の絶縁トレンチにおけるストレッサー材料の有無により、(i) 1またはそれ以上のN型またはP型の半導体デバイス構造で、(ii) 1またはそれ以上の幅方向またはチャネル方向に関して、(iii) 1またはそれ以上の<100>もしくは<110>半導体 オン - 絶縁体基板の応力利点を最適化するために、異なる応力をそれぞれ提供する。

## 【特許請求の範囲】

## 【請求項 1】

半導体活性層、絶縁層、および、半導体基板を有する半導体 オン - 絶縁体基板を提供するステップと、

前記半導体活性層内に第 1 の絶縁トレンチを形成するステップと、

前記第 1 のトレンチの底部に、デュアルユース薄膜を含むストレッサー材料を堆積させるステップと、

前記半導体活性層内に第 2 の絶縁トレンチを形成するステップとを有し、

前記第 2 の絶縁トレンチは、前記第 2 のトレンチの底部にストレッサー材料がなく、

前記第 1 および第 2 の絶縁トレンチにおけるストレッサー材料の有無により、

10

(i) 1 またはそれ以上の N 型または P 型の半導体デバイス構造で、

(ii) 1 またはそれ以上の幅方向またはチャネル方向に関して、

(iii) 1 またはそれ以上の <100> もしくは <110> 半導体 オン - 絶縁体基板の応力利点を最適化するために

異なる応力をそれぞれ提供する

ことを特徴とする半導体デバイス構造体の一部を形成するための方法。

## 【請求項 2】

前記デュアルユース薄膜が、圧縮応力を誘導するトレンチライナーを防止し、特定のデバイスおよび方位に異なる応力適用することを可能にするように前記第 1 の絶縁トレンチの底部に形成された窒化物層を有することを特徴とする請求項 1 に記載の方法。

20

## 【請求項 3】

前記第 1 のトレンチを形成するステップが、第 1 の波長でのパターニングおよびエッチングプロセスを使用することを含み、更に、前記第 1 の波長でのパターニングおよびエッティングプロセスが、248 nm 深紫外線パターニングおよびエッティングプロセスを含み、

第 2 の絶縁トレンチを形成するステップが、第 2 の波長でのパターニングおよびエッティングプロセスを使用することを含み、前記第 2 の波長が前記第 1 の波長と異なり、前記第 2 の波長でのパターニングおよびエッティングプロセスが、193 nm 深紫外線パターニングプロセスを含むことを特徴とする請求項 1 に記載の方法。

## 【請求項 4】

前記デュアルユース薄膜が、ストレッサー材料として、および、反射防止膜として使用するのに適した材料からなり、更に、前記デュアルユース薄膜が窒化物からなることを特徴とする請求項 1 に記載の方法。

30

## 【請求項 5】

前記第 1 および第 2 のトレンチの側壁部分に沿って前記第 1 および第 2 のトレンチのそれぞれにトレンチライナーを形成するステップと、を更に有し、

前記第 1 のトレンチの底部の上に横たわる前記デュアルユース薄膜によって、前記第 1 のトレンチのトレンチライナーが前記第 1 のトレンチの側壁に沿って完全に伸びるのを防止し、前記トレンチライナーは前記側壁の頂部から側壁の下方部分に向けて伸び、側壁の下方部分は、第 1 のトレンチ内でデュアルユース薄膜の頂部と接触することを特徴とする請求項 1 に記載の方法。

40

## 【請求項 6】

半導体活性化層、絶縁層、および、半導体基板を備えた半導体 - オン - 絶縁体を提供するステップと、

前記半導体活性層内に第 1 の絶縁トレンチを形成するステップと、

前記第 1 のトレンチの底部にデュアルユース薄膜を含むストレッサー材料を堆積するステップと、

前記半導体活性層内に第 2 の絶縁トレンチを形成するステップとを有し、

前記第 2 の絶縁トレンチが、前記第 2 のトレンチの底部にストレッサー材料を有さず、前記第 1 および第 2 の絶縁トレンチにおけるストレッサー材料の有無により、

(i) 1 またはそれ以上の N 型または P 型の半導体デバイス構造の

50

(ii) 1またはそれ以上の幅方向またはチャネル方向に関して、

(iii) 1またはそれ以上の<100>もしくは<110>半導体 オン - 絶縁体基板の応力利点を最適化するために、異なる応力をそれぞれ提供し、

前記半導体デバイス構造体の一部が、前記半導体活性層内に前記第1および第2の活性半導体領域を備えた第1および第2のトランジスタ構造を含み、前記第1のトランジスタ構造が、前記第1のトランジスタ構造の幅方向において制御された応力機構を含む、ことを特徴とする半導体デバイス構造体の一部を形成するための方法。

#### 【請求項 7】

前記第1のトランジスタ構造体の制御された応力機構が、前記第1のトランジスタ構造体の幅方向における応力の緩和を提供するために第1および第2の応力緩和機構を含むことを特徴とする請求項6に記載の方法。 10

#### 【請求項 8】

前記第1の応力緩和機構が、前記第1のトランジスタ構造体の活性化半導体領域の外側にデュアルユース薄膜を含み、前記デュアルユース薄膜が更に、前記第1のトランジスタ構造体の第1の活性化半導体領域の少なくとも2つの側の部分に隣接した第3および第4のトレンチの底部に沿って配置され、

前記第2の応力緩和機構が、前記第1のトランジスタ構造体の活性化半導体領域の内側に少なくとも1つの応力緩和および容量低減機構を含む、

ことを特徴とする請求項7に記載の方法。 20

#### 【請求項 9】

前記第1のトランジスタ構造体の制御された応力機構が、別の応力緩和および容量低減機構を更に含み、

前記別の応力緩和および容量低減機構が、前記半導体デバイス構造体の一部の幅方向において応力の更なる緩和を提供する、

ことを特徴とする請求項7に記載の方法。 30

#### 【請求項 10】

前記半導体活性層が、<110>結晶方位を有し、

前記活性化半導体領域のチャネル領域に渡って伸びることなく、前記活性化半導体領域だけのソース / ドレインの部分内に包含された複数の応力緩和および容量低減機構を提供するステップを更に有し、

前記複数の応力緩和および容量低減機構が前記トランジスタ構造体のゲート電極に平行に沿って配置され、

前記複数の応力緩和および容量低減機構が前記第1のトランジスタ構造体のチャネル方向において応力の緩和を提供する

ことを特徴とする請求項6に記載の方法。 40

#### 【請求項 11】

半導体活性層、絶縁層、および、半導体基板を有する半導体 オン - 絶縁体基板と、

前記半導体活性層内に形成された第1の絶縁トレンチと、を有し、

前記第1の絶縁トレンチは、該第1のトレンチの底部に堆積されストレッサー材料を備え、該ストレッサー材料はデュアルユース薄膜を含み、

前記半導体活性層内に形成された第2の絶縁トレンチと、を有し、

前記第2の絶縁トレンチは、前記第2のトレンチの底部にストレッサー材料がなく、

前記第1および第2の絶縁トレンチにおけるストレッサー材料の有無により、

(i) 1またはそれ以上のN型またはP型の半導体デバイス構造で、

(ii) 1またはそれ以上の幅方向またはチャネル方向に関して、

(iii) 1またはそれ以上の<100>もしくは<110>半導体 オン - 絶縁体基板の応力利点を最適化するために

異なる応力をそれぞれ提供する

ことを特徴とする半導体デバイス構造体。 50

#### 【請求項 12】

前記半導体活性化層内に第1及び第2の活性化半導体領域を各々備えた第1及び第2のトランジスタ構造を更に有し、

前記第1のトランジスタ構造が、第1のトランジスタ構造の幅方向に制御された応力機構を含む、ことを特徴とする請求項11に記載のデバイス構造体。

**【請求項13】**

前記第1のトランジスタ構造の制御された応力機構が、前記第1のトランジスタ構造の幅方向に応力の緩和を提供する、第1及び第2の応力緩和機構を含むことを特徴とする請求項11に記載のデバイス構造体。

**【請求項14】**

前記第1の応力緩和機構が、前記第1のトランジスタ構造の活性化半導体領域の外側にデュアルユース薄膜を含み、10

前記デュアルユース薄膜が更に、前記第1のトランジスタ構造の第1の活性化半導体領域の少なくとも2つの側の部分に隣接して配置されたトレンチの底部に沿って配置されていることを特徴とする請求項11に記載のデバイス構造体。

**【請求項15】**

前記第2の応力緩和機構が、前記第1のトランジスタ構造の活性化半導体領域の内側に少なくとも1つの応力緩和および容量低減機構を含むことを特徴とする請求項11に記載のデバイス構造体。

**【請求項16】**

前記第1のトランジスタ構造の活性化半導体領域が更に、前記活性化半導体領域の端に配置されたノッチを含み、20

前記ノッチが、前記活性化半導体領域のソース領域とドレイン領域との間にわたっていることを特徴とする請求項11に記載のデバイス構造体。

**【請求項17】**

前記第1の活性化半導体領域が、前記第1の応力緩和機構によって境界が定められており、更に、前記第1の応力緩和機構が、絶縁トレンチの底部に反射防止薄膜およびデュアルユース・ストレッサーを備えた絶縁トレンチを含む、

ことを特徴とする請求項11に記載のデバイス構造体。

**【請求項18】**

前記第1のトランジスタ構造の制御された応力機構が、第3の応力緩和および容量低減機構を含み、30

前記第3の応力緩和および容量低減機構は、半導体デバイス構造体の幅方向において更に応力の緩和を提供し、前記第3の応力緩和および容量低減機構は、前記半導体デバイス構造体のチャネル方向に延びる活性化半導体領域のエッジに沿って対向する端に配置される、ことを特徴とする請求項11に記載のデバイス構造体。

**【請求項19】**

前記第1のトランジスタ構造の制御された応力機構が更に別の応力緩和および容量低減機構を含み、前記別の応力緩和および容量低減機構が、前記半導体デバイス構造体の一部の幅方向において応力の緩和を更に提供することを特徴とする請求項11に記載のデバイス構造体。40

**【請求項20】**

前記半導体活性化層が、<110>結晶方位を有し、

更に、

前記活性化半導体領域のチャネル領域にわたって延びることなく、活性化半導体領域のみのソース／ドレイン領域の一部の内部に包含された複数の応力緩和および容量低減機構を有し、

前記複数の応力緩和および容量低減機構が前記第1のトランジスタ構造のゲート電極に平行に沿って配置され、前記複数の応力緩和および容量低減機構が、前記第1のトランジスタ構造のチャネル方向において応力の緩和を提供する、

ことを特徴とする請求項11に記載のデバイス構造体。50

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、概して半導体デバイスに関し、特に、<100>SOI基板上の最適化された応力効果に関する2重トレンチを備えたトランジスタ構造体および該トランジスタ構造体を作成する方法。

## 【背景技術】

## 【0002】

従来技術では、種々の形態のトレンチ絶縁および窒化物堆積が知られている。しかしながら、かかる周知技術は、異なるタイプのデバイスに異なる応力を異なる方位に同時に適用することができない。

10

## 【0003】

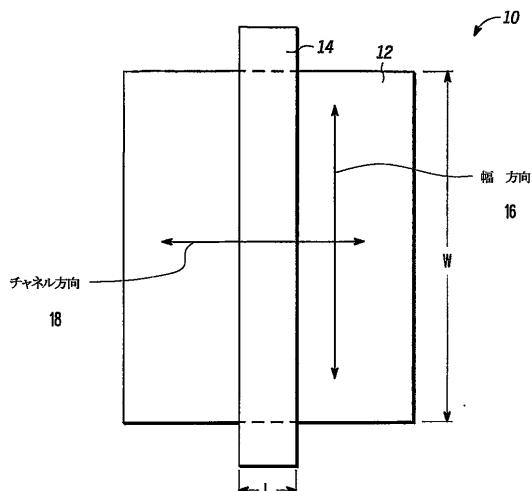

図1は、当該技術分野で周知のチャネル方向および幅方向を図示したCMOSトランジスタ10の平面図である。特に、CMOSトランジスタ10は、活性化領域12とゲート電極14を含み、ゲート誘電体(図示せず)が下に横たわる。活性化領域12は、幅方向に伸びる幅寸法Wによって特徴付けられ、幅方向は参考番号16によって示される。更に、活性化領域12は、適当な半導体材料からなる。ゲート電極14は、チャネル方向に伸びる長さ寸法Lによって特徴付けられ、チャネル方向は参考番号18によって示される。

## 【0004】

従って、従来技術の問題を克服した、改良されたトランジスタ構造およびそれを作成する方法を提供することが望まれる。

20

## 【発明の開示】

## 【課題を解決するための手段】

## 【0005】

ある実施形態では、半導体デバイス構造体の一部を形成するための方法は、半導体活性層、絶縁層、および、半導体基板を有する半導体 オン - 絶縁体基板を提供することを有する。第1の絶縁トレンチは、半導体活性層内に形成され、ストレッサー材料は、第1のトレンチの底部に堆積され、ストレッサー材料は、デュアルユース薄膜を含む。第2の絶縁トレンチは、半導体活性層内に形成され、第2の絶縁トレンチは、第2のトレンチの底部にストレッサー材料がない。第1および第2の絶縁トレンチにおけるストレッサー材料の有無により、(i) 1またはそれ以上のN型またはP型の半導体デバイス構造で、(ii) 1またはそれ以上の幅方向またはチャネル方向に関して、(iii) 1またはそれ以上の<100>もしくは<110>半導体 オン - 絶縁体基板の応力利点を最適化するために、異なる応力をそれぞれ提供する。

30

## 【発明を実施するための最良の形態】

## 【0006】

本発明の実施形態は、<100>SOI基板の応力利得を最適化させ最大にするために、異なるデバイス(N型およびP型)および異なる方位(幅方向または長さ方向)に異なる応力を適用するソリューションを提供する。例えば、本発明の実施形態は、ここで議論するように、デュアル(248nm / 193nm)フォトプロセスおよび異なるストレス効果にアドレスするように選択的な領域においてトレンチ絶縁および対応するナイトライド堆積を使用する。

40

## 【0007】

ある実施形態では、SOIのためのデュアルトレンチプロセスは、圧縮応力を導入するトレンチライナーを防止するように所望のトレンチ領域の底部に窒化物層を形成することと、それにより、特定のデバイスおよび方位に異なる応力を可能にさせることとを含む。さらに、この方法はまた、両方の波長に関して最適化された反射率を提供することにより、248nmおよび193nmのデュアルトレンチフォトプロセスを可能にする。

## 【0008】

図2は、種々のチャネル方位およびデバイスタイプに関する応力応答感度特性の表を示

50

す。特に、図2の表20は、チャネル方位22、デバイスタイプ24、好都合なチャネル応力26および好都合な幅応力28のカラムを含む。<110>のチャネル方位に関して、NMOSデバイスは、チャネル方向における引っ張り応力下で最高のパフォーマンスを示す。さらに、<110>のチャネル方位では、NMOSデバイスのパフォーマンスが、幅方向における応力に対して比較的小さな応答を有する。<110>のチャネル方位では、PMOSデバイスが、チャネル方向における圧縮応力下、および、幅方向における引っ張り応力下で最高のパフォーマンスを示す。<100>のチャネル方向では、NMOSデバイスが、チャネル方向における引っ張り応力下で最高のパフォーマンスを示し、幅方向における応力に対して比較的小さな応答を有する。最後に、<100>のチャネル方向では、PMOSデバイスのパフォーマンスは、チャネル方向における応力に対して比較的小さな応答を示し、幅方向における小さな圧縮応力に対して良好な応答を示す。

10

## 【0009】

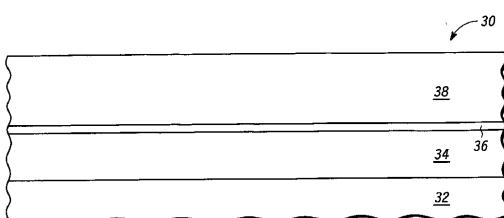

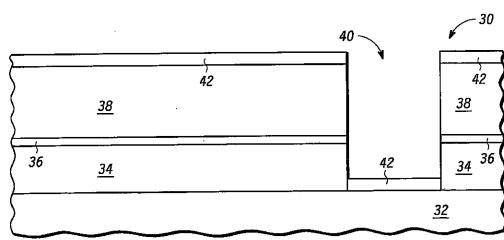

図3ないし7は、本発明のある実施形態による応力効果を最適化するためのデュアルトレンチプロセスを使用して製造された半導体デバイスの断面図である。図3では、半導体デバイス30は、半導体-オン-絶縁体(SOI)基板を含み、例えば、<100>SOI基板が当業者に知られている。SOI基板は、シリコン基板(図示せず)、シリコン基板の上に横たわる埋設酸化物(Box)32、および、Box32の上に横たわるシリコン層34を含む。上に横たわるシリコン層34は、熱酸化物36、例えば、パッド酸化物(pad oxide)である。上に横たわるパッド酸化物36は、窒化シリコン層38である。SOI基板に関しては、Box32は、1350乃至2000オングストロームのオーダーの厚さを有し、シリコン層34は、700乃至1100オングストロームのオーダーの厚さを有する。パッド酸化物36は、90乃至150オングストロームのオーダーの厚さを有する。さらに、窒化シリコン層38は、1000乃至1200オングストロームのオーダーの厚さを有する。ある実施形態では、窒化シリコン層38は、1050乃至1160オングストロームのレンジの厚さを有する。

20

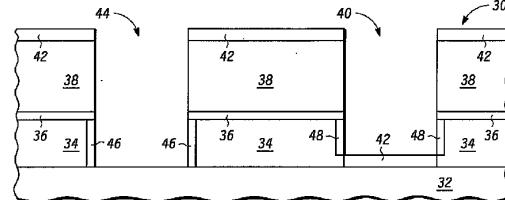

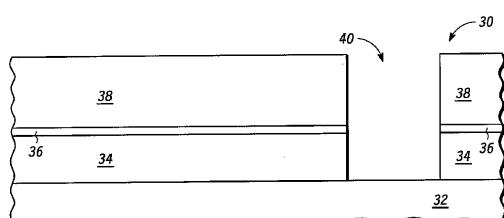

## 【0010】

図4では、第1のトレニチエッティングが、第1のトレニチ40を形成するために実施される。第1のトレニチ40を形成するために、第1のフォトプロセスが用いられる。ある実施形態では、第1のフォトプロセスは、例えば、248nmDUV(深紫外線)パターニングプロセスを含む。当該パターニングステップに続いて、エッティングステップが、第1のトレニチ40を形成するために実行される。

30

## 【0011】

図5では、第1のトレニチエッティングに続いて、ストレッサー/反射防止膜(ARC)薄膜成長が実施される。ストレッサー/ARC薄膜42を形成することは、デュアルユース薄膜を選択的に堆積させることを含む。即ち、ストレッサー/ARC薄膜は、1)ストレッサーおよび2)ARC薄膜のデュアル使用を実行することができるいかなる適当な薄膜をも含むことができ得る。ある実施形態では、ストレッサー/ARC薄膜は、例えば、窒化物からなる。更に、ストレッサー/ARC薄膜42の選択的な堆積は、窒化シリコン層38の露出した部分と、第1のトレニチ40の底部との上に薄膜を堆積することを含む。

40

## 【0012】

可能な変形実施形態では、堆積された層42の代わりに拡散バリアとして、開口部40に側壁スペーサを形成することが可能である。かかる場合には、側壁スペーサを形成する前に、Box層32内に伸びた開口部40に有益ともなり得、ここで側壁スペーサは、シリコン/Box界面をブロックする。

## 【0013】

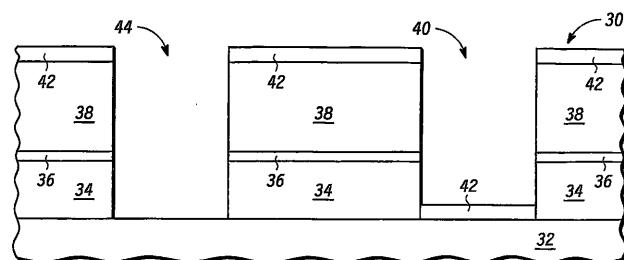

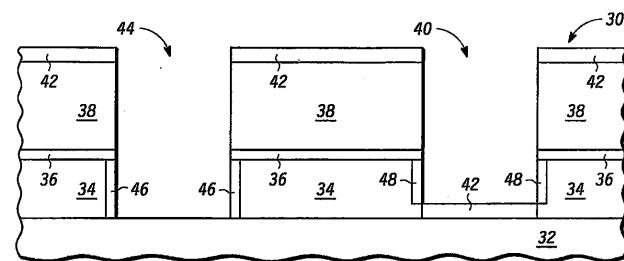

図6では、第2のトレニチエッティングが、第2のトレニチ44を形成することにより実施される。第2のトレニチ44を形成するために、第2のフォトプロセスが使用される。ある実施形態では、第2のフォトプロセスは、例えば、193nmDUV(深紫外線)パターニングプロセスを含む。かかるパターニングステップに続いて、エッティングステップ

50

が、第2のトレンチ44を形成するのに実行される。第1のトレンチの底部と異なり、第2のトレンチの底部は、いなかるストレッサー／ARC薄膜もない。

【0014】

図7では、トレンチライナー(46, 48)が、第1及び第2のトレンチ(40, 44)のそれぞれに形成される。トレンチライナー(46, 48)は、欠陥を外に出し、それぞれのトレンチにおけるシリコンの頂部コーナーを保護するために熱的に成長されたライナーを含む。第2のトレンチ44では、トレンチライナー46は、第2のトレンチ内にシリコン34の頂部から延び、埋設酸化物32まで完全に下がる。更に、第1のトレンチ40の底部の上に横たわるストレッサー／ARC薄膜42の存在の結果として、トレンチライナー48は、第1のトレンチ内にシリコン34で成長するのを妨げられ、埋設酸化物32まで完全に下がる。従って、第1のトレンチ40内のシリコン34の一部は、ストレッサー／ARC薄膜42によって保護される。

10

【0015】

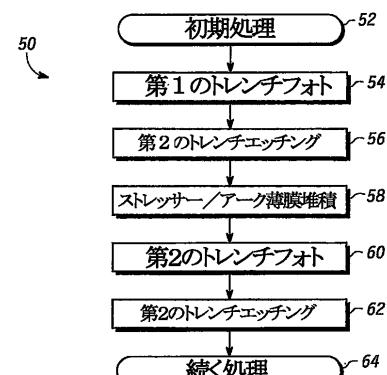

図8は、本発明のある実施形態による応力効果を最適化するためのデュアルトレンチプロセスのフローチャート50である。参照番号52によって示されたステップで初期処理が行われる。ステップ54では、図4について上述したように、第1のトレンチフォトが実行される。ステップ56では、図4について上述したように、第1のトレンチエッチングが、第1のトレンチを形成するために実行される。第1のトレンチエッチングに続いて、ステップ58では、例えば図5について上述したように、選択的なデュアルユース(ストレッサー／ARC薄膜)薄膜堆積が行われる。図6について上述したように、ステップ60では、第2のトレンチフォトが実行される。図6について更に上述したように、ステップ62では、第2のトレンチエッチングが、第2のトレンチを形成するために実行される。ステップ64における第2のトレンチエッチングに続いて、製造されるべき半導体デバイスの特定の要求によって引き続き処理が実行される。例えば、引き続き行われる処理には、図7について上述したように、トレンチライナーの形成を含まれる。

20

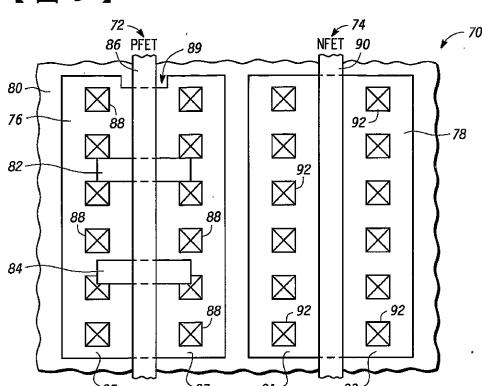

【0016】

図9は、CMOSトランジスタ構造72および74を含む半導体デバイス構造体70の平面図であり、構造体72は、上述したように本発明のある実施形態によってデュアルトレンチ処理を使用して製造された幅方向において制御された応力特性を含む。ある実施形態では、CMOSトランジスタ構造体72および74は、PFETデバイスおよびNFETデバイスをそれぞれ表す。CMOSトランジスタ構造体72および74は、活性化半導体領域76および78をそれぞれ含む。ある実施形態では、活性化半導体領域はシリコンからなる。

30

【0017】

PFET CMOSトランジスタ76の最適化は、参照番号80によって示された第1の応力緩和機構と、第2の応力緩和および容量低減機構(82, 84)を追加することを含み、かかる機構は、幅方向における応力を修正することを提供する。第1の応力緩和機構は、活性化半導体領域76の外側にデュアルユース・ストレッサー／ARC薄膜を有する。更に、第1の応力緩和機構80は、図5について先に議論したストレッサー／ARC薄膜堆積と第1のトレンチエッチングを介して達成される。ある実施形態では、第1の応力緩和機構は窒化物を含む。

40

【0018】

更に、応力緩和及び容量低減機構(82, 84)は、活性化半導体領域76の内側にあり、活性化領域76のソースとドRAINとの間に延びる。活性化領域76の一部は、ゲート電極86と関連するゲート誘電体(図示せず)の下に横たわる。応力緩和及び容量低減機構(82, 84)の一部はまた、ゲート電極86と関連するゲート誘電体(図示せず)の下に横たわる。ゲート電極86は、チャネル方向に延びる長さ寸法Lによって特徴付けられる。ある実施形態では、応力緩和及び容量低減機構(82, 84)は、前述のように、また図6及び7に関して先に議論したように、第2のトレンチエッチングによって活性化半導体材料を引き続き除去することにより形成される。応力緩和及び容量低減機構(8

50

2, 84)はさらに、各トレンチの手伊具をライニングするデュアルユース・ストレッサー/A R C薄膜がないことによって特徴付けられ、更に、各トレンチのトレンチ側壁ライナーは、活性下層材料の頂部から下に横たわる埋設酸化物までそれぞれのトレンチの中で十分に延びる。

【0019】

更に、第1の応力緩和機構80と、応力緩和及び容量低減機構(82, 84)とに関して、各々がトレンチ充填材料をそれぞれ更に含む。特定のトレンチ充填材料は、圧縮または引っ張り応力緩和のいずれかにより、特定のトランジスタアプリケーションに関して所望の追加の応力緩和によって選択される。たとえば、ある実施形態では、トレンチ充填材料は、圧縮応力緩和をもたらす酸化物を含む。別の実施形態では、トレンチ充填材料は、引っ張り応力緩和をもたらす窒化物を含む。10

【0020】

図9をまた参照すると、P F E T C M O Sトランジスタ72が、活性化領域76のソースおよびドレイン領域のそれぞれと接触をするためのコンタクト88を更に有する。P F E T C M O Sトランジスタ72に関して、パフォーマンスの点について先に議論したように、同様に最適化される。

【0021】

図9は、本発明の別の実施形態によるノッチ89を備えたP F E T C M O Sトランジスタ72を更に図示する。すなわち、P F E T C M O Sトランジスタ72は、活性化領域76にノッチ89を含む。ノッチ89は、活性化領域76の一方の端に配置され、ノッチは、P F E T C M O Sトランジスタ72のチャネル領域の一部にわたってかかっている。その存在により、ノッチ89は、所定のC M O Sトランジスタアプリケーションに関して要求されうるような種種のチップの機能的な論点および/または問題点を解決するために活性化領域76の全幅寸法を低減させる。20

【0022】

さらに図9には、N F E T C M O Sトランジスタ74の平面図が図示しており、トランジスタ74は、ゲート電極90および関連するゲート誘電対(図示せず)の下に横たわる活性化領域78を含む。活性化領域78は、幅方向に伸びる幅寸法Wによって特徴づけられ、半導体材料からなる。ゲート電極90は、チャネル方向に伸びる長さ寸法Lによって特徴づけられる。トランジスタ74はまた、活性化半導体領域78のソースおよびドレイン領域91および93のそれぞれと接触するコンタクト92を含む。活性化領域78はまた、デュアルユース・ストレッサー/A R C薄膜からなる第1の応力緩和機構によって取り囲まれることにも注意すべきである。活性化領域78を取り囲む第1の応力緩和機構80の形態は、図5について先に議論したように、第1のトレンチエッティング中およびストレッサー/A R C薄膜堆積中に達成される。30

【0023】

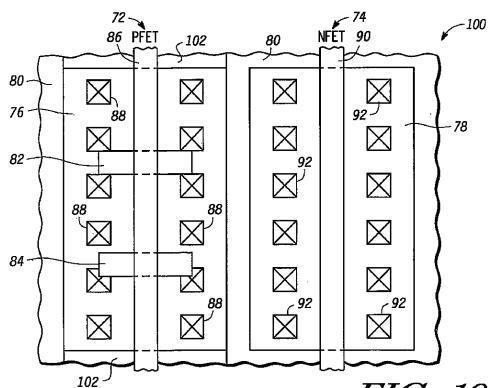

図10は、C M O Sトランジスタ構造72および74を含む半導体デバイス構造体100の平面図であり、構造72は、ここで先に議論したように本発明の別の実施形態によるデュアルトレンチプロセスを使用して製造される幅方向に制御された応力機構を含む。図10の実施形態は、図9について上述した実施形態と似ているが、以下のような差異がある。図10に示すように、構造72は更に、第3の応力緩和および容量低減機構102を含み、かかる機構は、構造72の幅方向における応力の更なる緩和を提供する。第3の応力緩和および容量低減機構102は、活性化領域76の対向する端に配置され、特に、チャネル方向に伸びる活性化領域のエッジに沿って配置される。40

【0024】

ある実施形態では、第3の応力緩和および容量低減機構102は、図6および7を参照して先に議論したように、第2のトレンチエッティングによって活性化半導体材料の除去に続いて形成される。応力緩和および容量低減機構102は更に、それぞれのトレンチの底部にライニングするデュアルユース・ストレッサー/A R C薄膜がないことによって特徴づけられ、更に、各トレンチのトレンチ側壁ライナーが活性化層材料の頂部から下に横た50

わる埋設酸化物まで、各トレンチ内で十分に延びる。

【0025】

更に第1の応力緩和機構80と、応力緩和および容量低減機構(82, 84, 102)に関して、各々はまたトレンチ充填材料を含む。特定のトレンチ充填材料は、圧縮または引っ張り応力緩和のいずれかについて、特定のトランジスタ用途のために所望の追加の応力緩和について選択される。たとえば、ある実施形態では、トレンチ充填材料は、圧縮応力緩和を提供するための酸化物を含む。別の実施形態では、トレンチ充填材料は、引っ張り応力緩和をもたらすチッ化物を含む。

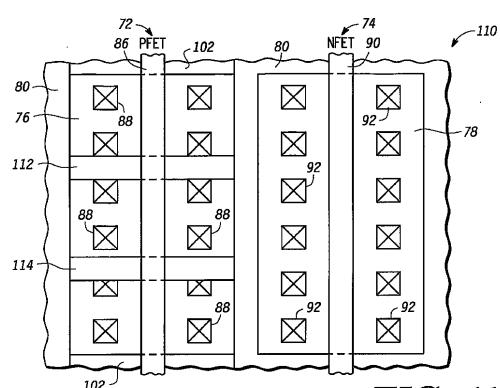

【0026】

図11は、CMOSトランジスタ構造72および74を含む半導体デバイス構造体110の平面図であり、構造72は、本発明の更に別の実施形態によるデュアルトレンチプロセスを使用して製造された幅方向に制御された応力機構を含む。図11の実施形態は図9について先に議論した実施形態と似ているが、以下のような相違点がある。図11に示すように、構造72は更に、別の応力緩和および容量低減機構(112, 114)を含み、該機構は、構造72の幅方向の応力の更なる緩和を提供する。応力緩和および容量低減機構(112, 114)は、活性化領域76にわたって配置され、特に活性化領域にわたって十分に、チャネル方向に延びる。応力緩和および容量低減機構(112, 114)によって分離された活性化領域の結合部分は、上に横たわるメタライゼーションを使用して達成され、たとえば、コンタクトレベルまたは、上に横たわる金属相互接続レベルのメタライゼーションである。

10

20

【0027】

ある実施形態では、応力緩和および容量低減機構(112, 114)は、図6および7について先に議論したように、第2のトレンチエッチングによる活性化半導体材料の除去に続いて形成される。応力緩和および容量低減機構(112, 114)は更に、それぞれのトレンチの底部でライニングするデュアルユース・ストレッサー/AWC薄膜がないことによって特徴づけられ、更に、各トレンチのトレンチ側壁ライナーは、活性化層材料の頂部から下に横たわる埋設酸化物までそれぞれのトレンチ内で十分に延びる。

30

【0028】

更に第1の応力緩和機構80と、応力緩和および容量低減機構(112, 114および102)とに関して、各々はまたトレンチ充填材料を含む。特定のトレンチ充填材料は、圧縮または引っ張り応力緩和のいずれかについて特定のトランジスタ用途に関する所望の追加の応力緩和によって選択される。たとえば、ある実施形態では、トレンチ充填材料は、圧縮応力緩和をもたらす酸化物を含む。別の実施形態では、トレンチ充填材料は、引っ張り応力緩和をもたらす窒化物を含む。

40

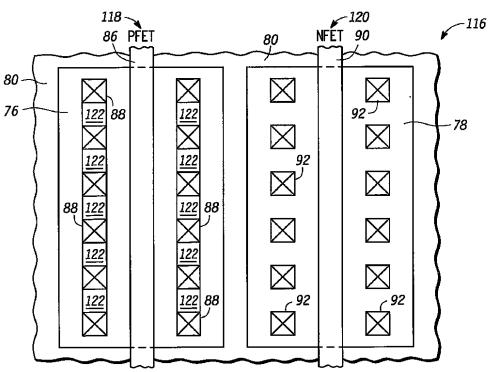

【0029】

図12は、本発明の更に別の実施形態によるデュアルトレンチプロセスを使用して製造されたチャネル方向に制御された応力機構を備えたCMOSトランジスタ構造118および120を含む半導体デバイス構造体116の平面図である。図12の実施形態は、図9について先に議論した実施形態と似ているが、以下のような差異がある。たとえば、<110>SOI基板からなる開始基板では、好適なチャネル応力を提供するのに更なる圧縮応力が望ましい。

【0030】

ある実施形態では、応力緩和および容量低減機構122は、図6および7について先に議論したように、第2のトレンチによって活性化半導体材料を除去することに続いて形成される。応力緩和および容量低減機構122は更に、各々のトレンチの底部をライニングするデュアルユース・ストレッサー/AWC薄膜がないことによって特徴づけられ、更に、活性化層材料の頂部から下に横たわる埋設酸化物まで各トレンチ内で十分に延びる。図12に図示したように、チャネル方向に関する応力緩和および容量低減機構122は、チャネル領域にわたって十分に延びることなく、または、下に横たわるゲート電極86および関連するゲート誘電対(図示せず)にわたることなく、活性化領域76のソース/ドレ

50

イン領域の一部だけの内部に包含される。更に、複数の応力緩和および容量低減機構 122 が、ゲート電極 86 と平行に沿って配置される。

#### 【0031】

更に第 1 の応力緩和機構 80 と、応力緩和および容量低減機構 122 とに関して、各々が更にトレーニング充填材料を含む。特定のトレーニング充填材料は、圧縮または引っ張り応力緩和のいずれかに関する、特定のトランジスタ用途に関する所望の追加の応力緩和によって選択される。たとえば、ある実施形態では、トレーニング充填材料は、圧縮応力緩和を提供するために酸化物を含む。別の実施形態では、トレーニング充填材料は、引っ張り応力緩和を提供するために窒化物を含む。

#### 【0032】

ある実施形態では、方法は、デュアルトレーニングプロセスにおいて選択的にチッ化物を堆積することを用いることを含む。選択的なチッ化物の堆積は、デュアル (248 nm / 193 nm) フォトプロセスで可能なだけでなく、<100> 結晶方位 SOI 基板で最大の応力効果を得るために NFE T および PFE T デバイスで、幅およびチャネル方向に異なる応力を与えることができる。すなわち、チッ化物堆積ステップは、248 nm / 193 nm デュアルトレーニングフォトプロセスを可能にし、選択的トレーニング応力マニュピレーションをも提供する。言い換えれば、本発明の実施形態は、同時に最適化された応力効果を達成しながら、248 nm および 193 nm の両方のフォトプロセスの異なる ARC 要求に取り組むことを同時に提供する。

#### 【0033】

本発明の実施形態では、デュアルトレーニングアプローチ（例えば、デュアルマスクアプローチ）は、幅およびチャネル方向の両方において同時に NFE T および PFE T の両方に関して最適化された応力を提供すること（即ち、もっとも有益な応力を提供すること）ができる。したがって、約 5ないし 7% のオーダーで対応するトランジスタ構造に関するパフォーマンスの改善が期待される。

#### 【0034】

ある実施形態によるデュアルマスクアプローチでは、通常の活性化領域および活性化領域のエッジでのトレーニングパターンが 248 nm マスクを使用してパターンングされ、次いでエッチングされる。次いで、薄い窒化物層（例えば、SiN）が、パターンングされた活性化領域の頂部（即ち、193 nm フォトプロセスで可能である）と、（即ち、圧縮応力を低減するために）トレーニングパターン中に形成されたトレーニングの底部に選択的に堆積される。引き続いて、（即ち、PFE T デバイスの活性化領域内の）1 またはそれ以上の完全に囲まれたカットアウトパターンが、193 nm フォトプロセスを使用してパターンングされる。この方法では、PFE T デバイスは、幅方向において高い圧縮応力が単独に提供される。更に、NFE T デバイス（即ち、幅およびチャネル方向の両方において）および、PFE T デバイス（即ち、チャネル方向において）は、より低い圧縮または引っ張り応力が得られ、NFE T および PFE T デバイスの両方に関して最良である。

#### 【0035】

高パフォーマンス CMOS 技術において、応力エンジニアリングは最も活性化した領域であることに注意すべきである。更に、SOI 基板は、いくつかの一意的な応力効果を有する。本発明の実施形態は、これらの効果の利点を利用する一意的な方法を提供する。更に、デュアルトレーニングプロセスは、たとえば、<100> SOI 基板などの SOI 基板上に特定のデバイスのために異なり、最適化された応力効果カスタマイズ応力を可能にする。更に、異なり最適化された応力効果カスタマイズは、より多いまたはより少ない応力、引っ張りまたは圧縮、異なる領域への適用を含む。

#### 【0036】

ここで議論したように、本発明の実施形態は、高パフォーマンスおよび / または低ダイナミックパワーを要求する SOI 製品に適用可能である。さらに実施形態は、SiGe ストレッサーまたは c-SiGe チャネルなどを使用したより複雑な方法よりもより簡単に実施でき、所望のパフォーマンス利点を得るための方法を提供する。

10

20

30

40

50

**【0037】**

上述のように、種々の実施形態を参照して開示を記載してきた。しかしながら、当該技術分野の当業者は、別途添付の特許請求の範囲の範囲を逸脱することなく、種々の修正および変形をすることができうる。従って、発明の詳細な説明および図面は、本願発明を限定するものではなく例示的なものであり、かかる修正および変形は、本願発明の範囲内に包含されるものである。例えば、本発明は、キャリア移動度がデバイス性能にきわめて重要である半導体デバイス技術に適用することが出来る。

**【0038】**

特定の実施形態に関して、利益、他の利点、および問題解決を開示してきた。しかしながら、かかる利益、利点、問題解決は、特許請求の範囲の全てに生じ、特定の実施形態に限定されるものではない。ここで使用してきた「含む」「有する」などという表現は、非排他的であることを意図しており、ここに記載したエレメントだけでなく他のエレメントも含みうる事を意図しているものである。

10

**【図面の簡単な説明】****【0039】**

【図1】周知の従来技術におけるチャネル方向と幅方向を図示したCMOSトランジスタの平面図である。

20

【図2】種々のチャネル方位とデバイスタイプに関する応力応答特性の表である。

【図3】本発明のある実施形態による応力効果を最適化するためのデュアルトレンチプロセスを使用して製造された半導体デバイスの断面図である。

【図4】本発明のある実施形態による応力効果を最適化するためのデュアルトレンチプロセスを使用して製造された半導体デバイスの断面図である。

【図5】本発明のある実施形態による応力効果を最適化するためのデュアルトレンチプロセスを使用して製造された半導体デバイスの断面図である。

【図6】本発明のある実施形態による応力効果を最適化するためのデュアルトレンチプロセスを使用して製造された半導体デバイスの断面図である。

【図7】本発明のある実施形態による応力効果を最適化するためのデュアルトレンチプロセスを使用して製造された半導体デバイスの断面図である。

【図8】本発明のある実施形態による応力効果を最適化するためのデュアルトレンチプロセスのフローチャートである。

【図9】本発明のある実施形態によるデュアルトレンチプロセスを使用して製造された幅方向における制御された応力特性を備えたCMOSトランジスタ構造を含む、半導体デバイス構造体の平面図である。

【図10】本発明の別の実施形態によるデュアルトレンチプロセスを使用して製造された幅方向における制御された応力特性を備えたCMOSトランジスタ構造を含む、半導体デバイス構造体の平面図である。

【図11】本発明のさらに別の実施形態によるデュアルトレンチプロセスを使用して製造された幅方向における制御された応力特性を備えたCMOSトランジスタ構造を含む、半導体デバイス構造体の平面図である。

【図12】本発明のさらにまた別の実施形態によるデュアルトレンチプロセスを使用して製造された幅方向における制御された応力特性を備えたCMOSトランジスタ構造を含む、半導体デバイス構造体の平面図である。

30

40

【図1】

【図2】

| チャネル<br>方向 | デバイス<br>タイプ | 好適なチャネル<br>応力 | 好適な<br>適応力 |

|------------|-------------|---------------|------------|

| <110>      | NMOS        | 引張            | 小さな感度      |

| <110>      | PMOS        | 圧縮            | 引張         |

| <100>      | NMOS        | 引張            | 小さな感度      |

| <100>      | PMOS        | 小さな感度         | 小さな圧縮      |

【図3】

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

【図7】

【図8】

【図9】

FIG. 9

【図 10】

FIG. 10

【図 12】

FIG. 12

【図 11】

FIG. 11

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                | International application No.<br>PCT/US05/38847 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>IPC: E01L 21/396( 2006.01); E01L 21/76( 2006.01)<br><br>USPC: 438/197,199,200,424,425; 257/213,288,350<br>According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                |                                                 |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>U.S. : 438/197, 199, 200, 424, 425; 257/213, 288, 350                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                |                                                 |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                |                                                 |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>Please See Continuation Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                |                                                 |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                |                                                 |

| Category *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Citation of document, with indication, where appropriate, of the relevant passages                                                                             | Relevant to claim No.                           |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | US 6,482,715 B2 (Park et al.) 19 November 2002 (11.19.2002), Figs. 3A-3G, Col. 2, line 55 - Col. 6, line 45.                                                   | 1-20                                            |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C. <input type="checkbox"/> See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                |                                                 |

| * Special categories of cited documents:<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier application or patent published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed |                                                                                                                                                                |                                                 |

| Date of the actual completion of the international search<br>18 October 2006 (18.10.2006)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Date of mailing of the international search report<br>21 Nov 2006                                                                                              |                                                 |

| Name and mailing address of the ISA/US<br>Mail Stop PCT, Attn: ISA/US<br>Commissioner for Patents<br>P.O. Box 1450<br>Alexandria, Virginia 22313-1450<br>Facsimile No. (571) 273-3201                                                                                                                                                                                                                                                                                                                                                                                                                              | Authorized officer<br><br>Matthew S. Smith<br>Telephone No. (571) 272-1950 |                                                 |

Form PCT/ISA/210 (second sheet) (April 2005)

## INTERNATIONAL SEARCH REPORT

|                                                 |

|-------------------------------------------------|

| International application No.<br>PCT/US05/38847 |

|-------------------------------------------------|

Continuation of B. FIELDS SEARCHED Item 3:

USPAT, USPGPUB, USOCR, EPO, JPO, DERWENT, IBMTDB

((trench recess groove open\$3 hole) near8 (silicon near5 nitride)) and ((stress near5 (layer film material) near5 (trench recess groove open\$3 hole) near8 (silicon near5 nitride))

## フロントページの続き

| (51) Int.Cl.             | F I          | テーマコード(参考) |

|--------------------------|--------------|------------|

| H 01 L 27/08 (2006.01)   | H 01 L 29/78 | 6 1 3 A    |

| H 01 L 21/8238 (2006.01) | H 01 L 27/08 | 3 3 1 E    |

| H 01 L 27/092 (2006.01)  | H 01 L 27/08 | 3 3 1 A    |

|                          | H 01 L 27/08 | 3 2 1 C    |

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IS,IT,LT,LU,LV,MC,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KM,KP,KR,KZ,LC,LK,LR,L

S,LT,LU,LY,MA,MD,MG,MK,MN,MW,MX,MZ,NA,NG,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SM,SY,TJ,

,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,YU,ZA,ZM,ZW

(74)代理人 100096013

弁理士 富田 博行

(74)代理人 100147681

弁理士 夫馬 直樹

(72)発明者 チェン , ジアン

アメリカ合衆国テキサス州 7 8 7 5 0 , オースティン , スイートネス・レーン 8 4 1 3

(72)発明者 ターナー ,マイケル・ディー

アメリカ合衆国テキサス州 7 8 2 0 9 , サン・アノンティオ , パーシング・アベニュー 2 1 9

(72)発明者 ヴァセク , ジェームズ・イー

アメリカ合衆国テキサス州 7 8 7 3 2 , オースティン , ジョン・シンプソン・トレイル 3 9 0 2

F ターム(参考) 5F032 AA03 AA91 AC02 BA01 BB01 CA17 CA20 DA22 DA53

5F048 AA04 AC04 BA10 BA16 BD01 BE03 BG07 BG13

5F110 AA04 BB04 CC02 DD05 DD12 GG01 GG02 GG06 GG12 GG17

GG23 GG25 HM04 NN65 QQ01